SAMSUNG K4S280832A Technical data

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!

K4S280832A CMOS SDRAM

128Mbit SDRAM

4M x 8Bit x 4 Banks

Synchronous DRAM

LVTTL

Revision 0.0

Aug. 1999

* Samsung Electronics reserves the right to change products or specification without notice.

Rev. 0.0 Aug. 1999

K4S280832A CMOS SDRAM

4M x 8Bit x 4 Banks Synchronous DRAM

GENERAL DESCRIPTIONFEATURES

• JEDEC standard 3.3V power supply

• LVTTL compatible with multiplexed address

• Four banks operation

• MRS cycle with address key programs

-. CAS latency (2 & 3)

-. Burst length (1, 2, 4, 8 & Full page)

-. Burst type (Sequential & Interleave)

• All inputs are sampled at the positive going edge of the system

clock.

• Burst read single-bit write operation

• DQM for masking

• Auto & self refresh

• 64ms refresh period (4K cycle)

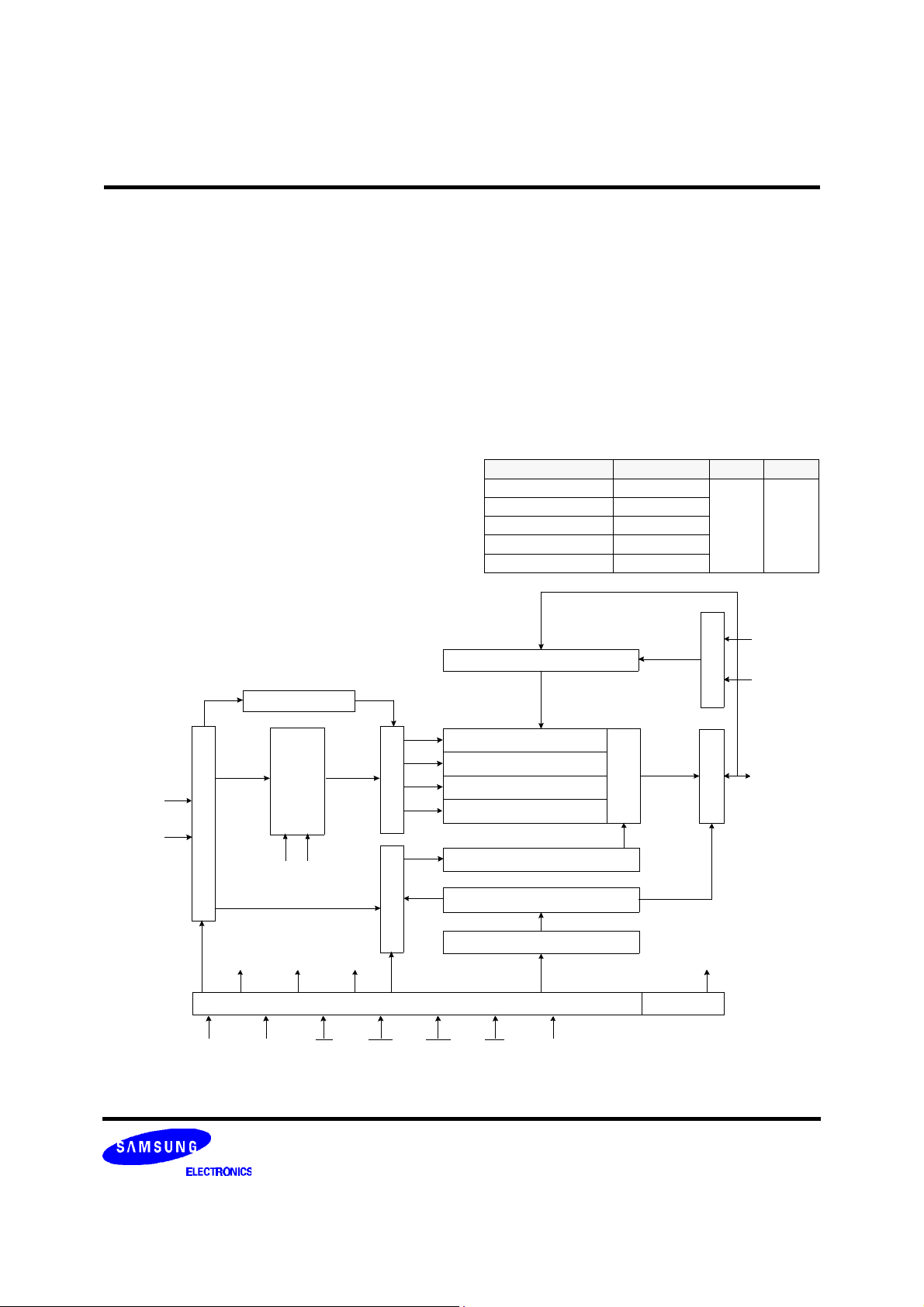

FUNCTIONAL BLOCK DIAGRAM

The K4S280832A is 134,217,728 bits synchronous high data

rate Dynamic RAM organized as 4 x 4,194,304 words by 8 bits,

fabricated with SAMSUNG′s high performance CMOS technology. Synchronous design allows precise cycle control with the

use of system clock I/O transactions are possible on every clock

cycle. Range of operating frequencies, programmable burst

length and programmable latencies allow the same device to be

useful for a variety of high bandwidth, high performance memory system applications.

ORDERING INFORMATION

Part No. Max Freq. Interface Package

K4S280832A-TC/L75 133MHz(CL=3)

K4S280832A-TC/L80 125MHz(CL=3)

K4S280832A-TC/L1H 100MHz(CL=2)

K4S280832A-TC/L1L 100MHz(CL=3)

K4S280832A-TC/L10 66MHz(CL=2 &3)

LVTTL

54

TSOP(II)

CLK

ADD

Data Input Register

Bank Select

Refresh Counter

Row Buffer

Address Register

LRAS

LCBR

LCKE

LRAS LCBR LWE LDQM

CLK CKE CS RAS CAS WE DQM

Row Decoder Col. Buffer

Latency & Burst Length

Programming Register

LCAS LWCBR

Timing Register

4M x 8

4M x 8

4M x 8

4M x 8

Column Decoder

LWE

LDQM

Sense AMP

Output BufferI/O Control

DQi

* Samsung Electronics reserves the right to change products or specification without notice.

Rev. 0.0 Aug. 1999

K4S280832A CMOS SDRAM

PIN CONFIGURATION (Top view)

VDD

A10/AP

PIN FUNCTION DESCRIPTION

DQ0

VDDQ

N.C

DQ1

VSSQ

N.C

DQ2

VDDQ

N.C

DQ3

VSSQ

N.C

VDD

N.C

WE

CAS

RAS

CS

BA0

BA1

A0

A1

A2

A3

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

VSS

DQ7

VSSQ

N.C

DQ6

VDDQ

N.C

DQ5

VSSQ

N.C

DQ4

VDDQ

N.C

VSS

N.C/RFU

DQM

CLK

CKE

N.C

A11

A9

A8

A7

A6

A5

A4

VSS

54Pin TSOP (II)

(400mil x 875mil)

(0.8 mm Pin pitch)

Pin Name Input Function

CLK System clock Active on the positive going edge to sample all inputs.

CS Chip select

CKE Clock enable

A0 ~ A11 Address

BA0 ~ BA1 Bank select address

RAS Row address strobe

CAS Column address strobe

WE Write enable

DQM Data input/output mask

DQ0 ~ 7 Data input/output Data inputs/outputs are multiplexed on the same pins.

VDD/VSS Power supply/ground Power and ground for the input buffers and the core logic.

VDDQ/VSSQ Data output power/ground

N.C/RFU

No connection

/reserved for future use

Disables or enables device operation by masking or enabling all inputs except

CLK, CKE and DQM

Masks system clock to freeze operation from the next clock cycle.

CKE should be enabled at least one cycle prior to new command.

Disable input buffers for power down in standby.

Row/column addresses are multiplexed on the same pins.

Row address : RA0 ~ RA11, Column address : CA0 ~ CA9

Selects bank to be activated during row address latch time.

Selects bank for read/write during column address latch time.

Latches row addresses on the positive going edge of the CLK with RAS low.

Enables row access & precharge.

Latches column addresses on the positive going edge of the CLK with CAS low.

Enables column access.

Enables write operation and row precharge.

Latches data in starting from CAS, WE active.

Makes data output Hi-Z, tSHZ after the clock and masks the output.

Blocks data input when DQM active.

Isolated power supply and ground for the output buffers to provide improved noise

immunity.

This pin is recommended to be left No Connection on the device.

Rev. 0.0 Aug. 1999

Loading...

Loading...