Features

• Pixel Size: 11 µm x 13 µm (13 µm Pitch)

• High Data Output Rate: 20 MHz

• High Responsivity and Resolution Over a Wide Spectral Range: from Blue (400 nm) up

to Near Infrared (1,100 nm)

• Low Dark Signal and Improved Uniformity

• Low Temporal Noise and High Dynamic Range: Over 6000/1

• Ease and Flexibility of Operation:

– Only Two External Basic Drive Clocks

– Choice of Internal or External Sampling and Reset

• 28-lead DIL Package

• Available with Standard Window or Antireflective Window in the Bandwidth 450 to

750 nm

Pin Identification

Pin Number Symbol Designation

2V

3

4S

5

9V

Φ

ECHA

Φ

Φ

OSA

ECHA

RA

DD

10 TP3 Test Point 3

11 TP2 Test Point 2

12 VT Register and Photosensitive Zone DC Bias

13 TP1 Test Point 1

14, 15, 28 V

16 V

18

19

20 V

21

24 S

25

26 V

27 V

Φ

Φ

Φ

Φ

Φ

ECHB

SS

INH

P

T

GS

RB

ECHB

OSB

DR

1, 6, 7, 8, 17, 22, 23 DNC Do not Connect

Video Output S ignal A (Odd Channel)

A Sample-and-hold Gate Input Channel

A Internal S ampling Clock Output Channel

A External Reset Clock Input Channel

Output Amplifier Drain And Internal Logic Supply

Substrate Bias (Ground)

Internal Sampling Clock Inhibiting Input (Dc Bias)

Transfer Clock

Register Transport Clock

Output Gate DC Bias

B External Reset Clock Output Channel

B Internal S ampling Clock Output Channel

B Sample-and-hold Gate Input Channel

Video Output Signal B (Even Channel)

Reset DC Bias

Linear CCD

Image Sensor

(2048 Pixels)

TH7841A

DNC

VOSA

ΦECHA

SΦECHA

ΦRA

DNC

DNC

DNC

VDD

TP3

TP2

VT

TP1

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VSS

VDR

VOSB

ΦECHB

SΦECHB

DNC

DNC

ΦRB

VGS

ΦT

ΦP

DNC

VINH

VSS

Rev. 1998A–IMAGE–05/0 2

1

T

Absolute Maximum Ratings*

Storage Temperature ..................................... -55°Cto+150°C

Operating Temperature ........................................0°Cto+70°C

Thermal Cycling..........................................................15°C/mn

Maximum Voltages:

• Pins: 3, 5, 9, 10, 11, 13,

16, 19, 20, 21, 25, 27........................................-0.3V to +18V

• Pins: 12. 18 ...................................................... -0.3V to +16V

*NOTICE: Stresses above those listed under ABSOLUTE

MAXIMUM RATINGS may cause permanent

device failure. Functionality at or above these

limits is not implied. Exposure to absolute maximum ratings for extended periods may affect

device reliability.

• Pins: 14, 15, 28 ................................................................. 0V

Operating Range Operating range defines the temperature limits between which the functionality is guar-

anteed: 0°Cto70°C.

Operating Precautions

Shorting the video output to VSSto VDD, even temporarily, can permanently damage the

output amplifier.

2

TH7841A

1998A–IMAGE–05/02

Operating Conditions (T = 25°C)

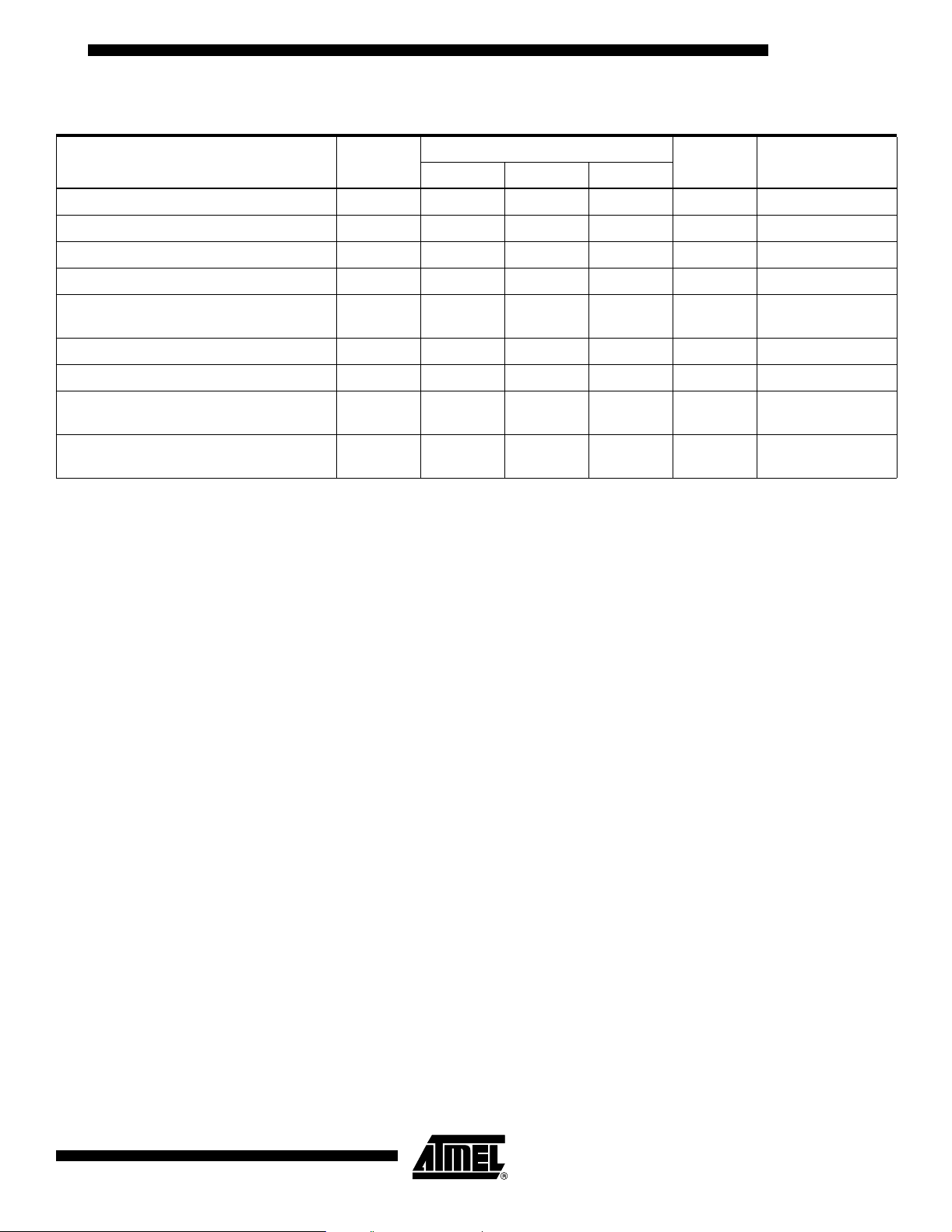

Table 1. DC Characteristics

TH7841A

Value s

Parameter Symbol

Output Amplifier Drain Supply V

Reset DC Bias V

Output Gate DC Bias V

Photosensitive Zone and

Register DC Bias

Substrate Bias V

DD

DR

GS

V

T

SS

14 15 16 V

12 13 14.5 V

5.566.5V

66.57 V

0.0 0.0

Te s t P o in t 1 T P 1 V

Test Points 2 and 3 TP2, TP3 V

Notes: 1. It is recommended to maintain VDRat VDD-2V.

2. V

nominal =

T

VΦT()high VΦT()low+

------------------------------------------------------------ 5%±

2

3. No use for operation – For testing purpose only.

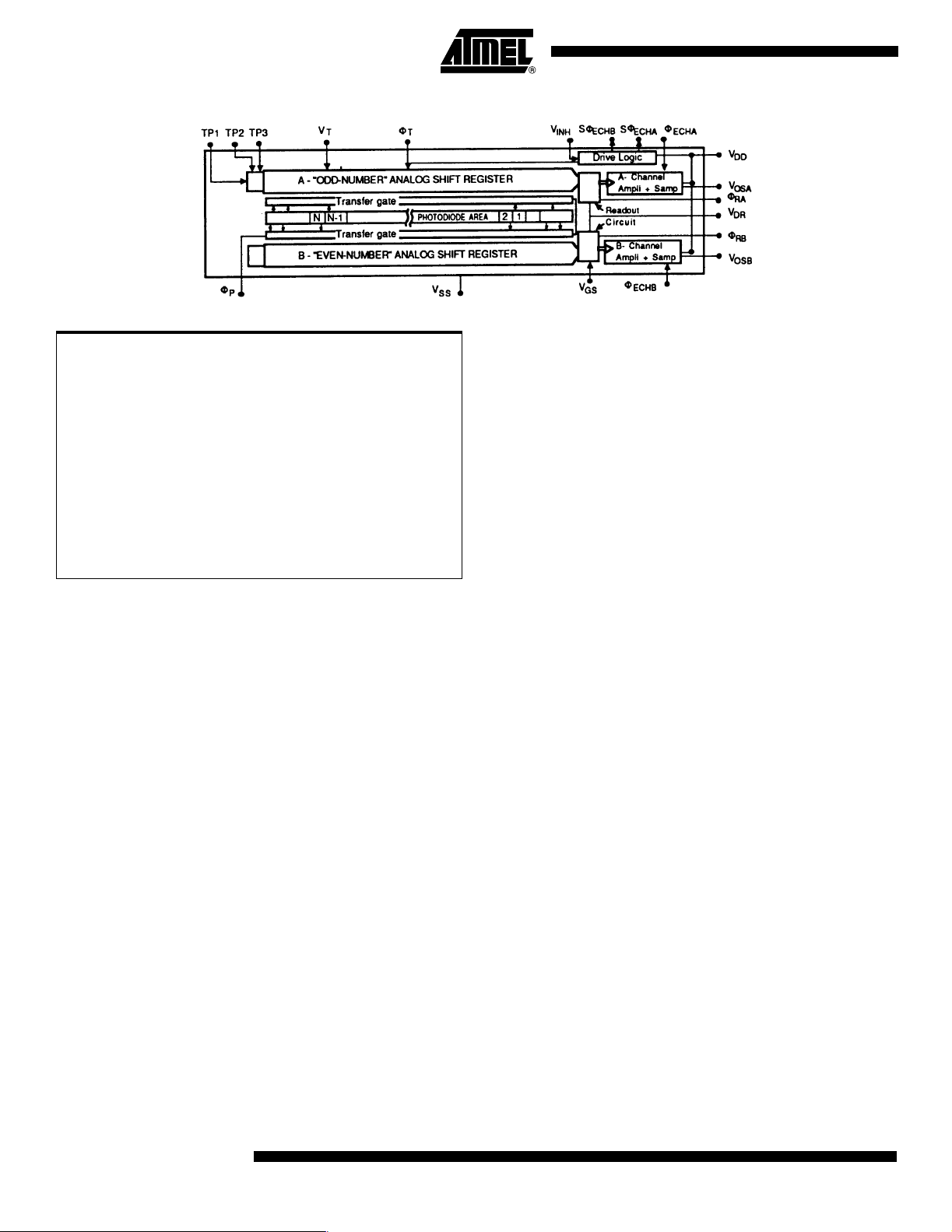

Basic Internal Configuration

SΦ

SΦ

ECHA

ECHB

and Φ

and Φ

RA

RB

internal to TH7841A

DD

SS

Unit NoteMin Typ Max

(1)

(2)

V

V

(3)

(3)

1998A–IMAGE–05/02

Table 2. Selection of Nominal Mode

Option Implementation Note

V

(16) Connected to V

INH

Internal Sampling

SΦ

SΦ

ECHA

ECHB

(4) and Φ

(24) and Φ

Internal Reset ΦRA(5) and ΦRB(21) Connected to VDD

Note: 1. Make the straps as short as possible to avoid any parasitic coupling to these connec-

tions. The load capacitance introduced by the strap should not exceed 5 pF.

(3) Strapped

ECHA

ECHB

SS

(25) Strapped

(1)

3

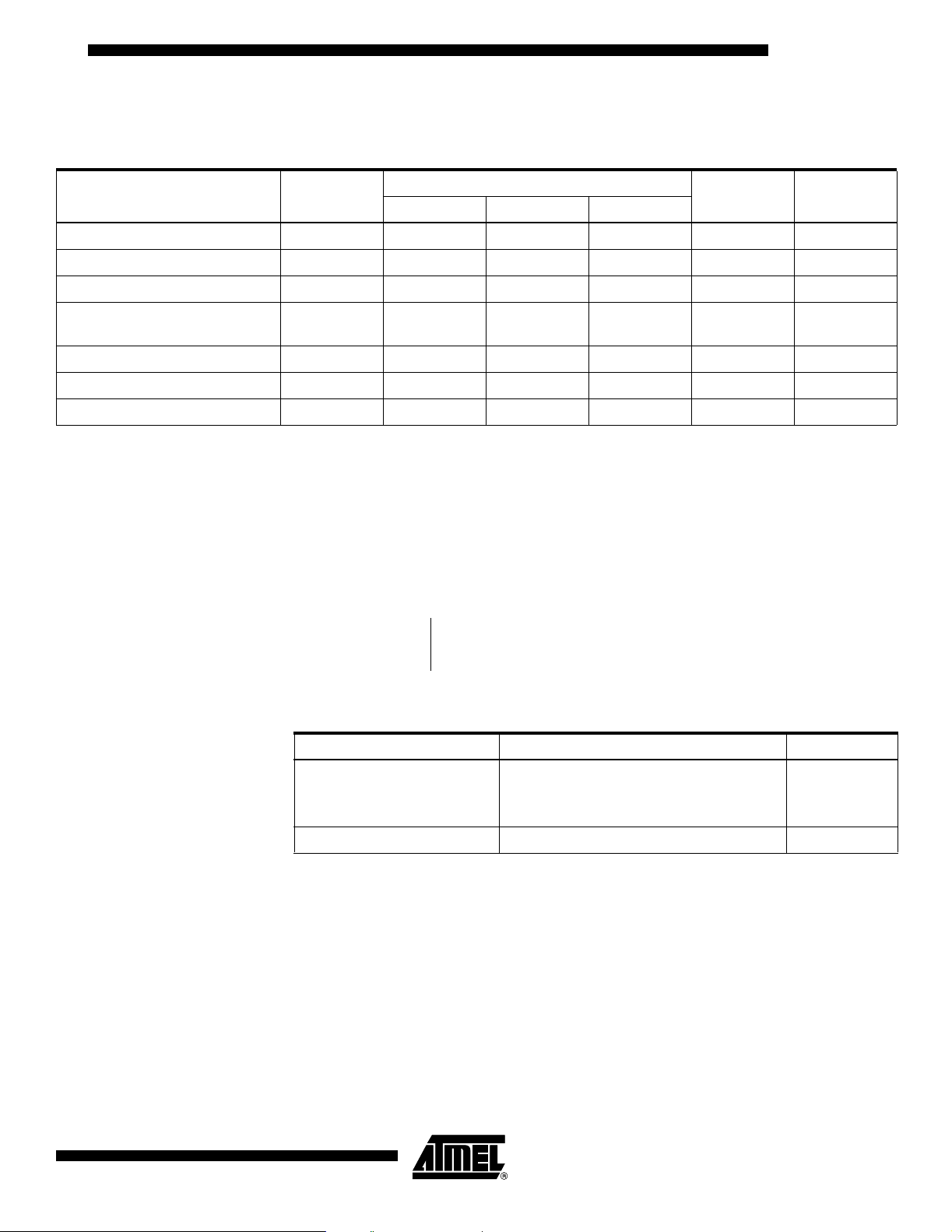

Figure 1. Timing Diagram — Clocks and Video Output Timing Diagram in Internal Sampling Mode

Table 3. Drive Clock Characteristics (see Figure 1)

Value s

Parameter Symbol Logic

Transfer Clock

Φ

Register Transport Clock Low 0.0 0.4 0.6

Register Transport Clock

Capacitance

Transfer Clock Capacitance CΦ

PΦT

CΦ

T

P

High 12 13 14 V

800 1200 pF

200 300 pF

Note: 1. Transients under 0.0V in the clock pulses will lead to charge injection, causing a localized increase in the dark signal if such

spurious negative transients are present, they can be suppressed by inserting a serial resistor of appropriate value (typically

20 to 100Ω) in the corresponding driver output.

4

TH7841A

Unit NoteMin Typ Max

(1)

1998A–IMAGE–05/02

Table 4. Static and Dynamic Electrical Characteristics

Parameter Symbol

TH7841A

Value s

Unit NoteMin Typ Max

DC Output Level V

Output Impedance Z

REF

S

81012V

500 Ω

Register Single-stage Transfer Efficiency CTE 99.992 99.998 % V

Max. Data Output Frequency FSmax. 12 20 MHz

Input Current on Pins: 3, 5, 10,11,12, 13,

18, 19, 20, 21, 25

Peak Current Sink on Φ

Peak Current Sink on Φ

Clock (IΦT)

T

Clock (IΦP)

P

Output Amplifier Drain Supply Current I

Static Power Dissipation P

Ie 2 µA

P

P

DD

D

500 mA t

125 mA t

17 mA

255 300 mW

Notes: 1. VOS= average video output voltage. Measurement excludes first and last pixels.

2. F

=2FΦT. The minimum clock frequency is limited by the increase in dark signal.

S

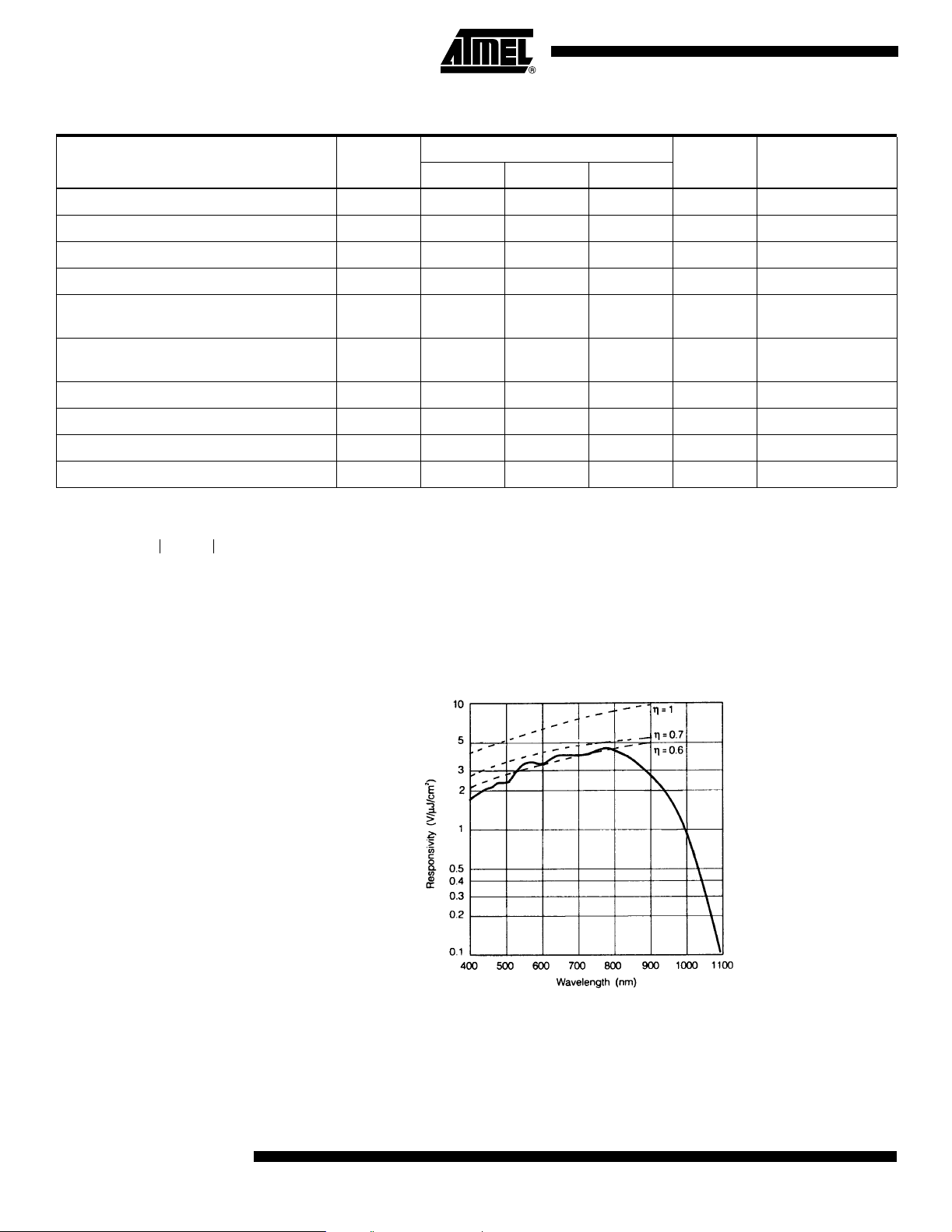

Electro-optical Performance

General measurement conditions: TC=25°C; Ti=1ms;FΦT=2.5MHz.

Light source: tungsten filament lamp (2854 K) + BG 38 filter (2 mm thick) + F/3.5 aperture. The filter limits the spectrum to 700 nm; in these conditions, 1 µJ/cm

to 3.5 lux.s.

Typical operating conditions; internal clock mode (see Table 2).

(1)

=1V

OS

(2)

Ve = 1 5V

All other pins: 0V

=15ns

rise

=15ns

rise

=0V

V

INH

V

=15V

DD

=0V

V

INH

V

=15V

DD

2

corresponds

First and last pixels, as well as reference elements, are excluded from the specification.

Measurements taken on each output in succession.

1998A–IMAGE–05/02

5

Table 5. Electro-optical Performance

Value s

Parameter Symbol

Saturation Output Voltage V

Saturation Exposure E

SAT

SAT

1.3 1.8 2.2 V

0.33 µJ/cm

Responsivity R 2.5 2.9 V/µJ/cm

Responsivity Unbalance ∆R/R 2 8 %

Unit NoteMin Typ Max

(1)(2)

2

2

(3)

Photo-response No-uniformity Peak-topeak

Contrast Transfer Function at FN

(38 I p/mm)

PRNU ±5 ±10 % V

CTF 70 % V

Temporal Noise in Darkness 160 µVrms

Dynamic Range (Relative to rms Noise) DR 3000 6000

Average Dark Signal V

DS

0.08 0.5 mV

Dark Signal Non-uniformity DSNU 0.15 0.5 mV

Notes: 1. Value measured with respect to zero reference level (see Figure 1).

2. Conversion factor is typically 1.1 µV/e-.

3. ∆R/R is defined as

200 RA RB–

---------- ------------- -----------

RA RB+

where RA is responsivity of video output A

RB is responsivity of video output B

4. Measured in Correlated Double Sampling (C.D.S.) mode.

Figure 2. Typical Spectral Response

OS

VOS=50mVto1V

= 0.75V

OS

(4)

(1)

6

TH7841A

1998A–IMAGE–05/02

Figure 3. CTF Typical Curves (2854 K Source)

TH7841A

Electro-optical

Performance Without

Infrared Cut-off

The TH7841A special semiconductor process exploits the silicon’s high near infrared

sensitivity while maintaining good imaging performance in terms of response uniformity

and resolution. Typical changes in performance with and without IR filtering are summarized below.

Filtering

With IR Cut-off Filter No IR Cut-off Filter

Average Video Signal Due To a Given Scene Illumination V

PRNU (Single Defects Excluded) ±5% ±5%

CTF at Nyquist Frequency 70% 50%

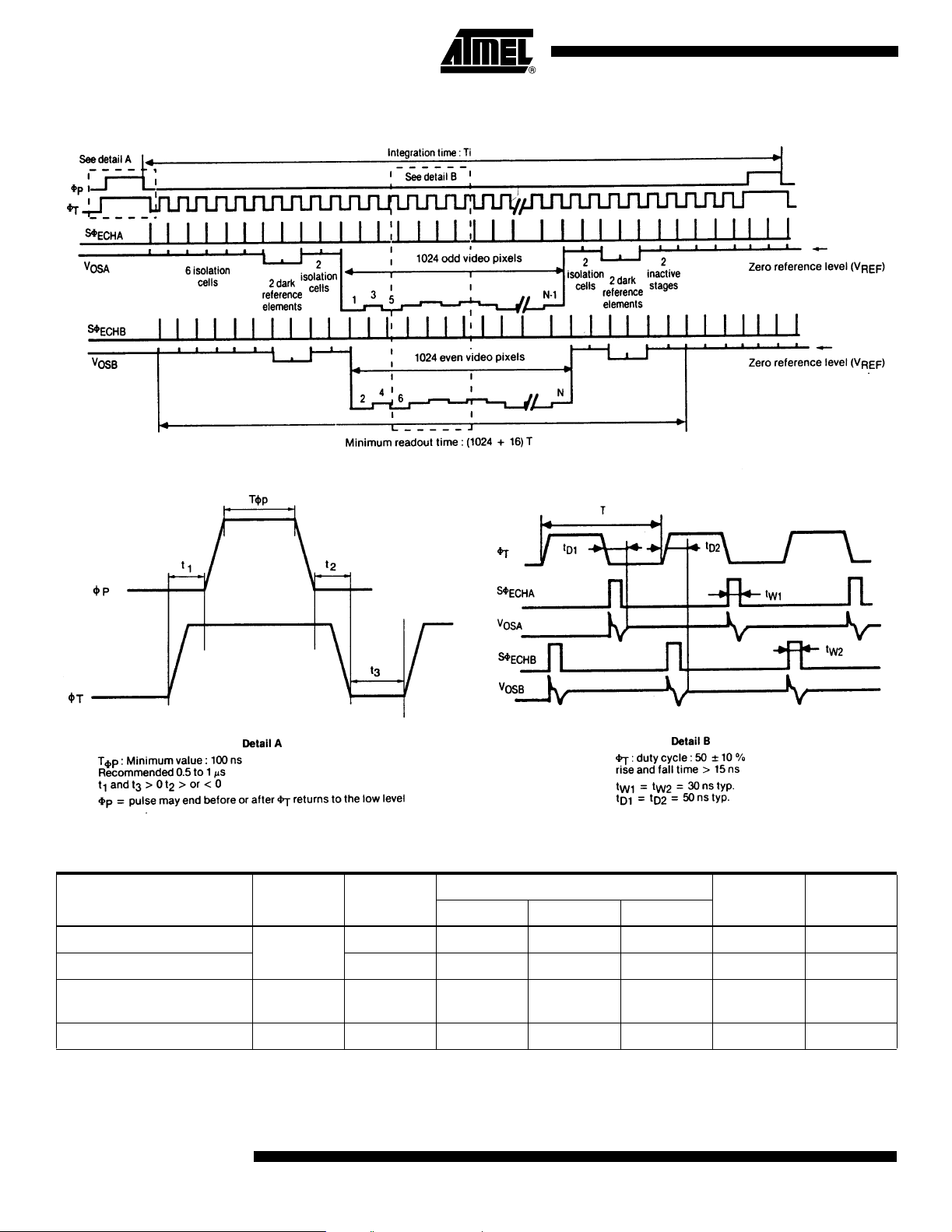

Complementary Operating Modes

The TH7841A may be used in several configurations in regards to video output sampling and charge sensing reset.

1. Sampling options

Inhibition of internal sampling pulses allows two possibilities:

a. no sampling: video output delivered in unsampled form,

b. sampling by external clocks: external sampling pulses directly applied to Φ

Φ

inputs.

ECHB

If internal sampling clocks SΦ

unpower the corresponding clock drivers, as this will greatly reduce on-chip power

consumption.

2. External reset position

ECHA

OS

and SΦ

are not used, it is recommended to

ECHB

VOSx4

ECHA

,

1998A–IMAGE–05/02

The position and period of the charge reset clocks may be optimized by using external

clocks on ΦRAand ΦRBinputs. This is especially interesting to optimize the video outputs

for Correlated Double Sampling (in order to reduce noise and improve S/N Ratio).

Control signals to be applied in the different configurations are shown in Table 6.

7

Table 6. Selection of Operating Modes

Option Implementation Note

Φ

No Sampling

Sampling By External Clocks

Reset Control By External Clocks

(3) and Φ

ECHA

S

Φ

(4) and SΦ

ECHA

(16) Connected to V

V

INH

Sampling Clocks Connected to

SΦ

V

Ext.

Ext.

and SΦ

ECHA

(16) Connected to V

INH

Φ

on ΦRA(5) Input

RA

Φ

on ΦRB(21) Input

RB

(25) Connected to VDD

ECHB

(24) Unconnected

ECHB

DD

Φ

Unconnected

ECHB

DD

ECHA

- Φ

ECHB

(1)

See Figure 4 for sampling

clock timing

SeeFigure4for

reset clock timing

Note: 1. Drain supply current IDDdecreases from 10 mA to 8 mA typically when internal sampling clock is disabled (V

15V).

Table 7. External ΦRA, ΦRB, ΦECHA, ΦECHB Clocks Characteristics

Valu es

(1)

INH=VDD

=

Parameter Symbol Logic

External Reset Clock

Sampling Clock

Reset And Sampling Clock

Capacitance

Φ

Φ

RA

ECHA

C

CΦ

CΦ

CΦ

, ΦRB,

, Φ

Φ

RA

RB

ECHA

ECHB

ECHB

High 12 13 14 V

Low 0.0 0.4 0.6 V

10 15 pF

Insertion of a serial resistor (typically 100Ω) at the driver output avoids spurious negative transients.

UnitMin Typ Max

8

TH7841A

1998A–IMAGE–05/02

TH7841A

Figure 4. Timing Diagram — Clocks and Video Output Timing Diagram With and Without On-chip Sampling

Table 8. Performance Improvement with External ΦRA, ΦRBConfiguration

Value s

Parameter Symbol

Saturation Output Voltage V

Responsivity R 5.0 V/µJ/cm

Dynamic Range DR 8,000

Notes: 1. Electro-optical performances obtained with complementary modes are not guaran-

teed for standard products.

2. The Conversion factor is typically 1.8 µV/e-.

SAT

2.0 V

(1)(2)

Unit(Typ)

2

1998A–IMAGE–05/02

9

Packaging Information

TH 7841A with standard window.

Z = 1.28 ± 0.23

2.16

Notes: 1. If an optical reference is needed, it is recommended to use the window face plane.

2. Variation of Z (azimuth) on the photosensitive area of a device is

3. Variation of Y between the first and the last pixel of the linear area is

≤ 0.1 mm

≤ ±130 µm.

Ordering Code The ordering code is: TH7841 ACC

10

TH7841A

1998A–IMAGE–05/02

TH7841A With Antireflective Window

Improvements in the bandwidth 450-750 nm:

• 5% increase in responsivity (typical value: 3.0 V/µJ/cm

• limitation of the parasitic reflections.

Package Drawing

TH7841A

2

).

2.16

Notes: 1. If an optical reference is needed, it is recommended to use the window face plane.

2. Variation of Z (azimuth) on the photosensitive area of a device is

3. Variation of Y between the first and the last pixel of the linear area is

≤ 0.1 mm

≤ ±130 µm.

Ordering Code The ordering code is: TH7841 ACC-R

1998A–IMAGE–05/02

11

Atmel Headquarters Atmel Operations

Corporate Headquarters

2325 Orchard Parkway

San Jose, CA 95131

TEL 1(408) 441-0311

FAX 1(408) 487-2600

Europe

Atmel Sarl

Route des Arsenaux 41

Case Postale 80

CH-1705 Fribourg

Switzerland

TEL (41) 26-426-5555

FAX (41) 26-426-5500

Asia

Room 1219

Chinachem Golden Plaza

77 Mody Road Tsimhatsui

East Kowloon

Hong Kong

TEL (852) 2721-9778

FAX (852) 2722-1369

Japan

9F, Tonetsu Shinkawa Bldg.

1-24-8 Shinkawa

Chuo-ku, Tokyo 104-0033

Japan

TEL (81) 3-3523-3551

FAX (81) 3-3523-7581

Memory

2325 Orchard Parkway

San Jose, CA 95131

TEL 1(408) 441-0311

FAX 1(408) 436-4314

Microcontrollers

2325 Orchard Parkway

San Jose, CA 95131

TEL 1(408) 441-0311

FAX 1(408) 436-4314

La Chantrerie

BP 70602

44306 Nantes Cedex 3, France

TEL (33) 2-40-18-18-18

FAX (33) 2-40-18-19-60

ASIC/ASSP/Smart Cards

Zone Industrielle

13106 Rousset Cedex, France

TEL (33) 4-42-53-60-00

FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd.

Colorado Springs, CO 80906

TEL 1(719) 576-3300

FAX 1(719) 540-1759

Scottish Enterprise Technology Park

Maxwell Building

East Kilbride G75 0QR, Scotland

TEL (44) 1355-803-000

FAX (44) 1355-242-743

RF/Automotive

Theresienstrasse 2

Postfach 3535

74025 Heilbronn, Germany

TEL (49) 71-31-67-0

FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd.

Colorado Springs, CO 80906

TEL 1(719) 576-3300

FAX 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom

Avenue de Rochepleine

BP 123

38521 Saint-Egreve Cedex, France

TEL (33) 4-76-58-30-00

FAX (33) 4-76-58-34-80

e-mail

literature@atmel.com

Web Site

http://www.atmel.com

© Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard warranty

whichisdetailedinAtmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors

which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does

not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted

by the Company in connection w ith the sale of Atmel products, expressly or by implication. Atmel’s products are not authorized for use as critical

components in life support devices or systems.

AT ME L®is the registered trademark of Atmel.

Other terms and product names may be the trademarks of others.

Printed on recycled paper.

1998A–IMAGE–05/02 0M

Loading...

Loading...