Page 1

查询UDA1355H供应商

INTEGRATED CIRCUITS

DATA SH EET

UDA1355H

Stereo audio codec with SPDIF

interface

Preliminary specification 2003 Apr 10

Page 2

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

CONTENTS

1 FEATURES

1.1 General

1.2 Control

1.3 IEC 60958 input

1.4 IEC 60958 output

1.5 Digital I/O interface

1.6 ADC digital sound processing

1.7 DAC digital sound processing

2 GENERAL DESCRIPTION

3 ORDERING INFORMATION

4 QUICK REFERENCE DATA

5 BLOCK DIAGRAM

6 PINNING

7 FUNCTIONAL DESCRIPTION

7.1 IC control

7.2 Microcontroller interface

7.3 Clock systems

7.4 IEC 60958 decoder

7.5 IEC 60958 encoder

7.6 Analog input

7.7 Analog output

7.8 Digital audio input and output

7.9 Power-on reset

8 APPLICATION MODES

8.1 Static mode pin assignment

8.2 Static mode basic applications

8.3 Microcontroller mode pin assignment

8.4 Microcontroller mode applications

9 SPDIF SIGNAL FORMAT

9.1 SPDIF channel encoding

9.2 SPDIF hierarchical layers

9.3 Timing characteristics

10 L3-BUS DESCRIPTION

10.1 Device addressing

10.2 Register addressing

10.3 Data write mode

10.4 Data read mode

11 I2C-BUS DESCRIPTION

11.1 Characteristics

11.2 Bit transfer

11.3 Byte transfer

11.4 Data transfer

11.5 Register address

11.6 Device address

11.7 Start and stop conditions

11.8 Acknowledgment

11.9 Write cycle

11.10 Read cycle

12 REGISTER MAPPING

12.1 Address mapping

12.2 Read/write registers mapping

12.3 Read registers mapping

13 LIMITING VALUES

14 THERMAL CHARACTERISTICS

15 CHARACTERISTICS

16 TIMING CHARACTERISTICS

17 PACKAGE OUTLINE

18 SOLDERING

18.1 Introduction to soldering surface mount

packages

18.2 Reflow soldering

18.3 Wave soldering

18.4 Manual soldering

18.5 Suitability of surface mount IC packages for

wave and reflow soldering methods

19 DATA SHEET STATUS

20 DEFINITIONS

21 DISCLAIMERS

22 PURCHASE OF PHILIPS I2C COMPONENTS

2003 Apr 10 2

Page 3

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

1 FEATURES

1.1 General

• 2.7 to 3.6 V power supply

• Integrated digitalinterpolator filter and Digital-to-Analog

Converter (DAC)

• 24-bit data path in interpolator

• No analog post filtering required for DAC

• Integrated Analog-to-Digital Converter (ADC),

Programmable Gain Amplifier (PGA) and digital

decimator filter

• 24-bit data path in decimator

• Master or slave mode for digital audio data I/O interface

• I2S-bus, MSB-justified, LSB-justified 16, 18, 20,

and 24 bits formats supported on digital I/O interface.

1.2 Control

• Controlled by means of static pins or microcontroller

(L3-bus or I2C-bus) interface.

1.3 IEC 60958 input

• On-chip amplifier for converting IEC 60958 input to

CMOS levels

• Supports level I, II and III timing

• Selectable IEC 60958 input channel, one of four

• Supports input frequencies from 28 to 96 kHz

• Lock indication signal available on pin LOCK

• 40 status bits can be read for left and right channel via

L3-bus or I2C-bus

• ChannelstatusbitsavailableviaL3-busorI2C-bus:lock,

pre-emphasis, audio sample frequency, two channel

Pulse Code Modulation (PCM) indication and clock

accuracy

• Pre-emphasis information of incoming IEC 60958

bitstream available in register

• Detection of digital data preamble, such as AC3,

available on pin in microcontroller mode.

1.4 IEC 60958 output

• 32, 44.1 and 48 kHz output frequencies (including

double and half of these frequencies) supported in

microcontroller mode

• Via microcontroller, 40 status bits can be set for left and

right channel.

1.5 Digital I/O interface

• Supports sampling frequencies from 16 to 100 kHz

• Supported static mode:

–I2S-bus format

– LSB-justified 16 and 24 bits format

– MSB-justified format.

• Supported microcontroller mode:

–I2S-bus format

– LSB-justified 16, 18, 20 or 24 bits format

– MSB-justified format.

• BCKand WS signals can be slave or master,depending

on application mode.

1.6 ADC digital sound processing

• Supports sampling frequencies from 16 to 100 kHz

• Analogfront-end includes a 0 to +24 dB PGA in steps of

3 dB, selectable via microcontroller interface

• Digital independent left and right volume control of

+24 to −63.5 dB in steps of 0.5 dB via microcontroller

interface

• Bitstream ADC operating at 64f

• Comb filter decreases sample rate from 64fsto 8f

• Decimator filter (8fsto fs) made of a cascade of three

FIR half-band filters.

s

s

• CMOS output level converted to IEC 60958 output

signal

• Full-swing digital signal, with level II timing using crystal

oscillator clock

• 32, 44.1 and 48 kHz output frequencies supported in

static mode

2003 Apr 10 3

1.7 DAC digital sound processing

• Digital de-emphasis for 32, 44.1, 48 and 96 kHz audio

sampling frequencies

• Automatic de-emphasis when using IEC 60958 to DAC

• Soft mute made of a cosine roll-off circuit selectable via

pin MUTE or L3-bus interface

Page 4

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

• Programmable digital silence detector

• Interpolating filter (fsto 64fs or fsto 128fs) comprising a

recursive and a FIR filter in cascade

• Selectable fifth-order noise shaper operating at 64fs or

third-order noise shaper operating at 128fs(specially for

low sampling frequencies, e.g. 16 kHz) generating

bitstream for DAC

• Filter Stream DAC (FSDAC)

• In microcontroller mode:

– Left and right volume control (for balance control)

0to−78 dB and −∞

– Left and right bass boost and treble control

– Optional resonant bass boost control

– Mixing possibility of two data streams.

2 GENERAL DESCRIPTION

The UDA1355H is a single-chip IEC 60958 decoder and

encoderwith integrated stereo digital-to-analogconverters

and analog-to-digital converters employing bitstream

conversion techniques.

The UDA1355H has a selectable one-of-four SPDIF input

(accepting level I, II and III timing) and one SPDIF output

which can generate level II output signals with CMOS

levels. In microcontroller mode the UDA1355H offers a

large variety of possibilities for defining signal flows

throughtheIC, offering a flexible analog, digital and SPDIF

converter chip with possibilities for off-chip sound

processing via the digital input and output interface.

A lock indicator is available on pin LOCK when the

IEC 60958 decoder and the clock regeneration

mechanism is in lock. By default the DAC output and the

digital data interface output are muted when the decoder

is not in lock.

TheUDA1355H contains two clock systems which can run

at independent frequencies, allowing to lock-on to an

incoming SPDIF or digital audio signal, and in the mean

time generating a stable signal by means of the crystal

oscillator for driving, for example, the ADC or SPDIF

output signal.

Using the crystal oscillator (which requires a 12.288 MHz

crystal) and the on-chip low jitter PLL, all standard audio

sampling frequencies (fs= 32, 44.1 and 48 kHz including

half and double these frequencies) can be generated.

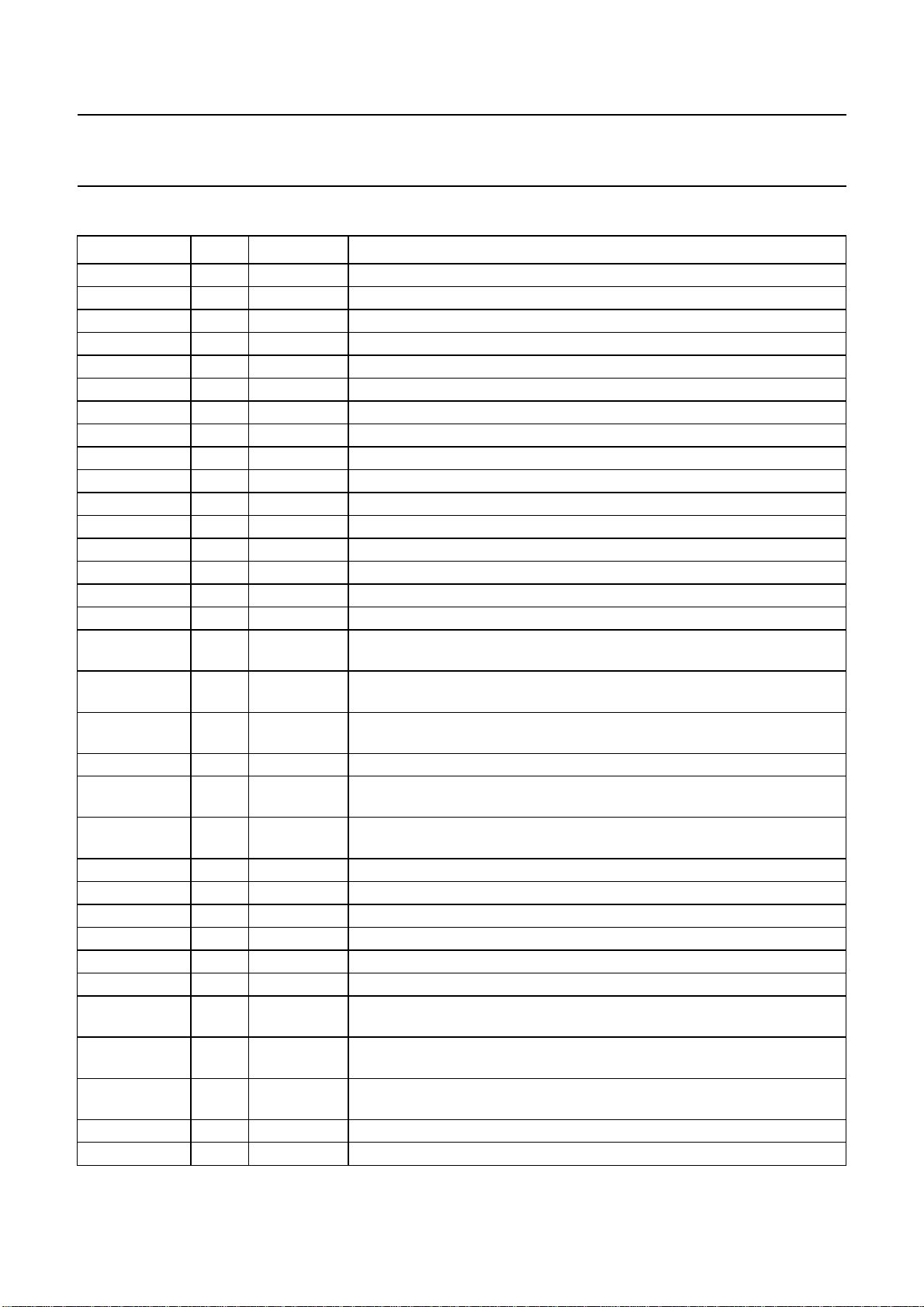

3 ORDERING INFORMATION

TYPE

NUMBER

UDA1355H QFP44 plastic quad flat package; 44 leads (lead length 1.3 mm); body

NAME DESCRIPTION VERSION

10 × 10 × 1.75 mm

PACKAGE

SOT307-2

2003 Apr 10 4

Page 5

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

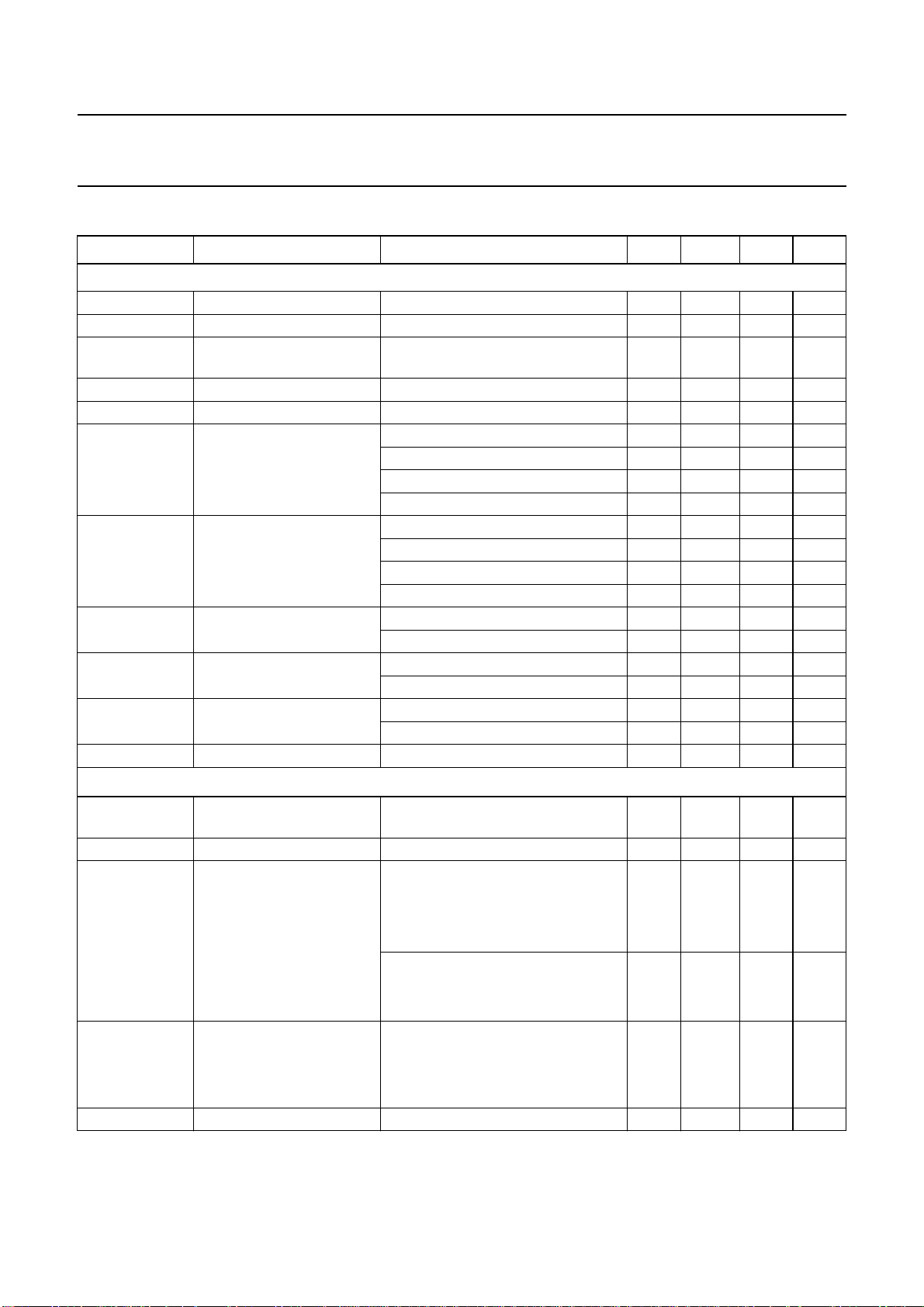

4 QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supplies

V

DDA1

V

DDA2

V

DDX

V

DDI

V

DDE

I

DDA1

I

DDA2

I

DDX

I

DDI

I

DDE

T

amb

Digital-to-analog converter; fi= 1 kHz; V

V

o(rms)

∆V

o

(THD+N)/S total harmonic

S/N signal-to-noise ratio IEC 60958 input; code = 0;

α

cs

DAC supply voltage 2.7 3.0 3.6 V

ADC supply voltage 2.7 3.0 3.6 V

crystal oscillator and PLL

2.7 3.0 3.6 V

supply voltage

digital core supply voltage 2.7 3.0 3.6 V

digital pad supply voltage 2.7 3.0 3.6 V

DAC supply current fs= 48 kHz; power-on − 4.7 − mA

f

= 96 kHz; power-on − 4.7 − mA

s

f

= 48 kHz; power-down − 1.7 −µA

s

= 96 kHz; power-down − 1.7 −µA

f

s

ADC supply current fs= 48 kHz; power-on − 10.2 − mA

f

= 96 kHz; power-on − 10.4 − mA

s

f

= 48 kHz; power-down − 0.2 −µA

s

= 96 kHz; power-down − 0.2 −µA

f

s

crystal oscillator and PLL

supply current

fs= 48 kHz; power-on − 0.9 − mA

f

= 96 kHz; power-on − 1.2 − mA

s

digital core supply current fs= 48 kHz; all on − 18.2 − mA

f

= 96 kHz; all on − 34.7 − mA

s

digital pad supply current fs= 48 kHz; all on − 0.5 − mA

f

= 96 kHz; all on − 0.7 − mA

s

ambient temperature −40 − +85 °C

= 3.0 V

DDA1

output voltage (RMS

− 900 − mV

value)

output voltage unbalance − 0.1 − dB

distortion-plus-noise to

signal ratio

IEC 60958 input; f

at 0 dB −−88 − dB

at −20 dB −−75 − dB

=48kHz

s

at −60 dB; A-weighted −−37 − dB

IEC 60958 input; fs=96kHz

at 0 dB −−83 − dB

at −60 dB; A-weighted −−37 − dB

A-weighted

fs= 48 kHz − 98 − dB

f

= 96 kHz − 96 − dB

s

channel separation − 100 − dB

2003 Apr 10 5

Page 6

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

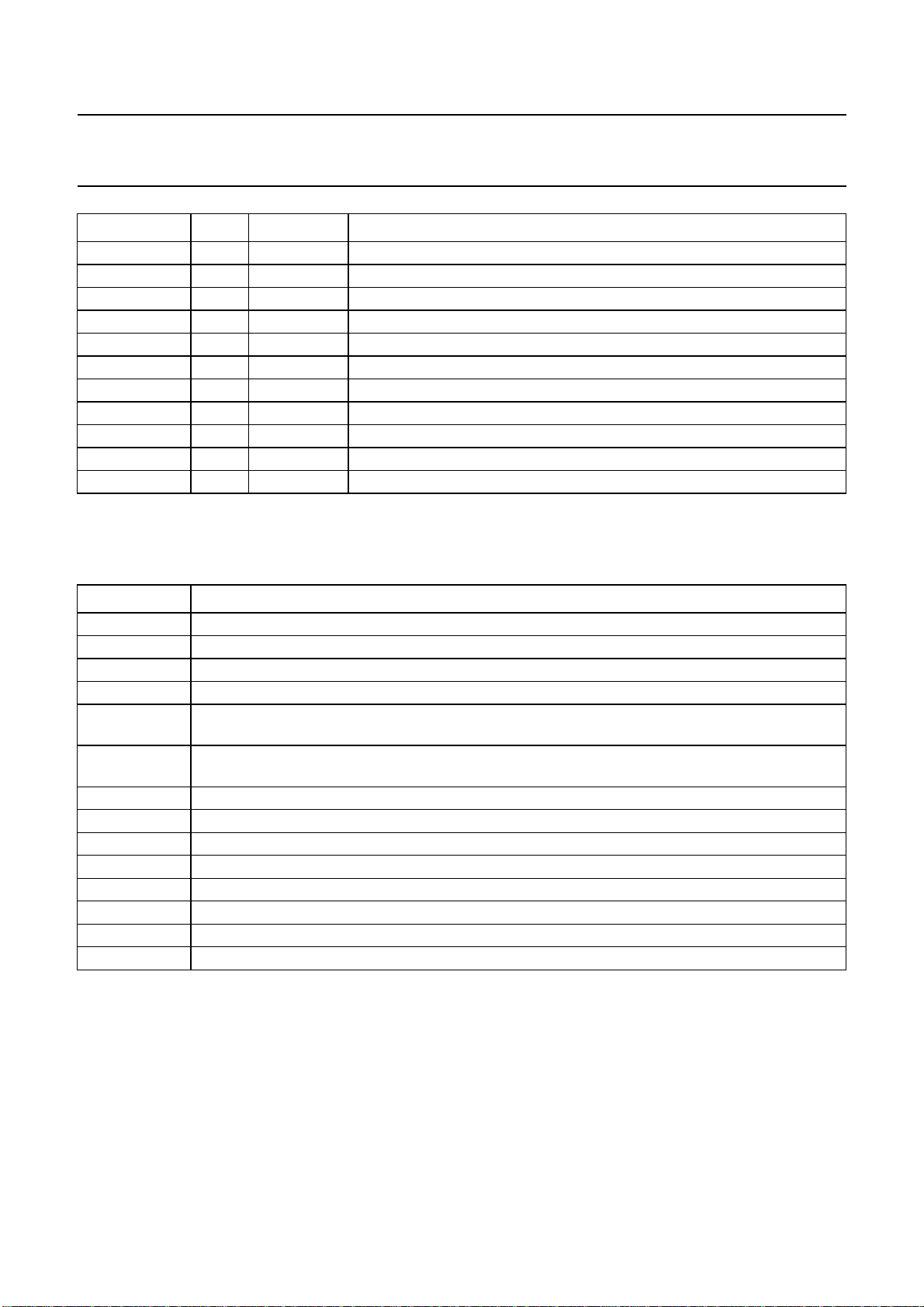

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Analog-to-digital converter; fi= 1 kHz; V

(rms) input voltage (RMS value) Vo= −1.16 dBFS digital output − 1.0 − V

V

i

∆V

i

input voltage unbalance − 0.1 − dB

(THD+N)/S total harmonic

distortion-plus-noise to

signal ratio

= 3.0 V

DDA2

f

= 48 kHz

s

at 0 dB −−85 − dB

at −60 dB; A-weighted −−35 − dB

f

= 96 kHz

s

at 0 dB −−85 − dB

at −60 dB; A-weighted −−35 − dB

S/N signal-to-noise ratio code = 0; A-weighted

f

= 48 kHz − 97 − dB

s

f

= 96 kHz − 95 − dB

s

α

cs

channel separation − 100 − dB

External crystal

f

C

xtal

L(xtal)

crystal frequency − 12.288 − MHz

crystal load capacitor − 10 − pF

Device reset

t

rst

reset time − 250 −µs

Power consumption

P

tot

total power consumption IEC 60958 input; fs=48kHz

DAC in playback mode − 74 − mW

DAC in Power-down mode − 63 − mW

2003 Apr 10 6

Page 7

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

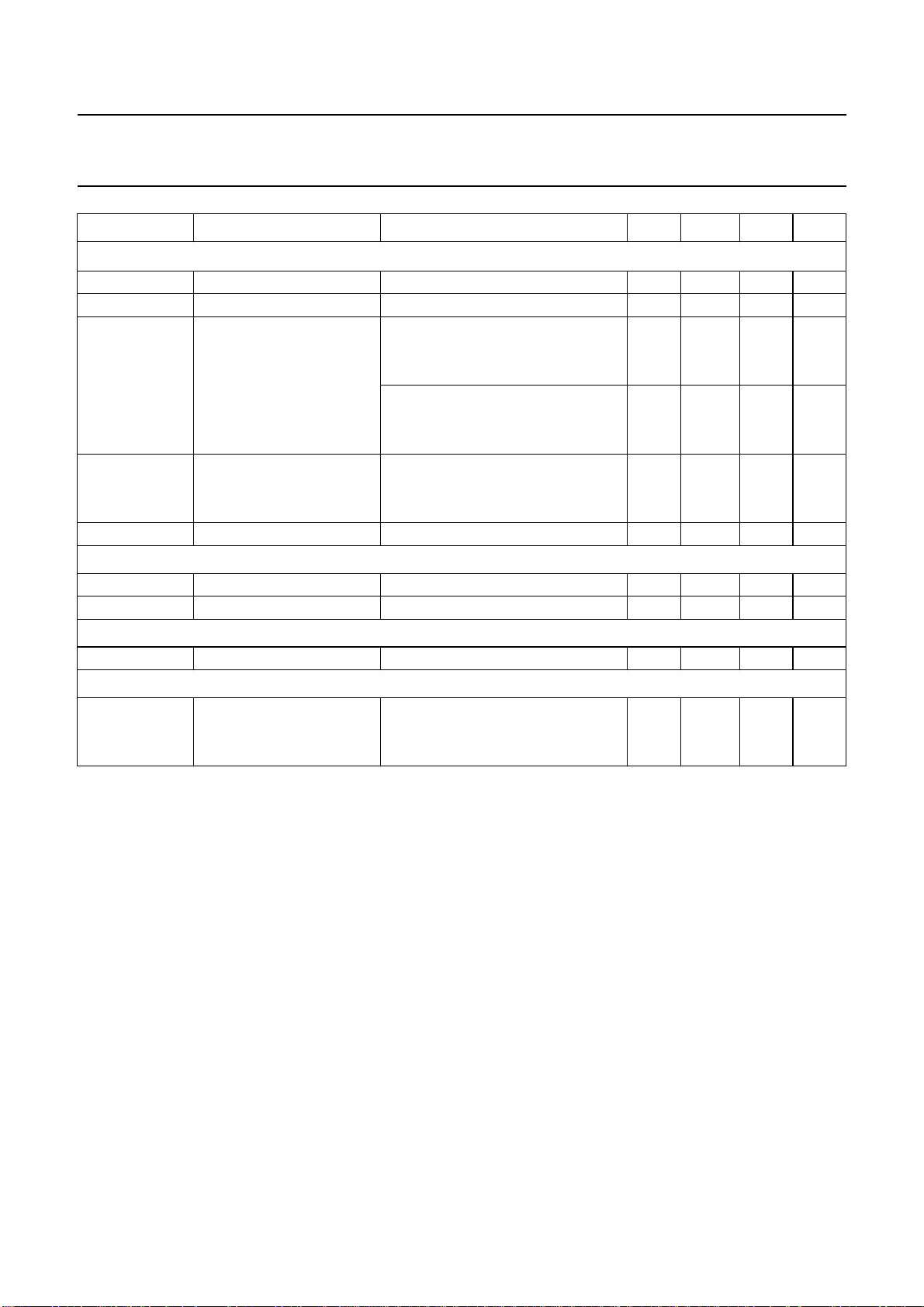

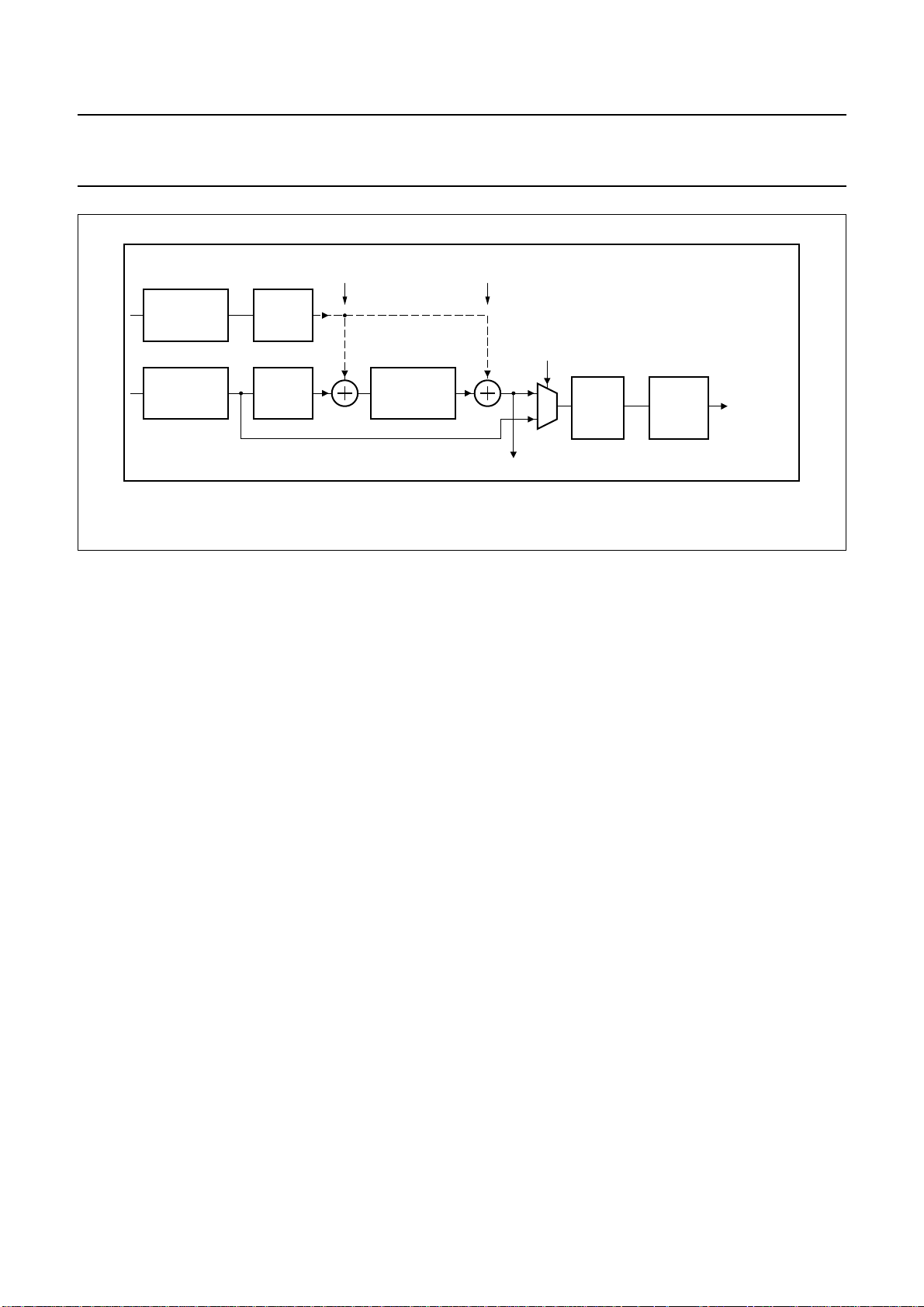

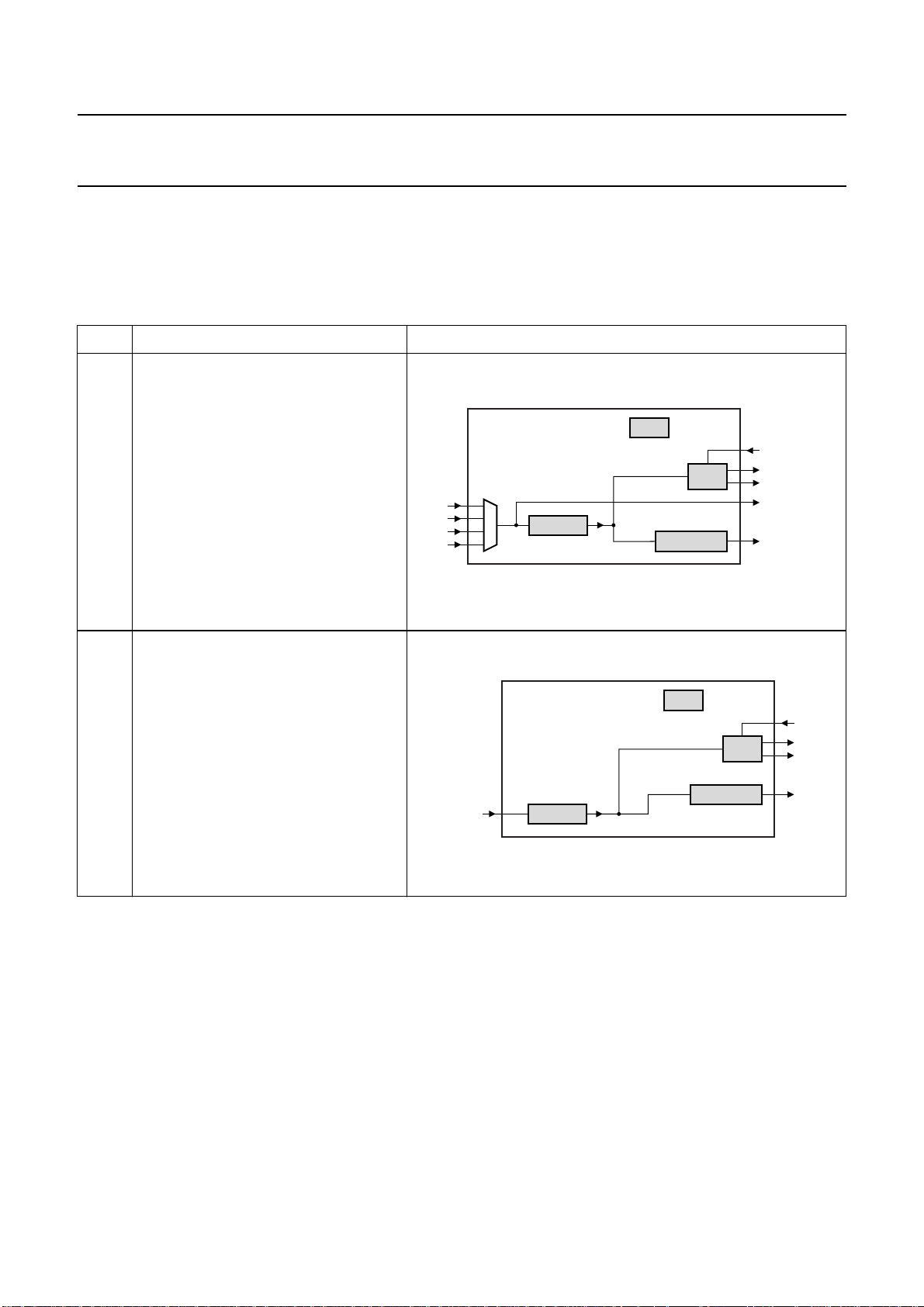

5 BLOCK DIAGRAM

VOUTL

VOUTR

MUTE

WSO

DATAO

DDA1

V

40

DAC

NOISE

INTER-

42

DAC

SHAPER

POLATOR

BCKO

9

44

8

10

DATA OUT

5

IEC 60958

ENCODER

SPDIFOUT

UDA1355H

41

MGU826

V

V

SSA1

SSE

DDE

V

ndbook, full pagewidth

REF

V

DDI

V

CLK_OUT

DDA2

V

ADCP

V

SSX

V

DDX

V

32 37 27 38 6 3911

15

12

TIMING

CLOCK AND

XTAL

13

14

AUDIO

AUDIO

ADC

34

FEATURE

PROCESSOR

FEATURE

PROCESSOR

DECI-

MATOR

COMB

FILTER

ADC

36

INPUT

16432

AND

OUTPUT

SELECT

DATA IN

3

1

IEC 60958

SLICER

232425

DECODER

26

21224

CONTROL

INTERFACE

MODE2

MODE1

MODE0

Fig.1 Block diagram.

SEL_STATIC

MP2

MP0

SSIS

V

ADCN

V

MP1

SSA2

V

29 30 31 20 17 18 19 7

33 35 28

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

2003 Apr 10 7

XTALIN

XTALOUT

VINL

VINR

RTCB

RESET

WSI

BCKI

DATAI

SPDIF0

SPDIF1

SPDIF2

SPDIF3

LOCK

SLICER_SEL0

SLICER_SEL1

Page 8

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

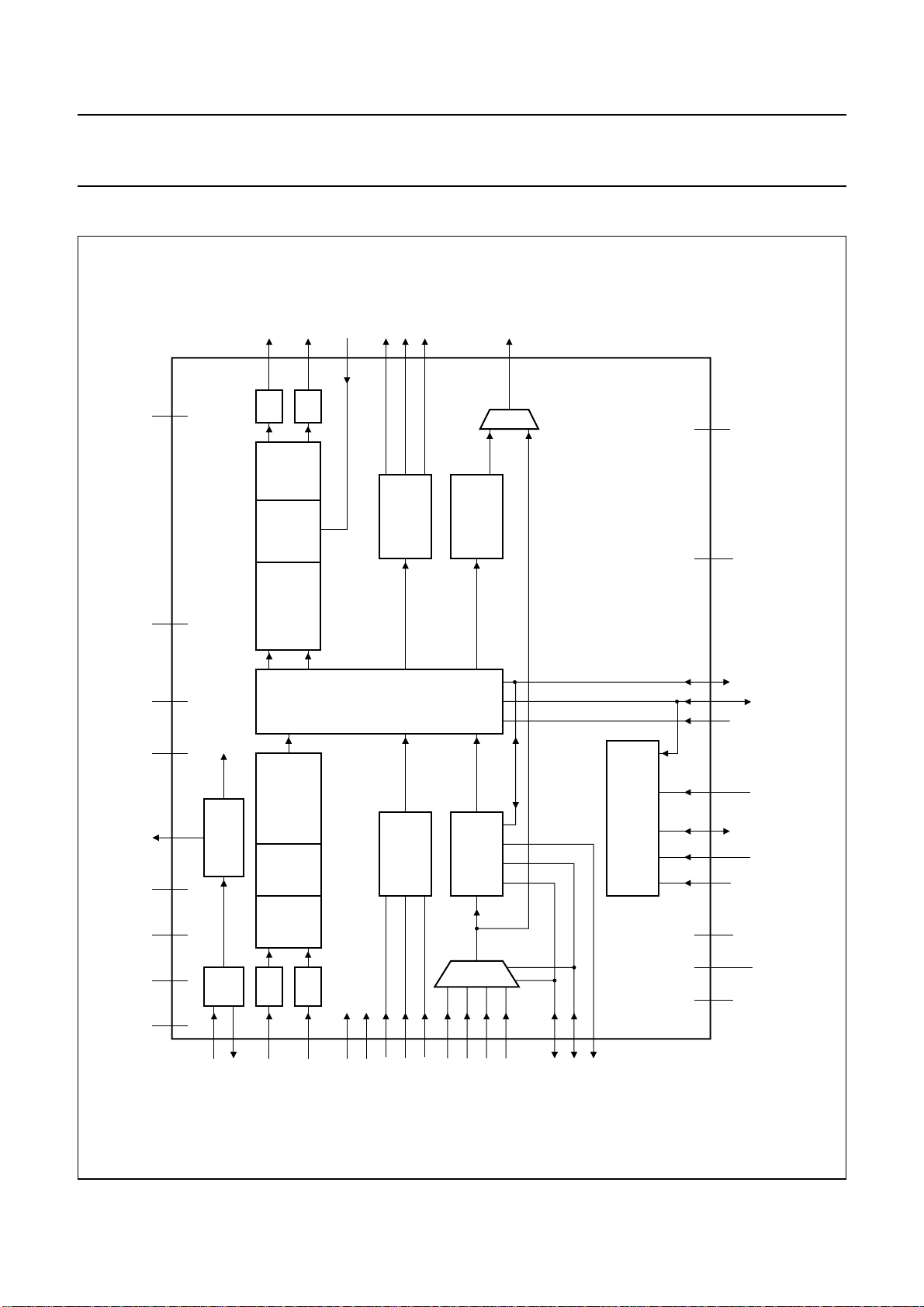

6 PINNING

SYMBOL PIN PAD

(1)

DESCRIPTION

BCKI 1 bpt4mtht5v bit clock input (master or slave)

WSI 2 bpt4mtht5v word select input (master or slave)

DATAI 3 iptht5v digital data input

LOCK 4 op4mc PLL lock indicator output

SPDIFOUT 5 op4mc SPDIF output

V

V

DDE

SSE

6 vdde digital pad supply voltage

7 vsse digital pad ground

DATAO 8 ops5c digital data output

WSO 9 bpt4mtht5v word select output (master or slave)

BCKO 10 bpt4mtht5v bit clock output (master or slave)

CLK_OUT 11 op4mc clock output; 256f

V

DDX

12 vddco crystal oscillator and PLL supply voltage

or 384f

s

s

XTALIN 13 apio crystal oscillator input

XTALOUT 14 apio crystal oscillator output

V

SSX

15 vssco crystal oscillator and PLL ground

RESET 16 ipthdt5v reset input

MODE0 17 apio mode selection input 0 for static mode or microcontroller mode (grounded

2

for I

C-bus)

MODE1 18 bpts5tht5v mode selection input 1 for static mode or AO address input and output for

microcontroller mode

MODE2 19 bpts5tht5v mode selection input 2 for static mode or U_RDY output for microcontroller

mode

SEL_STATIC 20 apio selection input for static mode, I

2

C-bus mode or L3-bus mode

SLICER_SEL0 21 bpts5tht5v SPDIF slicer selection input 0 for static mode and USER bit output for

microcontroller mode

SLICER_SEL1 22 bpts5tht5v SPDIF slicer selection input 1 for static mode and AC3 preamble detect

output for microcontroller mode

SPDIF0 23 apio SPDIF input 0

SPDIF1 24 apio SPDIF input 1

SPDIF2 25 apio SPDIF input 2

SPDIF3 26 apio SPDIF input 3

V

V

DDI

SSIS

27 vddi digital core supply voltage

28 vssis digital core ground

MP0 29 apio multi-purpose pin 0: frequency select for static mode, not used for

microcontroller mode

MP1 30 iptht5v multi-purpose pin 1: SFOR1 for static mode, SCL for I2C-bus mode and

L3CLOCK for L3-bus mode

2

MP2 31 iic400kt5v multi-purpose pin 2: SFOR0 for static mode, SDA for I

C-bus mode and

L3DATA for L3-bus mode

V

ADCP

V

ADCN

32 vddco positive ADC reference voltage

33 vssco negative ADC reference voltage

2003 Apr 10 8

Page 9

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

SYMBOL PIN PAD

(1)

DESCRIPTION

VINL 34 apio ADC left channel input

V

SSA2

35 vssco ADC ground

VINR 36 apio ADC right channel input

V

V

V

DDA2

REF

DDA1

37 vddco ADC supply voltage

38 apio reference voltage for ADC and DAC

39 vddco DAC supply voltage

VOUTL 40 apio DAC left channel output

V

SSA1

41 vssco DAC ground

VOUTR 42 apio DAC right channel output

RTCB 43 ipthdt5v test control input

MUTE 44 iipthdt5v DAC mute input

Note

1. See Table 1.

Table 1 Pad description

PAD DESCRIPTION

iptht5v input pad; push-pull; TTL with hysteresis; 5 V tolerant

ipthdt5v input pad; push-pull; TTL with hysteresis; pull-down; 5 V tolerant

op4mc output pad; push-pull; 4 mA output drive; CMOS

ops5c output pad; push-pull; 5 ns slew rate control; CMOS

bpt4mtht5v bidirectional pad; push-pull input; 3-state output; 4 mA output drive; TTL with hysteresis;

5 V tolerant

bpts5tht5v bidirectional pad; push-pull input; 3-state output; 5 ns slew rate control; TTL with hysteresis;

5 V tolerant

iic400kt5v I

2

C-bus pad; 400 kHz I2C-bus specification with open drain; 5 V tolerant

apio analog pad; analog input or output

vddco analog supply pad

vssco analog ground pad

vdde digital supply pad

vsse digital ground pad

vddi digital core supply pad

vssis digital core ground pad

2003 Apr 10 9

Page 10

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

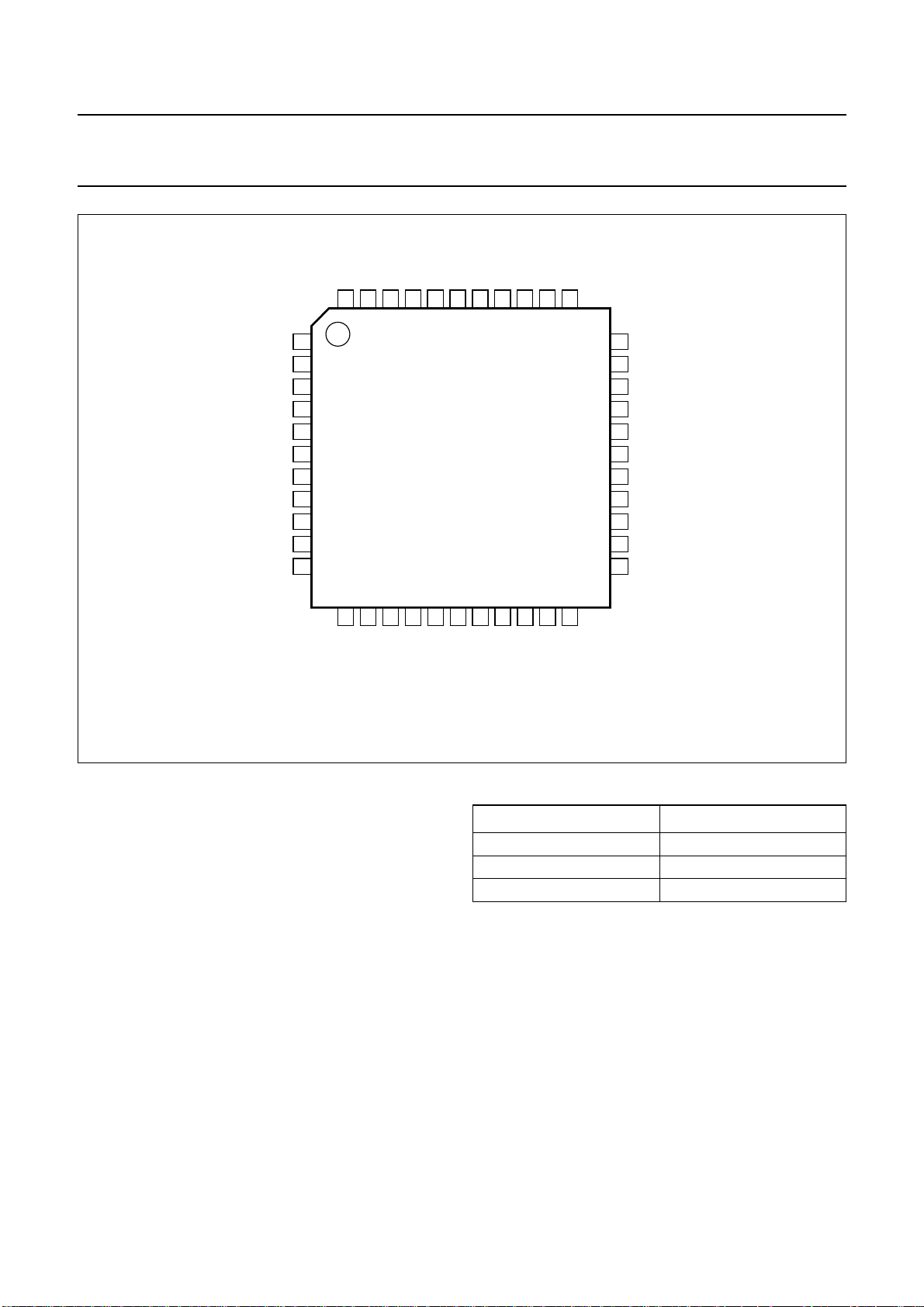

handbook, full pagewidth

DDA1

REF

V

38

DDA2

V

37

VINR

36

SSA2

V

35

VINL

34

33

32

31

30

29

28

27

26

25

24

23

V

ADCN

V

ADCP

MP2

MP1

MP0

V

SSIS

V

DDI

SPDIF3

SPDIF2

SPDIF1

SPDIF0

BCKI

WSI

DATAI

LOCK

SPDIFOUT

V

DDE

V

SSE

DATAO

WSO

BCKO

CLK_OUT

RTCB

43

42

V

VOUTL

41

40

UDA1355H

V

39

MUTE

44

1

2

3

4

5

6

7

8

9

10

11

SSA1

VOUTR

12

13

14

15

XTALIN

XTALOUT

SSX

V

DDX

V

Fig.2 Pin configuration.

7 FUNCTIONAL DESCRIPTION

7.1 IC control

The UDA1355H can be controlled either via static pins or

via the microcontroller serial hardware interface being the

I2C-bus with a clock up to 400 kHz or the L3-bus with a

clock up to 2 MHz. It is recommended to use the

microcontroller interface since this gives full access to all

the IC features.

The two microcontroller interfaces only differ in interface

format. The register addresses and features that can be

controlled are identical for L3-bus mode and I2C-bus

mode.

The UDA1355H can operate in three control modes:

• Static mode with limited features

• L3-bus mode with full featuring

• I2C-bus mode with full featuring.

The modes are selected via the 3-level pin SEL_STATIC

according to Table 2.

21

16

17

RESET

MODE0

18

19

MODE2

MODE1

22

20

SEL_STATIC

SLICER_SEL1

SLICER_SEL0

MGU828

Table 2 Control mode selection via pin SEL_STATIC

LEVEL MODE

HIGH static mode

MID I2C-bus mode

LOW L3-bus mode

7.2 Microcontroller interface

The UDA1355H has a microcontroller interface and all the

sound processing features and system settings can be

controlled by the microcontroller.

The controllable settings are:

• Restoring L3-bus defaults

• Power-on settings for all blocks

• Digital interface input and output formats

• Volume settings for the decimator

• PGA gain settings

2003 Apr 10 10

Page 11

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

• Set two times 40 bits of channel status bits of the SPDIF

output

• Select one of four SPDIF input sources

• Enable digital mixer inside interpolator

• Control mute and mixer volumes of digital mixer

• Selection of filter mode and settings of treble and bass

boost for the interpolator (DAC) section

• Volume settings of interpolator

• Selectionof soft mute via cosine roll-off (only effectivein

L3-bus control mode) and bypass of auto mute

• Selection of de-emphasis

• Enable and control of digital mixer inside interpolator.

The readable settings are:

• Mute status of interpolator

• PLL lock and adaptive lock

• Two times 40 bits of channels status bits of the SPDIF

input signal.

7.3 Clock systems

The UDA1355H has two clock systems.

The first system uses an external crystal of 12.288 MHz to

generate the audio related system clocks. Only a crystal

with a frequency of 12.288 MHz is allowed.

The second system is a PLL which locks on the SPDIF or

incoming digital audio signal (e.g. I2S-bus) and recovers

the system clock.

7.3.1 CRYSTAL OSCILLATOR CLOCK SYSTEM

The crystal oscillator and the on-chip PLL and divider

circuit can be used to generate internal and external clock

signals related to standard audio sampling frequencies

(such as 32, 44.1 and 48 kHz including half and double of

these frequencies).

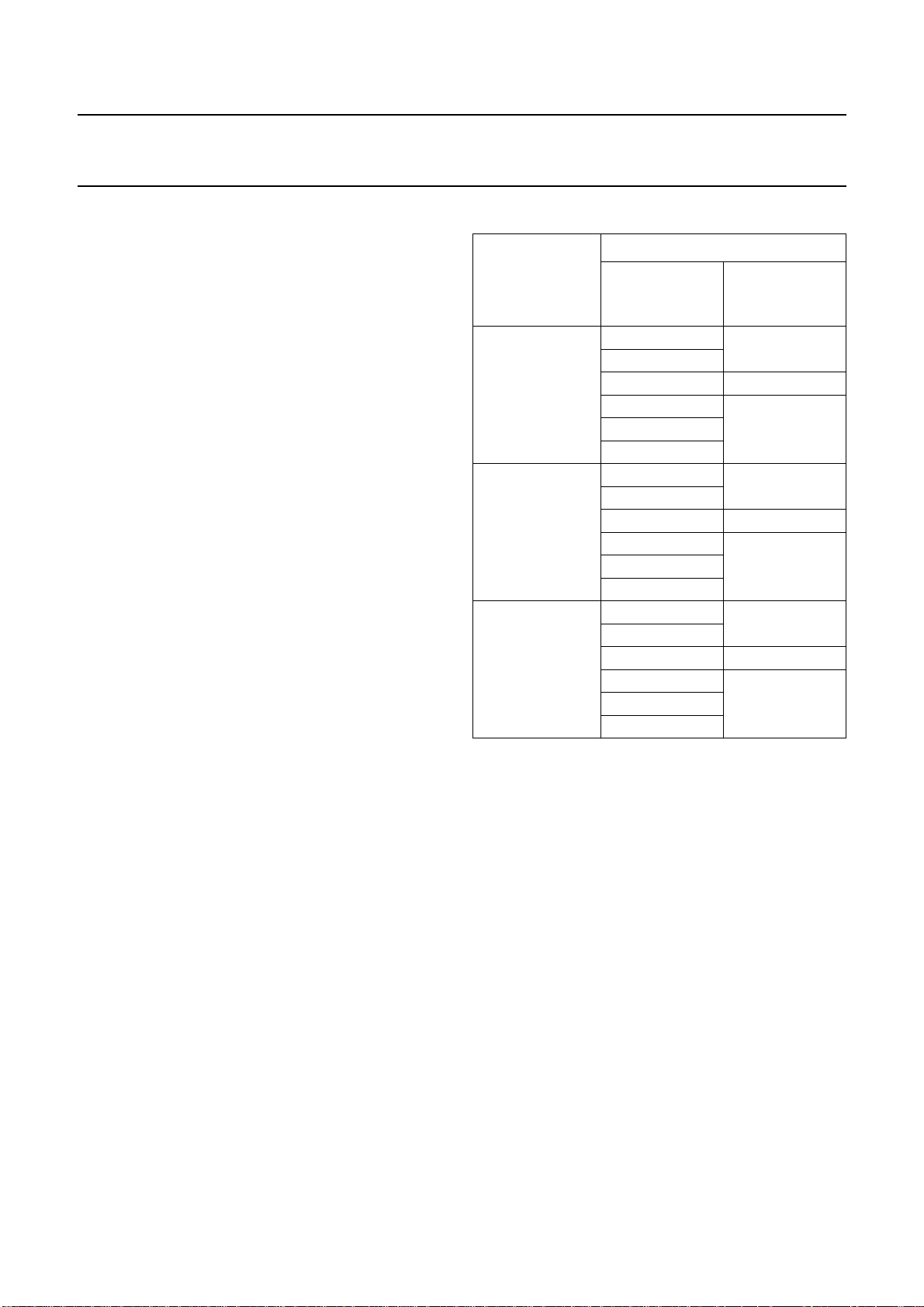

The audio frequencies supported in either microcontroller

mode or static mode are given in Table 3.

Table 3 Output frequencies

OUTPUT FREQUENCY

BASIC AUDIO

FREQUENCY

32 kHz 256 × 16 kHz

44.1 kHz 256 × 22.05 kHz

48 kHz 256 × 24 kHz

Remarks:

• If an application mode is selected which does not need

a crystal oscillator, the crystal oscillator cannot be

omitted. The reason is that the interpolator switches to

the crystal clock when an SPDIF input signal is

removed. This switch prevents the noise shaper noise

from moving inside the audio band as the PLL gradually

decreases in frequency.

• If no accurate output frequency is needed, the crystal

can be replaced with a resonator.

• Instead of the crystal, a 12.288 MHz system clock can

be applied to pin XTALIN.

MICRO-

CONTROLLER

MODE

384 × 16 kHz

256 × 32 kHz 256 × 32 kHz

384 × 32 kHz

256 × 64 kHz

384 × 64 kHz

384 × 22.05 kHz

256 × 44.1 kHz 256 × 44.1 kHz

384 × 44.1 kHz

256 × 88.2 kHz

384 × 88.2 kHz

384 × 24 kHz

256 × 48 kHz 256 × 48 kHz

384 × 48 kHz

256 × 96 kHz

384 × 96 kHz

STATIC MODE

2003 Apr 10 11

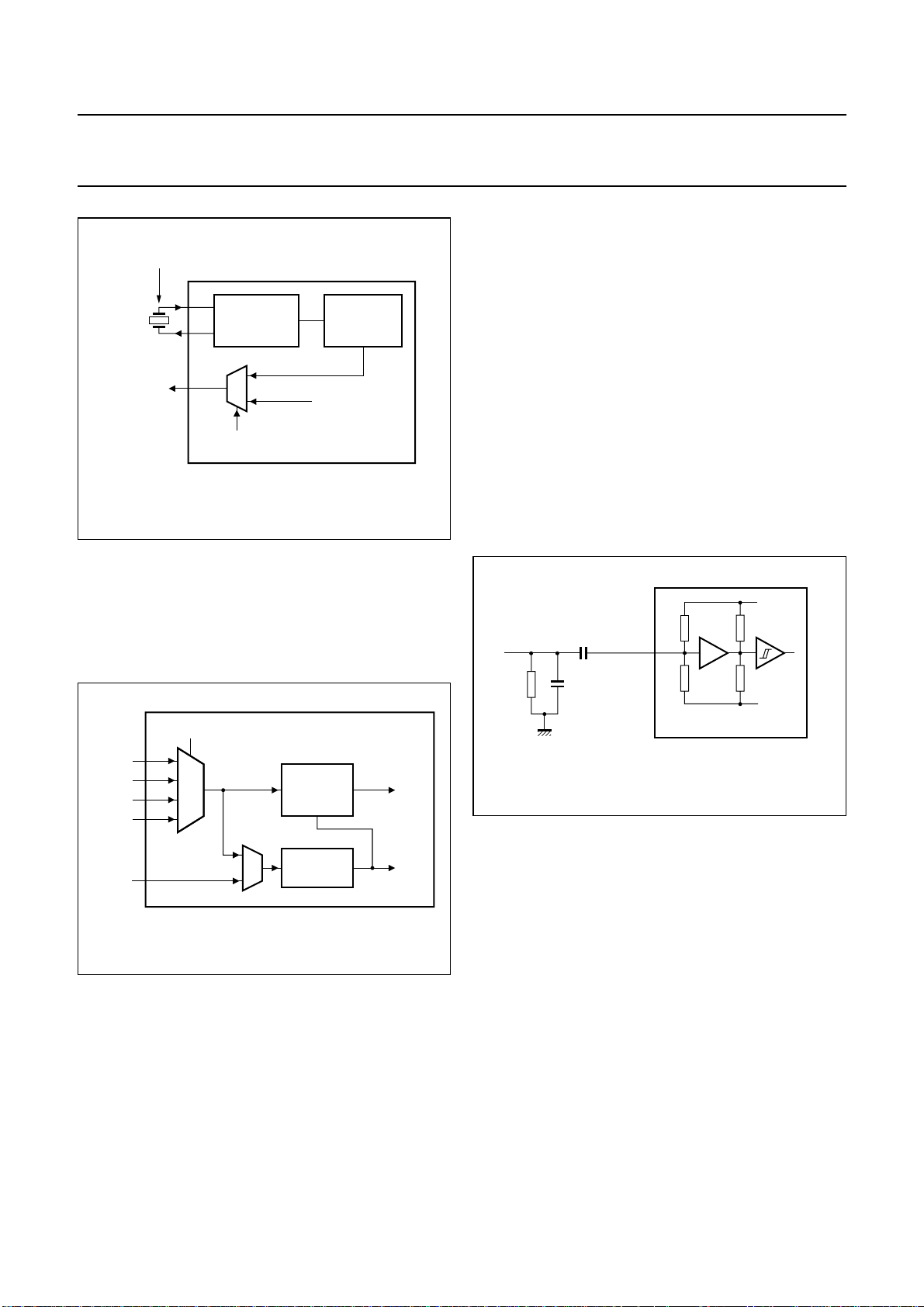

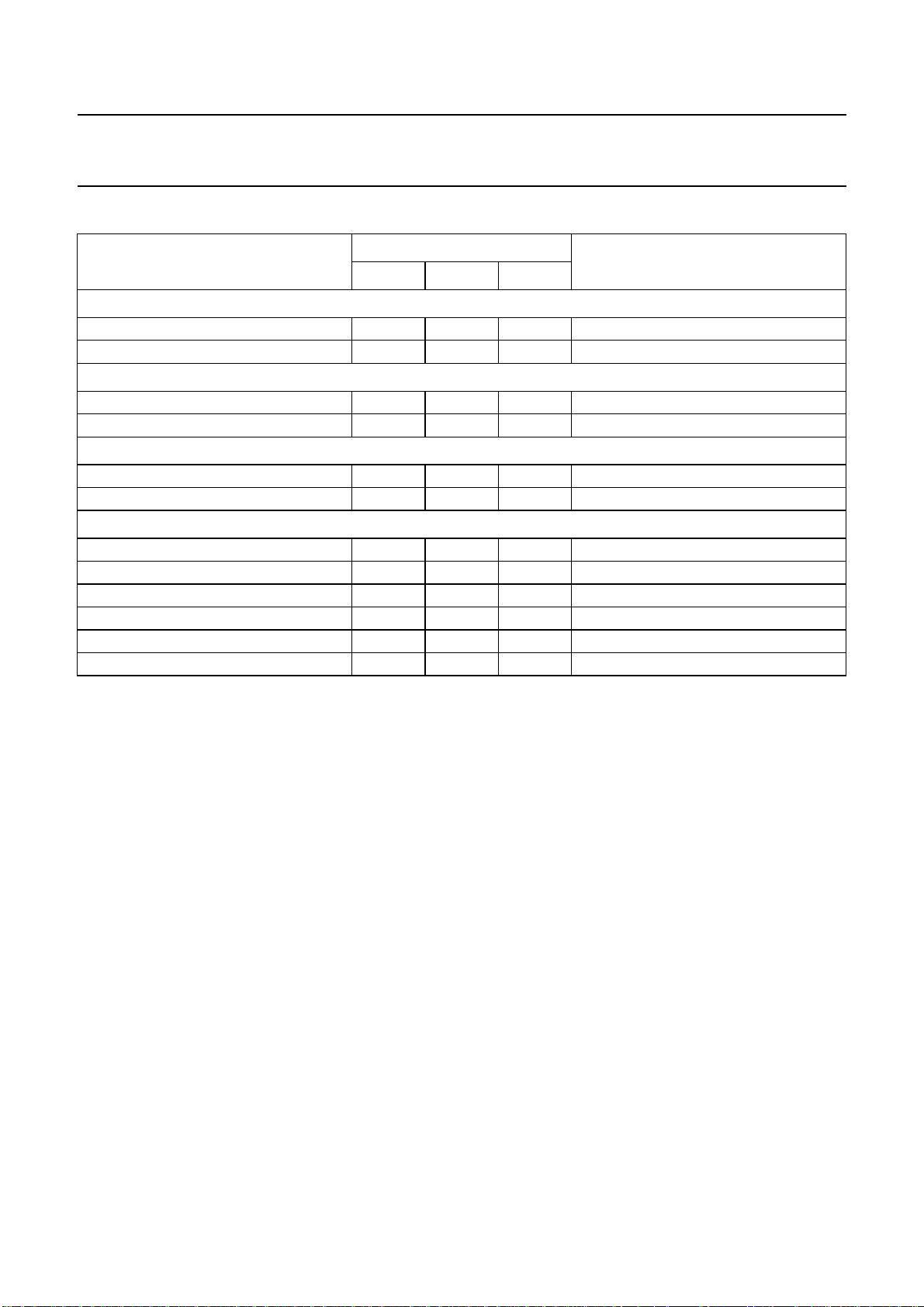

The block diagram of the crystal oscillator and the PLL

circuit is given in Fig.3.

Page 12

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

7.3.4 CLOCK OUTPUT

handbook, halfpage

12.288 MHz

XTALIN

XTALOUT

CLK_OUT

13

CRYSTAL

14

OSCILLATOR

11

L3-bus or I

register setting

256fs or 384fs clock

PLL clock

2

C-bus

UDA1355H

PLL

MODULE

MGU830

Fig.3 Crystal oscillator clock system.

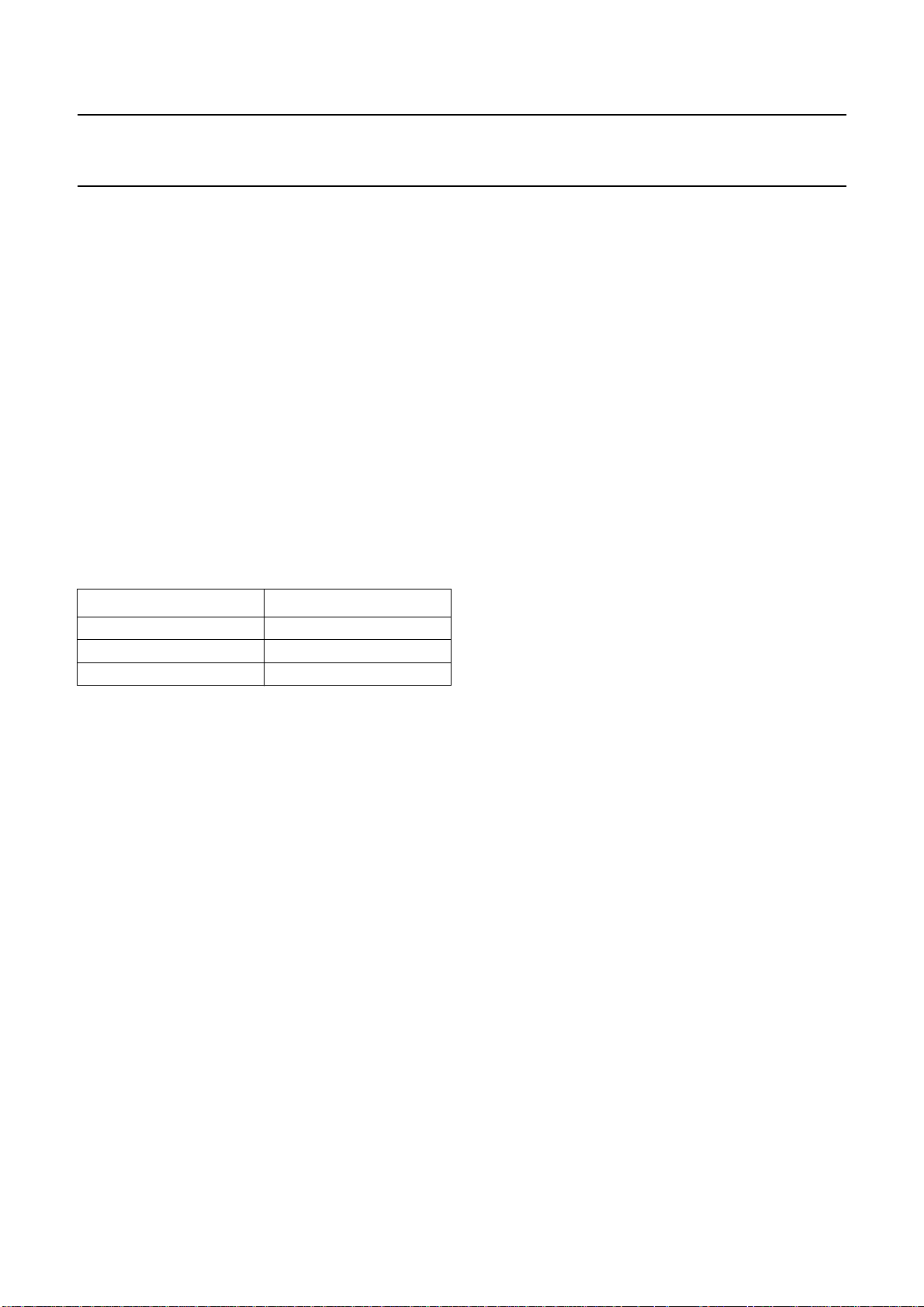

7.3.2 PLL CLOCK SYSTEM

The PLL locks on the incoming digital data of the SPDIF or

WS input signal. The PLL recovers the clock from the

SPDIForWSI signal and removes jitter toproduceastable

system clock (see Fig.4).

The UDA1355H has a clock output pin (pin CLK_OUT),

which can be used to drive other audio devices in the

system. In microcontroller mode the output clock is

256fsor 384fs. In static mode the output clock is 256 times

32, 44.1 and 48 kHz.

The source of the output clock is either the crystal

oscillator or the PLL, depending on the selected

application and control mode.

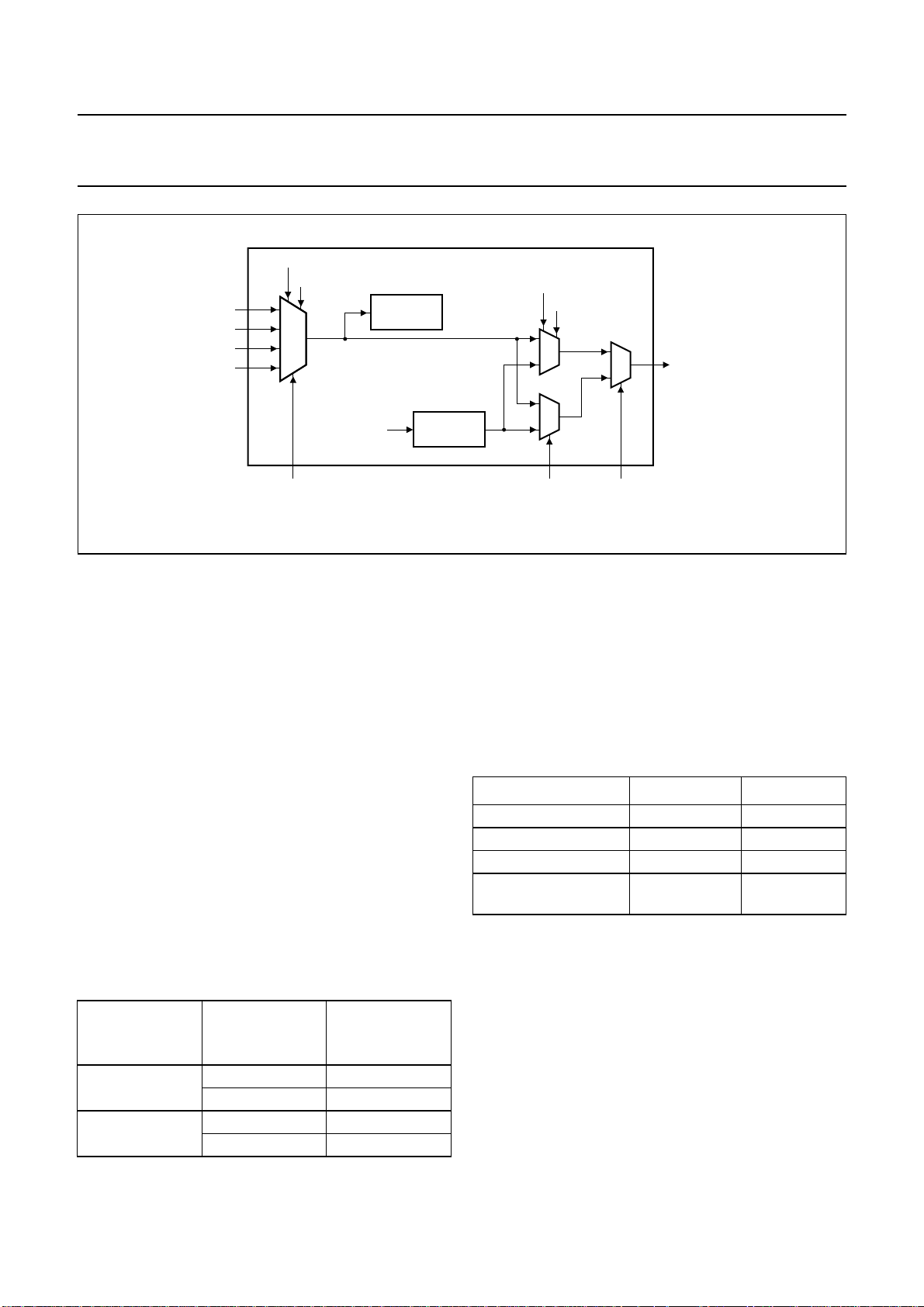

7.4 IEC 60958 decoder

The UDA1355H IEC 60958 decoder can selectone of four

SPDIFinputchannels. An on-chip amplifier with hysteresis

amplifies the SPDIF input signal to CMOS level, making it

possible to accept both analog and digital SPDIF signals

(see Fig.5).

handbook, halfpage

23

24

25

26

75 Ω

10 nF

180 pF

SPDIF0

SPDIF1

SPDIF2

SPDIF3

SPDIF0

SPDIF1

SPDIF2

SPDIF3

WSI

select SPDIF source

23

24

25

26

SLICER

2

IEC 60958

DECODER

PLL

UDA1355H

256f

384f

s

or

s

MGU827

Fig.4 PLL clock system.

7.3.3 WORD SELECTION DETECTION CIRCUIT

This circuit is clocked by the 12.288 MHz crystal oscillator

clock and generates a Word Selection (WS) detection

signal. If the WS detector does not detect any WS edge,

defined as 7 times LOW and 7 times HIGH, then the

WS detection signal is LOW. This information can be used

tosetthe clock for the noise shaper in theinterpolator.This

will prevent noise shaper noise in the audio band.

UDA1355H

MGU829

Fig.5 IEC 60958 input circuit.

7.4.1 AUDIO DATA

From the incoming SPDIF bitstream 24 bits of data for the

left and right channel are extracted.

There is a hard mute (not a cosine roll-off mute) if the

IEC 60958 decoder is out of lock or detects bi-mark phase

encoding violations. The lock indicator and the key

channel status bits are accessible in L3-bus mode.

The UDA1355H supports the following sample

frequencies and data rates, including half and double of

these frequencies:

• fs= 32 kHz; resulting in a data rate of 2.048 Mbit/s

• fs= 44.1 kHz; resulting in a data rate of 2.8224 Mbit/s

• fs= 48 kHz; resulting in a data rate of 3.072 Mbit/s.

2003 Apr 10 12

Page 13

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

7.4.2 CHANNEL STATUS AND USER BITS

As well as the data bits there are several IEC 60958 key

channel status bits:

• Pre-emphasis and audio sampling frequency bits

• Two channel PCM indicator bits

• Clock accuracy bits.

In total 40 status bits per channel are recovered from the

incomingIEC 60958bitstream.Thesearereadableviathe

microcontroller interface.

User bits, which can contain a large variety of data, such

asCD text, are output to pin SLICER_SEL0 (see Table 4).

In microcontroller mode this signal contains the raw user

bits extracted from the SPDIF bitstream. Signal U_RDY

gives a pulse on pin MODE2 each time there is a new user

bit available. Both signals can be used by an external

microcontroller to grab and decode the user bits.

Table 4 Signal names in microcontroller mode

PIN NAME SIGNAL NAME

SLICER_SEL0 USER

MODE2 U_RDY

SLICER_SEL1 AC3

7.4.3 D

Audio and digital data can be transmitted in the SPDIF

bitstream. The PCM channel status bit should be set to

logic 1 if the SPDIF bitstream is carrying digital data

instead of audio data, but in practice it proves that not all

equipment handles these channel status bits properly.

In the UDA1355H, digital data is detected via bit PCM, or

via the sync bytes as specified by IEC. These sync bytes

are two sync words, F872H and 4E1FH (two subframes)

preceded by four or more subframes filled with zeros.

Signal AC3 is kept HIGH for 4096 frames when the

UDA1355H detects this burst preamble. Signal AC3 is

present on pin SLICER_SEL1 in microcontroller mode

(see Table 4).

IGITAL DATA

7.5 IEC 60958 encoder

When using the crystal oscillator clock, the IEC 60958

encoder output is a full-swing digital signal with level II

timing.

When the recovered clock from the PLL is used the

IEC 60958 encoder will function correctly but will not meet

level II timing requirements.

7.5.1 S

All user and channel status bits are set to logic 0. This is

default value specified by IEC.

In static mode 0 and 2, the selected SPDIF input channel

can be looped through to pin SPDIFOUT (see Fig.6).

7.5.2 MICROCONTROLLER MODE

Two times 40 channel status bits can be set. Default value

for each status bit is logic 0. When setting the channel

status bits, it is possible to set only the left channel status

bits and have the bits copied to the right channel.

The procedure of writing the channel status bits is as

follows:

1. Set bit SPDO_VALID = 0 to prevent immediately

2. Set bit l_r_copy = 1 if the right channel needs the

3. Write the left and right channel status bits.

4. Set bit SPDO_VALID = 1 after writing all channel

In microcontroller modes 2 and 13, the selected SPDIF

input channel can be looped through to pin SPDIFOUT

(see Fig.6).

TATIC MODE

sending the status bits during writing.

same status bits as the left channel or set

bit l_r_copy = 0 if the right channel needs different

status bits to the left channel.

statusbitstotheregister.StartingfromthenextSPDIF

block the IEC 60958 encoder will use the new status

bits.

2003 Apr 10 13

Page 14

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

handbook, full pagewidth

SPDIF0

SPDIF1

SPDIF2

SPDIF3

SPDOUT_SEL1

SPDOUT_SEL0

23

24

25

26

SLICER_SEL[1:0

SLICER

select

SPDIF source

21, 22

]

SPDIF

source

UDA1355H

IEC 60958

DECODER

IEC 60958

ENCODER

Fig.6 Selection options for SPDIF output.

7.6 Analog input

7.6.1 ADC

The analog input is equipped with a Programmable Gain

Amplifier (PGA) which can be controlled via the

microcontroller interface. The control range is from

0 to 24 dB gain in 3 dB steps independent for the left and

right channels.

In applications in with a 2 V (RMS) input signal, a 12 kΩ

resistor must be used in series with the input of the ADC.

The 12 kΩ resistor forms a voltage divider together with

the internal ADC resistor and ensures that the voltage,

applied to the input of the IC, never exceeds 1 V (RMS).

In the application for a 2 V (RMS) input signal, the PGA

must be set to 0 dB. When a 1 V (RMS) input signal is

applied to the ADC in the same application, the PGA gain

must be set to 6 dB.

An overview of the maximum input voltages allowed with

and without an external resistor and the PGA gain setting

is given in Table 5.

Table 5 Maximum input voltage; VDD=3V

EXTERNAL

RESISTOR

(12 kΩ)

PGA GAIN

SETTING

MAXIMUM

INPUT

VOLTAGE

Present 0 dB 2 V (RMS)

6 dB 1 V (RMS)

Absent 0 dB 1 V (RMS)

6 dB 0.5 V (RMS)

SPDOUT_SEL2

MODE[3:0

17 to 19 20

MODE[2:0]SEL_STATIC

]

5

SPDIF OUT

MGU833

7.6.2 DECIMATION

Thedecimation from 64fsisperformed in two stages: comb

filter and decimation filter. The first stage realizes a

fourth-order characteristic with a decimation factor

sin x

----------- x

of eight. The second stage consists of three half-band

filters each decimating by a factor of two. Table 6 shows

the characteristics.

Table 6 Decimation filter characteristics

ITEM CONDITIONS VALUE (dB)

Pass-band ripple 0 to 0.45f

Stop band >0.55f

Dynamic range 0 to 0.45f

Overallgain from ADC

input to digital output

DC; V

note 1

= 0 dB;

I

s

s

s

±0.02

−60

140

−1.16

Note

1. Theoutput is not 0 dB when V

=1VatVDD=3V.

I(rms)

This is because the analog components can spread

over the process. When there is no external resistor,

the −1.16 dB scaling prevents clipping caused by

process mismatch.

In the ADC path there are left and right independent digital

volume controls with a range from +24 to −63.5 dB

and −∞ dB. This volume control is also used as a digital

linear mute that can be used to prevent plops when

powering-up or powering down the ADC front path.

2003 Apr 10 14

Page 15

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

7.6.3 DC FILTERING

In the decimator there are two digital DC blocking circuits.

The first blocking circuit is in front of the volume control to

remove DC bias from the ADC output. The DC bias is

added in the ADC to prevent audio band Idle tones

occurring in the noise shaper. With the DC components

removed, a signal gain of 24 dB can be achieved.

The second blocking circuit removes the DC components

introduced by the decimator stage.

7.6.4 OVERLOAD DETECTION

Bit OVERFLOW = 1 when the output data in the left or

right channel is larger than −1.16 dB of the maximum

possible digital swing. This condition is set for at least

512fs cycles (that is 11.6 ms at fs= 44.1 kHz). This

time-out is reset for each infringement.

7.7 Analog output

7.7.1 AUDIO FEATURE PROCESSOR

The audio feature processor provides automatic

de-emphasis for the IEC 60958 bitstream.

In microcontroller mode all features are available and

there is a default mute on start up.

7.7.2 INTERPOLATING FILTER

The digital filter interpolates from 1fsto 64fs, or from

1fsto 128fs, by cascading a half-band filter and a FIR filter.

The stereo interpolator has the following basic features:

• 24-bit data path

• Mixing of two channels:

– To prevent clipping inside the core, there is an

automatic signal level correction of −6 dB scaling

before mixing and +6 dB gain after digital volume

control

– Position of mixing can be set before or after bass

boost and treble

– Mastervolume control andmutewithindependent left

and right channel settings for balance control

– Independently left and right channel de-emphasis,

volume control and mute (no left or right)

– Output of the mixer is to the I2S-bus or IEC 60958

decoder.

• Full FIR filter implementation for all the upsampling

filters

• Integrated digital silence detection for left and right

channels with selectable silence detection time

• Support for 1fsand 2fs input data rate and 192 kHz

audio via I2S-bus.

The stereo interpolator has the following sound features:

• Linear volume control using 14-bit coefficients with

0.25 dB steps: range 0 to −78 dB and −∞ dB; hold for

master volume and mixing volume control

• A cosine roll-off soft mute with 32 coefficients; each

coefficientis used for four samples, in total 128 samples

are needed to fully mute or de-mute (approximately

3 ms at fs= 44.1 kHz)

• Independent selectable de-emphasis for 32, 44.1, 48

and 96 kHz for both channels

• Treble is the selectable positive gain for high

frequencies. The edge frequency of the treble is fixed

and depends on the sampling frequency. Treble can be

set independently for left and right channel with two

settings:

–fc= 1.5 kHz; fs= 44.1 kHz; 0 to 6 dB gain range with

2 dB steps

–fc= 3 kHz; fs= 44.1 kHz; 0 to 6 dB gain range with

2 dB steps.

• Normal bass boost is the selectable positive gain for low

frequencies. The edge frequency of the bass boost is

fixed and depends on the sampling frequency. Normal

bassboostcan be set independently for the left and right

channel with two sets:

–fc= 250 Hz;fs= 44.1 kHz;0 to 18 dBgainrangewith

2 dB steps

–fc= 300 Hz;fs= 44.1 kHz;0 to 24 dBgainrangewith

2 dB steps.

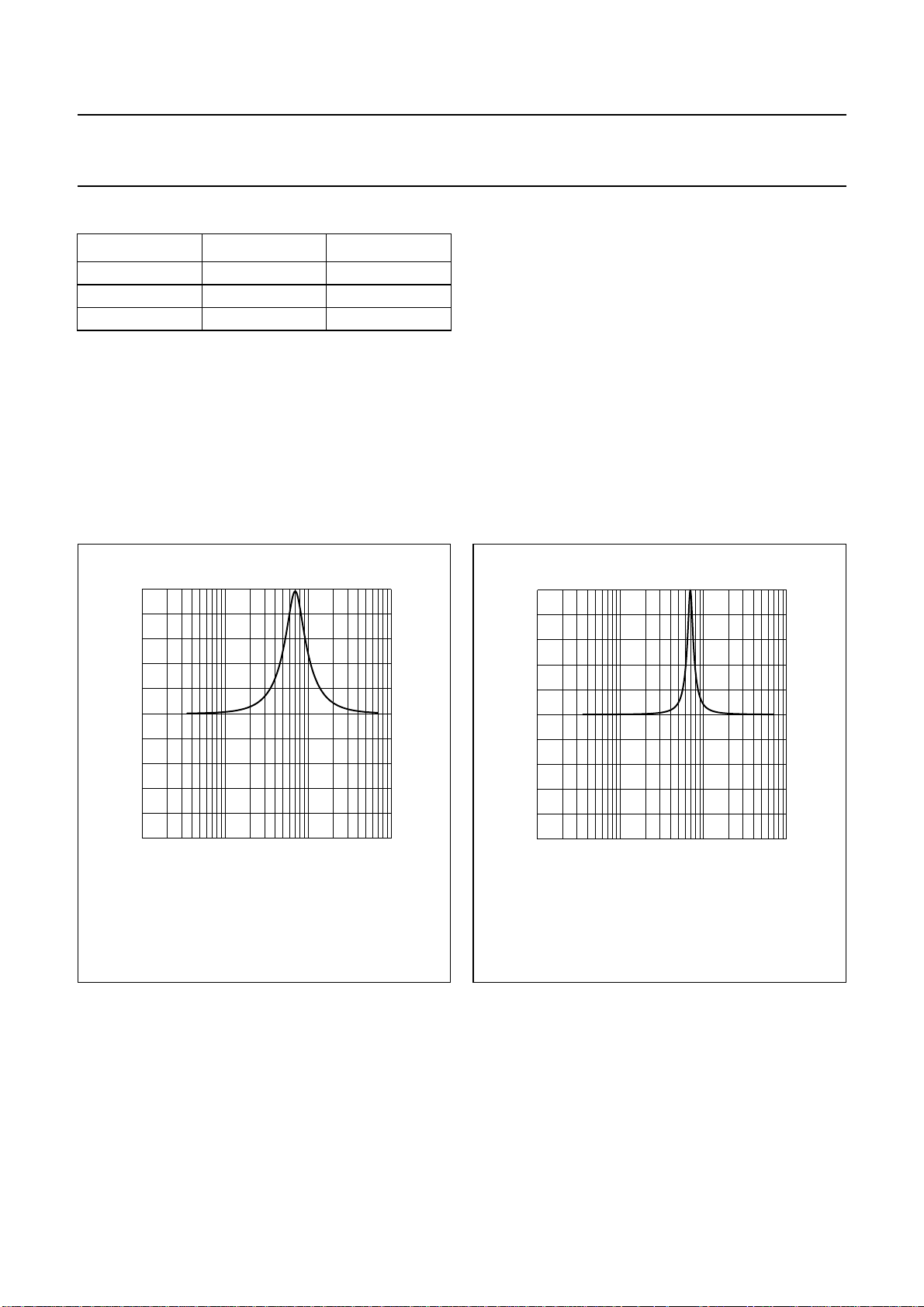

• Resonant bass boost optional function is selected if

bit BASS_SEL = 1. When selected, the characteristics

aredeterminedbysix14-bitcoefficients.Resonantbass

boost controls the left and right channel with the same

characteristics. When resonant bass boost is selected,

the treble control also changes to a single control for

both channels following the gain setting of the left

channel.

Asoftware program is available foruserstogenerate the

required six 14-bit coefficients by entering the desired

centre frequency (fc), positive or negative peak gain,

sampling frequency (fs) and shape factor (see

Figs 7 and 8).

2003 Apr 10 15

Page 16

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

Table 7 Interpolation filter characteristics

ITEM CONDITIONS VALUE (dB)

Pass-band ripple 0 to 0.45f

Stop band >0.55f

Dynamic range 0 to 0.4535f

7.7.3 D

IGITAL MIXER

s

s

s

±0.035

−60

140

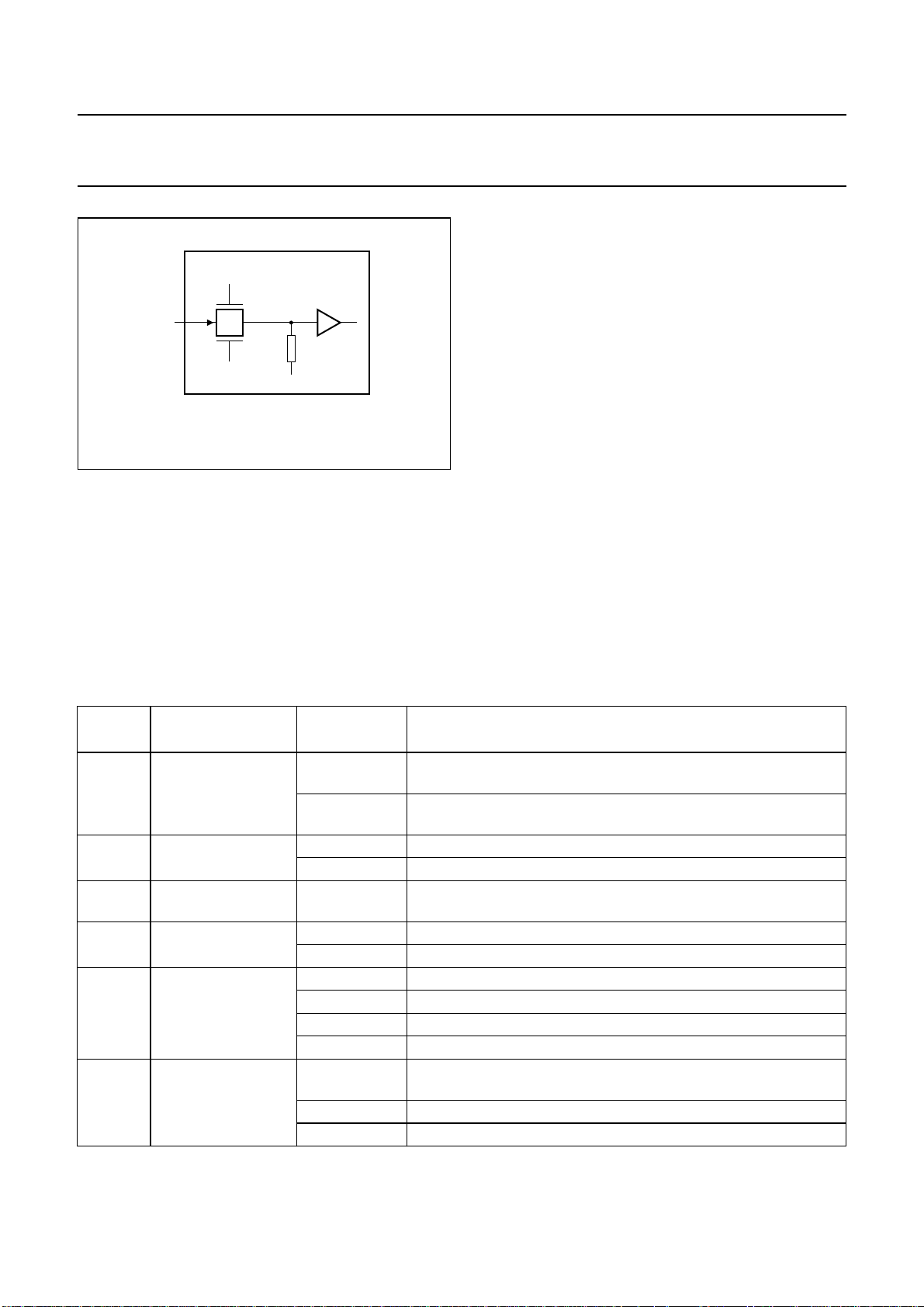

The UDA1355H has a digital mixer inside the interpolator.

Thedigitalmixer can be used as a cross over or a selector.

A functional block diagram of the mixer mode is shown in

Fig.9. This mixer can be used in microcontroller mode

only.

The UDA1355H can be set to the mixer mode by setting

bit MIX = 1.In the mixer mode, there are three volume and

10

handbook, halfpage

gain

8

(dB)

6

4

2

0

−2

−4

−6

−8

−10

11010

MGU832

2103

f (Hz))

mute controls available: for source 1, for source 2 and for

the master (sum) signal. All three volume ranges can be

controlled in 0.25 dB steps.

Topreventclipping inside the mixer, the signals are scaled

with −6 dB before mixing, therefore the sum of the two

signals is always equal to or lower than 0 dB. After the

mixing there is a 6 dB gain in the master volume control.

This means that at the analog output the signal can clip,

but the clipping can be undone by decreasing the master

volume control.

2

The output of the mixer is available via the I

S-bus output

or via the SPDIF output. The output signal of the mixer is

scaled to a maximum of 0 dB, so the digital output can

never clip.

10

handbook, halfpage

gain

8

(dB)

6

4

2

0

−2

−4

−6

−8

−10

11010

MGU831

2103

f (Hz))

fc=70Hz

fs= 44.1 kHz

Peak gain = 10 dB

Shape factor = 1.4142

Fig.7 Resonant bass boost example 1.

2003 Apr 10 16

fc=70Hz

fs= 44.1 kHz

Peak gain = 10 dB

Shape factor = 1.4142

Fig.8 Resonant bass boost example 2.

Page 17

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

handbook, full pagewidth

channel 2

VOLUME

DE-EMPHASIS

VOLUME

DE-EMPHASIS

channel 1

AND

MUTE

AND

MUTE

mixing before

sound features

BASS-BOOST

AND

TREBLE

Fig.9 Digital mixer (DAC) inside the interpolator DSP.

7.7.4 DIGITAL SILENCE DETECTOR

The UDA1355H is equipped with adigital silence detector.

This detects whether a certain amount of consecutive

samples are 0. The number of samples can be set with

bits SD_VALUE[1:0] to 3200, 4800, 9600 or 19600

samples.

The digital silence detection status can be read via the

microcontroller interface.

7.7.5 NOISE SHAPER (DAC)

The noise shaper shifts in-band quantization noise to

frequencies above the audio band. The noise shaper

output is converted into an analog signal using a Filter

Stream Digital-to-Analog Converter (FSDAC). This noise

shaping technique enables high signal-to-noise ratios to

be achieved.

The UDA1355H is equipped with two noise shapers:

• A third-order noise shaper operating at 128fs. Which is

used at low sampling frequencies (8 to 16 kHz) to

prevent noise shaper noise shifting into the audio band

for the fifth-order noise shaper

• A fifth-order noise shaper operating at 64fs. Which is

used at high sampling frequencies (from 32 kHz

upwards).

When the noise shaper changes, the clock to the FSDAC

changes and the filter characteristic of the FSDAC also

changes. The effect on the roll of is compensated by

selecting the filter matching speed and order of the noise

shaper.

mixing after

sound features

1f

s

output of mixer

L3/I

2

C bit

FILTER

INT.

UDA1355H

MASTER

2f

s

VOLUME

AND

MUTE

to

interpolation

filter and

DAC output

MGU834

7.7.6 FILTER STREAM DAC

The FSDAC is a semi digital reconstruction filter that

converts the 1-bit data bitstream of the noise shaper to an

analog output voltage. The filter coefficients are

implemented as current sources and are summed at

virtual ground of the operational amplifier output. In this

way, very high signal-to-noise performance and low clock

jitter sensitivity are achieved. A post filter is not needed

due to the inherent filter function of the FSDAC. On-chip

amplifiers convert the FSDAC output current to an output

voltage signal capable of driving a line output. The output

voltageoftheFSDAC scales proportionally with the supply

voltage.

7.7.7 DAC MUTE

The DAC and interpolator can be muted by setting

pin MUTE to a HIGH level. The output signal is muted to

zero via a cosine roll-off curve and the DAC is powered

down. When pin MUTE is at LOW level the signal rise

follows the same cosine curve.

To prevent plops in case of changing inputs, clock to the

DAC or application modes, a special mute circuit for the

DAC is implemented (see Table 8).

In all application modes in which the DAC is active the

DAC can be muted by pin MUTE. The microcontroller

mute bits and pin MUTE act as an OR function.

2003 Apr 10 17

Page 18

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

Table 8 Muting to prevent plopping

OCCASION

MT1 MT2 MTM

Input selection

Select channel 1 source x −−no mute after selection

Select channel 2 source − x − no mute after selection

Select chip mode

PLL is source for the DAC −−x wait until PLL is locked again

Crystal is source for the DAC −−x no mute after selection

Select between microcontroller mode and static mode

PLL is source for the DAC −−x wait until PLL is locked again

Crystal is source for the DAC −−x no mute after selection

Audio features

Select noise shaper order −−x no mute after selection

Select FSDAC output polarity −−x no mute after selection

Select SPDIF input −−x PLL is locked again

Select mixer −−−no mute needed

Select mixer position −−−no mute needed

Select crystal clock source −−x no mute after selection

BIT

DE-MUTE CONDITION

7.8 Digital audio input and output

The selection of the digital audio input and output formats

and master or slave modes differ for static and

microcontroller mode.

In master mode, when 256fs output clock is selected and

the digital interface is master, the BCK output clock will be

64fs.Incase384fsoutputclockisselected,theBCK output

clock will be 48fs.

In the static mode the digital audio input formats are:

• I2S-bus

• LSB-justified; 16 bits

• LSB-justified; 24 bits

• MSB-justified.

The digital audio output formats are:

• I2S-bus

• MSB-justified.

In the microcontroller mode, the following formats are

independently selectable:

• I2S-bus

• LSB-justified; 16 bits

• LSB-justified; 18 bits

• LSB-justified; 20 bits

• LSB-justified; 24 bits

• MSB-justified.

7.9 Power-on reset

The UDA1355H has a dedicated reset pin with an internal

pull-down resistor. In this way a Power-on reset circuit can

bemadewithacapacitorandaresistoratpin RESET.The

external resistor is needed since the pad is 5 V tolerant.

This means that there is a transmission gate in series with

the input and the resistor inside the pad cannot be seen

from the outside world (see Fig.10).

The reset timing is determined by the external pull-down

resistor and the external capacitor which is connected to

pin RESET. At Power-on reset, all the digital sound

processing features and the system controlling features

are set to the default setting of the microcontroller mode.

Since the bit controlling the clock of the synchronous

registers is set to enable, the synchronous registers are

also reset.

2003 Apr 10 18

Page 19

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

8 APPLICATION MODES

handbook, halfpage

RESET

Transmission gate

for 5V tolerance

16

UDA1355H

V

SS

MGU835

Fig.10 5 V tolerant pull-down input pad.

The clock should be running during the reset time. When

noclockcanbe guaranteed in microcontroller mode, a soft

reset should be given when the system is running by

writing to register 7FH.

Table 9 Static mode pin assignment

In this chapter the application modes for static mode and

microcontroller mode are described.

The UDA1355H can be controlled by static pins, the

L3-busorI2C-businterface.Duetothelimitationsimposed

bythe pin count, only basic functions are available in static

mode. For optimum use of the UDA1355H features, the

microcontroller mode is strongly recommended.

There are 11 application modes available in the static

mode and 14 application modes in microcontroller mode.

The application modes are explained in the two sections:

Section 8.2 explains the application modes 0 to 10.

Section 8.4 explains the more advanced features of

modes 0 to 10 and modes 12 to 14 available in the

microcontroller mode.

8.1 Static mode pin assignment

The default values for all non-pin controlled settings are

identical to the start-up defaults from the microcontroller

mode.WhetherBCK and WS are master or slave depends

on the selected application mode.

Table 9 defines the pin functions in static mode.

PIN

STATIC MODE

SYMBOL

LEVEL DESCRIPTION

4 LOCK LOW IEC 60958 decoder out of lock (when SPDIF input) or clock

regeneration out of lock (I

2

S-bus input)

HIGH IEC 60958 decoder in lock (when SPDIF input) or clock

regeneration in lock (I

2

S-bus input)

16 RESET LOW normal operation

HIGH reset

17, 18,19MODE0, MODE1,

− select application mode; see Table 10

MODE2

20 SEL_STATIC HIGH static pin control

LOW microcontroller mode

22, 21 SLICER_SEL1,

SLICER_SEL0

LOW, LOW IEC 60958 input from pin SPDIF0

LOW, HIGH IEC 60958 input from pin SPDIF1

HIGH, LOW IEC 60958 input from pin SPDIF2

HIGH, HIGH IEC 60958 input from pin SPDIF3

29 FREQ_SEL LOW select 44.1 kHz sampling frequency for the crystal oscillator,

note 1

MID select 32 kHz sampling frequency for the crystal oscillator, note 1

HIGH select 48 kHz sampling frequency for the crystal oscillator, note 1

2003 Apr 10 19

Page 20

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

PIN

30, 31 SFOR1, SFOR0 LOW, LOW set I

STATIC MODE

SYMBOL

LEVEL DESCRIPTION

2

S-bus format for digital data input and output interface

LOW, HIGH set LSB-justified 16 bits format for digital data input interface and

MSB-justified format for digital data output interface

HIGH, LOW set LSB-justified 24 bits format for digital data input interface and

MSB-justified format for digital data output interface

HIGH, HIGH set MSB-justified format for digital data input and output interface

44 MUTE LOW normal operation

HIGH mute active

Note

1. FPLL 256fs is output from pin CLKOUT in PLL locked static mode.

8.2 Static mode basic applications

The static application modes are selected with the pins MODE2, MODE1 and MODE0, with pin MODE0 being a 3-level

pin. In Table 10, the encoding of the pins MODE[2:0] is given.

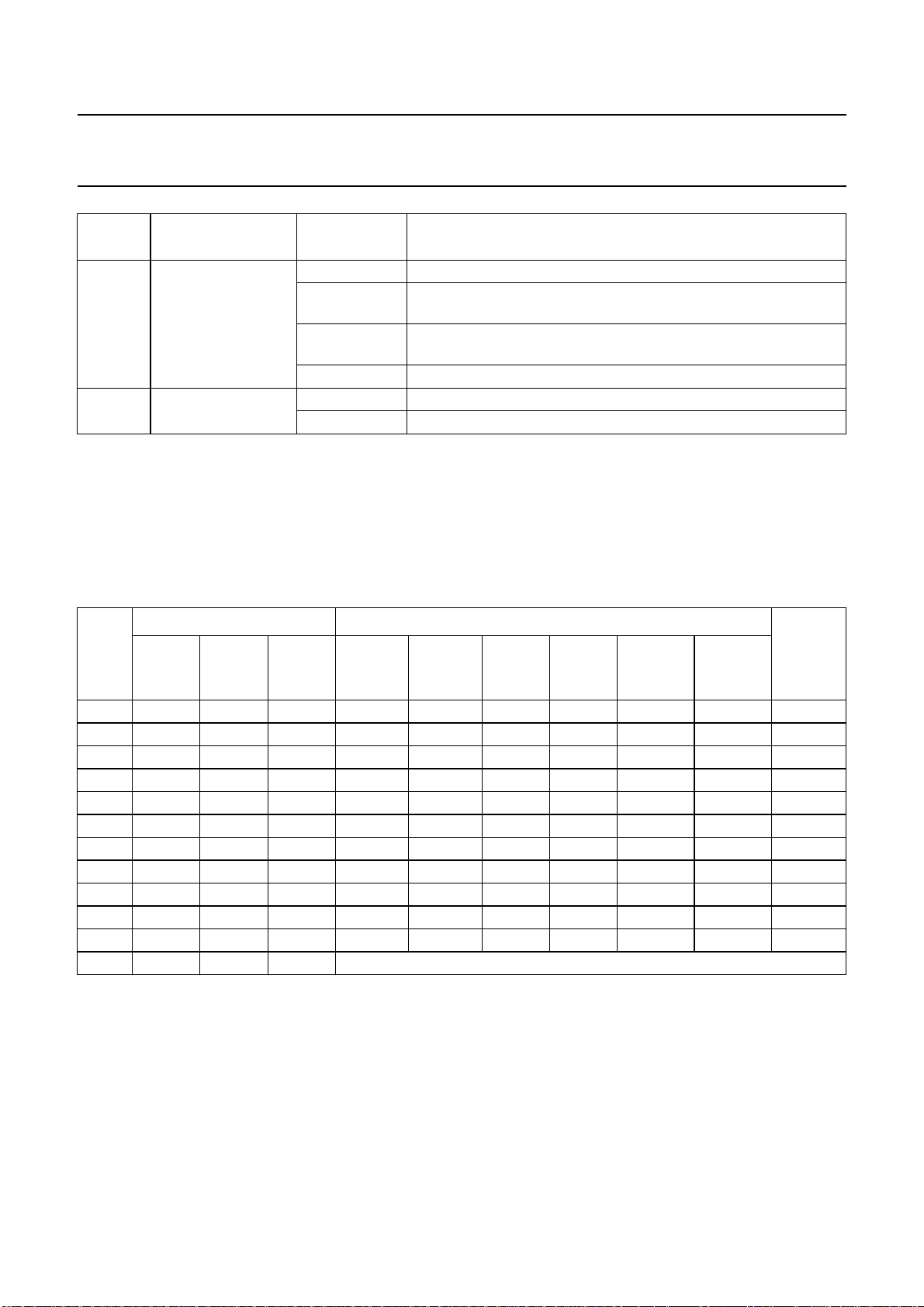

Table 10 Static mode basic applications

MODE

MODE SELECTION PINS

(1)

MODE2 MODE1 MODE0

SPDIF

INPUT

SPDIF

OUTPUT

CLOCK

ADC DAC

(2)

I2S-BUS

INPUT

SLAVE

I2S-BUS

OUTPUT

MASTER

PLL

LOCKS

ON

INPUT

0 L L L PLL PLL − PLL − PLL SPDIF

1L L M − PLL − PLL PLL − I2S-bus

2 L L H PLL PLL − PLL PLL PLL SPDIF

3L H L − xtal xtal −−xtal −

4L H M − xtal xtal xtal xtal xtal −

5L H H − xtal xtal xtal xtal xtal −

6H L L − PLL xtal PLL PLL xtal I

2

S-bus

7 H L M PLL xtal xtal PLL − xtal SPDIF

8H L H − xtal xtal PLL PLL xtal I2S-bus

9 H H L PLL xtal − xtal xtal PLL SPDIF

10 H H M PLL xtal − PLL xtal PLL SPDIF

11 H H H not used

Notes

1. In column mode selection pins means:

L: pin at 0 V; M: pin at half V

; H: pin at V

DDD

DDD

.

2. In column clock means:

xtal: the clock is based on the crystal oscillator; PLL: the clock is based on the PLL.

2003 Apr 10 20

Page 21

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

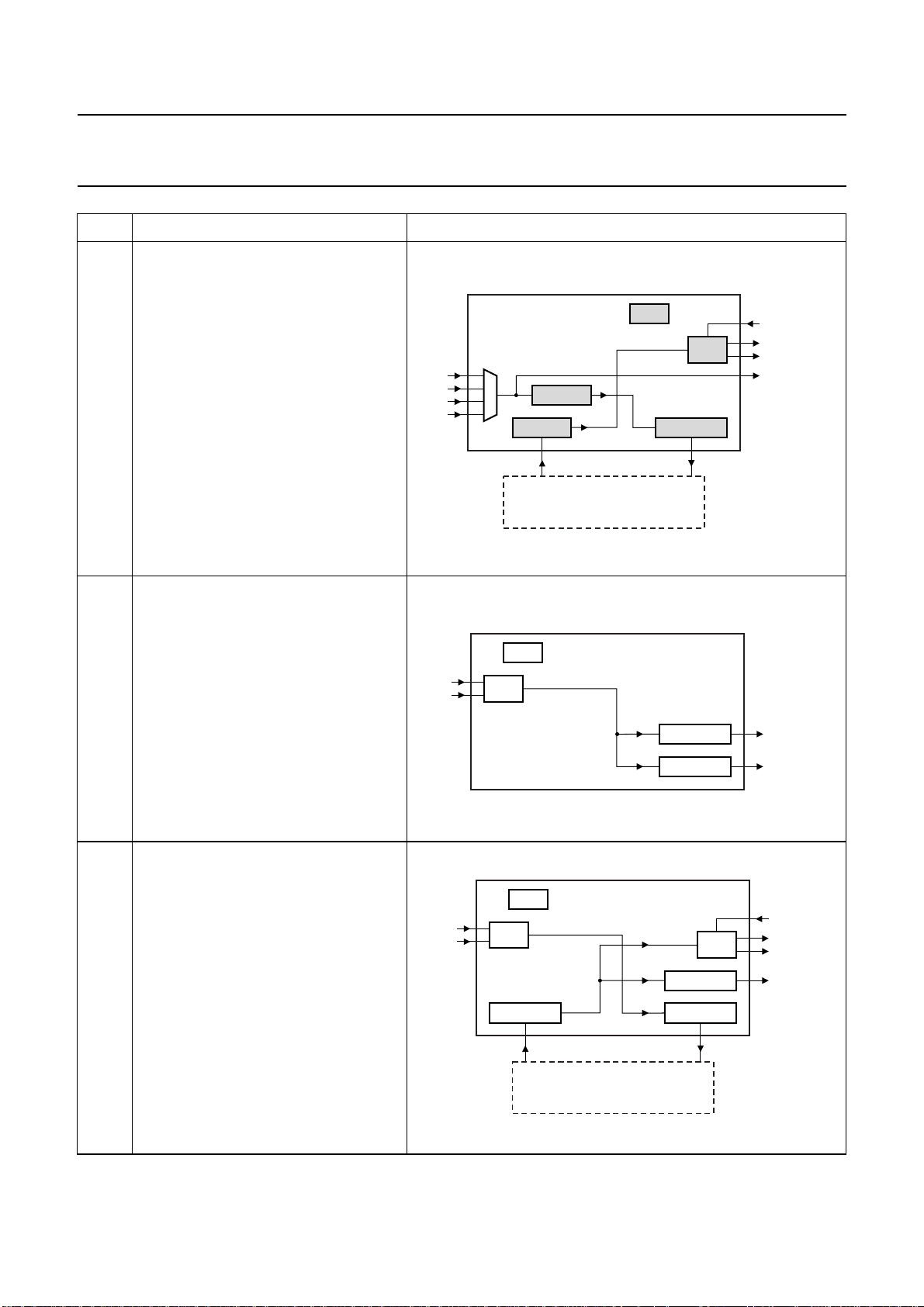

The first 11 application modes are given in this section. Schematic diagrams of these application modes are given in

Table 11. In this table the basic features are mentioned and also the extra features in case of microcontroller mode are

given. It should be noted that the blocks running at the crystal clock (XTAL) are marked unshaded while the blocks

running at the PLL clock are shaded.

Table 11 Overview of static mode basic applications

MODE FEATURES SCHEMATIC

0 Data path:

2

• Input SPDIF to outputs DAC, I

SPDIFOUT via loop through.

Features:

• System locks onto the SPDIF input

signal

• BCK and WS are master

• Microcontroller mode:

– DAC sound features can be used

– SPDIF input channel status bits

(two times 40 bits) can be read.

S or

SPDIF IN

SPDIF LOCK

PLL

MUTE

DAC

SPDIFOUT

I2S OUTPUT I2S master

MGU836

1 Data path:

• Input I

(level II not guaranteed: depends on

I2S-bus clock).

Features:

• System locks onto the WSI signal

• BCKI and WSI are slave

• Microcontroller mode:

– DAC sound features can be used

– SPDIF output channel status bits

(two times 40 bits) setting.

2

S to outputs DAC or SPDIF

I2S slave

I2S INPUT

PLL

I2S LOCK

MUTE

DAC

SPDIF OUT

MGU837

2003 Apr 10 21

Page 22

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

MODE FEATURES SCHEMATIC

2 Data path:

• Input SPDIF to outputs I

SPDIFOUT via loop through

• Input I2S to output DAC.

Features:

• Possibility to process input SPDIF via

2

S-bus using an external DSP and

I

then to output DAC

• System locks onto the SPDIF input

signal

• I2S input and output with BCK and WS

are master

• Microcontroller mode: see Section 8.4.

2

S or

SPDIF IN

I2S INPUT

I2S slave

EXTERNAL DSP

(e.g. equalizing, spatializing)

(SAA7715)

PLL

I2S OUTPUT

SPDIF LOCK

DAC

2

S master

I

MGU838

MUTE

SPDIFOUT

3 Data path:

• Input ADC to outputs I

Features:

• Crystal oscillator generates the clocks

• Microcontroller mode:

– PGA gain setting

– Volume control in decimator setting

– SPDIF output channel status bits

(two times 40 bits) setting.

4 Data path:

• Input ADC to output I

• Input I2S to outputs DAC or SPDIF.

Features:

• Possibility to process input ADC via

2

S-bus using a external DSP and then

I

to outputs DAC or SPDIF

• Crystal oscillator generates the clocks

• I2S input and output with BCK and WS

are master

• Microcontroller mode: see Section 8.4.

2

S or SPDIF.

2

S

ADC

ADC

I

2

XTAL

XTAL

S INPUT

I2S slave

EXTERNAL DSP

(e.g. equalizing, spatializing)

(SAA7715)

SPDIF OUT

I2S OUTPUT

MGU839

DAC

SPDIF OUT

2

I

S OUTPUT

I2S master

MGU840

I2S master

MUTE

2003 Apr 10 22

Page 23

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

MODE FEATURES SCHEMATIC

5 Data path:

• Input ADC to outputs I

• Input I2S to output DAC.

Features:

• Possibility to process input ADC via

2

I

S-bus using an external DSP and

then to output DAC

• Crystal oscillator generates the clocks

• I2S input and output with BCK and WS

are master

• Microcontroller mode: see Section 8.4.

2

S or SPDIF

XTAL

ADC

2

I

S INPUT

I2S slave

EXTERNAL DSP

(e.g. equalizing, spatializing)

(SAA7715)

DAC

SPDIF OUT

2

I

S OUTPUT

I2S master

MGU841

MUTE

6 Data path:

• Input ADC to output I

• Input I2S to outputs DAC or SPDIF

(level II not guaranteed: depends on

I2S-bus clock).

Features:

• Possibility to process input ADC via

2

I

S-bus using an external DSP and

then to outputs DAC or SPDIF

• Crystal oscillator generates the clocks

for input ADC and output I2S

• WSI is slave

• WSO is master

• Microcontroller mode: see Section 8.4.

2

S

I2S LOCK

XTAL

I2S INPUT

I2S slave

EXTERNAL DSP

(SAA7715)

PLL

SPDIF OUT

I

DACADC

2

S OUTPUT

I2S master

MGU842

MUTE

2003 Apr 10 23

Page 24

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

MODE FEATURES SCHEMATIC

7 Data path:

• Input SPDIF to output DAC

• Input ADC to outputs SPDIF or I

Features:

• Crystal oscillator generates the clocks

for outputs SPDIF and I

2

S

• PLL locks onto the SPDIF input signal

• WS of I2S output is master

• Microcontroller mode:

– Decimator features can be used

– DAC sound features can be used

– SPDIF input channel status bits

(two times 40 bits) can be read

– SPDIF output channel status bits

(two times 40 bits) setting.

2

S.

SPDIF LOCK

XTAL

ADC

SPDIF IN

PLL

I

DAC

SPDIF OUT

2

S OUTPUT

MGU843

MUTE

I2S master

8 Data path:

• Input ADC to outputs SPDIF or I

• Input I2S to output DAC.

Features:

• Possibility to process input ADC, via

2

I

S-bus using an external DSP and

then to output DAC

• Crystal oscillator generates the clocks

for outputs SPDIF and I2S

• WSI is slave

• WSO master

• Microcontroller mode:

– Decimator features can be used

– DAC sound features can be used

– SPDIF output channel status bits

(two times 40 bits) setting.

2

S

I2S LOCK

XTAL

ADC

I2S INPUT

I2S slave

EXTERNAL DSP

(e.g. Sample Rate Convertor)

(SAA7715)

PLL

SPDIF OUT

2

I

MUTE

DAC

S OUTPUT

I2S master

MGU844

2003 Apr 10 24

Page 25

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

MODE FEATURES SCHEMATIC

9 Data path:

• Input SPDIF to output I

• Input I2S to outputs DAC or SPDIF.

Features:

• Possibility to process input SPDIF, via

2

I

S-bus using an external DSP and

then to outputs DAC or SPDIF

• BCKand WS being master for both I2S

input and output (different clocks)

• Input I2S to outputs DAC and SPDIF;

BCK and WS being master; clocks

based on crystal oscillator

• Microcontroller mode:

– DAC sound features can be used

– SPDIF output channel status bits

(two times 40) setting.

2

S

SPDIF LOCK

XTAL

SPDIF IN

2

I

S INPUT

I2S slave

EXTERNAL DSP

(e.g. Sample Rate Convertor)

(SAA7715)

PLL

SPDIF OUT

I2S OUTPUT

MGU845

DAC

2

S master

I

MUTE

10 Data path:

• Input SPDIF to output DAC or I

• Input I2S-bus to output SPDIF.

Features:

• Possibility to process input SPDIF, via

2

I

S-bus using an external DSP and

then to output SPDIF

• Input SPDIF to outputs I2S and DAC;

locking onto the SPDIF input signal;

BCK and WS being master

• Input I2S to output SPDIF; BCK and

WS being master; clocks are

generated by the crystal oscillator

• Microcontroller mode:

– DAC sound features can be used

– SPDIF input channel status bits

(two times 40) can be read

– SPDIF output channel status bits

(two times 40) setting.

11 Not used

12 See microcontroller mode

13 See microcontroller mode

14 See microcontroller mode

15 Not used

2

S

SPDIF LOCK

XTAL

SPDIF IN

2

I

S INPUT

I2S slave

EXTERNAL DSP

(e.g. Sample Rate Convertor)

(SAA7715)

PLL

SPDIF OUT

I2S OUTPUT

MGU846

DAC

2

S master

I

MUTE

2003 Apr 10 25

Page 26

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

8.3 Microcontroller mode pin assignment

In microcontroller mode all features become available, such as volume control, PGA gain and mixing (in some modes).

The pin functions are defined in Table 12.

Table 12 Microcontroller mode pin assignment

PIN

SYMBOL

L3-BUS

SYMBOL

I2C-BUS

LEVEL DESCRIPTION

4 LOCK LOCK LOW FPLL and SPDIF are out of LOCK

HIGH FPLL in lock when SPDIF is not used; FPLL or SPDIF in lock when

SPDIF is used

16 RESET RESET LOW normal operation

HIGH reset

17 no function no function LOW connect to ground

18 A0 A0 − A0 address input/output bit (for microcontroller register)

19 U_RDY U_RDY LOW user bit stable

HIGH new user bit

20 SEL_STATIC SEL_STATIC MID I

2

C-bus mode

LOW L3-bus mode

HIGH static mode

21 USER USER − user bit output (new bit every SPDIF sub-frame)

22 AC3 AC3 LOW no I

HIGH I

29 L3MODE no function − L3MODE for L3-bus mode; no function for I

30 L3CLOCK SCL − L3CLOCK for L3-bus mode or SCL for I

31 L3DATA SDA − L3DATA for L3-bus mode or SDA for I

2

S-bus data preamble detected

2

S-bus data preamble detected

2

C-bus

2

C-bus mode

2

C-bus mode

44 MUTE MUTE LOW no mute

HIGH mute active

2003 Apr 10 26

Page 27

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

8.4 Microcontroller mode applications

In Table 13, the encoding of bits MODE[3:0] in the microcontroller mode is given.

Table 13 Microcontroller mode applications

MODE BITS CLOCK

MODE

MODE[3:0]

SPDIF

INPUT

SPDIF

OUTPUT

ADC DAC

0 0000 PLL PLL − PLL - PLL SPDIF

1 0001 − PLL − PLL PLL − I2S

2 0010 PLL PLL PLL PLL PLL PLL SPDIF

3 0011 − xtal xtal −−xtal −

4 0100 − xtal xtal xtal xtal xtal −

5 0101 − xtal xtal xtal xtal xtal −

6 0110 − PLL xtal PLL PLL xtal I

7 0111 PLL xtal xtal PLL − xtal SPDIF

8 1000 − xtal xtal PLL PLL xtal I

9 1001 PLL xtal xtal xtal xtal PLL SPDIF

10 1010 PLL xtal PLL PLL xtal PLL SPDIF

11 1011 not used

12 1100 PLL xtal xtal PLL PLL xtal SPDIF

13 1101 PLL PLL xtal PLL PLL xtal SPDIF

14 1110 − PLL PLL PLL PLL PLL I

15 1111 not used

(1)

I2S-BUS

INPUT

SLAVE

I2S-BUS

OUTPUT

MASTER

PLL

LOCKS

ON

INPUT

2

S

2

S

2

S

Note

1. In column clock means:

xtal: the clock is based on the crystal oscillator; PLL: the clock is based on the PLL.

2003 Apr 10 27

Page 28

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

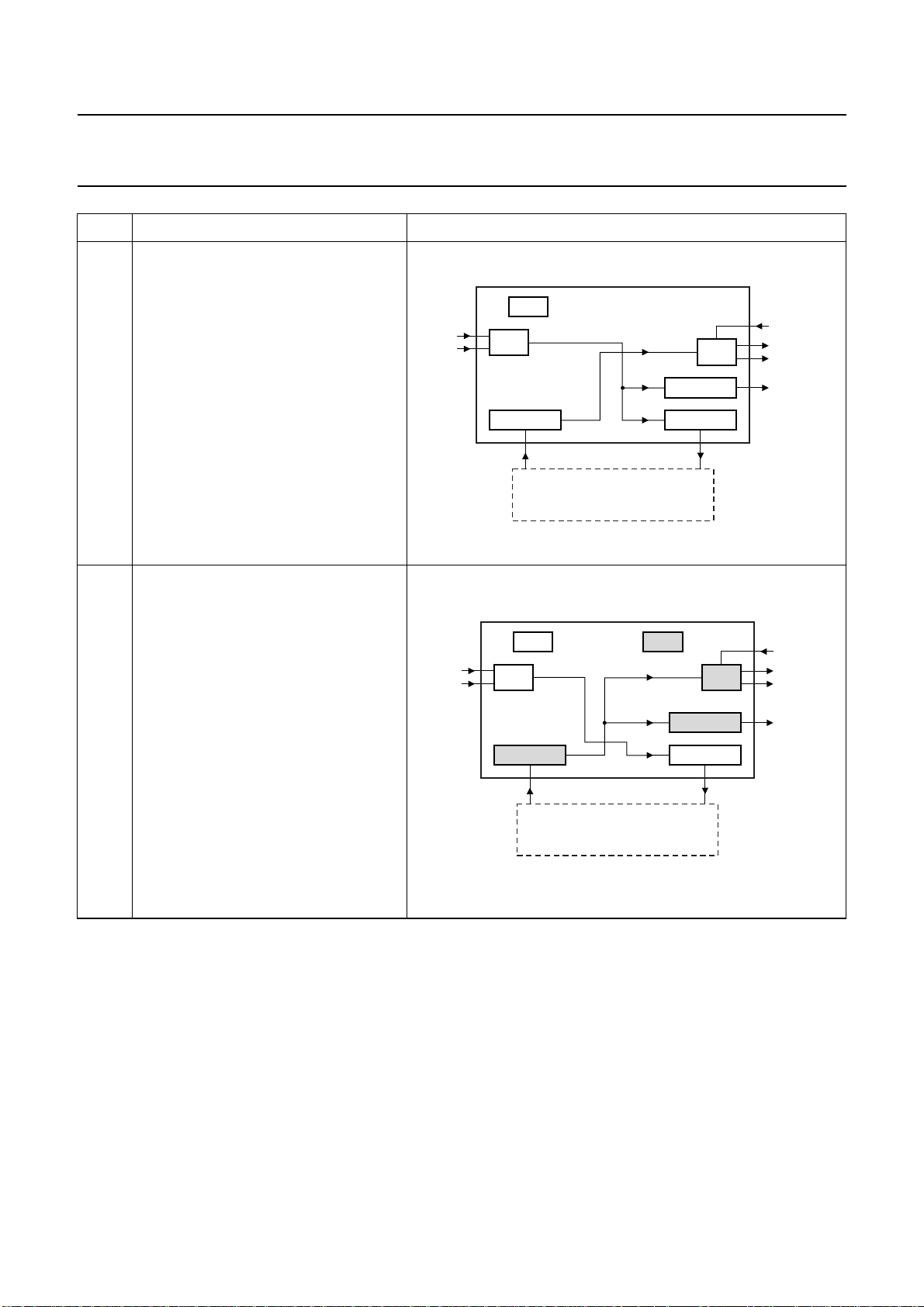

In the microcontroller mode, more features are available. The application modes are given in Table 14. Some modes are

the same in terms of data path as for the static mode. These modes are already explained in Section 8.2. Some modes

are combined into one mode (like modes 4 and 5).

Table 14 Overview of microcontroller modes

MODE FEATURE SCHEMATIC

0 See static mode

1 See static mode

2 Data path:

2

• Inputs ADC, I

DAC, I2S or SPDIF.

Features:

• All clocks are related to the SPDIF

clock

2

S input and output have master BCK

• I

and WS

• SPDIF input channel status bits (two

times 40) can be read

• OutputSPDIFsupported but the timing

not according to level II: depends on

I2S-bus clock

• Output SPDIFOUT loop through can

be selected with independent SPDIF

input channel select.

S and SPDIF to outputs

ADC

SPDIF IN

I2S INPUT

PLL

I2S slave

EXTERNAL DSP

(e.g. equalizing, spatializing)

(SAA7715)

SPDIF LOCK

DAC

SPDIF

OUT

I2S OUTPUT

2

I

MGU847

MUTE

SPDIF OUT

S master

3 See static mode

4 + 5 Data path:

• Inputs ADC and I2S to outputs DAC,

I2S or SPDIF.

Features:

• Mode 4 and 5 are combined in

microcontroller mode

• Crystal oscillator generates the clocks

2

S input and output have master BCK

• I

and WS

• SPDIF output channel status bits (two

times 40) setting.

2003 Apr 10 28

ADC

2

I

S INPUT

XTAL

I2S slave

EXTERNAL DSP

(e.g. equalizing, spatializing)

(SAA7715)

DAC

SPDIF OUT

2

I

S OUTPUT

I2S master

MGU848

MUTE

Page 29

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

MODE FEATURE SCHEMATIC

6 See static mode

7 See static mode

8 See static mode

9 Data path:

• Inputs ADC and I

SPDIF

• Input SPDIF to output I2S.

Features:

• Input SPDIF to output I

and WS being master; the clocks for

this are recovered from the SPDIF

input signal

• Therestoftheclocksaregeneratedby

the crystal oscillator

• SPDIF input channel status bits (two

times 40) can be read

• SPDIF output channel status bits (two

times 40) setting

• Possibility to process input SPDIF, via

I2S-bus using an external DSP and

then to outputs DAC or SPDIF.

2

S to outputs DAC or

2

S with BCK

XTAL

ADC

SPDIF IN

2

I

S INPUT

I2S slave

EXTERNAL DSP

(e.g. Sample Rate Convertor)

(SAA7715)

PLL

SPDIF OUT

I2S OUTPUT

SPDIF LOCK

DAC

2

S master

I

MGU849

MUTE

10 Data path:

• InputsADC and SPDIF to outputs DAC

or I2S

• Input I2S to output SPDIF.

Features:

• BCK and WS are master

• SPDIF input channel status bits (two

times 40) can be read

• SPDIF output channel status bits (two

times 40) setting

• Possibility to process inputs ADC or

SPDIF, via I

2

S-bus using an external

DSP and then to output SPDIF.

11 Not used

XTAL

ADC

SPDIF IN

2

I

S INPUT

I2S slave

EXTERNAL DSP

(e.g. Sample Rate Convertor)

(SAA7715)

PLL

SPDIF OUT

I2S OUTPUT

SPDIF LOCK

DAC

2

I

S master

MGU850

MUTE

2003 Apr 10 29

Page 30

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

MODE FEATURE SCHEMATIC

12 Data path:

• Input ADC to outputs I

• Inputs I2S and SPDIF to output DAC.

Features:

• BCK and WS of I

• Inputs SPDIF and I2S to output DAC

withmixing/selection possibility; clocks

aregenerated fromSPDIFinput signal,

and BCK and WS are master

• SPDIF input channel status bits (two

times 40) can be read

• SPDIF output channel status bits (two

times 40) setting.

2

S or SPDIF

2

S output are master

XTAL

ADC

SPDIF IN

I2S INPUT

PLL

I

SPDIF LOCK

DAC

SPDIF OUT

2

S OUTPUT

MGU851

MUTE

I2S masterI2S slave

13 Data path:

• Input ADC to output I

2

S

• Inputs I2S and SPDIF to outputs DAC

or SPDIF.

Features

• BCK and WS being master

• SPDIF input channel status bits (two

times 40) can be read

• OutputSPDIFsupported but the timing

not according to level II

• Output SPDIFOUT loop through can

be selected with independent SPDIF

input channel select.

14 Data path:

2

• Inputs ADC and I

S to outputs DAC

SPDIF and I2S.

Features:

• All clocks are related to WS signal of

2

I

S-bus input

• Master BCK and WS for I2S output;

slave BCK and WS for I2S input

• SPDIF output channel status bits (two

times 40) can be set; level II timing

depends on the I2S-bus clocks.

2

S slave

I

XTAL

ADC

SPDIF IN

I2S INPUT

ADC

I2S INPUT

PLL

SPDIF

OUT

2

I

S OUTPUT

PLL

SPDIF OUT

I2S OUTPUT

SPDIF LOCK

MUTE

DAC

SPDIF OUT

I2S master

MGU852

I2S LOCK

MUTE

DAC

I2S masterI2S slave

15 Not used

2003 Apr 10 30

MGU853

Page 31

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

9 SPDIF SIGNAL FORMAT

9.1 SPDIF channel encoding

The digital signal is coded using Biphase Mark Code

(BMC), which is a kind of phase modulation. In this

scheme, a logic 1 in the data corresponds to two

zero-crossings in the coded signal, and a logic 0 to one

zero-crossing. An example of the encoding is given in

Fig.11.

handbook, halfpage

clock

data

BMC

MGU606

Fig.11 Biphase mark encoding.

9.2 SPDIF hierarchical layers

The SPDIF signal format is shown in Fig.12. A PCM signal

is transmitted in sequential blocks. Each block consists

of 192 frames. Each frame contains two sub-frames, one

for each channel. Each subframe is preceded by a

preamble. There are three types of preambles: B, M

and W. Preambles can be spotted easily in an SPDIF

bitstream because these sequences never occur in the

channel parts of a valid SPDIF bitstream.

The sub-frame format is represented by Fig.13.

A sub-frame contains a single audio sample word which

may be 24 bits wide, a validity bit which indicates whether

the sample is valid, a bit containing user data, a bit

indicating the channel status and a parity bit for this

sub-frame.

Thedata bits 31 to 4 in each sub-frame are encodedusing

a BMC scheme. The sync preamble contains a violation of

the BMC scheme and can be detected. Table 15 indicates

the values of the preambles.

handbook, full pagewidth

channel 1MMMWW WBchannel 2 channel 1

handbook, full pagewidth

03478 27 28 31

sync

preamble

L

S

B

auxiliary

sub-frame

L

S

B

channel 2 channel 1 channel 2 channel 1 channel 2

sub-frame

frame 0 frame 191frame 191

block

Fig.12 SPDIF signal format

validity flag

user data

channel status

parity bit

MGU607

M

S

B

CUV

MGU608

Paudio sample word

Fig.13 Sub-frame format

2003 Apr 10 31

Page 32

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

Table 15 Preambles

PRECEDING

STATE

CHANNEL CODING

01

B 11101000 00010111

M 11100010 00011101

W 11100100 00011011

9.3 Timing characteristics

9.3.1 F

REQUENCY REQUIREMENTS

The SPDIF specification IEC 60958 supports three levels

of clock accuracy:

• Level I high accuracy: Tolerance of transmitting

sampling frequency shall be within 50 × 10

−6

• Level II, normal accuracy: All receivers should receive a

signal of 1000 × 10−6 of nominal sampling frequency

• Level III, variable pitch shifted clock mode: A deviation

of 12.5% of the nominal sampling frequency is possible.

The UDA1355H inputs support level I, II, and III as

specified by the IEC 60958 standard.

9.3.2 RISE AND FALL TIMES

Rise and fall times (see Fig.14) are defined as:

t

Rise time =

Fall time =

--------------tLtH+

t

f

--------------tLtH+

r

100%×

100%×

Rise and fall times should be in the range:

• 0% to 20% when the data bit is a logic 1

• 0% to 10% when the data bits are two succeeding

logic 0.

9.3.3 D

UTY CYCLE

The duty cycle (see Fig.14) is defined as:

t

Duty cycle =

H

--------------tLtH+

100%×

The duty cycle should be in the range:

• 40% to 60% when the data bit is a logic 1

• 45% to 55% when the data bits are two succeeding

logic 0.

10 L3-BUS DESCRIPTION

Theexchange of data and control information between the

microcontroller and the UDA1355H is accomplished

through a serial hardware L3-bus interface comprising the

following pins:

• MP0: mode line with signal L3MODE

• MP1: clock line with signal L3CLOCK

• MP2: data line with signal L3DATA.

The exchange of bytes in L3-bus mode is LSB first.

The L3-bus format has two modes of operation:

• Address mode

• Data transfer mode.

The address mode is used to select a device for a

subsequent data transfer. The address mode is

characterized by L3MODE being LOW and a burst of

8 pulses on L3CLOCK, accompanied by 8 bits (see

Fig.15). The data transfer mode is characterized by

L3MODE being HIGH and is used to transfer one or more

bytes representing a register address, instruction or data.

Basically two types of data transfers can be defined:

• Write action: data transfer to the device

• Read action: data transfer from the device.

handbook, halfpage

90%

50%

10%

t

H

t

r

t

L

t

f

MGU612

Fig.14 Rise, fall time and duty cycle.

2003 Apr 10 32

10.1 Device addressing

The device address consists of one byte with:

• Data Operating Mode (DOM) bits 0 and 1 representing

the type of data transfer (see Table 16)

• Address bits 2 to 7 representing a 6-bit device address.

Page 33

Philips Semiconductors Preliminary specification

Stereo audio codec with SPDIF interface UDA1355H

Table 16 Selection of data transfer

DOM BITS

BIT 0 BIT 1

0 0 not used

1 0 not used

0 1 write data or prepare read

1 1 read data

ThedeviceaddressoftheUDA1355Hisgiven in Table 17,

being the first 6 bits of the device address byte. The

address can be set one of two by using pin MODE1

(pin A0 in microcontroller mode).

Table 17 L3-bus device address

MSB ADDRESS LSB

00001A0

Remark: When using the device address, there is often

misunderstanding. This is caused by the fact that the data

is sent LSB first. This means that when we use the device

address in, for example the Philips L3-bus/I

bithacker’, we have to use the address like LSB → MSB.

For the UDA1355H this means that the device address to

be used is either 10H (010000) or 30H (110000).

10.2 Register addressing

After sending the device address, including Data

Operating Mode (DOM) bits indicating whether the

information is to be read or written, one data byte is sent

using bit 0 to indicate whether the information will be read

or written and bits 1 to 7 for the destination register

address.

Basically there are three methods for register addressing:

• Addressing for write data: bit 0 is logic 0 indicating a

write action to the destination register, followed by

bits 1 to 7 indicating the register address (see Fig.15)

• Addressing for prepare read: bit 0 is logic 1 indicating

that data will be read from the register (see Fig.16)

• Addressing for data read action: in this case the device

returnsaregisteraddresspriortosendingdata from that

register. When bit 0 is logic 0, the register address is

valid; in case bit 0 is logic 1 the register address is

invalid.

TRANSFER

2

C-bus

10.3 Data write mode

The data write mode is explained in the signal diagram of

Fig.15.

For writing data to a device, 4 bytes must be sent (see

Table 18):

• Byte 1 starting with 01 for signalling the write action to

the device, followed by the device address

• Byte 2 starting with 0 for signalling the write action,

followed by 7 bits indicating the destination address in

binary format with A6 being the MSB and A0 being the

LSB

• Byte 3 with bit D15 being the MSB

• Byte 4 with bit D0 being the LSB.

Itshould be noted that each time anewdestinationregister

address needs to be written, the device address must be

sent again.

10.4 Data read mode

For reading data from the device, first a prepare read must

be done and then data read. The data read mode is

explained in the signal diagram of Fig.16.

For reading data from a device, the following 6 bytes are

involved (see Table 19):

• Byte 1 with the device address including 01 for

signalling the write action to the device

• Byte 2 is sent with the register address from which data

needstobe read. This byte starts with 1, which indicates

thattherewillbe a read action from the register, followed

again by 7 bits for the destination address in binary

format with A6 being the MSB and A0 being the LSB

• Byte 3with the device address including 11issentto the

device. The 11 indicates that the device must write data

to the microcontroller

• Byte 4, sent by the device to the bus, with the