INTEGRATED CIRCUITS

DATA SH EET

PCF8570

256 × 8-bit static low-voltage RAM

with I

Preliminary specification

File under Integrated Circuits, IC12

Philips Semiconductors

2

C-bus interface

August 1994

Philips Semiconductors Preliminary specification

256 × 8-bit static low-voltage RAM with

2

I

C-bus interface

FEATURES

• Operating supply voltage 2.5 to 6.0 V

• Low data retention voltage; minimum 1.0 V

• Low standby current; maximum 15 µA

• Power saving mode; typical 50 nA

• Serial input/output bus (I2C-bus)

• Address by 3 hardware address pins

• Automatic word address incrementing

• Available in DIP8 and SO8L packages.

APPLICATIONS

• Telephony:

– RAM expansion for stored numbers in repertory

dialling (e.g. PCD33XX applications)

• General purpose RAM for applications requiring

extremely low current and low-voltage RAM retention

(i.e. battery or capacitor backed)

• Radio, television and video cassette recorder:

– channel presets

• General purpose:

– RAM expansion for the microcontroller families

PCD33XX, PCF84CXX, P80CLXXX and most other

microcontrollers.

PCF8570

GENERAL DESCRIPTION

The PCF8570 is a low power static CMOS RAM.

The PCF8570 is organized as 256 words by 8-bits.

Addresses and data are transferred serially via a two-line

bidirectional bus (I

register is incremented automatically after each written or

read data byte. Three address pins, A0, A1 and A2 are

used to define the hardware address, allowing the use of

up to 8 devices connected to the bus without additional

hardware.

2

C-bus). The built-in word address

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DD

I

DD

I

DDR

T

amb

T

stg

ORDERING INFORMATION

TYPE NUMBER

PCF8570P 8 DIP8 plastic SOT97-1

PCF8570T 8 SO8L plastic SOT176-1

August 1994 2

supply voltage 2.5 6.0

supply current (standby) f

supply current (power-saving mode) T

operating ambient temperature −40 +85 °C

storage temperature −65 +150 °C

PACKAGE

PINS PIN POSITION MATERIAL CODE

= 0 Hz − 15 µA

SCL

= 25 °C − 400 nA

amb

Philips Semiconductors Preliminary specification

256 × 8-bit static low-voltage RAM with

2

I

C-bus interface

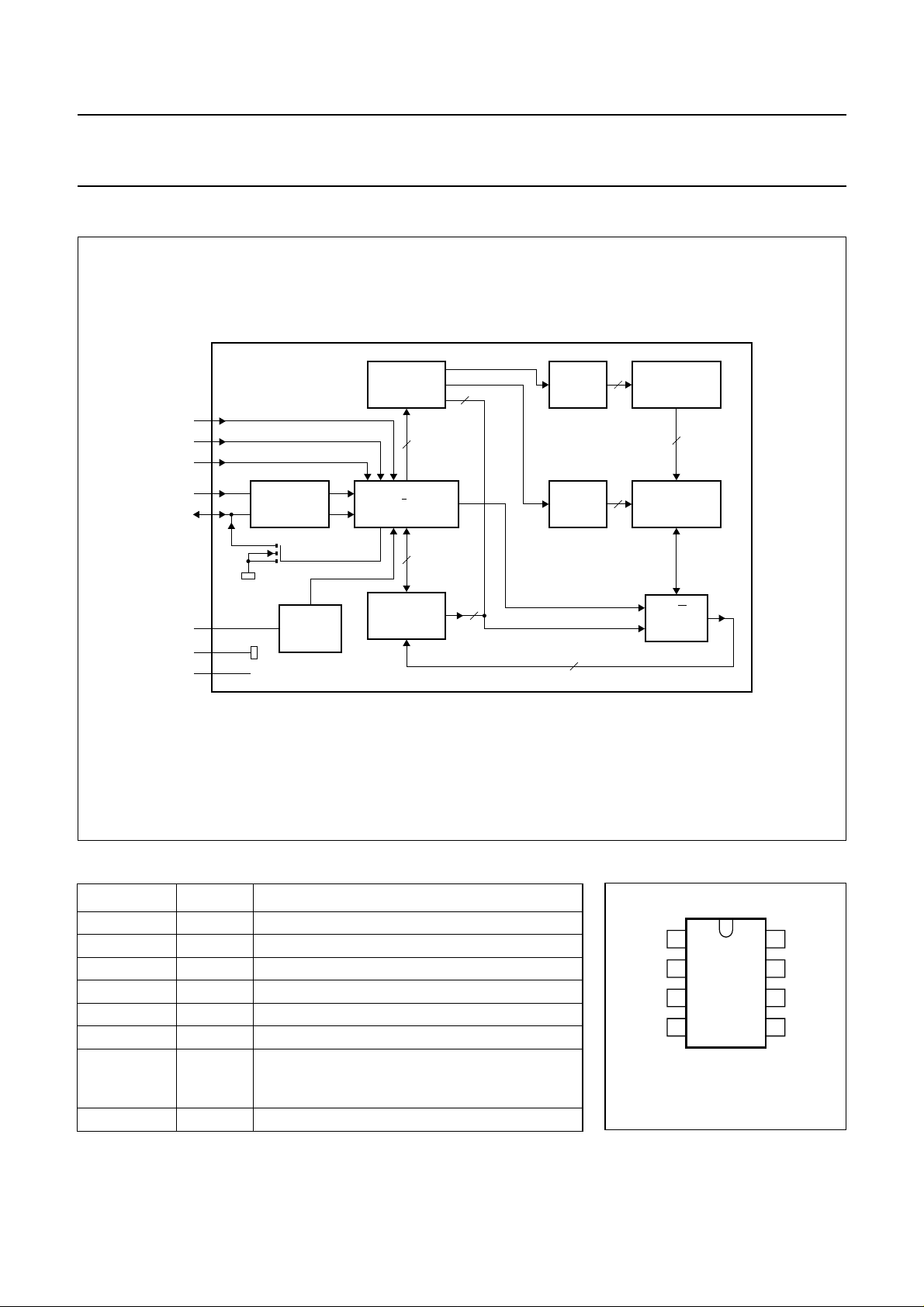

BLOCK DIAGRAM

handbook, full pagewidth

WORD

ADDRESS

REGISTER

2

I C BUS

CONTROL

A0

A1

A2

SCL

SDA

1

2

3

6

5

PCF8570C

INPUT

FILTER

PCF8570

ROW

7

SELECT

COLUMN

SELECT

MEMORY

CELL

ARRAY

MULTIPLEXER

8

V

DD

V

SS

TEST

8

4

7

POWER

ON

RESET

SHIFT

REGISTER

Fig.1 Block diagram.

PINNING

SYMBOL PIN DESCRIPTION

A0 1 hardware address input 0

A1 2 hardware address input 1

A2 3 hardware address input 2

V

SS

4 negative supply

SDA 5 serial data input/output

SCL 6 serial clock input

TEST 7 test output for test speed-up; must be connected

to V

when not in use (power saving mode, see

SS

Figs 13 and 14)

V

DD

8 positive supply

R/W

CONTROL

age

A0

1

A1

2

PCF8570C

A2

3

V

4

SS

Fig.2 Pin configuration.

MLB928

MLB929

V

8

DD

7

TEST

6

SCL

SDA

5

August 1994 3

Philips Semiconductors Preliminary specification

256 × 8-bit static low-voltage RAM with

2

I

C-bus interface

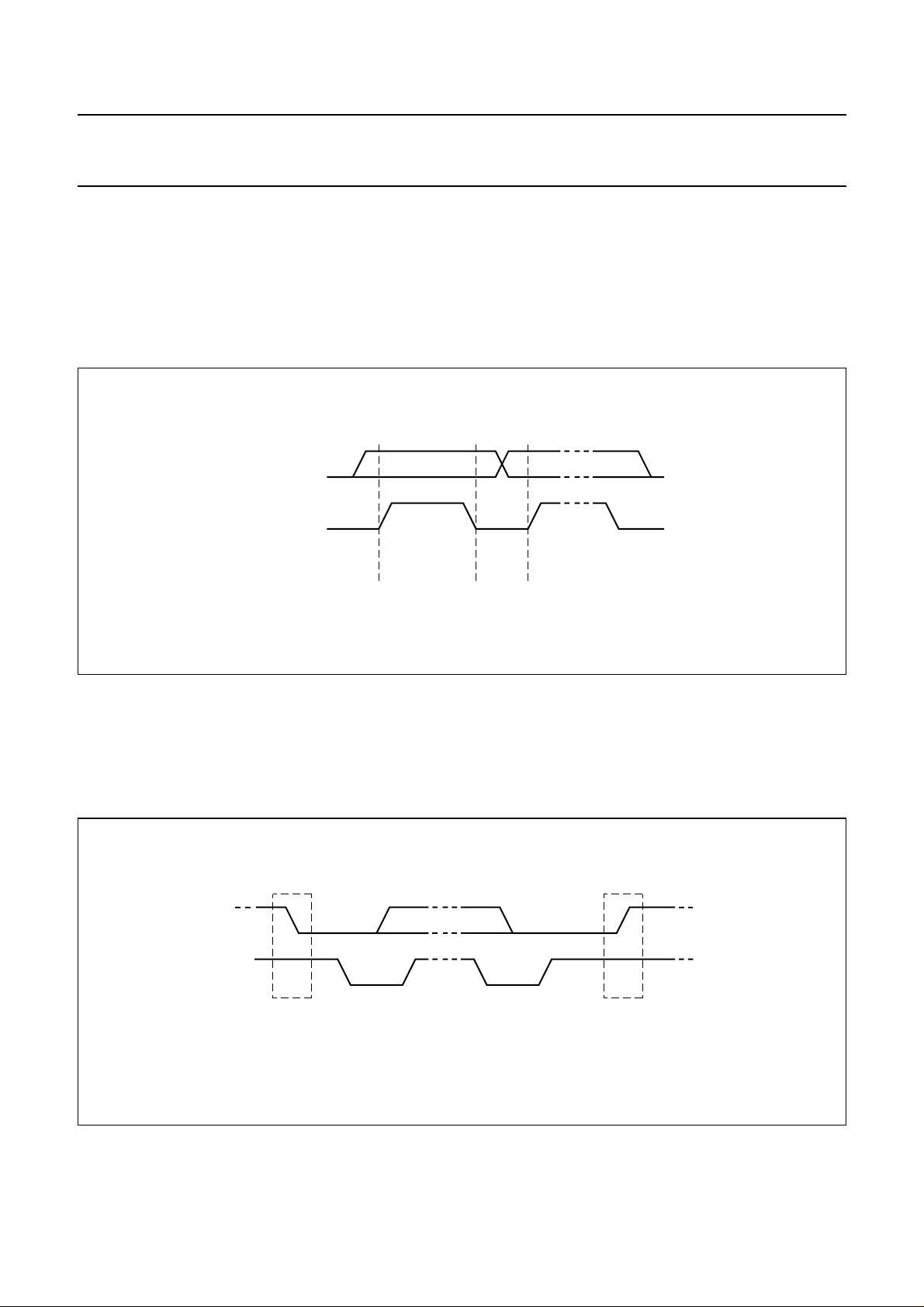

CHARACTERISTICS OF THE I2C-BUS

The I2C-bus is for bidirectional, two-line communication

between different ICs or modules. The two lines are a

serial data line (SDA) and a serial clock line (SCL). Both

lines must be connected to a positive supply via a pull-up

resistor. Data transfer may be initiated only when the bus

is not busy.

SDA

SCL

data line

stable;

data valid

PCF8570

Bit transfer

One data bit is transferred during each clock pulse. The

data on the SDA line must remain stable during the HIGH

period of the clock pulse as changes in the data line at this

time will be interpreted as a control signal.

change

of data

allowed

MBA607

Fig.3 Bit transfer.

Start and stop conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the

clock is HIGH is defined as the start condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is

defined as the stop condition (P).

SDA

SCL

S

START condition

P

STOP condition

SDA

SCL

MBA608

Fig.4 Definition of start and stop conditions.

August 1994 4

Philips Semiconductors Preliminary specification

256 × 8-bit static low-voltage RAM with

2

I

C-bus interface

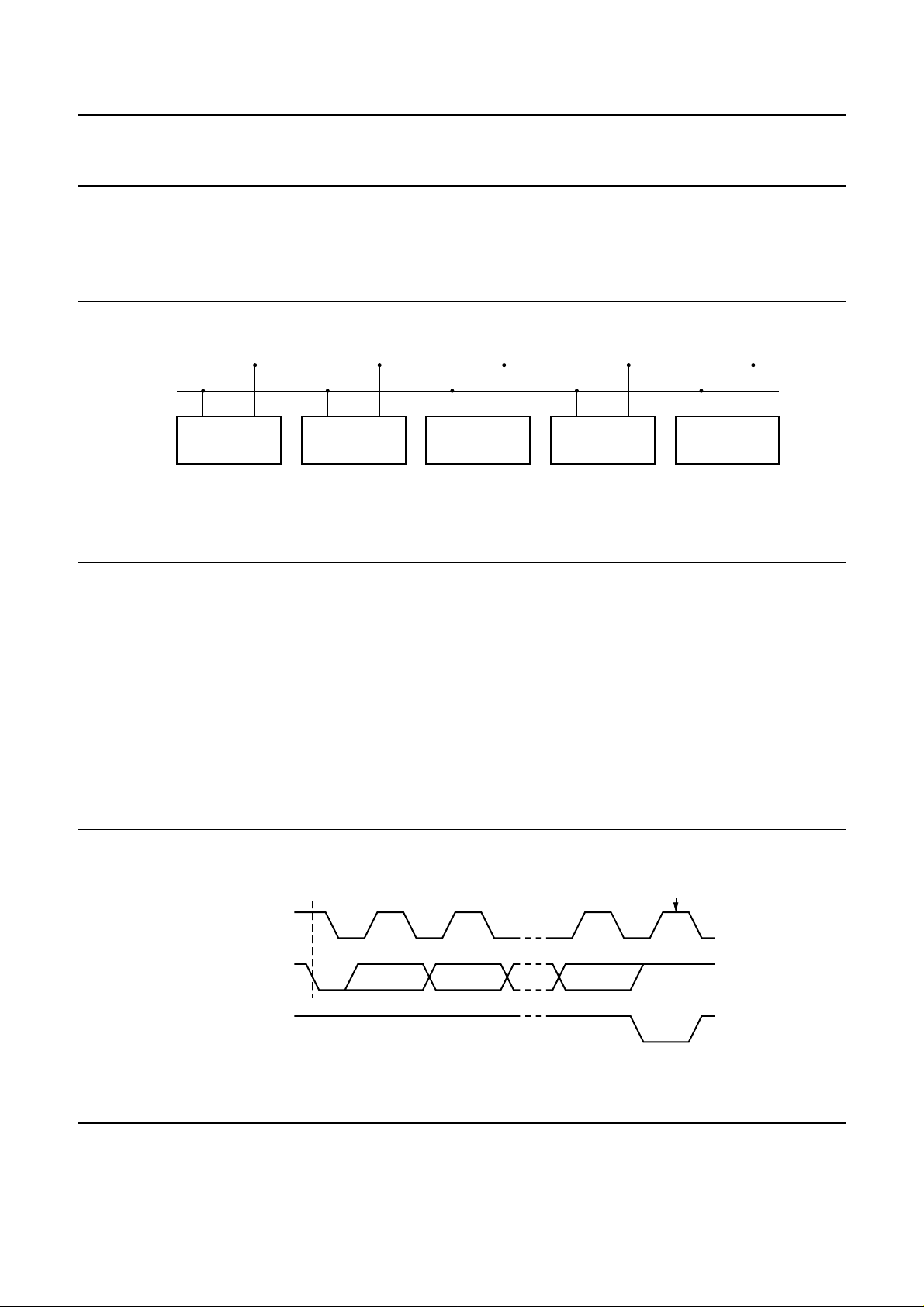

System configuration

A device generating a message is a ‘transmitter’, a device receiving a message is the ‘receiver’. The device that controls

the message is the ‘master’ and the devices which are controlled by the master are the ‘slaves’.

SDA

SCL

MASTER

TRANSMITTER /

RECEIVER

SLAVE

RECEIVER

SLAVE

TRANSMITTER /

RECEIVER

MASTER

TRANSMITTER

TRANSMITTER /

Fig.5 System configuration.

PCF8570

MASTER

RECEIVER

MBA605

Acknowledge

The number of data bytes transferred between the start

and stop conditions from transmitter to receiver is

unlimited. Each byte of eight bits is followed by an

acknowledge bit. The acknowledge bit is a HIGH level

signal put on the bus by the transmitter during which time

the master generates an extra acknowledge related clock

pulse. A slave receiver which is addressed must generate

an acknowledge after the reception of each byte. Also a

master receiver must generate an acknowledge after the

reception of each byte that has been clocked out of the

slave transmitter.

handbook, full pagewidth

BY TRANSMITTER

SCL FROM

MASTER

DATA OUTPUT

DATA OUTPUT

BY RECEIVER

START

condition

S

1

The device that acknowledges must pull down the SDA

line during the acknowledge clock pulse, so that the SDA

line is stable LOW during the HIGH period of the

acknowledge related clock pulse (set-up and hold times

must be taken into consideration). A master receiver must

signal an end of data to the transmitter by not generating

an acknowledge on the last byte that has been clocked out

of the slave. In this event the transmitter must leave the

data line HIGH to enable the master to generate a stop

condition.

clock pulse for

acknowledgement

2

8

MBA606 - 1

9

Fig.6 Acknowledgement on the I2C-bus.

August 1994 5

Philips Semiconductors Preliminary specification

256 × 8-bit static low-voltage RAM with

2

I

C-bus interface

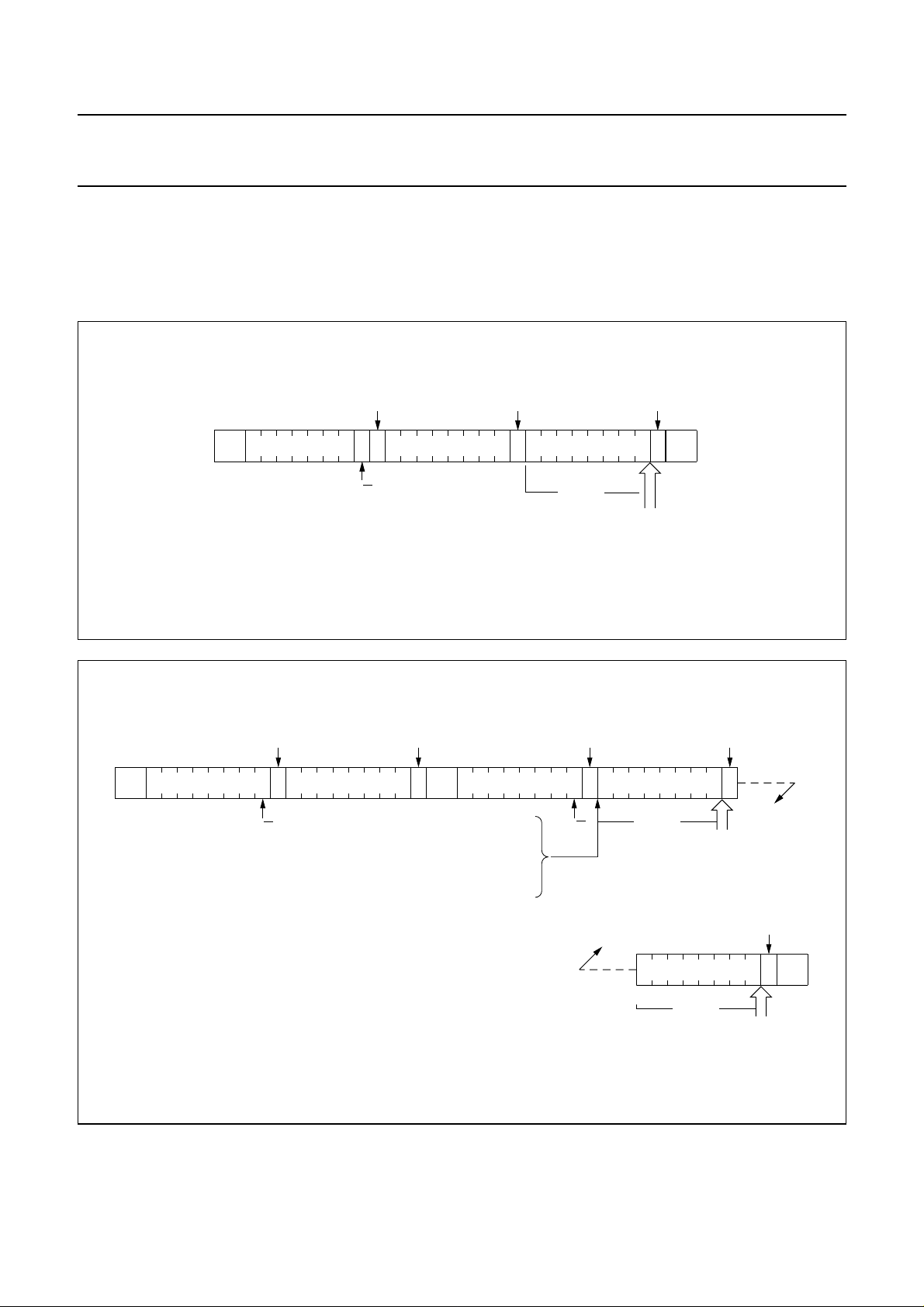

I2C-bus protocol

Before any data is transmitted on the I2C-bus, the device which should respond is addressed first. The addressing is

always carried out with the first byte transmitted after the start procedure. The I2C-bus configuration for the different

PCF8570 WRITE and READ cycles is shown in Figs 7, 8 and 9.

handbook, full pagewidth

acknowledgement

from slave

S 0ASLAVE ADDRESS WORD ADDRESS A ADATA P

R/W

acknowledgement

from slave

n bytes

acknowledgement

from slave

auto increment

memory word address

MBD822

PCF8570

Fig.7 Master transmits to slave receiver (WRITE) mode.

handbook, full pagewidth

S 0ASLAVE ADDRESS WORD ADDRESS A ASLAVE ADDRESS

acknowledgement

from slave

R/W

acknowledgement

from slave

S1

at this moment master transmitter becomes

master - receiver and

PCF8570C slave receiver becomes

slave - transmitter

acknowledgement

from slave

R/W

MLB930

acknowledgement

from master

n bytes

auto increment

memory word address

last byte

memory word address

ADATA

no acknowledgement

from master

P

1DATA

auto increment

Fig.8 Master reads after setting word address (WRITE word address; READ data).

August 1994 6

Loading...

Loading...