Philips PCF8566U, PCF8566U-10, PCF8566P Datasheet

DATA SH EET

Product specification

Supersedes data of 1997 Apr 02

File under Integrated Circuits, IC12

1998 May 04

INTEGRATED CIRCUITS

PCF8566

Universal LCD driver for low

multiplex rates

1998 May 04 2

Philips Semiconductors Product specification

Universal LCD driver for low multiplex

rates

PCF8566

CONTENTS

1 FEATURES

2 GENERAL DESCRIPTION

3 ORDERING INFORMATION

4 BLOCK DIAGRAM

5 PINNING

6 FUNCTIONAL DESCRIPTION

6.1 Power-on reset

6.2 LCD bias generator

6.3 LCD voltage selector

6.4 LCD drive mode waveforms

6.5 Oscillator

6.6 Internal clock

6.7 External clock

6.8 Timing

6.9 Display latch

6.10 Shift register

6.11 Segment outputs

6.12 Backplane outputs

6.13 Display RAM

6.14 Data pointer

6.15 Subaddress counter

6.16 Output bank selector

6.17 Input bank selector

6.18 Blinker

7I

2

C-BUS DESCRIPTION

7.1 Bit transfer

7.2 Start and stop conditions

7.3 System configuration

7.4 Acknowledge

7.5 PCF8566 I2C-bus controller

7.6 Input filters

7.7 I2C-bus protocol

7.8 Command decoder

7.9 Display controller

7.10 Cascaded operation

8 LIMITING VALUES

9 HANDLING

10 DC CHARACTERISTICS

11 AC CHARACTERISTICS

12 APPLICATION INFORMATION

13 CHIP DIMENSIONS AND BONDING PAD

LOCATIONS

14 PACKAGE OUTLINES

15 SOLDERING

15.1 Introduction

15.2 DIP

15.2.1 Soldering by dipping or by wave

15.2.2 Repairing soldered joints

15.3 SO and VSO

15.3.1 Reflow soldering

15.3.2 Wave soldering

15.3.3 Repairing soldered joints

16 DEFINITIONS

17 LIFE SUPPORT APPLICATIONS

18 PURCHASE OF PHILIPS I2C COMPONENTS

1998 May 04 3

Philips Semiconductors Product specification

Universal LCD driver for low multiplex

rates

PCF8566

1 FEATURES

• Single-chip LCD controller/driver

• Selectable backplane drive configuration: static

or 2, 3 or 4 backplane multiplexing

• Selectable display bias configuration: static,1⁄2or1⁄

3

• Internal LCD bias generation with voltage-follower

buffers

• 24 segment drives: up to twelve 8-segment numeric

characters; up to six 15-segment alphanumeric

characters; or any graphics of up to 96 elements

• 24 × 4-bit RAM for display data storage

• Auto-incremented display data loading across device

subaddress boundaries

• Display memory bank switching in static and duplex

drive modes

• Versatile blinking modes

• LCD and logic supplies may be separated

• 2.5 to 6 V power supply range

• Low power consumption

• Power saving mode for extremely low power

consumption in battery-operated and telephone

applications

• I

2

C-bus interface

• TTL/CMOS compatible

• Compatible with any 4-bit, 8-bit or 16-bit

microprocessors/microcontrollers

• May be cascaded for large LCD applications

(up to 1536 segments possible)

• Cascadable with the 40 segment LCD driver PCF8576C

• Optimized pinning for single plane wiring in both single

and multiple PCF8566 applications

• Space-saving 40 lead plasticvery small outline package

(VSO40; SOT158-1)

• No external components required (even in multiple

device applications)

• Manufactured in silicon gate CMOS process.

2 GENERAL DESCRIPTION

The PCF8566 is a peripheral device which interfaces to

almost any Liquid Crystal Display (LCD) having low

multiplex rates. It generates the drive signals for any static

or multiplexed LCD containing up to four backplanes and

up to 24 segments and can easily be cascaded for larger

LCD applications. The PCF8566 is compatible with most

microprocessors/microcontrollers and communicates via a

two-line bidirectional I

2

C-bus. Communication overheads

are minimized by a display RAM with auto-incremented

addressing, by hardware subaddressing and by display

memory switching (static and duplex drive modes).

3 ORDERING INFORMATION

TYPE NUMBER

PACKAGE

NAME DESCRIPTION VERSION

PCF8566P DIP40 plastic dual in-line package; 40 leads (600 mil) SOT129-1

PCF8566T VSO40 plastic very small outline package; 40 leads SOT158-1

1998 May 04 4

Philips Semiconductors Product specification

Universal LCD driver for low multiplex

rates

PCF8566

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

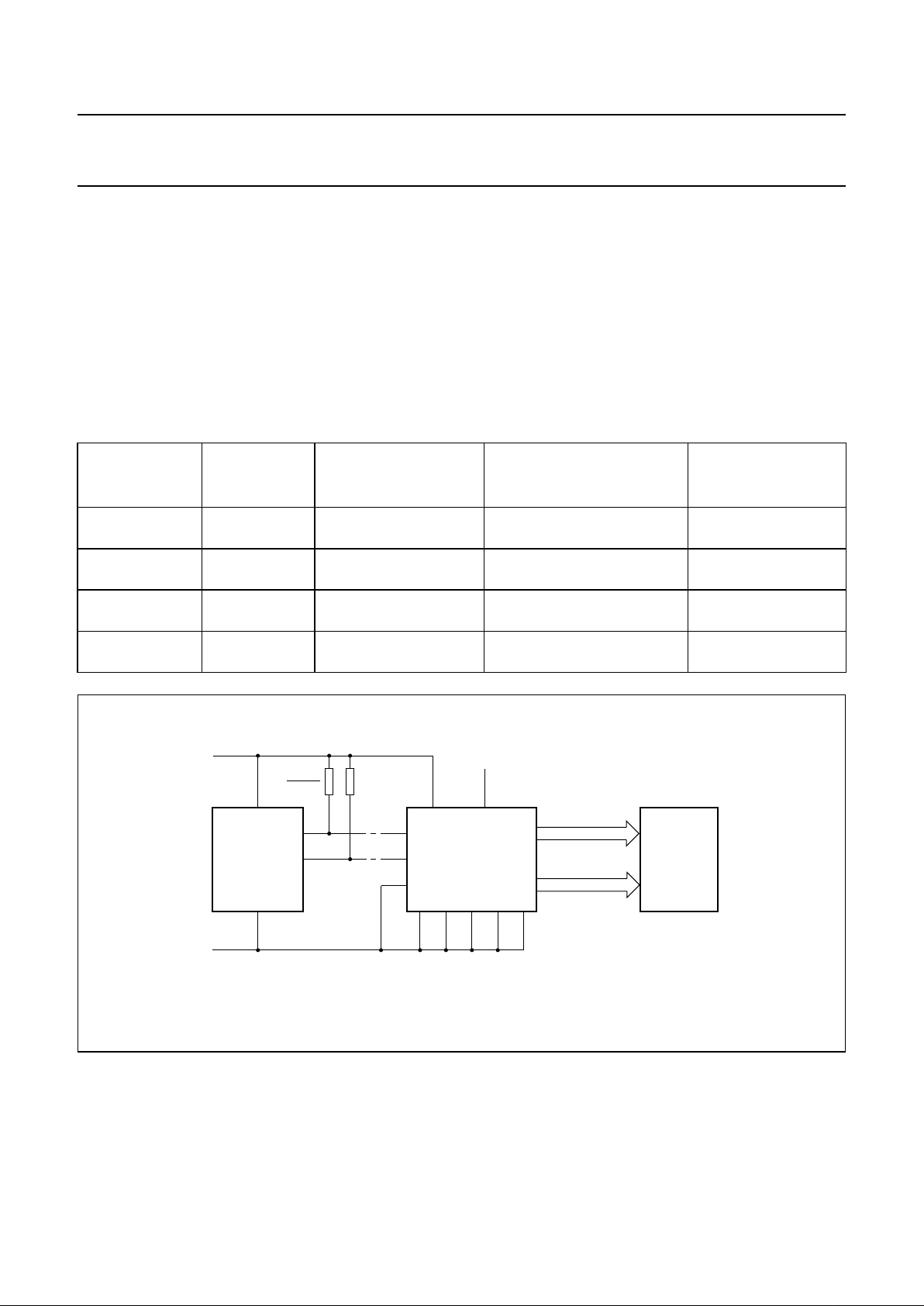

4 BLOCK DIAGRAM

a

ndbook, full pagewidth

MGG383

LCD

VOLTAGE

SELECTOR

12

5

TIMING BLINKER

OSCILLATOR

INPUT

FILTERS

I C-BUS

CONTROLLER

2

POWER-

ON

RESET

CLK

4

SYNC

3

OSC

6

11

SCL

2

SDA

1

SA0

10

DISPLAY

CONTROLLER

COMMAND

DECODER

BACKPLANE

OUTPUTS

13

BP014BP215BP116BP3

INPUT

BANK

SELECTOR

DISPLAY

RAM

24 × 4 BITS

OUTPUT

BANK

SELECTOR

DATA

POINTER

SUBADDRESS

COUNTER

DISPLAY SEGMENT OUTPUTS

DISPLAY LATCH

SHIFT REGISTER

17 to 40

S0 to S23

A07A18A2

9

PCF8566

LCD BIAS

GENERATOR

V

SS

V

LCD

V

DD

R

R

R

Fig.1 Block diagram.

1998 May 04 5

Philips Semiconductors Product specification

Universal LCD driver for low multiplex

rates

PCF8566

5 PINNING

SYMBOL PIN DESCRIPTION

SDA 1 I

2

C-bus data input/output

SCL 2 I

2

C-bus clock input/output

SYNC 3 cascade synchronization

input/output

CLK 4 external clock input/output

V

DD

5 positive supply voltage

OSC 6 oscillator input

A0 7

I

2

C-bus subaddress inputsA1 8

A2 9

SA0 10 I

2

C-bus slave address bit 0 input

V

SS

11 logic ground

V

LCD

12 LCD supply voltage

BP0 13

LCD backplane outputs

BP2 14

BP1 15

BP3 16

S0 to S23 17 to 40 LCD segment outputs

Fig.2 Pin configuration.

handbook, halfpage

PCF8566

MGG382

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

S23

S22

S21

S20

S19

S18

S17

S16

S15

S14

S13

S12

S11

S10

S9

S8

S7

S6

S5

S4

SDA

SCL

SYNC

CLK

V

DD

OSC

A0

A1

A2

SA0

V

SS

V

LCD

BP0

BP2

BP1

BP3

S0

S1

S2

S3

1998 May 04 6

Philips Semiconductors Product specification

Universal LCD driver for low multiplex

rates

PCF8566

6 FUNCTIONAL DESCRIPTION

The PCF8566 is a versatile peripheral device designed to

interface any microprocessor to a wide variety of LCDs.

It can directly drive any static or multiplexed LCD

containing up to 4 backplanes and up to 24 segments.

The display configurations possible with the PCF8566

depend on the number of active backplane outputs

required; a selection of display configurations is given in

Table 1.

All of the display configurations given in Table 1 can be

implemented in the typical system shown in Fig.3.

The host microprocessor/microcontroller maintains the

two-line I

2

C-bus communication channel with the

PCF8566. The internal oscillator is selected by tying OSC

(pin 6) to VSS. The appropriate biasing voltages for the

multiplexed LCD waveforms are generated internally.

The only other connections required to complete the

system are to the power supplies (VDD, VSSand V

LCD

) and

to the LCD panel chosen for the application.

Table 1 Selection of display configurations

ACTIVE

BACKPLANE

OUTPUTS

NUMBER OF

SEGMENTS

7-SEGMENT NUMERIC

14-SEGMENT

ALPHANUMERIC

DOT MATRIX

4 96 12 digits + 12 indicator

symbols

6 characters + 12 indicator

symbols

96 dots (4 × 24)

3 72 9 digits + 9 indicator

symbols

4 characters + 16 indicator

symbols

72 dots (3 × 24)

2 48 6 digits + 6 indicator

symbols

3 characters + 6 indicator

symbols

48 dots (2 × 24)

1 24 3 digits + 3 indicator

symbols

1 character + 10 indicator

symbols

24 dots

Fig.3 Typical system configuration.

handbook, full pagewidth

HOST

MICRO-

PROCESSOR/

MICRO-

CONTROLLER

SDA

SCL

OSC

1 17 to 40

13 to 16

2

6

78

512

91011

24 segment drives

4 backplanes

LCD PANEL

(up to 96

elements)

PCF8566

A0 A1 A2 SA0

V

DD

V

DD

V

LCD

V

SS

V

SS

MGG385

R ≤

t

rise

2 C

bus

1998 May 04 7

Philips Semiconductors Product specification

Universal LCD driver for low multiplex

rates

PCF8566

6.1 Power-on reset

At power-on the PCF8566 resets to a defined starting

condition as follows:

1. All backplane outputs are set to V

DD

2. All segment outputs are set to V

DD

3. The drive mode ‘1 : 4 multiplex with1⁄3bias’ is selected

4. Blinking is switched off

5. Input and output bank selectors are reset (as defined

in Table 5)

6. The I2C-bus interface is initialized

7. The data pointer and the subaddress counter are

cleared.

Data transfers on the I

2

C-bus should be avoided for 1 ms

following power-on to allow completion of the reset action.

6.2 LCD bias generator

The full-scale LCD voltage (V

op

) is obtained from

VDD− V

LCD

. The LCD voltage may be temperature

compensated externally through the V

LCD

supply to pin 12.

Fractional LCD biasing voltages are obtained from an

internal voltage divider of three series resistors connected

between VDD and V

LCD

. The centre resistor can be

switched out of circuit to provide a1⁄2bias voltage level for

the 1 : 2 multiplex configuration.

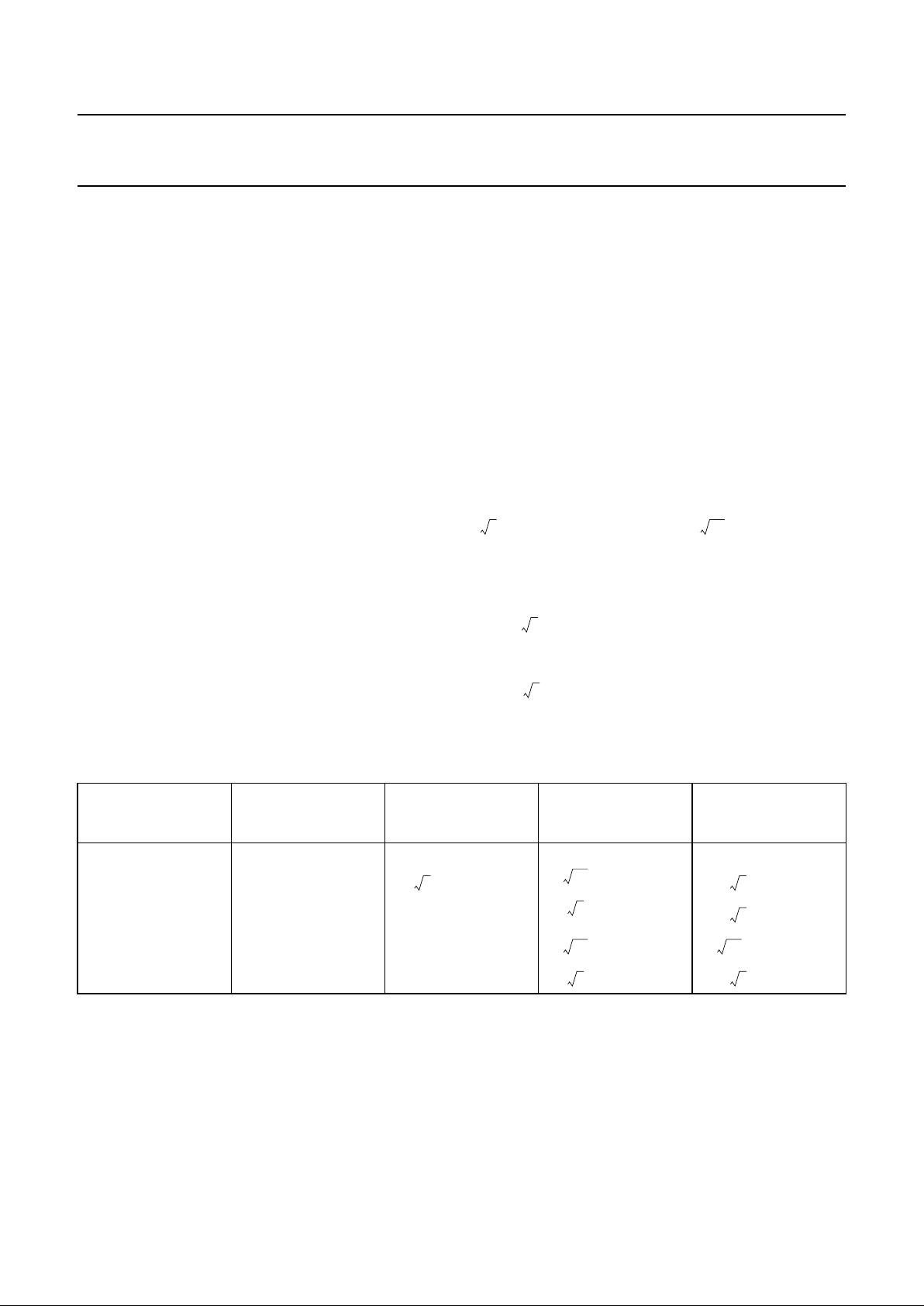

6.3 LCD voltage selector

The LCD voltage selector coordinates the multiplexing of

the LCD according to the selected LCD drive

configuration. The operation of the voltage selector is

controlled by MODE SET commands from the command

decoder. The biasing configurations that apply to the

preferred modes of operation, together with the biasing

characteristics as functions of V

op=VDD

− V

LCD

and the

resulting discrimination ratios (D), are given in Table 2.

A practical value of V

op

is determined by equating V

off(rms)

with a defined LCD threshold voltage (Vth), typically when

the LCD exhibits approximately 10% contrast. In the static

drive mode a suitable choice is V

op

≥ 3Vth. Multiplex drive

ratios of 1 : 3 and 1 : 4 with

1

⁄2bias are possible but the

discrimination and hence the contrast ratios are smaller

( for 1 : 3 multiplex or for

1 : 4 multiplex). The advantage of these modes is a

reduction of the LCD full scale voltage V

op

as follows:

1 : 3 multiplex (

1

⁄2bias):

1 : 4 multiplex (

1

⁄2bias):

These compare with V

op

=3V

off(rms)

when1⁄3bias is used.

3 1.732=

21 3⁄ 1.528=

V

op

6V

op(mrs)

2.449V

off rms()

==

Vop343⁄ V

off rms()

2.309V

off rms()

==

Table 2 Preferred LCD drive modes: summary of characteristics

LCD DRIVE MODE

LCD BIAS

CONFIGURATION

Static (1 BP) static (2 levels) 0 1 ∞

1 : 2 MUX (2 BP)

1

⁄2(3 levels)

1 : 2 MUX (2 BP)

1

⁄3(4 levels)

1

⁄3= 0.333

1 : 3 MUX (3 BP)

1

⁄3(4 levels)

1

⁄3= 0.333

1 : 4 MUX (4 BP)

1

⁄3(4 levels)

1

⁄3= 0.333

V

off rms()

V

op

-----------------------

V

on rms()

V

op

---------------------- -

D

V

on rms()

V

off rms()

-----------------------

=

2 4 0.354=⁄

10 4⁄ 0.791=

52.236=

53⁄ 0.745=

52.236=

33 9⁄ 0.638= 33 3⁄ 1.915=

33⁄ 0.577= 31.732=

1998 May 04 8

Philips Semiconductors Product specification

Universal LCD driver for low multiplex

rates

PCF8566

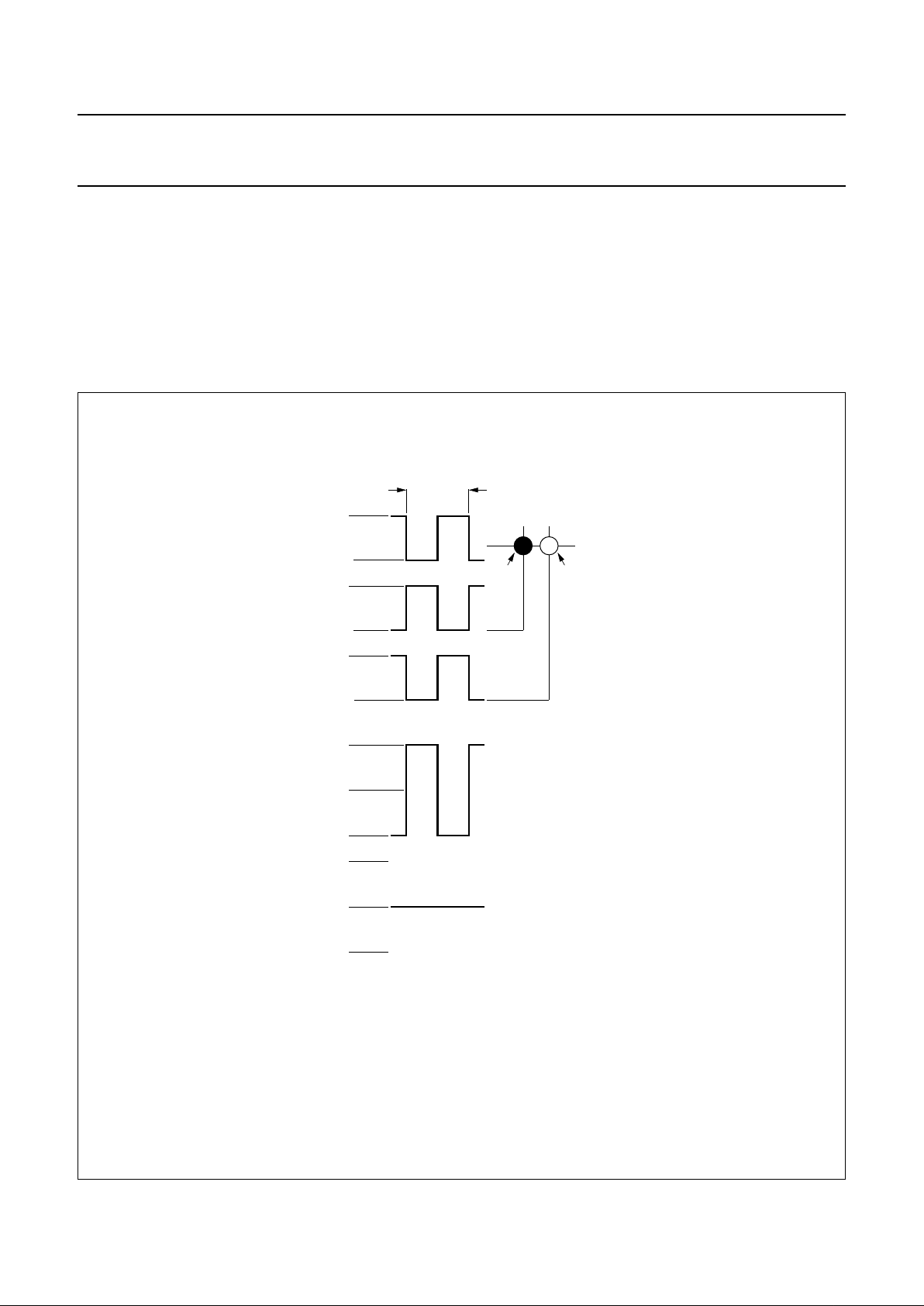

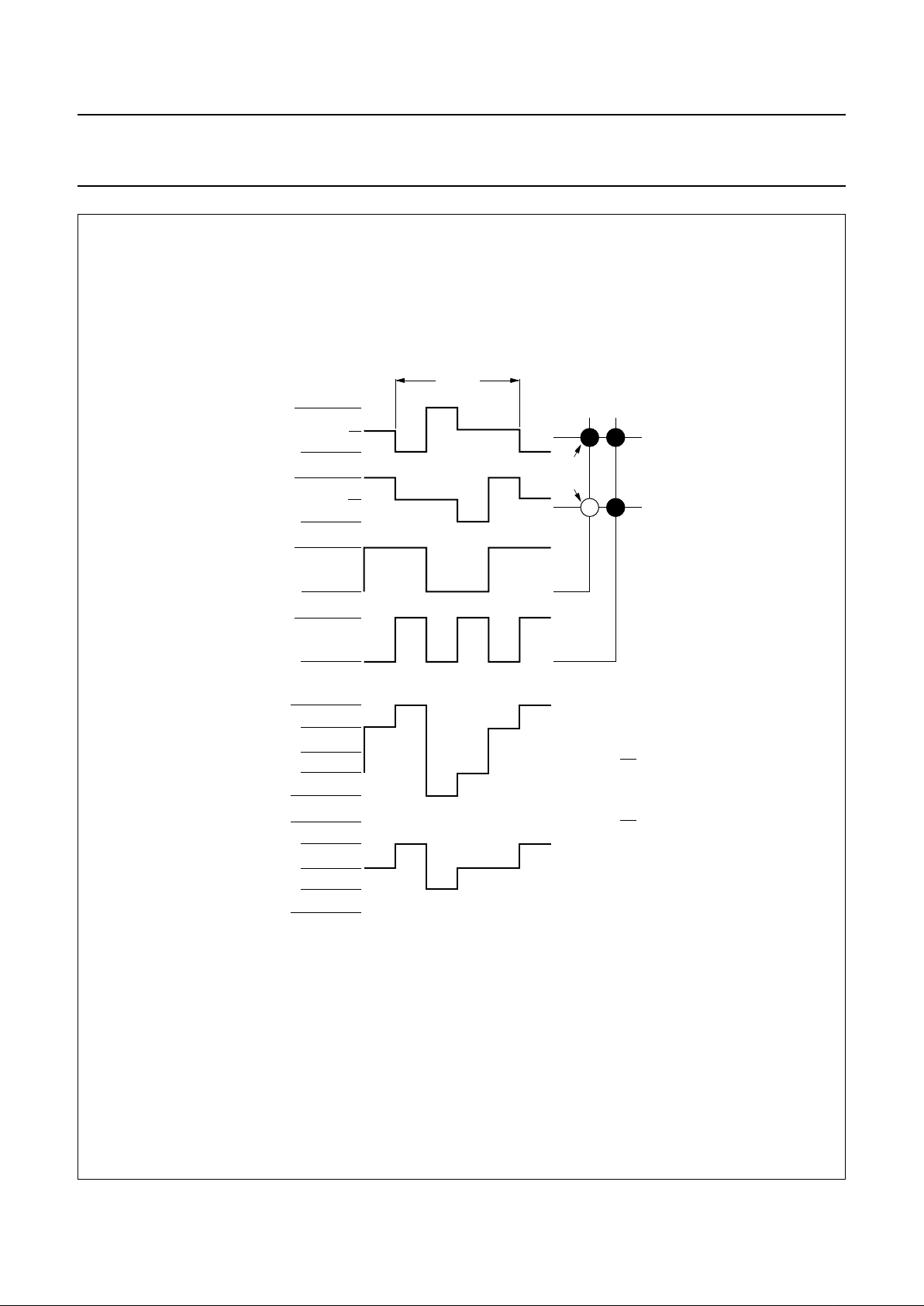

6.4 LCD drive mode waveforms

The static LCD drive mode is used when a single backplane is provided in the LCD. Backplane and segment drive

waveforms for this mode are shown in Fig.4.

When two backplanes are provided in the LCD the 1 : 2 multiplex drive mode applies. The PCF8566 allows use of

1

⁄2or1⁄3bias in this mode as shown in Figs 5 and 6.

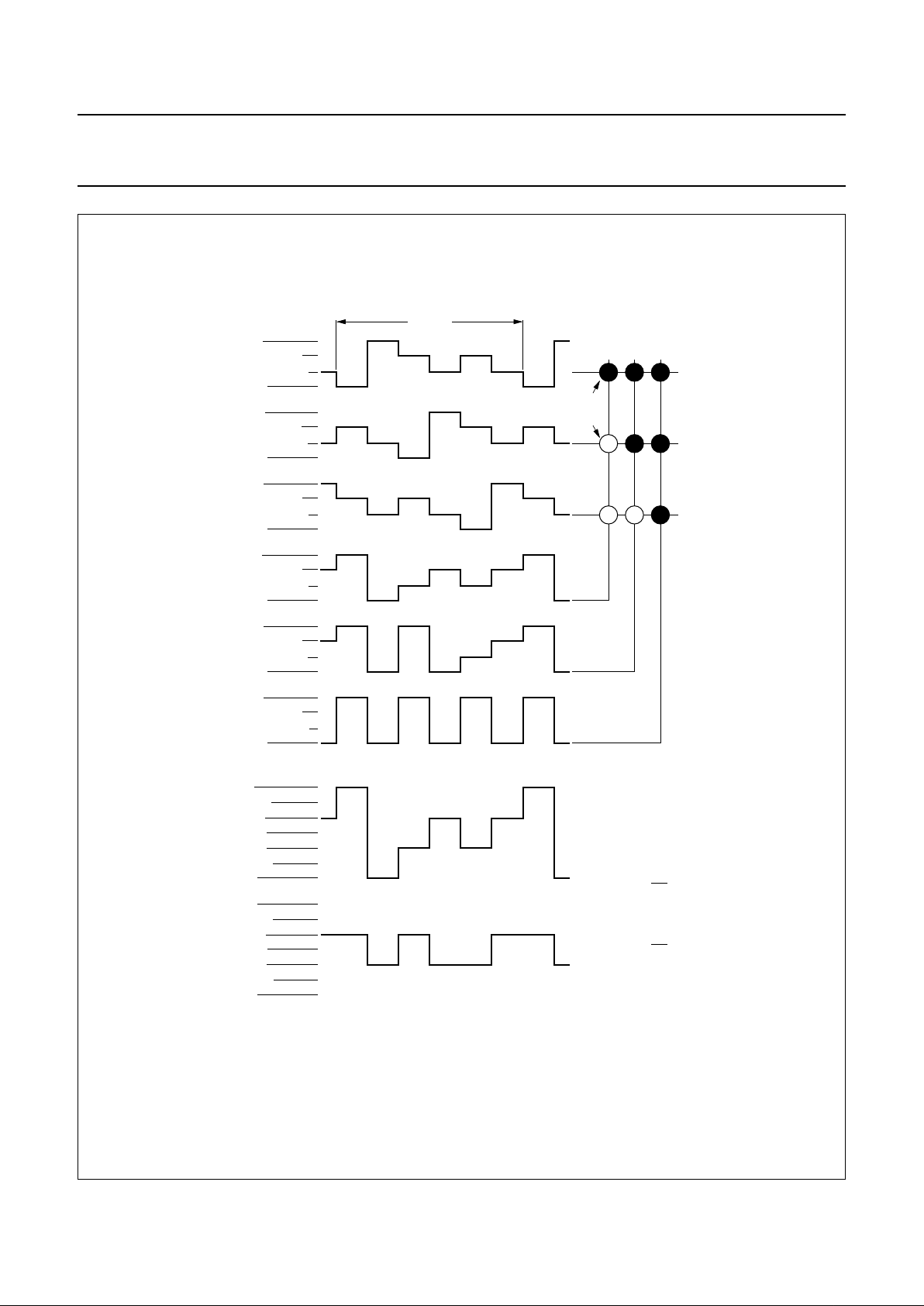

The backplane and segment drive waveforms for the 1 : 3 multiplex drive mode (three LCD backplanes) and for the 1 : 4

multiplex drive mode (four LCD backplanes) are shown in Figs 7 and 8 respectively.

Fig.4 Static drive mode waveforms: Vop=VDD− V

LCD

.

handbook, full pagewidth

MGG392

state 1

At any instant (t):

V

state 1

(t) = V

S

n

(t) − V

BP0

(t)

V

on(rms)

= V

op

V

state 2

(t) = V

S

n + 1

(t) − V

BP0

(t)

V

off(rms)

= 0 V

0

BP0

state 2 0

(a) waveforms at driver

(b) resultant waveforms

at LCD segment

LCD segments

state 1

(on)

state 2

(off)

V

DD

V

LCD

V

DD

V

LCD

V

DD

V

LCD

V

op

−V

op

V

op

−V

op

T

frame

S

n

S

n + 1

1998 May 04 9

Philips Semiconductors Product specification

Universal LCD driver for low multiplex

rates

PCF8566

Fig.5 Waveforms for 1 : 2 multiplex drive mode with1⁄2bias: Vop=VDD− V

LCD

.

handbook, full pagewidth

MGG394

state 1

BP0

S

n + 1

(a) waveforms at driver

(b) resultant waveforms

at LCD segment

LCD segments

state 2

BP1

S

n

state 2

state 1

V

DD

(V

DD

+ V

LCD

)/2

V

LCD

V

DD

(V

DD

+ V

LCD

)/2

V

LCD

V

DD

V

LCD

V

DD

V

LCD

V

op

Vop/2

0

−Vop/2

−V

op

V

op

Vop/2

0

−Vop/2

−V

op

T

frame

At any instant (t):

V

state 1

(t) = V

S

n

(t) − V

BP0

(t)

V

on(rms)

=

V

op

√10 = 0.791V

op

4

V

state 2

(t) = V

S

n

(t) − V

BP1

(t)

V

off(rms)

=

V

op

√2 = 0.354V

op

4

1998 May 04 10

Philips Semiconductors Product specification

Universal LCD driver for low multiplex

rates

PCF8566

Fig.6 Waveforms for 1 : 2 multiplex drive mode with1⁄3bias: Vop=VDD− V

LCD

.

andbook, full pagewidth

MGG393

state 1 0

BP0

(a) waveforms at driver

(b) resultant waveforms

at LCD segment

LCD segments

state 2

BP1

state 1

state 2 0

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

op

−V

op

2Vop/3

−2Vop/3

Vop/3

−Vop/3

V

op

−V

op

2Vop/3

−2Vop/3

Vop/3

−Vop/3

S

n + 1

S

n

T

frame

At any instant (t):

V

state 1

(t) = V

S

n

(t) − V

BP0

(t)

V

on(rms)

=

V

op

√5 = 0.745V

op

3

V

state 2

(t) = V

S

n

(t) − V

BP1

(t)

V

off(rms)

=

V

op

= 0.333V

op

3

1998 May 04 11

Philips Semiconductors Product specification

Universal LCD driver for low multiplex

rates

PCF8566

Fig.7 Waveforms for 1 : 3 multiplex drive mode: Vop=VDD− V

LCD

.

handbook, full pagewidth

MGG395

state 1 0

BP0

(b) resultant waveforms

at LCD segment

LCD segments

state 2

BP1

state 1

state 2 0

(a) waveforms at driver

BP2

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

op

−V

op

2Vop/3

−2Vop/3

Vop/3

−Vop/3

V

op

−V

op

2Vop/3

−2Vop/3

Vop/3

−Vop/3

S

n

S

n + 1

S

n + 2

T

frame

At any instant (t):

V

state 1

(t) = V

S

n

(t) − V

BP0

(t)

V

on(rms)

=

V

op

√33 = 0.638V

op

9

V

state 2

(t) = V

S

n

(t) − V

BP1

(t)

V

off(rms)

=

V

op

= 0.333V

op

3

1998 May 04 12

Philips Semiconductors Product specification

Universal LCD driver for low multiplex

rates

PCF8566

Fig.8 Waveforms for 1 : 4 multiplex drive mode: Vop=VDD− V

LCD.

handbook, full pagewidth

MGG396

state 1 0

BP0

(b) resultant waveforms

at LCD segment

LCD segments

state 2

BP1

state 1

state 2 0

BP2

(a) waveforms at driver

BP3

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

DD

V

DD

− Vop/3

V

DD

− 2Vop/3

V

LCD

V

op

−V

op

2Vop/3

−2Vop/3

Vop/3

−Vop/3

V

op

−V

op

2Vop/3

−2Vop/3

Vop/3

−Vop/3

S

n

S

n + 1

Sn + 2

S

n + 3

T

frame

At any instant (t):

V

state 1

(t) = V

S

n

(t) − V

BP0

(t)

V

on(rms)

=

V

op

√3 = 0.577V

op

3

V

state 2

(t) = V

S

n

(t) − V

BP1

(t)

V

off(rms)

=

V

op

= 0.333V

op

3

Loading...

Loading...