Philips PCA9544 Datasheet

INTEGRATED CIRCUITS

PCA9544

2

4-channel I

C multiplexer and interrupt

controller

Product specification

Supersedes data of 1999 Apr 01

1999 Oct 07

Philips Semiconductors Product specification

PCA95444-channel I2C multiplexer and interrupt controller

FEA TURES

•1-of-4 bi-directional translating multiplexer

•Channel selection via I

2

C bus

•Operating supply voltage 2.5 to 3.6 V

•Operating temperature range 0°C to 70°C

•Power-up with all multiplexer channels deselected

•3 address pins, allowing up to 8 devices on the I

2

C bus

•Low on resistance

DESCRIPTION

The PCA9544 is a 1-of-4 bi-directional translating multiplexer,

controlled via the I

four SCx/SDx downstream pairs, or channels. Only one SCx/SDx

channel is selected at a time, determined by the contents of the

programmable control register . Four interrupt inputs, one for each of

the SCx/SDx downstream pair, are provided. One interrupt output,

which acts as an AND of the four interrupt inputs, is provided. All I/O

pins are 5 V tolerant.

The pass gates of the multiplexer are constructed such that the V

pin can be used to limit the maximum high voltage which will be

passed by the PCA9544. This allows the use of different bus

voltages on each SCx/SDx pair, so that 3.3 V parts can

communicate with 5 V parts without any additional protection.

External pull-up resistors can pull the bus up to the desired voltage

level for this channel.

2

C bus. The SCL/SDA upstream pair fans out to

DD

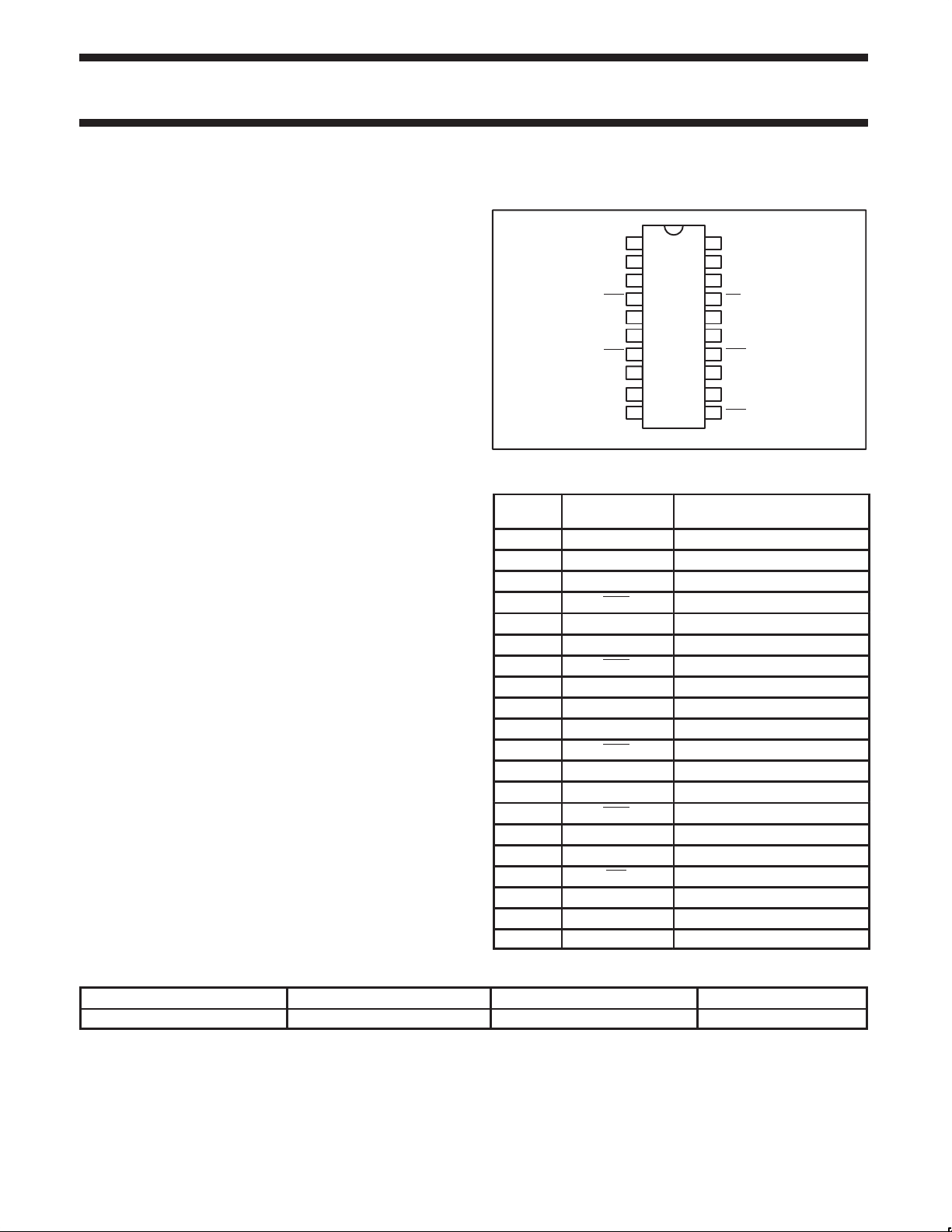

PIN CONFIGURATION

A0

1

2

A1

3

A2

4

INT0

5

SD0

6

SC0

INT1

7

8

SD1

SC1

9

10

VSS

PIN DESCRIPTION

PIN

NUMBER

1 A0 Address input 0

2 A1 Address input 1

3 A2 Address input 2

4 INT0 Interrupt input 0

5 SD0 Serial data 0

6 SC0 Serial clock 0

7 INT1 Interrupt input 1

8 SD1 Serial data 1

9 SC1 Serial clock 1

10 VSS Supply ground

11 INT2 Interrupt input 2

12 SD2 Serial data 2

13 SC2 Serial clock 2

14 INT3 Interrupt input 3

15 SD3 Serial data 3

16 SC3 Serial clock 3

17 INT Interrupt output

18 SCL Serial clock line

19 SDA Serial data line

20 V

SYMBOL FUNCTION

DD

Supply voltage

V

20

DD

SDA

19

SCL

18

INT

17

SC3

16

SD3

15

INT3

14

SC2

13

SD2

12

11

INT2

SW00373

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE ORDER CODE DRAWING NUMBER

20-Pin Plastic TSSOP 0°C to +70°C PCA9544 PW DH SOT360-1

1999 Oct 07 853–2178 22487

2

Philips Semiconductors Product specification

PCA95444-channel I2C multiplexer and interrupt controller

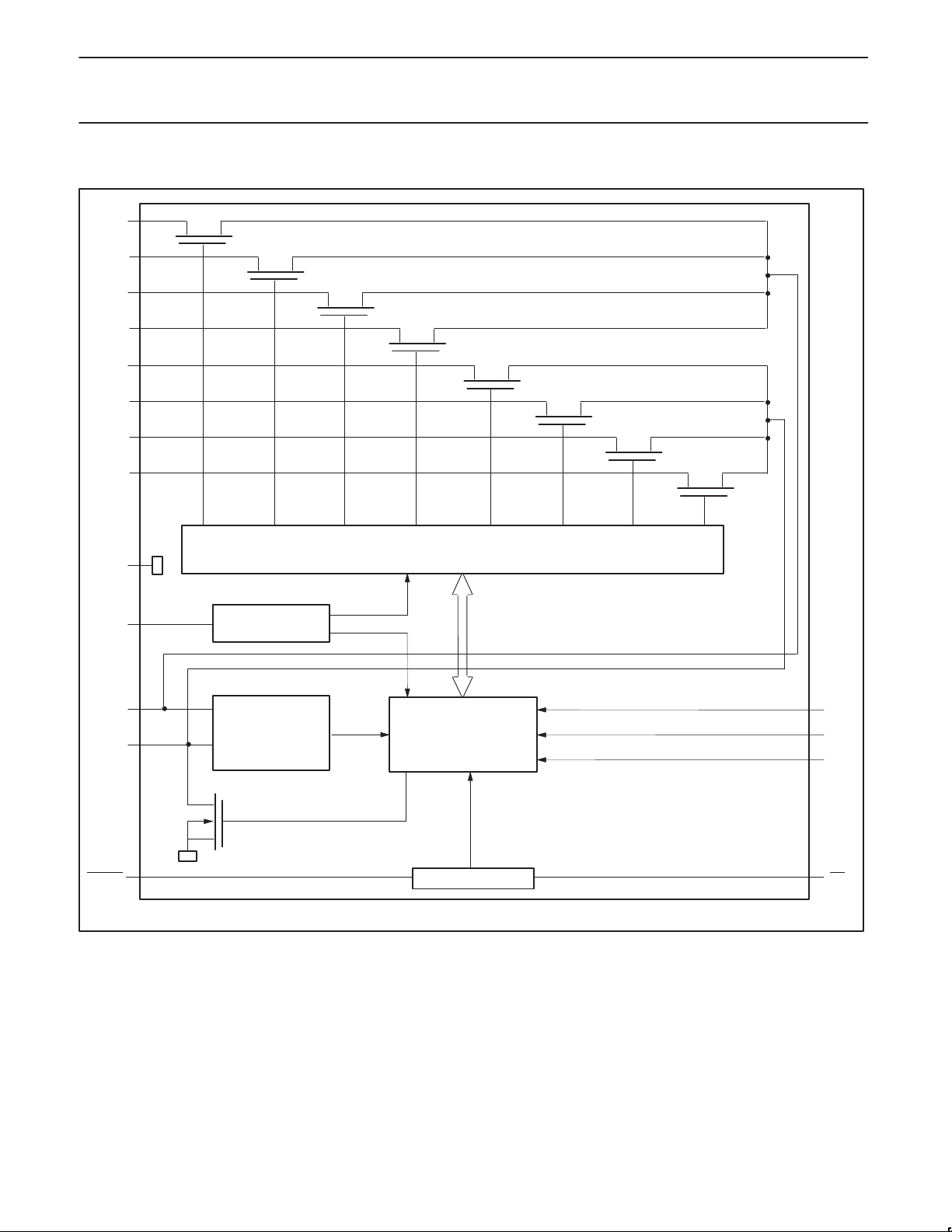

BLOCK DIAGRAM

SC0

SC1

SC2

SC3

SD0

SD1

SD2

SD3

V

SS

V

DD

SCL

SDA

INT[0–3] INT LOGIC INT

POWER-ON

RESET

INPUT

FILTER

2

I

C-BUS

CONTROL

SW00379

A0

A1

A2

1999 Oct 07

3

Philips Semiconductors Product specification

PCA95444-channel I2C multiplexer and interrupt controller

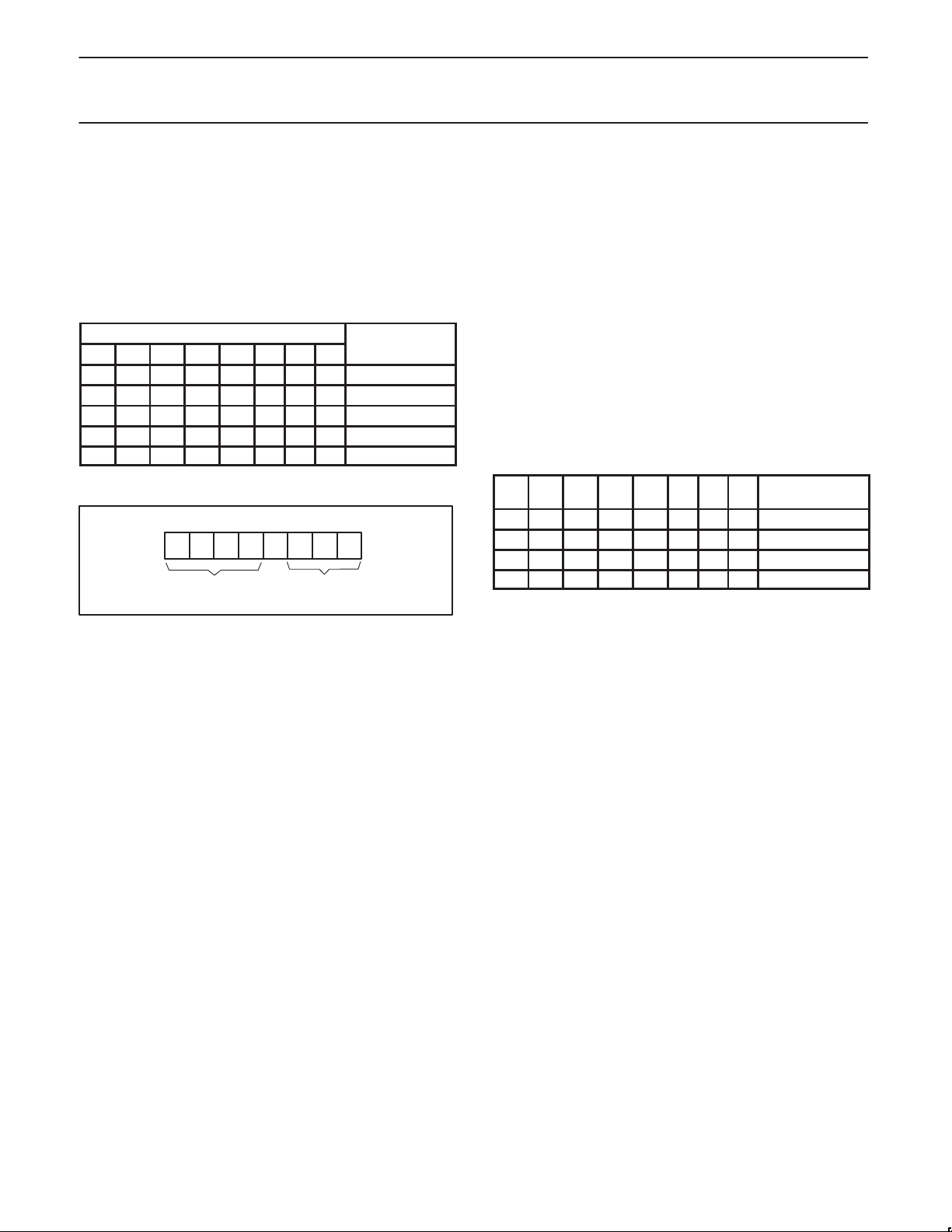

CHANNEL SELECTION

A SC0x/SD0x downstream pair, or channel, is selected by the

contents of the control register. This register is written after the

PCA9544 has been addressed. The 3 LSBs of the control byte are

used to determine which channel is to be selected. When a channel

is selected, the channel will become active after a stop condition has

been placed on the I

2

C bus. This ensures that all SCx/SDx lines will

be in a HIGH state when the channel is made active, so that no

false conditions are generated at the time of connection.

CONTROL BYTE

7 6 5 4 3 2 1 0

SELECTED

CHANNEL

X X X X X 0 X X none

X X X X X 1 0 0 0 (SC0/SD0)

X X X X X 1 0 1 1 (SC1/SD1)

X X X X X 1 1 0 2 (SC2/SD2)

X X X X X 1 1 1 3 (SC3/SD3)

CONTROL REGISTER

6 5 4 2 1 0 7 3

INT2 INT1 INT0 B2 B1 B0

INT3

Interrupt bits

(read only) (read/write)

X

Channel select bits

SW00386

INTERRUPT HANDLING

The PCA9544 provides 4 interrupt inputs, one for each channel and

one open drain interrupt output. When an interrupt is generated by any

device, it will be detected by the PCA9544 and the interrupt output

will be driven LOW. The channel need not be active for detection of

the interrupt. A bit is also set in the control byte. Bits 4 – 7 of the

control byte correspond to channels 0 – 3 of the PCA9544,

respectively. Therefore, if an interrupt is generated by any device

connected to channel 2, then bit 6 will be set in the control register.

Likewise, an interrupt on any device connected to channel 3 would

cause bit 7 of the control register to be set. The master can then

address the PCA 9544 and read the contents of the control byte to

determine which channel contains the device generating the interrupt.

The master can then reconfigure the PCA9544 to select this

channel, and locate the device generating the interrupt and clear it.

The interrupt clears when the device originating the interrupt clears.

It should be noted that more than one device can be providing an

interrupt on a channel, so it is up to the master to ensure that all

devices on a channel are interrogated for an interrupt.

7

6 5 4 3 2 1 0

0 0 0 1 X X X X 0 (SC0/SD0)

0 0 1 0 X X X X 1 (SC1/SD1)

0 1 0 0 X X X X 2 (SC2/SD2)

1 0 0 0 X X X X 3 (SC3/SD3)

INTERRUPTING

CHANNEL

POWER-ON RESET

During power-up, the control register defaults to all zeroes causing

all the channels to be deselected.

1999 Oct 07

4

Loading...

Loading...