Philips N74F776A, N74F776N, N74F776F Datasheet

74F776

Pi-bus transceiver

Product specification

IC15 Data Handbook

1990 Dec 19

INTEGRATED CIRCUITS

Philips Semiconductors Product specification

74F776Pi–bus transceiver

2

December 19, 1990 853 1121 01321

FEA TURES

• Octal latched transceiver

• Drives heavily loaded backplanes with equivalent load impedances

down to 10 ohms

• High drive (100mA) open collector drivers on B port

• Reduced voltage swing (1 volt) produces less noise and reduces

power consumption

• High speed operation enhances performance of backplane buses

and facilitates incident wave switching

• Compatible with Pi–bus and IEEE 896 Futurebus standards

• Built–in precision band–gap reference provides accurate receiver

thresholds and improved noise immunity

• Controlled output ramp and multiple GND pins minimize ground

bounce

• Glitch–free power up/power down operation

• Multiple package options

• Industrial temperature range available (–40°C to +85°C)

DESCRIPTION

The 74F776 is an octal bidirectional latched transceiver and is

intended to provide the electrical interface to a high performance

wired–OR bus. The B port inverting drivers are low–capacitance open

collector with controlled ramp and are designed to sink 100mA from 2

volts. The B port inverting receivers have a 100 mV threshold region

and a 4ns glitch filter.

The 74F776 B port interfaces to ’Backplane Transceiver Logic’ (BTL).

BTL features a reduced (1V to 2V) voltage swing for lower power

consumption and a series diode on the drivers to reduce capacitive

loading. Incident wave switching is employed, therefore BTL

propagation delays are short. Although the voltage swing is less for

BTL, so is its receiver threshold, therefore noise margins are excellent.

BTL offers low power consumption, low ground bounce, EMI and

crosstalk, low capacitive loading, superior noise margin and low

propagation delays. This results in a high bandwidth, reliable

backplane.

The 74F776 A port has TTL 3–state drivers and TTL receivers with a

latch function. A separate high–level control voltage input (V

X

) is

provided to limit the A side output level to a given voltage level (such

as 3.3V). For 5.0V systems, V

X

is simply tied to VCC.

The 74F776 has a designed feature to control the B output transitions

during power sequencing. There are two possible sequencing, They

are as follows:

1.When LE

= low and OEBn = low then the B outputs are disabled until

the LE

circuitry takes control. Then the B outputs will follow the A inputs,

making a maximum of one transition during power–up (or down).

2. If LE = high or OEBn = high then the B outputs will be disabled during

power–up (or down).

TYPE

TYPICAL PROPAGA-

TION DELAY

TYPICAL SUPPL Y

CURRENT( TOTAL)

74F776 6.5ns 80mA

ORDERING INFORMATION

ORDER CODE

COMMERCIAL RANGE INDUSTRIAL RANGE

DESCRIPTION

VCC = 5V ±10%, T

amb

= 0°C to +70°C VCC = 5V ±10%, T

amb

= –40°C to +85°C

PKG DWG #

28–pin plastic DIP (600 mil) N74F776N I74F776N SOT117-2

28–pin PLCC N74F776A I74F776A SOT261-2

INPUT AND OUTPUT LOADING AND FAN OUT TABLE

PINS DESCRIPTION

74F (U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

A0 – A7 PNP latched inputs 3.5/0.1 17 70µA/70µA

B0 – B7 Data inputs with threshold circuitry 5.0/0.167 100µA/100µA

OEA A output enable input (active high) 1.0/0.033 20µA/20µA

OEB0, OEB1 B output enable inputs (active low) 1.0/0.033 20µA/20µA

LE Latch enable input (active low) 1.0/0.033 20µA/20µA

A0 – A7 3–state outputs 150/40 3mA/24mA

B0 – B7 Open collector outputs OC/166.7 OC/100mA

Notes to input and output loading and fan out table

One (1.0) FAST unit load is defined as: 20µA in the high state and 0.6mA in the low state.

OC = Open collector.

Philips Semiconductors Product specification

74F776Pi–bus transceiver

December 19, 1990

3

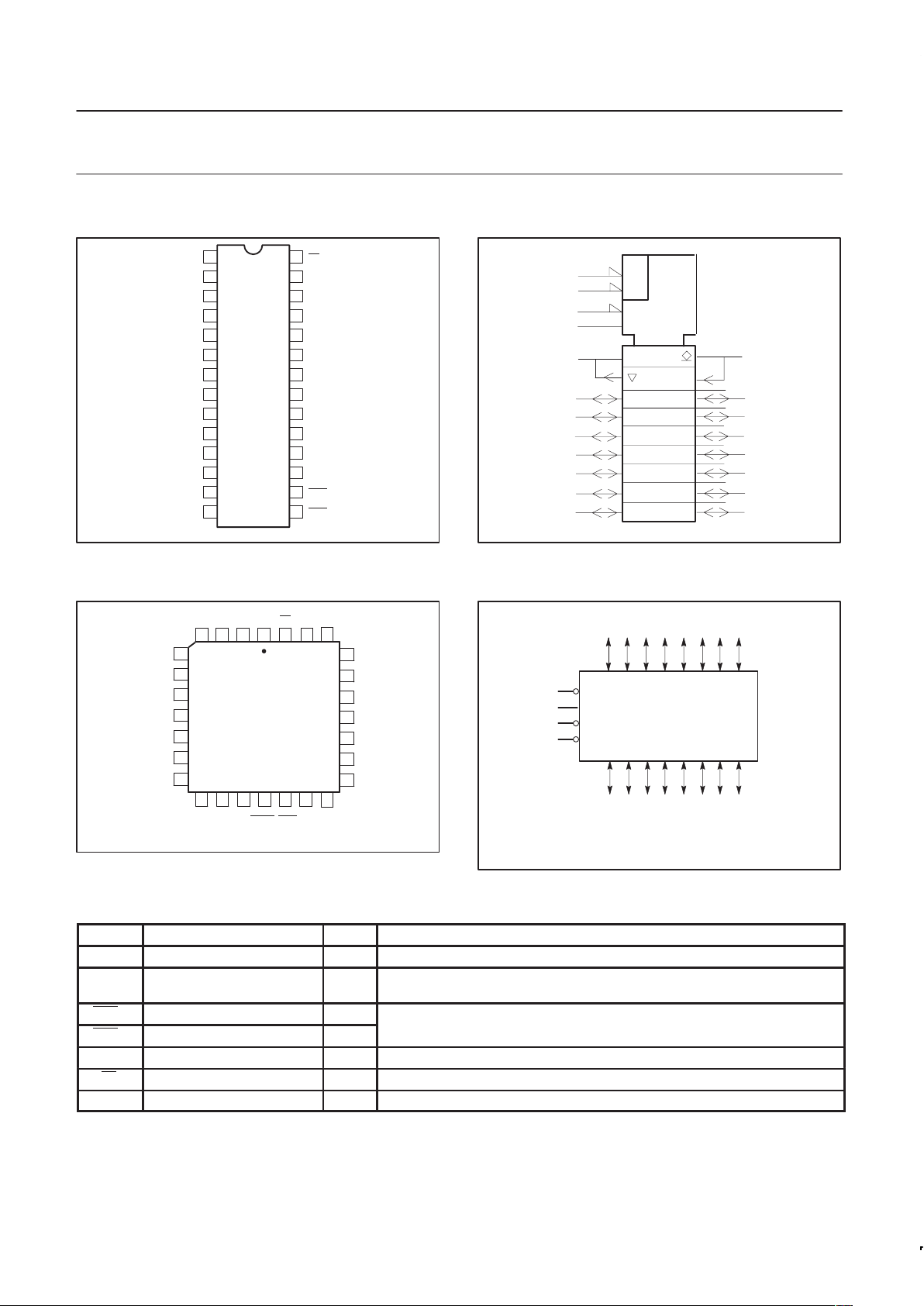

PIN CONFIGURATION

1

2

3

4

5

6

7

8

9

10 19

20

21

22

23

24

25

26

27

28

V

CC

11

12

13

14 15

16

17

18

LE

B0

B1

GND

B2

B3

GND

B4

B5

B6

GND

B7

OEB

1

OEB

0

OEA

A0

GND

A1

A2

A3

GND

A4

A5

GND

A6

A7

VX

SF00422

PIN CONFIGURA TION PLCC

4 3 2 1 28 27

25

24

23

22

21

20

11

10

9

8

7

6

18

16 17151413

26

19

12

5

PLCC

A1

A2

A3

GND

A4

A5

GND

V

CC

OEAA0GND LE B0 B1

GNDOEB0

B7

V

X

A7A6 OEB1

GND

B2

B3

GND

B4

B5

B6

SF00423

IEC/IEEE SYMBOL

2

3

&

EN2

EN1

EN3

ID

27

26

24

23

21

20

19

17

5

6

7

9

10

12

13

3

15

16

28

2

SF00424

LOGIC SYMBOL

VCC = Pin 1, V

X

= Pin 14

GND = Pin 4, 8, 11, 18, 22, 25

15

2

28

16

OEB0

OEA

LE

OEB1

B0 B1 B2 B3 B4 B5 B6 B7

27 26 24 23 21 20 19 17

35679101213

A0 A1 A2 A3 A4 A5 A6 A7

SF00425

PIN DESCRIPTION

SYMBOL PINS TYPE NAME AND FUNCTION

A0 – A7 3, 5, 6, 7, 9, 10, 12, 13 I/O PNP latched input/3–state output (with VX control option)

B0 – B7 27, 26, 24, 23, 21, 20, 19, 17 I/O

Data input with special threshold circuitry to reject noise/ open collector output, high

current drive

OEB0 15 Input Enables the B outputs when both pins are low

OEB1 16 Input

OEA 2 Input Enables the A outputs when high

LE 28 Input Latched when high (a special feature is built in for proper enabling times)

V

X

14 Input Clamping voltage keeping VOH from rising above VX (VX = Vcc for normal use)

Philips Semiconductors Product specification

74F776Pi–bus transceiver

December 19, 1990

4

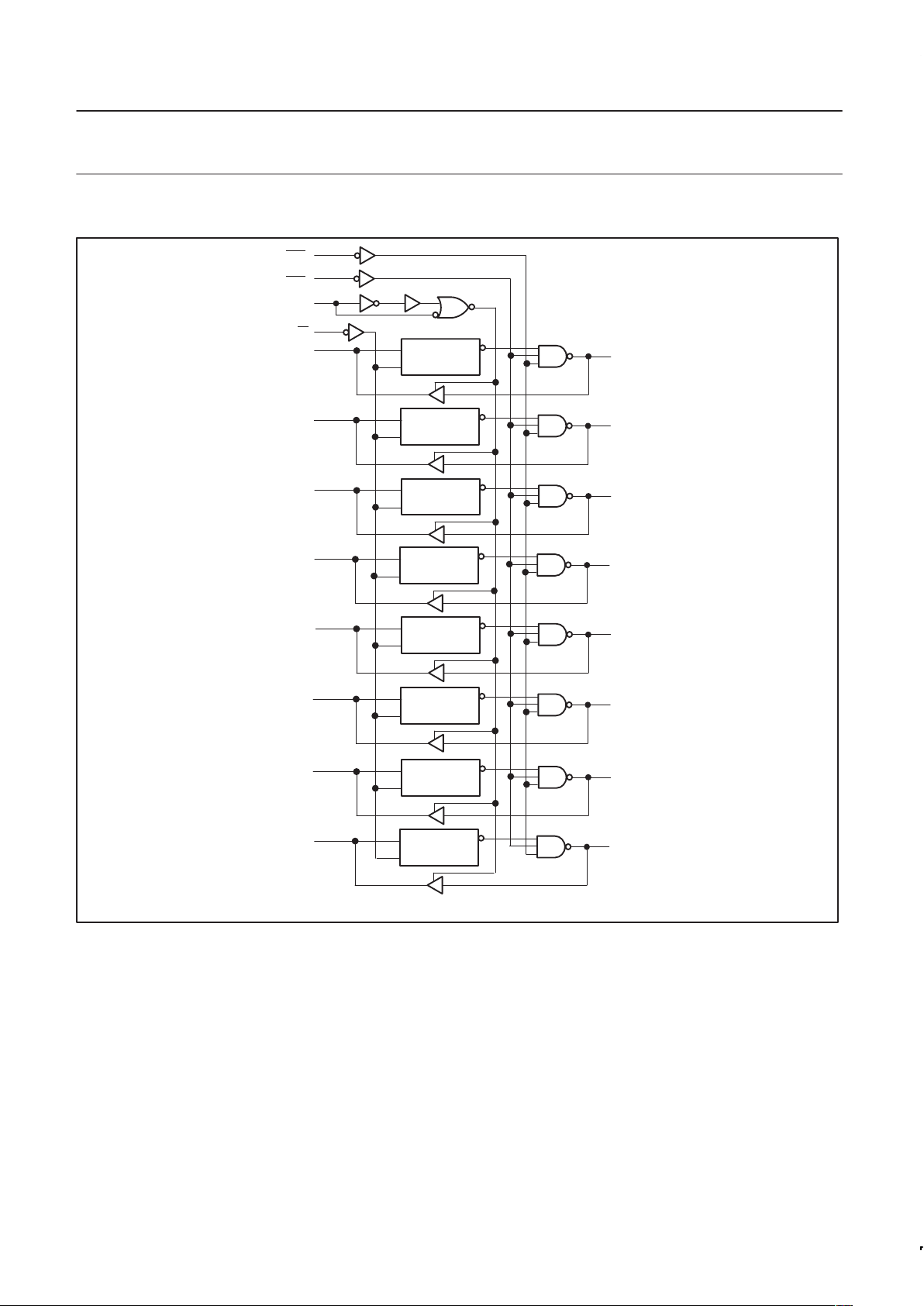

LOGIC DIAGRAM

LE

B0

OEB0

Data

Q

27

3

LE

OEA

V

CC

= Pin 1, V

X

= Pin 14,

GND = Pin 4, 8, 11, 18, 22, 25

A0

LE

B1

Data

Q

26

5

A1

LE

B2

Data

Q

24

6

A2

LE

B3

Data

Q

23

7

A3

LE

B4

Data

Q

21

9

A4

LE

B5

Data

Q

20

10

A5

LE

B6

Data

Q

19

12

A6

LE

B7

Data

Q

17

13

A7

28

2

16

15

OEB

1

SF00426

Loading...

Loading...