Philips N74ALS245A-1D, N74ALS245A-1DB, N74ALS245A-1N, N74ALS245AD, N74ALS245ADB Datasheet

...

74ALS245A/74ALS245A–1

Octal transceiver (3–State)

Product specification

IC05 Data Handbook

1991 Jun 03

INTEGRATED CIRCUITS

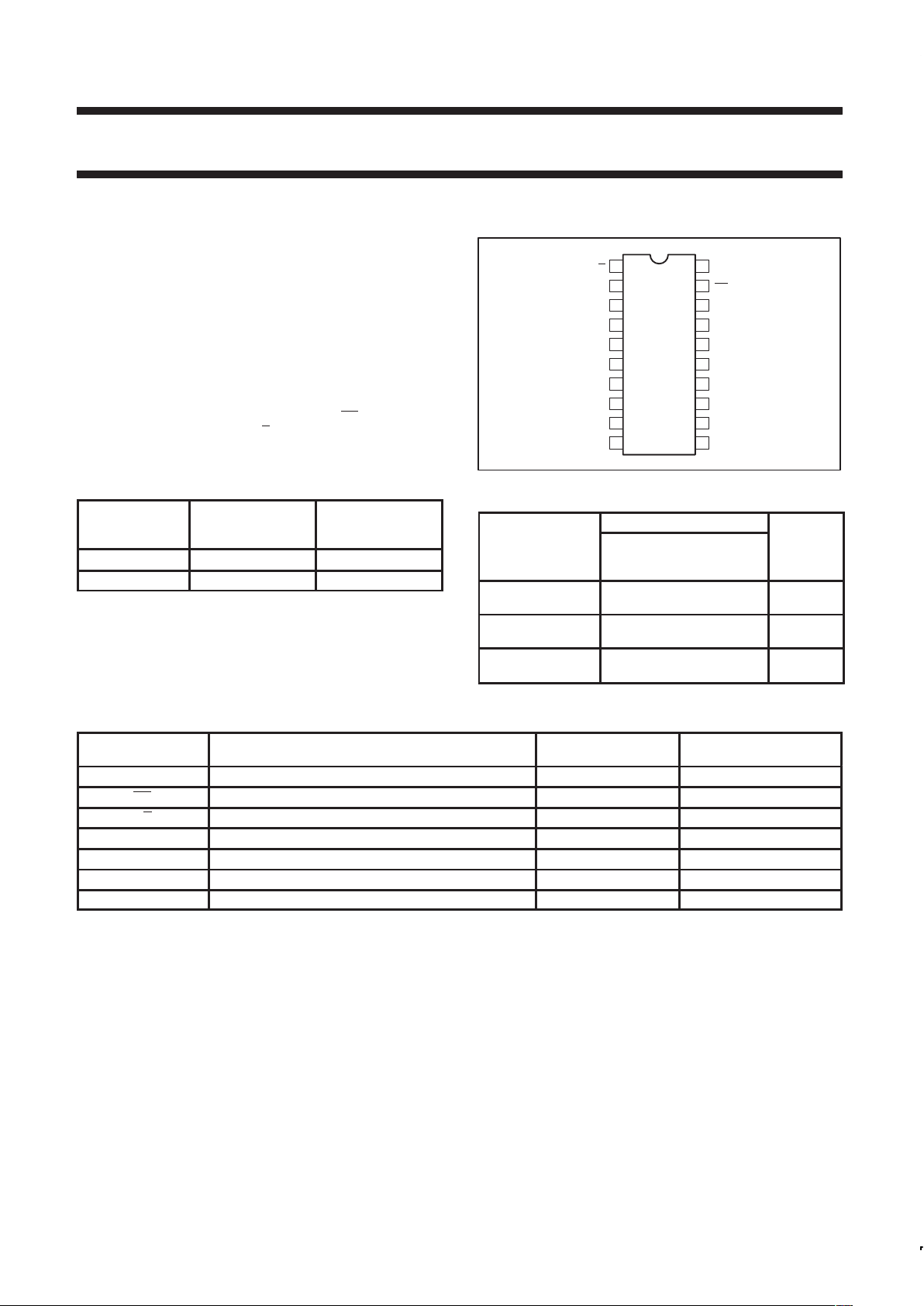

Philips Semiconductors Product specification

74ALS245A/74ALS245A-1Octal transceiver (3-State)

2

1991 Jun 03 853–001 1 02709

FEA TURES

•Octal bidirectional bus interface

•3-State buffer outputs sink 24mA and source 15mA

•Outputs are placed in high impedance state during power-off

conditions

•The -1 version sinks 48mA

DESCRIPTION

The 74ALS245A is an octal transceiver featuring non-inverting

3-State bus compatible outputs in both transmit and receive

directions. The device features an output enable (OE

) input for easy

cascading and transmit/receive (R/T

) input for direction control.

The 74ALS245A-1 is the same as the 74ALS245A except that both

ports sink 48mA within the ±5% V

CC

range.

TYPE

TYPICAL

PROPAGATION

DELA Y

TYPICAL

SUPPLY CURRENT

(TOTAL)

74ALS245A 7.0ns 34mA

74ALS245A-1 7.0ns 34mA

PIN CONFIGURATION

SF00198

1

2

3

4

5

6

7

8

9

10 11

12

13

14

15

16

17

18

19

20

T/R

A0

A1

A2

A3

A4

A5

A6

A7

GND

V

CC

OE

B0

B1

B2

B3

B4

B6

B5

B7

ORDERING INFORMA TION

ORDER CODE

DESCRIPTION

COMMERCIAL RANGE

V

CC

= 5V ±10%,

T

amb

= 0°C to +70°C

DRAWING

NUMBER

20-pin plastic DIP

74ALS245AN,

74ALS245A-1N

SOT146-1

20-pin plastic SOL

74ALS245AD,

744ALS245A-1D

SOT163-1

20-pin plastic SSOP

Type II

74ALS245ADB,

74ALS245A-1DB

SOT339-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74ALS (U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

A0 – A7, B0 – B7 Data inputs 1.0/1.0 20µA/0.1mA

OE Output Enable input (active-Low) 1.0/1.0 20µA/0.1mA

T/R T ransmit/receive input 1.0/1.0 20µA/0.1mA

A0 – A7 A port outputs 750/240 15mA/24mA

B0 – B7 B port outputs 750/240 15mA/24mA

A0 – A7 A port outputs (-1 version) 750/480 15mA/48mA

B0 – B7 B port outputs (-1 version) 750/480 15mA/48mA

NOTE: One (1.0) ALS unit load is defined as: 20µA in the High state and 0.1mA in the Low state.

Philips Semiconductors Product specification

74ALS245A/74ALS245A-1Octal transceiver (3-State)

1991 Jun 03

3

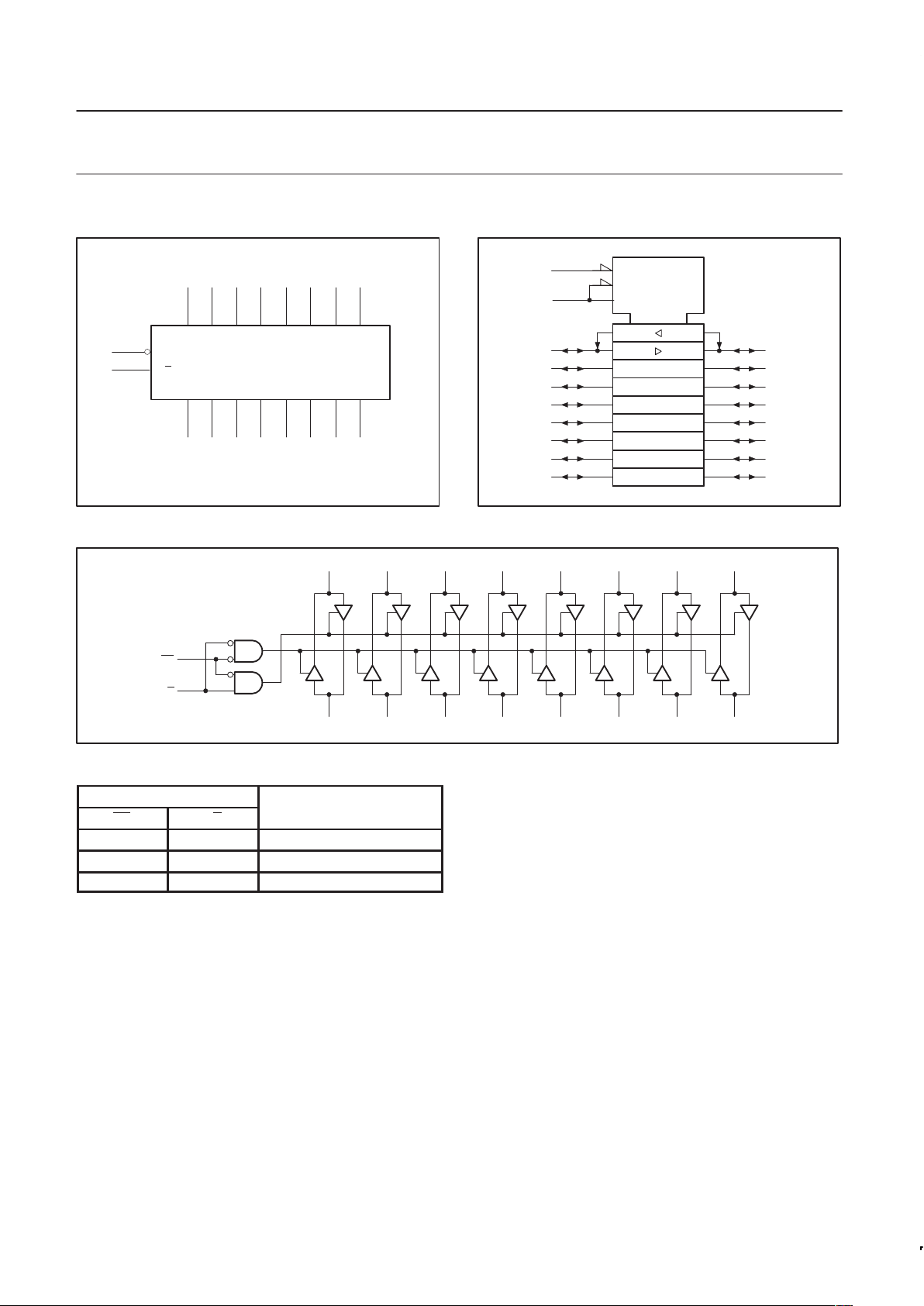

LOGIC SYMBOL

B2 B3 B4 B5

16 15 14 13

234

V

CC

= Pin 20

GND = Pin 10

SF00199

B1

17

B0

18

19

1

OE

T/R

A0 A1 A2 A3 A4 A5

567

B6 B7

12 11

A6 A7

89

IEC/IEEE SYMBOL

SC00097

G3

19

3EN1 [BA]

1

3EN2 [AB]

∇ 1

2 ∇

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

LOGIC DIAGRAM

SF00201

18

B0

17

B1

16

B2

15

B3

14

B4

13

B5

12

B6

11

B7

A0 A1 A2 A3 A4 A5 A6 A7

23456789

19

1

OE

T/R

VCC = Pin 20

GND = Pin 10

FUNCTION TABLE

INPUTS

OE T/R

OUTPUTS

L L Bus B data to Bus A

L H Bus A data to Bus B

H X Z

H = High voltage level

L = Low voltage level

X = Don’t care

Z = High impedance “off” state

Loading...

Loading...