Philips N74ALS175D, N74ALS175N Datasheet

74ALS175

Quad D flip–flop

Product specification

IC05 Data Handbook

1991 Feb 08

INTEGRATED CIRCUITS

Philips Semiconductors Product specification

74ALS175Quad D flip-flop

2

1991 Feb 08 853–1024 01670

FEA TURES

•Four edge-triggered D flip-flops

•Buffered common clock

•Buffered asynchronous master reset

•True and complementary outputs

DESCRIPTION

The 74ALS175 is a quad, edge-triggered D-type flip-flops with

individual D inputs and both Q and Q

outputs. The common buffered

clock (CP) and master reset (MR

) inputs load and reset (clear) all

flip-flops simultaneously.

The register is fully edge-triggered. The state of each D input, one

setup time before the Low-to-High clock transition is transferred to

the corresponding flip-flop’s Q output.

All Q outputs will be forced Low independent of clock or data inputs

by a Low voltage level on the MR

input. The device is useful for

applications where both true and complement outputs are required,

and the clock and master reset are common to all storage elements.

TYPE

TYPICAL

f

MAX

TYPICAL

SUPPLY CURRENT

(TOTAL)

74ALS175 70MHz 7mA

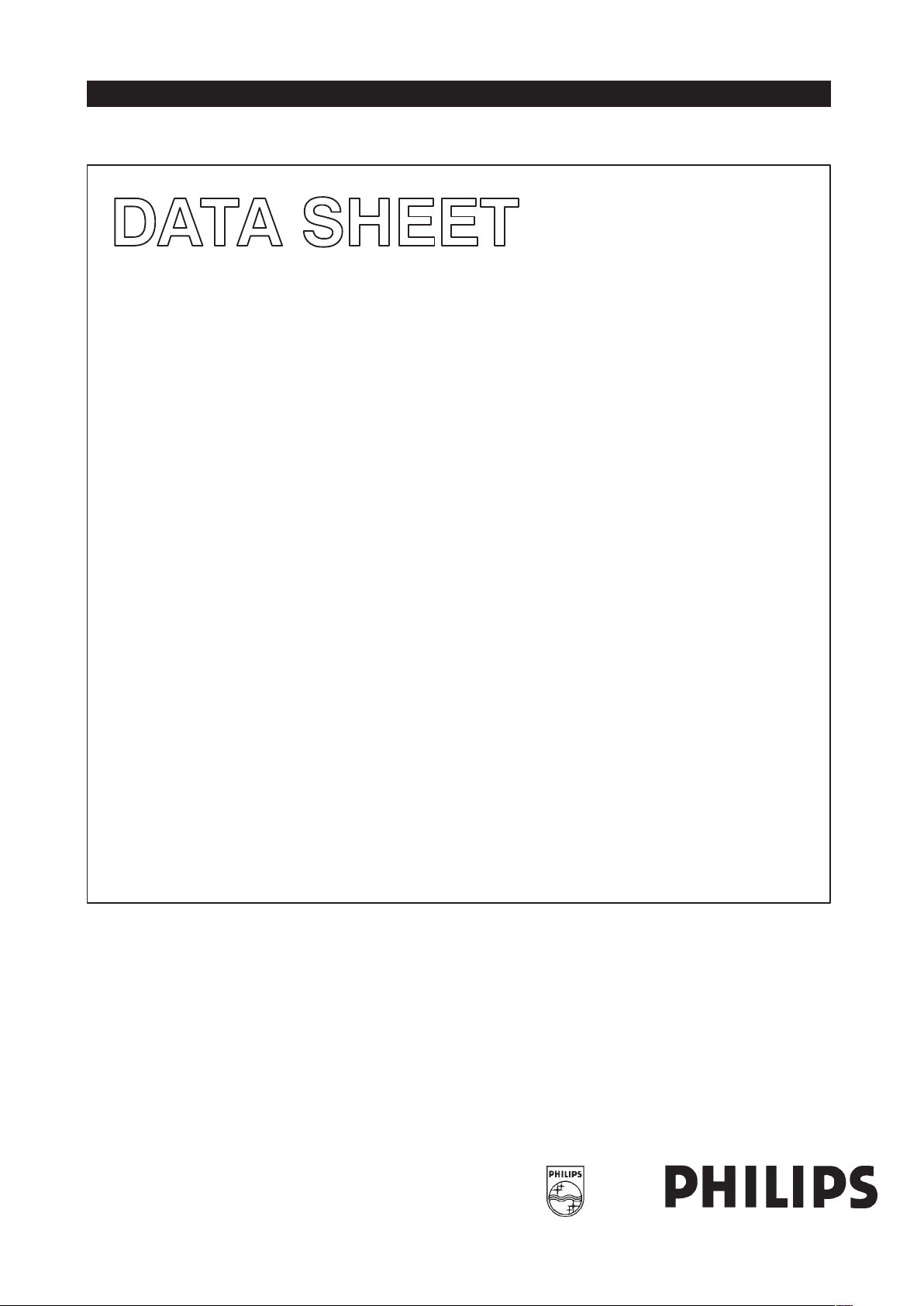

PIN CONFIGURATION

16

15

14

13

12

11

107

6

5

4

3

2

1

98

V

CC

SF00718

Q3

Q3

D3

D2

Q

2

Q2

CP

MR

Q0

Q0

D0

D1

Q

1

Q1

GND

ORDERING INFORMA TION

ORDER CODE

DESCRIPTION COMMERCIAL RANGE

V

CC

= 5V ±10%,

T

amb

= 0°C to +70°C

DRAWING

NUMBER

16-pin plastic DIP 74ALS175N SOT38-4

16-pin plastic SO 74ALS175D SOT109-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74ALS (U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

D0 – D3 Data inputs 1.0/1.0 20µA/0.1mA

CP Clock Pulse input (active rising edge) 1.0/1.0 20µA/0.1mA

MR Master Reset input (active-Low) 1.0/1.0 20µA/0.1mA

Q0 – Q3 True outputs 20/80 0.4mA/8mA

Q0 – Q3 Complementary outputs 20/80 0.4mA/8mA

NOTE: One (1.0) ALS unit load is defined as: 20µA in the High state and 0.1mA in the Low state.

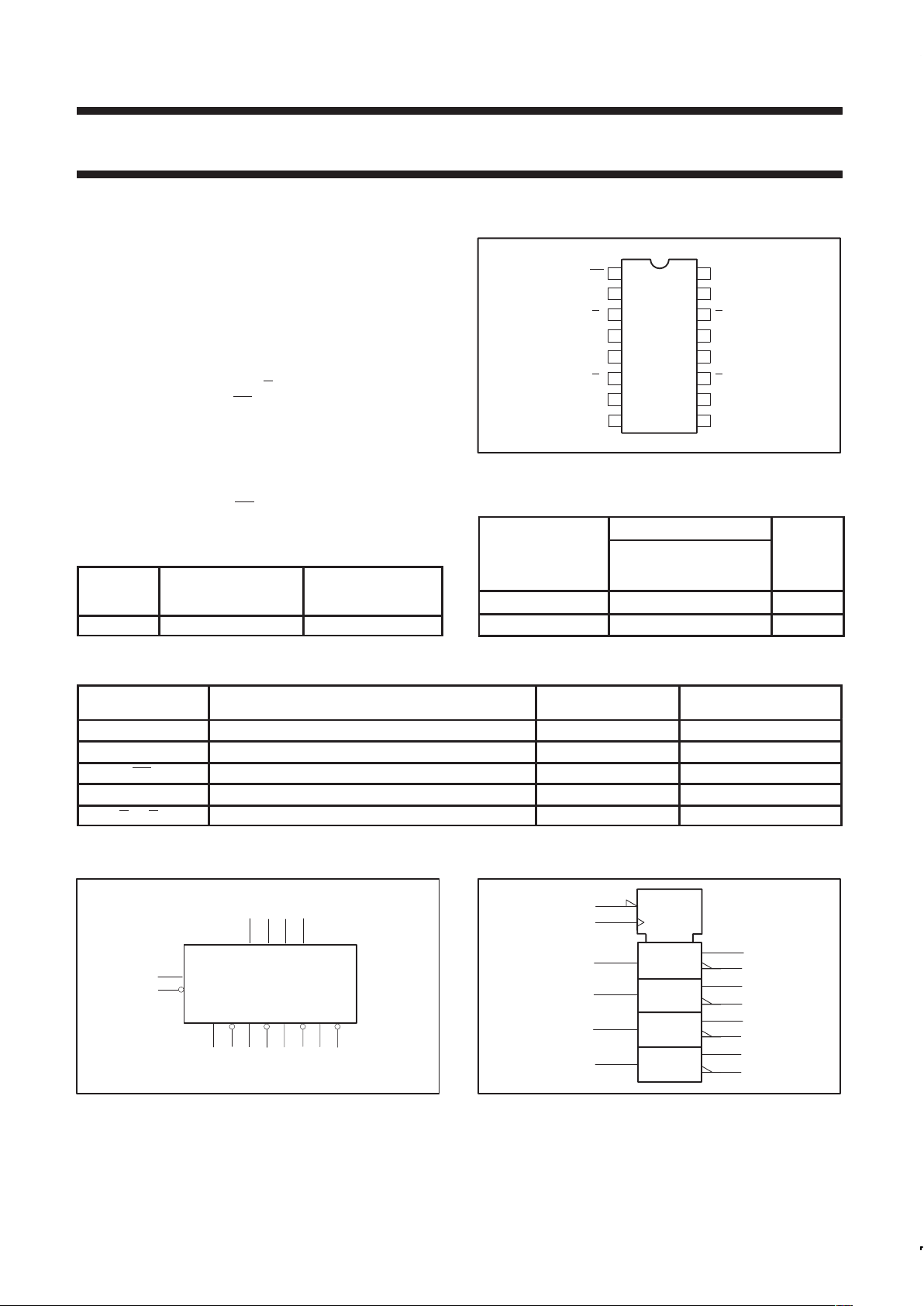

LOGIC SYMBOL

VCC = Pin 16

GND = Pin 8

SF00719

4 5 12 13

D0 D1 D2 D3

CP

MR

9

1

2 3 7 6 10 11 15 14

Q0 Q0 Q1 Q1 Q2 Q2 Q3 Q3

IEC/IEEE SYMBOL

R

C1

1D

SF00720

1

9

4

5

12

13

2

3

7

6

10

11

15

14

Philips Semiconductors Product specification

74ALS175Quad D flip-flop

1991 Feb 08

3

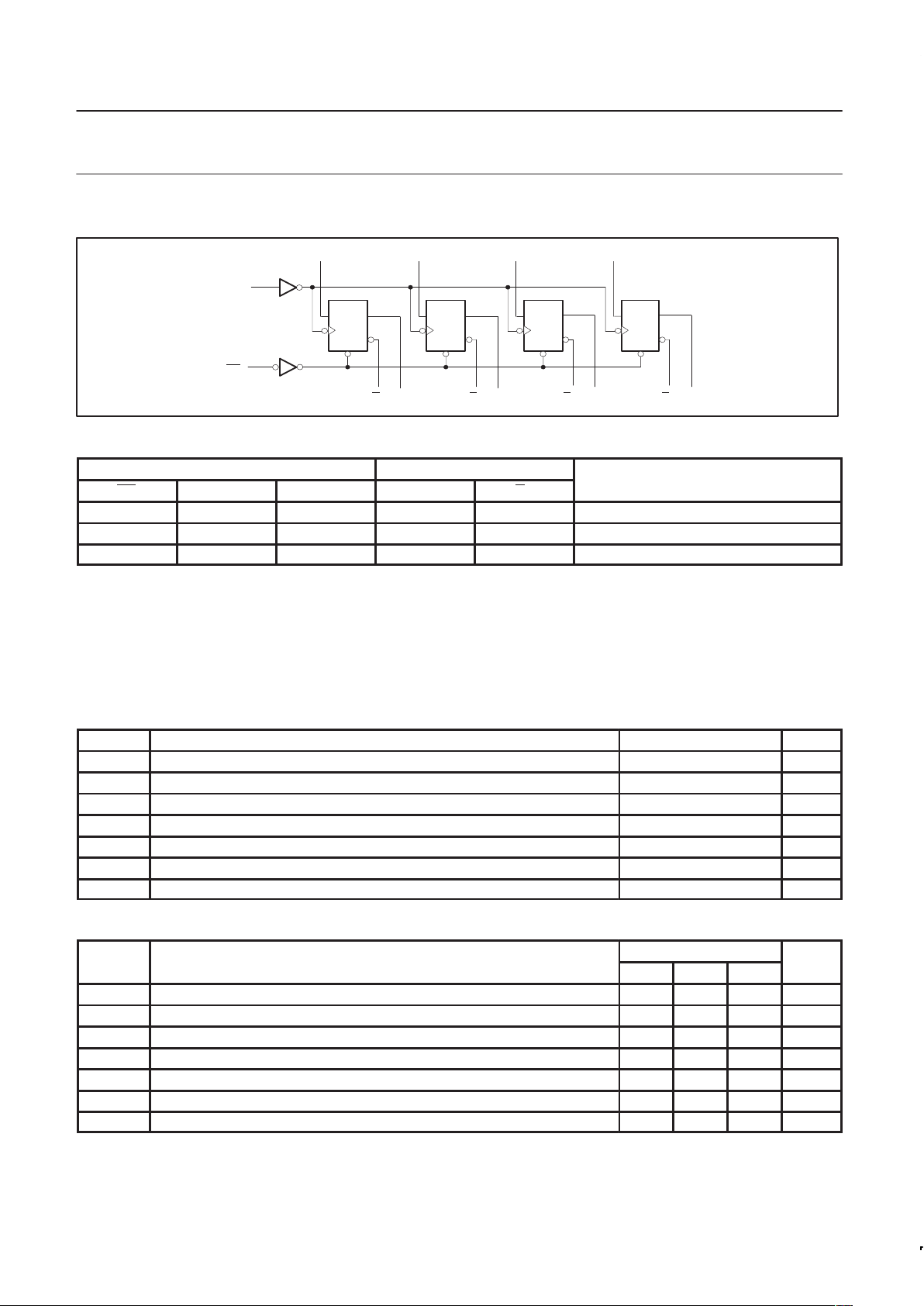

LOGIC DIAGRAM

DQ

RD

V

CC

= Pin 16

GND = Pin 8

CP

D0

4

DQ

RD

CP

D1

5

DQ

RD

CP

D2

12

DQ

RD

CP

D3

13

Q

SF00721

CP

MR

9

1

32 6 1110 14157

Q

0Q0 Q1Q1 Q2Q2 Q3Q3

FUNCTION TABLE

INPUTS OUTPUTS

OPERATING

MR CP D Q

n

Q

n

MODE

L X X L H Reset (clear)

H ↑ h H L Load “1”

H ↑ I L H Load “0”

NOTES:

H = High-voltage level

h = High state must be present one setup time before the Low-to-High clock transition

L = Low-voltage level

l = Low state must be present one setup time before the Low-to-High clock transition

X = Don’t care

↑ = Low-to-High clock transition

ABSOLUTE MAXIMUM RATINGS

(Operation beyond the limit set forth in this table may impair the useful life of the device.

Unless otherwise noted these limits are over the operating free air temperature range.)

SYMBOL

PARAMETER RATING UNIT

V

CC

Supply voltage –0.5 to +7.0 V

V

IN

Input voltage –0.5 to +7.0 V

I

IN

Input current –30 to +5 mA

V

OUT

Voltage applied to output in High output state –0.5 to V

CC

V

I

OUT

Current applied to output in Low output state 16 mA

T

amb

Operating free-air temperature range 0 to +70 °C

T

stg

Storage temperature range –65 to +150 °C

RECOMMENDED OPERATING CONDITIONS

LIMITS

SYMBOL

PARAMETER

MIN NOM MAX

UNIT

V

CC

Supply voltage 4.5 5.0 5.5 V

V

IH

High-level input voltage 2.0 V

V

IL

Low-level input voltage 0.8 V

I

IK

Input clamp current –18 mA

I

OH

High-level output current –0.4 mA

I

OL

Low-level output current 8 mA

T

amb

Operating free-air temperature range 0 +70 °C

Loading...

Loading...