Panasonic CQC-9701-N, CQC-9901-N Service manual

Specifications*

ORDER NO. ACED050210C8

AUTOMOTIVE AFTERMARKET

CQ-C9901N

CQ-C9701N

WMA MP3 CD Player/Receiver with 512

Color OEL Display

General

Power Supply DC 12V (11V - 16V),

Test Voltage 14.4V

Negative Ground

Tone Controls (Bass/Treble) Bass: ±12dB at 80Hz

Treble: ±12dB at 6kHz

Equalizer Center Frequency

(SQ)

Variable Range of Equalizer -12dB to 12dB (2dB step)

Current Consumption Less than 2.5A

Maximum Power Output 70W × 4 (at 4Ω)

Power Output 33W × 4 (DIN45 324,at 4Ω)

Speaker Impedance 4-8Ω

Pre-amp Output Voltage 5V (CD mode)

Subwoofer Output Voltage 5V

Pre-amp Output Impedance 60Ω

Subwoofer Output Impedance 60Ω

External Input Impedance 10kΩ (AUX1, CH/AUX2 IN)

External Input Sensitivity Max. 2V (AUX1, CH/AUX2 IN)

CD Player

Sampling Frequency 8 Times Oversampling

Pick-up Type Astigma 3-Beam

Light Source Semiconductor Laser

Wavelength 790 nm

62.5, 125, 250, 500, 1k, 2k, 4K, 8k,

16k (Hz, default)

(CD mode; 0.5W × 4-speaker)

Frequency Response 20 Hz-20kHz (±1dB)

Signal to Noise Ratio 96dB (2V), 106 dB (5V)

Total Harmonic Distortion 0.01% (1kHz)

Wow and Flutter Below Measurable Limits

Channel Separation 85dB (2V)

FM Stereo Radio

Frequency Range 87.5MHz - 108MHz

Usable Sensitivity 8dB/µV (S/N 30dB)

Stereo Separation 40dB(at 1kHz)

AM (MW) Radio

Frequency Range 531kHz - 1,602kHz

Usable Sensitivity 25dB/µV (S/N 20dB)

AM (LW) Radio

Frequency Range 153kHz - 279kHz

Usable Sensitivity 30dB/µV (S/N 20dB)

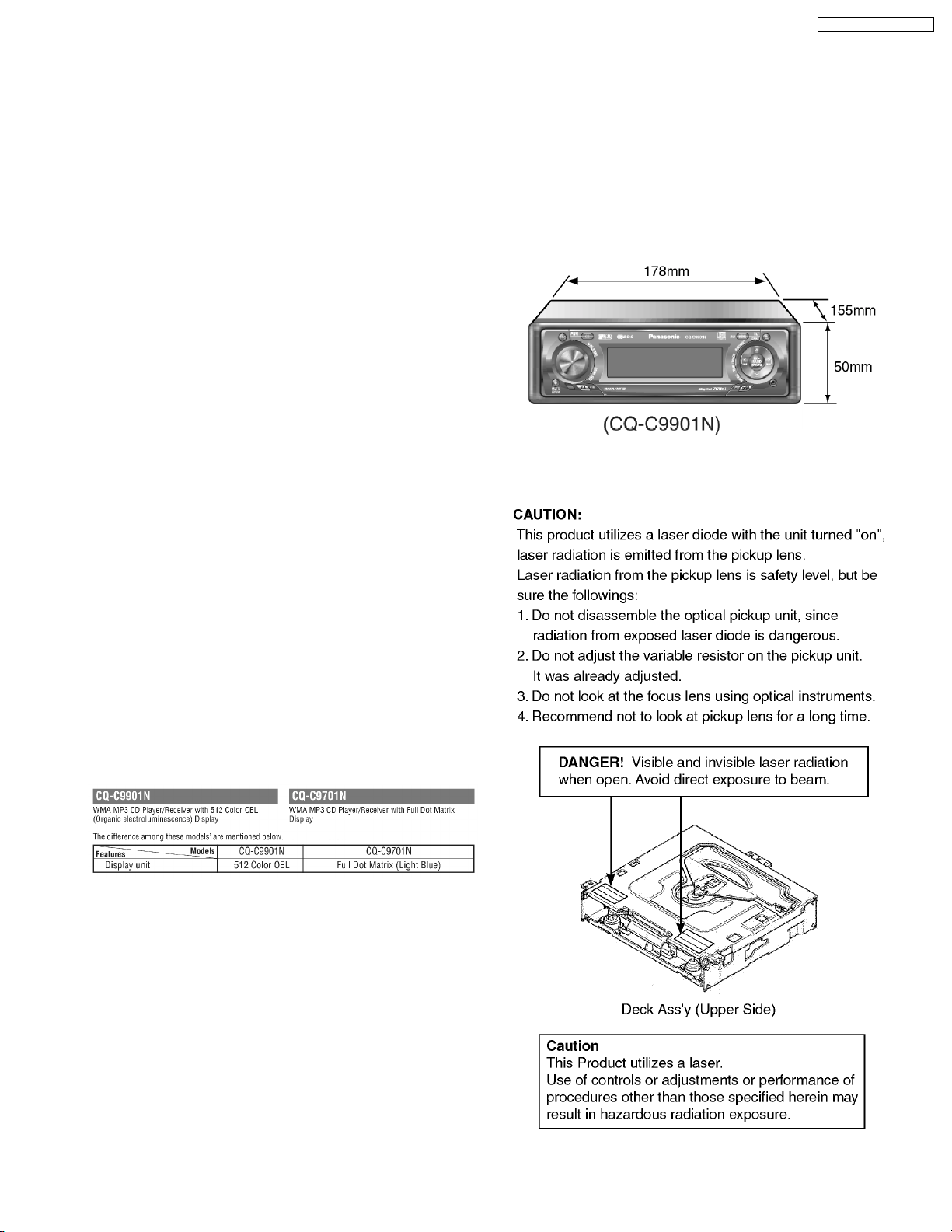

Dimensions (W×H×D)**

Weight** 1.7kg

* Specifications and the design are subject to possible modification

without notice due to improvements.

** Dimensions and Weight shown are approximate.

** Above specifications comply with EIA standards.

178×50×155mm

© 2005 Matsushita Electric Industrial Co., Ltd. All

rights reserved. Unauthorized copying and

distribution is a violation of law.

CQ-C9901N / CQ-C9701N

CONTENTS

Page Page

1 ABOUT LEAD FREE SOLDER (PbF) 3

2 FEATURES

3 REPLACEING THE FUSE

4 MAINTENANCE

5 NOTES

6 DIMENSIONS

7 LASER PRODUCTS

8 WIRING CONNECTION

9 BLOCK DIAGRAM

10 DISASSEMB LY INSTRUCTI ONS

11 TERMINALS DESCRIPTION

12 PACKGE AND IC BLOCK DIAGRAM

13 REPLACEM ENT PARTS LIST [CQ-C9901N]

3

3

14 EXPLODED VIEW (Unit) [CQ-C9901N]

15 REPLACEM ENT PARTS LIST [CQ-C9701N]

3

3

16 EXPLODED VIEW (Unit) [CQ-C9701N]

3

17 CD PLAYER PARTS LIST

18 EXPLODED VIEW (CD PLAYER)

3

4

19 WIRING DIAGRAM

20 SCHEMATIC DIAGRAM-1

6

12

21 SCHEMATIC DIAGRAM-2

15

21

25

34

35

44

45

47

48

56

57

2

CQ-C9901N / CQ-C9701N

1 ABOUT LEAD FREE

SOLDER (PbF)

Distinction of PbF PCB:

PCBs (manufactured) using lead free solder will have a PbF

stamp on the PCB.

Caution :

•

• Pb free solder has a higher melting point than standard

• •

solder; Typically the melting point is 50 - 70°F (30 40°C) higher. Please use a soldering iron with

temperature control and adjust it to 700 ± 20°F (370 ±

10°C). In case of using high temperature soldering iron,

please be careful not to heat too long.

•

• Pb free solder will tend to splash when heated too high

• •

(about 1100°F/600°C)

•

• This lead free solder will be used for the products after

• •

serial No. 1,000,001.

2 FEATURES

•

• MP3/WMA Playback from CD-R/RW

• •

•

• Full Digital CD Receiver

• •

•

• Radio DSP

• •

•

• Fully Motorized Front Panel

• •

•

• 256×64 pixel 512-color OEL display (CQ-C9901N only)

• •

•

• CS Auto (Circle Surround Automotive)

• •

•

• Six Preset Modes (FLAT, POP, ROCK, VOCAL, JAZZ,

• •

CLUB)

•

• SQ9 (9 Bands Sound Quality)

• •

•

• Full Lineup of optional parts

• •

•

• Innovated APM (Auto Preset Memor y) method

• •

•

• CD Changer Control

• •

•

• DVD Changer Control

• •

•

• Differences Among 2 Models

• •

5 NOTES

[RADIO BLOCK]

Do not align the AM/FM package block. When the package

block is necessary, it will be supplied already aligned at the

factory.

[CD DECK BLOCK]

This model has no servo alignment points because

microcomputer controls the servo circuit

6 DIMENSIONS

7 LASER PRODUCTS

3 REPLACEING THE FUSE

Use fuses of the same specified rating 15 amps. Using different

substitutes or fuses with higher ratings, or connecting the unit

directly without a fuse, could cause fire or damage to the stereo

unit.

4 MAINTENANCE

Your products is designed and manufactured to ensure a

minimum of maintenance. Use a soft cloth for routine exterior

cleaning. Never use benzine, thinner or other solvent.

3

CQ-C9901N / CQ-C9701N

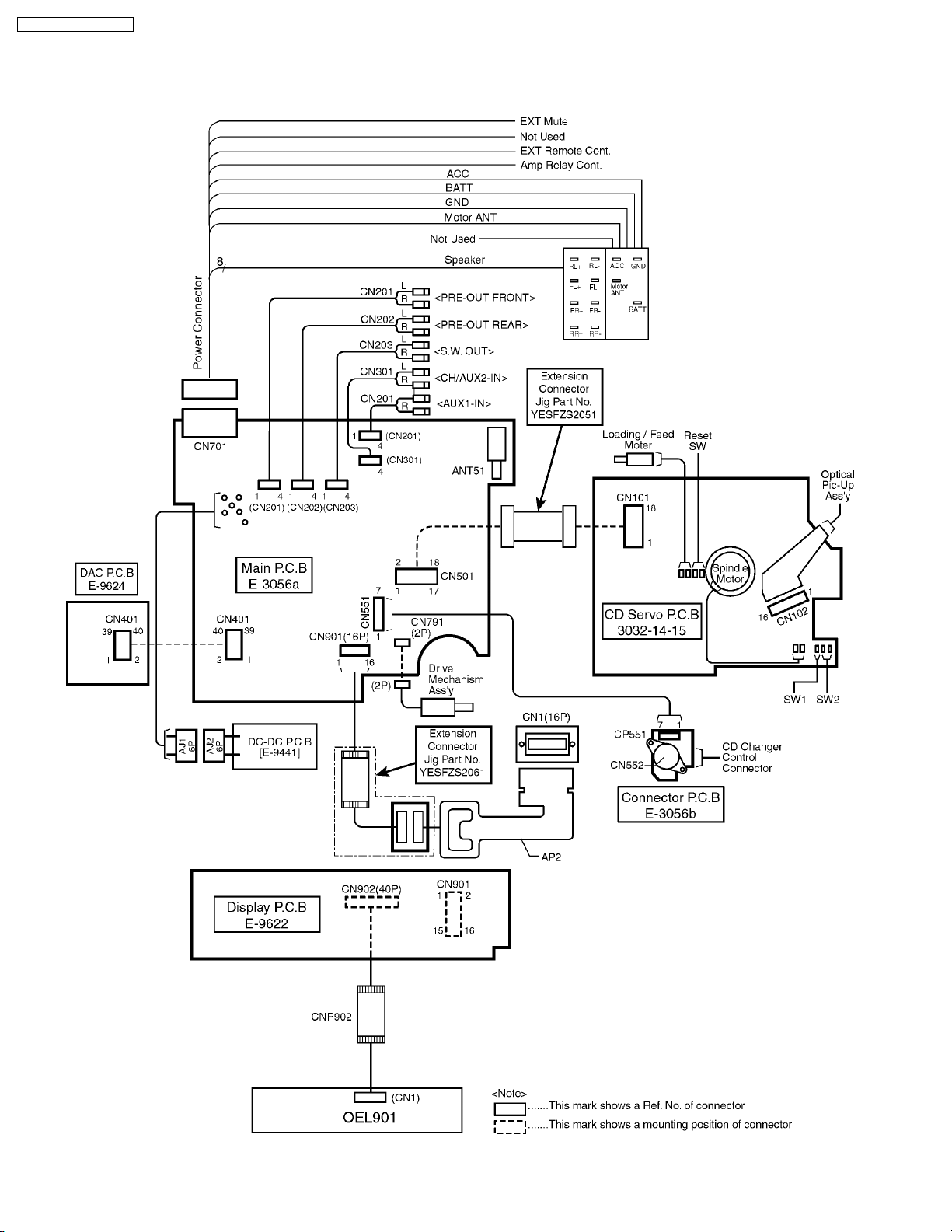

8 WIRING CONNECTION

8.1. CQ-C9901N

4

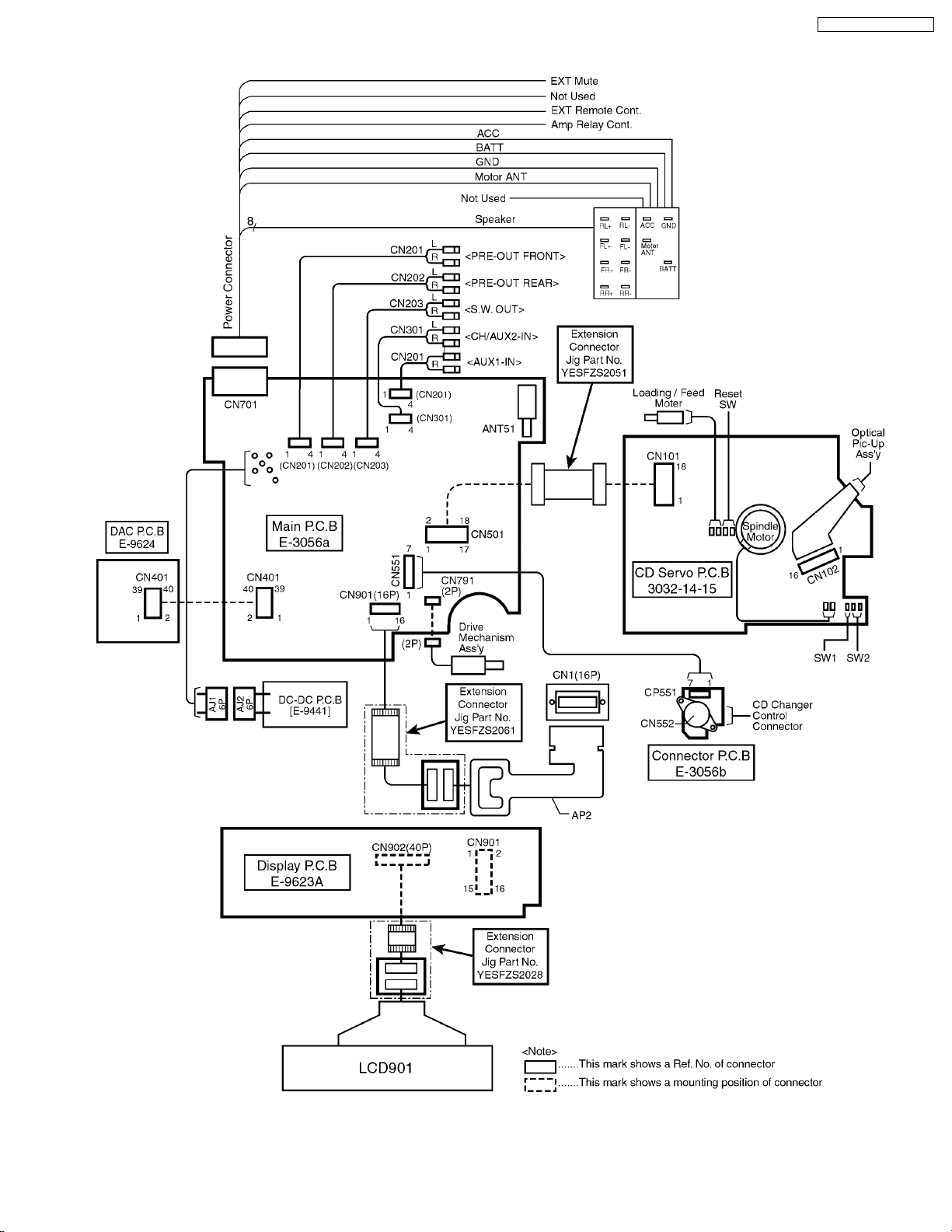

8.2. CQ-C9701N

CQ-C9901N / CQ-C9701N

5

CQ-C9901N / CQ-C9701N

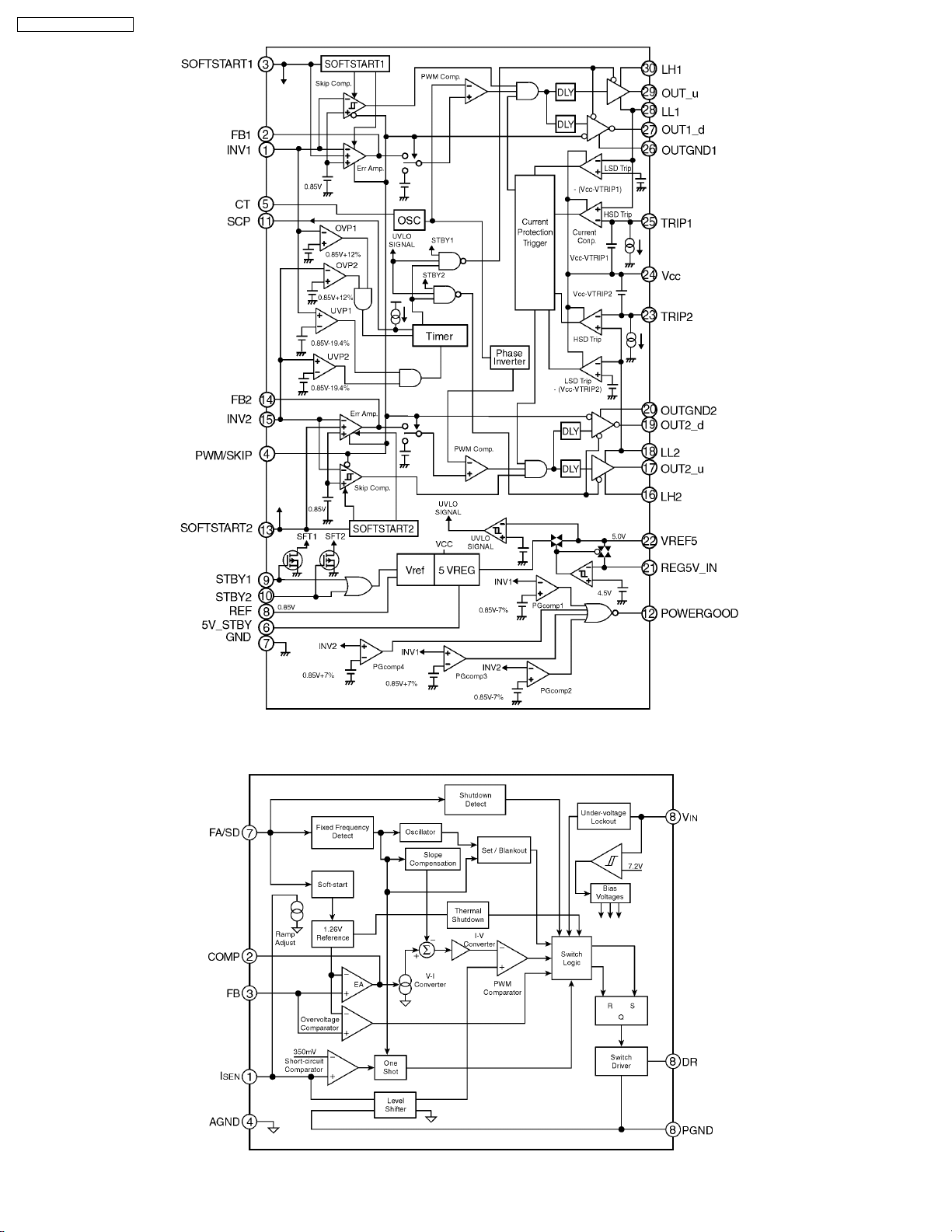

9 BLOCK DIAGRAM

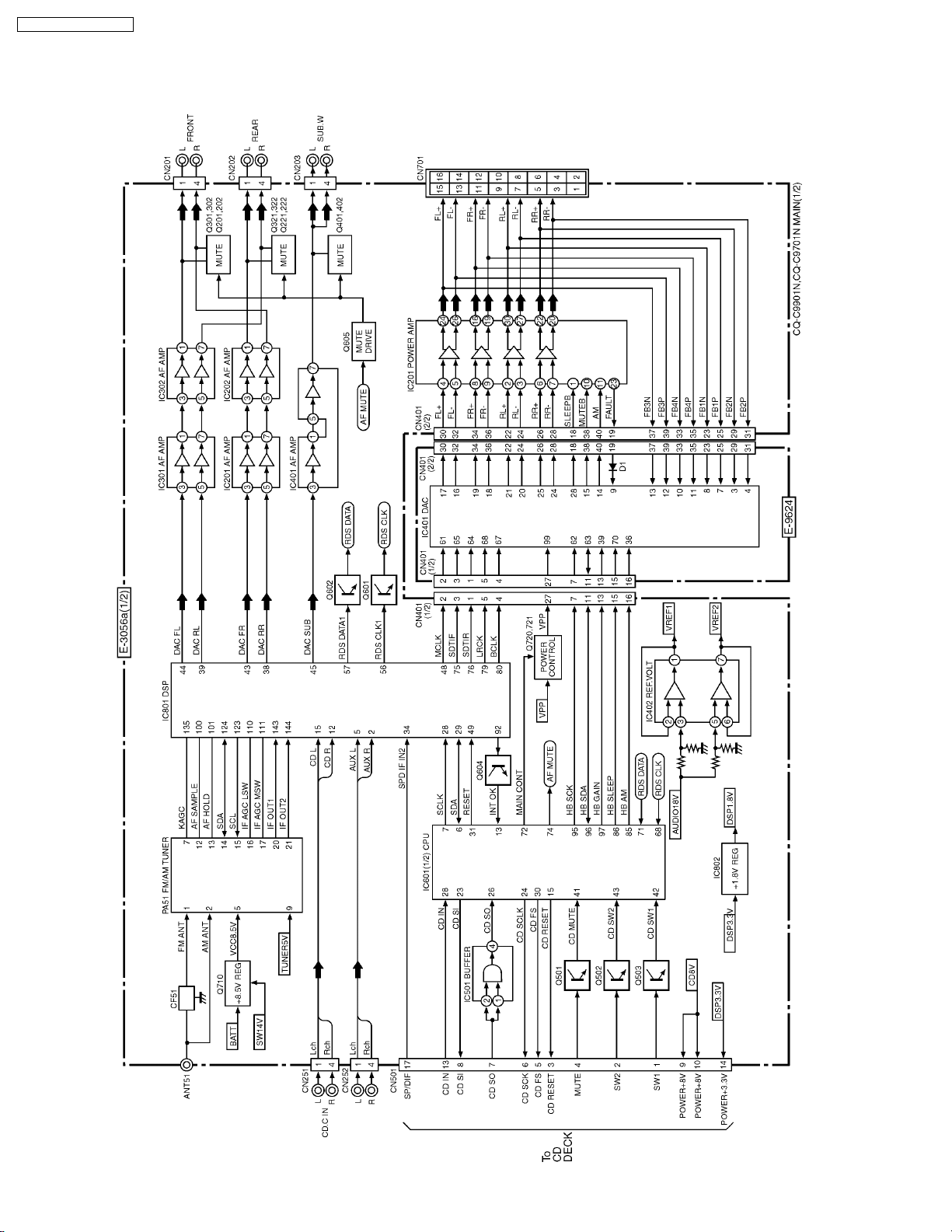

9.1. Main-1/DAC Block (CQ-C9901N/C9701N)

6

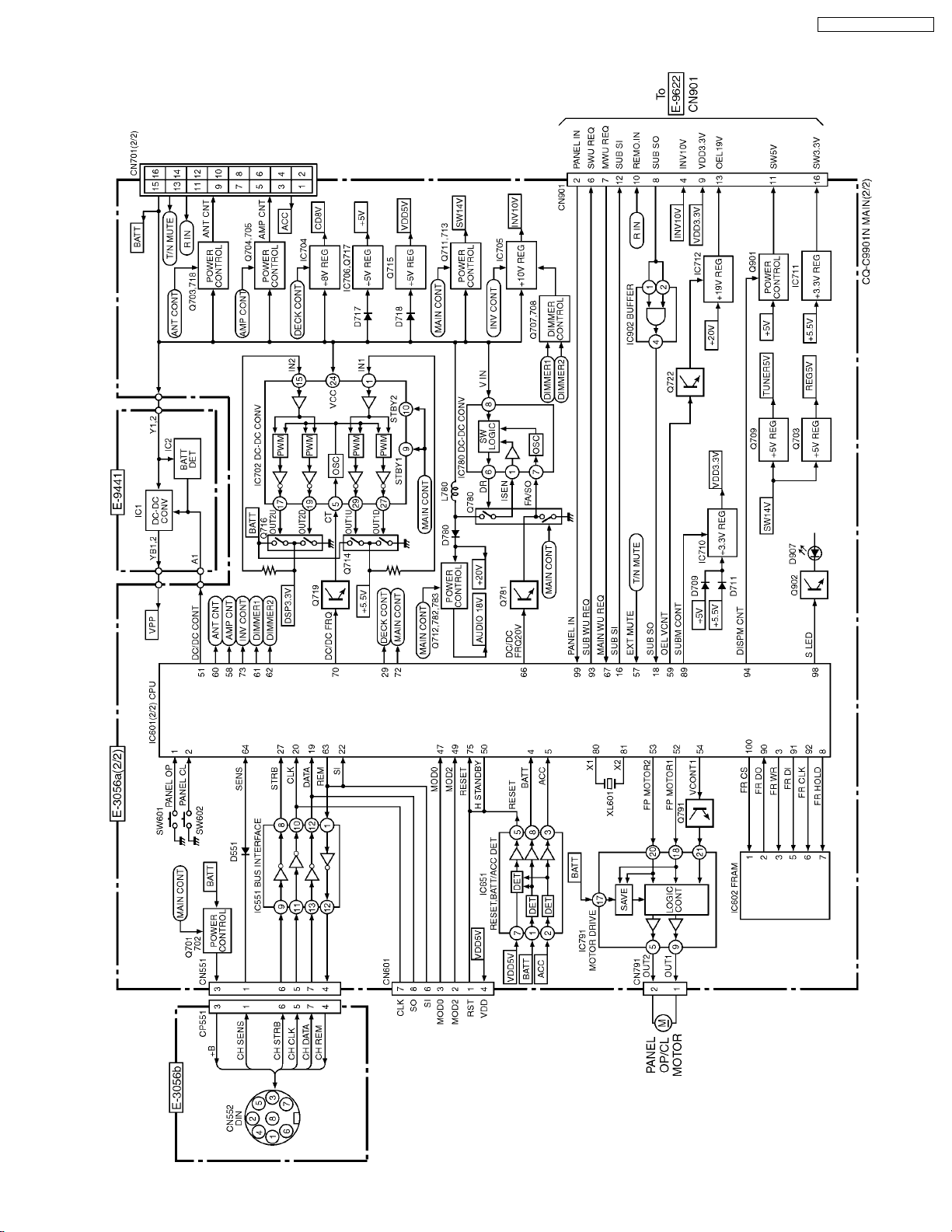

9.2. Main-2/Connector/DC-DC Block (CQ-C9901N)

CQ-C9901N / CQ-C9701N

7

CQ-C9901N / CQ-C9701N

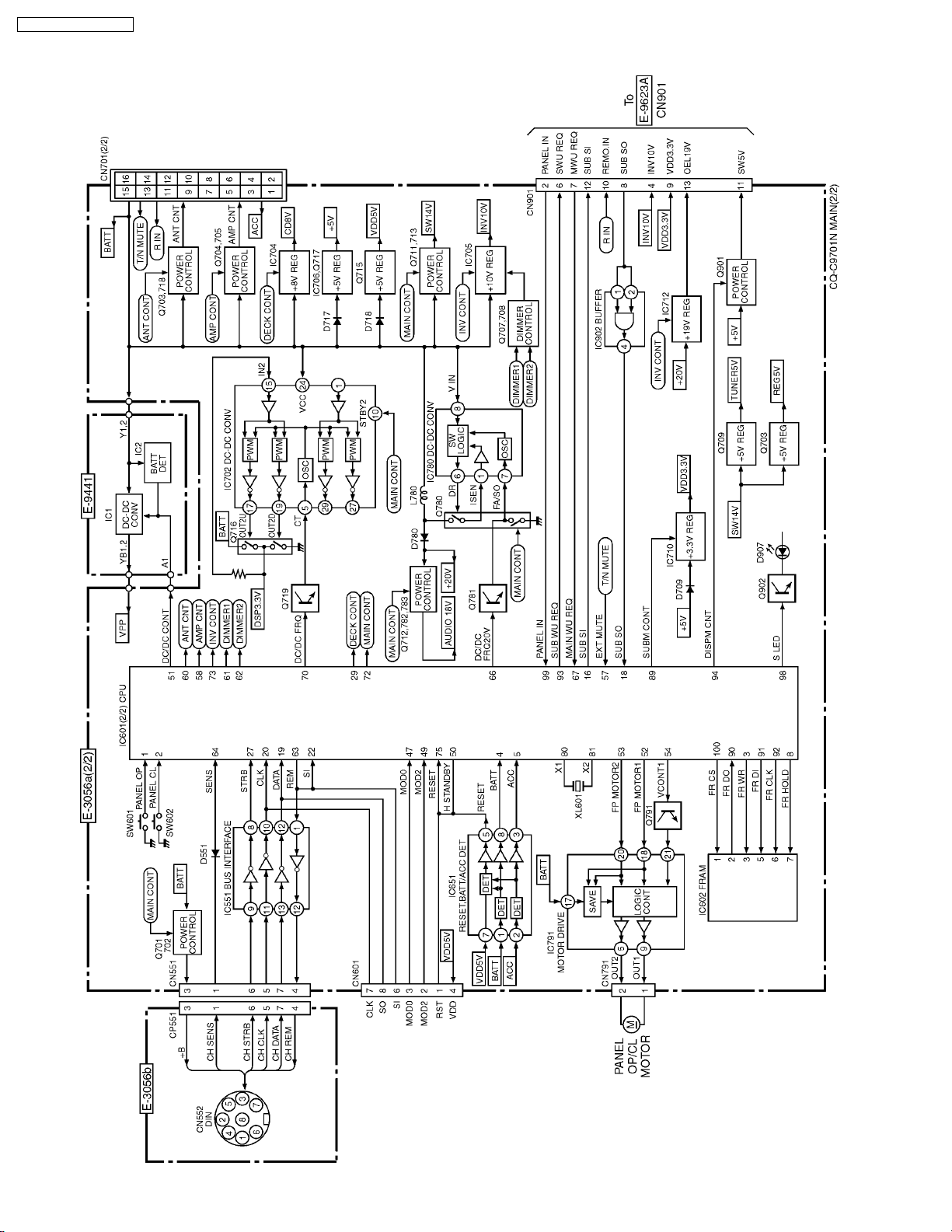

9.3. Main-2/Connector/DC-DC Block (CQ-C9701N)

8

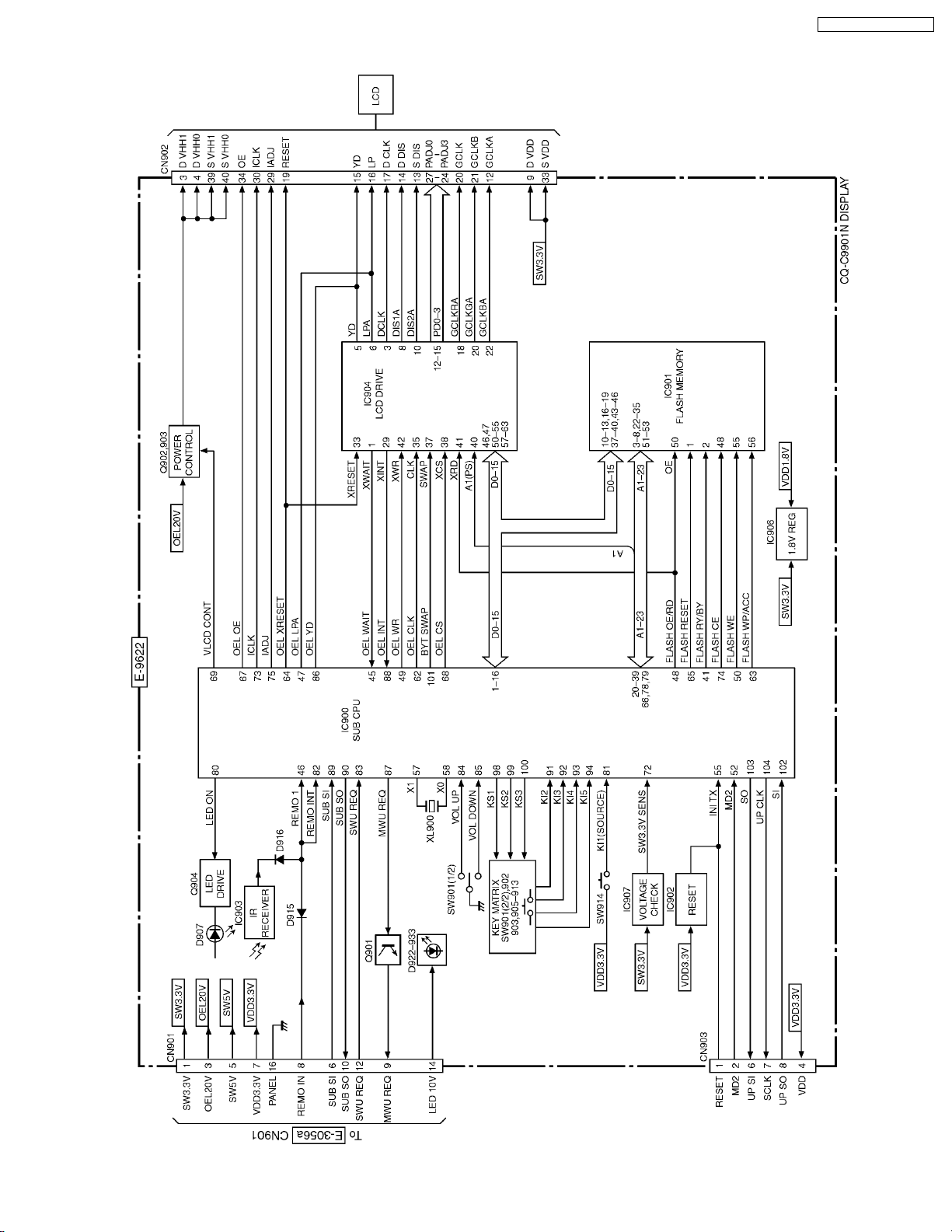

9.4. Display Block (CQ-C9901N)

CQ-C9901N / CQ-C9701N

9

CQ-C9901N / CQ-C9701N

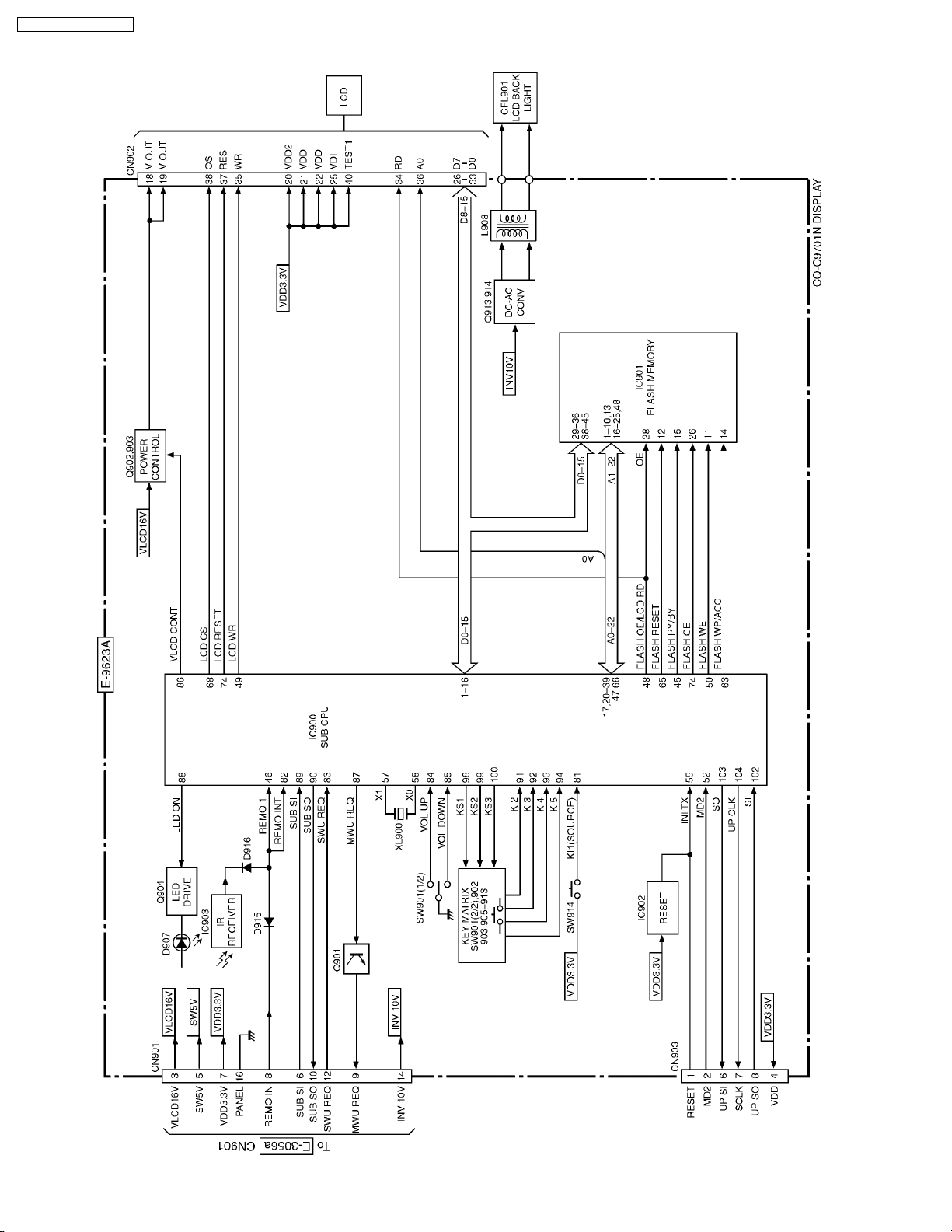

9.5. Display Block (CQ-C9701N)

10

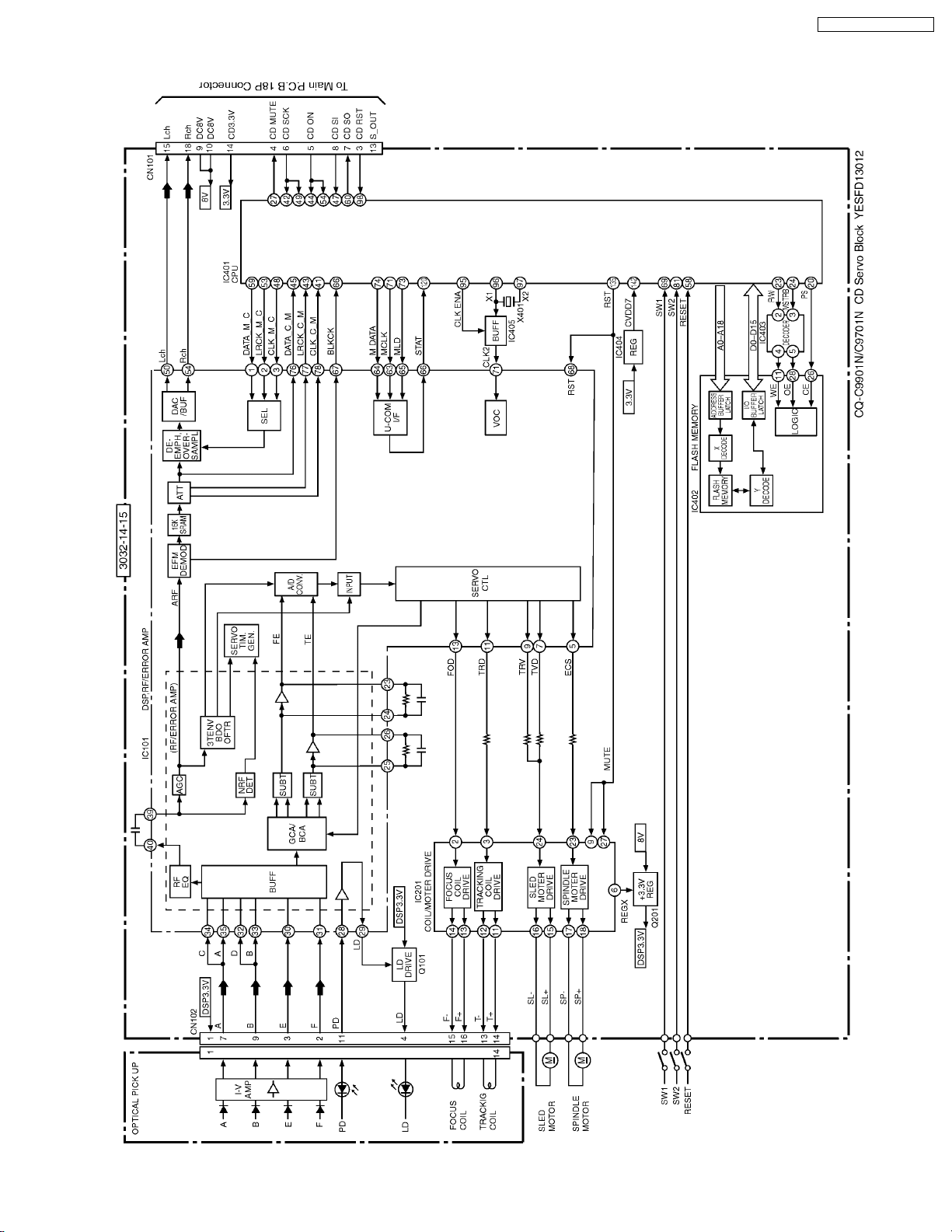

9.6. CD Servo Block

CQ-C9901N / CQ-C9701N

11

CQ-C9901N / CQ-C9701N

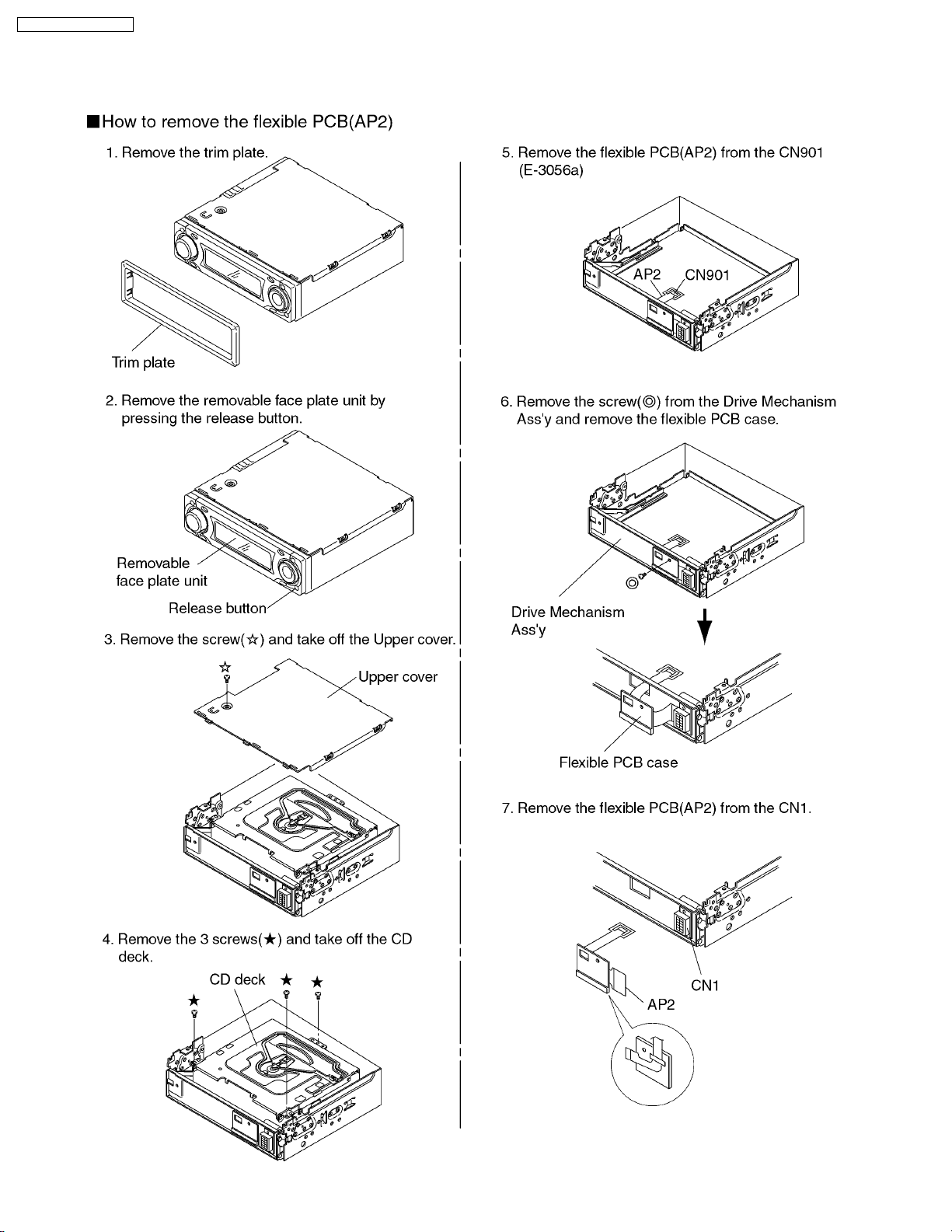

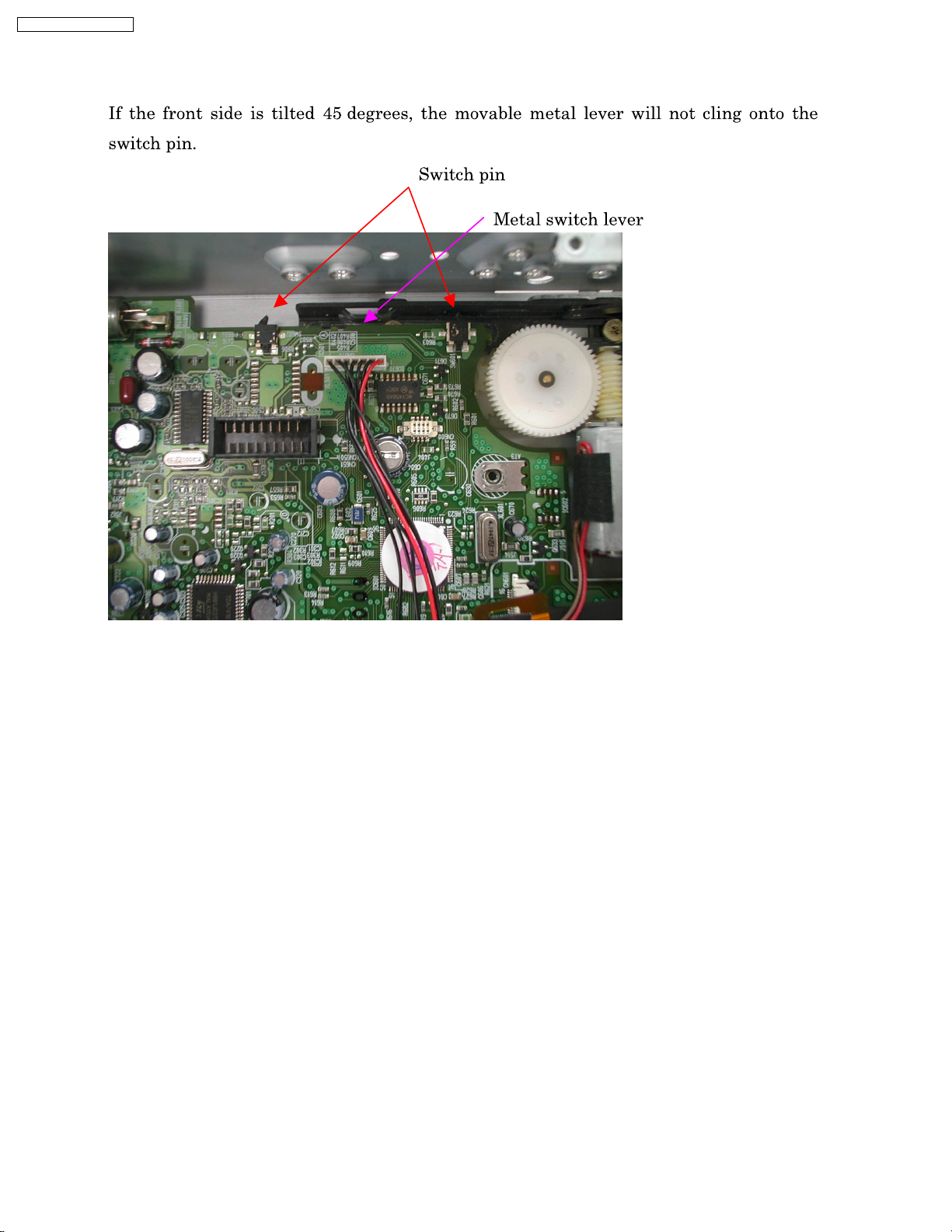

10 DISASSEMBLY INSTRUCTIONS

10.1. How to Remove the Flexible PCB(AP2)

12

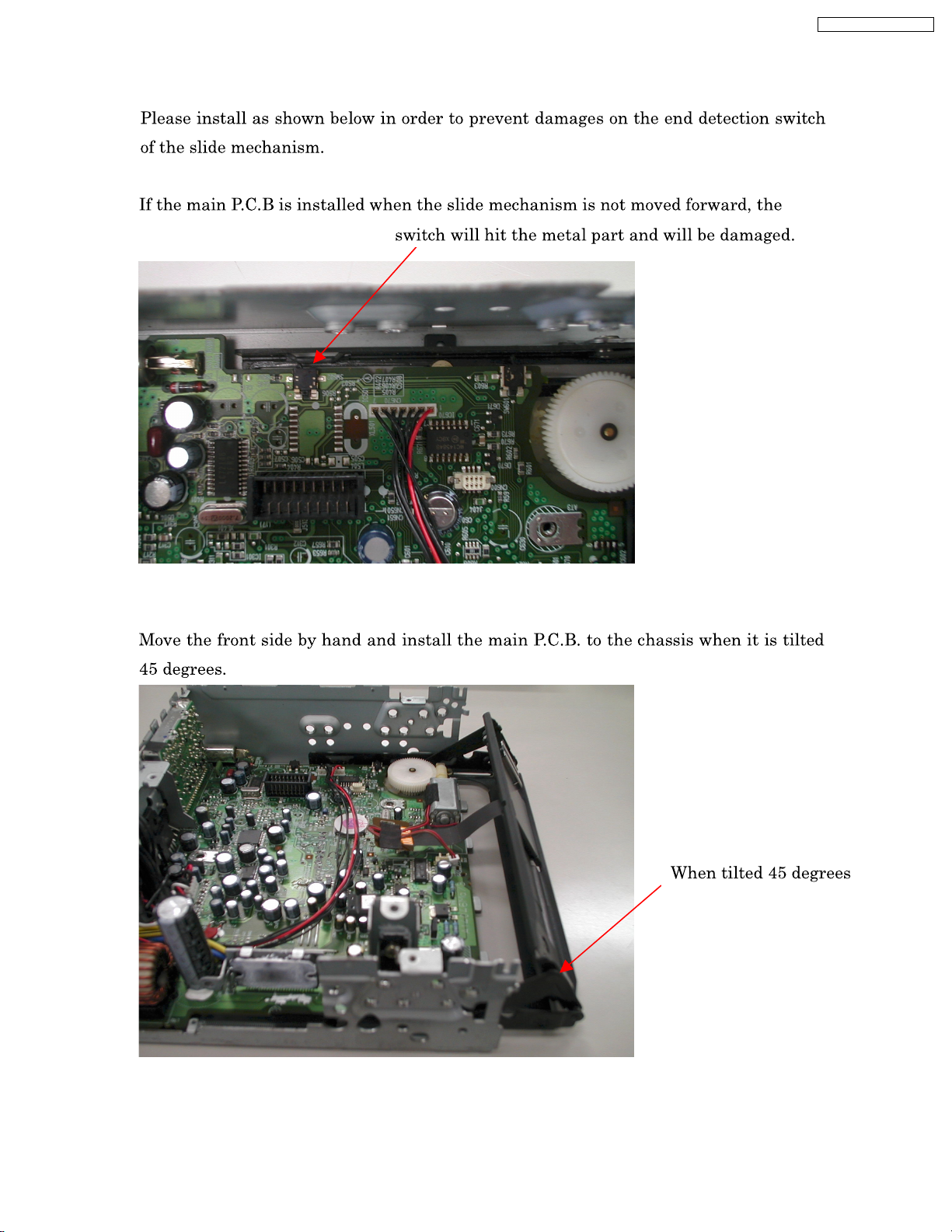

10.2. How to Install the Main P.C.B. of the Electric Display

CQ-C9901N / CQ-C9701N

13

CQ-C9901N / CQ-C9701N

14

11 TERMINALS DESCRIPTION

CQ-C9901N / CQ-C9701N

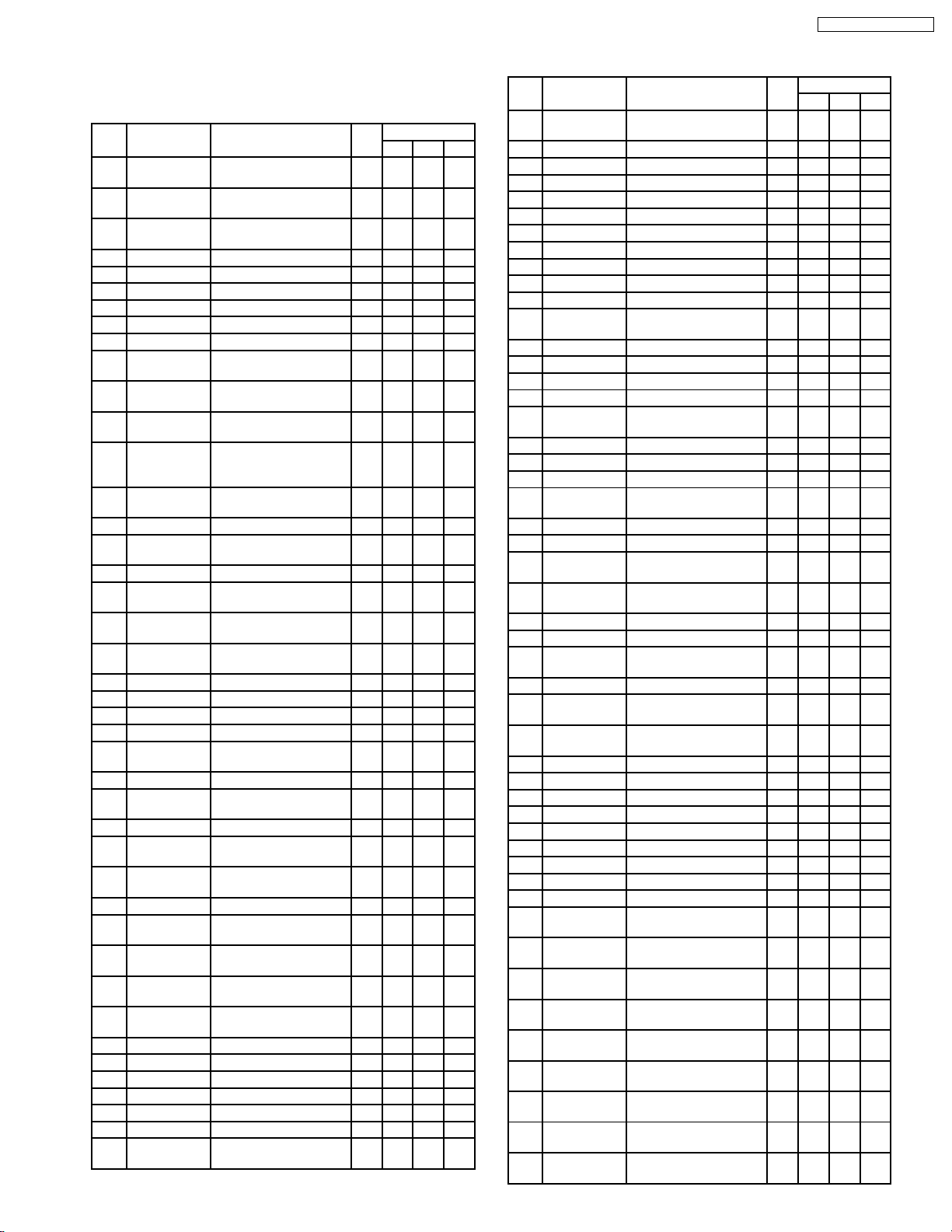

11.1. Main Block [CQ-C9901N]

Pin

No.

1 PANEL

2 PANEL

3 FR WP Write-protection of

4 BATT BATT detection I 5.0 5.0 5.0

5 ACC ACC detection I 5.0 5.0 5.0

6 I2C DATA DSP data I/O I/O 4.9 4.9 4.9

7 I2C CLK DSP clock output O 4.6 4.6 4.6

8 FR HOLD Holding signal to FRAM O 4.8 4.8 4.8

9 Vss GND power supply I 0 0 0

10 NC(LMTR

11 NC(LMTR S L

12 NC(LMTR S

13 DSP INIT OK DSP initialization

14 NC(DE EMPH

15 CD RST CD deck reset output O 4.7 4.7 4.7

16 SUB SI Data transmission to

17 NC No Connection - - - 18 SUB SO Data reception from

19 CH DATA Data reception from CD

20 CH CLK Clock reception from

21 Vdd 5V Power input I 4.8 4.8 4.8

22 UP SI FLASH W SI S0 0.2 4.8 4.8

23 CD SI CD DATA transmission SO 0.3 0.3 0.3

24 CD SCLK CD clock transmission SCK 4.6 4.6 4.6

25 CONDENSORCapacitor terminal for

26 CD SO CD DATA reception SI 0 0 1.4

27 CDC STB Changer stororb signal

28 CD IN DISC Holding detection O 5.0 5.0 5.0

29 DECK V

30 CD FS CD deck frame sink

31 DSP RST Reset output to DSP O 4.6 4.6 4.6

32 Avdd Positive power supply of

33 AVREF Reference voltage for

34 AVGND Standard GND for D/A

35 AVSS Grand potential for A/D

36 NC No Connection - - - 37 INIT A Initialization A A/D 0 0 5.0

38 INIT B Initialization B A/D 0 0 0

39 NC No Connection - - - 40 Vss GND, power supply I 0 0 0

41 CD MUTE CD deck mute detection I 0 0 5.0

42 CD SW1 CD deck DISC

Port Description (I/O) (V)

OPEN

CLOSE

FR)

MONO)

R CENT)

I2S1)

CONT

IC601 : C2CBKG000024

FM AM CD

PANEL OPEN detection I 5.2 5.2 5.2

PANEL CLOSE

detection

FRAM

No Connection - - - -

No Connection - - - -

No Connection - - - -

notifying of timer end

input

No Connection - - - -

SUB u-com

SUB u-com

changer

CD Changer

power supply

input

DECK power supply

control output

output

D/A converter

D/A converter

converter

and D/A converter

detection switch 1

I 0 0 0

O 4.8 4.8 4.8

I 0 0 0

SO 0.8 0.8 0.8

SI 2.4 2.4 2.4

SI 0 0 0

SCK 0 0 0

- 3.1 3.1 3.1

INT 5.2 5.2 5.2

O 4.8 4.8 4.8

O 3.5 3.5 3.5

I 5.1 5.1 5.1

I 5.1 5.1 5.1

I 0 0 0

I 0 0 0

I 5.1 5.1 0

Pin

No.

43 CD SW2 CD deck DISC

44 NC No Connection - - - 45 NC No Connection - - - 46 NC No Connection - - - 47 MOD0 Operating mode input 0 I 5.1 5.1 5.1

48 MOD1 Operating mode input 1 I 5.1 5.1 0

49 MOD2 Operating mode input 2 I 0 0 0

50 H STANDBY External standby input I 4.9 4.9 4.9

51 DC DC CNT DC/DC control for 6 0W O 0 0 0

52 FP MOTOR1 Front switching control 1 O 4.7 4.7 4.7

53 FP MOTOR2 Front switching control 2 O 4.7 4.7 4.7

54 V CNT1 Coordinated control 1 of

55 V CNT2(NC) No Connection - - - 56 NC No Connection - - - 57 EXT MUTE TEL/NAVI MUTE input I 5.1 5.1 5.1

58 AMP CONT External AMP control O 4.8 4.8 4.8

59 OEL VCNT OEL power supply

60 ANT CONT Motor antenna control O 4.8 4.8 0

61 DIM1 Dimmer control output 1 O 0 0 0

62 DIM2 Dimmer control output 2 O 0 0 0

63 CDC REM

64 CDC SENS CDC 1/2 detection I 5.2 5.2 5.2

65 CDC 1/2(NC) No Connection - - - 66 DCDC

67 MAIN.W.U.REQMAIN.WAKE.UP.REQ

68 NC No Connection - - - 69 RDS CLK RDS Clock I 2.6 2.6 2.6

70 DCDC FRQ Frequency switch of

71 RDS DATA RDS Data I 2.6 0 0

72 MAIN CONT MAIN power supply

73 INV CONT INV power supply

74 AF MUTE Tr-MUTE control O/I 0 5.0 5.0

75 RESET Reset input I 4.9 4.9 4.9

76 NC No Connection - - - 77 NC No Connection - - - 78 NC Ground I 0 0 0

79 Vss Ground I 0 0 0

80 X1 Crystal input I 2.0 2.0 2.0

81 X2 Crystal output O 2.5 2.5 2.5

82 Vdd Positive power supply I 5.0 5.0 5.0

83 P00 Pull-doÇón specification

84 P01 Pull-up specification

85 HB AM Analog mode of hybrid

86 HB SLEEP SLEEP control of hybridICO 4.9 4.9 4.9

87 N.C(HB

88 ILL SENS External dimmer control

89 SUBM CNT 3.3V control for SUB

90 FR DO(MI) FRAM communication

91 FR DI(MO) FRAM communication

Port Description (I/O) (V)

I 0 0 5.0

O 0 0 0

O 3.8 3.8 3.8

O 4.8 4.8 4.8

O 4.8 4.8 4.8

I 5.0 5.0 5.0

O 0 0 0

O 4.8 4.8 4.8

O 4.8 4.8 4.8

I 0 0 0

I 5.1 5.1 5.1

O 4.9 4.9 0

I 5.0 5.0 5.0

O 4.9 4.9 4.9

I 0 0 0

O 0 0 0

OUT

FRQ20V

MUTE)

detection switch 2

driving voltage of panel

control terminal

Remote control code

output to Changer

Output the 70th DCDC

FRQ and opposite.

input

power circuit DC/DC

control output

control output

port for writing

port for writing

IC switch control

No Connection - - - -

input

microcomputer

data entry

data output

FM AM CD

15

CQ-C9901N / CQ-C9701N

Pin

No.

92 FR CLK FRAM communication

93 SUB W U

94 DISPM CNT Power supply control

95 HB CLK Clock output to DAC in

96 HB DATA Data I/O to DAC in

97 HB GAIN Hybrid IC GAIN change O 0 0 0

98 S LED Security LED control

99 PANEL IN There is PANEL and it

100 FR CS Chip selection of FRAM O 4.9 4.9 4.9

Port Description (I/O) (V)

CLK

SUB.WAKE.UP.REQ O 4.8 4.8 4.8

REQ

output of display 5V

hybrid IC

hybrid IC

output(CD ILL using

combinedly)

detects it.

11.2. Main Block [CQ-C9701N]

Pin

No.

1 PANEL

2 PANEL

3 FR WP Write-protection of

4 BATT BATT detection I 5.0 5.0 5.0

5 ACC ACC detection I 5.0 5.0 5.0

6 I2C DATA DSP data I/O I/O 4.9 4.9 4.9

7 I2C CLK DSP clock output O 4.6 4.6 4.6

8 FR HOLD Holding signal to FRAM O 4.8 4.8 4.8

9 Vss GND, power supply I 0 0 0

10 NC(LMTR

11 NC(LMTR S L

12 NC(LMTR S

13 DSP INIT OK DSP initialization

14 NC(DE EMPH

15 CD RST CD deck reset output O 4.7 4.7 4.7

16 SUB SI Data transmission to

17 NC No Connection - - - 18 SUB SO Data reception from

19 CH DATA Data reception from CD

20 CH CLK Clock reception from

21 Vdd 5V Power input I 4.8 4.8 4.8

22 UP SI FLASH W SI S0 0.2 4.8 4.8

23 CD SI CD DATA transmission SO 0.3 0.3 0.3

24 CD SCLK CD clock transmission SCK 4.6 4.6 4.6

25 CONDENSORCapacitor terminal for

26 CD SO CD DATA reception SI 0 0 1.4

27 CDC STB Changer stororb signal

28 CD IN DISC Holding detection O 5.0 5.0 5.0

Port Description (I/O) (V)

OPEN

CLOSE

FR)

MONO)

R CENT)

I2S1)

IC601 : C2CBKG000026

PANEL OPEN detection I 5.2 5.2 5.2

PANEL CLOSE

detection

FRAM

No Connection - - - -

No Connection - - - -

No Connection - - - -

notifying of timer end

input

No Connection - - - -

SUB u-com

SUB u-com

changer

CD Changer

power supply

input

FM AM CD

O 0 0 0

O/I 0 0 0

O 4.9 4.9 4.9

O 4.9 4.9 4.9

O 0 0 0

I 0 0 0

FM AM CD

I 0 0 0

O 4.8 4.8 4.8

I 0 0 0

SO 0.8 0.8 0.8

SI 2.4 2.4 2.4

SI 0 0 0

SCK 0 0 0

- 3.1 3.1 3.1

INT 5.2 5.2 5.2

Pin

No.

29 DECK V

30 CD FS CD deck frame sink

31 DSP RST Reset output to DSP O 4.6 4.6 4.6

32 Avdd Positive power supply of

33 AVREF Reference voltage for

34 AVGND Standard GND for D/A

35 AVSS Grand potential for A/D

36 NC No Connection - - - 37 INIT A Initialization A A/D 0 0 5.0

38 INIT B Initialization B A/D 0 0 0

39 NC No Connection - - - 40 Vss GND, power supply I 0 0 0

41 CD MUTE CD deck mute detection I 0 0 5.0

42 CD SW1 CD deck DISC

43 CD SW2 CD deck DISC

44 NC No Connection - - - 45 NC No Connection - - - 46 NC No Connection - - - 47 MOD0 Operating mode input 0 I 5.1 5.1 5.1

48 MOD1 Operating mode input 1 I 5.1 5.1 0

49 MOD2 Operating mode input 2 I 0 0 0

50 H STANDBY External standby input I 4.9 4.9 4.9

51 DC DC CNT DC/DC control for 6 0W O 0 0 0

52 FP MOTOR1 Front switching control 1 O 4.7 4.7 4.7

53 FP MOTOR2 Front switching control 2 O 4.7 4.7 4.7

54 V CNT1 Coordinated control 1 of

55 V CNT2(NC) No Connection - - - 56 NC No Connection - - - 57 EXT MUTE TEL/NAVI MUTE input I 5.1 5.1 5.1

58 AMP CONT External AMP control O 4.8 4.8 4.8

59 NC No Connection - - - 60 ANT CONT Motor antenna control O 4.8 4.8 0

61 DIM1 Dimmer control output 1 O 0 0 0

62 DIM2 Dimmer control output 2 O 0 0 0

63 CDC REM

64 CDC SENS CDC 1/2 detection I 5.2 5.2 5.2

65 CDC 1/2(NC) No Connection - - - 66 DCDC

67 MAIN.W.U.REQMAIN.WAKE.UP.REQ

68 NC No Connection - - - 69 RDS CLK RDS Clock I 2.6 2.6 2.6

70 DCDC FRQ Frequency switch of

71 RDS DATA RDS Data I 2.6 0 0

72 MAIN CONT MAIN power supply

73 INV CONT INV power supply

74 AF MUTE Tr-MUTE control O/I 0 5.0 5.0

75 RESET Reset input I 4.9 4.9 4.9

76 NC No Connection - - - 77 NC No Connection - - - 78 NC Ground I 0 0 0

79 Vss Ground I 0 0 0

80 X1 Crystal input I 2.0 2.0 2.0

81 X2 Crystal output O 2.5 2.5 2.5

82 Vdd Positive power supply I 5.0 5.0 5.0

Port Description (I/O) (V)

CONT

OUT

FRQ20V

DECK power supply

control output

output

D/A converter

D/A converter

converter

and D/A converter

detection switch 1

detection switch 2

driving voltage of panel

Remote control code

output to Changer

Output the 70th DCDC

FRQ and opposite.

input

power circuit DC/DC

control output

control output

O 4.8 4.8 4.8

O 3.5 3.5 3.5

I 5.1 5.1 5.1

I 5.1 5.1 5.1

I 0 0 0

I 0 0 0

I 5.1 5.1 0

I 0 0 5.0

O 0 0 0

O 4.8 4.8 4.8

O 4.8 4.8 4.8

I 5.0 5.0 5.0

O 0 0 0

O 4.8 4.8 4.8

O 4.8 4.8 4.8

FM AM CD

16

Pin

No.

83 P00 Pull-doÇón specification

84 P01 Pull-up specification

85 HB AM Analog mode of hybrid

86 HB SLEEP SLEEP control of hybridICO 4.9 4.9 4.9

87 N.C(HB

88 ILL SENS External dimmer control

89 SUBM CNT 3.3V control for SUB

90 FR DO FRAM communication

91 FR DI FRAM communication

92 FR CLK FRAM communication

93 SUB W U

94 DISPM CNT Power supply control

95 HB CLK Clock output to DAC in

96 HB DATA Data I/O to DAC in

97 HB GAIN Hybrid IC GAIN change O 0 0 0

98 S LED Security LED control

99 PANEL IN There is PANEL and it

100 FR CS Chip selection of FRAM O 4.9 4.9 4.9

Port Description (I/O) (V)

FM AM CD

I 0 0 0

port for writing

I 5.1 5.1 5.1

port for writing

O 4.9 4.9 0

IC switch control

No Connection - - - -

MUTE)

I 5.0 5.0 5.0

input

O 4.9 4.9 4.9

microcomputer

I 0 0 0

data entry

O 0 0 0

data output

O 0 0 0

CLK

SUB.WAKE.UP.REQ O 4.8 4.8 4.8

REQ

O/I 0 0 0

output of display 5V

O 4.9 4.9 4.9

hybrid IC

O 4.9 4.9 4.9

hybrid IC

O 0 0 0

output(CD ILL using

combinedly)

I 0 0 0

detects it.

CQ-C9901N / CQ-C9701N

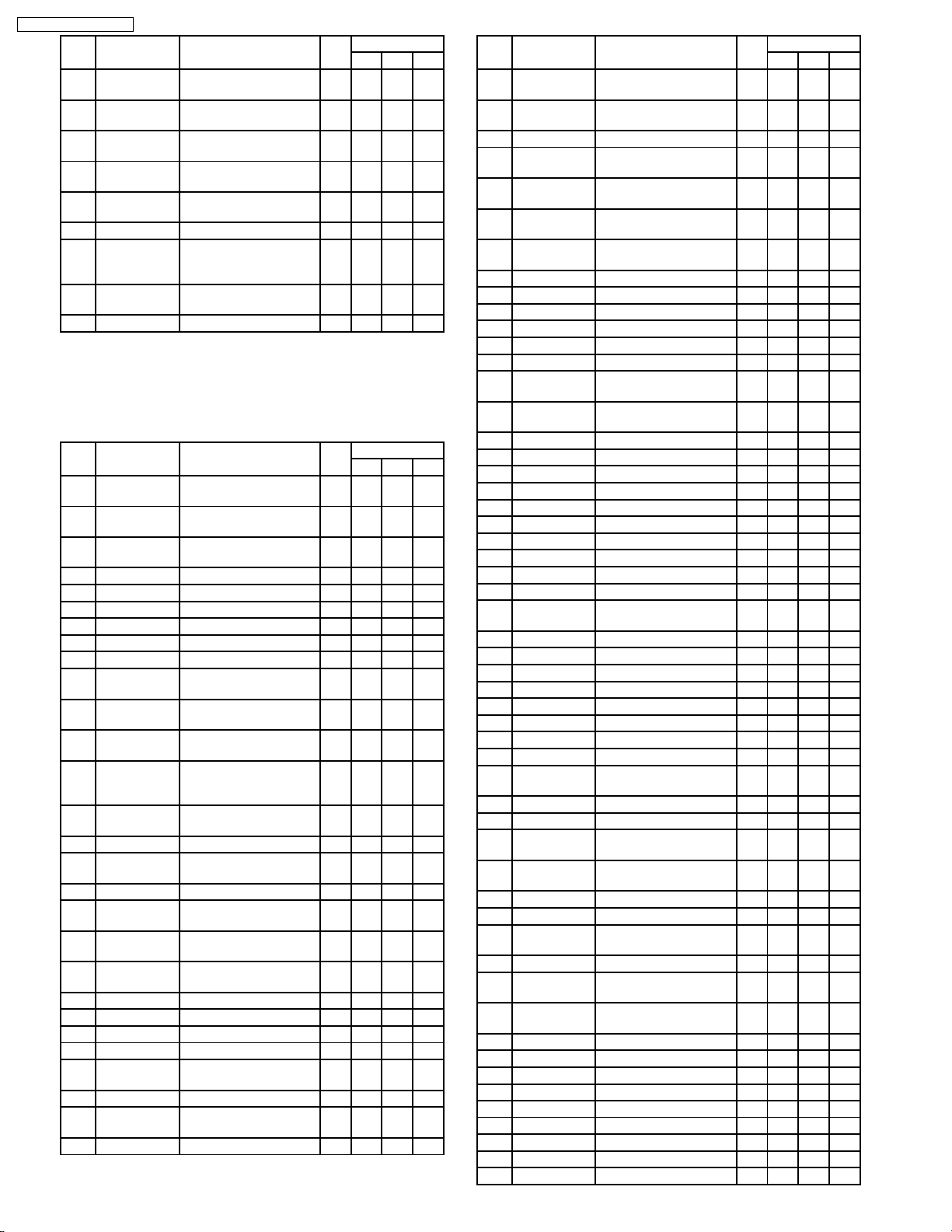

11.3. Display Block [CQ-C9901N]

Pin

No.

1 D0 FLASH D0/OEL D0 I 0.7

2 D1 FLASH D1/OEL D1 I 1.3

3 D2 FLASH D2/OEL D2 I 1.3

4 D3 FLASH D3/OEL D3 I 1.6

5 D4 FLASH D4/OEL D4 I 1.7

6 D5 FLASH D5/OEL D5 I 1.6

7 D6 FLASH D6/OEL D6 I 1.4

8 D7 FLASH D7/OEL D7 I 1.3

9 D8 FLASH D8/OEL D8 I/O 1.4

10 D9 FLASH D9/OEL D9 I/O 1.3

11 D10 FLASH D10/OEL D10 I/O 1.6

12 D11 FLASH D11/OEL D11 I/O 1.6

13 D12 FLASH D12/OEL D12 I/O 1.6

14 D13 FLASH D13/OEL D13 I/O 1.5

15 D14 FLASH D14/OEL D14 I/O 1.6

16 D15 FLASH D15/OEL D15 I/O 1.5

17 N.C No Connection - 18 VSS Ground - 0

19 VCC Positive power supply - 3.0

20 A1/OEL RS FLASH A0/OEL controller data

21 A2 FLASH A1 O 0.6

22 A3 FLASH A2 O 0.1

23 A4 FLASH A3 O 0.6

24 A5 FLASH A4 O 0.6

25 A6 FLASH A5 O 0.8

26 A7 FLASH A6 O 0.9

27 A8 FLASH A7 O 0.6

28 A9 FLASH A8 O 0

29 A10 FLASH A9 O 0

30 A11 FLASH A10 O 0.8

31 A12 FLASH A11 O 1.2

32 A13 FLASH A12 O 1.2

33 A14 FLASH A13 O 0

34 A15 FLASH A14 O 0

35 A16 FLASH A15 O 1.0

36 A17 FLASH A16 O 0

37 A18 FLASH A17 O 0

38 A19 FLASH A18 O 0

39 A20 FLASH A19 O 0

40 VSS Ground - 0

41 FLASH

42 NC No Connection - 43 VSS Ground - 0

44 VCC Positive power supply - 3.2

45 OEL WAIT OEL controller WAIT signal input I 3.2

46 REMO 1 Remote control signal input I 3.3

47 OEL LPA OEL module Horizontal

48 FLASH

49 OEL WR OEL controller write strobing signal

50 FLASH WE FLASH write enable signal output O 3.2

51 NMI Connecting to VDD I 3.2

52 MD2 Mode setting I 0

53 MD1 Mode setting I 0

54 MD0 Mode setting I 0

55 INITX System RESET signal input I 3.2

56 VCC Positive power supply - 3.3

57 X1 MAIN system clock output

58 X0 MAIN system clock input (12.5MHz) I 1.2

Port Description I/O (V)

RY/BY

OE/OEL RD

IC900 : C2DBKJ000248

command distinction

H:Data, L:Command

Busy FLASH lady/input I -

Synchronizing signal input

FLASH output enable/OEL

controller lead strobing output

output

(12.5MHz)

O 0

I 18.7

O 3.2

O 3.2

O 1.5

17

CQ-C9901N / CQ-C9701N

Pin

No.

59 VSS Ground - 0

60 X0A Ground I 0

61 X1A No Connection - 62 OEL CLK OEL controller system clock output O 63 FLASH

WP/ACC

64 OEL RESET OEL controller reset control output O 65 FLASH

RESET

66 A21 FLASH A20 O 67 OEL OE OEL output enable output O 68 OEL CS OEL controller chip selection output O 69 VLCD

CONT

70 PN0 - - 0

71 PN2 - - 3.2

72 SW3.3

SENS

73 ICLK Anode output current adjustment

74 FLASH CE FLASH chip enable O 75 IADJ Anode output current adjustment

76 VSS Ground - 0

77 VCC Positive power supply supply - 3.2

78 A22 FLASH A21 O 79 A23 FLASH A22 O 80 LED ON P.LED control output O 81 KI1(SOURCE)Key return signal 1input INT/I 0

82 REMO INT Remote control signal interrupt

83 S W U REQ SUB-u-com wake up demand input INT 3.0

84 ROTARY.1 Rotary encoder signal input 1(VOL

85 ROTARY.2 Rotary encoder signal input 2(VOL

86 OEL YD OEL module Vertical Synchronizing

87 MWU

REQ

88 OEL INIT OEL controller interrupt signal input I 3.1

89 SUB SI MAIN-u-com communication data

90 SUB SO MAIN-u-com communication data

91 KI2 Key return signal 2 input I 0

92 KI3 Key return signal 3 input I 0

93 KI4 Key return signal 4 input I 0

94 KI5 Key return signal 5 input I 0

95 VCC Positive power supply supply - 3.2

96 VSS Ground - 0

97 N.C No Connection - 98 KS1 Key scann signal 1 output O 0

99 KS2 Key scann signal 2 output O 0

100 KS3 Key scann signal 3 output O 101 Byt SWAP OEL controller byte SWAP control O 102 UP SO External Flash rewriting input I 103 UP SI External Flash rewriting output O 104 UP CLK External Flash rewriting switch I 3.2

105 NC No Connection - 106 NC No Connection - 107 DAVS D/A converter grand potential - 0

108 DAVC Positive power supply supply for

109 AVCC Positive power supply supply for

110 AVRH Input of reference voltage of A/D

Port Description I/O (V)

FLASH writeprotection/Acseraration output

FLASH reset control output O -

VLCD 16V control O -

OEL controller power supply supply

detection input

data transfer clock output

data output

input

UP)

DOWN)

signal input

MAIN-u-com wake up demand

output

entry

output

D/A converter

A/D converter

converter

O -

I 0

O -

O -

INT 3.2

I 2.3

I 2.3

I 3.1

O 0

I 0.2

O 2.5

- 3.2

- 3.2

- 3.2

Pin

No.

111 AVSS/AVRL Ground potential of A/D converter - 0

112 VSS Ground - 0

113 INIT Initialization switch input (Not used) I 3.2

114 TH DETECT Temperature detection input I 1.2

115 NC Ground - 0

116 NC Ground - 0

117 NC Ground - 0

118 NC Ground - 0

119 NC Ground - 0

120 NC Ground - 0

Port Description I/O (V)

11.4. Display Block [CQ-C9701N]

Pin

No.

1 D0 FLASH D0 I 0.7

2 D1 FLASH D1 I 1.3

3 D2 FLASH D2 I 1.3

4 D3 FLASH D3 I 1.6

5 D4 FLASH D4 I 1.7

6 D5 FLASH D5 I 1.6

7 D6 FLASH D6 I 1.4

8 D7 FLASH D7 I 1.3

9 D8 FLASH D8 I/O 1.4

10 D9 FLASH D9 I/O 1.3

11 D10 FLASH D10 I/O 1.6

12 D11 FLASH D11 I/O 1.6

13 D12 FLASH D12 I/O 1.6

14 D13 FLASH D13 I/O 1.5

15 D14 FLASH D14 I/O 1.6

16 D15 FLASH D15 I/O 1.5

17 A0 LCD driver data command

18 VSS Ground - 0

19 VCC Positive power supply - 3.0

20 A1 FLASH A0 O 0

21 A2 FLASH A1 O 0.6

22 A3 FLASH A2 O 0.1

23 A4 FLASH A3 O 0.6

24 A5 FLASH A4 O 0.6

25 A6 FLASH A5 O 0.8

26 A7 FLASH A6 O 0.9

27 A8 FLASH A7 O 0.6

28 A9 FLASH A8 O 0

29 A10 FLASH A9 O 0

30 A11 FLASH A10 O 0.8

31 A12 FLASH A11 O 1.2

32 A13 FLASH A12 O 1.2

33 A14 FLASH A13 O 0

34 A15 FLASH A14 O 0

35 A16 FLASH A15 O 1.0

36 A17 FLASH A16 O 0

37 A18 FLASH A17 O 0

38 A19 FLASH A18 O 0

39 A20 FLASH A19 O 0

40 VSS Ground - 0

41 NC No Connection - 42 NC No Connection - 43 VSS Ground - 0

44 VCC Positive power supply - 3.2

45 FLASH RY/BY Busy FLASH lady/input I 3.2

46 REMO 1 Remote control signal input I 3.3

47 A22 FLASH A21 I 18.7

Port Description I/O (V)

IC900 : C2DBKJ000247

O 0.8

distinction

18

Pin

No.

48 FLASH

49 LCD WR LCD driver write strobing signal

50 FLASH WE FLASH write enable signal output O 3.2

51 NC No Connection - 52 MD2 Mode setting I 0

53 MD1 Mode setting I 0

54 MD0 Mode setting I 0

55 INITX System RESET signal input I 3.2

56 VCC Positive power supply - 3.3

57 X1 MAIN system clock output

58 X0 MAIN system clock input

59 VSS Ground - 0

60 X0A Ground I 0

61 X1A No Connection - 62 NC No Connection - 63 FLASH

64 LCD RESET LCD driver reset control output O 65 FLASH

66 A21 FLASH A20 O 67 NC No Connection - 68 LCD CS LCD driver chip selection output O 69 NC No Connection - 70 PN0 - - 0

71 PN2 - - 3.2

72 NC No Connection - 73 NC No Connection - 74 FLASH CE FLASH chip enable O 75 NC No Connection - 76 VSS Ground - 0

77 VCC Positive power supply - 3.2

78 NC No Connection - 79 NC No Connection - 80 NC No Connection - 81 KI1(SOURCE) Key return signal 1input INT/I 0

82 REMO INT Remote control signal interrupt

83 S W U REQ SUB-u-com wake up demand

84 ROTARY.1 Rotary encoder signal input 1(VOL

85 ROTARY.2 Rotary encoder signal input 2(VOL

86 VLCD CONT VLCD 16V control terminal I 3.1

87 M W U REQ MAIN-u-com wake up demand

88 LED ON P.LED control output I 3.1

89 SUB SI MAIN-u-com communication data

90 SUB SO MAIN-u-com communication data

91 KI2 Key return signal 2 input I 0

92 KI3 Key return signal 3 input I 0

93 KI4 Key return signal 4 input I 0

94 KI5 Key return signal 5 input I 0

95 VCC Positive power supply - 3.2

96 VSS Ground - 0

97 KI6(NC) No Connection - 98 KS1 Key scann signal 1 output O 0

99 KS2 Key scann signal 2 output O 0

100 KS3 Key scann signal 3 output O 0

101 NC No Connection - 102 UP SO External Flash rewriting input I -

Port Description I/O (V)

OE/LCD RD

WP/ACC

RESET

FLASH output enable/LCD driver

lead strobing output

output

(12.5MHz)

(12.5MHz)

FLASH writeprotection/Acseraration output

FLASH reset control output O -

input

input

UP)

DOWN)

output

input

output

O 3.2

O 3.2

O 1.5

I 1.2

O -

INT 3.2

INT 3.0

I 2.3

I 2.3

O 0

I 0.2

O 2.5

CQ-C9901N / CQ-C9701N

Pin

No.

103 UP SI External Flash rewriting output O 104 UP CLK External Flash rewriting switch I 3.2

105 NC No Connection - 106 NC No Connection - 107 DAVS D/A converter grand potential - 0

108 DAVC Positive power supply supply for

109 AVCC Positive power supply supply for

110 AVRH Input of reference voltage of A/D

111 AVSS/AVRL Ground potential of A/D converter - 0

112 VSS Ground - 0

113 INIT Initialization switch input (Not

114 TH DETECT Temperature detection input I 1.2

115 NC Ground - 0

116 NC Ground - 0

117 NC Ground - 0

118 NC Ground - 0

119 NC Ground - 0

120 NC Ground - 0

Port Description I/O (V)

- 3.2

D/A converter

- 3.2

A/D converter

- 3.2

converter

I 3.2

used)

11.5. CD Servo Block

Pin

No.

1 CVSS1 GND - 0

2 A22 TP407 - 0

3 CVSS2 GND - 0

4 DVDD1 I/O system (3.3V) power supply - 3.1

5 A10 Address bus of FLASH ROM O 3.1

6 HD7(NC) No Connection - 7 A11 Address bus of FLASH ROM O 0

8 A12 O 3.1

9 A13 O 3.1

10 A14 O 3.1

11 A15 O 0

12 /CVDD1 CORE CPU system (1.6V) power

13 HAS(NC) No Connection - 14 DVSS1 GND - 0

15 CVSS3 GND - 0

16 /CVDD2 I/O system (3.3V) power supply - 1.6

17 HCS(NC) No Connection - 18 HR/W(NC) No Connection - 19 READY - - 3.1

20 /PS FLASH ROM selection signal O 3.1

21 /DS(NC) No Connection - 22 /IS(NC) No Connection - 23 R/W Lead/light signal to FLASH ROM O 3.1

24 /MSTRB Memory access signal O 3.1

25 /IOSTRB(NC) No Connection - 26 /MSC - - 3.1

27 MUTE Mute signal output (H:Mute on) O 0

28 /HOLDA(NC) No Connection - 29 /IAQ(NC) No Connection - 30 /HOLD - - 3.1

31 BIO SUBO input I 0

32 MP/MC Operation mode setting (external

33 DVDD2 I/O system (3.3V) power supply - 3.1

34 CVSS4 GND - 0

35 BD R1 GND I 0

Port Descriptions I/O (V)

IC401 : YESAM275

- 1.6

supply

I 3.1

pull-up)

19

CQ-C9901N / CQ-C9701N

Pin

No.

36 BFSR1 - - 37 CVSS5 GND - 0

38 SW1 - - 39 HCNTL0 No Connection - 40 DVSS2 GND - 0

41 CLK C M AUDIO bit clock input I 1.6

42 SCK Clock input I 3.0

43 LRCK C M AUDIO L/R identifying signal input I 1.6

44 CDFS Serial frame sink signal input I 2.4

45 DATA CM AUDIO serial data input I 1.6

46 /HCNTL1(NC) No Connection - 47 SI Serial data input I 0

48 CLK M C AUDIO bit clock output O 1.6

49 SCK Clock input I 3.0

50 CVSS6 GND - 0

51 /HINT(NC) No Connection - 52 CVDD3 CORE CPU system (1.6V) power

53 LRCK M C AUDIO L/R identifying signal

54 CDFS Serial frame sink signal input I 2.4

55 HRDY(NC) No Connection - 56 DVDD3 I/O system (3.3V) power supply - 3.1

57 DVSS3 GND - 0

58 REST SW Mechanics deck REST SW input I 3.1

59 DATA M C AUDIO serial data output O 1.6

60 SO Serial data output O 1.1

61 /IACK(NC) No Connection - 62 HBIL(NC) No Connection - 63 /NMI - - 3.1

64 /INT0 - - 3.1

65 /INT1 - - 3.1

66 BLKCK Subcode block clock pulse input I 0

67 /INT3 - - 3.1

68 CV DD4 CORE CPU system (1.6V) power

69 MCLK Clock output (To Servo DSP) I 0

70 CVSS7 GND - 0

71 BCLKX1(NC) No Connection - 72 DVSS4 GND - 0

73 BFSX1(NC) No Connection - 74 BDX1 - O 3.1

75 DVDD4 I/O system (3.3V) power supply - 3.1

76 DVSS5 GND - 0

77 CLK MD1 Clock mode setting (L fixation) I 0

78 CLK MD2 Clock mode setting (H fixation) I 3.1

79 CLK MD3 Clock mode setting (L fixation) I 0

80 HPI16(NC) No Connection - 81 MLD Command load signal output (To

82 TOUT(NC) No Connection - 83 EMU0 - - 3.1

84 EMU/OFF - - 3.1

85 TDO - - 0

86 TDI - - 3.1

87 /TRST - - 0

88 TCK - - 3.1

89 TMS - - 3.1

90 CVSS8 GND - 0

91 CVDD5 CORE CPU system (1.6V) power

92 HPIENA GND I 0

93 DVSS6 GND - 0

94 CLKOUT(NC) No Connection - 95 CLKENA Oscillation output Cainabl signal O 0

96 X1 Crystal Connection O 0.7

97 X2/CLKIN Crystal Connection I 1.0

Port Descriptions I/O (V)

- 1.6

supply

O 1.5

output

- 1.6

supply

I 0.2

Servo DSP)

- 1.6

supply

Pin

Port Descriptions I/O (V)

No.

98 RS Reset signal input I 3.1

99 D0 Data base of FLASH ROM I/O 0

100 D1 I/O 0

101 D2 I/O 0

102 D3 I/O 0

103 D4 I/O 0

104 D5 I/O 0

105 A16 Address bus of FLASH ROM O 3.1

106 DVSS7 GND - 0

107 A17 Address bus of FLASH ROM O 3.1

108 A18 Address bus of FLASH ROM O 0

109 A19 TP415 O 0

110 A20 TP416 O 0

111 CVSS9 GND - 0

112 DVDD5 I/O system (3.3V) power supply - 3.1

113 D6 Data bus of FLASH ROM I/O 0

114 D7 I/O 0

115 D8 I/O 0

116 D9 I/O 0

117 D10 I/O 0

118 D11 Data bus of FLASH ROM I/O 0

119 D12 I/O 0

120 STAT Status signal input I 3.0

121 D13 Data path of FLASH ROM I/O 3.1

122 D14 I/O 0

123 D15 I/O 0

124 HD5(NC) No Connection - 125 CVDD6 CORE CPU system (1.6V) power

- 1.6

supply

126 CVSS10 GND - 0

127 /HDSI(NC) No Connection - 128 DVSS8 GND - 0

129 /HDS2(NC) No Connection - 130 DVDD6 I/O system (3.3V) power supply - 3.1

131 A0 Address bus of FLASH ROM O 3.1

132 A1 O 0

133 A2 O 0

134 A3 O 0

135 /RST Reset signal output(To Servo

O 3.1

DSP)

136 A4 Address bus of FLASH ROM O 0

137 A5 O 3.1

138 A6 O 3.1

139 A7 O 0

140 A8 O 3.1

141 A9 O 3.1

142 CVDD7 CORE CPU system (1.6V) power

- 1.6

supply

143 A12 TP406 - 0

144 DVSS9 GND - 0

20

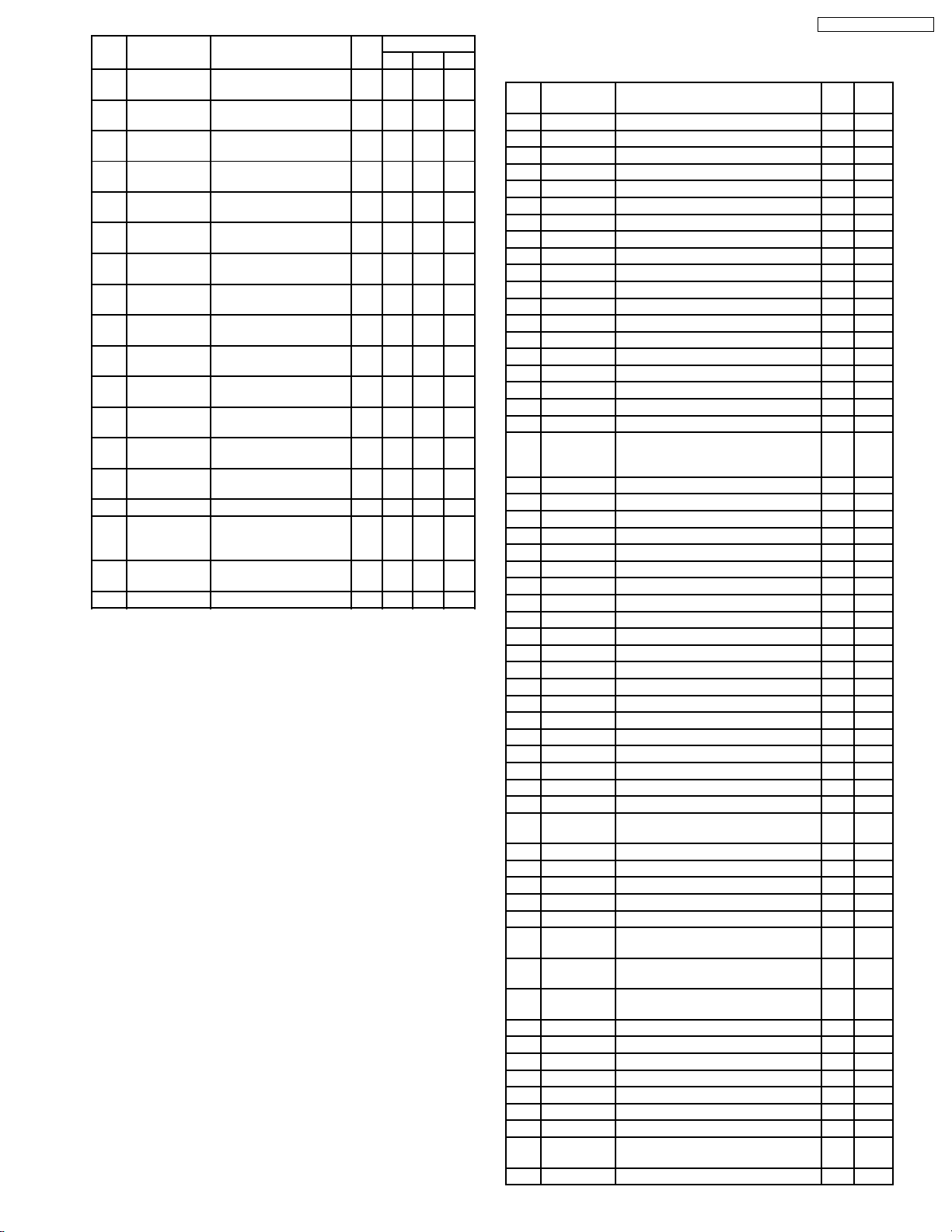

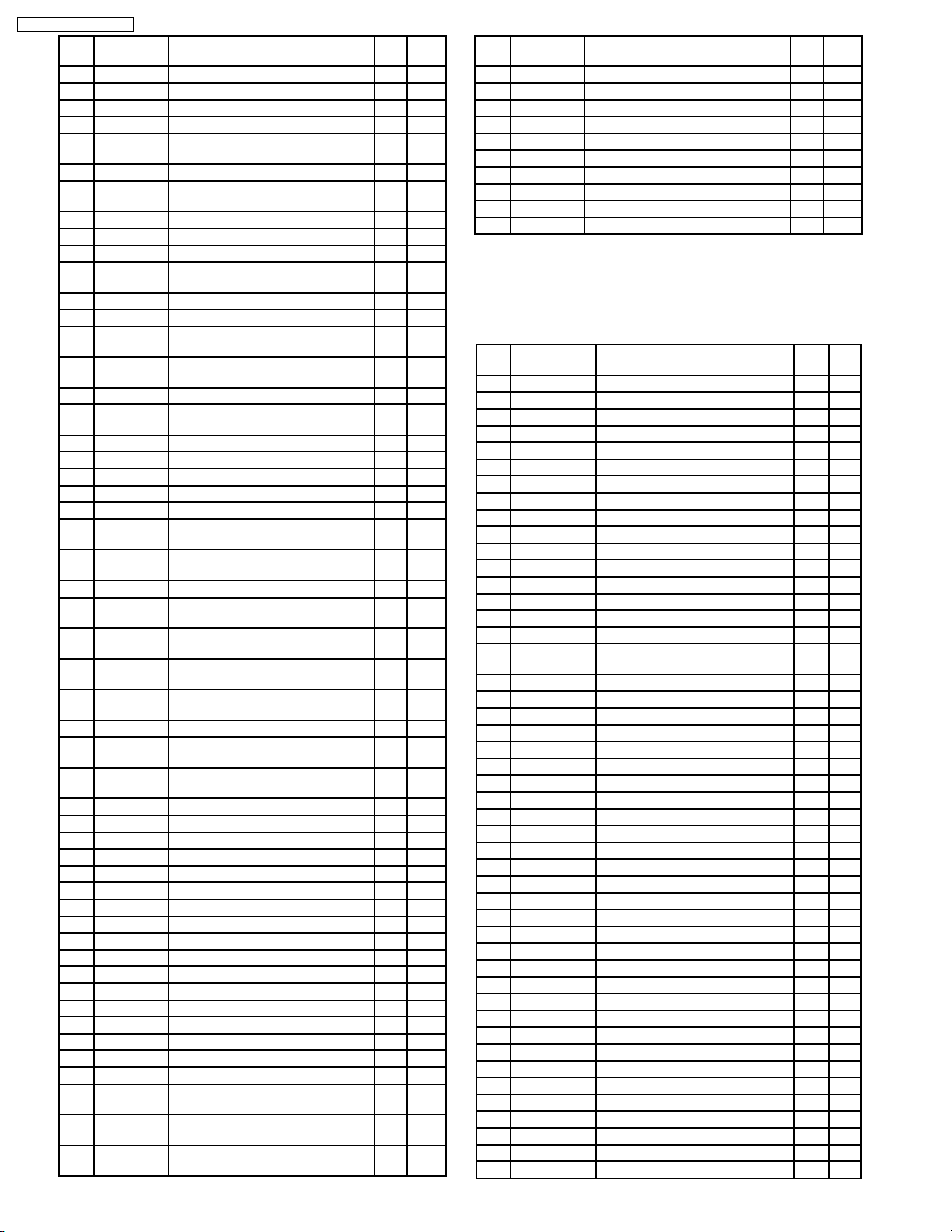

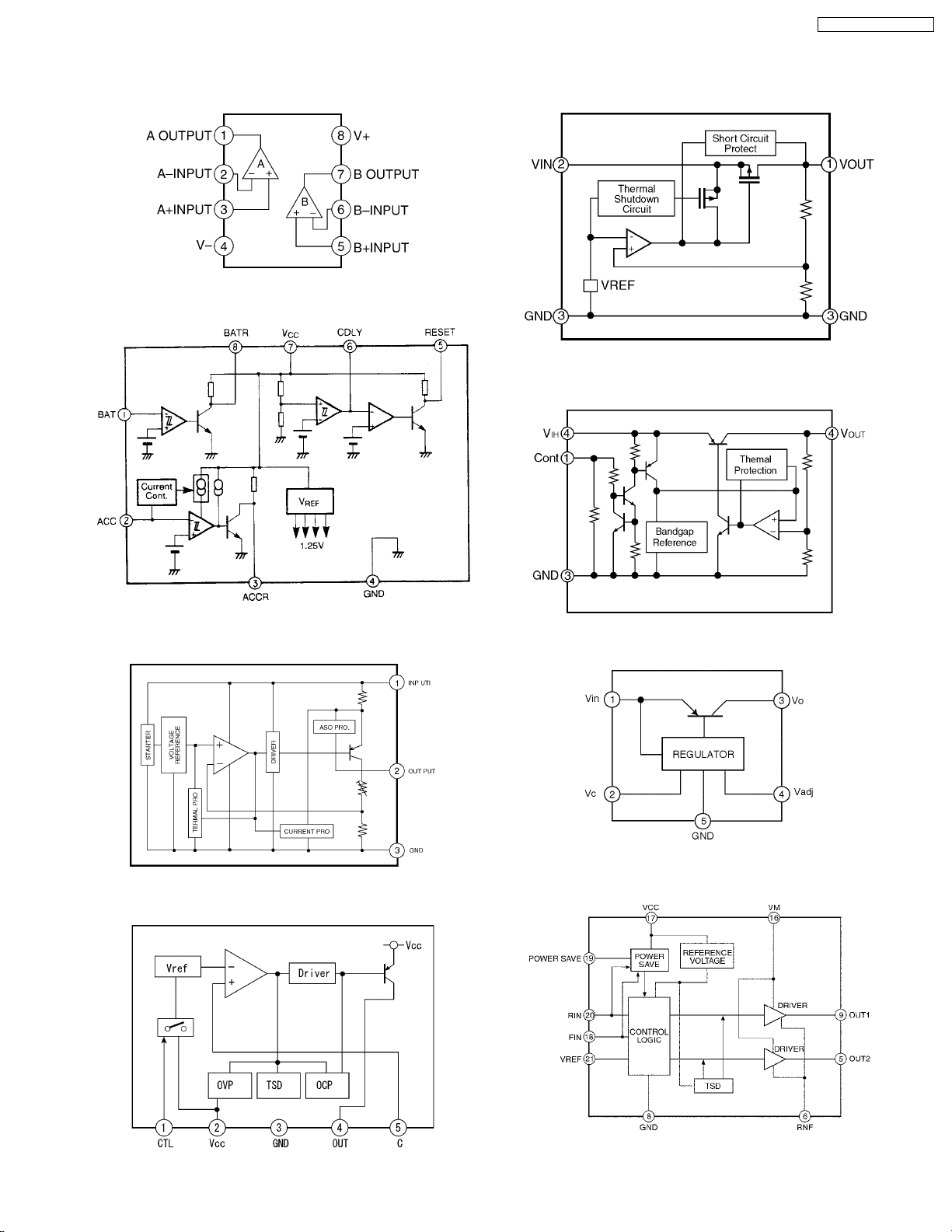

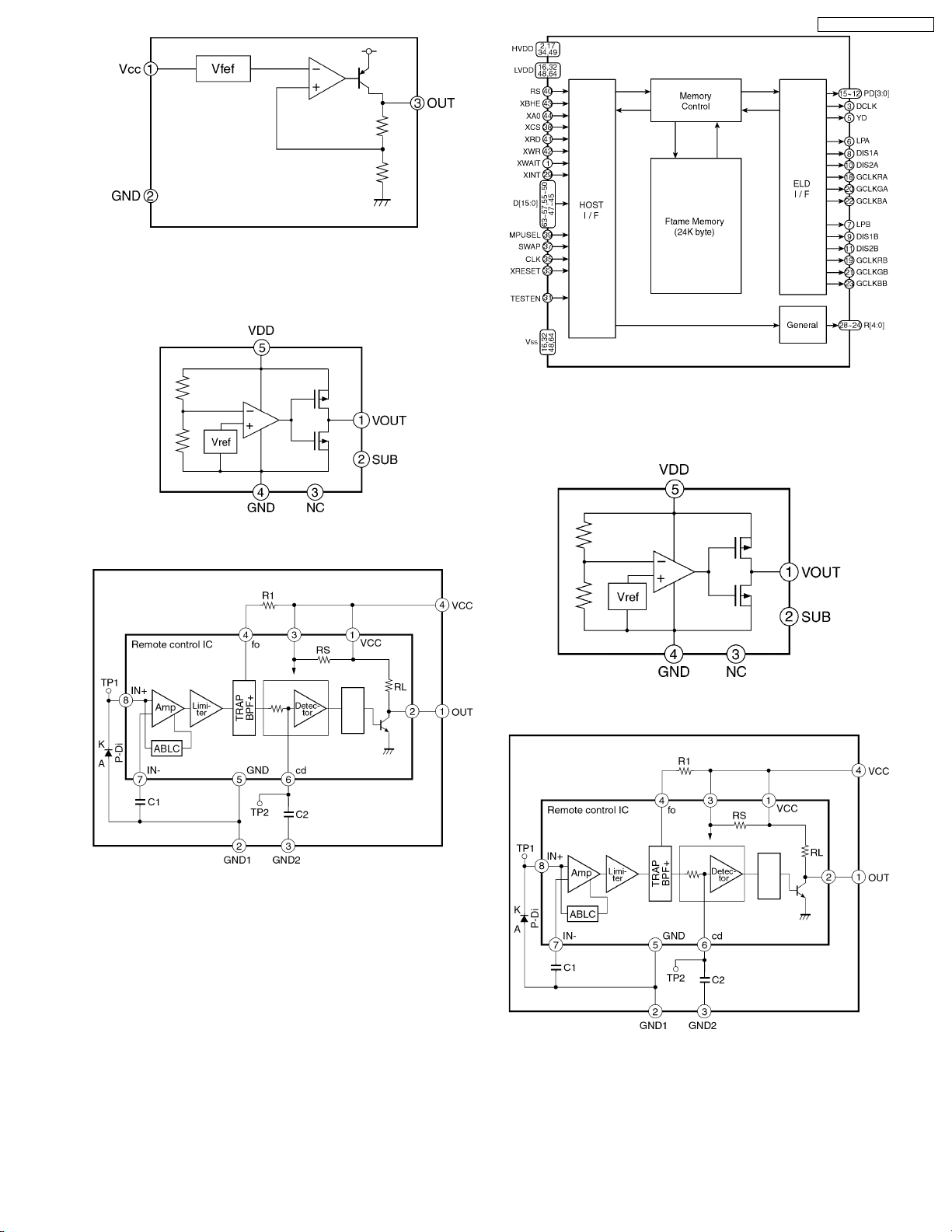

12 PACKGE AND IC BLOCK DIAGRAM

12.1. Main Block

IC201,202,301,302,401,402 : C0ABBB000184

CQ-C9901N / CQ-C9701N

IC706 : C0CBADE00034

IC651 : AN8065SE1

IC703 : YEAMPC2905E1

IC710,711 : C0CBABE00054

IC712 : C0DBEZG00002

IC704,705 : C0DAEKG00002

IC791 : C0GBG0000032

21

CQ-C9901N / CQ-C9701N

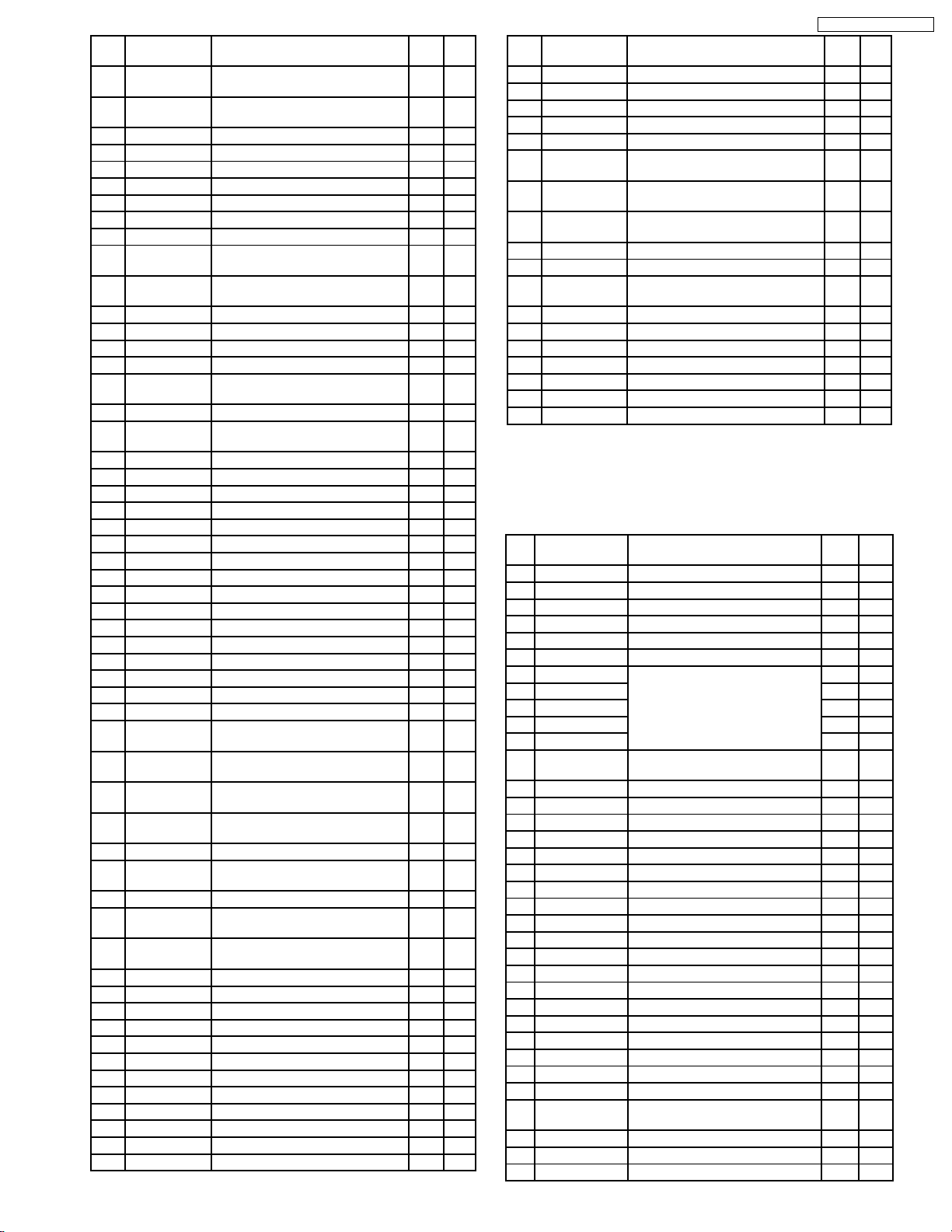

IC702 : C0DBAZG00028

IC780 : C0DBAZG00035

22

IC802 : C0CBAAG00003

12.2. Display Block [CQ-C9901N]

CQ-C9901N / CQ-C9701N

IC904 : C0HBZ0000056

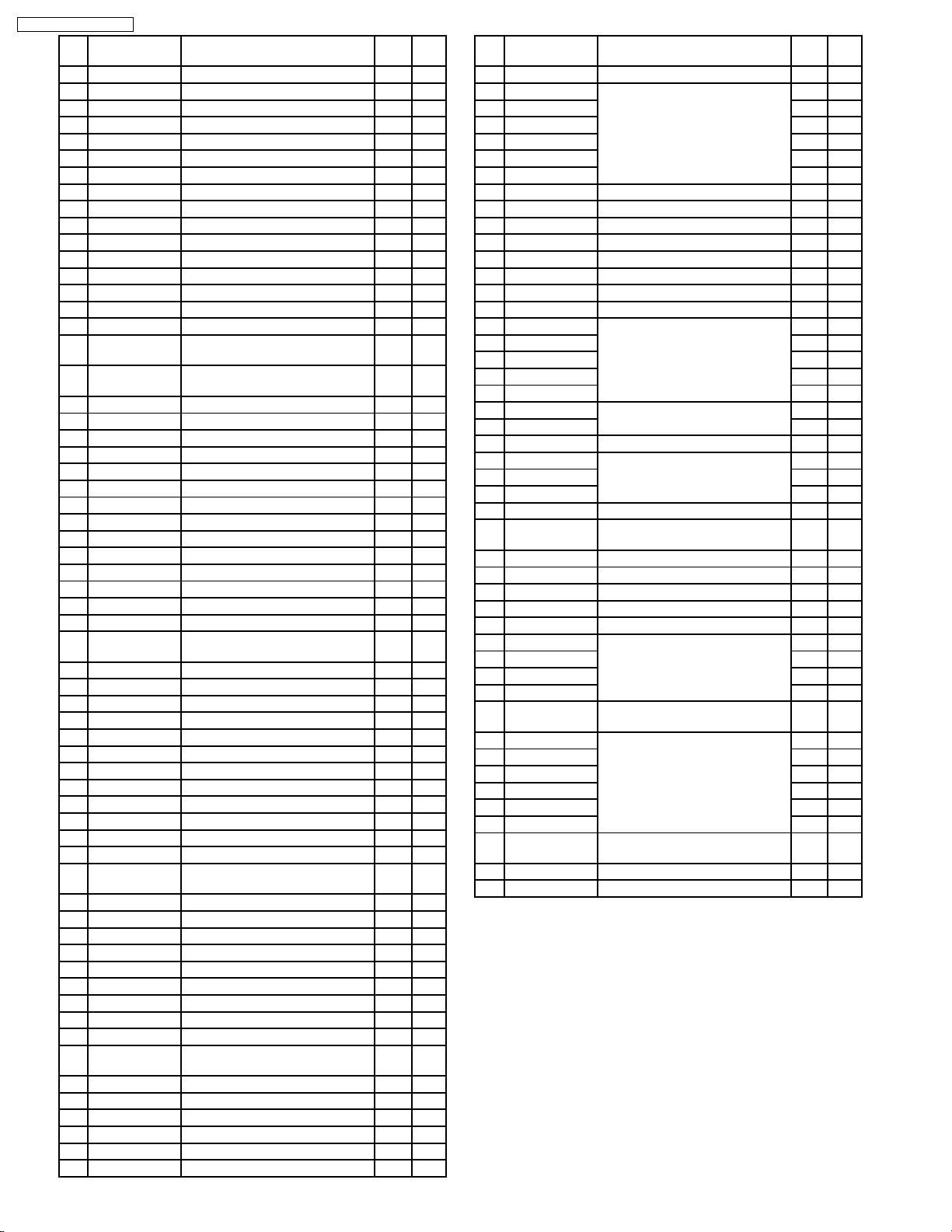

12.3. Display Block [CQ-C9701N]

IC902,907 : C0EBF0000374

IC903 : B3MBZ0000006

IC902 : C0EBF0000374

23

IC903 : B3MBZ0000006

CQ-C9901N / CQ-C9701N

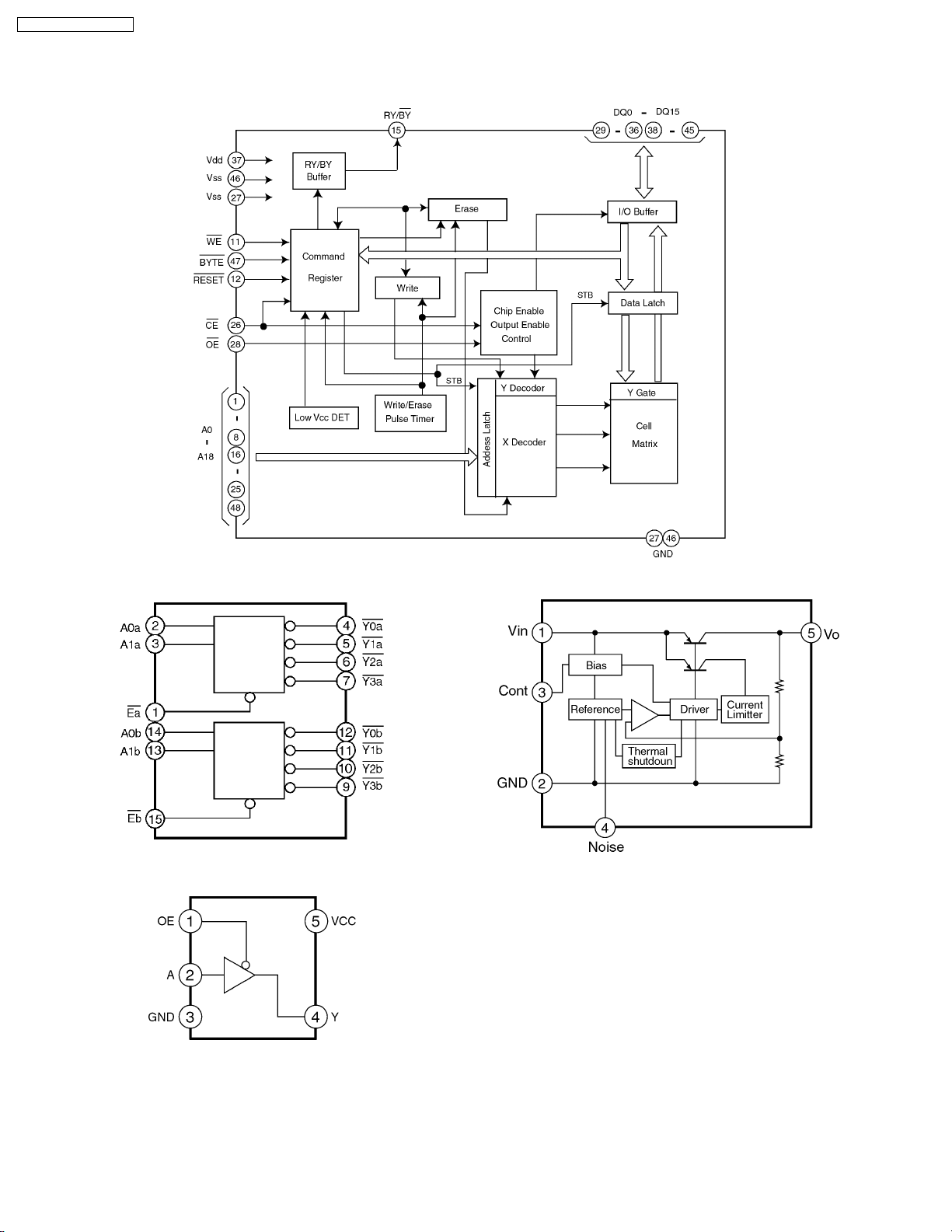

12.4. CD Servo Block

IC403 : YESAM171

IC402 : YESAM280

IC404 : YESAM178

IC405 : YESAM270

24

Loading...

Loading...