SA572

Programmable Analog

Compandor

The SA572 is a dual-channel, high-performance gain control

circuit in which either channel may be used for dynamic range

compression or expansion. Each channel has a full-wave rectifier to

detect the average value of input signal, a linearized, temperaturecompensated variable gain cell (G) and a dynamic time constant

buffer. The buffer permits independent control of dynamic attack and

recovery time with minimum external components and improved low

frequency gain control ripple distortion over previous compandors.

The SA572 is intended for noise reduction in high-performance

audio systems. It can also be used in a wide range of communication

systems and video recording applications.

Features

• Independent Control of Attack and Recovery Time

• Improved Low Frequency Gain Control Ripple

• Complementary Gain Compression and Expansion with

External Op Amp

• Wide Dynamic Range − Greater than 110 dB

• Temperature-Compensated Gain Control

• Low Distortion Gain Cell

• Low Noise − 6.0 V Typical

• Wide Supply Voltage Range − 6.0 V-22 V

• System Level Adjustable with External Components

• Pb−Free Packages are Available*

Applications

• Dynamic Noise Reduction System

• Voltage Control Amplifier

• Stereo Expandor

• Automatic Level Control

• High-Level Limiter

• Low-Level Noise Gate

• State Variable Filter

http://onsemi.com

http://onsemi.com

MARKING DIAGRAMS

16

16

1

SOIC−16 WB

D SUFFIX

CASE 751G

16

1

PDIP−16

N SUFFIX

CASE 648

16

1

TSSOP−16

DTB SUFFIX

CASE 948F

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G or G = Pb−Free Package

(Note: Microdot may be in either location)

1

16

1

16

1

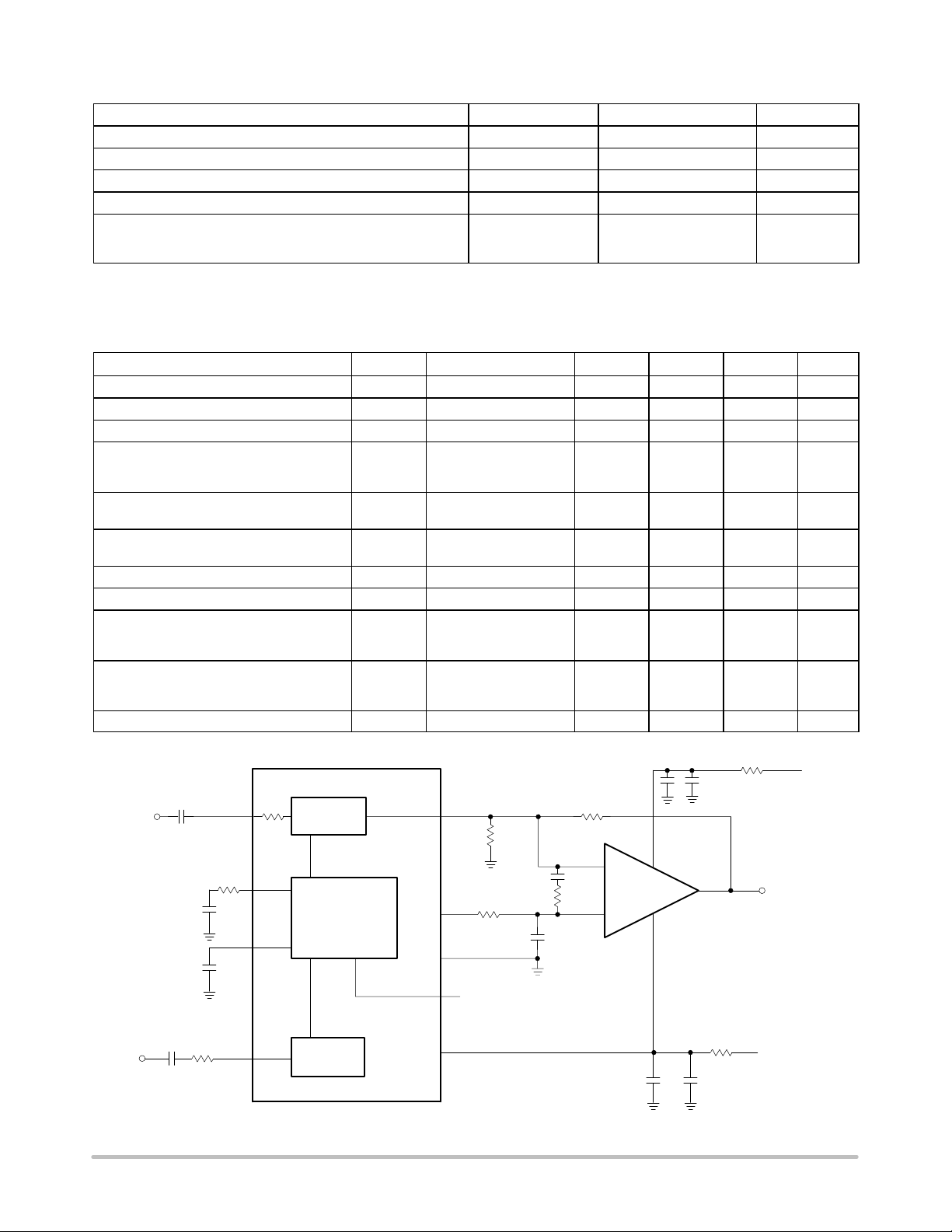

PIN CONNECTIONS

D, N, DTB Packages*

SA572D

AWLYYWWG

SA572N

AWLYYWWG

SA

572

ALYW G

G

*For additional information on our Pb−Free strategy and soldering details, please

download the ON Semiconductor Soldering and Mounting Techniques Reference

Manual, SOLDERRM/D.

© Semiconductor Components Industries, LLC, 2006

March, 2006 − Rev. 2

1 Publication Order Number:

16

V

CC

15

TRACK TRIM B

14

RECOV. CAP B

13

RECT. IN B

12

ATTACK CAP B

11

G OUT B

10

THD TRIM B

9

G IN B

G IN A

GND

1

2

3

4

5

6

7

8

TRACK TRIM A

RECOV. CAP A

RECT. IN A

ATTACK CAP A

G OUT A

THD TRIM A

*D package released in large SO (SOL) package only.

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 10 of this data sheet.

SA572/D

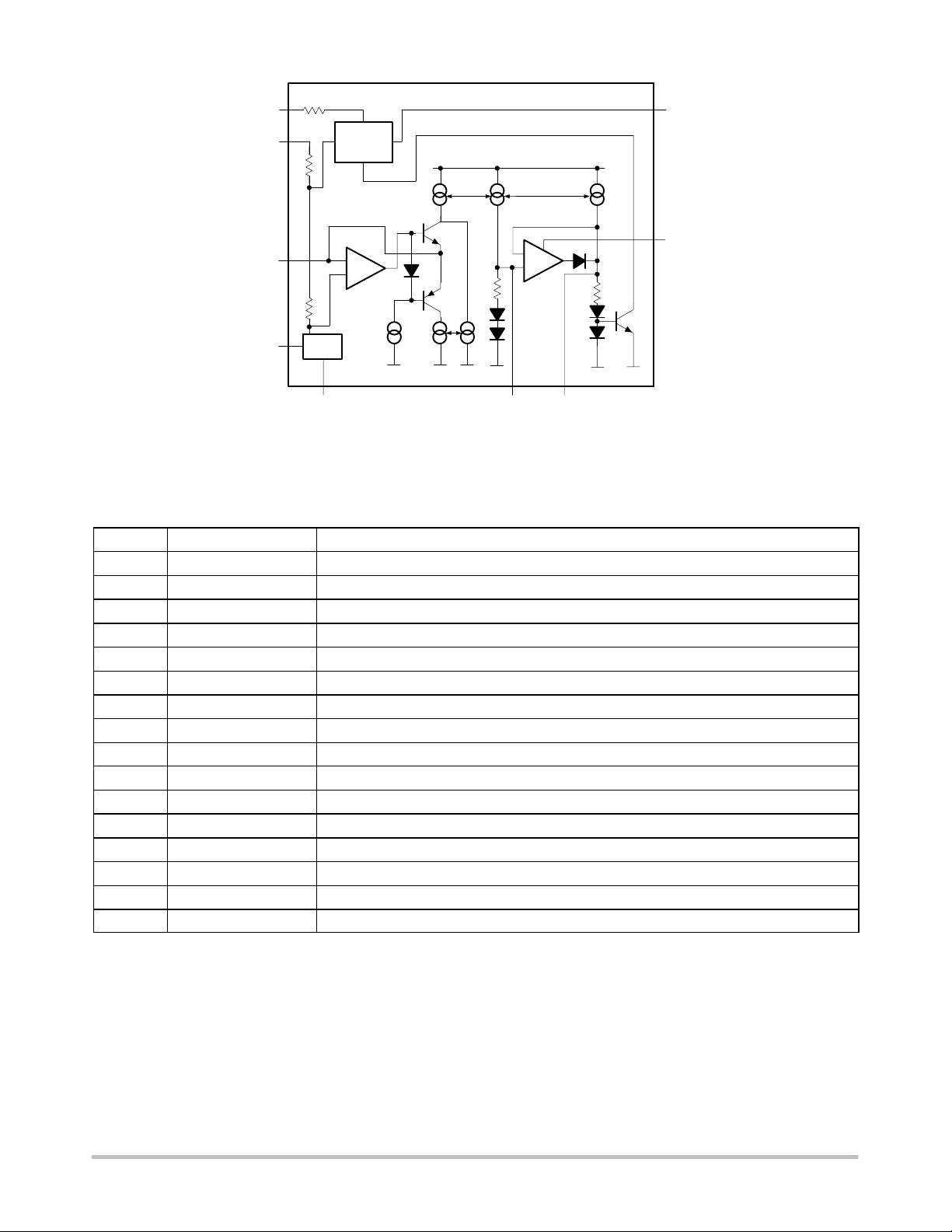

(7,9)

(6,10)

500

Ω

R

6.8k

1

SA572

(5,11)

G

GAIN CELL

(3,13)

(16)

−

+

270

Ω

RECTIFIER

P.S.

(8) (4,12) (2,14)

10k

−

+

BUFFER

Figure 1. Block Diagram

PIN FUNCTION DESCRIPTION

Pin Symbol Description

1 TRACK TRIM A Tracking Trim A

2 RECOV. CAP A Recovery Capacitor A

3 RECT. IN A Rectifier A Input

4 ATTACK CAP A Attack Capacitor A

5 G OUT A Variable Gain Cell A Output

6 THD TRIM A Total Harmonic Distortion Trim A

7 G IN A Variable Gain Cell A Input

8 GND Ground

9 G IN B Variable Gain Cell B Input

10 THD TRIM B T otal Harmonic Distortion Trim B

11 G OUT B Variable Gain Cell B Output

12 ATTACK CAP B Attack Capacitor B

13 RECT. IN B Rectifier B Input

14 RECOV. CAP B Recovery Capacitor B

15 TRACK TRIM B Tracking Trim B

16 V

CC

Positive Power Supply

(1,15)

10k

http://onsemi.com

2

SA572

MAXIMUM RATINGS

Rating Symbol Value Unit

Supply Voltage V

Operating Temperature Range T

Operating Junction Temperature T

Power Dissipation P

Thermal Resistance, Junction−to−Ambient N Package

D Package

CC

A

J

D

R

JA

DTB Package

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the

Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect

device reliability.

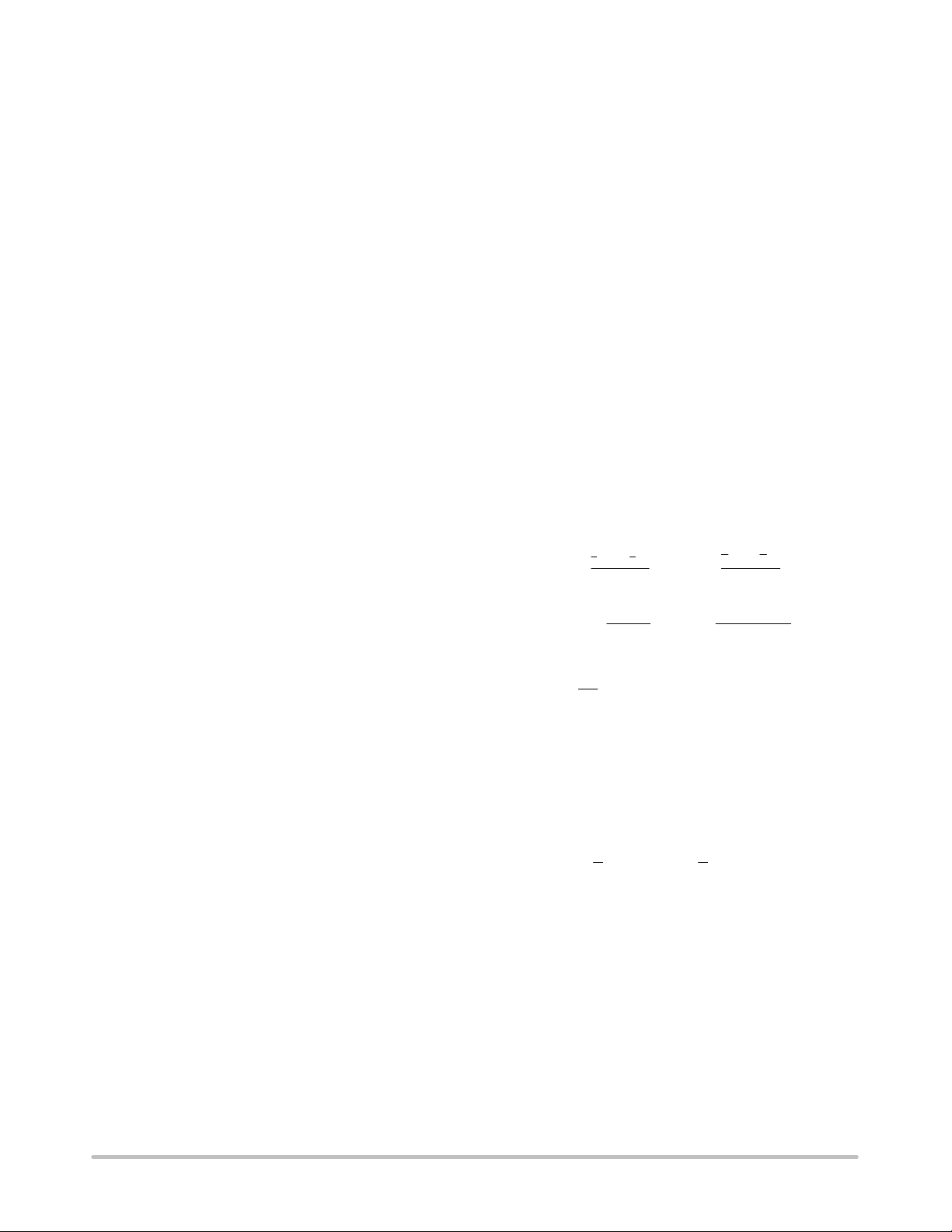

DC ELECTRICAL CHARACTERISTICS Standard test conditions, V

signals at unity gain level (0 dB) = 100 mV

at 1.0 kHz; V

RMS

1

= V2; R

= 3.3 k; R

2

= 15 V , T

CC

= 25°C; Expandor mode (see Test Circuit). Input

A

= 17.3 k unless otherwise noted.

3

Characteristic Symbol Test Conditions Min Typ Max Unit

Supply Voltage V

Supply Current I

Internal Voltage Reference V

Total Harmonic Distortion (Untrimmed)

Total Harmonic Distortion (Trimmed)

Total Harmonic Distortion (Trimmed)

CC

CC

THD

THD

THD

R

1.0 kHz, C

1.0 kHz, C

No Signal Output Noise Input to V1 and V

grounded (20−20 kHz)

DC Level Shift (Untrimmed) Input change from no

signal to 100 mV

− 6.0 − 22 V

No Signal − − 6.3 mA

− 2.3 2.5 2.7 V

A

R

100 Hz

= 1.0 F

= 10 F

2

−

−

−

− 6.0 25 V

− "20 "50 mV

RMS

Unity Gain Level − −1.5 0 +1.5 dB

Large-Signal Distortion V

Tracking Error

(Measured relative to value at unity gain) =

[V

(unity gain)] dB−V

O−VO

dB

2

V2 = +6.0 dB, V1 = 0 dB

V

2

Channel Crosstalk 200 mV

channel A, measured

= V

= 400 mV − 0.7 3.0 %

1

2

Rectifier Input

−

= −30 dB, V

RMS

= 0 dB

1

into

−

60 − − dB

output on channel B

Power Supply Rejection Ratio PSRR 120 Hz − 70 − dB

22 V

−40 to +85 °C

150 °C

500 mW

75

°C/W

105

133

0.2

0.05

0.25

1.0

−

−

"0.2

"0.5 −2.5, +1.6

DC

DC

DC

%

%

%

dB

dB

+

22F

22F

100

V

+15V

−15V

0

1F

2.2F

1%

R

17.3k

270pF

3

−

NE5234

+

0.1F

+

2.2F

V

1

C

= 10F

R

C

= 1F

A

2.2F

V

2

3.3k

R

1%

2

5

(7,9)

(3,13)

6.8k

(2,14)

(4,12)

G

BUFFER

RECTIFIER

(5,11)

(6,10)

(8)

(1,15)

(16)

1k

82k

2.2k

+

Figure 2. Test Circuit

http://onsemi.com

3

SA572

Audio Signal Processing IC Combines VCA and

Fast Attack/Slow Recovery Level Sensor

In high-performance audio gain control applications, it

is desirable to independently control the attack and

recovery time of the gain control signal. This is true, for

example, in compandor applications for noise reduction. In

high end systems the input signal is usually split into two

or more frequency bands to optimize the dynamic behavior

for each band. This reduces low frequency distortion due

to control signal ripple, phase distortion, high frequency

channel overload and noise modulation. Because of the

expense in hardware, multiple band signal processing up to

now was limited to professional audio applications.

With the introduction of the SA572 this highperformance noise reduction concept becomes feasible for

consumer hi fi applications. The SA572 is a dual channel

gain control IC. Each channel has a linearized,

temperature-compensated gain cell and an improved level

sensor. In conjunction with an external low noise op amp

for current-to-voltage conversion, the VCA features low

distortion, low noise and wide dynamic range.

BASIC APPLICATIONS

The novel level sensor which provides gain control

current for the VCA gives lower gain control ripple and

independent control of fast attack, slow recovery dynamic

response. An attack capacitor CA with an internal 10 k

resistor RA defines the attack time A. The recovery time

R of a tone burst is defined by a recovery capacitor CR and

an internal 10 k resistor RR. Typical attack time of 4.0 ms

for the high-frequency spectrum and 40 ms for the low

frequency band can be obtained with 0.1 F and 1.0 F

attack capacitors, respectively. Recovery time of 200 ms

can be obtained with a 4.7 F recovery capacitor for a

100 Hz signal, the third harmonic distortion is improved by

more than 10 dB over the simple RC ripple filter with a

single 1.0 F attack and recovery capacitor, while the

attack time remains the same.

The SA572 is assembled in a standard 16-pin dual in-line

plastic package and in oversized SOL package. It operates

over a wide supply range from 6.0 V to 22 V. Supply

current is less than 6.0 mA. The SA572 is designed for

applications from −40°C to +85°C.

Description

The SA572 consists of two linearized, temperature-

compensated gain cells (G), each with a full-wave

rectifier and a buffer amplifier as shown in the block

diagram. The two channels share a 2.5 V common bias

reference derived from the power supply but otherwise

operate independently. Because of inherent low distortion,

low noise and the capability to linearize large signals, a

wide dynamic range can be obtained. The buffer amplifiers

are provided to permit control of attack time and recovery

time independent of each other. Partitioned as shown in the

block diagram, the IC allows flexibility in the design of

system levels that optimize DC shift, ripple distortion,

tracking accuracy and noise floor for a wide range of

application requirements.

Gain Cell

Figure 3 shows the circuit configuration of the gain cell.

Bases of the differential pairs Q1-Q2 and Q3-Q4 are both

tied to the output and inputs of OPA A1. The negative

feedback through Q1 holds the VBE of Q1-Q2 and the V

BE

of Q3-Q4 equal. The following relationship can be derived

from the transistor model equation in the forward active

region.

V

(VBE = VT IIN IC/IS)

BE

Q3Q4

+

BE

Q1Q2

1

I

G

2

I

* I1* I

2

1

*

I

O

2

Ǔ

I

S

I

S

(eq. 1)

IN

Ǔ

where I

R

= 6.8 k

1

= 140 A

I

1

= 280 A

I

2

IN

V

T

+ V

+

1

1

I

)

I

G

2

I

ǒ

n

I

n

T

V

IN

R

1

O

2

Ǔ* V

I

S

I

) I

1

IN

ǒ

I

S

Ǔ

* V

I

ǒ

n

T

ǒ

I

n

T

IO is the differential output current of the gain cell and I

is the gain control current of the gain cell.

If all transistors Q1 through Q4 are of the same size,

equation 1 can be simplified to:

2

I

+

O

@ IIN@ IG*

I

2

1

ǒ

I

2

I

2

* 2I

Ǔ

@ I

1

(eq. 2)

G

The first term of equation 2 shows the multiplier

relationship of a linearized two quadrant transconductance

amplifier. The second term is the gain control feedthrough

due to the mismatch of devices. In the design, this has been

minimized by large matched devices and careful layout.

Offset voltage is caused by the device mismatch and it leads

to even harmonic distortion. The offset voltage can be

trimmed out by feeding a current source within "25 A

into the THD trim pin.

G

http://onsemi.com

4

SA572

The residual distortion is third harmonic distortion and

is caused by gain control ripple. In a compandor system,

available control of fast attack and slow recovery improve

ripple distortion significantly. At the unity gain level of

100 mV, the gain cell gives THD (total harmonic

distortion) of 0.17% typ. Output noise with no input signals

1

1

IG)

I

O I

2

2

I

O

Q

Q

4

I

G

3

THD

TRIM

is only 6.0 V in the audio spectrum (10 Hz-20 kHz). The

output current IO must feed the virtual ground input of an

operational amplifier with a resistor from output to

inverting input. The non-inverting input of the operational

amplifier has to be biased at V

if the output current I

REF

is DC coupled.

V+

1

140A

A1

V

REF

−

Q

1

I

2

2

6.8k

Q

R

1

280A

V

IN

+

O

Figure 3. Basic Gain Cell Schematic

Rectifier

The rectifier is a full-wave design as shown in Figure 4.

The input voltage is converted to current through the input

resistor R2 and turns on either Q5 or Q6 depending on the

signal polarity. Deadband of the voltage to current

converter is reduced by the loop gain of the gain block A2.

If AC coupling is used, the rectifier error comes only from

input bias current of gain block A2. The input bias current

is typically about 70 nA. Frequency response of the gain

block A2 also causes second-order error at high frequency.

The collector current of Q6 is mirrored and summed at the

collector of Q5 to form the full wave rectified output

current IR. The rectifier transfer function is:

V

* V

IN

I

+

R

REF

R

2

(eq. 3)

If VIN is AC-coupled, then the equation will be reduced

to:

I

RAC

VIN(AVG)

+

R

2

The internal bias scheme limits the maximum output

current IR to be around 300 A. Within a "1.0 dB error

band the input range of the rectifier is about 52 dB.

V

REF

V

IN

+

A2

−

R

2

Q

Q

Figure 4. Simplified Rectifier Schematic

V

* V

IN

V+

I

+

R

5

D

7

6

REF

R

2

http://onsemi.com

5

SA572

Buffer Amplifier

In audio systems, it is desirable to have fast attack time

and slow recovery time for a tone burst input. The fast

attack time reduces transient channel overload but also

causes low-frequency ripple distortion. The low-frequency

ripple distortion can be improved with the slow recovery

time. If different attack times are implemented in

corresponding frequency spectrums in a split band audio

system, high quality performance can be achieved. The

buffer amplifier is designed to make this feature available

with minimum external components. Referring to

Figure 5, the rectifier output current is mirrored into the

input and output of the unipolar buffer amplifier A3 through

Q8, Q9 and Q10. Diodes D11 and D12 improve tracking

accuracy and provide common-mode bias for A3. For a

positive-going input signal, the buffer amplifier acts like a

voltage-follower. Therefore, the output impedance of A

makes the contribution of capacitor CR to attack time

insignificant. Neglecting diode impedance, the gain Ga(t)

for G can be expressed as follows:

*t

Ga(t) + (Ga

Ga

= Initial Gain

INT

= Final Gain

Ga

FNL

= R

• CA = 10 k • C

A

A

INT

* Ga

FNL

)e

) Ga

A

A

FNL

where A is the attack time constant and RA is a 10 k

internal resistor. Diode D15 opens the feedback loop of A

for a negative-going signal if the value of capacitor CR is

larger than capacitor C

. The recovery time depends only

A

on CR • RR. If the diode impedance is assumed negligible,

the dynamic gain GR (t) for G is expressed as follows:

*t

G

(t) + (G

R

G

(t) + (G

R

= R

3

where R is the recovery time constant and RR is a 10 k

R

* G

RINT

* G

RINT

• CR = 10 k • C

R

RFNL

RFNL

)e

)e

) G

R

*t

) G

R

R

internal resistor. The gain control current is mirrored to the

gain cell through Q14. The low level gain errors due to input

bias current of A2 and A3 can be trimmed through the

tracking trim pin into A3 with a current source of "3.0 A.

3

RFNL

RFNL

V+

Q8Q

9

Q

17

V

IN

I

+

R

R

C

A

10k

Q

10

I

= 2IR

Q

2

IR

2

X2

Q

10k

−

A3

+

IR

1

D

11

D

12

TRACKING

TRIM

D

15

C

R

D

13

Q

14

16

X2

Q

18

Figure 5. Buffer Amplifier Schematic

http://onsemi.com

6

SA572

Basic Expandor

Figure 6 shows an application of the circuit as a simple

expandor. The gain expression of the system is given by:

IN(AVG)

1

2

Ǔ

(eq. 4)

R

V

V

OUT

IN

+

2

ǒ

I

(I

1

@ V

3

@

R

1

= 140 A)

2

@ R

Both the resistors R1 and R2 are tied to internal summing

nodes. R1 is a 6.8 k internal resistor. The maximum input

current into the gain cell can be as large as 140 A. This

corresponds to a voltage level of 140 A•6.8 k = 952 mV

peak. The input peak current into the rectifier is limited to

300 A by the internal bias system. Note that the value of

R1 can be increased to accommodate higher input level. R

and R3 are external resistors. It is easy to adjust the ratio of

R3/R2 for desirable system voltage and current levels. A

small R2 results in higher gain control current and smaller

static and dynamic tracking error. However, an impedance

buffer A

may be necessary if the input is voltage driven

1

with large source impedance.

The gain cell output current feeds the summing node of

the external OPA A2. R3 and A2 convert the gain cell output

current to the output voltage. In high-performance

applications, A2 has to be low-noise, high-speed and wide

band so that the high-performance output of the gain cell

will not be degraded. The non-inverting input of A

biased at the low noise internal reference Pin 6 or 10.

Resistor R4 is used to bias up the output DC level of A2 for

maximum swing. The output DC level of A2 is given by:

R

1 )

3

Ǔ

* V

R

4

V

DC + V

OUT

2

VB can be tied to a regulated power supply for a dual

REF

ǒ

supply system and be grounded for a single supply system.

CA sets the attack time constant and CR sets the recovery

time constant.

+VB

R

4

R

3

17.3k

can be

2

R

3

B

(eq. 5)

R

4

−

R

5

100k

A1

+

C

V

IN1

IN

2.2F

C

2.2F

C

IN3

2.2F

3.3k

R

IN2

2

(7,9)

(3,13)

R

6.8k

(8)

1

Figure 6. Basic Expandor Schematic

Basic Compressor

Figure 7 shows the hook-up of the circuit as a

compressor. The IC is put in the feedback loop of the OPA

A1. The system gain expression is as follows:

1

V

OUT

V

IN

+

I

1

ǒ

@

2

(I

= 140 A)

1

R

@ R

2

R

@ V

3

1

IN(AVG)

2

Ǔ

(eq. 6)

V

REF

R

+V

DC1

(5,11)

(6,10)

(2,14)

(4,12)

CC

, R

R

6

1k

C

RCA

10F1F

, and CDC form a DC feedback for A1. The

DC2

G

BUFFER

(16)

output DC level of A1 is given by:

V

DC + V

OUT

* VB@

The zener diodes D1 and D2 are used for channel

overload protection.

C

1

2.2F

REF

A2

ǒ

ǒ

1 )

R

DC1

R

DC1

) R

R

4

) R

R

DC2

V

OUT

DC2

Ǔ

4

(eq. 7)

Ǔ

http://onsemi.com

7

SA572

R

4

C

IN1

2.2F

V

IN

R

3

17.3k

C

(2,14)

C

R

10F

R

DC1

9.1k 9.1k

C

.1F

2

−

A1

1k

(6,10)

+

R

5

V

1

(5,11)

(4,12)

C

1F

A

BUFFER

(8)

REF

G

V

C

DC

10F

CC

D1D

R

1

6.8k

(16)

R

DC2

(7,9)

3.3k

2

C

2.2F

R

2

(3,13)

IN2

V

OUT

C

2.2F

IN3

Figure 7. Basic Compressor Schematic

Basic Compandor System

The above basic compressor and expandor can be

applied to systems such as tape/disc noise reduction, digital

audio, bucket brigade delay lines. Additional system

design techniques such as bandlimiting, band splitting,

1

2

V

RMS

COMPRESSION

IN

3.0 V

547.6 mV

400 mV

100 mV

10 mV

1 mV

100 V

pre-emphasis, de-emphasis and equalization are easy to

incorporate. The IC is a versatile functional block to

achieve a high performance audio system. Figure 8 shows

the system level diagram for reference.

2

EXPANDOR

REL LEVEL ABS LEVEL

OUT

+29.54

+14.77

dB dBM

+12.0

0.0

−20

−40

−60

+11.76

−3.00

−5.78

−17.78

−37.78

−57.78

−77.78

10 V

Figure 8. SA572 System Level

http://onsemi.com

8

−80

−97.78

C

1

2.2 F

SA572

ATTACK

CAP

C

A

4

+

R

3.3k

1

1 F

3, 13

4, 12

5, 11

BUFFER

6.8k

R

G

2

R

DC1

9.1k 9.1k

+

C

10 F

DC

+

C

R

RECOVERY

CAP

10 F

2, 14

C

2

+

7, 9

2.2 F

R

DC2

+

R

X

R

100k

R

C

3

V

IN

TO THD

TRIM PIN

OF 572

PINS 6, 10

+

2.2 F

3

17.3k

R

5

1k

+

22 F

C

5

Figure 9. Automatic Level Control

Automatic Level Control (ALC)

In the ALC configuration, the variable gain cell is placed

in the feedback loop of the operational amplifier and the

rectifier is connected to the input. As the input amplitude

increases above the crossover point, the overall system

gain decreases proportionally, holding the output

amplitude constant. As the input amplitude decreases

below the crossover point, the overall system gain

increases proportionally, holding the output amplitude at

the same constant level.

R1R2I

Gain +

2R3VIN(avg)

1

where: R1 = 6.8 k (Internal)

R2 = 3.3 k

R3 = 17.3 k

I1 = 140 A

The output DC level can be set using the following

equation:

R

) R

V

DC +ǒ1 )

OUT

DC1

DC2

Ǔ

V

R

4

REF

V+

2

−

5532

3

+

V−

V

1

OUT

DC

2.2 F

+

V

OUT

The output level is calculated using the following

equation:

V

OUT_LEVEL

R1R2I

+

2R

3

1

ǒ

VIN(avg)

V

IN

Ǔ

where: R1 = 6.8 k (Internal)

R2 = 3.3 k

R3 = 17.3 k

I1 = 140 A

V

IN

VIN(avg)

+

+ 1.11 (for sine waves)

Ǹ

22

Note that for very low input levels, ALC may not be

desired and to limit the maximum gain, resistor RX has

been added.

R

1)Rx

ǒ

Ǔ

·R2·I

V

Gain max. +

R

^ ((desired max gain) 26 k) * 10 k

x

REF

2R

B

3

where: R4 = 100 k

R

= R

DC1

V

REF

DC2

= 2.5 V

= 9.1 k

http://onsemi.com

9

SA572

ORDERING INFORMATION

Device Description Package Temperature Range Shipping†

SA572D 16−Pin Plastic Small Outline Package SO−16 WB −40 to +85°C 47 Units / Rail

SA572DG 16−Pin Plastic Small Outline Package

(Pb−Free)

SA572DR2 16−Pin Plastic Small Outline Package SO−16 WB −40 to +85°C 1000 / Tape & Reel

SA572DR2G 16−Pin Plastic Small Outline Package

(Pb−Free)

SA572DTB 16−Pin Thin Shrink Small Outline Package TSSOP−16* −40 to +85°C 96 Units / Rail

SA572DTBG 16−Pin Thin Shrink Small Outline Package TSSOP−16* −40 to +85°C 96 Units / Tube

SA572DTBR2 16−Pin Thin Shrink Small Outline Package TSSOP−16* −40 to +85°C 2500 / Tape & Reel

SA572DTBR2G 16−Pin Thin Shrink Small Outline Package TSSOP−16* −40 to +85°C 2500 / Tape & Reel

SA572NG 16−Pin Plastic Dual In−Line Package PDIP−16 −40 to +85°C 25 Units / Rail

SA572NG 16−Pin Plastic Dual In−Line Package

(Pb−Free)

†For information on / Tape and reel specifications, including part orientation and / Tape sizes, please refer to our / Tape and Reel Packaging

Specification Brochure, BRD8011/D.

*This package is inherently Pb−Free.

SO−16 WB −40 to +85°C 47 Units / Rail

SO−16 WB −40 to +85°C 1000 / Tape & Reel

PDIP−16 −40 to +85°C 25 Units / Rail

http://onsemi.com

10

SA572

PACKAGE DIMENSIONS

SOIC−16 WB

D SUFFIX

CASE 751G−03

ISSUE C

16 9

M

B

H8X

M

0.25

0.25 B

14X

D

B16X

M

S

A

T

e

A

q

E

_

h X 45

81

B

S

A

L

A1

SEATING

PLANE

T

C

NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES

PER ASME Y14.5M, 1994.

3. DIMENSIONS D AND E DO NOT INLCUDE

MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

5. DIMENSION B DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.13 TOTAL IN

EXCESS OF THE B DIMENSION AT MAXIMUM

MATERIAL CONDITION.

MILLIMETERS

DIM MIN MAX

A 2.35 2.65

A1 0.10 0.25

B 0.35 0.49

C 0.23 0.32

D 10.15 10.45

E 7.40 7.60

e 1.27 BSC

H 10.05 10.55

h 0.25 0.75

L 0.50 0.90

q 0 7

__

PDIP−16

CASE 648−08

ISSUE T

−A−

916

B

18

F

C

S

SEATING

−T−

PLANE

H

G

D

16 PL

0.25 (0.010) T

K

M

A

J

M

http://onsemi.com

11

NOTES:

1. DIMENSIONING AND TOLERANCING PER

ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEADS

WHEN FORMED PARALLEL.

4. DIMENSION B DOES NOT INCLUDE

MOLD FLASH.

5. ROUNDED CORNERS OPTIONAL.

L

M

DIM MIN MAX MIN MAX

A 0.740 0.770 18.80 19.55

B 0.250 0.270 6.35 6.85

C 0.145 0.175 3.69 4.44

D 0.015 0.021 0.39 0.53

F 0.040 0.70 1.02 1.77

G 0.100 BSC 2.54 BSC

H 0.050 BSC 1.27 BSC

J 0.008 0.015 0.21 0.38

K 0.110 0.130 2.80 3.30

L 0.295 0.305 7.50 7.74

M 0 10 0 10

S 0.020 0.040 0.51 1.01

MILLIMETERSINCHES

____

SA572

ÉÉ

PACKAGE DIMENSIONS

TSSOP−16

CASE 948F−01

ISSUE A

0.10 (0.004)

−T−

SEATING

PLANE

L

U0.15 (0.006) T

PIN 1

IDENT.

U0.15 (0.006) T

D

S

2X L/2

S

16X REFK

0.10 (0.004) V

M

S

U

T

S

K

K1

16

9

J1

B

−U−

1

8

J

N

A

SECTION N−N

0.25 (0.010)

M

−V−

N

F

DETAIL E

C

DETAIL E

H

NOTES:

1. DIMENSIONING AND TOLERANCING PER

ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A DOES NOT INCLUDE MOLD

FLASH. PROTRUSIONS OR GATE BURRS.

MOLD FLASH OR GATE BURRS SHALL NOT

EXCEED 0.15 (0.006) PER SIDE.

4. DIMENSION B DOES NOT INCLUDE

INTERLEAD FLASH OR PROTRUSION.

INTERLEAD FLASH OR PROTRUSION SHALL

NOT EXCEED 0.25 (0.010) PER SIDE.

5. DIMENSION K DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.08 (0.003) TOTAL

IN EXCESS OF THE K DIMENSION AT

MAXIMUM MATERIAL CONDITION.

6. TERMINAL NUMBERS ARE SHOWN FOR

REFERENCE ONLY.

7. DIMENSION A AND B ARE TO BE

DETERMINED AT DATUM PLANE −W−.

DIM MIN MAX MIN MAX

A 4.90 5.10 0.193 0.200

B 4.30 4.50 0.169 0.177

C −−− 1.20 −−− 0.047

D 0.05 0.15 0.002 0.006

F 0.50 0.75 0.020 0.030

G 0.65 BSC 0.026 BSC

H 0.18 0.28 0.007 0.011

J 0.09 0.20 0.004 0.008

J1 0.09 0.16 0.004 0.006

K 0.19 0.30 0.007 0.012

K1 0.19 0.25 0.007 0.010

L 6.40 BSC 0.252 BSC

−W−

M 0 8 0 8

____

INCHESMILLIMETERS

G

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice

to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any

liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental

damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over

time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under

its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body,

or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death

may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees,

subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of

personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part.

SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor

P.O. Box 61312, Phoenix, Arizona 85082−1312 USA

Phone: 480−829−7710 or 800−344−3860 Toll Free USA/Canada

Fax: 480−829−7709 or 800−344−3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800−282−9855 Toll Free

USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center

2−9−1 Kamimeguro, Meguro−ku, Tokyo, Japan 153−0051

Phone: 81−3−5773−3850

http://onsemi.com

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your

local Sales Representative.

SA572/D

12

Loading...

Loading...