OKI MSM64162A-xxx, MSM64162A-xxxGS-BK Datasheet

E2E0049-18-95

¡ Semiconductor MSM64162A

This version: Sep. 1998

¡ Semiconductor

MSM64162A

4-Bit Microcontroller with Built-in RC Oscillation Type A/D Converter and LCD Driver

GENERAL DESCRIPTION

The MSM64162A is a low power 4-bit microcontroller that employs Oki's original CPU core nX4/20.

The MSM64162A has 2-channel RC oscillation type A/D converter, LCD driver for up to 80

segments, and buzzer output port. It is best suited for applications such as low power, high

precision thermometers and hygrometers.

FEATURES

• Operating range

Operating frequencies : 32.768 kHz, 400 kHz

Operating voltage : 1.25 to 1.7 V (1.5 V spec.)

2.0 to 3.5 V (3 V spec.)

2.2 to 3.5 V (3 V spec., 1/2 duty)

Operating temperature : –40 to +85°C

• Memory space

Internal program memory : 2016 bytes

Internal data memory : 128 nibbles

• Minimum instruction execution time : 7.5 ms @ 400 kHz

91.6 ms @ 32.768 kHz

• RC oscillation type A/D converter : 2 channels

Time division 2-channel method

• LCD driver : 24 outputs

(1) At 1/4 duty and 1/3 bias : 80 segments (max)

(2) At 1/3 duty and 1/3 bias : 63 segments (max)

(3) At 1/2 duty and 1/2 bias : 44 segments (max)

Voltage Regulator for LCD Driver (selectable by mask option)

The LCD panel display is stable regardless of temporary supply voltage drop, because

the voltage generated by the voltage regulator for LCD driver is supplied to the bias

voltage generator as a reference voltage.

LCD Operating Voltage

When the voltage regulator for LCD driver is used

: 3.6 V (Duty cycle = 1/4 or 1/3)

2.4 V (Duty cycle = 1/2)

When the voltage regulator for LCD driver is not used

: 4.5 V (Duty cycle = 1/4 or 1/3)

3.0 V (Duty cycle = 1/2)

• Buzzer driver : 1 output (4 output modes selectable)

• Capture circuit : 2 channels

• Watchdog timer

• Clock : 32.768 kHz crystal oscillator and 400 kHz RC

oscillator (with an external resistor)

CPU clock : 32.768 kHz/400 kHz (switchable by software)

Time base clock : 32.768 kHz

• Power supply voltage : 1.5 V/3 V (selectable by mask option)

1/40

¡ Semiconductor MSM64162A

• I/O port

Input-output port : 2 ports ¥ 4 bits

Input port : 1 port ¥ 4 bits

Output port : 1 port ¥ 4 bits

(8 out of the 24 LCD driver outputs can be used

as output-only ports by mask option.)

• Interrupt sources

External interrupt : 2 sources

Internal interrupt : 7 sources

• Battery check circuit : 1 (incorporated into the input-only port)

• Package:

80-pin plastic QFP (QFP80-P-1420-0.80-BK) : (Product name : MSM64162A-¥¥¥GS-BK)

Chip : (Product name : MSM64162A-¥¥¥)

¥¥¥ indicates a code number.

2/40

¡ Semiconductor MSM64162A

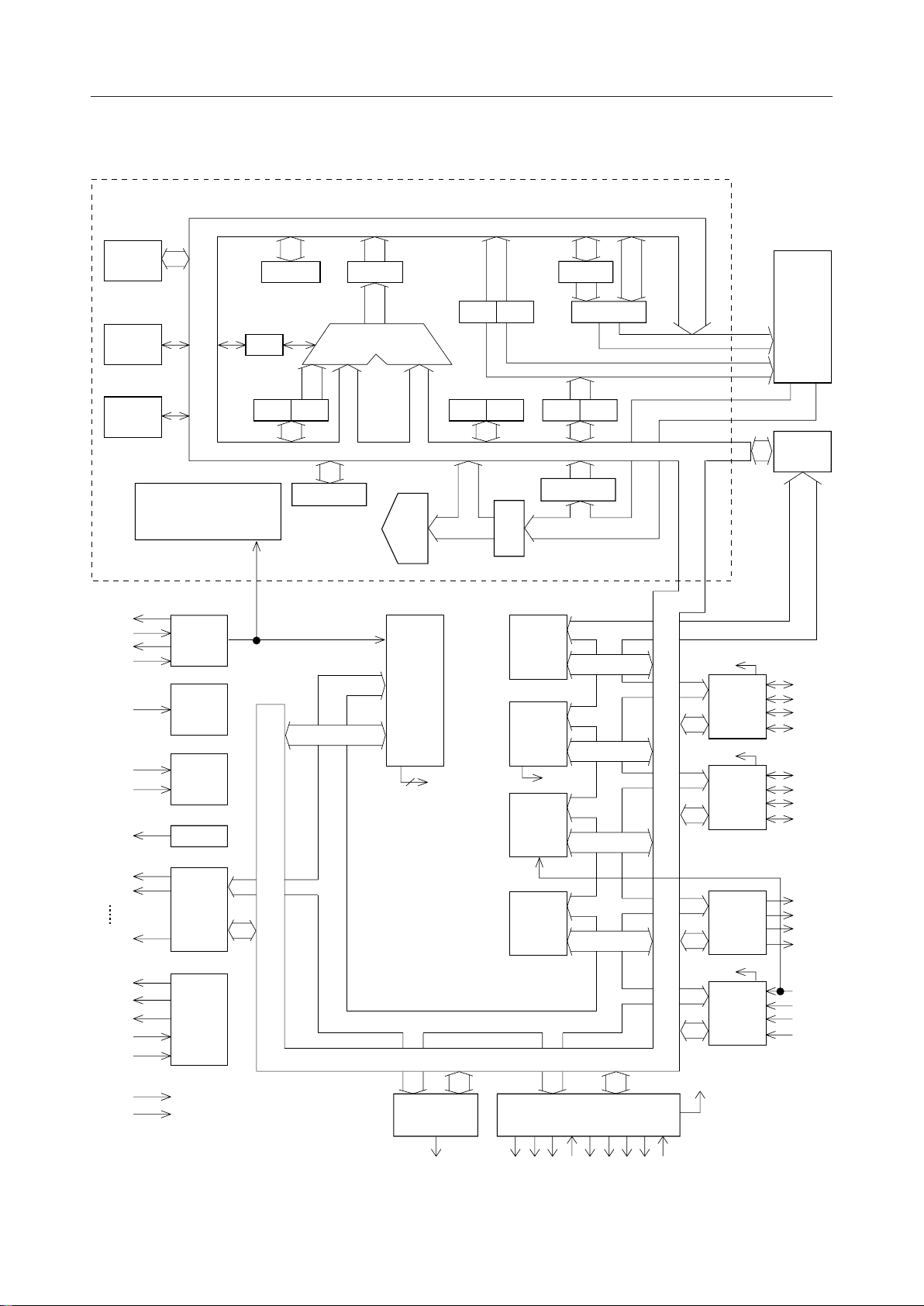

BLOCK DIAGRAM

CPU CORE: nX-4/20

OSC2

OSC1

XT

XT

RESET

TST1

TST2

V

SSL

BSR

HALT

MIEF

TIMING

CONTROLLER

2CLK

RSTG

TST

VR

TR2 TR0

(4)

C

BA H L XY

ALU

(4) (4)

PCM

PCL

TR1

PCH

DB7 to DB0 (8)

SP

IR

IR

ROMR

DECODER

TBC

INTC

WDT

5

INT

INT

BC

(8)

A11 to A8

A7 to A0

INT

PORT3

INT

PORT2

ROM

2016B

RAM

128N

P3.3

P3.2

P3.1

P3.0

P2.3

P2.2

P2.1

P2.0

V

V

V

C1

C2

V

V

L0

L1

L23

SS1

SS2

SS3

DD

SS

LCD

BIAS

PORT ADDRESS

DB7 to DB0

BD

CAPR

RT1

RS1

CS1

ADCBD

IN1

RT0

RS0

CRT0

CS0

IN0

INT

PORT1

INT

PORT0

P1.3

P1.2

P1.1

P1.0

P0.3

P0.2

P0.1

P0.0

3/40

¡ Semiconductor MSM64162A

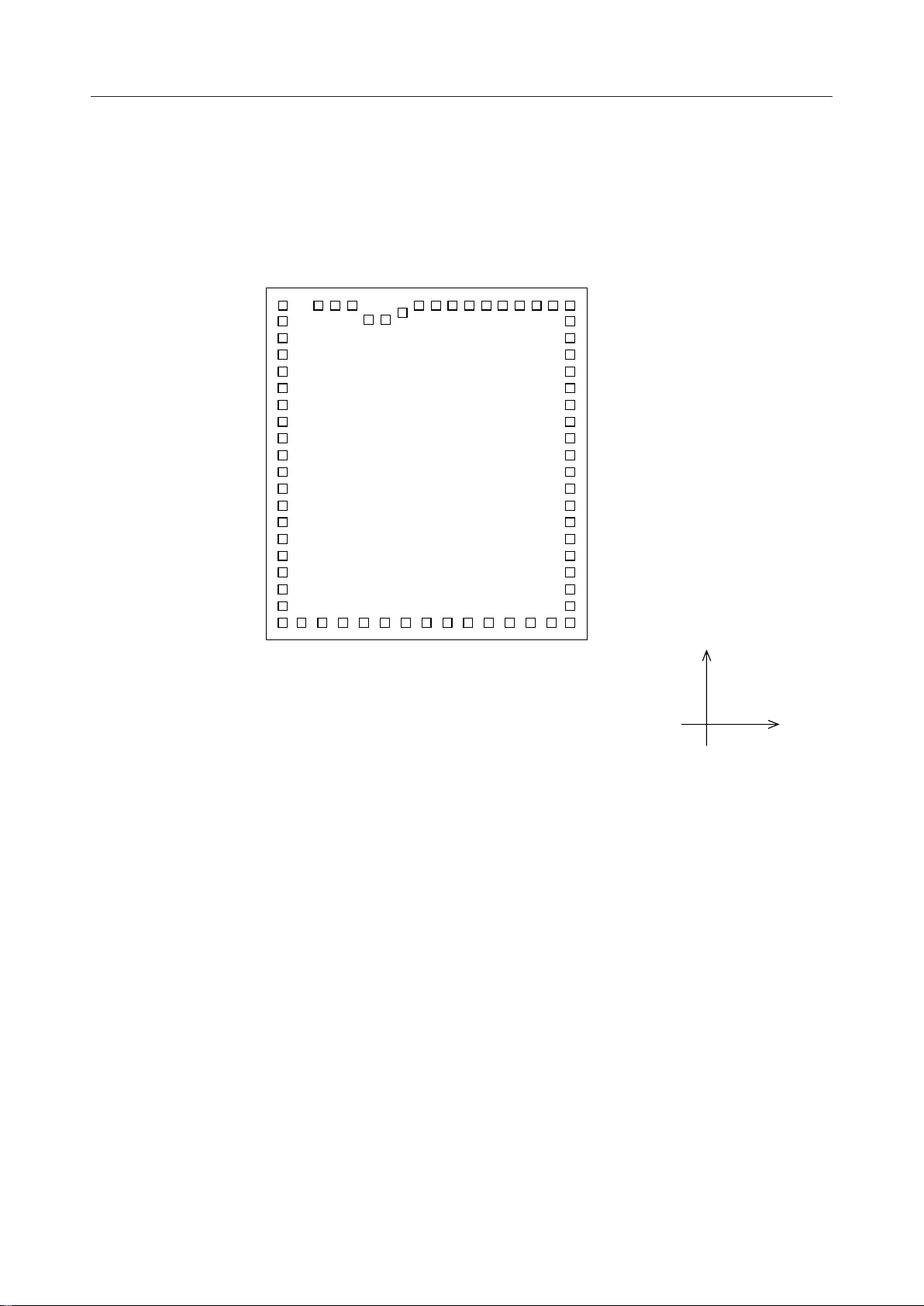

PIN CONFIGURATION (TOP VIEW)

TST2

P0.0

P0.1

P0.2

P0.3

RT0

(NC)

CRT0

RS0

CS0

IN0

IN1

CS1

(NC)

RS1

RT1

P2.0

P2.1

P2.2

P2.3

P3.0

P3.1

(NC)

P3.2

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

TST1

80

1

2

3

4

5

6

7

8

9

(NC)

RESET

78

79

77

76

75

74

73

DD

(NC)

V

(NC)

XT

XT

OSC1

OSC2

71

72

(NC)

70

L22/P6.2

L23/P6.3

68

69

L21/P6.1

(NC)

66

67

L20/P6.0

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

L19/P5.3

L18/P5.2

L17/P5.1

L16/P5.0

L15

(NC)

L14

L13

L12

L11

L10

(NC)

L9

L8

L7

L6

L5

L4

L3

L2

L1

L0

C2

C1

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

P3.3

BD

P1.0

P1.1

P1.2

P1.3

(NC)

(NC)

(NC)

SS

SS1

V

V

(NC)

V

SS2

(NC)

SSL

V

V

80-Pin Plastic QFP

Note: Pins marked as (NC) are no-connection pins which are left open.

SS3

4/40

¡ Semiconductor MSM64162A

PAD CONFIGURATION

Pad Layout

SS3

C2 33

L0 34

L1 35

L2 36

L3 37

L4 38

L5 39

L6 40

L7 41

L8 42

L9 43

L10 44

L11 45

L12 46

L13 47

L14 48

L15 49

L16 50

L17 51

L18 52

32 C1

31 V

SSL

30 V

(NC)

(NC)

(NC)

SS2

SS1

29 V

28 V

27 VSS26 P1.3

25 P1.2

24 P1.1

23 P1.0

22 BD

21 P3.3

20 P3.2

19 P3.1

18 P3.0

17 P2.3

16 P2.2

15 P2.1

14 P2.0

13 RT1

12 RS1

11 CS1

10 IN1

9 IN0

8 CS0

7 RS0

6 CRT0

5 RT0

4 P0.3

3 P0.2

2 P0.1

1 P0.0

Y

60

DD

XT 61

L19 53

L20 54

L21 55

L22 56

L23 57

OSC1 58

OSC2 59

XT 62

V

RESET 63

TST1 64

TST2 65

Chip Size : 3.96 mm ¥ 4.32 mm

Chip Thickness : 350 mm (typ.)

Coordinate Origin : Chip center

Pad Hole Size : 110 mm ¥ 110 mm

Pad Size : 120 mm ¥ 120 mm

Minimum Pad Pitch : 180 mm

Note: The chip substrate voltage is VDD.

X

5/40

¡ Semiconductor MSM64162A

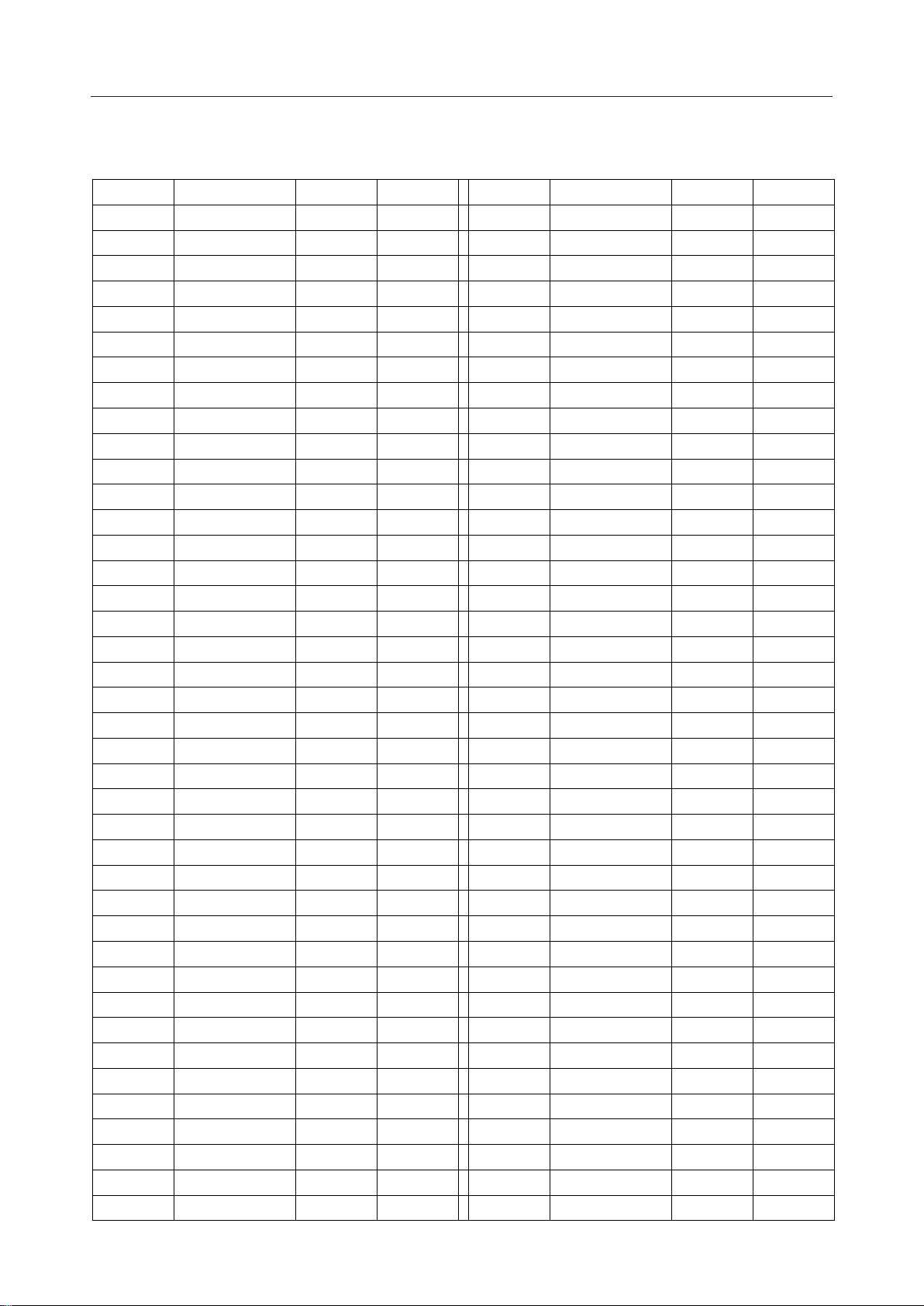

Pad Coordinates

Pad No. Y (µm)X (µm)Pad Name Pad No. Y (µm)X (µm)Pad Name

1 P0.0 1828.80 –1940.40

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20 1769.70

21 1589.70

22 1317.60

P0.1

P0.2

P0.3

RT0

CRT0

RS0

CS0

IN0

IN1

CS1

RS1

RT1

P2.0

P2.1

P2.2

P2.3

P3.0

P3.1

P3.2

P3.3

BD

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

1828.80

23 P1.0 999.30

24 P1.1 674.70

25 P1.2 354.90

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

P1.3

V

SS

V

SS1

V

SS2

V

SSL

V

SS3

C1

C2

L0

L1

L2

L3

L4

L5

L6

30.30

–231.00

–411.00

–647.10

–1289.40

–1469.40

–1649.40

–1829.40

–1829.40

–1829.40

–1829.40

–1829.40

–1829.40

–1829.40

–1829.40

–1719.30

–1539.30

–1310.10

–1048.50

–831.30

–651.30

–396.00

–208.20

–12.90

175.50

390.30

580.50

794.10

1001.70

1194.00

1374.00

1555.20

1735.20

1957.80

1957.80

1957.80

1957.80

1957.80

1957.80

1957.80

1957.80

1957.80

1957.80

1957.80

1957.80

1957.80

1957.80

1704.00

1524.00

1344.00

1111.20

919.50

739.50

559.50

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

L7

L8

L9

L10

L11

L12

L13

L14

L15

L16

L17

–1829.40

–1829.40

–1829.40

–1829.40

–1829.40

–1829.40

–1829.40

–1829.40

–1829.40

–1829.40

–1829.40 –1710.00

L18 –1829.40

L19

L20

L21

L22

L23

OSC1

OSC2

V

DD

XT

XT

RESET

TST1

TST2

–1495.20

–1226.70

–958.80

–694.80

–448.80

–243.00

24.90

300.60

480.60

660.60

979.50

1247.70

1599.90

379.50

199.50

10.20

–232.20

–412.20

–592.20

–772.20

–1008.00

–1290.00

–1470.00

–1928.10

–1957.50

–1957.50

–1957.50

–1957.50

–1957.50

–1957.50

–1957.50

–1957.50

–1957.50

–1957.50

–1957.50

–1957.50

–1957.50

6/40

¡ Semiconductor MSM64162A

PIN DESCRIPTIONS

Basic Functions

Function Symbol Pin Pad Type Description

V

DD

74

60

— 0 V power supply

Negative power supply:

V

SS

34

27

—

Ground V

Ground V

. (for 1.5 V spec.)

SS1

. (for 3.0 V spec.)

SS2

Negative power supply (for 1.5 V spec.)

Bias output for drivig LCD (–1.5 V) (for 3.0 V spec.)

Power

Supply

V

SS1

V

SS2

V

SS3

C1

C2

35

37

40

41

42

28

—

29 —

31

32

33

—

—

—

Bias output for driving LCD (–1.2 V) (when the voltage

regulator for LCD driver is used)

Negative power supply (for 3.0 V spec.)

Bias output for driving LCD (–3.0 V) (for 1.5 V spec.)

Bias output for driving LCD (–4.5 V).

Pins for connecting a capacitor for generating LCD

driving bias

Negative power supply for internal logic

V

SSL

39 30

—

(An internally generated constant voltage is present at

this pin.)

61

62

58

59

I

O

I

O

Low-speed clock oscillation input and output pins:

Connect to a crystal (32.768 kHz).

High-speed clock oscillation input and output pins:

Connect to an external resistor for oscillation (R

Input pins for testing.

A pull-up resistor is internally connected to these pins.

Oscillation

Test

XT

XT

OSC1

OSC2

TST1

TST2

76

77

71

72

80 64 I

165 I

System reset input pin.

Setting this pin to "L" level puts this device into a reset state.

Reset

RESET

79

63

I

Then, setting this pin to "H" level starts executing an

instruction from address 000H.

A pull-up resistor is internally connected to this pin.

OS

).

7/40

¡ Semiconductor MSM64162A

Basic Functions (continued)

Function Symbol Pin Pad Type Description

P0.0 2 1 I

P0.1 3 2 I

P0.2 4 3 I

P0.3 5 4 I

4-bit input port (P0):

Selectable as pull-up resistor input, pull-down resistor

input, or high impedance input by the port 01 control

register (P01CON).

As secondary functions, P0.0 to P0.3 are assigned

external interrupt functions, P0.0 and P0.1 are assigned

a capture trigger function, and P0.3 is assigned an

analog comparator input for battery check.

Ports

Buzzer

A/D

Converter

P1.0 27 23 O

P1.1 28 24 O

P1.2 29 25 O

P1.3 30 26 O

P2.0 17 14 I/O

P2.1 18 15 I/O

P2.2 19 16 I/O

P2.3 20 17 I/O

P3.0 21 18 I/O

P3.1 22 19 I/O

P3.2 24 20 I/O

P3.3/MON 25 21 I/O

26 22 O Output pin for the buzzer driverBD

RT0

CRT0

IN0

RT1

65O

86O

97ORS0 Reference resistor connection pin (for channel 0)

10 8 OCS0 Reference capacitor connection pin (for channel 0)

11 9 I Input pin for RC oscillator circuit (for channel 0)

16 13 O

15 12 ORS1 Reference resistor connection pin (for channel 1)

13 11 OCS1 Reference capacitor connection pin (for channel 1)

12 10 IIN1 Input pin for RC oscillator circuit (for channel 1)

4-bit output port (P1):

Selectable as NMOS open drain output or CMOS output

by the port 01 control register (P01CON). P1.0 is a

high current drive output port.

4-bit input-output port (P2):

Following can be specified for each bit by the port 2

control registers 0 to 3 (P20CON to P23CON): (1) input

or output, (2) pull-up/pull-down resistor input or high

impedance input, and (3) NMOS open drain output or

CMOS output.

As secondary functions, P2.0 to P2.3 are assigned

external interrupt functions.

4-bit input-output port (P3):

Following can be specified for each bit by the port 3

control registers 0 to 3 (P30CON to P33CON): (1) input

or output, (2) pull-up/pull-down resistor input or high

impedance input, and (3) NMOS open drain output or

CMOS output.

As secondary functions, P3.0 to P3.3 are assigned

external interrupt functions, P3.3 is assigned a function

that monitors the RC oscillation clock for A/D converter.

Resistance temperature sensor connection pin

(for channel 0)

Resistance/capacitance temperature sensor connection

pin (for channel 0)

Resistance temperature sensor connection pin

(for channel 1)

8/40

¡ Semiconductor MSM64162A

Basic Functions (continued)

Function Symbol Pin Pad Type Description

LCD

Driver

L1

43 34 OL0

44 35 O

45 36 OL2

46 37 OL3

47 38 OL4

48 39 OL5

49 40 OL6

50 41 OL7

51 42 OL8

52 43 OL9

54 44 OL10

55 45 OL11

56 46 OL12

57 47 OL13

58 48 OL14

60 49 OL15

LCD segment and common signals output pins.

61 50 OL16/P5.0

62 51 OL17/P5.1

63 52 OL18/P5.2

64 53 OL19/P5.3

65 54 OL20/P6.0

66 55 OL21/P6.1

68 56 OL22/P6.2

69 57 OL23/P6.3

LCD segment and common signals output pins.

Functions as output ports by mask option.

9/40

¡ Semiconductor MSM64162A

Secondary Functions

Function Symbol Pin Pad Type Description

14

15

16

17

18

19

20

21

21

1

2

3

4

4

I

I

I

O

I

Secondary functions of P0.0 to P0.3:

Level-triggered external interrupt input pins.

The change of input signal level causes an interrupt to

occur.

Secondary functions of P2.0 to P2.3 and P3.0 to P3.3:

Level-triggered external interrupt input pins.

The change of input signal level causes an interrupt to

occur.

Secondary functions of P0.0 and P0.1:

Capture circuit trigger input pins.

Secondary function of P3.3:

Monitor output pin for an RC oscillation clock for A/D

converter and a 400 kHz RC oscillation clock for the

system clock.

Secondary function of P0.3:

Analog comparator input pin for battery check.

External

Interrupt

Capture

Trigger

RC Oscillation

Monitor

Battery

Check

P0.0

P0.1

P0.2

P0.3

P2.0

P2.1

P2.2

P2.3

P3.0

P3.1

P3.2

P3.3

P0.0

P0.1

P3.3

P0.3

2

3

4

5

17

18

19

20

21

22

24

25

21

32

25

5

10/40

¡ Semiconductor MSM64162A

,

,

,

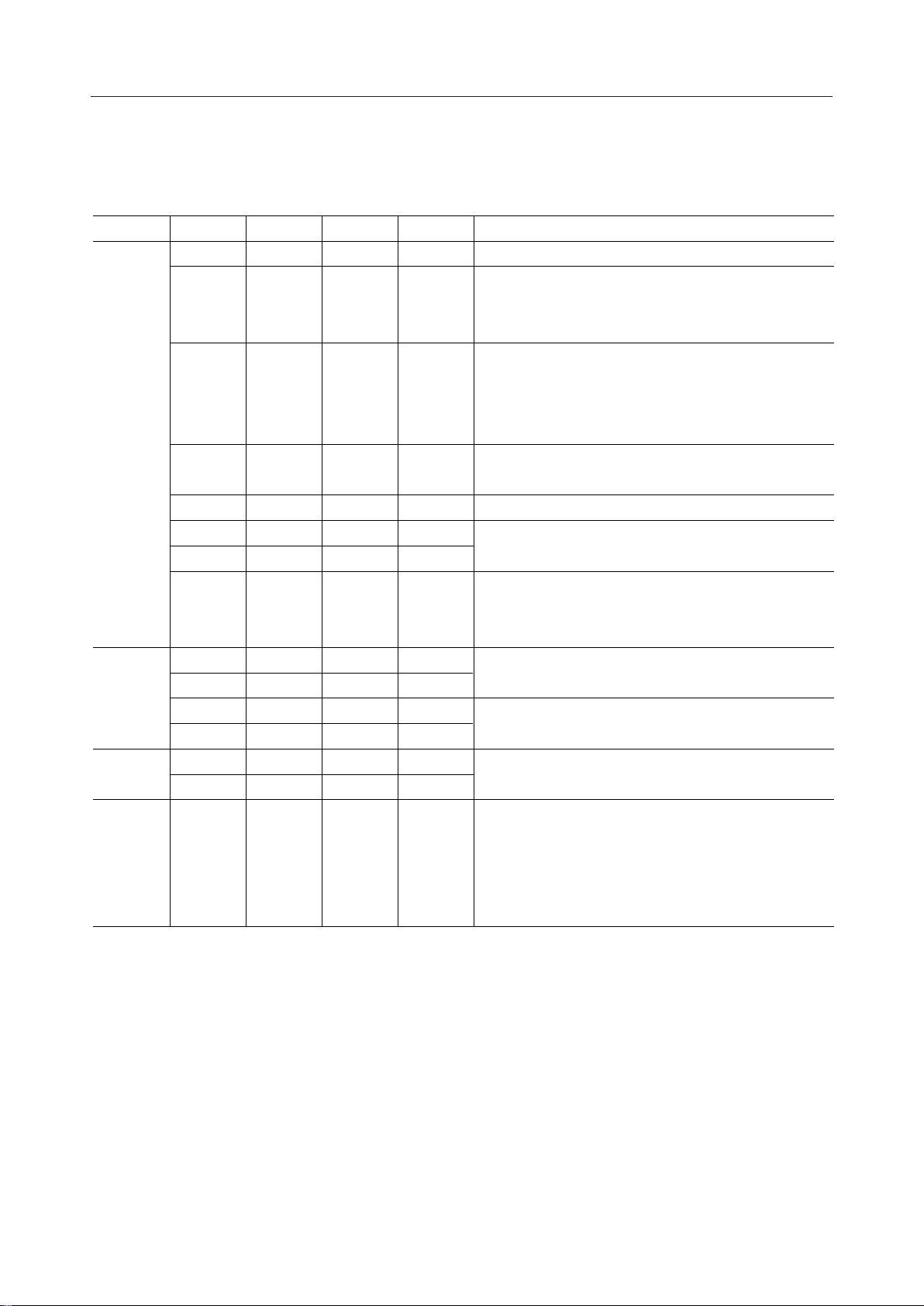

MEMORY MAPS

Program Memory

Test program area

07FFH

07E0H

03EH

,,,,,,,,,,,

,,,,,,,,,,,

,,,,,,,,,,,

Interrupt area

32 bytes

2016 bytes

03BH

038H

032H

02FH

02CH

029H

026H

023H

020H

Contents of interrupt area

Watchdog interrupt

External interrupt (0)

External interrupt (1)

ADC interrupt

256 Hz interrupt

32 Hz interrupt

16 Hz interrupt

1 Hz interrupt

4 Hz interrupt

020H

CZP area

010H

Start address

000H

8 bits

Program Memory Map

Address 000H is the instruction execution start address by the system reset.

The CZP area from address 010H to address 01FH is the start address for the CZP subroutine of

1-byte call instruction.

The start address of interrupt subroutine is assigned to the interrupt address from address 020H

to 03DH.

The user area has 2016 bytes of address 000H to address 07DFH. No program can be stored in

the test program area.

11/40

¡ Semiconductor MSM64162A

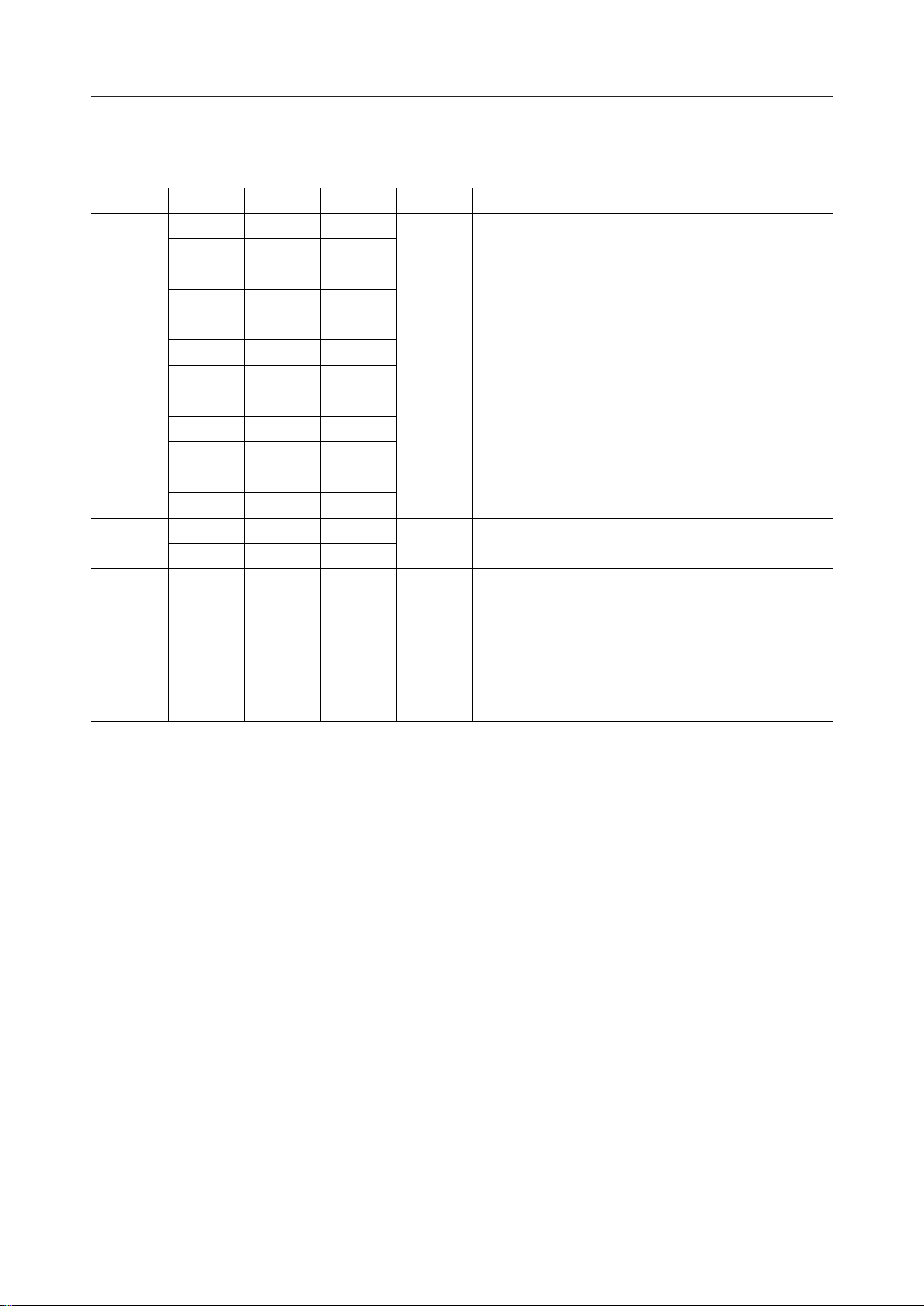

Data Memory

The data memory area consists of 8 banks and each bank has 256 nibbles (256 ¥ 4 bits).

The data RAM is assigned to BANK 7 and peripheral ports are assigned to BANK 0.

7FFH

780H

77FH

700H

BANK 7

Data RAM area

Unused area

Inaccessible area

Data/Stack area (128 nibbles)

Contents of 000H to 07FH

07FH

SFR area

100H

0FFH

080H

07FH

000H

Unused area

BANK 0

000H

4 bits

Data Memory Map

The data RAM area (128 nibbles) is shared by the stack area. The stack is a memory starting from

address 7FFH toward the low-order addresses where 4 nibbles are used by Subroutine Call

Instruction and 8 nibbles are used by an interrupt.

The addresses 080H to 0FFH of BANK 0 and the addresses 700H to 77FH of BANK 7 are not

assigned as the data memory, so access to these addresses has no effect. Moreover, it is

impossible to access BANK 1 to BANK 6.

12/40

Loading...

Loading...