OKI MSM63P180-xxxGS-BK, MSM63P180-xxxNGS-BK Datasheet

E2E0043-38-95

¡ Semiconductor MSM63P180

¡ Semiconductor

This version: Sep. 1998

Previous version: Mar. 1996

MSM63P180

4-Bit Microcontroller with Built-in 16K Word PROM and 1024-Dot Matrix LCD Drivers

GENERAL DESCRIPTION

The MSM63P180 is an M6318x series one-time-programmable ROM version product of OLMS63K family, which employs Oki's original CPU core nX-4/250.

The MSM63P180 has one-time PROM as internal program memory.

The MSM63188 and other mask ROM-version products have mask ROM as internal program

memory.

The specifications of the MSM63P180 are equal to those of the MSM63188 except for electrical

characteristics, packaging, and some functions.

The MSM63P180 is used for evaluating the software development of M6318x series products.

FEATURES

• Rich instruction set

439 instructions

Transfer, rotate, increment/decrement, arithmetic operations, comparison, logic operations,

mask operations, bit operations, ROM table reference, external memory transfer, stack

operations, flag operations, branch, conditional branch, call/return, control.

• Rich selection of addressing modes

Indirect addressing of four data memory types, with current bank register, extra bank

register, HL register and XY register.

Data memory bank internal direct addressing mode.

• Processing speed

Two clocks per machine cycle, with most instructions executed in one machine cycle.

Minimum instruction execution time : 61 ms (@ 32.768 kHz system clock)

1 ms (@ 2 MHz system clock)

• Clock generation circuit

Low-speed clock : 32.768 kHz crystal oscillator

High-speed clock : 2 MHz (Max.) RC or ceramic oscillator select

• Program memory space

16K words (PROM)

Basic instruction length is 16 bits/1 word

• Data memory space

3584 nibbles

• External data memory space

64 Kbytes (expandable by using an I/O port)

1/35

¡ Semiconductor MSM63P180

• Stack level

Call stack level : 16 levels

Register stack level : 16 levels

• I/O ports

Input ports: Selectable as input with pull-up resistance/input with pull-down resistance/

high-impedance input

Output ports: Selectable as P-channel open drain output/N-channel open drain output/

CMOS output

Input-output ports: Selectable as input with pull-up resistance/input with pull-down

resistance/high-impedance input

Selectable as P-channel open drain output/N-channel open drain

output/CMOS output

Can be interfaced with external peripherals that use a different power supply than this device

uses.

Number of ports:

Input port : 2 ports ¥ 4 bits

Output port : 6 ports ¥ 4 bits

Input-output port : 8 ports ¥ 4 bits

• Buzzer function

Buzzer output : 0.946 to 5.461 kHz (adjustable in 15 steps)

Buzzer output modes : Intermittent sound 1, 2; simple sound; continu-

ous sound

• Melody output function

Melody sound frequency : 529 to 2979 Hz

Tone length : 63 types

Tempo : 15 types

Note data : Resides in the program memory

• LCD driver

Number of segments : 1024 Max. (64 SEG ¥ 16 COM)

1/1 to 1/16 duty

1/4 or 1/5 bias (regulator built-in)

Selectable as all-on mode/all-off mode/power down mode/normal display mode

Adjustable contrast

• Multiplier/divider circuits

Multiplier : (8 bits) ¥ (8 bits) Æ Product (16 bits)

Divider : (16 bits) ÷ (8 bits) Æ Quotient (16 bits), Remainder (8 bits)

• Reset function

Reset through RESET pin

Power-on reset

Reset by low-speed oscillation halt

• Battery check

Low-voltage supply check

Criterion voltage : Selectable as 2.2 V or 2.8 V

2/35

¡ Semiconductor MSM63P180

• Power supply backup

Backup circuit (voltage multiplier) enables operation at 1.45 V minimum

• Timers and counter

8-bit timer ¥ 4

Selectable as auto-reload mode/capture mode/clock frequency measurement mode

Watchdog timer ¥ 1

Overflows in 2 sec.

100 Hz timer ¥ 1

Measurable in steps of 1/100 sec.

15-bit time base counter ¥ 1

1, 2, 4, 8, 16, 32, 64, and 128 Hz signals can be read

• Time base capture function

Captures the time base counter output values (32, 64, 128, and 256 Hz) upon the rise (fall) of

P1.0 and P1.1

• Serial port

Mode : UART mode, synchronous mode

UART communication speed : 1200 bps, 2400 bps, 4800 bps, 9600 bps

Clock frequency in synchronous mode : 32.768 kHz (internal clock mode), external

clock frequency

Data length : 5 to 8 bits

• Shift register

Shift clock : 1x or 1/2x system clock, timer 1 overflow,

external clock

Data length : 8 bits

• Interrupt sources

External interrupt : 6

Internal interrupt : 14 (watchdog timer interrupt is a nonmask-

able interrupt)

• Operating voltage

When backup used : VDD = 1.45 to 2.7 V

When backup not used : VDD = 2.7 to 5.5 V

• Package:

176-pin plastic LQFP (LQFP176-P-2424-0.50-BK)

Product name : MSM63P180-xxxGS-BK (written PROM)

MSM63P180-NGS-BK (blanked PROM)

xxx indicates a code number.

3/35

¡ Semiconductor MSM63P180

BLOCK DIAGRAM

An asterisk (*) indicates the port secondary function. indicates that the power is supplied

to the circuits corresponding to the signal names inside from V

interface).

nX-4/250

H

RESET

TST1

TST2

XT0

XT1

OSC0

OSC1

TBCCLK*

HSCLK*

TIMING

CONTROL

SP

RSP

STACK

CAL: 16-level

REG: 16-level

RST

TST

OSC

V

CB1

CB2

V

V

V

V

V

DDH

V

DD1

DD2

DD3

DD4

DD5

DD

C1

C2

CBR

EBR

ALU

INSTRUCTION

DECODER

TBCAP0*

TBCAP1*

BACKUP

BIAS

INT0*

INT1*

INT2*

INT3*

INT4*

INT

1

INT

1

INT

1

L

YX

CG

RAM

3584N

MULDIV

TBC

TBCAPR

BLD

100HzTC

WDT

RA

A

Z

MIE

IR

INT

PC

BUS

CONTROL

DATA BUS

LCLK*

FRAME*

INT

4

INT

2

INT

1

INT

1

INT5

1

INT0-4

5

PROM

16KW

EXTMEM

TIMER

8bit ¥ 4

SIO

(sync/async)

SFT

MELODY

BUZZER

INPUT

PORT

OUTPUT

PORT

I/O

PORT

LCD

&

DSPR

(power supply for

DDI

V

PP

V

DDH

D0-7*

A0-15*

RD*

WR*

TM0CAP/TM1CAP*

TM0OVF/TM1OVF*

T02CK*

T13CK*

RXC*

TXC*

RXD*

TXD*

SIN*

SOUT*

SCLK*

MD

MDB

BD

BDB

P0.0-P0.3

P1.0-P1.3

P2.0-P2.3

P3.0-P3.3

P4.0-P4.3

P5.0-P5.3

P6.0-P6.3

P7.0-P7.3

P8.0-P8.3

P9.0-P9.3

PA.0-PA.3

PB.0-PB.3

PC.0-PC.3

PD.0-PD.3

PE.0-PE.3

PF.0-PF.3

COM1-16

SEG0-63

V

DDI

V

SS

4/35

¡ Semiconductor MSM63P180

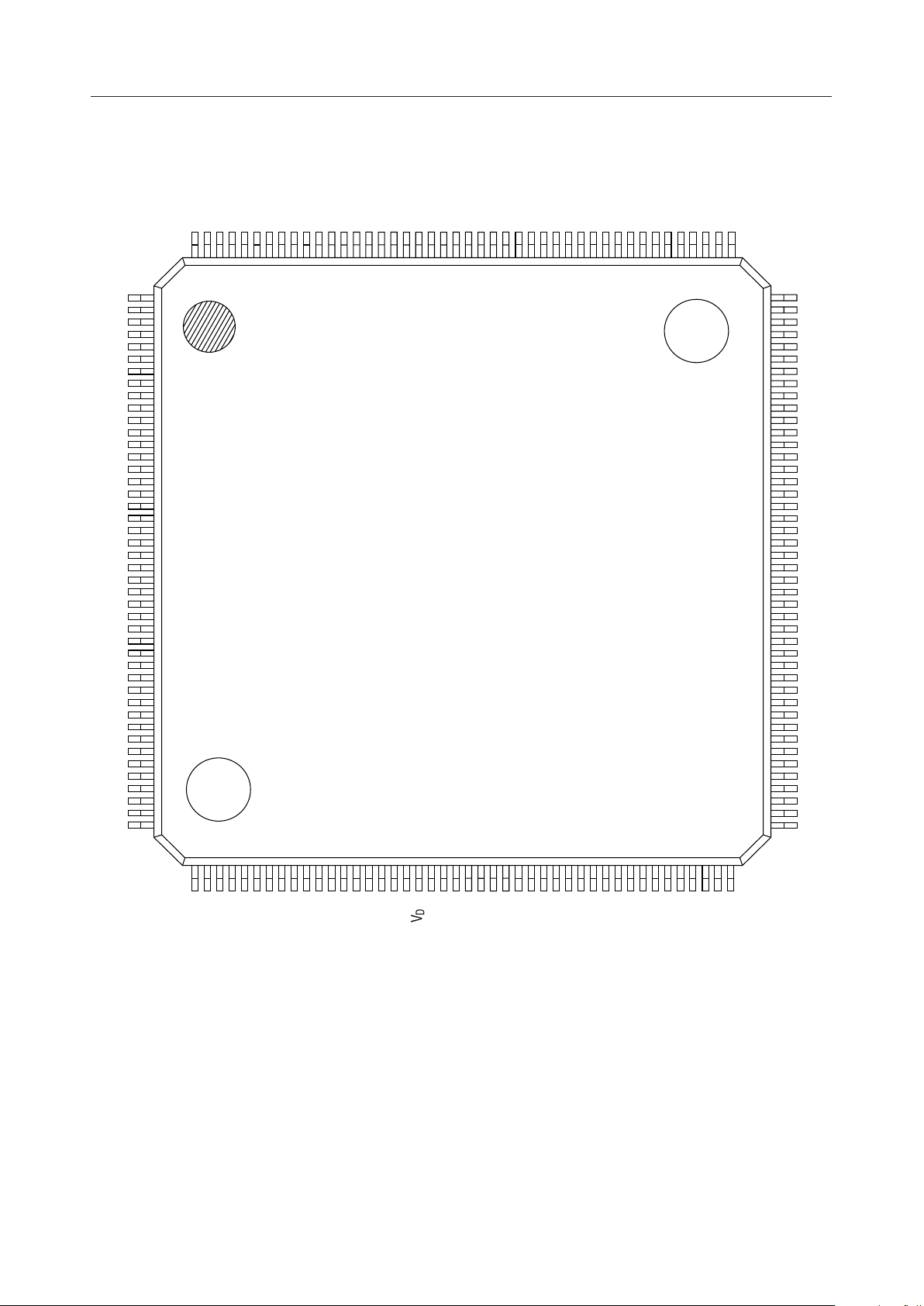

PIN CONFIGURATION (TOP VIEW)

SEG61

SEG62

SEG63

(NC)

P0.0

P0.1

P0.2

P0.3

P1.0

P1.1

P1.2

P1.3

P2.0

P2.1

P2.2

P2.3

P3.0

P3.1

P3.2

P3.3

P4.0

P4.1

P4.2

P4.3

(NC)

(NC)

SEG44

SEG45

SEG46

SEG47

SEG48

SEG49

SEG50

SEG51

SEG52

SEG53

SEG54

SEG55

SEG56

SEG57

SEG58

SEG59

SEG60

(NC)

SEG43

SEG42

SEG41

SEG40

SEG39

SEG38

SEG37

SEG36

SEG35

SEG34

SEG33

SEG32

SEG31

SEG30

SEG29

SEG28

SEG27

SEG26

SEG25

SEG24

SEG23

SEG22

SEG21

SEG20

SEG19

SEG18

SEG17

SEG16

SEG15

SEG14

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

175

176

173

172

171

170

169

168

167

1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

174

166

4546474849505152535455565758596061

165

164

163

162

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

161

160

159

62

63646566676869707172737475767778798081828384858687

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

88

99

98

97

96

95

94

93

92

91

90

89

P5.0

P5.1

P5.2

P5.3

P6.0

P6.1

P6.2

P6.3

P7.0

P7.1

P7.2

P7.3

P8.0

P8.1

P8.2

P8.3

P9.0

P9.1

P9.2

P9.3

PA.0

PA.1

PA.2

PA.3

PB.0

PB.1

PB.2

PB.3

PC.0

PC.1

PC.2

PC.3

PD.0

PD.1

PD.2

PD.3

PE.0

PE.1

PE.2

PE.3

PF.0

PF.1

PF.2

PF.3

(NC)

COM16

COM15

COM14

COM13

COM12

COM11

COM10

COM9

COM8

COM7

COM6

COM5

COM4

COM3

COM2

SS

DD1VDD2VDD3VDD4VDD5

V

V

COM1

C1

C2

DDH

V

CB1

V

CB2

DD

(NC)

OSC1

OSC0

RESET

XT1

XT0

TST2

TST1

176-Pin Plastic LQFP

Note: Pins marked as (NC) are no-connection pins which are left open.

BD

MD

BDB

PP

V

MDB

DDI

V

(NC)

5/35

¡ Semiconductor MSM63P180

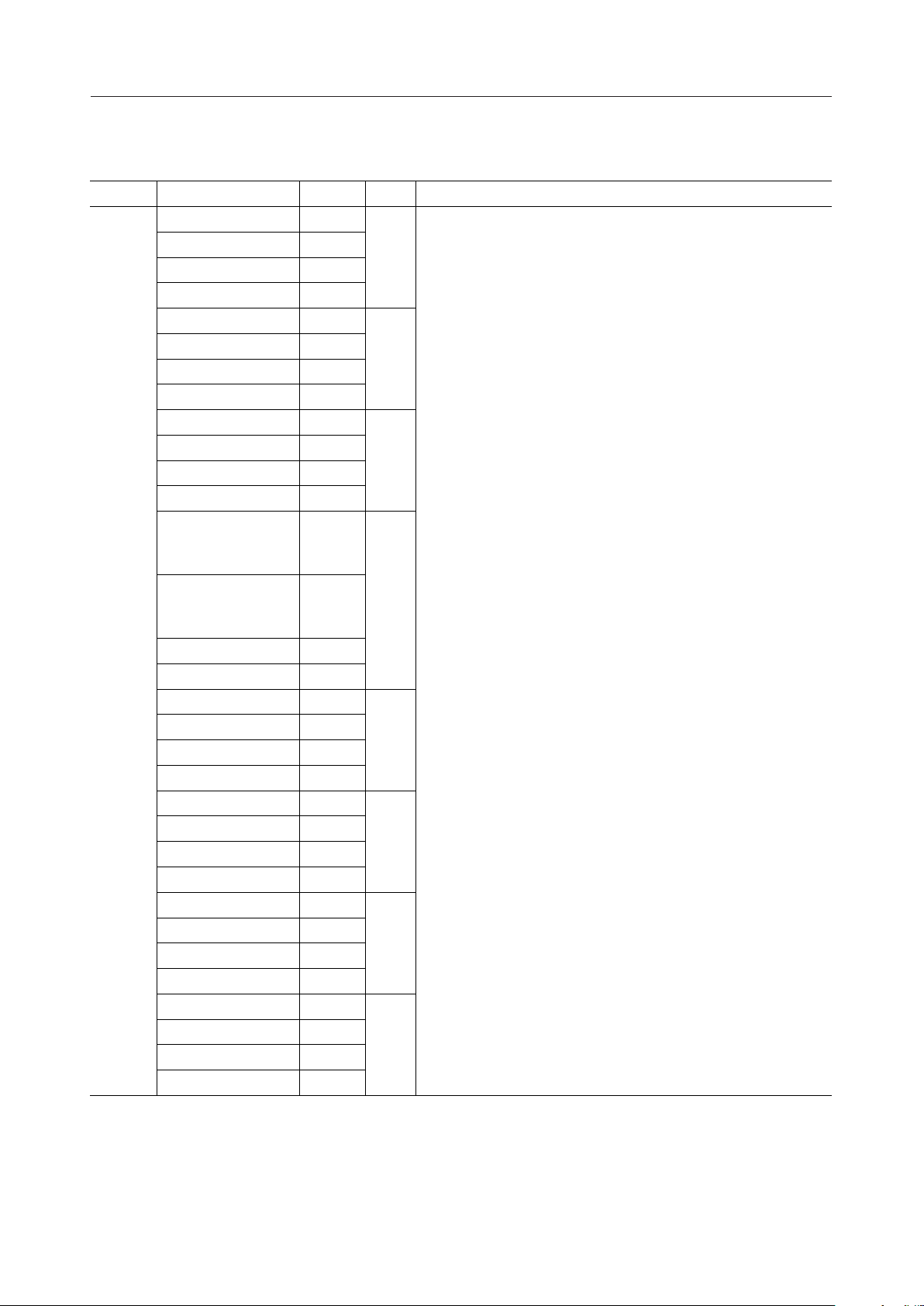

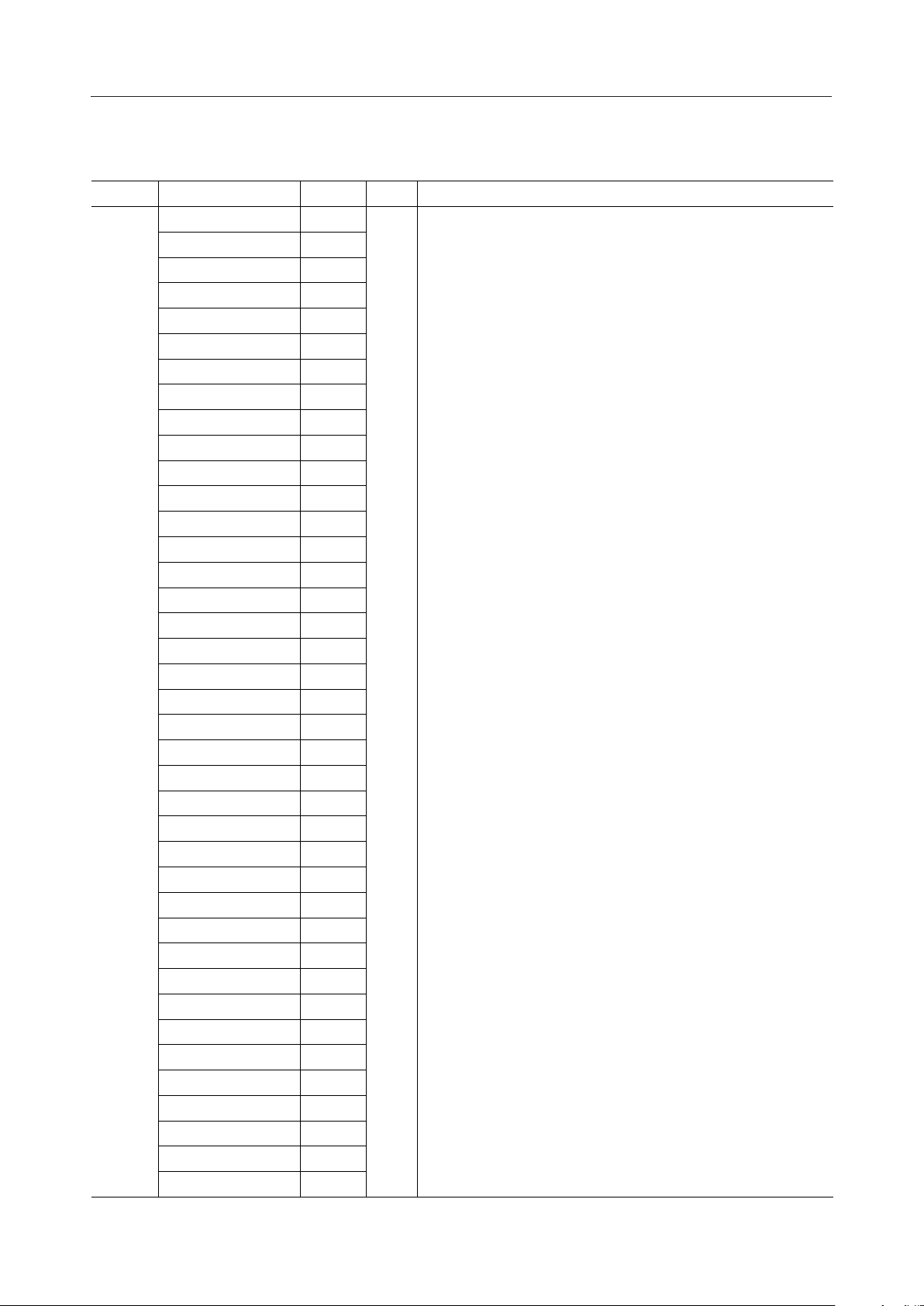

PIN DESCRIPTIONS

The basic functions of each pin of the MSM63P180 are described in Table 1.

A symbol with a slash (/) denotes a pin that has a secondary function.

Refer to Table 2 for secondary functions.

For type, "—" denotes a power supply pin, "I" an input pin, "O" an output pin, and "I/O" an inputoutput pin.

Table 1 Pin Descriptions (Basic Functions)

Function Symbol Pin Type Description

V

PP

V

DD

V

SS

V

DD1

V

DD2

V

DD3

V

DD4

V

Power

Supply

DD5

C1 68

C2 69

V

DDI

V

DDH

CB1 71 —

CB2 72 —

XT0 79 I

XT1 78 O

Oscillation

OSC0 76 I

OSC1 75 O

TST1 81 I

Test

TST2 80 I

Reset RESET 77 I

RESET 77 I

86 — Power supply (+12.5 V) for PROM writing

73 — Positive power supply

62 — Negative power supply

63

64

65 —

Power supply pins for LCD bias (internally generated).

Capacitors (0.1 mF) should be connected between these pins and

VSS.

66

67

Capacitor connection pins for LCD bias generation.

—

A capacitor (0.1 mF) should be connected between C1 and C2.

Positive power supply pin for external interface

87 —

70 —

(power supply for input, output, and input-output ports)

Voltage multiplier pin for power

supply backup (internally generated).

Pins to connect a capacitor for

voltage multiplier.

A capacitor (0.1 mF) should be

connected between CB1 and CB2.

To enable high-speed oscillation, apply

2.7 V to V

(backup OFF).

To disable high-speed oscillation, connect

a 1 mF capacitor between V

and between CB1 and CB2.

Low-speed clock oscillation pins.

A 32.768 kHz crystal should be connected between XT0 and XT1,

(12 to 30 pF) should be connected between XT0 and VSS.

and C

G

High-speed clock oscillation pins.

A ceramic resonator and capacitors (C

oscillation resistor (R

) should be connected to these pins.

OS

L0

Input pins for testing.

A pull-down resistor is internally connected to these pins.

The user cannot use these pins.

Reset input pin.

Setting this pin to "H" level puts this device into a reset state.

Then, setting this pin to "L" level starts executing an instruction

from address 0000H.

A pull-down resistor is internally connected to this pin.

with CB1 and CB2 left open

DDH

and V

DDH

, CL1) or external

SS

Buzzer

Melody

BD 82 O Buzzer output pin (non-inverted output)

BDB 83 O

MD 84 O

MDB 85 O

Buzzer output pin (inverted output)

Melody output pin (non-inverted output)

Melody output pin (inverted output)

6/35

¡ Semiconductor MSM63P180

Table 1 Pin Descriptions (Basic Functions) (continued)

Function Symbol

P0.0/INT5

P0.1/INT5

P0.2/INT5

P0.3/INT5

P1.0/INT5

P1.1/INT5

P1.2/INT5

P1.3/INT5

P2.0

P2.1

P2.2

P2.3

P3.0

P3.1

P3.2

Port

P3.3

P4.0/A0

P4.1/A1

P4.2/A2

P4.3/A3

P5.0/A4

P5.1/A5

P5.2/A6

P5.3/A7

P6.0/A8

P6.1/A9

P6.2/A10

P6.3/A11

P7.0/A12

P7.1/A13

P7.2/A14

P7.3/A15

Pin

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

132

131

130

129

128

127

126

125

124

123

122

121

Type Description

4-bit input ports.

Pull-up resistor input, pull-down resistor input, or

I

high-impedance input is selectable for each bit.

I

4-bit output ports.

P-channel open drain output, N-channel open drain output,

O

CMOS output, or high-impedance output is selectable for each

bit.

O

O

O

O

O

7/35

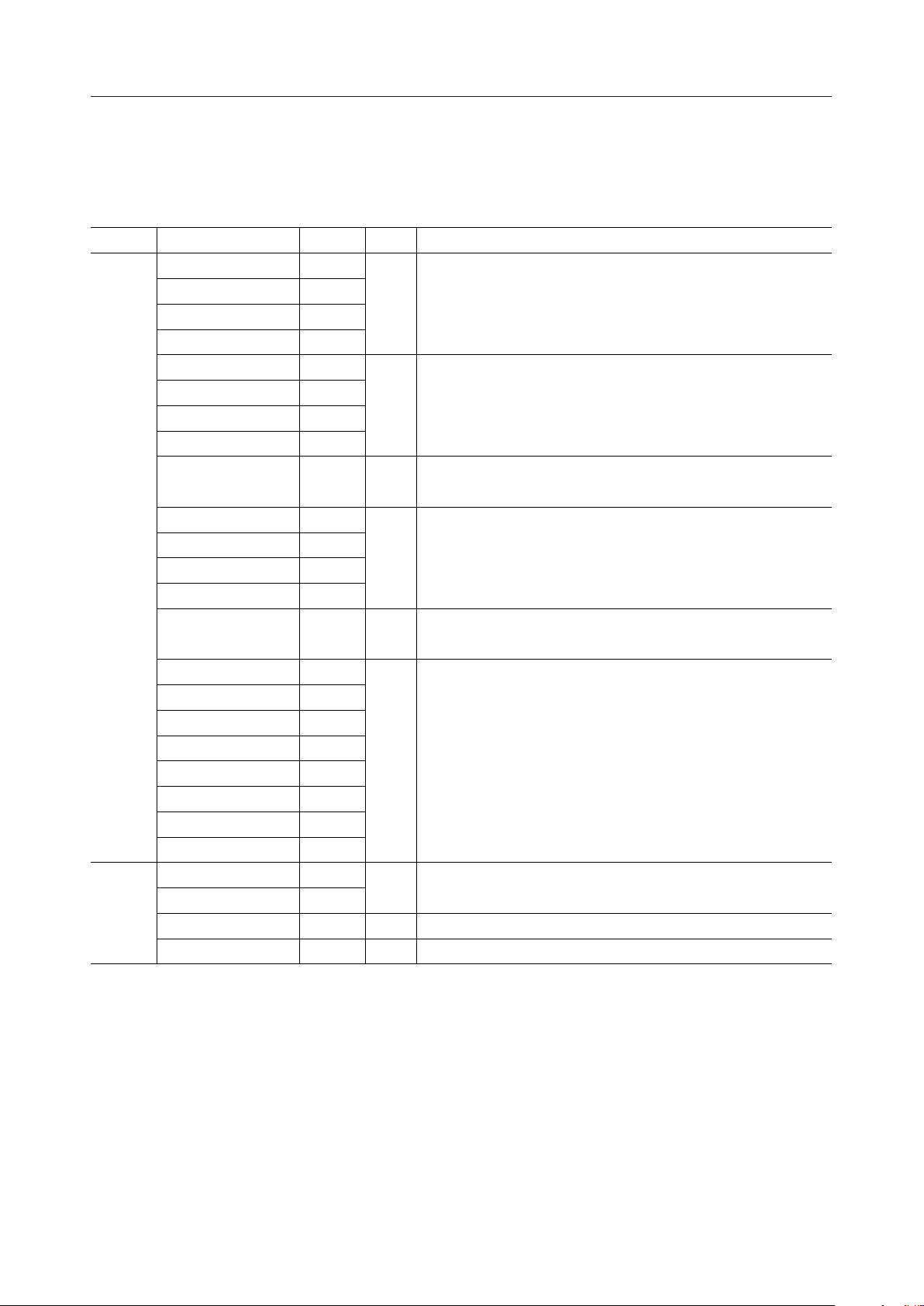

¡ Semiconductor MSM63P180

Table 1 Pin Descriptions (Basic Functions) (continued)

Function Symbol

P8.0/RD

P8.1/WR

P8.2

P8.3/INT4

P9.0/D0

P9.1/D1

P9.2/D2

P9.3/D3

PA.0/D4

PA.1/D5

PA.2/D6

PA.3/D7

PB.0/INT0/

TM0CAP/

TM0OVF

PB.1/INT0/

TM1CAP/

Port

TM1OVF

PB.2/INT0/T02CK

PB.3/INT0/T13CK

PC.0/INT1/RXD

PC.1/INT1/TXC

PC.2/INT1/RXC

PC.3/INT1/TXD

PD.0/FRAME

PD.1/LCLK

PD.2/TBCCLK

PD.3/HSCLK

PE.0/SIN

PE.1/SOUT

PE.2/SCLK

PE.3/INT2

PF.0/INT3

PF.1/INT3

PF.2/INT3

PF.3/INT3

Pin

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

Type Description

4-bit input-output ports.

In input mode, pull-up resistor input, pull-down resistor input,

I/O

or high-impedance input is selectable for each bit.

In output mode, P-channel open drain output, N-channel open

drain output, CMOS output, or high-impedance output is

selectable for each bit.

I/O

I/O

I/O

I/O

I/O

I/O

I/O

8/35

¡ Semiconductor MSM63P180

Table 1 Pin Descriptions (Basic Functions) (continued)

Function Symbol

COM1

COM2

COM3

COM4

COM5

COM6

COM7

COM8

COM9

COM10

COM11

COM12

COM13

COM14

COM15

COM16

SEG0

SEG1

SEG2

SEG3

LCD

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG20

SEG21

SEG22

SEG23

SEG24

Pin Type

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

O

O

Description

LCD common signal output pins

LCD segment signal output pins

9/35

¡ Semiconductor MSM63P180

Table 1 Pin Descriptions (Basic Functions) (continued)

Function Symbol

SEG25

SEG26

SEG27

SEG28

SEG29

SEG30

SEG31

SEG32

SEG33

SEG34

SEG35

SEG36

SEG37

SEG38

SEG39

SEG40

SEG41

SEG42

SEG43

LCD

SEG44

SEG45

SEG46

SEG47

SEG48

SEG49

SEG50

SEG51

SEG52

SEG53

SEG54

SEG55

SEG56

SEG57

SEG58

SEG59

SEG60

SEG61

SEG62

SEG63

Pin Type

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

O

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

156

Description

LCD segment signal output pins

10/35

¡ Semiconductor MSM63P180

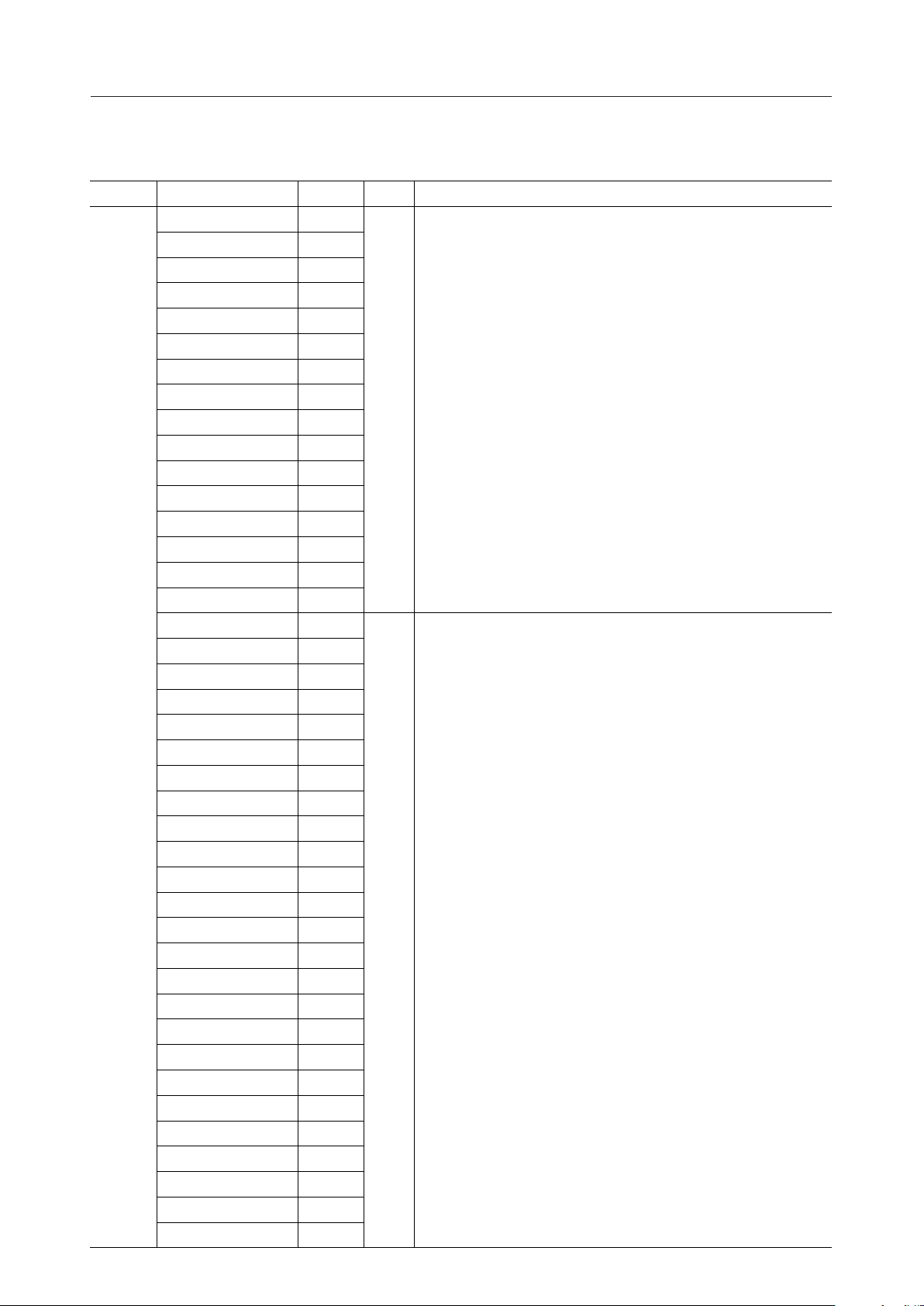

Table 2 shows the secondary functions of each pin of the MSM63P180.

Table 2 Pin Descriptions (Secondary Functions)

Function Symbol

PB.0/INT0

PB.1/INT0

PB.2/INT0

PB.3/INT0

PC.0/INT1

PC.1/INT1

PC.2/INT1

PC.3/INT1

PE.3/INT2

External

Interrupt

Capture

PF.0/INT3

PF.1/INT3

PF.2/INT3

PF.3/INT3

P8.3/INT4

P0.0/INT5

P0.1/INT5

P0.2/INT5

P0.3/INT5

P1.0/INT5

P1.1/INT5

P1.2/INT5

P1.3/INT5

P1.0/TBCAP0

P1.1/TBCAP1

PB.0/TM0CAP

PB.1/TM1CAP

Pin

108

107

106

105

104

103

102

101

93

92

91

90

89

117

154

153

152

151

150

149

148

147

150

149

108 I

107 I

Type Description

External 0 interrupt input pins.

The change of input signal level causes an interrupt to occur.

I

The Port B Interrupt Enable register (PBIE) enables or disables

an interrupt for each bit.

External 1 interrupt input pins.

The change of input signal level causes an interrupt to occur.

I

The Port C Interrupt Enable register (PCIE) enables or disables

an interrupt for each bit.

External 2 interrupt input pin.

I

The change of input signal level causes an interrupt to occur.

External 3 interrupt input pins.

The change of input signal level causes an interrupt to occur.

I

The Port F Interrupt Enable register (PFIE) enables or disables

an interrupt for each bit.

External 4 interrupt input pin.

I

The change of input signal level causes an interrupt to occur.

External 5 interrupt input pins.

The change of input signal level causes an interrupt to occur.

The Port 0 Interrupt Enable register (P0IE) and Port 1 Interrupt

Enable register (P1IE) enable or disable an interrupt for each bit.

I

I

Time base counter capture trigger input pins

Timer 0 capture trigger input pin

Timer 1 capture trigger input pin

11/35

Loading...

Loading...