OKI ML2500 Datasheet

FEDL2500-01

FEDL2500-01

¡ Semiconductor ML2500

¡ Semiconductor

This version: Jul. 2000

Previous version: Jun. 1999

ML2500

Analog-Storage Single-chip Record/Playback LSI with 1M Bit-Cell Flash Memory

This document contains minimum specifications. For full specifications, please contact your

nearest Oki office or representative.

GENERAL DESCRIPTION

Thanks to newly developed Analog Multi-Level Storage technology, ML2500 stores noncompressed analog source signal directly into on-chip 1M Bit-Cell Flash memory. The result is

superb sound quality without noise and distortions introduced through coding/decoding, and

impressive long-time record/playback capability up to 256 sec. ML2500 is fully controllable by

an external MCU via the industry's standard Serial Peripheral Interface.

In addition, no backup requirement and low operating voltage (2.7 to 3.3 V) make the LSI an ideal

choice for compact, handy and portable terminals. ML2500 is a true shingle-chip solution to

record/playback subsystem for use with today's size-critical electronic products.

FEATURES

• On-chip non-volatile 1M bit-cell Flash memory

Program/Erase Cycles : 10,000 cycles

Data Retention : 10 years

• MCU Interface

Serial Peripheral Interface (SPI; Mode 0)

• Record/Playback Time Length (With the int. Osc. or ext. clock at 8.192 MHz)

ap. 160 sec (At fsam = 6.4 kHz)

ap. 190 sec (At fsam = 5.3 kHz)

ap. 256 sec (At fsam = 4.0 kHz)

• Selectable Sampling Frequencies

4.0 kHz, 5.3 kHz, 6.4 kHz

• Maximum number of recording phrases: 320 phrases

• Phrase Control

Fully controllable with user-definable Start, Stop addresses

• Built-in LPF/Smoothing Filter (LPF attenuation –40dB/oct)

• Built-in Oscillation Circuit (8.192 MHz), No oscillator required

Optional external clock input (Clock Frequency 4.0 MHz to 8.192 MHz)

• Power Supply : 2.7 to 3.3 V

• Operating Temperature:

–10 to +70°C (guaranteed for both function and voice quality)

–40 to +85°C (guaranteed for function only) *Notice

*Notice

The voice quality can deteriorate at temperatures beyond the range of –10 to +70°C.

DC and AC characteristics in this data sheet are specified for –10 to +70°C operating

temperature range.

• Package:

32-pin Plastic TSOP (TSOPI32-P-814-0.50-1K) (Product name: ML2500TA)

1/7

FEDL2500-01

¡ Semiconductor ML2500

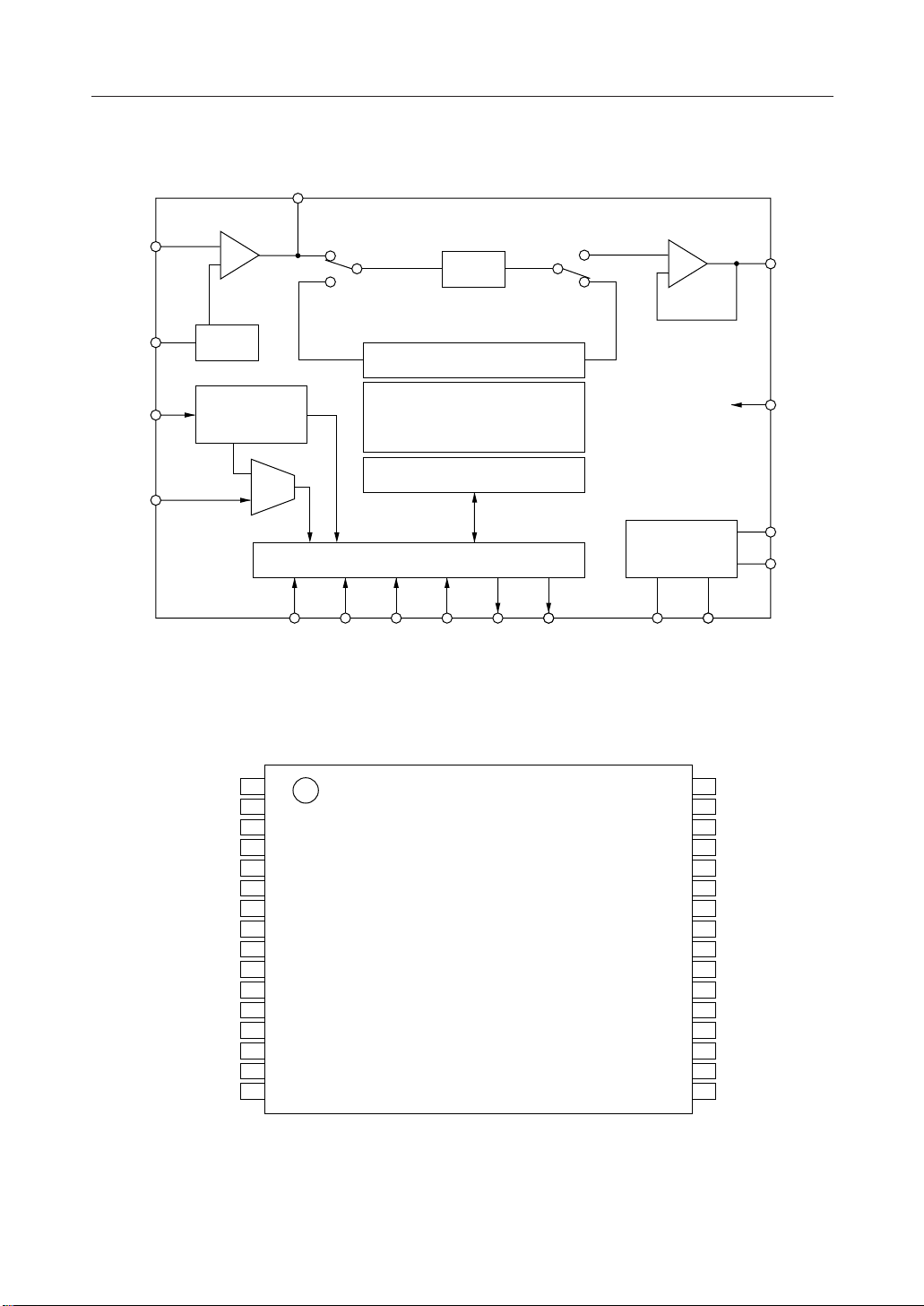

BLOCK DIAGRAM

LOUT

LIN

LPF

AOUT

SG

ROSC

EXTCLK

SG

Internal

Oscillator

MUX

Analog Write & Read Circuits

Serial Peripheral Interface & Controller

RESET

CS SCK DI DO MON DVDDDGND

PIN CONFIGURATION (TOP VIEW)

132

DV

DD

RESET

EXTCLK

TEST2

TEST2

231

330

CS

429

SCK

528

DI

627

DO

726

MON

825

924

NC

10 23

NC

11 22

12 21

NC

13 20

14 19

NC

15 18

ROSC

16 17

DGND

1M Bit Cell

Analog Storage Flash

Memory Array

Address Decoder

Power

Supplies

AV

DD

LIN

LOUT

TEST2

TEST2

AOUT

SG

NC

TEST1

NC

TEST2

NC

TEST2

NC

TEST2

AGND

TEST1

AV

DD

AGND

NC: No connection. Keep NC pins open.

32-Pin Plastic TSOP (Type

11

1)

11

2/7

FEDL2500-01

¡ Semiconductor ML2500

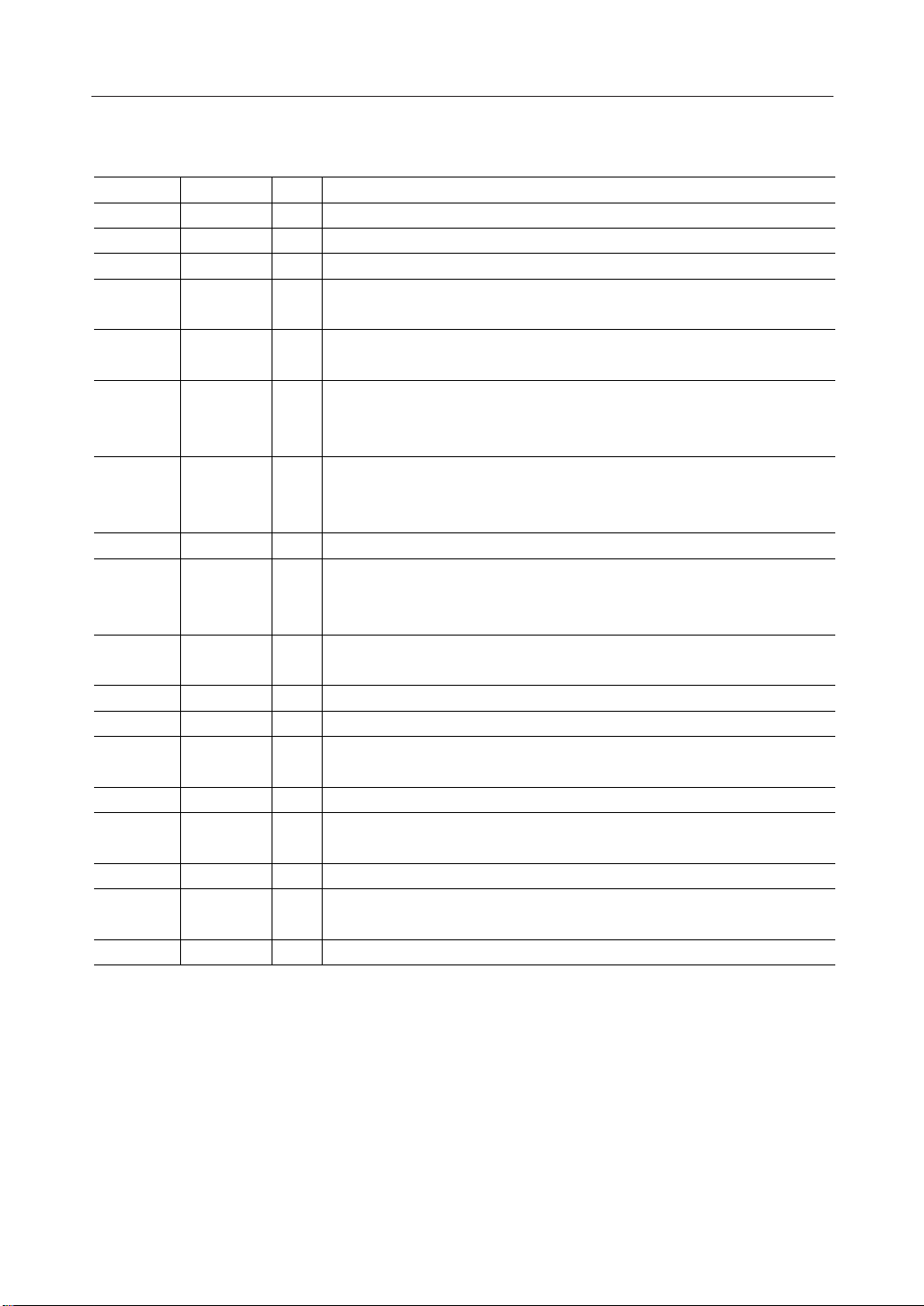

PIN DESCRIPTIONS

Pin

5

3

2

15

8

7

26

31

20, 22, 28, 29

24

1

32

Symbol Type Description

DI I Serial input pin for command data.

DO O Serial output pin for status data.6

SCK I Shift clock input pin for the DI and the DO pins.4

CS I

RESET I

ROSC I

EXTCLK I

MON O Output "H" level during recording/playback operation.

SG O

LIN I

LOUT O Output pin from the internal OP amplifier.30

AOUT O Analog waveform output. Connect to an amplifier to drive a SP.27

TEST2 O

TEST1 I LSI's testing pin. Must be connected to DGND.

DV

DD

DGND — Digital Ground pin.16

AV

DD

AGND — Analog Ground pin.17

Chip select pin. "L" level input enables data input/output through the serial

interface.

RESET input pin, resetting the serial interface circuit only. "L" level input to

this pin initializes the serial interface. Must input "L" pulse after each power-on.

Insert a 30 kW resistor (Precision within ±1%) between this pin and the DGND pin.

The same resistor should also be inserted if an external clock is used.

The resistor value determines the frequency of the clock for control in this device.

External clock input pin. Allowable clock frequency range is 4.0 MHz to 8.192

MHz. When external clock is unused and internal oscillation clock in used,

connect this pin to the DGND.

Analog reference voltage (Signal Ground Voltage) output pin. It is

recommendable to insert a capacitor smaller than 3300 pF between this pin and

the AGND pin. Loads except for capacitors should not be connected to this pin.

Inverting input pin for the internal OP amplifier. Non-inverting input pin is

internally connected to SG voltage.

Pins for testing the LSI. Must be held "OPEN".11, 13, 18,

Digital power supply pin. Insert a 0.1 mF or larger by-pass capacitor between

—

this pin and the DGND pin .

Analog power supply pin. Insert a 0.1 mF or larger by-pass capacitor between

—

this pin and the AGND pin.

3/7

Loading...

Loading...