OKI ML2201-XXX Datasheet

FEDL2201-01

1

Semiconductor

This version: Mar. 2000

ML2201-XXX

Speech Synthesizer LSI with on-chip 384K Mask ROM

GENERAL DESCRIPTION

The ML2201 is a PCM-based speech synthesizer LSI having an on-chip 384K Mask ROM, D/A Converter and

Low Pass Filter. Utilizing the serial interface enables smaller footprint packaging, which makes the chip an ideal

choice for a pre-recorded message subsystem used with today’s size-critical applications.

FEATURES

•

Sampling Frequency (Selectable for each single phrase)

4.0/5.3/6.4/8.0/10.6/12.8/16.0 kHz

•

On-chip 384 Kbit Mask ROM

•

Maximum Playback Time (At f

12.0 sec At f

6.0 sec At f

3.0 sec At f

•

External Clock Frequency Range

f

= 3.5 to 4.096 MHz (Typ.) to 17.0 MHz

EXTCLK

•

On-chip Phrase Control Table

•

Maximum Number of Phrase s: 31 Phrases

•

Built-in 10-bit Current-Output Type D/A Converter

•

Built-in LPF

•

Packaging: 8-pin Plastic SSOP (SSOP8-P-44-0.65-K)

(Product Code: ML2201-XXX MBZ060)

•

Power Supply Voltage: +2.0 to +5.5 V

= 4.0 kHz

SAM

= 8.0 kHz

SAM

= 16.0 kHz

SAM

= 4.096 MHz)

EXTCLK

*

*

Note: As of February 2000, ceramic oscillation on this chip is under development and thus the chip is not

functional with a ceramic oscillator. The manufacturer intends to add a ceramic oscillation option to the

chip. For more information on availability in commercial quantity, contact your sales representative.

1/20

Semiconductor

1

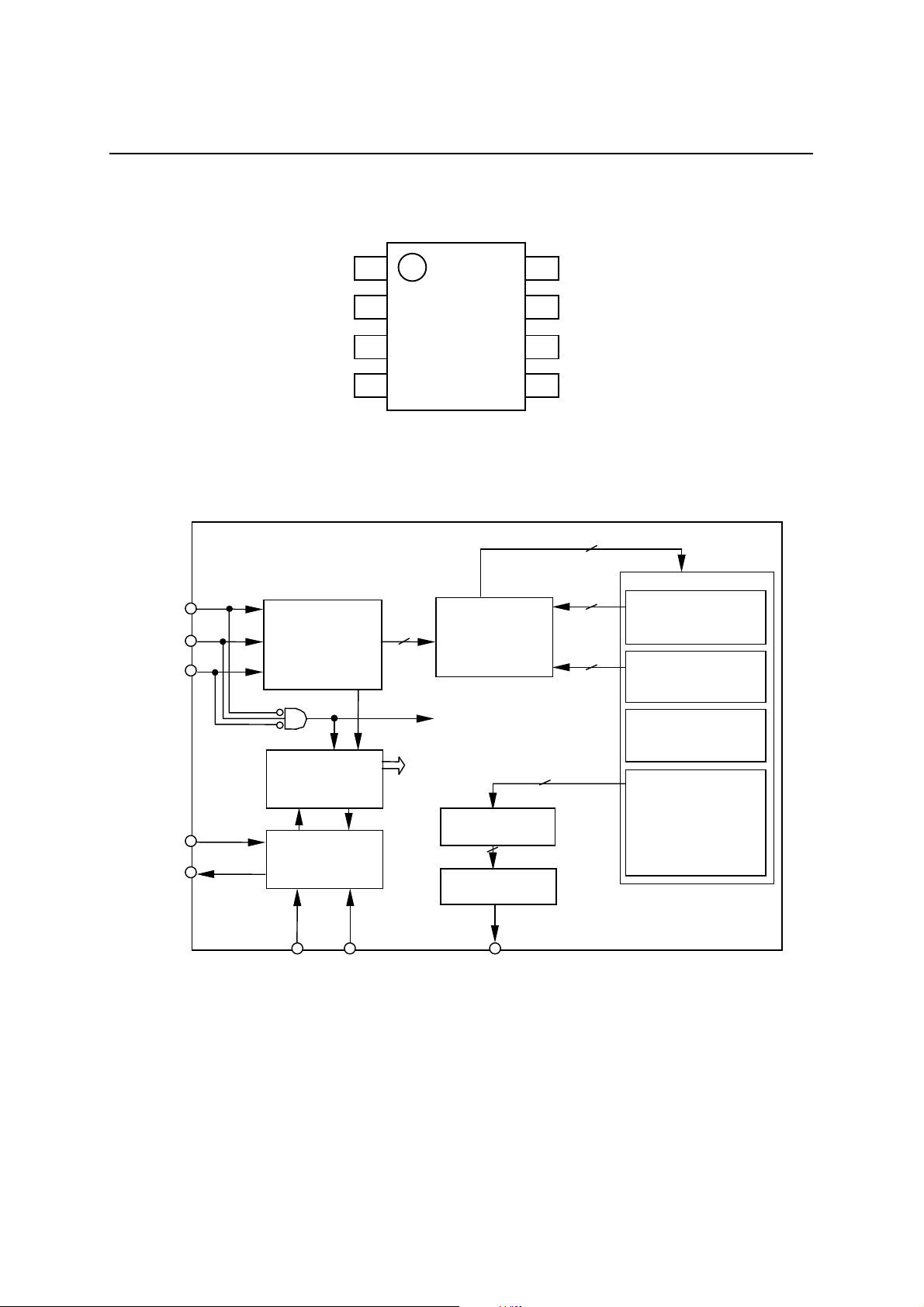

PIN LAYOUT (TOP VIEW)

FEDL2201-01

ML2201–XXX

BLOCK DIAGRAM

ST

PI

PDWN

ST

PI

GND

AOUT

Serial

Interface

1

2

3

4

8-Pin Plastic SSOP

5

16 bit Address

controller

PDWN

8

XT

7

6

XT

5

V

DD

16

384 Kbit ROM

8

Edit ROM 2 Kbit

(Phrase Control Table)

8

Address ROM 2 Kbit

(Phrase Address Table)

XT

XT

Timing

Controller

OSC

Circuit

DD

Reset, Power Down

8

PCM

Synthesizer

10

10 bit DAC

LPF

AOUTGNDV

Test ROM 2 Kbit

PCM data Area

378 Kbit

2/20

Semiconductor

1

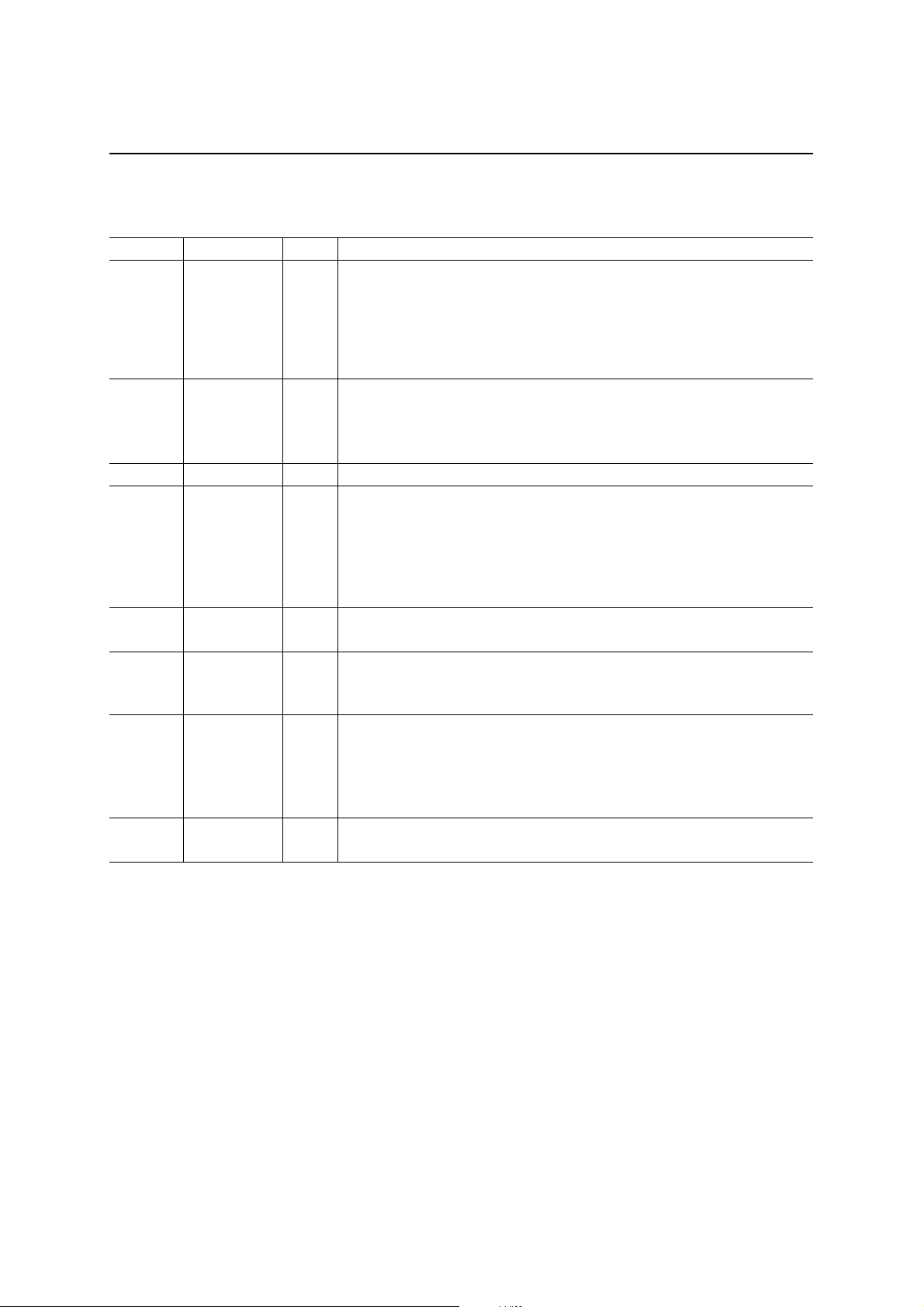

PIN DESCRIPTION

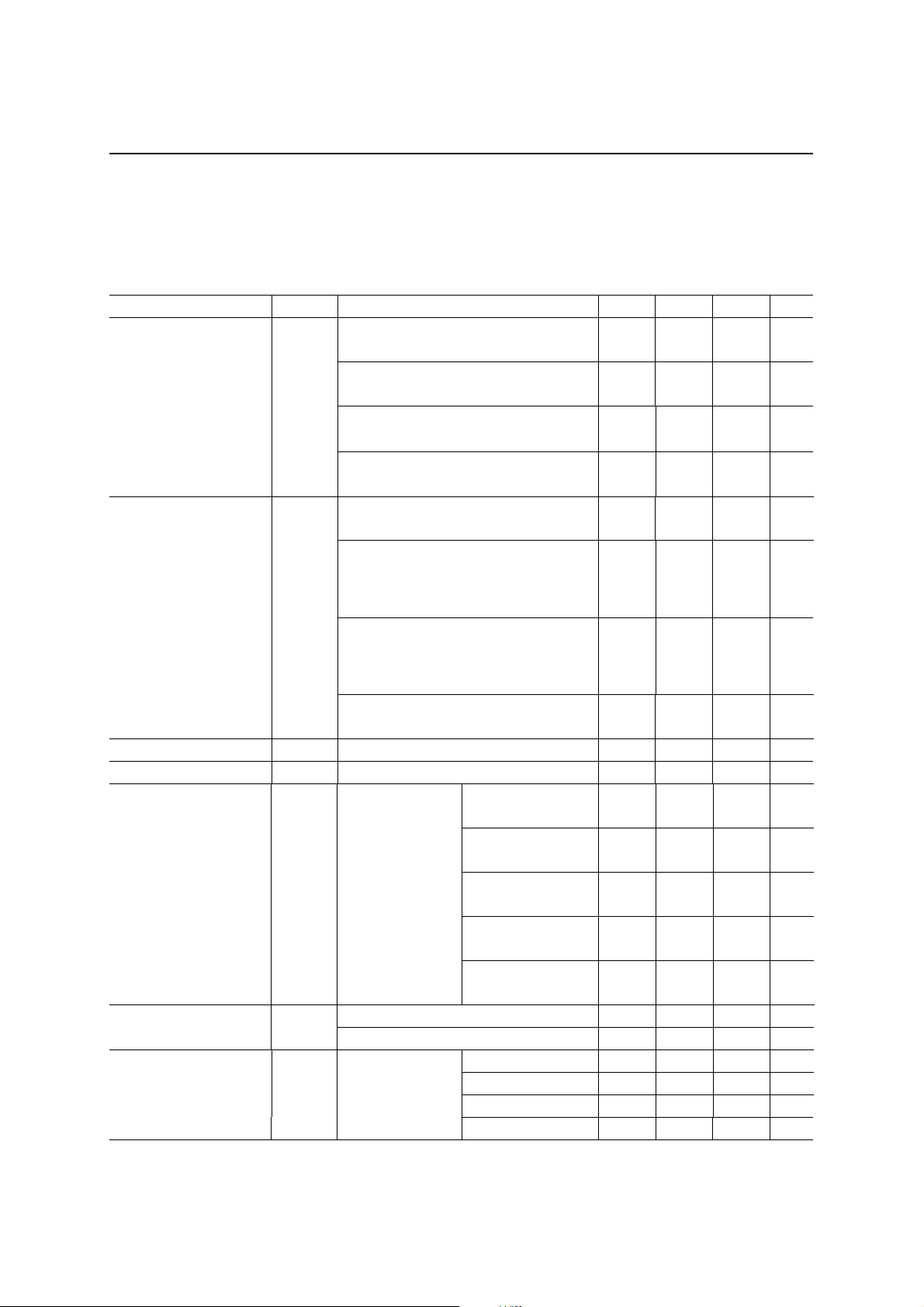

Pin No. Pin Name I/O Description

The playback trigger pin.

The number of pulses input to the PI pin, while this pin is held “L”,

1 ST I

2 PI I

3 GND — The ground pin.

4AOUTO

5VDD—

6XTI

7 XT O

8 PDWN I

determines the Phrase Address for playback. At the ST’s rising edge, the

phrase address data is loaded into the LSI and playback starts. When no

pulse input to PI occurs w hile this p in is held “L”, the LS I recognizes it as the

“Stop Code” that results in stopping playback.

The address input pin.

The number of pulses input to this pin, while the ST pin is held “L”,

determines the Phrase Address for playback.

When 32 pulses are input, th e interna l counter ret urns to its initial v alue, “0”.

The analog output pin.

Configured as N-MOS open drain, analog signal is output in the form of

change in output (attraction) current. While the PDWN pin being held “H”,

this pin is sustained at 1/2 level and thus the current keeps on flowing.

When shifting to standby state and shifting back to ready state from

standby, the pop-noise canceller is put to work.

The power supply pin.

Insert a 0.1 µF bypass capacitor between this pin and the GND pin.

The external clock input pin.

The ceramic resonator connection pin for ceramic oscillation option under

development.

Keep this pin open.

The LSI’s operations may become unstable if this pin includes any

capacitive component.

The ceramic resonator connection pin for ceramic oscillation option under

development.

The power down pin.

The LSI stays standby state while the pin being held “L”.

FEDL2201-01

ML2201–XXX

3/20

FEDL2201-01

Semiconductor

1

ML2201–XXX

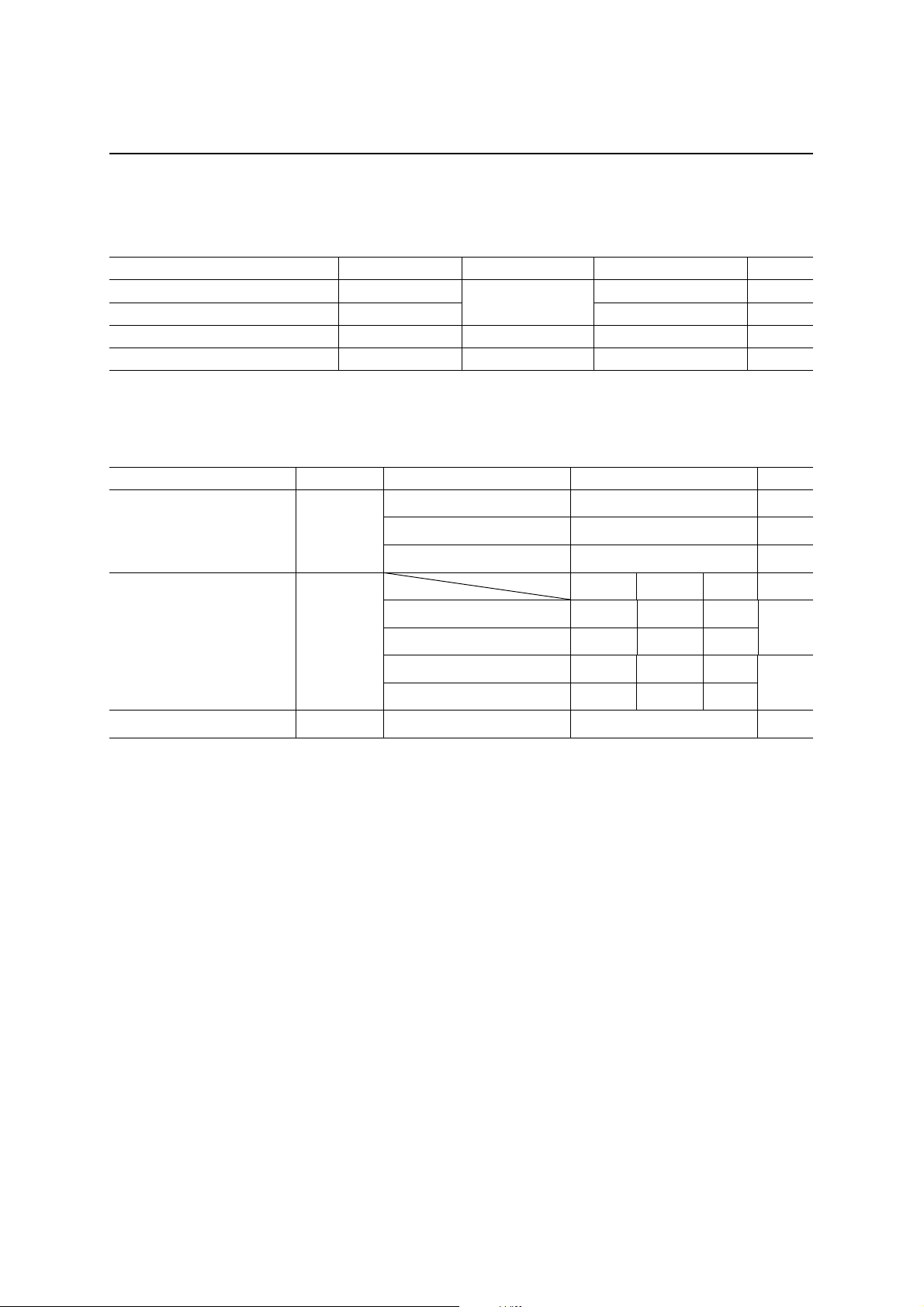

ABSOLUTE MAXIMUM RATINGS

(GND = 0 V)

Parameter Symbol Condition Rating Unit

Power Supply Voltage V

Input Voltage V

Storage Temperature T

DD

STG

IN

Ta = 25°C

— –55 to +150 °C

–0.3 to +7.0 V

–0.3 to V

+0.3 V

DD

Power Drain Allowance Pd Ta = 25°C 250 mW

RECOMMENDED OPERATING CONDITIONS

(GND = 0 V)

Parameter Symbol Condition Range Unit

f

= 3.5 to 4.5 MHz +2.0 to +5.5 V

EXTCLK

f

Power Supply Voltage V

DD

= 3.5 to 13.5 MHz +2.6 to +5.5 V

EXTCLK

f

= 3.5 to 17.0 MHz +3.0 to +5.5 V

EXTCLK

Min. Typ. Max.

VDD = 2.0 to 5.5 V 3.5 4.096 4.5

MHz

External Clock Frequency f

EXTCLK

Operating Temperature T

OP

V

= 2.6 to 5.5 V 3.5 — 13.5

DD

V

= 2.7 to 5.5 V 3.5 — 14.5

DD

VDD = 3.0 to 5.5 V 3.5 — 17.0

— –40 to +85 °C

4/20

Semiconductor

1

ELECTRICAL CHARACTERISTICS

DC Characteristics

FEDL2201-01

ML2201–XXX

VDD = 2.0 to 5.5 V, GND = 0 V, f

= 4.096 MHz, Ta = –40 to +85°C (unless otherwise specified)

EXTCLK

Parameter Symbol Condition Min. Typ. Max. Unit

F

“H” Input Voltage V

“L” Input Voltage V

“H” Input Current I

“L” Input Current I

Supply Current I

Standby Current I

IH

IL

IH

IL

DD

DS

EXTCLK

VDD = 3.0 to 5.5 V

f

EXTCLK

V

f

EXTCLK

V

f

V

F

EXTCLK

VDD = 3.0 to 5.5 V

f

EXTCLK

V

f

EXTCLK

VDD = 2.6 to 2.7 V

f

V

Except AOUT

output current

Ta = –40 to +70°C——10µA

Ta = –40 to +85°C — — 50 µA

> 14.5 MHz

≤ 14.5 MHz

= 2.7 to 5.5 V

DD

≤ 13.5 MHz

= 2.6 to 2.7 V

DD

≤ 4.5 MHz

EXTCLK

= 2.0 to 5.5 V

DD

> 14.5 MHz

≤ 14.5 MHz

= 2.7 to 5.5 V

DD

≤ 13.5 MHz

≤ 4.5 MHz

EXTCLK

= 2.0 to 5.5 V

DD

VIH = V

DD

VIL = GND –10 — — µA

VDD = 5.5 V

f

= 4.096 MHz

EXTCLK

VDD = 3.0 V

f

= 4.096 MHz

EXTCLK

VDD = 2.0 V

f

= 4.096 MHz

EXTCLK

VDD = 5.5 V

f

= 16 MHz

EXTCLK

V

= 3.0 V

DD

f

= 16 MHz

EXTCLK

V

DD

× 0.85

V

DD

× 0.8

V

DD

× 0.85

V

DD

× 0.8

——V

——V

——V

——V

——

——

——

——

——10µA

—1.73.9mA

—0.92.1mA

—0.51.4mA

— 4.6 12.0 mA

—1.86.5mA

VDD = 2.0 to 5.5 V 0.5 — 10.0 mA

AOUT Output Current I

AOUT

At max.

output current

VDD = 5.5 V 4.3 6.8 10.0 mA

VDD = 3.0 V 1.4 2.7 3.9 mA

V

= 2.0 V 0.5 1.2 2.2 mA

DD

V

DD

× 0.15

V

DD

× 0.2

V

DD

× 0.15

V

DD

× 0.2

V

V

V

V

5/20

Semiconductor

1

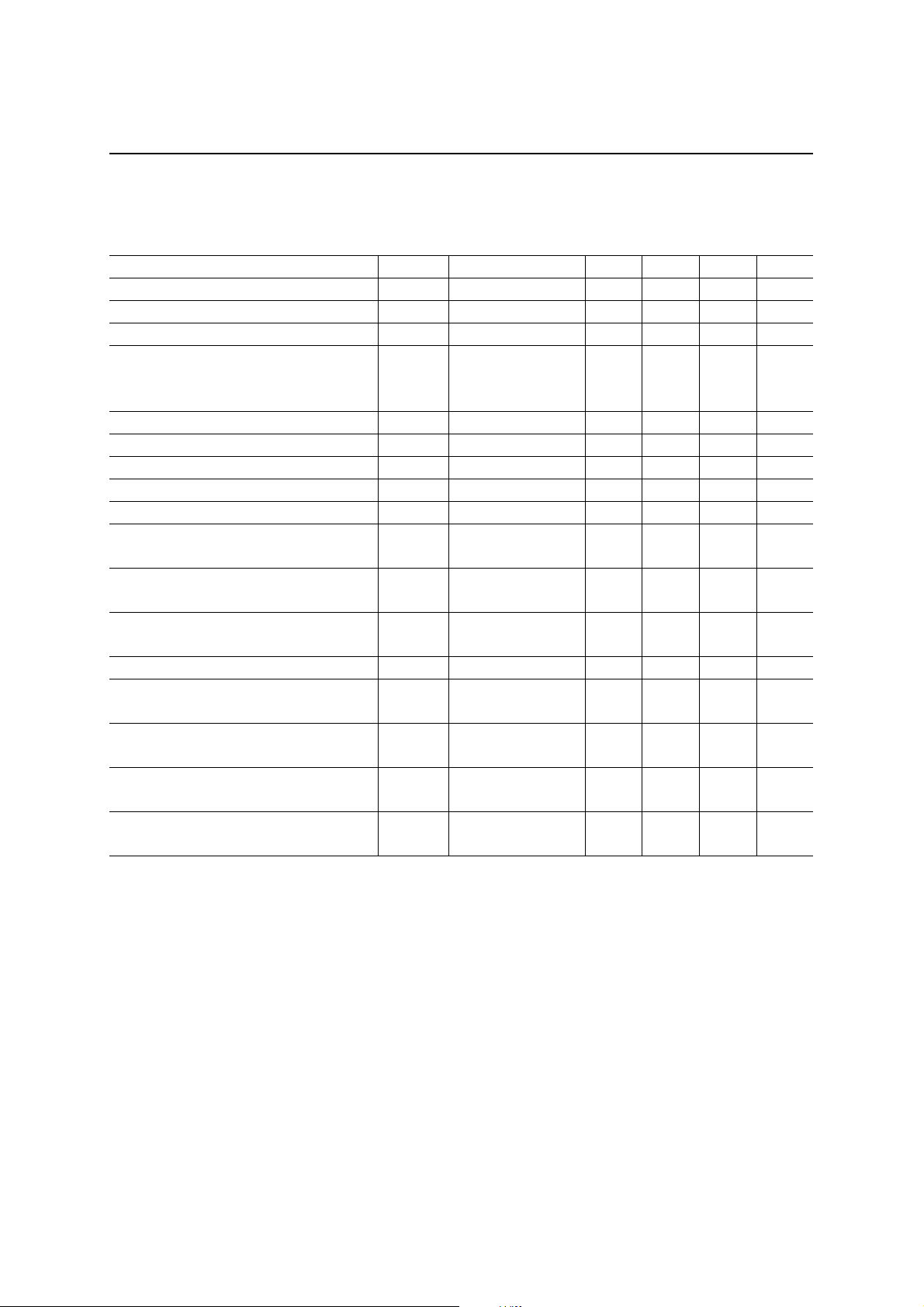

AC Characteristics

FEDL2201-01

ML2201–XXX

VDD = 2.0 to 5.5 V, GND = 0 V, f

Parameter Symbol Condition Min. Typ. Max. Unit

Clock Oscillation Duty Cycle f

Reset Input Time after Powering Up t

PDWN Hold Time after Reset Input t

D/A Converter Transit Time

(Pop-Noise Canceller Work Time)

t

DAR

Note *1

PDWN – ST Setup Time t

ST – PI Setup Time t

PI Pulse Width t

PI Cycle Time t

ST – PI Hold Time t

ST – AOUT Setup Time

Note *2

Phrase Stop Time

Note *2

Silence Time between Phrases

Note *2

Stop ST Pulse Wi dth t

Phrase ST – Phrase ST Pulse Duration

Note *2

Phrase ST – Stop ST Pulse Duration

Note *2

Stop ST – Phrase ST Pulse Duration

Note *2

Sampling Frequency

Note *3

= 4.096 MHz, Ta = –40 to +85°C (unless otherwise specified)

EXTCLK

DUTY

RST

PDH

, t

PDSS

SPS

PW

PC

SPH

t

SAS

t

DPS

t

BLN

SSW

t

PP

t

PS

t

SP

f

SAM

DAF

— 405060%

—10——µs

—10——µs

— 606468ms

—1——µs

—1——µs

— 0.35 — 2000 µs

— 0.7 — 4000 µs

—1——µs

At f

= 8.0 kHz — 1050 µs

SAM

At f

= 8.0 kHz — 700 µs

SAM

At f

= 8.0 kHz — 700 µs

SAM

— 0.35 — 2000 µs

At f

= 8.0 kHz 1050 — — µs

SAM

At f

= 8.0 kHz 1050 — — µs

SAM

At f

= 8.0 kHz 500 — — µs

SAM

— 3.9 — 28.0 kHz

Note *1: The value changes in proportion to the external clock frequency, f

Note *2: The value changes in proportion to the sampling frequency, f

SAM

EXTCLK

.

Note *3: The sampling frequency is determined by the external clock frequency, f

factor that is selected for each phrase.

.

, and the dividing

EXTCLK

6/20

Loading...

Loading...