NSC DP84910VHG-36 Datasheet

DP84910 (-36/-50)

Integrated Read Channel

General Description

The DP84910 integrates most functions of the hard disk

read channel electronics onto a single 5V chip. It incorporates a pulse/servo detector, a programmable integrated

channel filter, a data synchronizer, a frequency synthesizer,

and a serial port interface. The chip receives data from a

read preamplifier, filters and peak detects the read pulses

for both data and embedded servo information and resynchronizes the data with the system clock.

The DP84910 is available in two versions, DP84910VHG-36

and DP84910VHG-50. The DP84910VHG-36 is specified to

operate over a data rate range of 7.5 Mbits/sec to

36 Mbits/sec. The other version, DP84910VHG-50, will operate over a data rate range of 13.7 Mbits/sec to 50 Mbits/

sec.

This device is specifically designed to address zoned data

rate applications. A channel filter with control register selectable cutoff frequency and equalization is provided onchip. This eliminates the need for multiple external channel

filters and allows for greater flexibility in the selection of

zone frequencies. The frequency synthesizer provides center frequency information for the data synchronizer and a

variable frequency write clock. There is no need for any offchip frequency setting components or DACs.

A four-bank control register is included to control zoning

operations and configure general chip functions. At V

power-up the chip self-configures by presetting all bits in the

control register to predetermined operating setup conditions.

CC

October 1994

Independent power down control for all of the major blocks

within the chip is provided via three bits in the control

register (SYNCÐPWRÐDN, STHÐPWRÐDN and

PDÐPWRÐDN) to manage power consumption. In addition, two pins (SLEEP

control power management. The sleep mode pin (SLEEP

powers down all circuitry on the chip including the control

register. In this mode the maximum power supply current is

2 mA; the control register data must be reentered when

exiting this mode. The idle/servo mode pin (IDLE/SERVO

toggles the device between the idle and servo modes. In the

idle mode, only the control register and pulse detector biasing circuitry necessary for a quick recovery are active. In the

servo mode, the pulse detector portions needed for servo

detection are active as well as the control register. Less

than 15 ms is required for the pulse detector to recover from

the idle condition. The control register data is not lost when

this pin is toggled. The pin can be rapidly toggled (

to achieve average power consumption savings and will

keep the read/write head on track. Seventeen power and

ground pins are provided to isolate major functional blocks

and allow for independent supply voltage filtering, thus enhancing noise immunity. (Continued)

and IDLE/SERVO) are available to

k

15 ms)

DP84910 (-36/-50) Integrated Read Channel

)

)

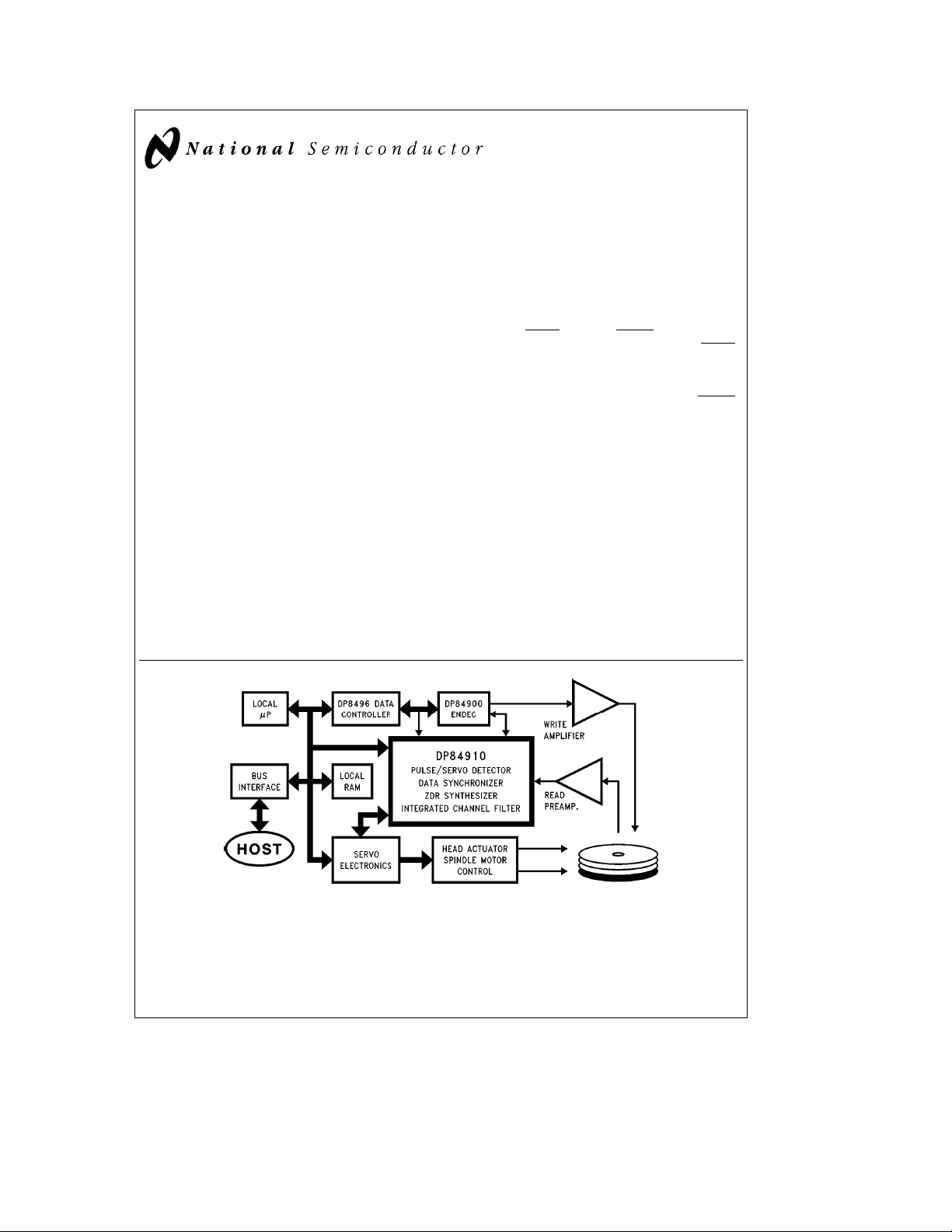

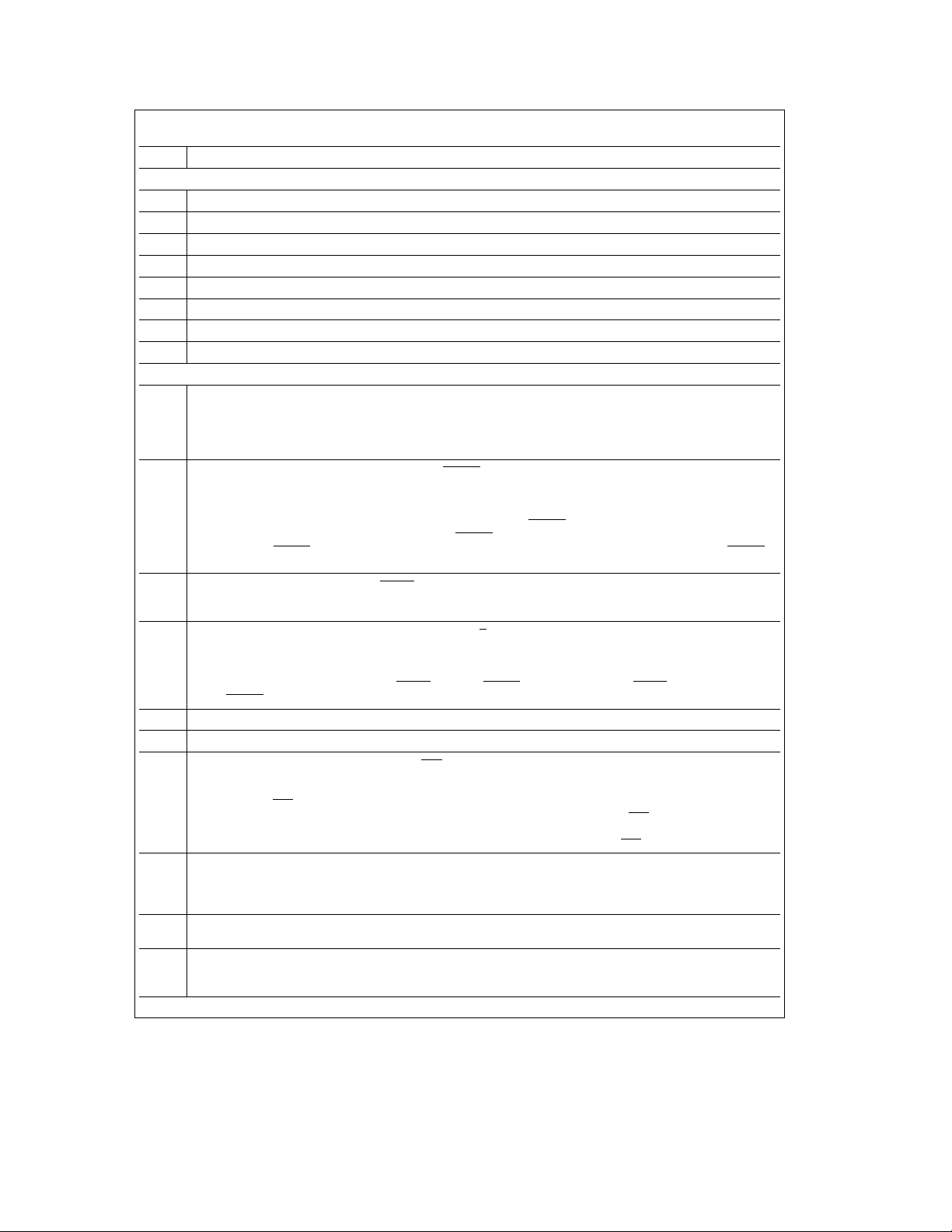

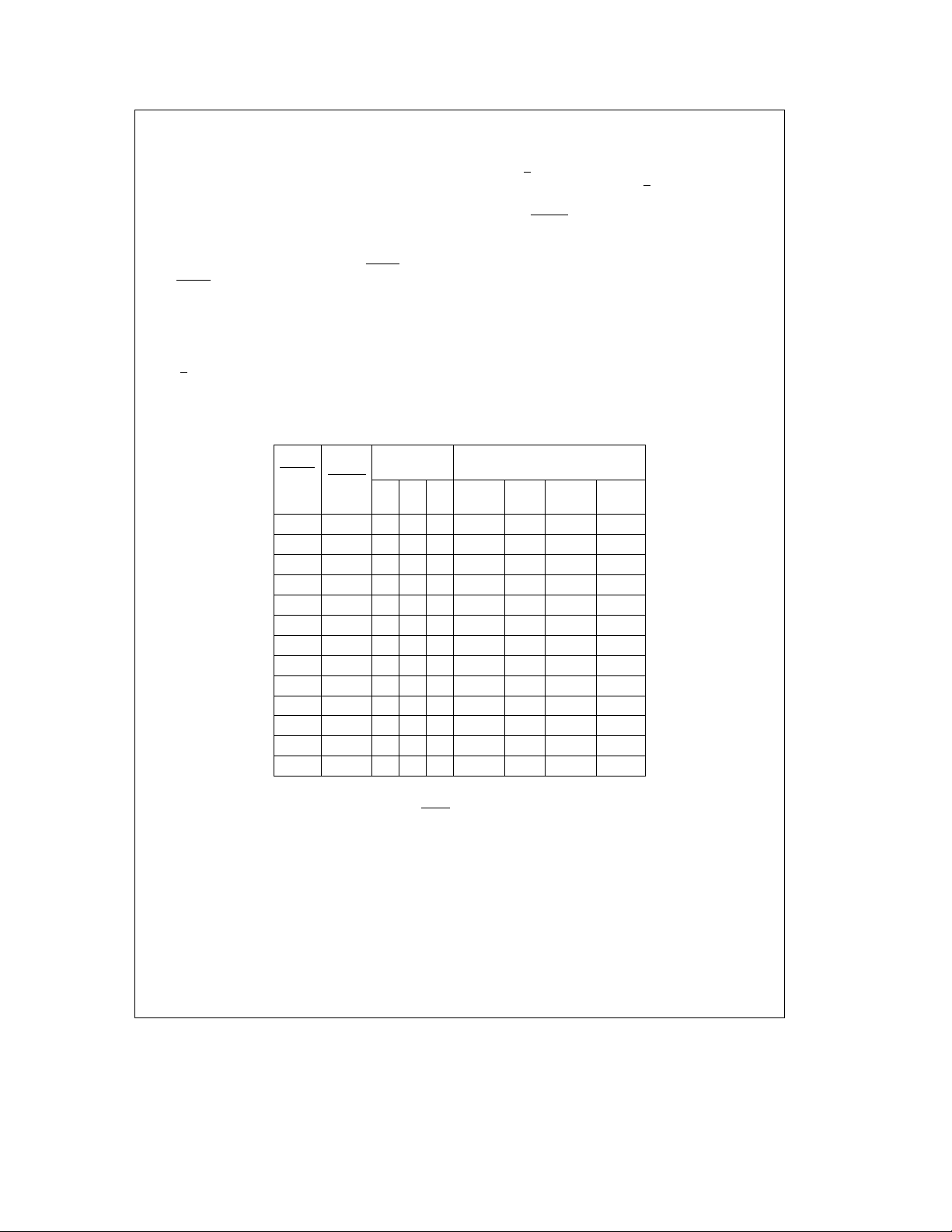

FIGURE 1. DP84910 in a Typical Disk Drive System

MICROWIRETMis a trademark of National Semiconductor Corporation.

C

1996 National Semiconductor Corporation RRD-B30M116/Printed in U. S. A.

TL/F/11777

TL/F/11777– 1

http://www.national.com

General Description (Continued)

The pulse detector section detects the peaks of the analog

pulses from the read preamplifier and converts them to digital pulses whose leading edges represent the time position

of the analog pulses’ peaks. In order to not interpret noise

on the baseline as input data, hysteresis is included. The

hysteresis level for a data field is set at the SETHYSD pin

while the hysteresis level for a servo field is set at the

SETHYSS pin. A third pin (SFIELD) is used to select between these two levels of hysteresis. This allows for the

setting of different hysteresis levels for these two fields. The

data field hysteresis level is also selectable in 8 steps

through bits in the control register (HYSÐVTH0–HYS

VTH2) with the level set at the SETHYSD pin as the nominal

value.

The pulse detector section includes an automatic gain control (AGC) circuit which normalizes the analog data signal to

a constant amplitude. The response of the AGC is partially

controlled by one of the device’s pins (VAGCIN). Two

VAGCIN pins (VAGCIND, VAGCINS) are provided so that

different capacitor values can be selected to provide different AGC time constants for data and servo field information.

The switching between these pins/capacitors is controlled

by the SFIELD pin. The SERVO

able (or disable) the SFIELD pin’s ability to control the

amount of equalization provided to the on-chip channel filter. When enabled, the state of the SFIELD pin selects between two groups of control register bits (EQ0, EQ1, EQ2

and SERVOÐEQ0, SERVOÐEQ1, SERVOÐEQ2) which

can separately determine the amount of equalization provided. This feature allows for an adjustment of the channel

filter bandwidth in a servo field. Thus the channel filter can

have different bandwidths in a servo field and a data field.

The pulse detector section has a delayed, low impedance

switch at the gain controlled amplifier inputs (AMPIN1, AMPIN2) which allows for rapid recovery from the write mode.

The amount of delay (either 1.7 msor3.4ms) coming out of

the low impedance mode is selectable through a bit in the

control register (SLOW

). A pattern insensitive, fast responding AGC circuit (with HOLD function) allows rapid head

switch settling and embedded servo normalization. Selectable delay (in four steps) in the qualification channel, along

with a ‘‘view internal signals’’ mode, allow the timing and

qualification channels to be optimally aligned. Four gated

servo detectors are incorporated for recovery of quadrature

embedded servo information. The four peak detected values are available at the SERVO CAPACITOR outputs

(SCAP1–4). Two servo difference amplifiers are provided.

Each difference amplifier output (DIFFAMP1/2) provides

the difference between two of the servo peak detectors,

centered about an external reference voltage (VDIFF).

The channel filter section is a seven-pole 0.05 degree error,

equal ripple filter. It utilizes the Kost pulse slimming technique similar to that which is employed on the DP8491/92

integrated read channel devices. The amount of pulse slimming is control register selectable in 8 steps up to a maximum of 9 dB measured from the base frequency. The bandwidth of the filter is derived from the XTLIN frequency; from

this point, the

b

3 dB frequency is selectable via 7 bits in the

control register (FILTÐ3dBÐ0–FILTÐ3dBÐ6).

control register bit can en-

The data synchronizer section incorporates zero-phasestart (ZPS) and digitally controlled window strobe functions.

The voltage controlled oscillator (VCO) is fully integrated,

requiring no external components, and provides a wide dynamic range necessary for zoned data rate applications.

Data windowing is based on precise VCO duty cycle symmetry (in contrast to delay line based centering). An internal

silicon delay line, used to establish the phase detector retrace angle, automatically tracks zoned data recording data

rate changes. The charge pump output (CPO) and voltage

controlled oscillator input (VCOI) are provided as separate

Ð

pins, allowing ample design flexibility in the external loop

filter. Frequency lock may be employed within the synchronization field. Charge pump (phase detector) gain may be

selected to remain constant or to vary either by a factor of

two or four as instructed via the charge pump gain pin

(CPGAIN) and a bit in the control register (CPRATIO).

The frequency synthesizer section, capable of producing a

large number of frequencies from a single external reference source, generates the write clock and reference frequency for the synchronizer. This section includes a phase

locked loop (PLL) with selectable dividers at the input port

and in its feedback loop. The values for the dividers are

controlled by two control words within the control register.

The user has full control over both the input (five bit word,

PDATA6–PDATA10) and feedback (six bit word, PDATA0 –

PDATA5) divider selection. The feedback divider has an extra bit when compared to previous NSC integrated read

channel circuits to improve the resolution of frequency setting. All blocks within the synthesizer, except the RC loop

filter, are fully integrated. The loop filter resides external to

the chip giving the user full control over the phase locked

loop’s dynamics.

This device is available in an 80-pin 12 mm x 12 mm PQFP

package and operates off of a single

a

5V supply.

Features

Y

Operates at NRZ data rates up to 50 Mbits/sec (equivalent 2/3 (1,7) code data rate)

Y

Operates with a singlea5V power supply

Y

Multiple power down modes available with dedicated

SLEEP

Y

Y

Y

Y

Y

Y

Y

Y

and IDLE/SERVO power down pins

Sleep mode included where I

Directly addresses zoned data recording requirements

e

2 mA maximum

CC

Ð Integrated channel filter with selectable equalization

and bandwidth eliminates multiple external filter elements

Ð Fully integrated frequency synthesizer on-chip to pro-

vide write clock and center frequency for the synchronizer

Selectable delay impedance switch (clamp) at pulse detector input for rapid recovery from the write mode

Pattern insensitive fast AGC for rapid head switch settling and embedded servo normalization

Built-in AGC hold for embedded servo

Two AGC control voltage pins providedÐone for servo

field and one for data field

Four gated detectors for quadrature embedded servo

information

Two servo difference amplifiers on-chip

http://www.national.com 2

Features (Continued)

Y

Reference voltage input pin provided for the servo difference amplifiers

Y

Two selectable hysteresis control pins providedÐone

for servo field and one for data field

Y

Data field hysteresis level is control register selectable

in eight steps

Y

Logic polarity for write gate assertion is control register

selectable

Y

Capability provided for different channel filter bandwidths for servo and data fieldsÐchange on the fly with

no settling issues

General Block Diagram

Y

Selectable qualification channel delay

Y

Dual gain synchronizer requiring no external or internal

center frequency setting components, external adjustments, or precision components

Y

Digitally controlled synchronizer window strobing

Y

Zero-phase-start synchronizer lock acquisition

Y

Two port synchronizer PLL filtering

Y

Frequency lock option for 2T or 3T synchronization

field (preamble)

Y

TTL compatible inputs and outputs

Y

Chip configurable through serial port interface

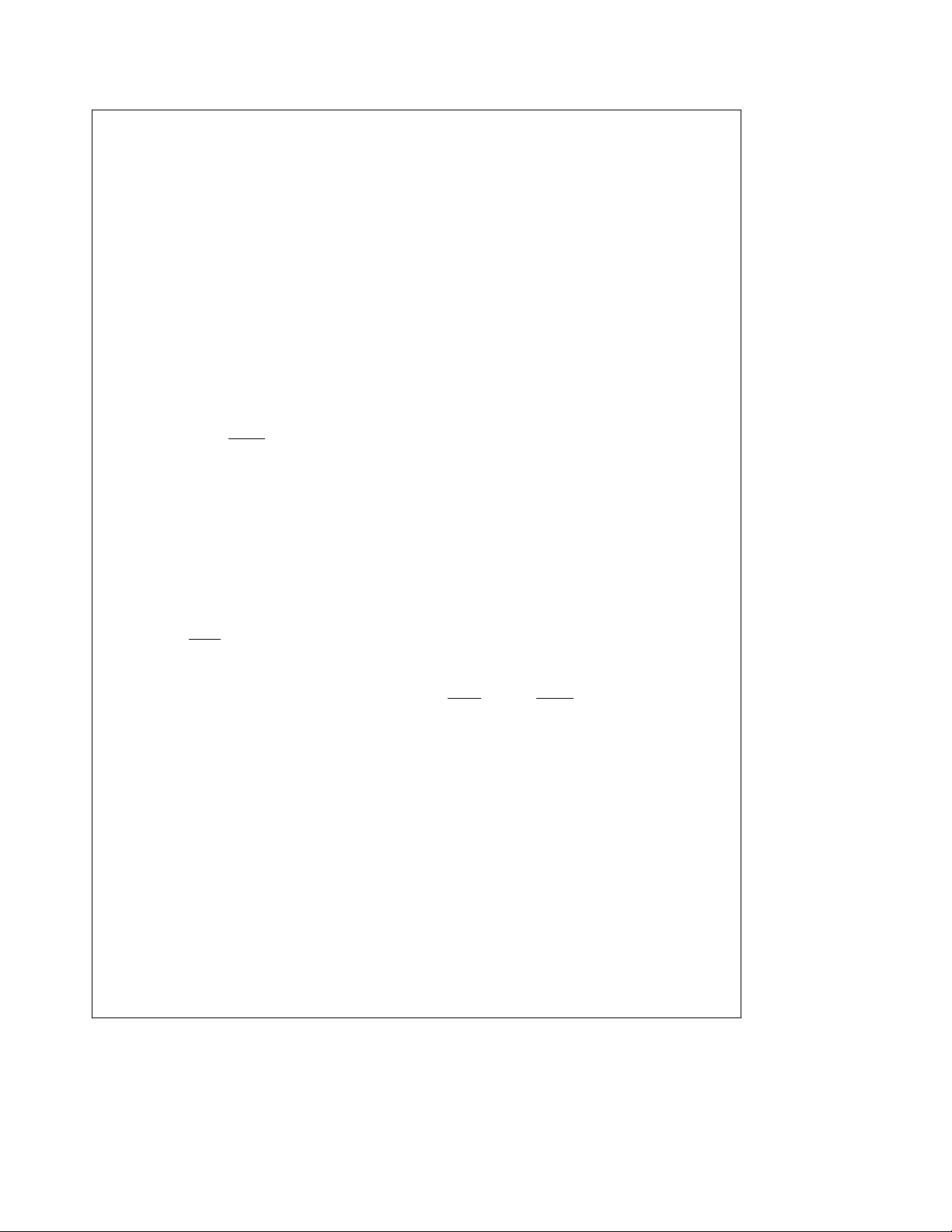

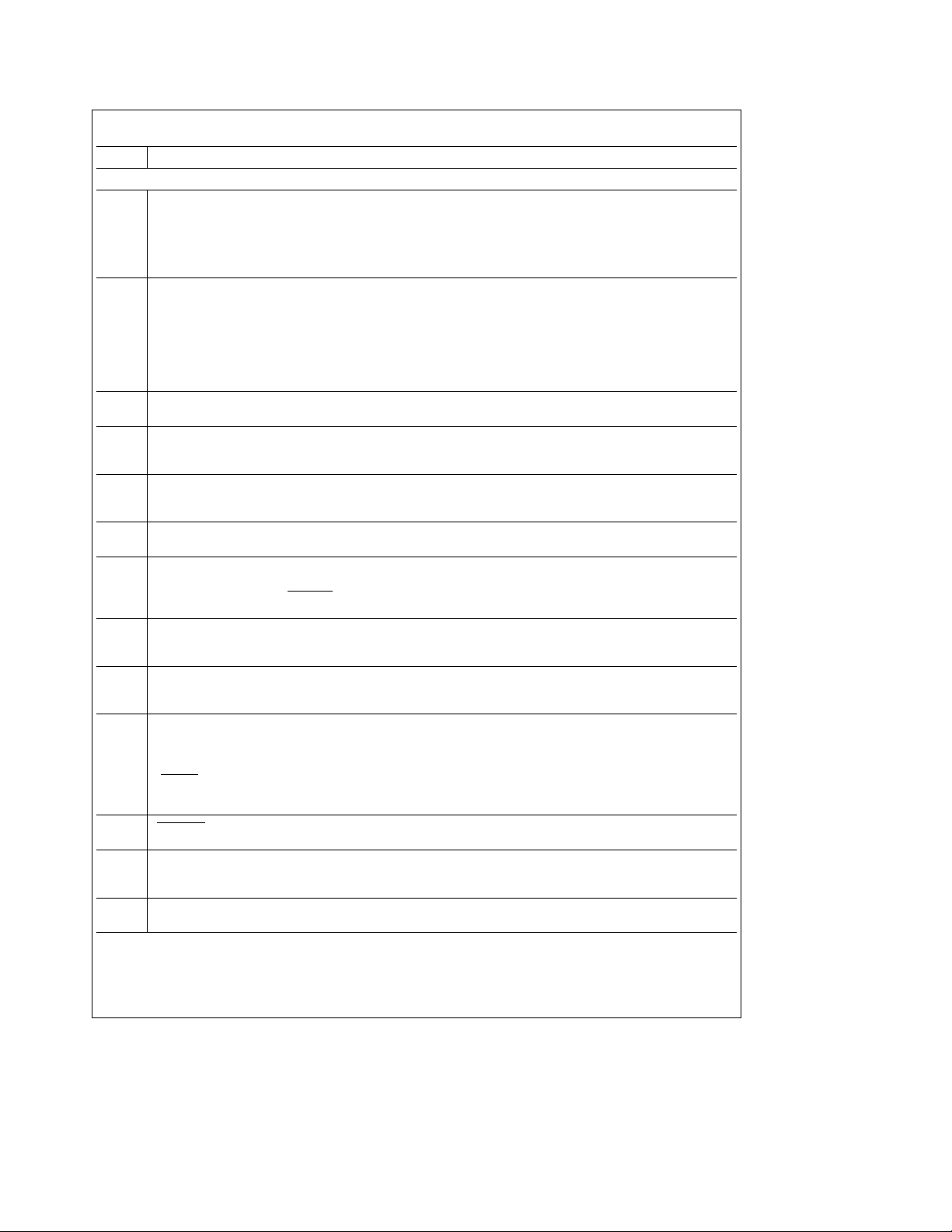

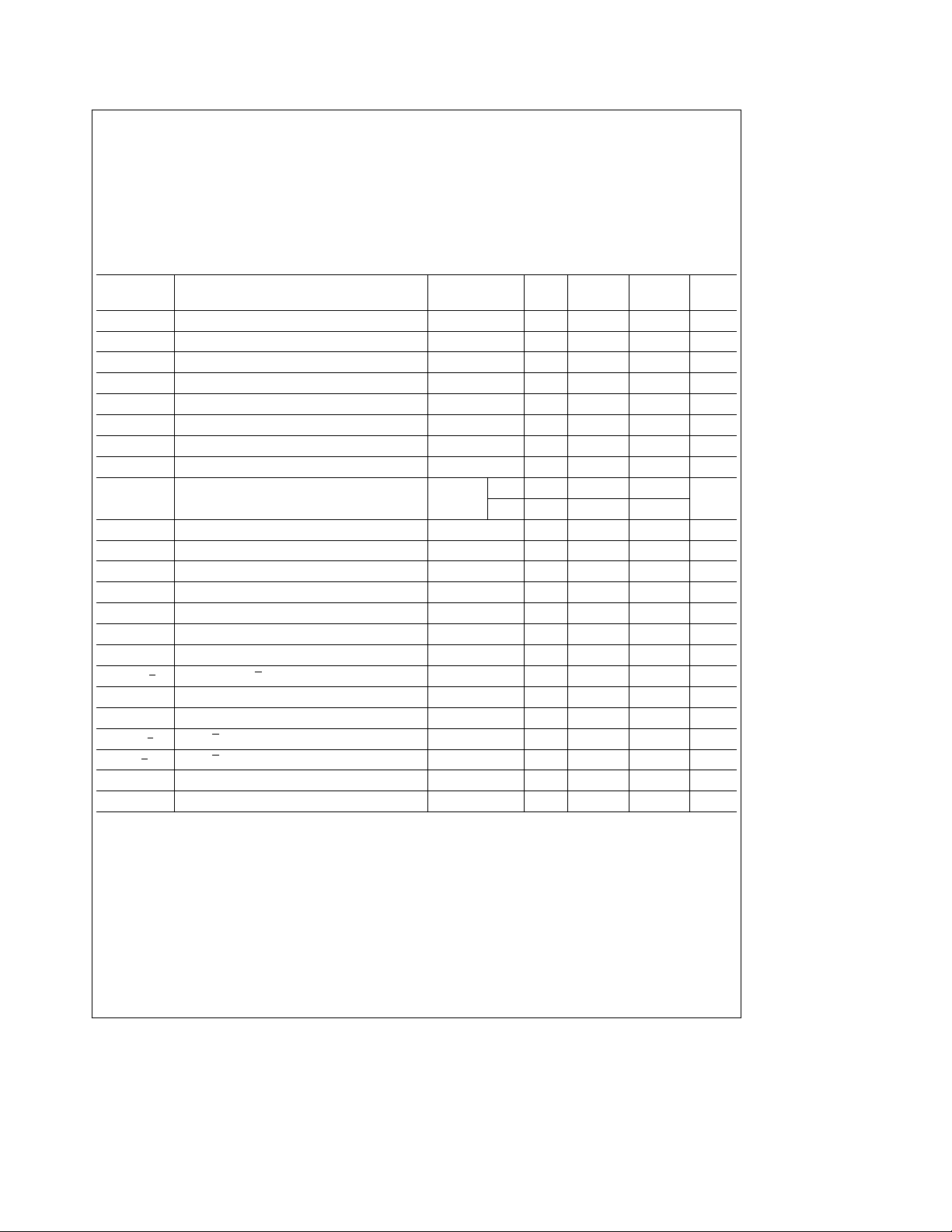

FIGURE 2

TL/F/11777– 2

http://www.national.com3

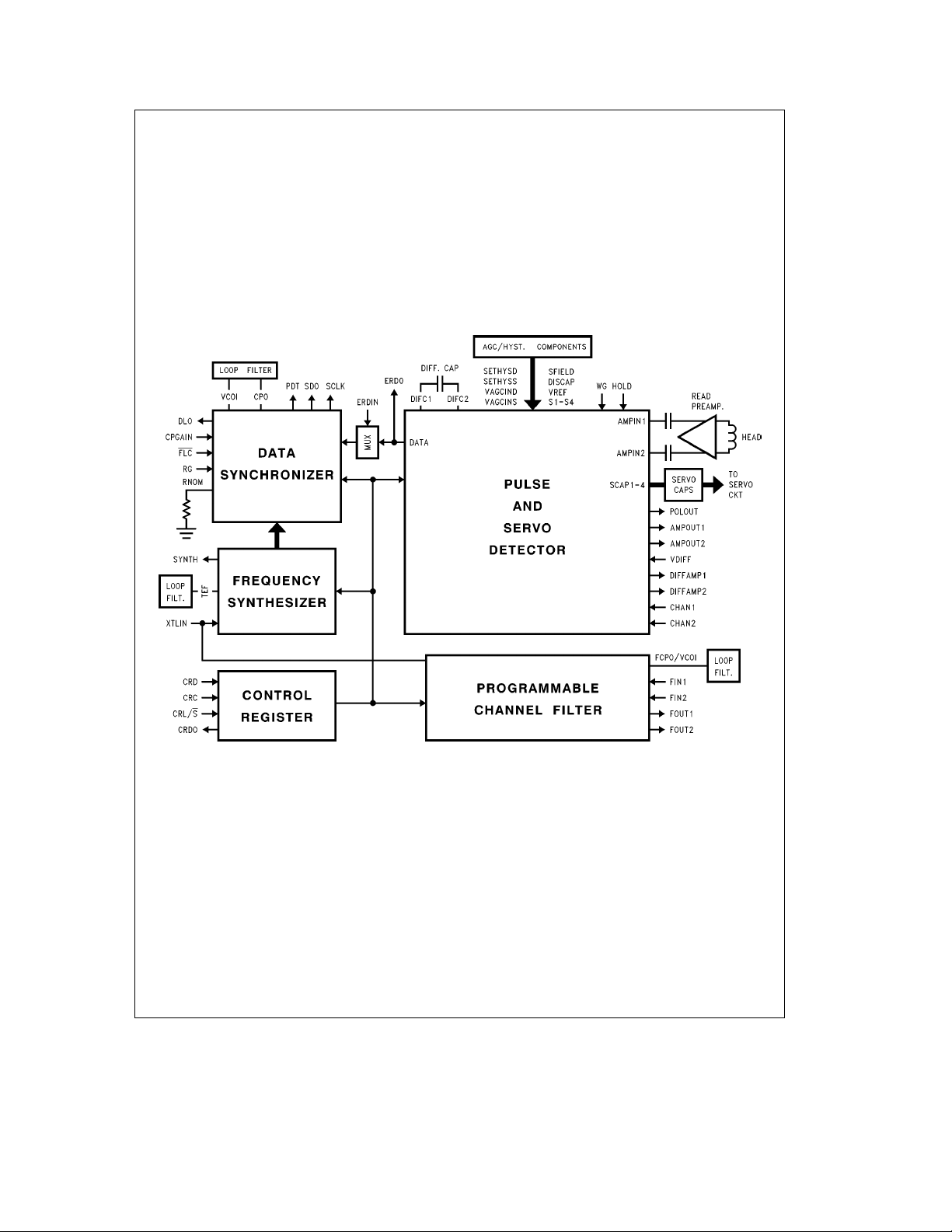

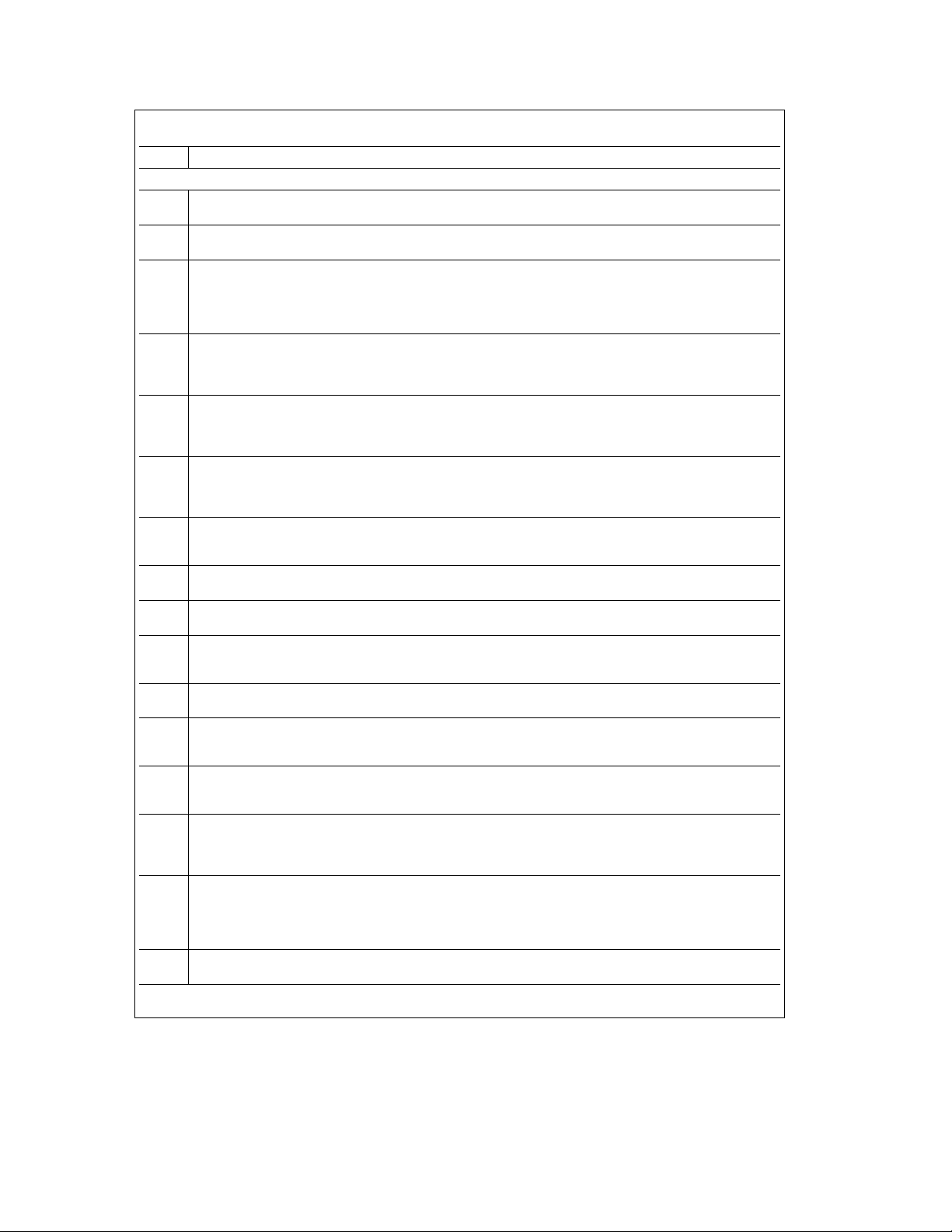

Connection Diagram

Note: Make no external connections to the NSC test pins. TL/F/11777– 3

Order Number DP84910VHG-36 or DP84910VHG-50

See NS Package Number VHG80A

FIGURE 3

Pin Definitions

Ý

Pin

POWER SUPPLY AND GROUND PINS

16 INPUT/OUPUT BUFFER SUPPLY VOLTAGE (BVCC): 5Va5/b10%

17, 18, 20 INPUT/OUTPUT BUFFER GROUNDS (BGND)

24 PLL DIGITAL SUPPLY VOLTAGE (DVCC): 5Va5/b10%

25 PLL DIGITAL GROUND (DGND)

33 PULSE DETECTOR DIGITAL SUPPLY VOLTAGE (PDVCC): 5Va5/b10%

35 PULSE DETECTOR DIGITAL GROUND (PDGND)

http://www.national.com 4

Description

Pin Definitions (Continued)

Ý

Pin

POWER SUPPLY AND GROUND PINS (Continued)

65 PULSE DETECTOR ANALOG SUPPLY VOLTAGE (PAVCC): 5Va5/b10%

66 PULSE DETECTOR ANALOG GROUND (PAGND)

68 FILTER ANALOG SUPPLY VOLTAGE (FVCC): 5Va5/b10%

69 FILTER ANALOG GROUND (FGND)

72 SYNCHRONIZER PLL ANALOG SUPPLY VOLTAGE (SYCVCC): 5Va5/b10%

75 SYNCHRONIZER PLL ANALOG GROUND (SYCGND)

78 SYNTHESIZER PLL ANALOG SUPPLY VOLTAGE (STHVCC): 5Va5/b10%

80 SYNTHESIZER PLL ANALOG GROUND (STHGND)

TTL LEVEL LOGIC PINS

1 WRITE GATE INPUT (WG): This pin receives the write mode control input signal from the controller. The logic polarity

for WG assertion is selectable via a bit in the control register (INVÐWG, Bank (1,1) bit 5). WG is active low if the control

register bit is set to invert (INVÐWG

held in a low impedance state and the automatic gain control of the puIse detector is in the hold mode. There are no

setup or hold timing restrictions on WG enabling or disabling.

2 IDLE/SERVO BAR POWER DOWN INPUT (IDLE/SERVO): This input controls the power status of the servo detection

circuitry in the pulse detector. When high (idle mode), this pin powers down all pulse detector circuitry except for biasing

circuitry necessary for quick recovery (k15 ms) from this mode. When low (servo mode), this pin powers on the circuitry

necessary for servo information detection in the puIse detector. The synchronizer and synthesizer power are unaffected

by this pin. The controI register power is also unaffected by the IDLE/SERVO

register’s input’s are only powered on when the IDLE/SERVO

when the IDLE/SERVO

pin.

3 SLEEP BAR POWER DOWN INPUT (SLEEP): This active low input powers down aIl circuitry on the chip. The control

register is powered down in this mode thus it does not retain its information. The control register wiII be reset to the

initial power-on conditions when exiting the sleep mode. The maximum supply current in the sleep mode is 2 mA.

4 CONTROL REGISTER LATCH/SHIFT BAR INPUT (CRL/S): A logical low on this input allows the CONTROL

REGISTER CLOCK input to shift data into the control register’s shift register via the CONTROL REGISTER DATA input.

A positive transition latches the data into the addressed bank of latches and issues the information to the appropriate

circuitry within the device. To minimize power consumption, this pin should be kept at a logical high state except when

shifting data into the control register. The SLEEP

IDLE/SERVO

5 CONTROL REGISTER DATA INPUT (CRD): ControI register data input.

6 CONTROL REGISTER CLOCK INPUT (CRC): Positive-edge-active control register clock input.

7 FREQUENCY LOCK CONTROL BAR INPUT (FLC): This input enables or disables the frequency lock function during a

read operation. It has no effect when READ GATE is disabled. Frequency lock is automatically employed for the full

duration of the time READ GATE is disabled regardless of the level of this input. When READ GATE is taken to a logical

high level while FLC

(2T or 3T sync. field) selected in the control register (PREAMÐ2T, Bank (1,1) bit 4). When FLC

level, the frequency lock action is terminated and the PLL employs a pulse gate to accommodate random disk data

patterns. There are no setup or hold timing restrictions on the positive-going transition of FLC

8 PREAMBLE DETECTED OUTPUT (PDT): This output issues a logical high state after the following sequence; the

enabling of READ GATE, the completion of the zero-phase-start sequence and the detection of approximately 16

sequential pulses of 2T or 3T preamble. Following preamble detection, this output remains latched high until READ

GATE is disabled. This output will be at a logical low state whenever READ GATE is inactive (low).

9 READ GATE INPUT (RG): This input receives the read mode control input signal from the controller, active high for a

read operation. There are no setup or hold timing restrictions on RG enabling or disabling.

10 DELAY LINE OUTPUT (DLO): This active low, open collector output pin issues encoded read data (ERD) delayed by

the selected value in the delay line at the input to the synchronizing latch. By viewing this signal’s phase, the user can

directly view the amount of window movement as the control register’s strobe bits are changed.

pin is high. The contents of the controI register is not affected by the state of the IDLE/SERVO

e

low) in order to shift data into the control register.

is at a logical low level (frequency lock enabled), the PLL is forced to lock to the pattern frequency

e

1). When WG is active, the pulse detector inputs (AMPIN1 and AMPIN2) are

Description

pin but its input buffers are. The control

pin is low. Thus, the controI register cannot be loaded

and IDLE/SERVO pins must be disabled (SLEEPehigh and

is taken to a logical high

.

http://www.national.com5

Pin Definitions (Continued)

Ý

Pin

TTL LEVEL LOGIC PINS (Continued)

11 ENCODED READ DATA OUTPUT (ERDO): This output issues the raw, pulsed output of the pulse detector when

enabled by the control register bits ERD0 and ERD1 (Bank (1,1), bits 3 and 4). When disabled (see Table III) this output

will be high. When enabled, the pulsed data from the pulse detector can continue to be issued to the synchronizer

depending on the combination of states of the ERD0 and ERD1 control register bits. When both the ERD0 and ERD1

control register bits are high, the part is put into a test mode where the gain of the GCA is held constant (i.e. fixed gain

mode). In this test mode the synchronizer and synthesizer VCOs can be driven by external test signals.

12 ENCODED READ DATA INPUT (ERDIN): This pin is the input to the synchronizer. It is enabled/disabled via control

register bits ERD0 and ERD1 (Bank (1,1), bits 2 and 3). When enabled (see Table III), this buffer admits external pulsed

data to the synchronizer via this pin and raw data output from the pulse detector is NOT internally fed to the

synchronizer. This allows for testing/exercising of the synchronizer, or for external processing of the peak-detected

data prior to being fed to the synchronizer. When ERDO is disabled, the pulse detector’s data is fed internally to the

synchronizer. When both the ERD0 and ERD1 control register bits are high, the part is put into a test mode where the

gain controlled amplifier is put into a fixed gain. In this test mode the synchronizer and synthesizer VCOs can be driven

by external test signals.

14 SYNCHRONIZED DATA OUTPUT (SDO): This output issues resynchronized data directly from the synchronizing PLL

block.

15 MULTIPLEXED SYNCHRONIZED CLOCK OUTPUT (SCLK): This output issues either the synchronizer or synthesizer

clock signal dependent on whether the device is in the read or non-read mode. The synchronizer clock is selected

during read mode while the synthesizer clock is selected during non-read mode. Multiplexing is done without glitches.

19 CRYSTAL INPUT (XTLIN): This input is the synthesizer and filter reference frequency input. It is designed for

connection from a TTL frequency source. Duty cycle is not critical. An input attenuation resistor is normally used to

minimize transient noise at this pin.

21 POLARITY OUTPUT (POLOUT): This TTL output issues a signal that is the output of the pulse detector’s comparator

with hysteresis. The logical polarity of this signal corresponds to the polarity of the signal at the channel input pins.

22 SYNTHESIZER REFERENCE OUTPUT (SYNTH): This output issues a continuous reference signal from the frequency

synthesizer when enabled. At V

a bit in the control register (ENSTHO

rate.

23 CONTROL REGISTER DATA OUTPUT (CRDO): This output issues data from the control register. It can be connected

to the input of another device’s control register such as the DP84900 (ENDEC) so that the number of data lines from

the controller can be minimized.

27–30 SERVO SWITCH INPUTSÝ1,Ý2,Ý3,Ý4 (S1, S2, S3, S4): These pins, in conjunction with the AGC HOLD pin,

control the gating action of the gated servo peak detectors and the discharge of the servo channeIs. These pins also

enabIe or disabIe the output internal signals, the track follow and the seek modes according to Table IV.

31 SERVO FIELD SELECT INPUT (SFIELD): When at a high logic level, this pin switches the hysteresis threshold control

of the puIse detector’s comparator from the SET HYSTERESIS-DATA FIELD (SETHYSD) pin to the SET

HYSTERESIS-SERVO FIELD (SETHYSS) pin. It also switches the AGC controI from the AGC control capacitor-data

field (VAGCIND) pin to the AGC control capacitor-servo field (VAGCINS) pin. When enabled by a control register bit

e

(SERVO

filter, between data equalization control bits (EQ0, EQ1, EQ2, Bank (0,0) bits 9, 10, 11) and servo equalization control

bits (SERVOÐEQ0, SERVOÐEQ1 SERVOÐEQ2, Bank (1,1) bits 10, 11, 12).

36 OPTICAL: The optical (unipolar) mode is enabled by the application of ground to this pin. For magnetic operation this

pin must be left open (no connection to it). Refer to design guide for details of operation.

67 COAST/AGC HOLD INPUT (HOLD): When high, this input controls an internal switch which freezes the pulse detector

AGC level for the reading of the servo burst. Phase comparisons within the synchronizer (read mode only) are also

disabled, allowing the PLL to coast.

77 CHARGE PUMP GAIN INPUT (CPGAIN): This input selects the gain of the synchronizer’s charge pump in conjunction

with a bit in the control register (CPRATIO, Bank (1,0) bit 12) (see Table VIII).

1, Bank (0,0) bit 12), this pin can switch the equalization, and consequently the bandwidth of the channel

power up this pin is in the inactive state (a logical high state) and can be enabled via

CC

, Bank (1,0) bit 5). The output frequency will be the same as the media code clock

Description

http://www.national.com 6

Pin Definitions (Continued)

Ý

Pin

ANALOG SIGNAL PINS

32 VPHASE: An internally generated voltage is present at his pin to control the Q of the integrated filter. An external

network (24 kX to FV

34 FILTER CHARGE PUMP OUTPUT/VCO INPUT NODE (FCPO/VCOI): This is the filter node for the channel filter PLL.

An externaI resistor and capacitor loop filter is tied in series between this pin and ground.

37 SERVO CAPACITORÝ4 (SCAP4): This pin is the connection point for the peak detector capacitor for the embedded

servo gated detector. The DC level on this capacitor represents the amplitude of one of four servo bursts. When the

‘‘output internal signals’’ mode is selected by applying a high logical level to the S2 pin and a low logical level on the

HOLD pin, the signal on this pin becomes the output of the seIectable delay block in the qualification channel (see

Table IV).

38 SERVO CAPACITORÝ3 (SCAP3): This pin is the connection point for the peak detector capacitor for the embedded

servo gated detector. The DC level on this capacitor represents the amplitude of one of four servo bursts. When the

‘‘output internal signals’’ mode is selected by applying a high logical level to the S2 pin and a low logical level on the

HOLD pin, the signal on this pin becomes the output of the time channel zero-cross detector (see Table IV).

39 SERVO CAPACITORÝ2 (SCAP2): This pin is the connection point for the peak detector capacitor for the embedded

servo gated detector. The DC level on this capacitor represents the amplitude of one of four servo bursts. When the

‘‘output internal signals’’ mode is selected by applying a high logical level to the S2 pin and a low logical Ievel on the

HOLD pin, the signal on this pin becomes one of the differential outputs of the differentiator (see Table IV).

40 SERVO CAPACITORÝ1 (SCAP1): This pin is the connection point for the peak detector capacitor for the embedded

servo gated detector. The DC level on this capacitor represents the amplitude of one of four servo bursts. When the

‘‘output internal signals’’ mode is selected by applying a high logical level to the S2 pin and a low logical level on the

HOLD pin, the signal on this pin becomes one of the differential outputs of the differentiator (see Table IV).

41, 42 SERVO DIFFERENCE AMPLIFIERS OUTPUTSÝ1,Ý2 (DIFAMP1, DIFAMP2): These low impedance pins issue an

output signal which is the difference in voltage between SCAP4 and SCAP3 pins (DIFAMP2) and SCAP2 and SCAP1

pins (DIFAMP1). These differences will be centered about a reference level set by the voltage on the VDlFF pin.

43 SERVO DIFFERENCE VOLTAGE REFERENCE INPUT (VDIFF): A voltage applied to this pin provides a reference for

the zero-level of the signals issued by the difference amplifiers on DIFAMP1 and DIFAMP2 pins.

45, 46 DIFFERENTIATOR CAPACITOR NODESÝ1,Ý2 (DIFC1, DIFC2): These pins are connection points for the

differentiator components (typically a resistor, capacitor, and inductor).

48, 49 GAIN CONTROLLED AMPLIFIER OUTPUTSÝ1,Ý2 (AMPOUT1, AMPOUT2): These pins are complimentary emitter

follower outputs from the gain controlled amplifier. They are to be externally capacitively coupIed to the channel filter

inputs (FIN1, FIN2).

50, 51 FILTER INPUTSÝ2,Ý1 (FIN2, FIN1): These channel filter inputs are to be externally capacitively coupled to the gain

controlled amplifier outputs (AMPOUT1, AMPOUT2).

53, 54 FILTER OUTPUTSÝ1,Ý2 (FOUT1, FOUT2): These pins are complimentary emitter foIIower outputs from the channeI

filter. They are to be externally capacitively coupled to the timing-gating channel/AGC sense/servo channel inputs

(CHAN1, CHAN2).

55, 56 TIMING-GATING CHANNEL/AGC SENSE/SERVO INPUTSÝ2,Ý1 (CHAN2, CHAN1): These input pins are to be

externally capacitively coupled from the channel filter outputs (FOUT1, FOUT2). These pins are the inputs to the

differentiator, AGC amplifier, servo channel and qualification channel.

57 SET HYSTERESIS INPUT-SERVO FIELD (SETHYSS): When activated by a logical high level on the SFIELD pin, the

voltage applied to this pin determines the amount of hysteresis for the pulse detector’s hysteresis comparator. This

level should be set high enough to eliminate noise which might occur in the shoulder region between read pulses from

the preamplifier. The SVCC pin is provided to be used as a supply reference for a resistive divider to set this level.

58 SET HYSTERESIS INPUT-DATA FIELD (SETHYSD): When activated by a logical low level on the SFlELD pin, the

voltage applied to this pin in conjunction with three control register bits (HYSÐVTH0, HYSÐVTH1, HYSÐVTH2,

Bank (1,1), bits 7, 8, 9) determines the amount of hysteresis for the pulse detector’s hysteresis comparator. This level

should be set high enough to eliminate noise which might occur in the shouIder region between read pulses from the

preamplifier. The SVCC pin is provided to be used as a supply reference for a resistive divider to set this level.

59 SERVO FIELD AUTOMATIC GAIN CONTROL VOLTAGE INPUT (VAGCINS): When activated by a logical high level

on the SFIELD pin, the voltage at this pin controls the gain of the gain controlled amplifier.

and 18 kX to GND) should be connected to this pin to optimize the filter’s performance.

CC

Description

http://www.national.com7

Pin Definitions (Continued)

Ý

Pin

ANALOG SIGNAL PINS (Continued)

60 DATA FIELD AUTOMATIC GAIN CONTROL VOLTAGE INPUT (VAGCIND): When activated by a logical low level on

the SFIELD pin, the voltage at this pin controls the gain of the gain controlled amplifier.

62, 63 AMPLIFIER INPUTSÝ2,Ý1 (AMPIN2, AMPIN1): These inputs accept the preamplified, analog, coded data signal

read from the disk. They are to be externally capacitively coupled from the preamplifier. They go to a low impedance

state when WRITE GATE is enabled and remain low impedance for either 1.7 msor3.4ms (selectable by control

register bit, SLOW

remove DC offsets accumulated across the amplifier input coupling capacitors during the write mode.

64 AGC REFERENCE VOLTAGE INPUT (VREF): This input provides the reference voltage to the AGC circuit for

controlling the peak-to-peak signal swing at the channel input pins. The voltage on this pin corresponds directly to the

peak-to-peak channel input signal level. A resistor divider between supply and ground can be used to provide this

voltage. The SVCC pin is provided to be used as a supply reference.

70 SWITCHED SUPPLY VOLTAGE (SVCC): This emitter-follower output may be used as the supply for the external VREF

resistor voltage divider and for both the external servo and data hysteresis resistor voltage dividers. The voltage at this

pin will typically be V

71 DISCHARGE CAPACITOR (DISCAP): A capacitor is tied from this pin to ground to establish an RC time constant which

sets the minimum operational frequency and decay characteristics of the AGC. The voltage at this pin can also be used

for dynamic hysteresis. Note, unlike the DP8491/92 which requires an RC combination tied to this pin, the DISCAP pin

has an internal 10 kX resistor connected to ground. Thus, only an external capacitor is required to set the RC time

constant.

73 VOLTAGE CONTROLLED OSCILLATOR INPUT (VCOI): This pin is the input to the voltage control block for the

synchronizer VCO and is to be connected to the external loop filter output.

74 CHARGE PUMP OUTPUT (CPO): This pin issues the signal from the synchronizer PLL charge pump and is to be

connected to the external loop filter input.

76 RNOMINAL (RNOM): A resistor connected from this pin to ground sets the synchronizer charge pump current.

79 TIMING EXTRACTOR FILTER (TEF): This pin is the filter node for the synthesizer phase locked loop (PLL). An

external resistor and capacitor loop filter is tied in series between this pin and ground.

, Bank (1,1) bit 6, 0e3.4 ms) after WRITE GATE is disabled. This low impedance state is used to

b

1V. The voltage at this pin goes low in the sleep mode.

CC

Description

http://www.national.com 8

Power Down Operation

The DP84910 has several methods available to control or

manage device power consumption. Three control register

bits and two pins are provided to control the power status of

elements in this device. The control register bits control the

power status of the pulse detector (PDÐPWRÐDN, Bank

(1,0) bit 4), synchronizer (SYNCÐPWRÐDN, Bank (1,0) bit

2) and synthesizer (STHÐPWRÐDN, Bank (1,0) bit 3). The

device is configured to initially power up with the synchronizer, synthesizer and pulse detector powered down. The control register power is controlled only by the SLEEP

The SLEEP

pin is one of the two pins available for power

management. This pin powers down all circuitry on the chip

including the control register. In this mode the maximum

power supply current is 2 mA. The control register latches

are preset into specific states when exiting the sleep mode.

The shift register flip-flops, however, are in indeterminate

states until all 13 bits have been shifted in. Note that if the

CRL/S

input is given a positive transition after exiting the

sleep mode but before valid data has been entered into

the shift register, the indeterminate contents of the shift reg-

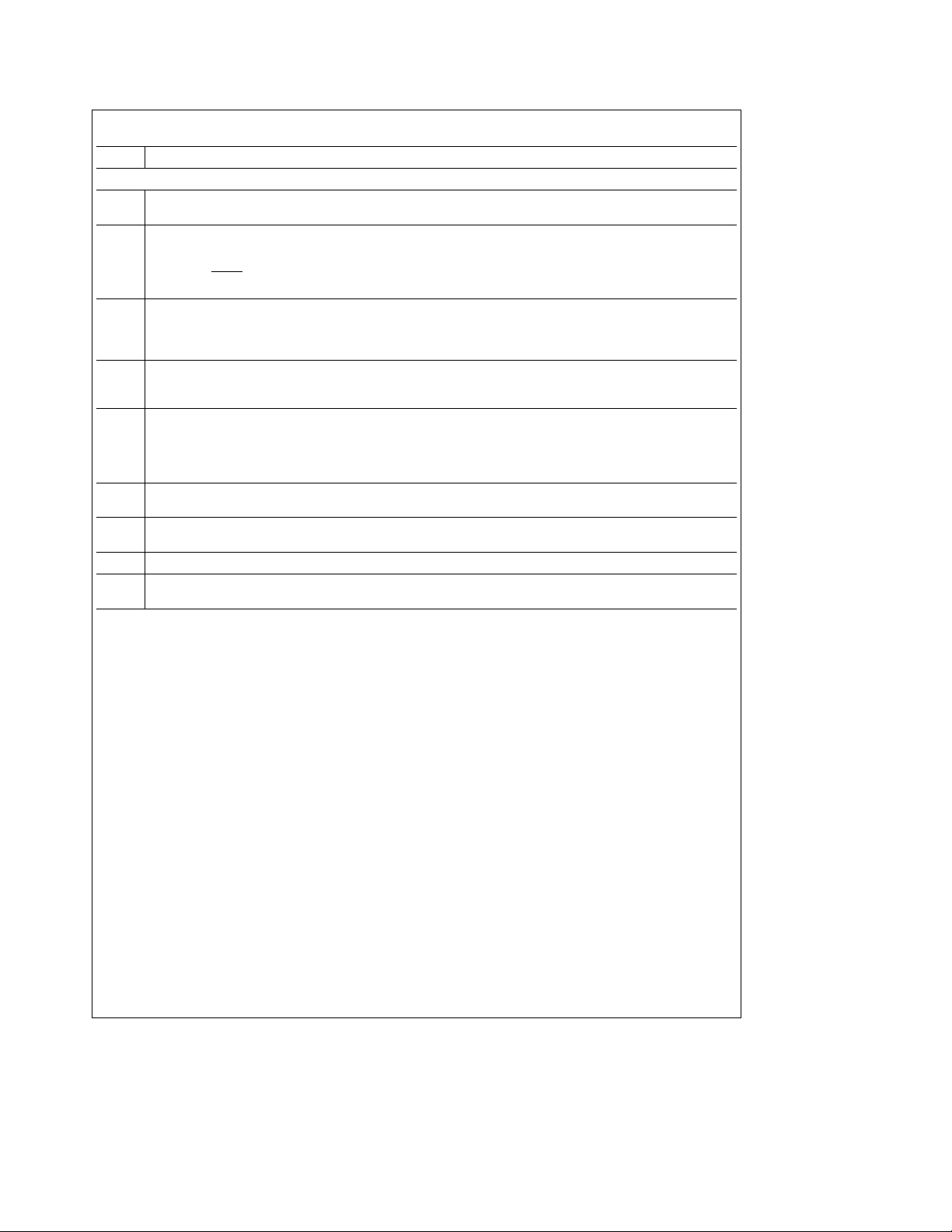

TABLE I. Selective Power Down Truth Table

Pin

IDLE/

SERVO

Pin

SLEEP

0 X X X X OFF OFF OFF OFF

1 1 0 0 0 OFF* ON** ON ON

1 1 0 0 1 OFF* ON** OFF ON

1 1 0 1 0 OFF* ON** ON OFF

1 1 0 1 1 OFF* ON** OFF OFF

10000ONONONON

1 0 0 0 1 ON ON OFF ON

1 0 0 1 0 ON ON ON OFF

1 0 0 1 1 ON ON OFF OFF

1 X 1 0 0 OFF ON** ON ON

1 X 1 0 1 OFF ON** OFF ON

1 X 1 1 0 OFF ON** ON OFF

1 X 1 1 1 OFF ON** OFF OFF

*Except for pulse detector circuitry biasing necessary for quick recovery from power down mode.

**Control register buffers powered down. Data in register will not be affected but new data cannot

be loaded into register when IDLE/SERVO

pin.

Ctrl Reg.

Bank (1,0)

B4 B3 B2

ister will be randomly loaded into one of the four banks of

latches. Although the sleep mode can be safely exited with

the CRL/S

into the shift register before CRL/S

pin either high or low, valid data must be loaded

is given a positive tran-

sition.

The IDLE/SERVO

pin is the second of the two pins available for power management. This pin toggles the device

between the idle and servo modes. In the idle mode, only

the control register and pulse detector biasing circuitry necessary for a quick recovery from the power down mode are

active. In the servo mode, the pulse detector portions needed for servo detection are active as well as the control register. Less than 15 ms is required for the pulse detector to

recover from the idle condition. The control register data is

not lost when this pin is toggled. This pin does not control

the power status of the synchronizer or synthesizer. To

achieve maximum power savings during extended servoonly activity, the synchronizer and synthesizer should be

powered down.

Power Status by Block

PD &

SERVO

is high.

CR SYNCH SYNTH

http://www.national.com9

Absolute Maximum Ratings are those

values beyond which the safety of the device cannot be

guaranteed. The device should not be operated at these

limits. The parametric values defined in the ‘‘Electrical Characterisitics’’ tables are not guaranteed at these ratings. The

‘‘Operating Conditions’’ table will define the conditions for

actual device operation.

Supply Voltage 7V

TTL Input Maximum Voltage 7V

Maximum Output Voltage 7V

Maximum Input Current (Analog Pins) 2 mA

(or as specified on per-pin basis)

ESD Susceptibility 1500V

(Note 1)

Operating Conditions guaranteed over operating temperature and supply voltage ranges unless otherwise speci-

fied. Minimum and/or maximum limits are guaranteed by outgoing testing unless otherwise specified.

Symbol Parameter Conditions Min

V

T

T

I

OH

I

OL

V

V

C

f

NRZ

CC

A

S

IH

IL

L

Supply Voltage 4.5 5.0 5.5 V

Operation Ambient Temperature 0 70

Storage Temperature

High Logic Level Output Current for TTL Outputs (Note 2)

Low Logic Level Output Current for TTL Outputs (Note 2) 8 mA

High Logic Level Input Voltage 2 V

Low Logic Level Input Voltage 0.8 V

Capacitive Load on Any TTL Output (Note 2) 15 pF

NRZ Transfer Rate Operating Frequency -36 7.5 36

-50 13.7 50

f

VCO

f

STH

f

XTL

t

PWH(XTL)

t

PWL(XTL)

t

PWH(ERDIN)

t

PWL(ERDIN)

t

PW(CRL/S)

t

SU(CRD)

t

H(CRD)

t

SU(CRL/S)

t

H(CRL/S)

t

PW(CRC)

I

RNOM

Note 1: Human body model is used. (120 pF through 1.5 kX)

Note 2: Parameter guaranteed by design or correlation data. No outgoing tests are performed.

Note 3: Typical values are specified at 25

Synchronizer VCO Operating Frequency (Note 2) 1.5 f

Synthesizer VCO Operating Frequency (Note 2) 1.5 f

Crystal Input Operating Frequency (Note 2) 20 MHz

Width of XTLIN Pulse (High) 20 ns

Width of XTLIN Pulse (Low) 20 ns

Width of ERDIN Pulse (High) 15 9 ns

Width of ERDIN Pulse (Low) 10 5 ns

Width of CRL/S Pulse (High or Low) (Note 2) 50 ns

CRD Setup Time with Respect to CRC (Note 2) 20 ns

CRD Hold Time with Respect to CRC (Note 2) 20 ns

CRL/S Setup Time with Respect to CRC (Note 2) 200 ns

CRL/S Hold Time with Respect to CRC (Note 2) 20 ns

CRC Pulse Width (High or Low) (Note 2) 25 ns

RNOM Pin Current 90 130 170 mA

C and 5V supply.

§

b

Typ

(Note 3)

Max Units

65 150

b

400 mA

NRZ

NRZ

C

§

C

§

Mb/s

MHz

MHz

http://www.national.com 10

Loading...

Loading...