NSC DM7493AN, DM7490AN, DM5490J Datasheet

DM5490/DM7490A, DM7493A

Decade and Binary Counters

General Description

Each of these monolithic counters contains four masterslave flip-flops and additional gating to provide a divide-bytwo counter and a three-stage binary counter for which the

count cycle length is divide-by-five for the 90A and divideby-eight for the 93A.

All of these counters have a gated zero reset and the 90A

also has gated set-to-nine inputs for use in BCD nine’s complement applications.

To use their maximum count length (decade or four-bit binary), the B input is connected to the Q

count pulses are applied to input A and the outputs are as

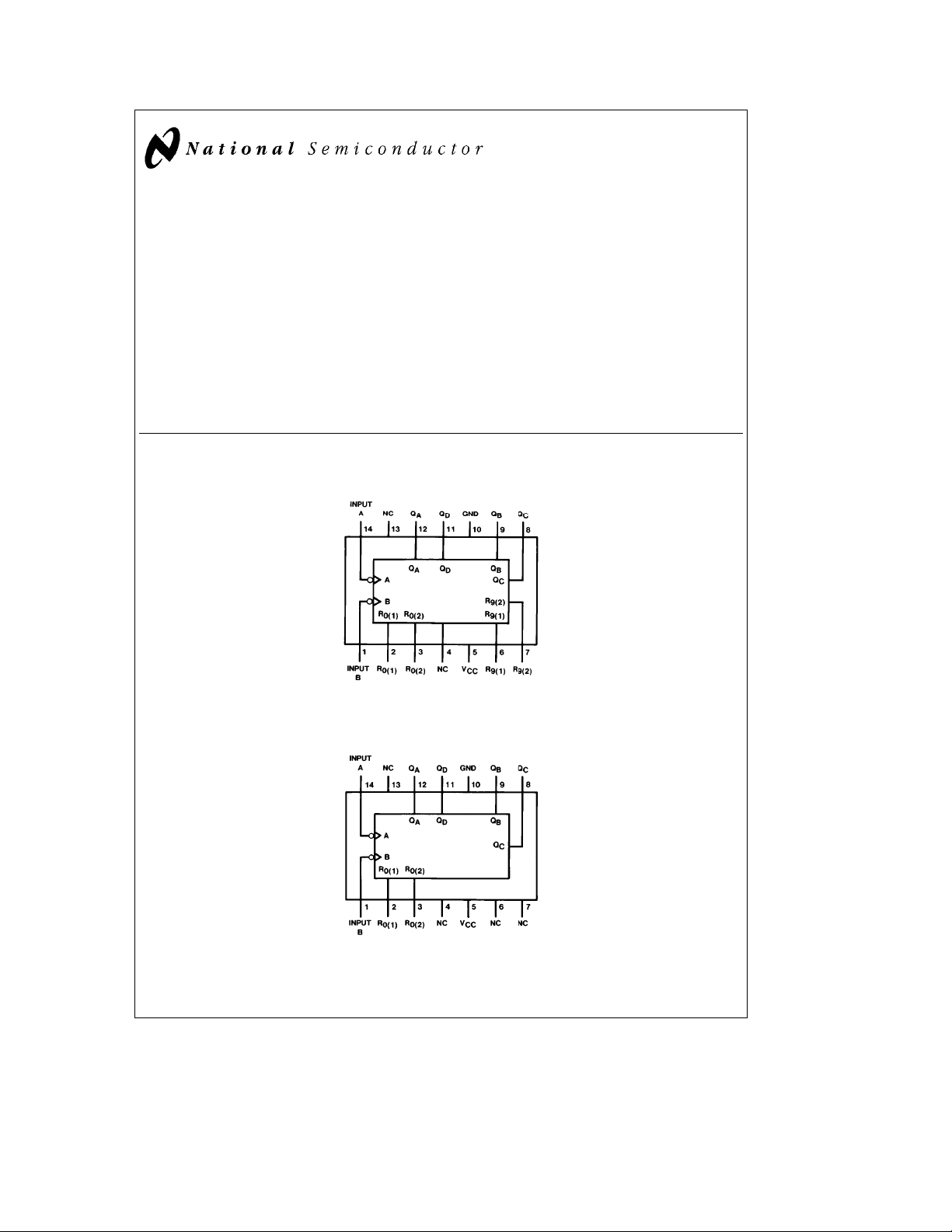

Connection Diagrams

output. The input

A

Dual-In-Line Package

July 1992

described in the appropriate truth table. A symmetrical divide-by-ten count can be obtained from the 90A counters by

connecting the Q

input count to the B input which gives a divide-by-ten square

wave at output Q

output to the A input and applying the

D

.

A

Features

Y

Typical power dissipation

Ð 90A 145 mW

Ð 93A 130 mW

Y

Count frequency 42 MHz

DM5490/DM7490A, DM7493A

Decade and Binary Counters

Order Number DM5490J, DM5490W or DM7490AN

See NS Package Number J14A, N14A or W14B

Dual-In-Line Package

Order Number DM7493AN

See NS Package Number N14A

C

1995 National Semiconductor Corporation RRD-B30M105/Printed in U. S. A.

TL/F/6533

TL/F/6533– 1

TL/F/6533– 2

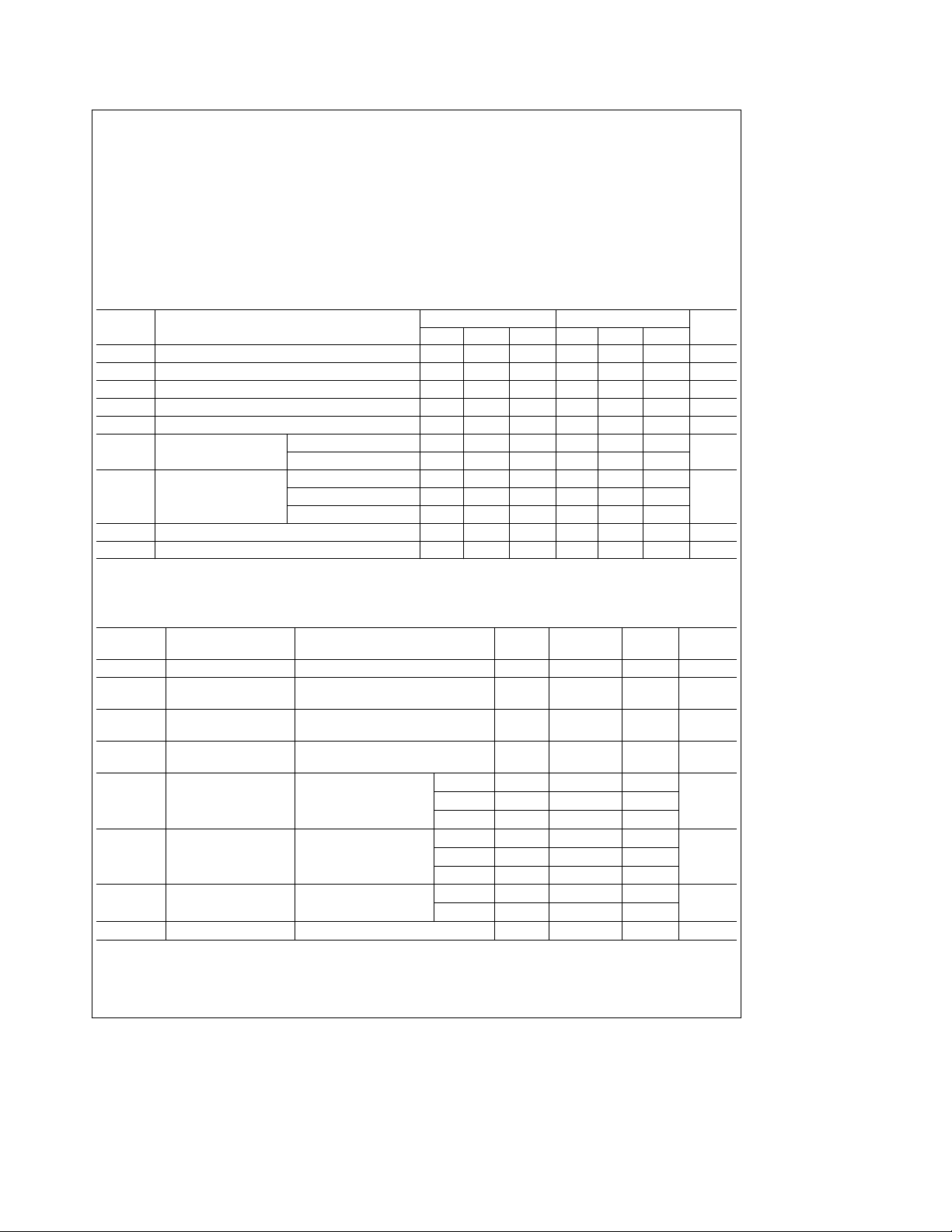

Absolute Maximum Ratings (Note)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage 7V

Input Voltage 5.5V

Operating Free Air Temperature Range

DM54

DM74 0

Storage Temperature Range

b

55§Ctoa125§C

Ctoa70§C

§

b

65§Ctoa150§C

Recommended Operating Conditions

Symbol Parameter

V

V

V

I

I

f

t

t

T

CC

IH

IL

OH

OL

CLK

W

REL

A

Supply Voltage 4.5 5 5.5 4.75 5 5.25 V

High Level Input Voltage 2 2 V

Low Level Input Voltage 0.8 0.8 V

High Level Output Current

Low Level Output Current 16 16 mA

Clock Frequency A 0 32 0 32

(Note 5)

Pulse Width A 15 15

(Note 5)

B 0 16 0 16

B3030ns

Reset 15 15

Reset Release Time (Note 5) 25 25 ns

Free Air Operating Temperature

The ‘‘Absolute Maximum Ratings’’ are those values

Note:

beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The

parametric values defined in the ‘‘Electrical Characteristics’’

table are not guaranteed at the absolute maximum ratings.

The ‘‘Recommended Operating Conditions’’ table will define

the conditions for actual device operation.

DM5490 DM7490A

Min Nom Max Min Nom Max

b

0.8

b

0.8 mA

Units

MHz

b

55 125 0 70

C

§

’90A Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Symbol Parameter Conditions Min

e

V

I

V

OH

V

OL

I

I

I

IH

I

IL

I

OS

I

CC

Note 1: All typicals are at V

Note 2: Not more than one output should be shorted at a time.

Note 3: I

Note 4: Q

Note 5: T

Input Clamp Voltage V

High Level Output V

Voltage V

Low Level Output V

Voltage V

Input Current@Max V

Input Voltage

High Level Input V

Current V

Low Level Input V

Current V

Short Circuit V

Output Current (Note 2)

Supply Current V

e

e

5V, T

CC

A

is measured with all outputs open, both RO inputs grounded following momentary connection to 4.5V, and all other inputs grounded.

CC

outputs are tested at I

A

e

25§C and V

A

e

Max plus the limit value of IILfor the B input. This permits driving the B input while maintaining full fan-out capability.

OL

e

5V.

CC

25§C.

CC

CC

IL

CC

IH

CC

CC

I

CC

I

CC

CC

e

e

e

e

eb

Min, I

e

Min, I

Max, V

e

Min, I

Min, V

e

Max, V

e

Max A 80

2.7V

I

OH

OL

IL

e

e

IH

e

e

e

I

12 mA

Max

Min

Max

Max (Note 4)

5.5V

2.4 3.4 V

Reset 40 mA

B 120

e

Max A

0.4V

Reset

B

e

Max DM54

DM74

e

Max (Note 3) 29 42 mA

b

b

2

Typ

(Note 1)

Max Units

b

1.5 V

0.2 0.4 V

1mA

b

3.2

b

1.6 mA

b

4.8

20

18

b

57

b

57

mA

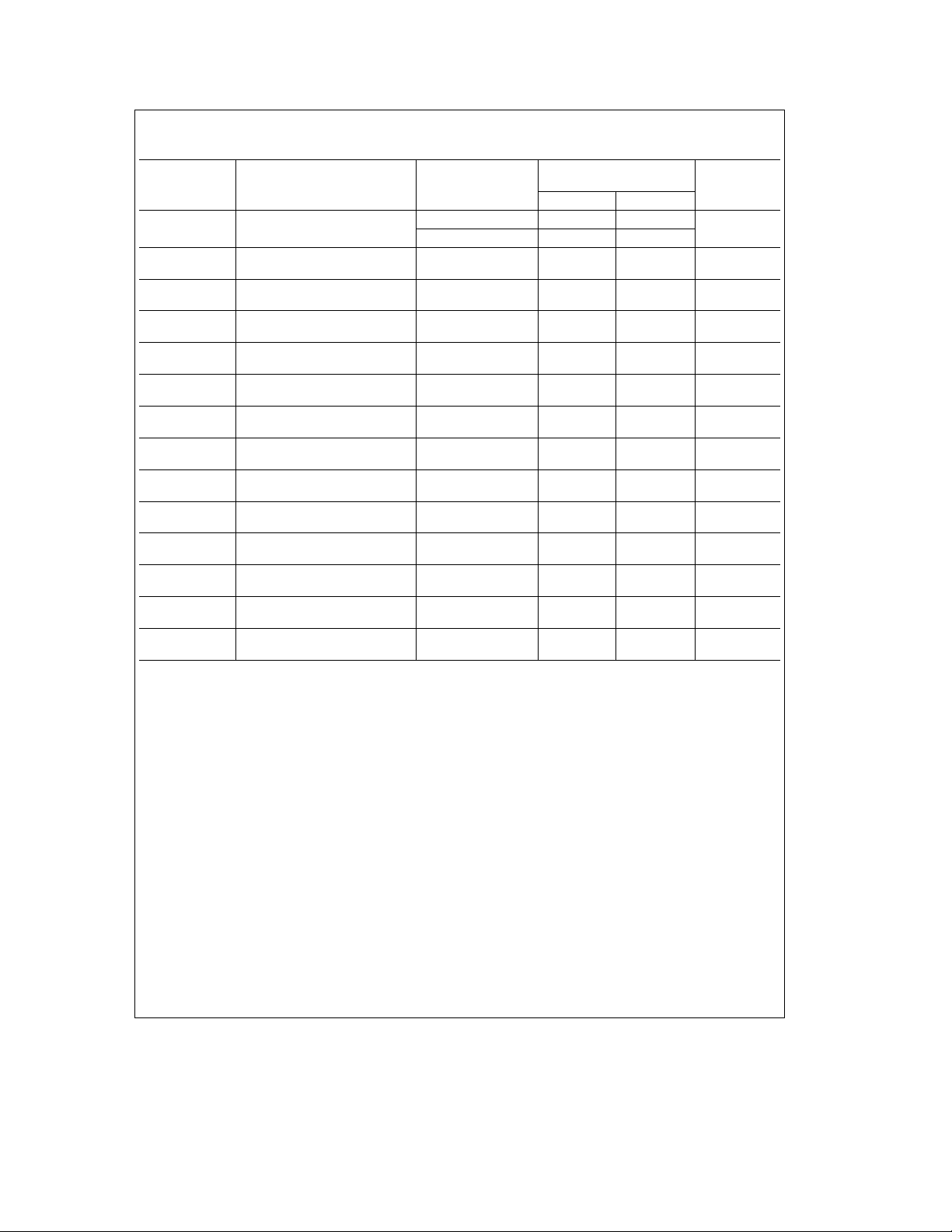

’90A Switching Characteristics

at V

CC

e

5V and T

e

25§C (See Section 1 for Test Waveforms and Output Load)

A

Symbol Parameter

f

MAX

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PHL

Maximum Clock A to Q

Frequency

Propagation Delay Time

Low to High Level Output

Propagation Delay Time

High to Low Level Output

Propagation Delay Time

Low to High Level Output

Propagation Delay Time

High to Low Level Output

Propagation Delay Time

Low to High Level Output

Propagation Delay Time

High to Low Level Output

Propagation Delay Time

Low to High Level Output

Propagation Delay Time

High to Low Level Output

Propagation Delay Time

Low to High Level Output

Propagation Delay Time

High to Low Level Output

Propagation Delay Time SET-9 to

Low to High Level Output Q

Propagation Delay Time SET-9 to

High to Low Level Output Q

Propagation Delay Time SET-0

High to Low Level Output Any Q

From (Input)

To (Output)

A

BtoQ

B

AtoQ

A

AtoQ

A

AtoQ

D

AtoQ

D

BtoQ

B

BtoQ

B

BtoQ

C

BtoQ

C

BtoQ

D

BtoQ

D

A,QD

B,QC

e

R

400X

L

e

C

15 pF Units

L

Min Max

32

16

16 ns

18 ns

48 ns

50 ns

16 ns

21 ns

32 ns

35 ns

32 ns

35 ns

30 ns

40 ns

40 ns

MHz

3

Loading...

Loading...