NSC DAC1208LCJ-1, DAC1208LCJ Datasheet

February 1995

MICRO-DACTMDAC1208/DAC1209/DAC1210/DAC1230/

DAC1231/DAC1232 12-Bit, mP Compatible,

Double-Buffered D to A Converters

MICRO-DAC DAC1208/DAC1209/DAC1210/DAC1230/DAC1231/DAC1232

12-Bit, mP Compatible, Double-Buffered D to A Converters

General Description

The DAC1208 and the DAC1230 series are 12-bit multiplying D to A converters designed to interface directly with a

wide variety of microprocessors (8080, 8048, 8085, Z-80,

etc.). Double buffering input registers and associated control lines allow these DACs to appear as a two-byte ‘‘stack’’

in the system’s memory or I/O space with no additional interfacing logic required.

The DAC1208 series provides all 12 input lines to allow single buffering for maximum throughput when used with 16-bit

processors. These input lines can also be externally configured to permit an 8-bit data interface. The DAC1230 series

can be used with an 8-bit data bus directly as it internally

formulates the 12-bit DAC data from its 8 input lines. All of

these DACs accept left-justified data from the processor.

The analog section is a precision silicon-chromium (Si-Cr)

R-2R ladder network and twelve CMOS current switches.

An inverted R-2R ladder structure is used with the binary

weighted currents switched between the I

maintaining a constant current in each ladder leg indepen-

OUT1

and I

OUT2

dent of the switch state. Special circuitry provides TTL logic

input voltage level compatibility.

The DAC1208 series and DAC1230 series are the 12-bit

members of a family of microprocessor compatible DACs

(MICRO-DACs

TM

). For applications requiring other resolutions, the DAC1000 series for 10-bit and DAC0830 series

for 8-bit are available alternatives.

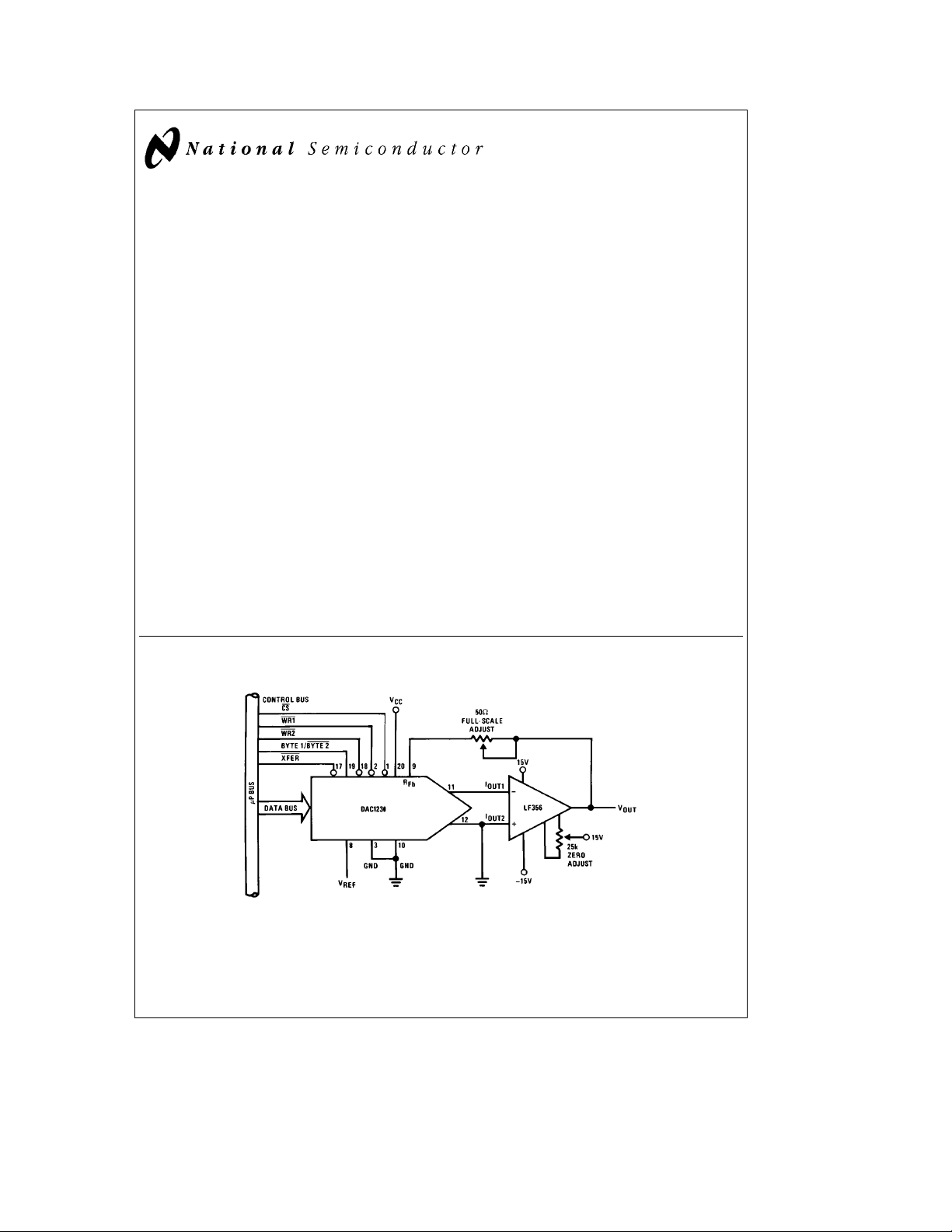

Typical Application

Features

Y

Linearity specified with zero and full-scale adjust only

Y

Direct interface to all popular microprocessors

Y

Double-buffered, single-buffered or flow through digital

data inputs

Y

Logic inputs which meet TTL voltage level specs (1.4V

logic threshold)

Y

Works withg10V referenceÐfull 4-quadrant

multiplication

Y

Operates stand-alone (without mP) if desired

Y

All parts guaranteed 12-bit monotonic

Y

DAC1230 series is pin compatible with the DAC0830

series 8-bit MICRO-DACs

Key Specifications

Y

Current Settling Time 1 ms

Y

Resolution 12 Bits

Y

Linearity (Guaranteed

over temperature) 10, 11, or 12 Bits of FS

Y

Gain Tempco 1.3 ppm/§C

Y

Low Power Dissipation 20 mW

Y

Single Power Supply 5 VDCto 15 V

DC

TL/H/5690– 1

TRI-STATEÉis a registered trademark of National Semiconductor Corp.

TM

MICRO-DAC

C

1995 National Semiconductor Corporation RRD-B30M115/Printed in U. S. A.

is a trademark of National Semiconductor Corp.

TL/H/5690

Absolute Maximum Ratings

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

(Notes 1 and 2)

Supply Voltage (V

Voltage at Any Digital Input VCCto GND

Voltage at V

Storage Temperature Range

Package Dissipation at T

(Note 3)

DC Voltage Applied to I

(Note 4)

ESD Susceptability 800V

Electrical Characteristics

e

V

10.000 VDC,V

REF

Note 13); all other limits T

Parameter Conditions Notes

)17V

REF

CC

Input

b

e

25§C.

65§Ctoa150§C

b

100 mV to V

e

25§C 500 mW

A

or I

OUT1

OUT2

e

11.4 VDCto 15.75 VDCunless otherwise noted. Boldface limits apply from T

CC

e

T

A

J

DC

g

25V

CC

Operating Conditions

Lead Temperature (Soldering, 10 sec.) 300§C

Temperature Range T

DAC1208LCJ, DAC1209LCJ,

DAC1210LCJ, DAC1230LCJ,

DAC1231LCJ, DAC1232LCJ,

DAC1231LIN, DAC1232LIN

DAC1208LCJ-1, DAC1210LCJ-1,

DAC1230LCJ-1, DAC1231LCJ-1,

DAC1232LCJ-1, DAC1231LCN,

DAC1232LCN, DAC1231LCWM,

DAC1232LCWM 0

Range of V

CC

Voltage at Any Digital Input VCCto GND

Typ

(Note 10)

Tested Design

Limit Limit Units

(Note 5) (Note 6)

s

MIN

b

40§CsT

CsT

§

4.75 VDCto 16 V

to T

MIN

A

A

T

A

s

s

MAX

s

a

a

Resolution 12 12 12 Bits

Linearity Error Zero and Full-Scale 4, 7, 13

(End Point Linearity) Adjusted

Differential Non-Linearity Zero and Full-Scale 4, 7, 13

DAC1208, DAC1230

DAC1209, DAC1231

DAC1210, DAC1232

Adjusted

DAC1208, DAC1230

DAC1209, DAC1231

DAC1210, DAC1232

g

0.018g0.018 %ofFSR

g

0.024g0.024 %ofFSR

g

0.050g0.05 %ofFSR

g

0.018g0.018 %ofFSR

g

0.024g0.024 %ofFSR

g

0.050g0.05 %ofFSR

Monotonicity 4 12 12 12 Bits

Gain Error (Min) Using Internal R

Gain Error (Max)

e

V

ref

g

10V,g1V

Fb

Gain Error Tempco 7

Power Supply Rejection All Digital Inputs

Reference Input Resistance (Min)

Reference Input Resistance (Max) 15 20 20

Output Feedthrough Error V

Output Capacitance All Data Inputs I

Latched High

13

e

20 Vp-p, fe100 kHz

REF

All Data Inputs Latched 9 3.0 mVp-p

Low

Latched High I

All Data Inputs I

Latched Low I

OUT1

OUT2

OUT1

OUT2

b

7

7

7

0.1 0.0 % of FSR

b

0.1

g

1.3

g

3.0

b

0.2 % of FSR

g

6.0 ppm of FS/§C

g

30 ppm of FSR/V

15 10 10

200 pF

70 pF

70 pF

200 pF

kX

Supply Current Drain 13 2.0 2.5 mA

Output Leakage Current

I

OUT1

I

OUT2

Digital Input Threshold Low Threshold 13 0.8 0.8 V

Digital Input Currents Digital Inputsk0.8V 13

All Data Inputs Latched 11, 13 0.1 15 15 nA

Low

All Data Inputs Latched 11, 13 0.1 15 15 nA

High

High Threshold 13 2.2 2.2 V

b

Digital Inputsl2.2V 13 10 10 mA

200

b

200 mA

DC

DC

T

DC

DC

MAX

85§C

70§C

DC

(see

2

Electrical Characteristics (Continued)

e

V

10.000 VDC,V

REF

Note 13); all other limits T

Symbol Parameter Conditions

e

11.4 VDCto 15.75 VDCunless otherwise noted. Boldface limits apply from T

CC

e

e

T

A

25§C.

J

See Typ

Note (Note 10)

to T

MIN

MAX

Tested Design

Limit Limit Units

(Note 5) (Note 6)

AC CHARACTERISTICS

OUT1

IL

IL

IL

IL

IL

IL

REF

e

e

e

e

e

e

or I

b

e

t

s

t

W

t

DS

t

DH

t

CS

t

CH

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: This 500 mW specification applies for all packages. The low intrinsic power dissipation of this part (and the fact that there is no way to significantly modify

the power dissipation) removes concern for heat sinking.

Note 4: Both I

example, if V

Note 5: Tested and guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 6: Design limits are guaranteed but not 100% tested. These limits are not used to calculate outgoing quality levels. Guaranteed for V

and V

Note 7: The unit FSR stands for full-scale range. Linearity Error and Power Supply Rejection specs are based on this unit to eliminate dependence on a particular

V

REF

performing a zero and full-scale adjustment, the plot of the 4096 analog voltage outputs will each be within 0.012%

zero and full-scale. The unit ppm of FSR(parts per million of full-scale range) and ppm of FS(parts per million of full-scale) are used for convenience to define specs

of very small percentage values, typical of higher accuracy converters. In this instance, 1 ppm of FSR

output voltage quantity. For example, the gain error tempco spec of

b

40§Ctoa85§Cofg(6)(V

Note 8: This spec implies that all parts are guaranteed to operate with a write pulse or transfer pulse width (t

100 ns. The entire write pulse must occur within the valid data interval for the specified t

Note 9: To achieve this low feedthrough in the D package, the user must ground the metal lid. If the lid is left floating the feedthrough is typically 6 mV.

Note 10: Typicals are at 25

Note 11: A 10 nA leakage current with R

Note 12: Human body model, 100 pF discharged through a 1.5 kX resistor.

Note 13: Tested limit for

Current Setting Time V

Write and XFER V

Pulse Width Min. 320

Data Setup Time Min. V

Data Hold Time Min. V

Control Setup Time Min. V

Control Hold Time Min. V

and I

OUT1

e

REF

eb

10V toa10V.

REF

value to indicate the true performance of the part. The Linearity Error specification of the DAC1208 is 0.012% of FSR(max). This guarantees that after

must go to ground or the virtual ground of an operational amplifier. The linearity error is degraded by approximately V

OUT2

10Vthena1mVoffset, VOS,onI

/106)(125§C) org0.75 (10

REF

C and represent the most likely parametric norm.

§

b

1 suffix parts applies only at 25§C.

e

Fb

20k and V

e

0V, V

0V, V

0V, V

0V, V

0V, V

0V, V

OUT2

3

)V

10V corresponds to a zero error of (10c10

5V 1.0 ms

IH

e

5V

IH

e

5V 70 320

IH

e

5V 30 90

IH

e

5V 60 320

IH

e

5V 0 10

IH

will introduce an additional 0.01% linearity error.

g

6 ppm of FS/§C represents a worst-case full-scale gain error change with temperature from

which isg0.075% of V

REF

8

W,tDS,tDH

50 320

c

V

e

V

/106is the conversion factor to provide an actual

REF

.

REF

) of 320 ns. A typical part will operate with tWof only

W

and tSto apply.

b

9

c

20c103)c100% 10V or 0.002% of FS.

CC

of a straight line which passes through

REF

320

90

320

e

11.4V to 15.75V

d

OS

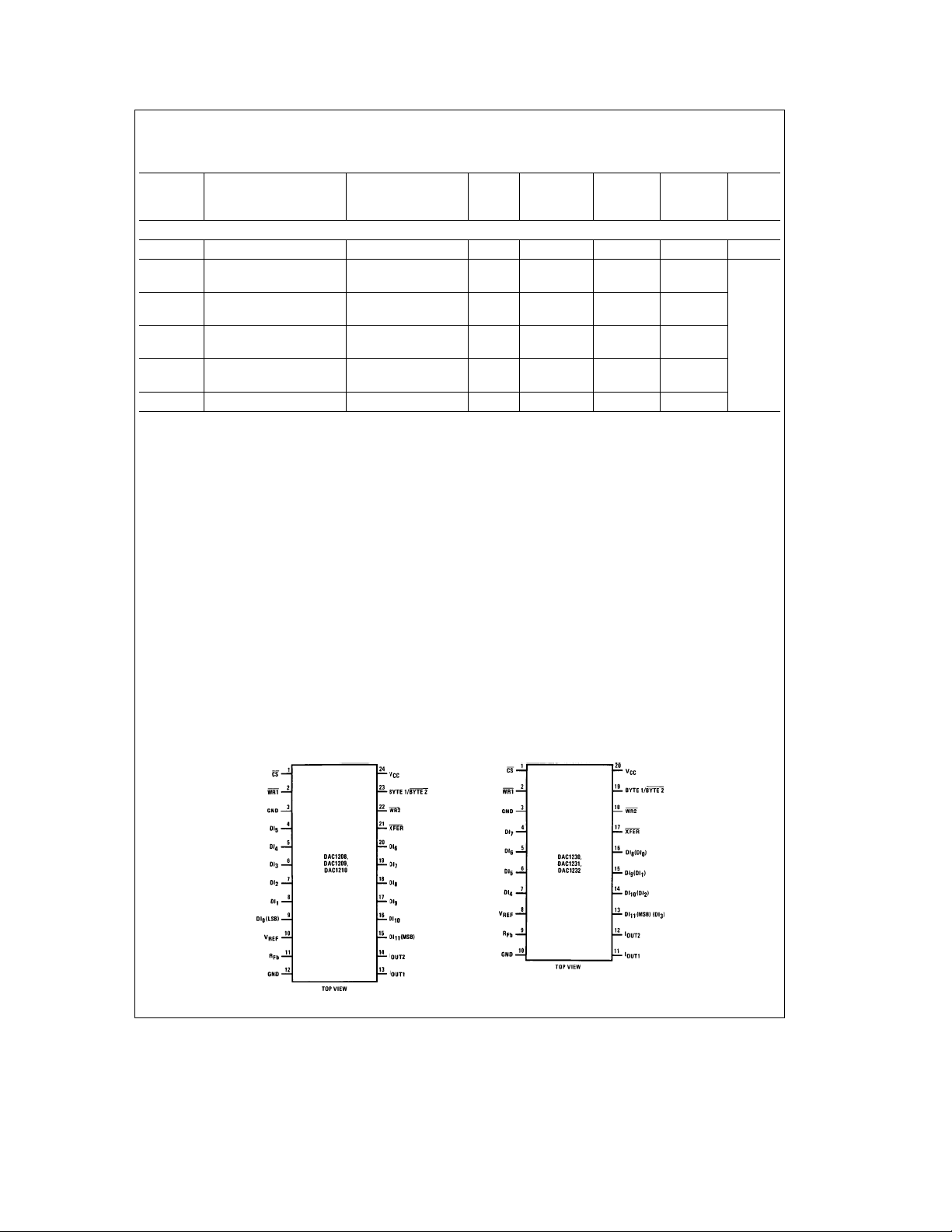

Connection Diagrams

Dual-In-Line Package Dual-In-Line Package

(see

ns

V

. For

REF

See Ordering Information

TL/H/5690– 2

3

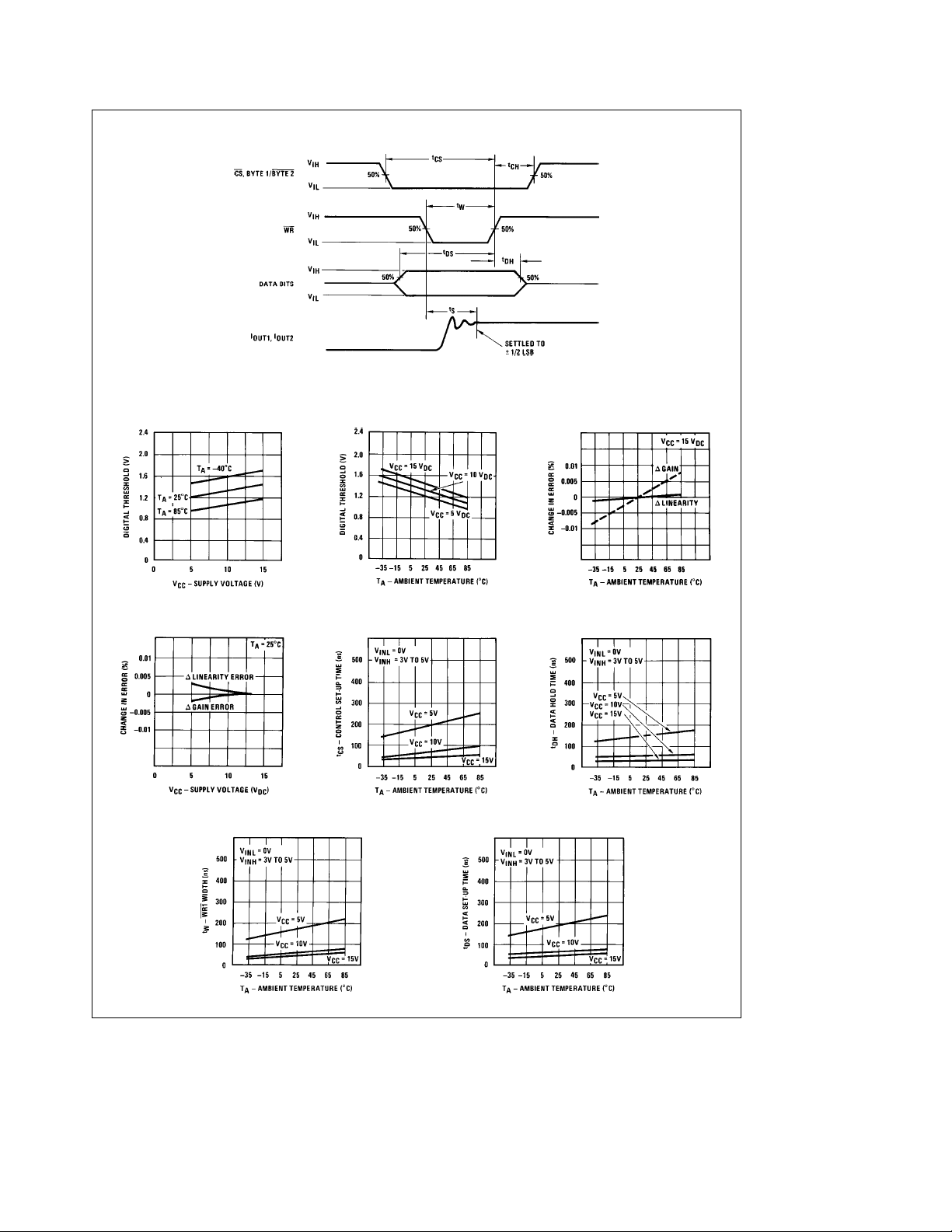

Switching Waveforms

Typical Performance Characteristics

Digital Input Threshold

vs V

CC

Digital Input Threshold vs

Temperature

TL/H/5690– 3

Gain and Linearity Error

Variation vs Temperature

Gain and Linearity Error

Variation vs Supply Voltage Control Set-Up Time, t

Write Pulse Width, t

W

4

CS

Data Set-Up Time, t

Data Hold Time, t

DS

DH

TL/H/5690– 4

Definition of Package Pinouts

CONTROL SIGNALS (all control signals are level actuated)

CS: Chip Select (active low). The CS will enable WR1.

WR1: Write 1. The active low WR1 is used to load the digital

data bits (DI) into the input latch. The data in the input latch

is latched when WR1

into two latches. One holds the first 8 bits, while the other

holds 4 bits. The Byte 1/Byte 2

both latches when Byte 1/Byte 2

4-bit input latch when in the low state.

Byte 1/Byte 2

high, all 12 locations of the input latch are enabled. When

low, only the four least significant locations of the input latch

are enabled.

WR2

: Write 2 (active low). The WR2 will enable XFER.

XFER: Transfer Control Signal (active low). This signal, in

combination with WR2

available in the input latches to transfer to the DAC register.

DI

to DI11: Digital Inputs. DI0is the least significant digital

0

input (LSB) and DI

(MSB).

I

: DAC Current Output 1. I

OUT1

digital code of all 1s in the DAC register, and is zero for all

0s in the DAC register.

I

: DAC Current Output 2. I

OUT2

I

,orI

OUT1

voltage). This constant current is

OUT1

divided by the reference input resistance.

: Feedback Resistor. The feedback resistor is provided

R

Fb

on the IC chip for use as the shunt feedback resistor for the

external op amp which is used to provide an output voltage

for the DAC. This on-chip resistor should always be used

(not an external resistor) since it matches the resistors in

the on-chip R-2R ladder and tracks these resistors over

temperature.

V

: Reference Voltage Input. This input connects an ex-

REF

ternal precision voltage source to the internal R-2R ladder.

V

can be selected over the range of 10V tob10V. This

REF

is also the analog voltage input for a 4-quadrant multiplying

DAC application.

V

: Digital Supply Voltage. This is the power supply pin for

CC

the part. V

optimum for 15 V

CC

GND: Pins 3 and 12 of the DAC1208, DAC1209, and

DAC1210 must be connected to ground. Pins 3 and 10 of

is high. The 12-bit input latch is split

control pin is used to select

is high or to overwrite the

: Byte Sequence Control. When this control is

, causes the 12-bit data which is

is the most significant digital input

11

is a maximum for a

OUT1

is a constant minus

a

I

OUT2

V

REF

OUT2

e

constant (for a fixed reference

c

1

b

1

4096

#

J

can be from 5 VDCto 15 VDC. Operation is

.

DC

the DAC1230, DAC1231, and DAC1232 must be connected

to ground. It is important that I

potential for current switching applications. Any difference

of potential (V

change of

For example, if V

mV offset from I

0.03%.

on these pins) will result in a linearity

OS

e

10V and these ground pins are 9

REF

and I

OUT

1

and I

3V

OUT

OUT

V

OS

REF

OUT

1

, the linearity change will be

2

2

are at ground

Definition of Terms

Resolution: Resolution is defined as the reciprocal of the

number of discrete steps in the DAC output. It is directly

related to the number of switches or bits within the DAC. For

example, the DAC1208 has 2

has 12-bit resolution.

Linearity Error: Linearity error is the maximum deviation

from a

straight line passing through the endpoints of the

DAC transfer characteristic

for zero and full-scale. Linearity error is a parameter intrinsic

to the device and cannot be externally adjusted.

National’s linearity test (a) and the best straight line test (b)

used by other suppliers are illustrated below. The best

straight line (b) requires a special zero and FS adjustment

for each part, which is almost impossible for the user to

determine. The end point test uses a standard zero FS adjustment procedure and is a much more stringent test for

DAC linearity.

Power Supply Sensitivity: Power supply sensitivity is a

measure of the effect of power supply changes on the DAC

full-scale output.

Settling Time: Full-scale current settling time requires zero

to full-scale or full-scale to zero output change. Settling time

is the time required from a code transition until the DAC

output reaches within

Full-Scale Error: Full-scale error is a measure of the output

error between an ideal DAC and the actual device output.

Ideally, for the DAC1208 or DAC1230 series, full-scale is

b

V

1 LSB. For V

REF

V

FULL-SCALE

error is adjustable to zero.

e

10.0000Vb2.44 mVe9.9976V. Full-scale

Differential Non-Linearity: The difference between any

two consecutive codes in the transfer curve from the theoretical 1 LSB is differential non-linearity.

Monotonic: If the output of a DAC increases for increasing

digital input code, then the DAC is monotonic. A 12-bit DAC

which is monotonic to 12 bits simply means that input increasing digital input codes will produce an increasing analog output.

12

or 4096 steps and therefore

. It is measured after adjusting

g

(/2 LSB of the final output value.

e

10V and unipolar operation,

REF

a) End Point Test After Zero

and FS Adjust

b) Shifting FS Adjust to Pass

TL/H/5690– 5

Best Straight Line Test

5

Application Hints

1.0 DIGITAL INTERFACE

These DACs are designed to provide all of the necessary

digital input circuitry to permit a direct interface to a wide

variety of microprocessor systems. The timing and logic level convention of the input control signals allow the DACs to

be treated as a typical memory device or I/O peripheral with

no external logic required in most systems. Essentially

these DACs can be mapped as a two-byte stack in memory

(or I/O space) to receive their 12 bits of input data in two

successive 8-bit data writing sequences. The DAC1230 series is intended for use in systems with an 8-bit data bus.

The DAC1208 series provides all 12 digital input lines which

can be externally configured to be controlled from an 8-bit

bus or can be driven directly from a 16-bit data bus.

All of the digital inputs to these DACs contain a unique

threshold regulator circuit to maintain TTL voltage level

compatibility independent of the applied V

Any input can also be driven from higher voltage CMOS

logic levels in non-microprocessor based systems. To prevent damage to the chip from static discharge, all unused

digital inputs should be tied to V

shooting aid, if any digital input is inadvertently left floating,

the DAC will interpret the pin as a logic ‘‘1’’.

Double buffered digital inputs allow the DAC to internally

format the 12-bit word used to set the current switching R2R ladder network (see section 2.0) from two 8-bit data

write cycles.

ters and their controlling logic circuitry. The timing diagrams

for updating the DAC output are shown in sections 1.1, 1.2

and 1.3 for three possible control modes. The method used

depends strictly upon the particular application.

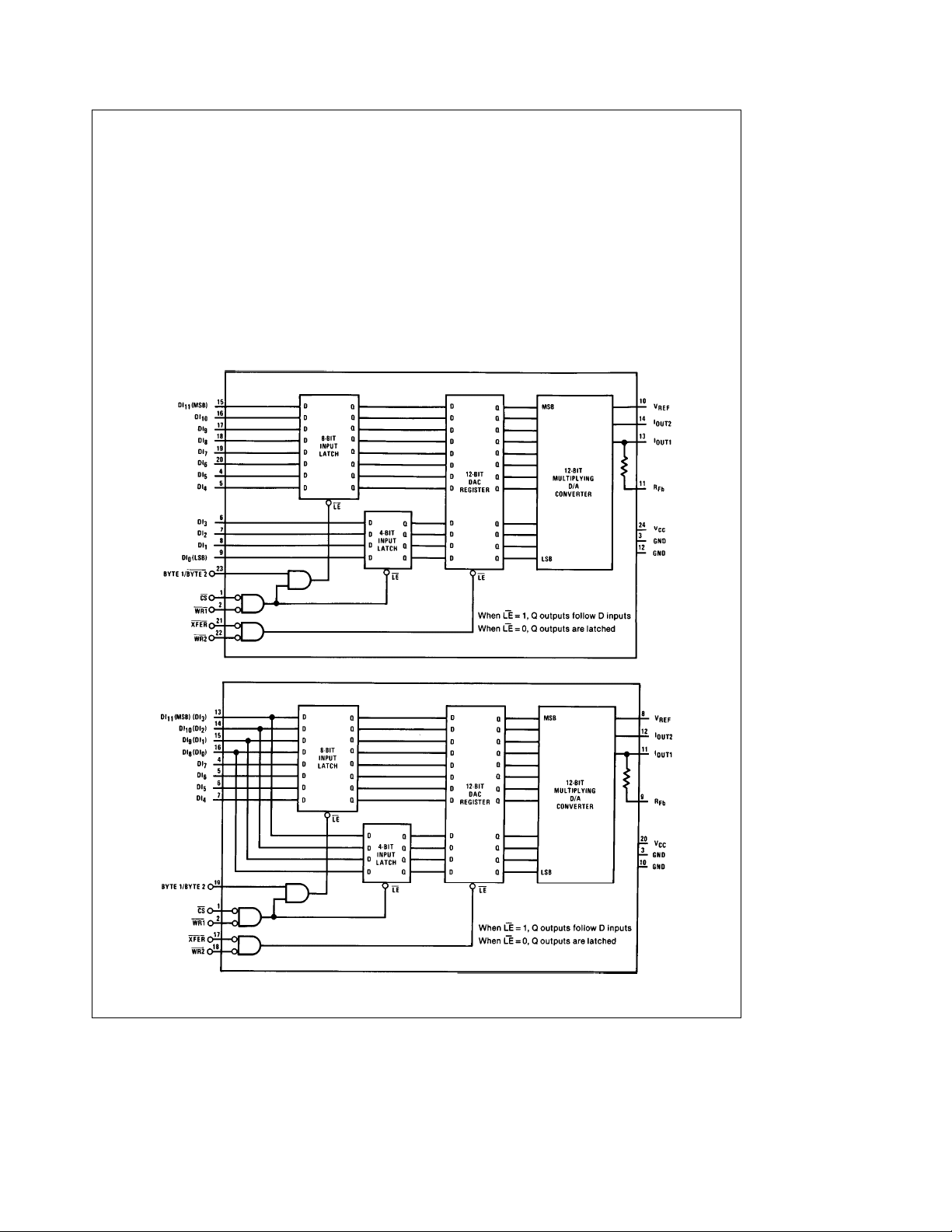

Figures 1

and2show the internal data regis-

or ground. As a trouble-

CC

to the DAC.

CC

FIGURE 1. DAC1208, DAC1209, DAC1210 Functional Diagram

FIGURE 2. DAC1230, DAC1231, DAC1232 Functional Diagram

6

TL/H/5690– 6

Loading...

Loading...