NOVATEK NT68F62, NT68F62U Datasheet

NT68F62

8-Bit Microcontroller for Monitor (32K Flash MTP Type)

Features

Operating voltage range: 4.5V to 5.5V

CMOS technology for low power consumption

6502 8-bit CMOS CPU core

8 MHz operation frequency

32K bytes of flash memory for Multi -Times Program

512 bytes of RAM

2Kbytes Masked BootROM for ISP.

One 8-bit base timer

13 channels of 8-bit PWM outputs with 5V open drain

4 channel A/D converters with 6-bit resolution

25 bi-directional I/O port pins (8 dedicated I/O pins)

Hsync/Vsync signals processor for separate &

composite signals, including hardware sync signals

polarity detection and freq. counters with 2 sets of

Hsync counting intervals

Hsync/Vsync polarity controlled output, 5 selectable

free run output signals and self-test patterns, automute function, half freq. I/O function

Two built-in IIC bus interfaces support VESA

DDC1/2B+

General Description

The NT68F62 is a new generation of monitor µC for autosync and digital control applications. Particularly, this chip

supports various functions to allow users to easily develop

USB monitors. It contains the 6502 8-bit CPU core, 512

bytes of RAM for use as working RAM and as stack area,

32K bytes of Flash memory, 13-channels of 8-bit PWM D/A

converters, 4-channel A/D converters for detection of keys

which can save I/O pins, one 8-bit pre-loadable base timer,

an internal Hsync and Vsync signals processor and a

watch-dog timer, which prevents the system from abnormal

Two layers of interrupt management

NMI interrupt sources

- INTE0 (External INT with selectable edge trigger)

- INTMUTE (Auto Mute Activated)

IRQ interrupt sources

- INTS0/1 (SCL Go-low INT)

- INTA0/1 (Slave Address Matched INT)

- INTTX0/1 (Shift Register INT)

- INTRX0/1 (Shift Register INT)

- INTNAK0/1 (No Acknowledge)

- INTSTOP0/1 (Stop Condition Occurred INT)

- INTE1 (External INT with Selectable Edge Trigger)

- INTV (VSYNC INT)

- INTMR (Base Timer INT)

- INTADC (AD Conversion Done INT)

Hardware watch-dog timer function

40-pin P-DIP and 42-pin S-DIP packages

operation and two IIC bus interfaces. The user can store

EDID data in the 128 bytes of RAM for DDC1/2B, so that

the user can reduce a dedicated EEPROM for EDID. The

half frequency output function can save the external oneshot circuit. All of these designs are borne of our

committment to offer our user savings on component costs.

The 42 pin S-DIP IC provides two additional I/O pins –

port40 & port41, Part number NT68F62U represents the SDIP IC. For future reference, port40 & port42 are only

available for the 42 pin S-DIP IC.

1 V1.0

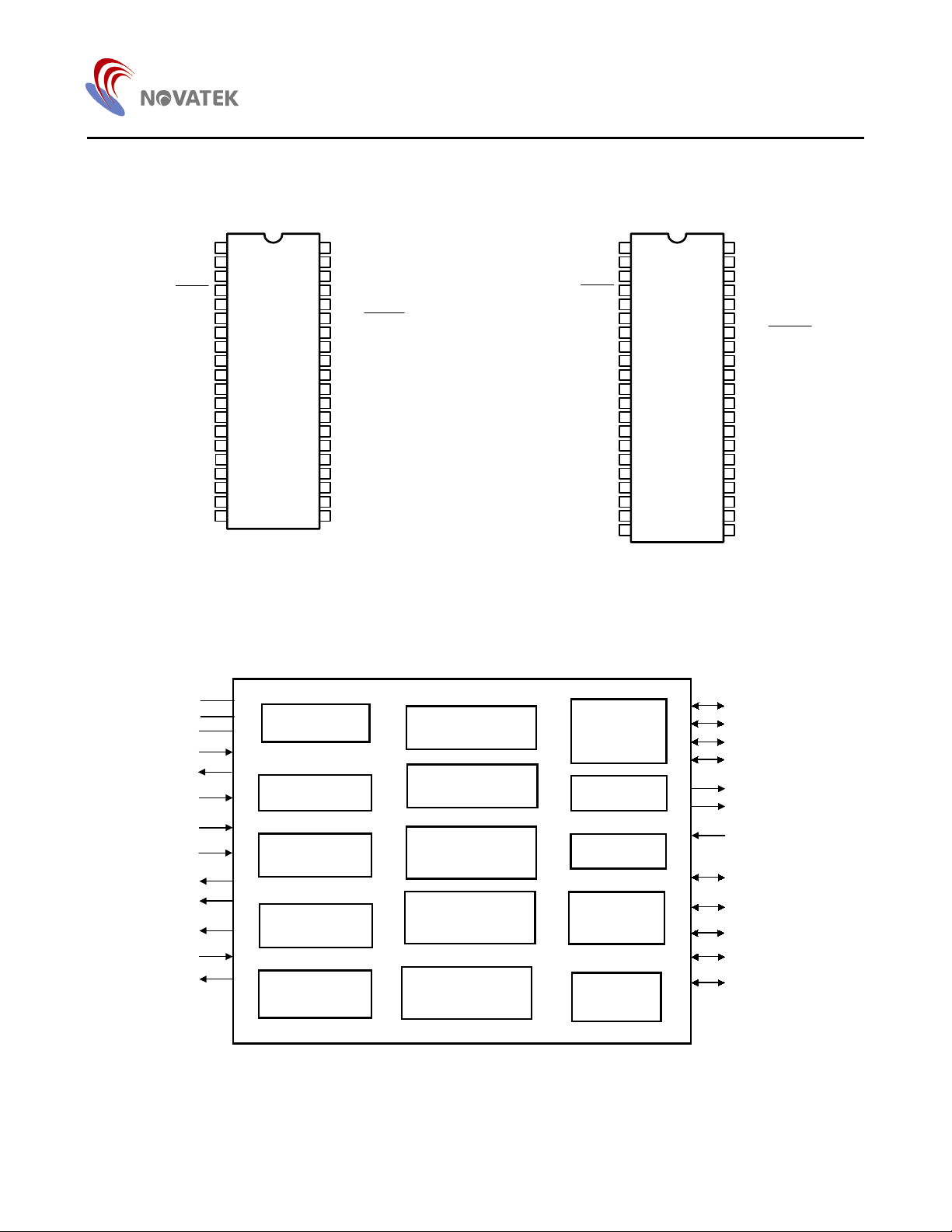

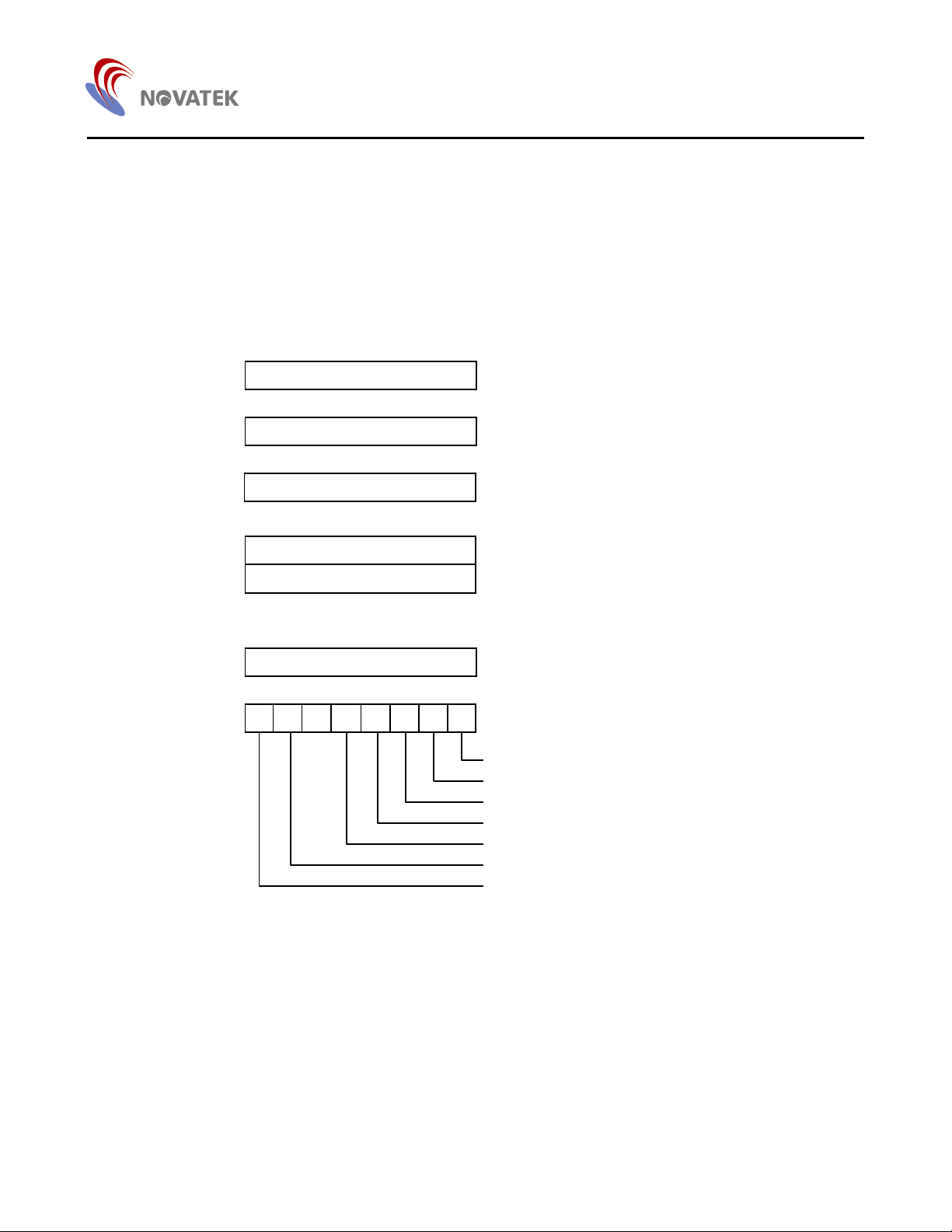

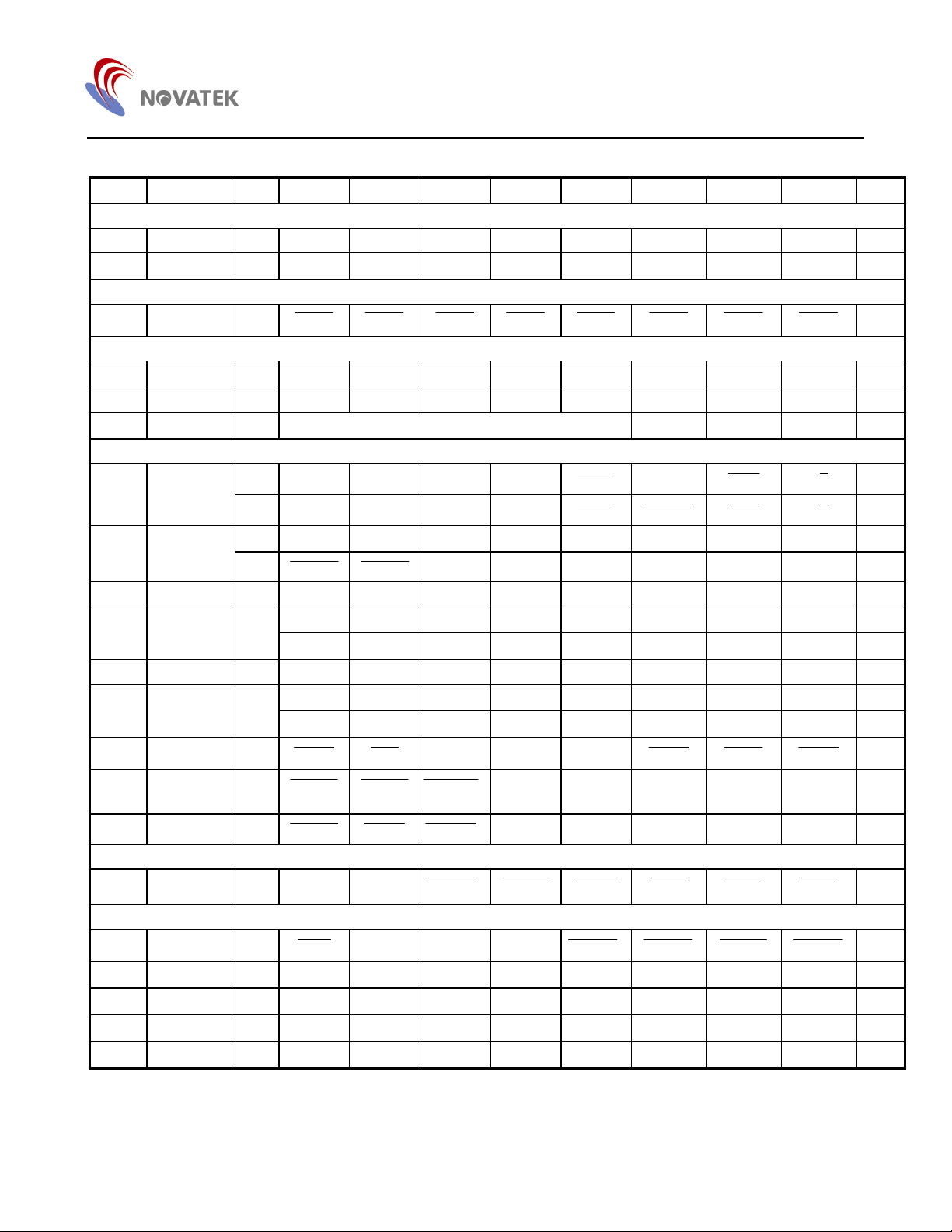

Pin Configurations

40-Pin P-DIP 42-Pin S-DIP

40

39

38

37

36

35

34

33

NT68F62

32

31

30

29

28

27

26

25

24

23

22

21

VSYNCI/INTV [XA8]

HSYNCI[0]

DAC3 [NV]

DAC4/SCL1 [ERASE]

DAC5/SDA1 [MASS]

DAC6 [EXRSTB]

CREG[TMR]

P07/HSYNCO [XA1]

P06/VSYNCO [XA0]

P05/DAC12 [XY5]

P04/DAC11 [XY4]

P03/DAC10 [XY3]

P02/DAC9 [XY2]

P01/DAC8 [XY1]

P00/DAC7 [XY0]

P31/SCL0 [XA7]

P30/SDA0 [XA6]

P20 [DB0]

P21 [DB1]

P22 [DB2]

VDD

P40

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

NT68F62U

[PG] DAC2

[0] DAC1/ADC3

[YE] DAC0/ADC2

[VPP] RESET

[8MHZ]OSCO

[0]OSCI

[OE/SE] P15/INTE0

[XE] P14/PATTERN

[XA5] P13/HALFI

[XA4] P12/HALFO

[XA3] P11/ADC1

[XA2] P10/ADC0

[1]P16/INTE1

[DB7] P27

[DB6] P26

[DB5] P25

[DB4] P24

[DB3] P23

* [ ]: Flash Mode

[PG] DAC2

[0] DAC1/ADC3

[YE] DAC0/ADC2

[VPP] RESET

VDD

GND

[8MHZ]OSCO

[OE/SE] P15/INTE0

[XE] P14/PATTERN

[0]OSCI

[XA5] P13/HALFI

[XA4] P12/HALFO

[XA3] P11/ADC1

[XA2] P10/ADC0

[1]P16/INTE1

[DB7] P27

[DB6] P26

[DB5] P25

[DB4] P24

[DB3] P23

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

* [ ]: Flash Mode

42

VSYNCI/INTV [XA8]

41

HSYNCI[0]

40

DAC3 [NV]

39

DAC4/SCL1 [ERASE]

38

DAC5/SDA1 [MASS]

P41

37

DAC6 [EXRSTB]

36

CREG[TMR]

35

P07/HSYNCO [XA1]

34

33

P06/VSYNCO [XA0]

P05/DAC12 [XY5]

32

31

P04/DAC11 [XY4]

30

P03/DAC10 [XY3]

P02/DAC9 [XY2]

29

P01/DAC8 [XY1]

28

P00/DAC7 [XY0]

27

26

P31/SCL0 [XA7]

25

P30/SDA0 [XA6]

24

P20 [DB0]

23

P21 [DB1]

P22 [DB2]

22

NT68F62

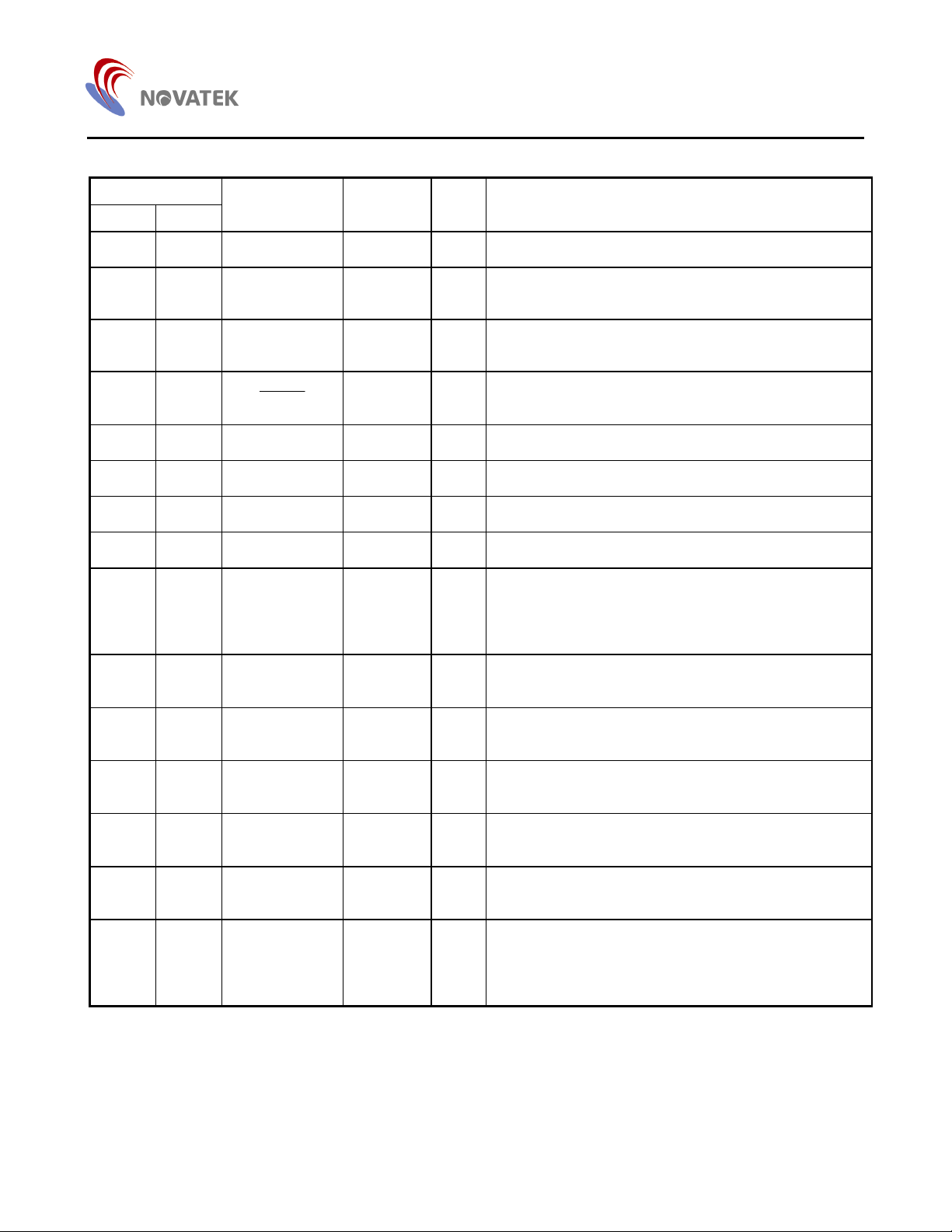

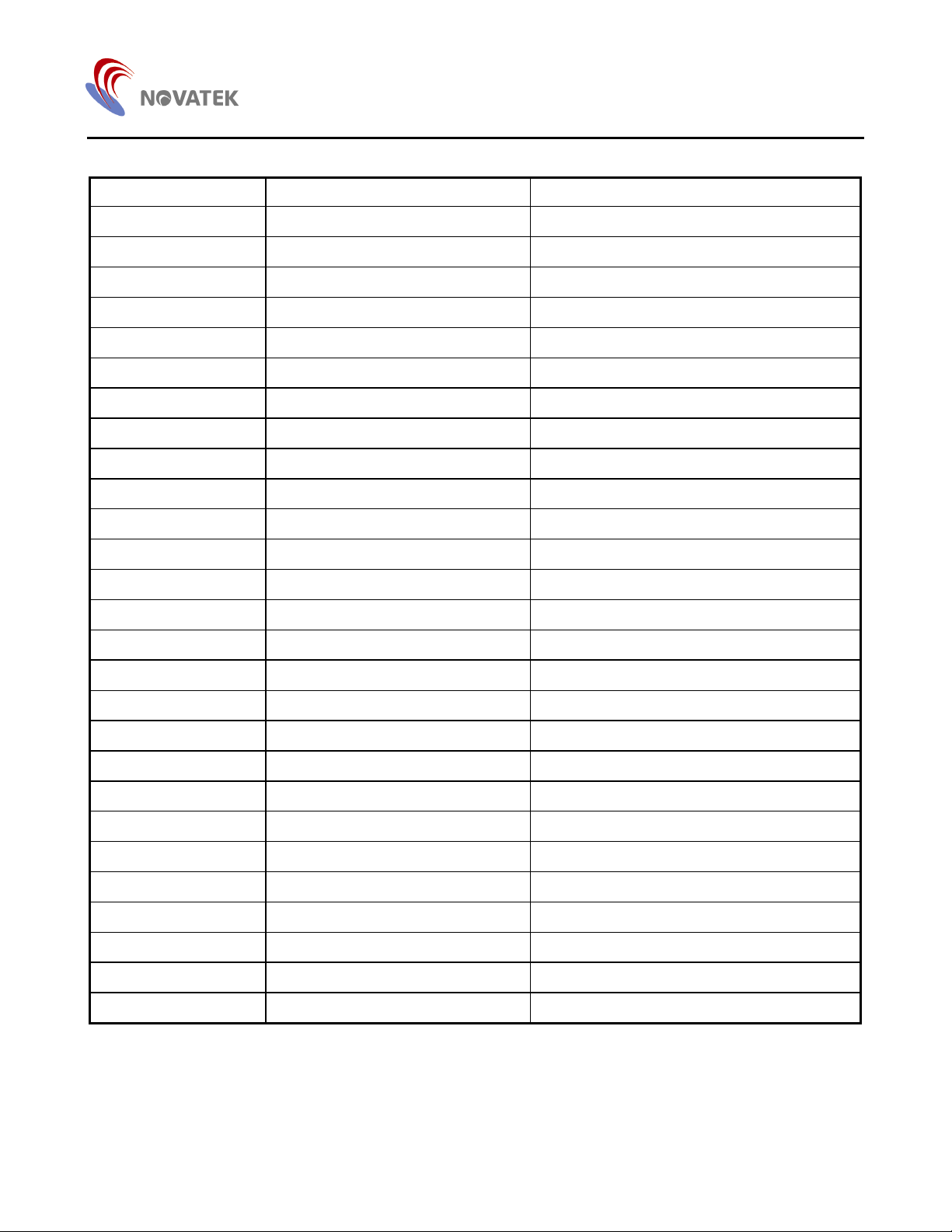

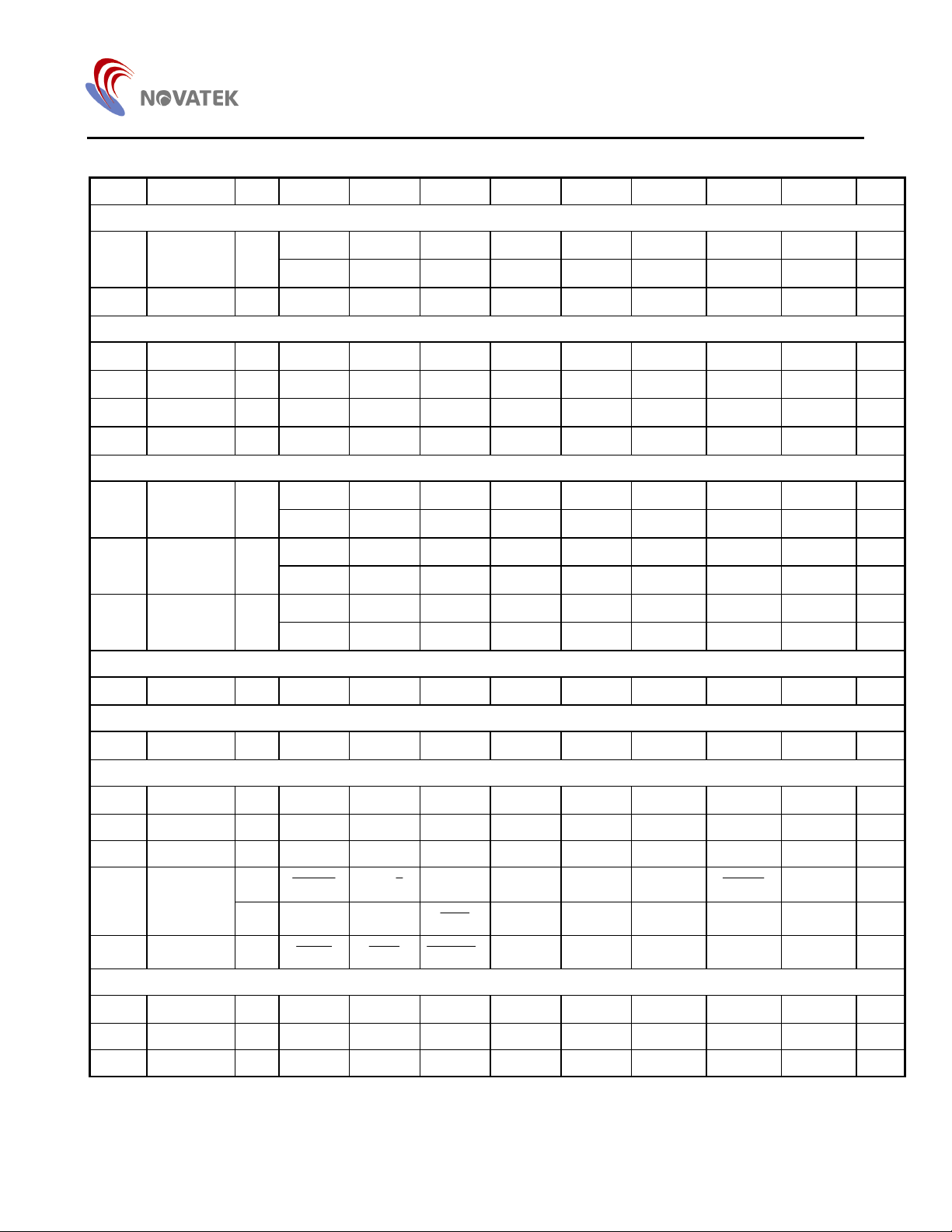

Block Diagram

V

DD

CREG

GND

OSCI

OSCO

INTE0/1

VSYNCI/INTV

HSYNCI

VSYNCO

HSYNCO

PATTERN

HALFI

HALFO

Voltage

Regulator

Timing Generator

CPU core

6502

Interrupt

Controller

H/V Sync Signals

Processor

32KB Flash memory &

2KB BootROM

SRAM + STACK

512 Bytes

8-Bit Base Timer

Watch Dog Timer

JEDEC Control

Block

IIC BUS

PWM DACs

A/D Converter

I/O Ports

ISP Control

Block

SCL0

SDA0

SCL1

SDA1

DAC0 - DAC7

DAC8 - DAC12

ADC0 - ADC3

P00 - P07

P10 - P16

P20 - P27

P30 - P31

P40 - P41

2

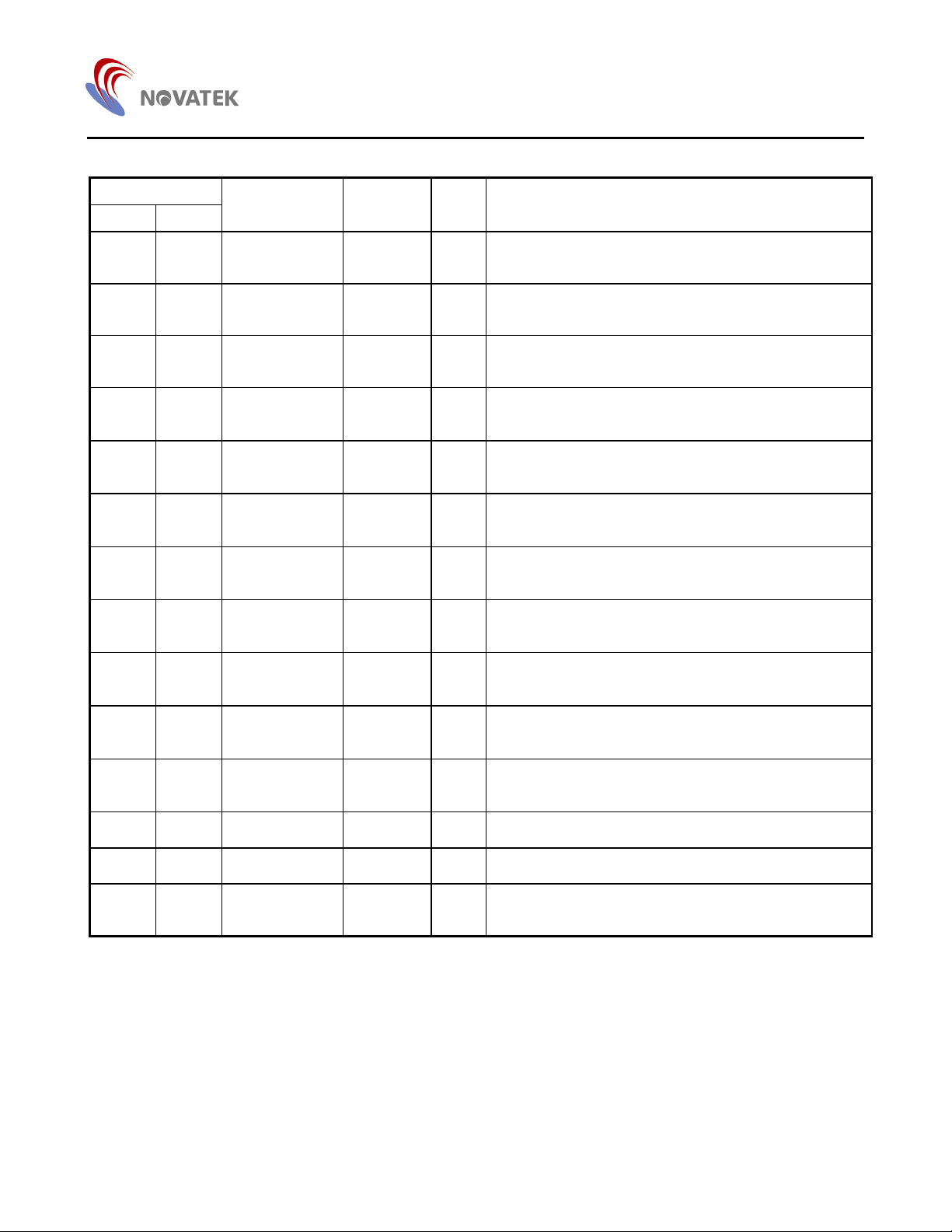

Pin Description

Pin No.

40 Pin 42 Pin

1 1 DAC2 O Open drain 5V, D/A converter output 2

Designation Reset Init. I/O Description

NT68F62

2 2 DAC1/ADC3 DAC1 O

3 3 DAC0/ADC2 DAC0 O

4 4

5 5 VDD P Power

6 7 GND P Ground

7 8 OSCO O Crystal OSC output

8 9 OSCI I Crystal OSC input

9 10 P15/INTE0 I/O

10 11 P14/PATTERN I/O

11 12 P13/HALFI P13 I/O

RESET

I

Open drain 5V, D/A converter output 1, shared with the A/D

converter channel 3 input

Open drain 5V, D/A converter output 0, shared with the A/D

converter channel 2 input

Schmitt Trigger input pin, low active reset with internal

pulled down 50KΩ resistor *

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with input pin of external interrupt source0 (NMI),

withSchmitt trigger, selectable triggered, and internal pulled

up 22KΩ resistor

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with the output of the self test pattern

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with the half hsync input

12 13 P12/HALFO P12 I/O

13 14 P11/ADC1 P11 I/O

14 15 P10/ADC0 P10 I/O

15 16 P16/INTE1 P16 I/O

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with the half hsync output

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with the A/D converter channel 1 input

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with the A/D converter channel 0 input

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with input pin of external interrupt source1, with

Schmitt Trigger, selectable triggered, and an internal pulled

up 22KΩ resistor

3

Pin Description (continued)

NT68F62

Pin No.

40 Pin 42 Pin

16 - 23 17 - 24 P27 – P20 I/O

24 25 P30/SDA0 P30 I/O

25 26 P31/SCL0 P31 I/O

26 27 P00/DAC7 P00 I/O

27 28 P01/DAC8 P01 I/O

28 29 P02/DAC9 P02 I/O

29 30 P03/DAC10 P03 I/O

30 31 P04/DAC11 P04 I/O

Designation Reset Init. I/O Description

Bi-directional I/O pin, push-pull structure with high current

drive/sink capability

Open drain 5V bi-directional I/O pin P30, shared with the

SDA0 pin of IIC bus Schmitt Trigger buffer

Open drain 5V bi-directional I/O pin P31, shared with the

SCL0 pin of IIC bus Schmitt Trigger buffer

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with open drain 5V D/A converter output 7

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with the open drain 5V D/A converter output 8

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with the open drain 5V D/A converter output 9

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with the open drain 5V D/A converter output 10

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with the open drain 5V D/A converter output 11

31 32 P05/DAC12 P05 I/O

32 33 P06/VSYNCO P06 I/O

33 34 P07/HSYNCO P07 I/O

34 35 DAC7 O Open drain 5V, D/A converter output 7

35 36 DAC6 O Open drain 5V, D/A converter output 6

36 38 DAC5/SDA1 DAC5 O

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with the open drain 5V D/A converter output 12

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with the vsync out

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

shared with the hsync out

Open drain 5V, D/A converter output 5, shared with open

drain SDA1 line of IIC bus, Schmitt Trigger buffer

4

Pin Description (continued)

NT68F62

Pin No.

40 Pin 42 Pin

37 39 DAC4/SCL1 DAC4 O

38 40 DAC3 O Open drain 5V, D/A converter output 3

39 41 HSYNCI I

40 42 VSYNCI/INTV VSYNCI I

- 6 P40 I/O

- 37 P41 I/O

* This RESET pin must be pulled high by an external pulled-up resistor (5KΩ suggestion), or it will remain at low voltage to

continually rest system.

Designation Reset Init. I/O Description

Open drain 5V, D/A converter output 4, shared with the

open drain SCL1 line of IIC bus, Schmitt Trigger buffer

Debouncing & Schmitt Trigger input pin for video horizontal

sync signal, internal pull high, shared with the composite

sync input

Debouncing & Schmitt trigger input pin for video vertical

sync signal, internal pull high, shared with the input pin of

the external interrupt source, intv, with Schmitt Trigger,

selectable triggered and internal pulled up 22KΩ resistor

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

only 42 pin S-DIP available

Bi-directional I/O pin with internal pulled up 22KΩ resistor,

only 42 pin S-DIP available

5

NT68F62

Functional Description

1. 6502 CPU

The 6502 is an 8-bit CPU that provides 56 instructions, decimal and binary arithmetic, thirteen addressing modes, true

indexing capability, programmable stack pointer and variable length stack, a wide selection of addressable memory ranges,

and interrupt input options.

The CPU clock cycle is 4MHz (8MHz system clock divided by 2). Please refer to the 6502 data sheet for more detailed

information.

07

Accumnlator A

7

Index Register Y

70

Index Register X

Program Counter PCH

PCL

70

7

Stack Pointer SP

7

NV

B

0

815

0

0

C

ZID

Status Register P

Carry

Zero

IRQ Disable

Decimal Mode

BRK Command

Overflow

Negative

1=TRUE

1=Result ZERO

1=DISABLE

1=TRUE

1=BRK

1=TRUE

1=NEG

Figure 1.1. The 6502 CPU Registers and Status Flags

6

2. Instruction Set List

Instruction Code Meaning Operation

NT68F62

ADC Add with carry

AND Logical AND

ASL Shift left one bit

BCC Branch if carry clears

BCS Branch if carry sets

BEQ Branch if equal to zero

BIT Bit test

BMI Branch if minus

BNE Branch if not equal to zero

BPL Branch if plus

BRK Break

BVC Branch if overflow clears

BVS Branch if overflow sets

CLC Clear carry

CLD Clear decimal mode

A + M + C → A, C

A•M → A

C ← M7…M0 ← 0

Branch on C = 0

Branch on C = 1

Branch on Z = 1

A•M, M7→N, M6→V

Branch on N = 1

Branch on Z = 0

Branch on N = 0

Forced Interrupt PC+2↓ PC↓

Branch on V = 0

Branch on V = 1

0 → C

0 → D

CLI Clear interrupt disable bit

CLV Clear overflow

CMP Compare Accumulator to memory

CPX Compare with index register X

CPY Compare with index register Y

DEC Decrement memory by one

DEX Decrement index X by one

DEY Decrement index Y by one

EOR Logical exclusive-OR

INC Increment memory by one

INX Increment index X by one

INY Increment index Y by one

0 → I

0 → V

A - M

X - M

Y - M

M - 1 → M

X - 1 → X

Y - 1 → Y

A ⊕ M→A

M + 1 → M

X + 1 → X

Y + 1 → Y

7

Instruction Set List (continued)

Instruction Code Meaning Operation

NT68F62

JMP Jump to new location

JSR Jump to subroutine

LDA Load accumulator with memory

LDX Load index register X with memory

LDY Load index register Y with memory

LSR Shift right one bit

NOP No operation No operation (2 cycles)

ORA Logical OR

PHA Push accumulator on stack

PHP Push status register on stack

PLA Pull accumulator from stack

PLP Pull status register from stack

ROL Rotate left through carry

ROR Rotate right through carry

RTI Return from interrupt

RTS Return from subroutine

(PC+1)→ PCL, (PC+2)→ PCH

PC+2↓, (PC+1)→ PCL, (PC+2)→ PCH

M → A

M → X

M → Y

0 → M7…M0 → C

A + M → A

A ↓

P ↓

A ↑

P ↑

C ← M7…M0 ← C

C → M7…M0 → C

P ↑, PC ↑

PC ↑, PC+1 → PC

SBC Subtract with borrow

SEC Set carry

SED Set decimal mode

SEI Set interrupt disable status

STA Store accumulator in memory

STX Store index register X in memory

STY Store index register Y in memory

TAX Transfer accumulator to index X

TAY Transfer accumulator to index Y

TSX Transfer stack pointer to index X

TXA Transfer index X to accumulator

TXS Transfer index X to stack pointer

TYA Transfer index Y to accumulator

* Refer to 6502 programming data book for more details.

A - M - C → A, C

1 → C

1 → D

1 → I

A → M

X → M

Y → M

A → X

A → Y

S → X

X → A

X → S

Y → A

8

NT68F62

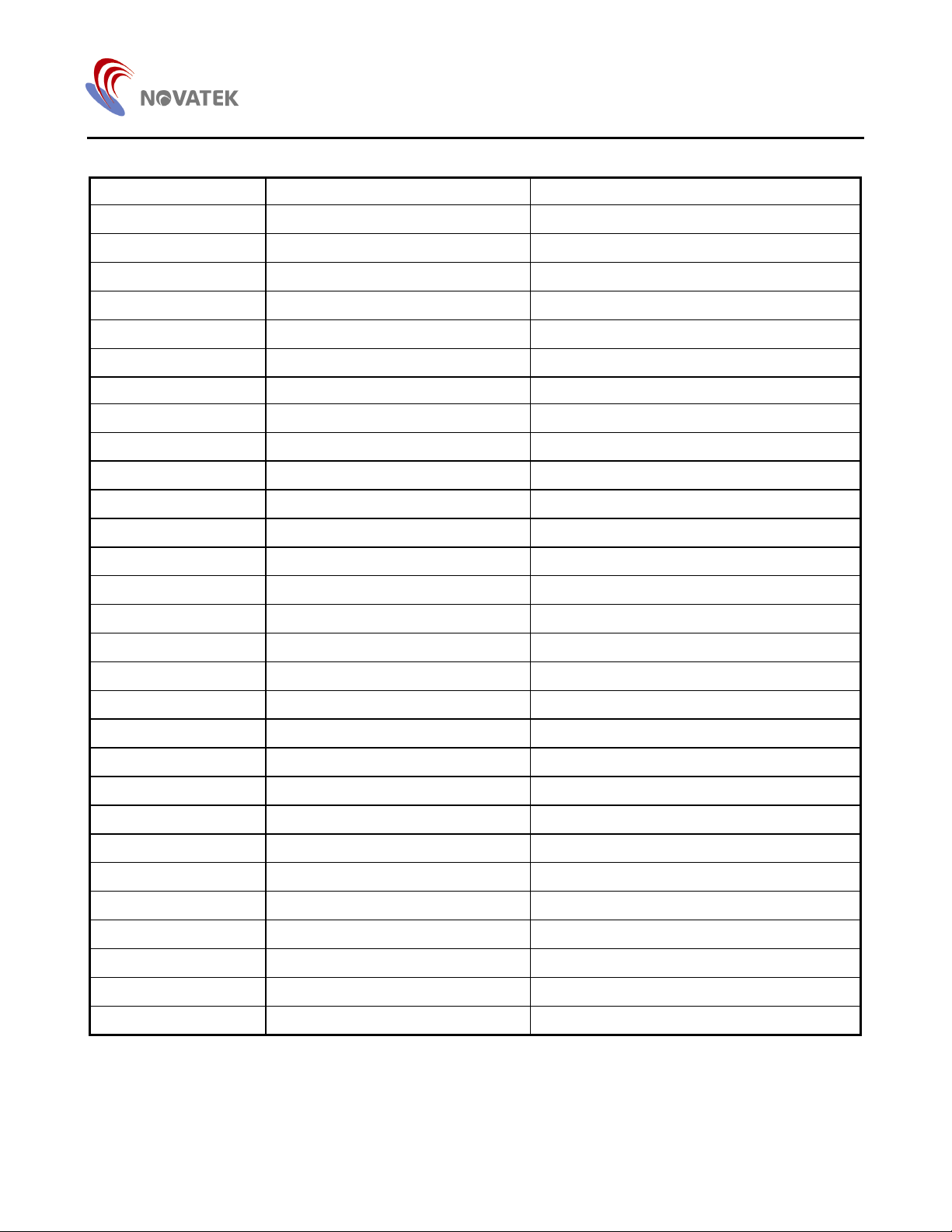

3. RAM: 512 X 8 bits

The built-in 512 X 8-bit SRAM is used for data memory and stack area. The RAM addressing range is from $0080 to $027F.

The contents of RAM are undetermined at power-up and are not affected by system reset. Software programmers can

allocate stack area in the RAM by setting stack pointer register (S). Since the 6502 default stack pointer is $01FF,

programmers must set S register to FFH when starting the program.

as; LDX #$FF

TXS

$0000

$003E

$0080

$01FF

$027F

$0280

$77FF

$7800

( 2 K Bytes )

$7FFA NMI-L

$7FFB

$7FFC RST-L

$7FFD

$7FFE

$7FFF

$8000

( 32 K Bytes )

System Registers

Unused

RAM

( 512 Bytes )

Unused

Boot

ROM

NMI-H

RST-H

IRQ-L

IRQ-H

Flash

Memory

stack pointer

NMI vector

RESET vector

IRQ vector

$FFFA NMI-L

$FFFB

$FFFC RST-L

$FFFD

$FFFE

$FFFF

NMI-H

RST-H

IRQ-L

IRQ-H

NMI vector

RESET vector

IRQ vector

4.1. BootROM: 2K X 8 bits

NT68F62 Provides 2K bytes of Boot-ROM for ISP. The memory space is from $7800 to $7FFF. The addresses, from $7FFA

to $7FFF, are reserved for the 6502 CPU vector.

4.2. Flash memory: 32K X 8 bits

NT68F62 provides 32K flash memory space for programming. The flash memory space is located from $8000 to $FFFF.

The addresses, from $FFFA to $FFFF, are reserved for the 6502 CPU vectors, thus users must arrange them by

themselves. This flash memory can be progammed repeatly at limited times to guarantee its performance.

9

NT68F62

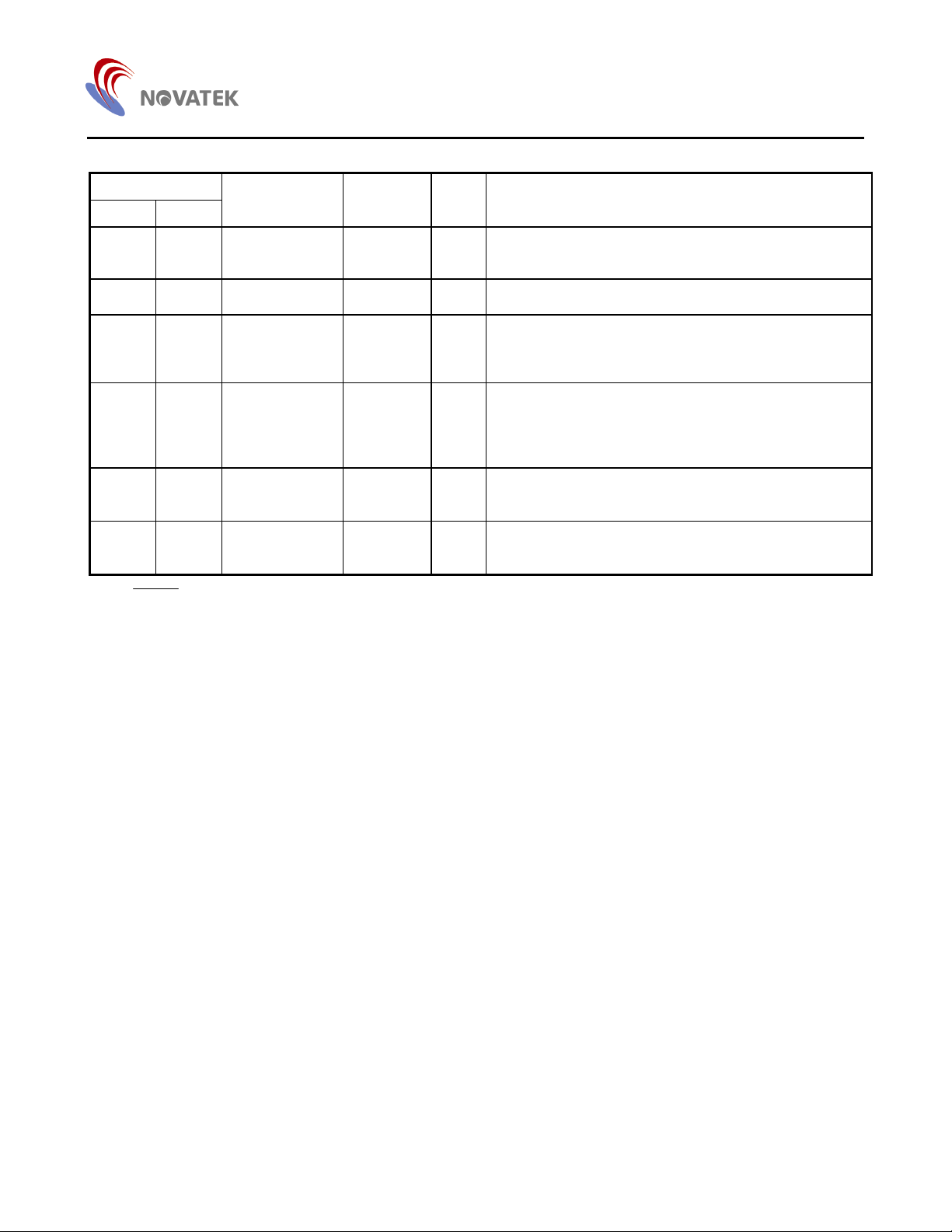

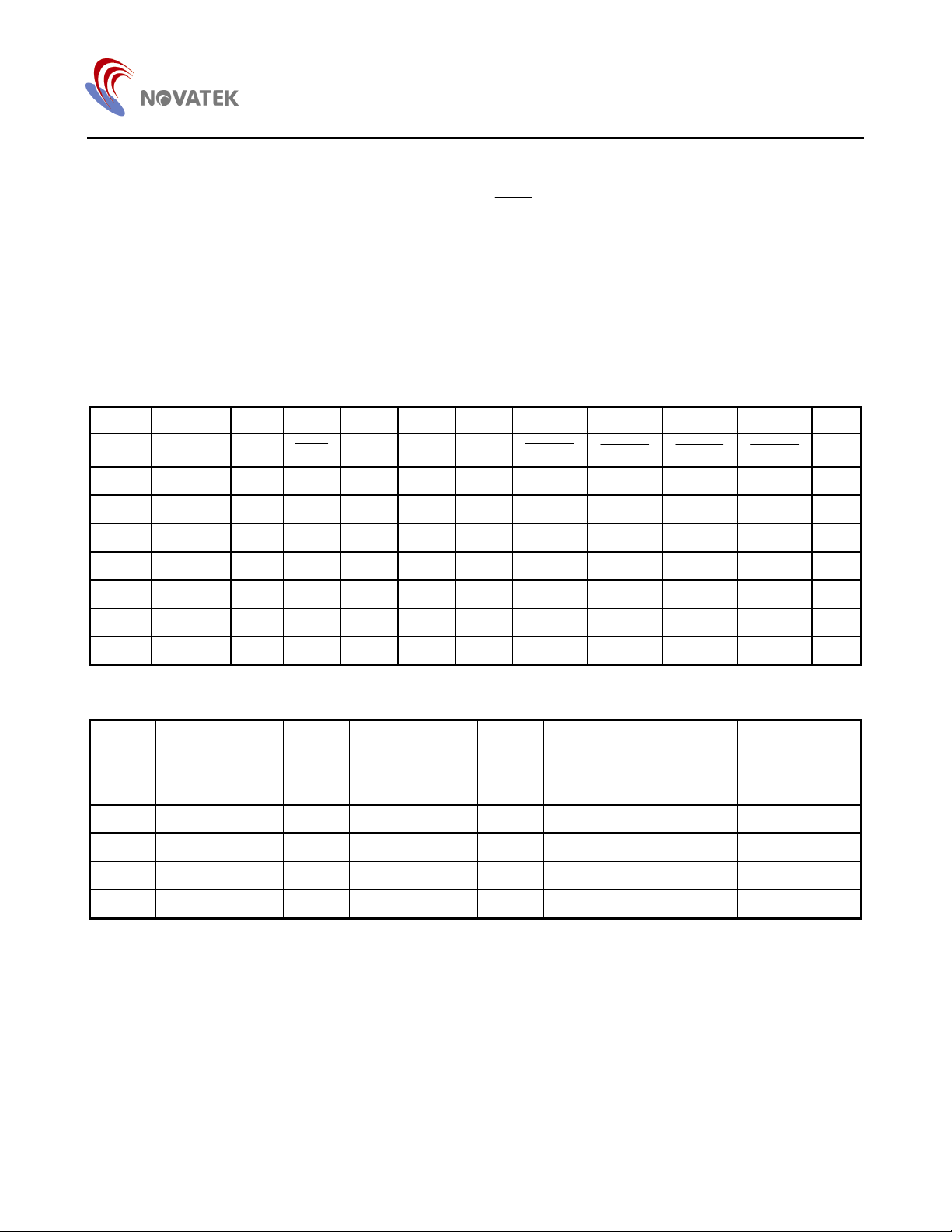

5. System Registers

Addr. Register INIT Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 R/W

Control Registers for I/O Port0 & Port1

$0000 PT0 FFH P07 P06 P05 P04 P03 P02 P01 P00 RW

$0001 PT1 7FH

$0002 PT2DIR FFH

$0003 PT2 FFH P27 P26 P25 P24 P23 P22 P21 P20 RW

$0004 PT3 03H

$0005 PT4 03H Only available for the 42 Pin SDIP version

$0006 SYNCON

$0008 HCNT L 00H HCL7 HCL6 HCL5 HCL4 HCL3 HCL2 HCL1 HCL0 R

$000A VCNT L 00H VCL7 VCL6 VCL5 VCL4 VCL3 VCL2 VCL1 VCL0 R

$000C FREECON FFH

$000D HALFCON FFH

$000E AUTOMUTE FFH

$000F ENDAC FFH

$0010 ENADC FFH

$0011 AD0 REG C0H

$0012 AD1 REG 00H

$0013 AD2 REG 00H

$0014 AD3 REG 00H

FFH

FFH

FFH

FFH

―

P27OE P26OE P25OE P24OE P23OE

― ― ― ― ― ―

― ― ― ―

― ― ― ―

― ―

ENHOUT ENHOUT

HCNTOV

CLRHOV

VCNTOV

CLRVOV

ENPAT

ENHALF

ENHDIFF

― ―

CSTA

― ―

― ―

― ―

― ―

P16 P15 P14 P13 P12 P11 P10 RW

Control Register to Control Port2 I/O Direction

P22OE

Control Registers for I/O Port2 - 4

―

Control Registers for Synprocessor

―

INSEN

INSEN

HSYNCI VSYNCI HPOLI VPOLI HPOLO VPOLO R $0007 HV CON

― ― ― ―

― ― ―

― ― ― ― ― ― ―

―

― ― ― ― ― ― ―

PAT1

NOHALF

ENPOL ENOVER

Control Registers to Enable PWM 8 - 15 Channels

Control Registers for ADC 0 - 3 Channels

― ― ―

VCH5 VCH4 VCH3 VCH2 VCH1 VCH0 R $000B VCNT H 00H

― ― ―

― ― ― ― ―

HALFPOL

ENDK12 ENDK11

―

AD05 AD04 AD03 AD02 AD01 AD00 R

AD15 AD14 AD13 AD12 AD11 AD10 R

AD25 AD24 AD23 AD22 AD21 AD20 R

AD35 AD34 AD33 AD32 AD31 AD30 R

HCH3 HCH2 HCH1 HCH0 R $0009 HCNT H 00H

HDIFFVL3 HDIFFVL2 HDIFFVL1 HDIFFVL0 W

ENDK10

ENADC3 ENADC2 ENADC1 ENADC0

ENHSEL

FREQ2

ENDK9

P21OE

P31 P30 RW

P41 P40 RW

HSEL

HSEL

HPOLO VPOLO W

FREQ1

ENDK8

P20OE

S/C

S/C

FREQ0

ENDK7

W

R

W

W

W

W

W

W

W

10

NT68F62

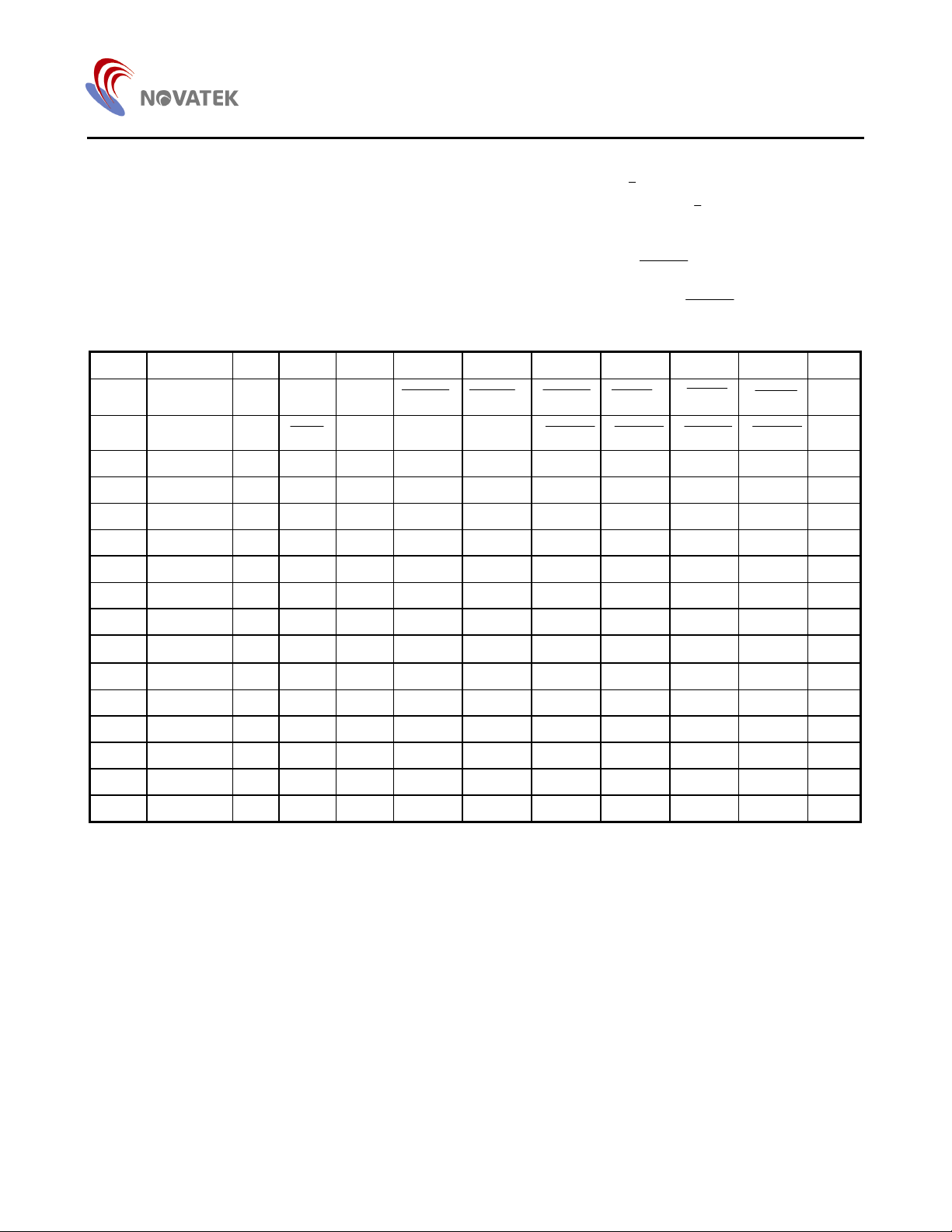

System Registers (continued)

Addr. Register INIT Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 R/W

Control Register for Polling (Read) Interrupt Groups & Clearing (Write) INTE0 & INTMUTE Interrupt Requests

$0016 NMIPOLL 00H

$0017 IRQPOLL 00H

$0018 IENMI 00H

$0019 IEIRQ0 00H

$001A IEIRQ1 00H

$001B IEIRQ2 00H

Control Registers for Polling (Read) & Clearing (Write) Interrupt Requests

$001E IRQ2 00H

$001F TRIGGER FFH

― ― ― ― ― ―

― ― ― ― ― ―

― ― ― ― ―

Control Registers of Interrupt Enable

― ― ― ― ― ―

― ―

― ―

― ― ― ―

― ―

― ―

― ―

― ―

― ― ― ―

― ― ― ―

Selection of Edge Triggered for INTV, INTE0 & 1 Interrupts

― ― ― ― ―

INTS0 INTA0 INTTX0 INTRX0 INTNAK0 INTSTOP0 RW

INTS1 INTA1 INTTX1 INTRX1 INTNAK1 INTSTOP1 RW

INTADC INTV INTE1 INTMR RW

INTS0 INTA0 INTTX0 INTRX0 INTNAK0 INTSTOP0 R $001C IRQ0 00H

CLRS0 CLRA0 CLRTX0 CLRRX0 CLRNAK0 CLRSTOP0 W

INTS1 INTA1 INTTX1 INTRX1 INTNAK1 INTSTOP1 R $001D IRQ1 00H

CLRS1 CLRA1 CLRTX1 CLRRX1 CLRNAK1 CLRSTOP1 W

INTADC INTV INTE1 INTMR R

CLRADC CLRV CLRE1 CLRMR W

IRQ2 IRQ1 IRQ0 R

INTVR INTE1R INTE0R R/W

INTE0 INTMUTE R

CLRE0 CLRMUTE W

INTE0 INTMUTE RW

Control Registers for Clearing Watch Dog Timer

$0020 CLR WDT

$0021 CH0ADDR A0H ADR7 ADR6 ADR5 ADR4 ADR3 ADR2 ADR1

$0022 CH0TXDAT 00H TX7 TX6 TX5 TX4 TX3 TX2 TX1 TX0 W

$0023 CH0RXDAT 00H RX7 RX6 RX5 RX4 RX3 RX2 RX1 RX0 R

$0024 CH0CON

$0025 CH0CLK FFH

$0026 CH1ADDR A0H ADR7 ADR6 ADR5 ADR4 ADR3 ADR2 ADR1

$0027 CH1TXDAT 00H TX7 TX6 TX5 TX4 TX3 TX2 TX1 TX0 W

$0028 CH1RXDAT 00H RX7 RX6 RX5 RX4 RX3 RX2 RX1 RX0 R

―

E0H

0 1 0 1 0 1 0 1 W

Control Register for DDC1/2B+ of Channel 0

W

W

R

W

ENDDC

― ―

MODE

MD1/

2

―

SRW

MRW RSTART

Control Register for DDC1/2B+ of Channel 1

START STOP

START STOP

― ―

―

―

― ― ―

DDC2BR2 DDC2BR1 DDC2BR0 W

TXACK

―

―

11

NT68F62

System Registers (continued)

Addr. Register INIT Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 R/W

$0029 CH1CON E0H

$002A CH1CLK FFH

$002E BT 00H BT7 BT6 BT5 BT4 BT3 BT2 BT1 BT0 W

$002F BTCON 03H

$0030 DACH0 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0031 DACH1 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0032 DACH2 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0033 DACH3 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0034 DACH4 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0035 DACH5 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0036 DACH6 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0037

$0038 DACH7 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0039 DACH8 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$003A DACH9 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

ENDDC

― ―

MODE

― ― ― ― ― ―

― ― ― ― ― ― ― ― ―

MD1/

2

MRW RSTART

Control Registers for Base Timer

Control Registers for PWM Channel 0 - 13

―

SRW

START STOP

START STOP

― ―

―

― ― ―

DDC2BR2 DDC2BR1 DDC2BR0 W

TXACK

BTCLK

―

ENBT

W

R

W

$003B DACH10 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$003C DACH11 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$003D DACH12 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$003E ISP REG

00H

03H

ISP

DDC1_ISP

CH1_A0

DDC0_IS

P

CH0_A0

R

W

12

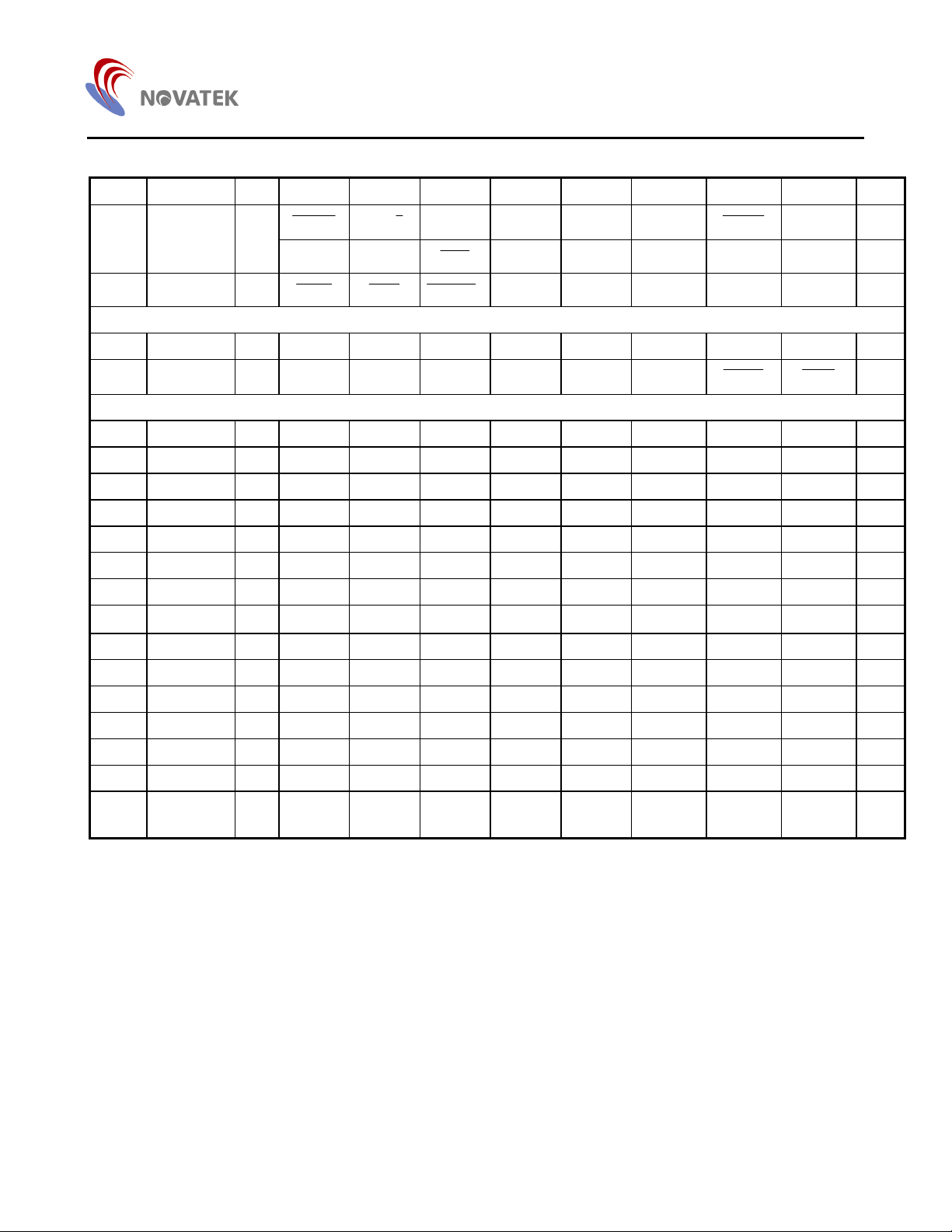

6. Timing Generator

This block generates the system timing and control signals

to be supplied to the CPU and on-chip peripherals. A

crystal quartz, ceramic resonator, or an external clock

signal which will be provided to the OSCI pin generates

system timing. It generates 8MHz for the system clock and

4MHz for the CPU. Although internal circuits have a

NT68F62

feedback resistor and compacitor included, users can

externally add these components for proper operating.

The typical clock frequency is 8MHz. Different frequencies

will affect the operation of those on-chip peripherals whose

operating frequency is based on the system clock.

OSCI

8MHz

OSCO

(1)

NT68F62

Figure 6.1. Oscillator Connections

7. RESET

The NT68F62 can be reset by the external reset pin or by

the internal watch-dog timer. This is used to reset or start

the microcontroller from a POWER DOWN condition.

During the time that this reset pin is held LOW (*reset line

must be held LOW for at least two CPU clock cycles),

writing to or from the µC is inhibited. When a positive edge

is detected on the RESET input, the µC will immediately

begin the reset sequence.

After a system initialization time of six CPU clock cycles,

the mask interrupt flag will be set and the µC will load the

program counter from the memory vector locations $FFFC

and $FFFD. This is the start location for program control.

An internal Schmitt Trigger buffer at the

provided to improve noise immunity.

RESET

pin is

External Clock

Unconnected

The reset status is as follows:

1. PORT0、PORT1、PORT2、PORT3 (& PORT4) pins

will act as I/O ports with HIGH output

2. Sync processor counters reset and VCNT | HCNT

latches cleared

3. All sync outputs are disabled

4. Base timer is disabled and cleared

5. Various Interrupt sources are disabled and cleared

6. A/D converter is disabled and stopped

7. DDC1/2B+ function is disabled

8. PWM DAC0 – DAC6 output 50% duty waveform and

DAC7 - DAC12 is disabled

9. Watch-dog timer is cleared and enabled

OSCI

OSCO

NT68F62

(2)

13

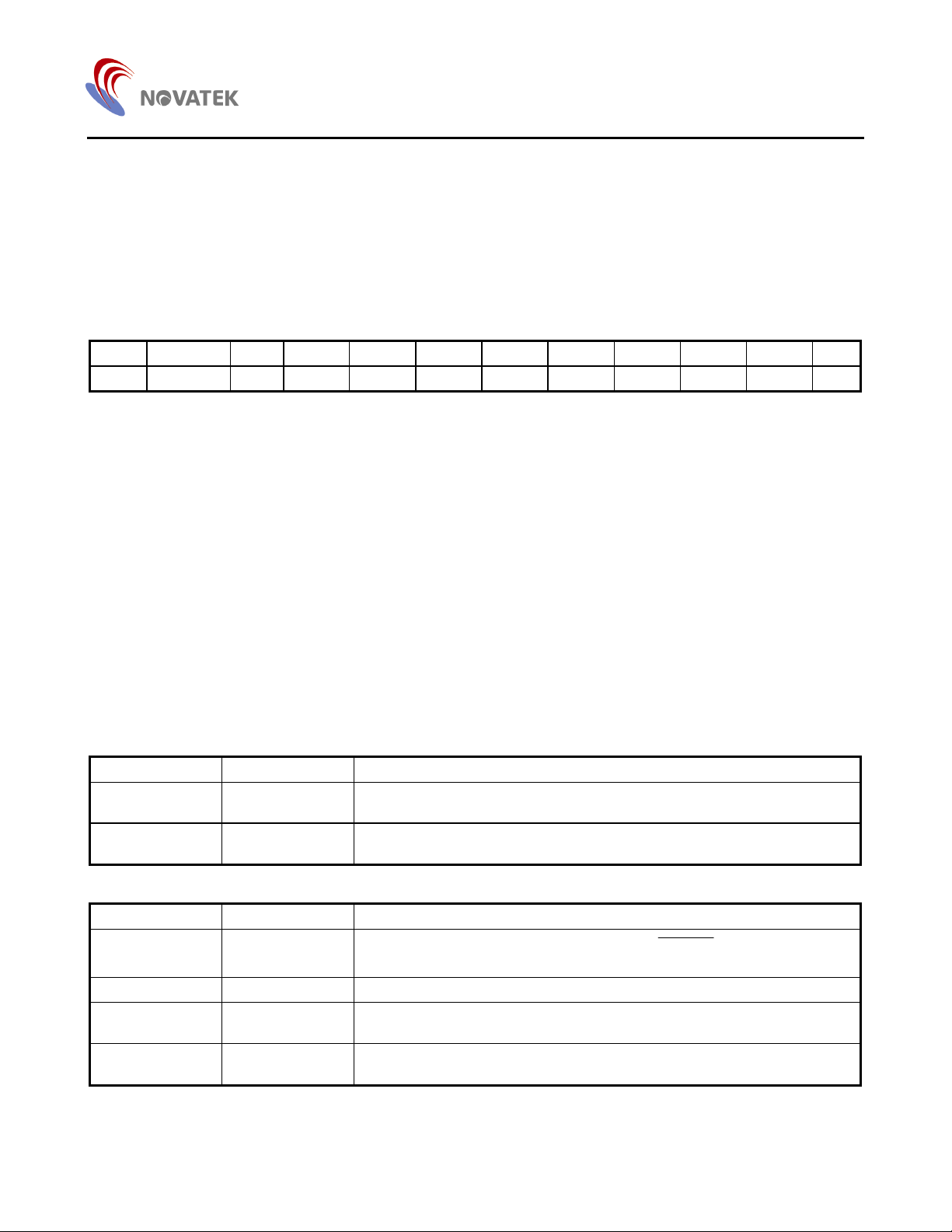

8. A/D Converters

NT68F62

The structure of these analog to digital converters is 6-bit

successive approximation. Analog voltage is supplied from

external sources to the A/D input pins and the result of the

conversion is stored in the 6-bit data latch registers ($0011

& $0014). The A/D channels are activated by clearing the

correspondent control bits in the ENADC control register.

When users write '0' into one of the enabled control bits, its

correspondent I/O pin or DAC will be switched to the A/D

converter input pin (ADC0 & ADC1 are shared with

PORT10 & PORT 11; ADC2 & ADC3 are shared with

DAC0 & DAC1). Conversion will be started by clearing the

CSTA

bit (CONVERSION START) in the ENADC control

register. When the conversion is finished, the system will

set this INTADC bit. Users can monitor this bit to get the

valid A/D conversion data in the AD latch registers ($0011 $0014). Users can also open the interrupt sources to

remind users to get the stable digital data. Notice that only

at the activated A/D channel, its latched data are available.

The analog voltage to be measured should be stable during

the conversion operation and the variation must not exceed

LSB for the best accuracy in measurement.

Addr. Register INIT Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 R/W

$0010 ENADC FFH

$0011 AD0 REG C0H

$0012 AD1 REG 00H

$0013 AD2 REG 00H

$0014 AD3 REG 00H

$001B IEIRQ2 00H

$001E IRQ2 00H

CSTA

― ―

― ―

― ―

― ―

― ― ― ―

― ― ― ―

― ― ― ―

― ― ―

AD05 AD04 AD03 AD02 AD01 AD00 R

AD15 AD14 AD13 AD12 AD11 AD10 R

AD25 AD24 AD23 AD22 AD21 AD20 R

AD35 AD34 AD33 AD32 AD31 AD30 R

ENADC3 ENADC2 ENADC1 ENADC0

INTADC INTV INTE1 INTMR R/W

INTADC INTV INTE1 INTMR R

CLRADC CLRV CLRE1 CLRMR W

W

Reference ADC Table

(V

= 5.0V)

DD

15 1.50V 1C 2.06V 23 2.59V 2A 3.14V

16 1.58V 1D 2.12V 24 2.67V 2B 3.22V

17 1.66V 1E 2.20V 25 2.75V 2C 3.30V

18 1.74V 1F 2.28V 26 2.82V 2D 3.38V

19 1.82V 20 2.35V 27 2.91V 2E 3.46V

1A 1.90V 21 2.44V 28 2.98V 2F 3.54V

1B 1.98V 22 2.51V 29 3.07V 30 3.62V

Note: It is strongly recommended that the ADC’s input signal should be allocated within the ADC’s linear voltage

range (1.5V~3.5V) to obtain a stable digital value. Do not use the outer ranges (0V~1.4V & 3.6V~5.0V) in which

the converted digital value is not guaranteed.

14

NT68F62

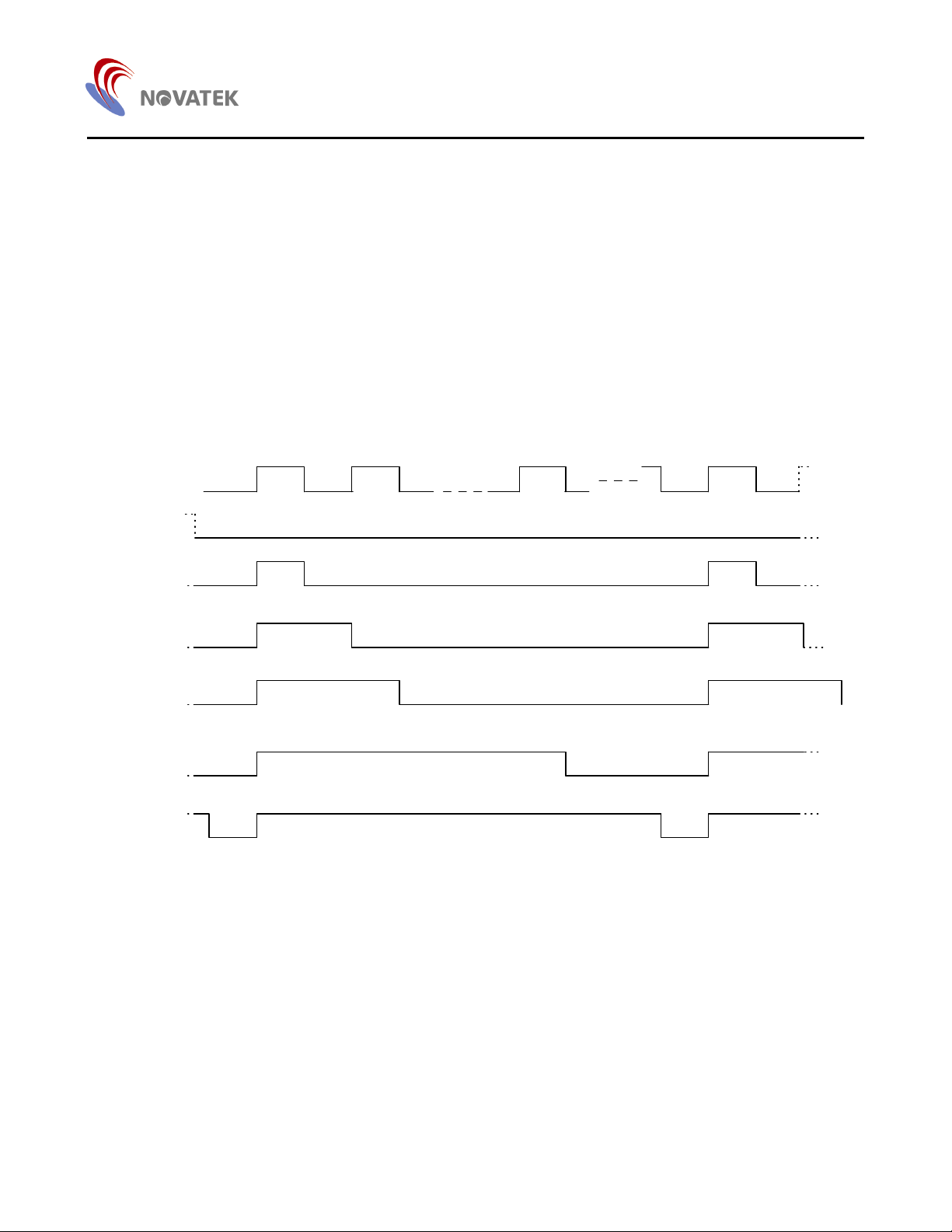

9. PWM DACs

There are 13 PWM D/A converters with 8-bit resolution in the NT68F62. All of these D/A (DAC0 - DAC12) converters are of

open-drain output structure with an external 5V applied maximum. DAC0 – DAC6 are dedicated PWM channels, and DAC7 DAC12 are shared with the I/O pins. These shared PWM channels are activated by clearing the correspondent control bits in

the ENDAC control register ($000F). When users write '0' into one of the enable control bits, its correspondent I/O pin will be

switched to a PWM output pin.

The PWM refresh rate is 62.5KHz operating on an 8MHz system clock. There are 13 readable DACH registers

corresponding to 13 PWM channels ($0030 - $003D). Each PWM output pulse width is programmable by setting the 8 bit

digital to the corresponding DACH registers. When these DACH registers are set to 00H, the DAC will output LOW (GND

level) and every 1 bit addition will add 62.5ns pulse width. After reset, all DAC outputs are set to 80H (1/2 duty output).

(Please refer to Figure 9.1 for the detailed timing diagram of the PWM D/A output.)

(Pulse Width Modulation D/A Converters)

Fosc

8MHz

255 0 1 2 m

00

01

3 m-1 0

255

1PWM value :

02

03

m

255(FF)

Figure 9.1. The DAC Output Timing Diagram and Wave Table

15

NT68F62

PWM DACs (continued)

DAC0 & DAC1 are shared with the ADC2 & ADC3 input pins respectively. If ENADC2/3 bit in the ENADC control register is

cleared to LOW, the A/D converters will activate simultaneously. After the chip is reset, ENADC2/3 bits will be in HIGH state

and DAC0 & DAC1 will act as PWM output pins.

DAC4 & DAC5 are shared with SCL1 & SDA1 I/O pins respectively. If users clear the

ENDDC

bit in the CH1CON control

register to LOW, channel 1 of the DDC will be activated. When used as the DDC channel, the I/O port will be of an open

drain structure and include a 'Schmitt Trigger' buffer for noise immunity. After the chip is reset,

ENDDC

bits will be in HIGH

state and DAC4 - DAC5 will act as PWM output pins.

Addr. Register INIT Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 R/W

$000F ENDAC FFH

$0010 ENADC FFH

$0030 DACH0 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0031 DACH1 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0032 DACH2 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0033 DACH3 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0034 DACH4 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0035 DACH5 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0036 DACH6 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0037

― ― ― ― ― ― ― ― ―

― ―

CSTA

ENDK12 ENDK11 ENDK10 ENDK9

― ― ―

ENADC3 ENADC2 ENADC1 ENADC0

ENDK8

ENDK7

W

W

$0038 DACH7 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$0039 DACH8 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$003A DACH9 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$003B DACH10 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$003C DACH11 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

$003D DACH12 80H DKVL7 DKVL6 DKVL5 DKVL4 DKVL3 DKVL2 DKVL1 DKVL0 RW

DAC control register ($000F) and DAC value register ($0030 - $003D)

16

NT68F62

10. Watch-Dog Timer (WDT)

The NT68F62 implements a watch-dog timer reset to avoid

system stop or malfunction. The clock of the WDT is taken

from the on-chip RC oscillator, which does not require any

external components. Thus, the WDT will run, even if the

clock on the OSCI/OSCO pins of the device has been

stopped. The WDT time interval is about 0.5 second. The

as; LDA #$55

STA $0020

Addr. Register INIT Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 R/W

$0020 CLR WDT - 0 1 0 1 0 1 0 1 W

WDT must be cleared within every 0.5 second when the

software is in normal sequence, otherwise the WDT will

overflow and cause a reset. The WDT is cleared and

enabled after the system is reset, and can not be disabled

by the software. Users can clear the WDT by writing 55H to

the CLRWDT register ($0020).

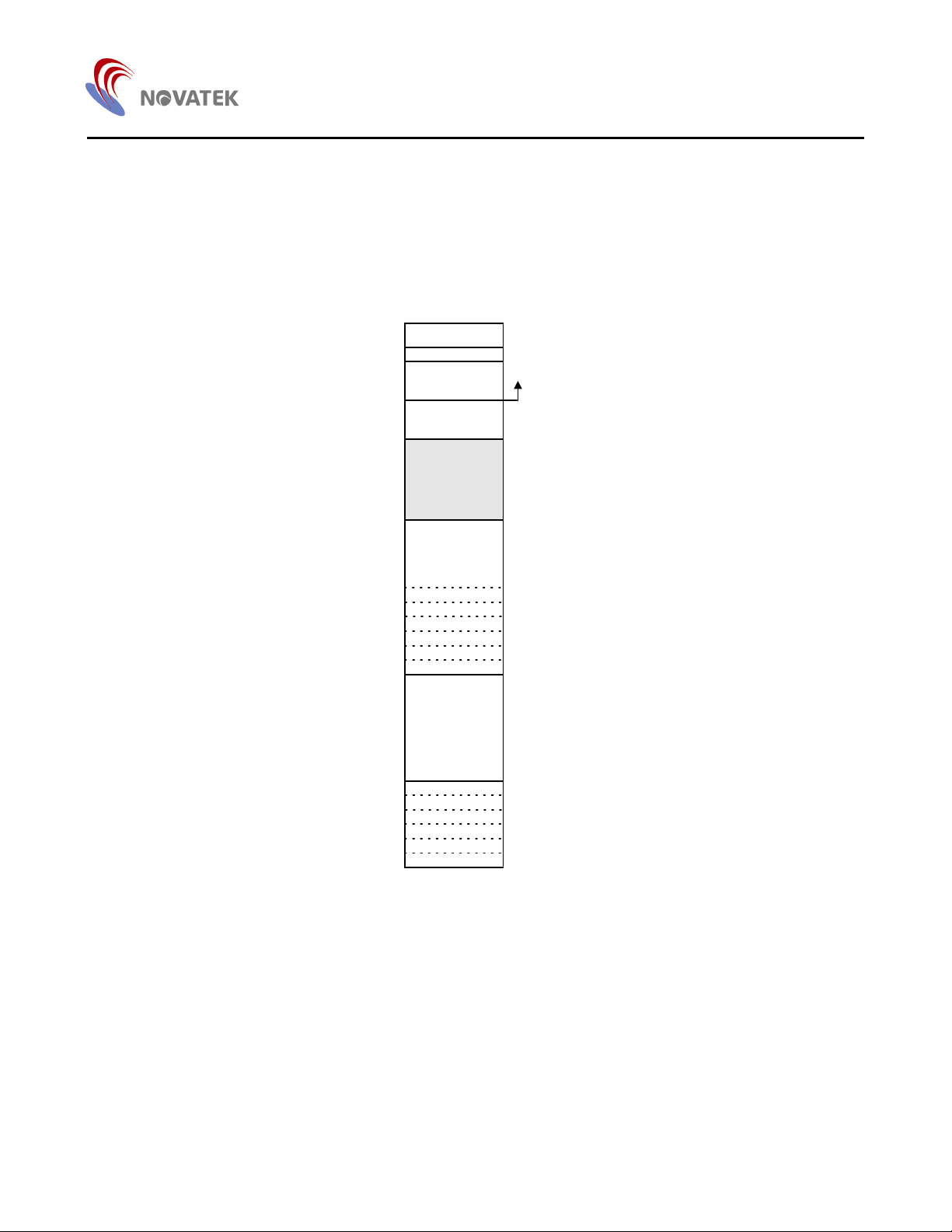

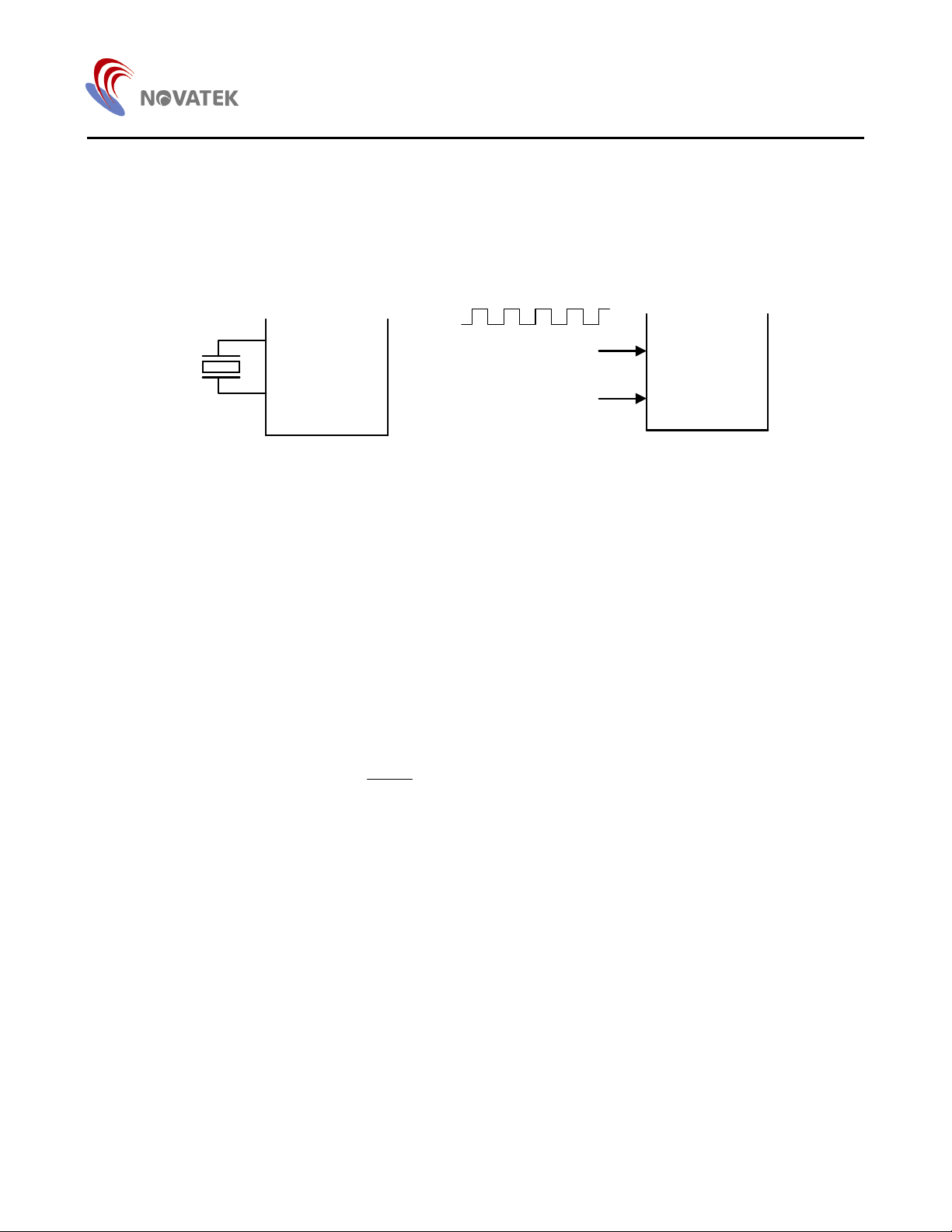

11. Interrupt Controller

The system provides two kinds of interrupt sources: NMI &

IRQ. The NMI cannot be masked if user enabled this NMI

interrupt. Users will execute the NMI interrupt vector any

time that sources are activated. The IRQ interrupts can be

masked by executing a CLI instruction or by setting the

interrupt mask flag directly in the µC status register. In the

process of an IRQ interrupt, if the interrupt mask flag is not

set, the µC will begin an interrupt sequence. The program

counter and processor status register will be stored in the

stack. The µC will then set the interrupt mask flag high so

that no further interrupts may occur. At the end of this

cycle, the program counter will be loaded from addresses

$FFFE & $FFFF, thus transferring program control to the

memory vector located at these addresses. For NMI

interrupt, µC will transfer execution sequence to the

memory vector located at addresses $FFFA & $FFFB.

When manipulating various interrupt sources, NT68F62

divides them into two groups for accessing them easily.

One is the NMI group and the other is the IRQ group.

- The NMI group includes INTE0, INTMUTE.

- The IRQ group includes the subgroup of IRQ0,

IRQ1,RQ2:

IRQ0: DDC1/2B+ Channel 0 interrupt sources; It

includes INTS0, INTA0, INTTX0, INTRX0,

INTNAK0 and INTSTOP0 interrupts.

IRQ1: DDC1/2B+ Channel 1 interrupt sources; It

includes INTS0, INTA1, INTTX1, INTRX1,

INTNAK1 and INTSTOP1.

IRQ2: It includes INTADC, INTV, INTE1 and INTMR

interrupt sources.

Below are the interrupt sources.

Nonmaskable Interrupt Group:

Interrupt Meaning Action

INTE0 INT External 0 INT

INTMUTE Auto Mute

It will be activated by the rising or falling edge of the external interrupt pulse.

The triggered edge can be selected by EDGE0 bit.

It will be activated when the mute condition occurs (Hsync frequency change).

Please refer the synprocessor section for a more detailed explanation.

Maskable Interrupt Group:

Interrupt Meaning Action

INTADC

INTV INT Vsync INT It will be activated by the rising edge of every vsync pulse.

INTE1 INT External 1 INT

INTMR INT Timer INT

A/D Conversion

Done

User activates the ADC by clearing the

conversion is done, this bit will be set.

It will be activated by the rising or falling edge of the external interrupt pulse.

The triggered edge can be selected by EDGE1 bit.

It will be activated by the rising edge of every ??? when the Base Timer

counter overflows and counting from $FF to $00.

17

CSTART

bit. When the AD

NT68F62

DDC Channel 0/1 Maskable Interrupt Sources:

Interrupt Meaning Action

INTS INT SCL Go-Low INT In DDC1 mode, it will be activated when the external device proceed a DDC2

communication. This action includes pulling the SCL line to ground or sending

out a 'START' condition directly. The system will respond to this action by

changing DDC1 mode to DDC2 slave mode.

INTA INT Address Matched

INT

It will be activated in DDC2 slave mode when the external device calls a

NT68F62 slave address. If this calling address matches the NT68F62 address,

the system will generate this interrupt to remind the user

INTTX INT Transfer Buffer

Empty INT

INTRX INT Receiving Buffer

Overflow INT

INTNAK INT No Acknowledge

INT

It will be activated in DDC2 mode when the transmission buffer, IIC_TXDAT, is

empty in transmission mode.

It will be activated in DDC2 mode when the new data are stored in the

IIC_RXDAT register in receive mode.

In transmission mode, this interrupt will be activated when the NT68F62 has

send out one byte of data but the external device does not respond with an

acknowledgement bit to it.

INTSTOP INT DDC2 Stop INT In SLAVE mode, this interrupt will be activated when the NT68F62 receives a

'STOP' condition.

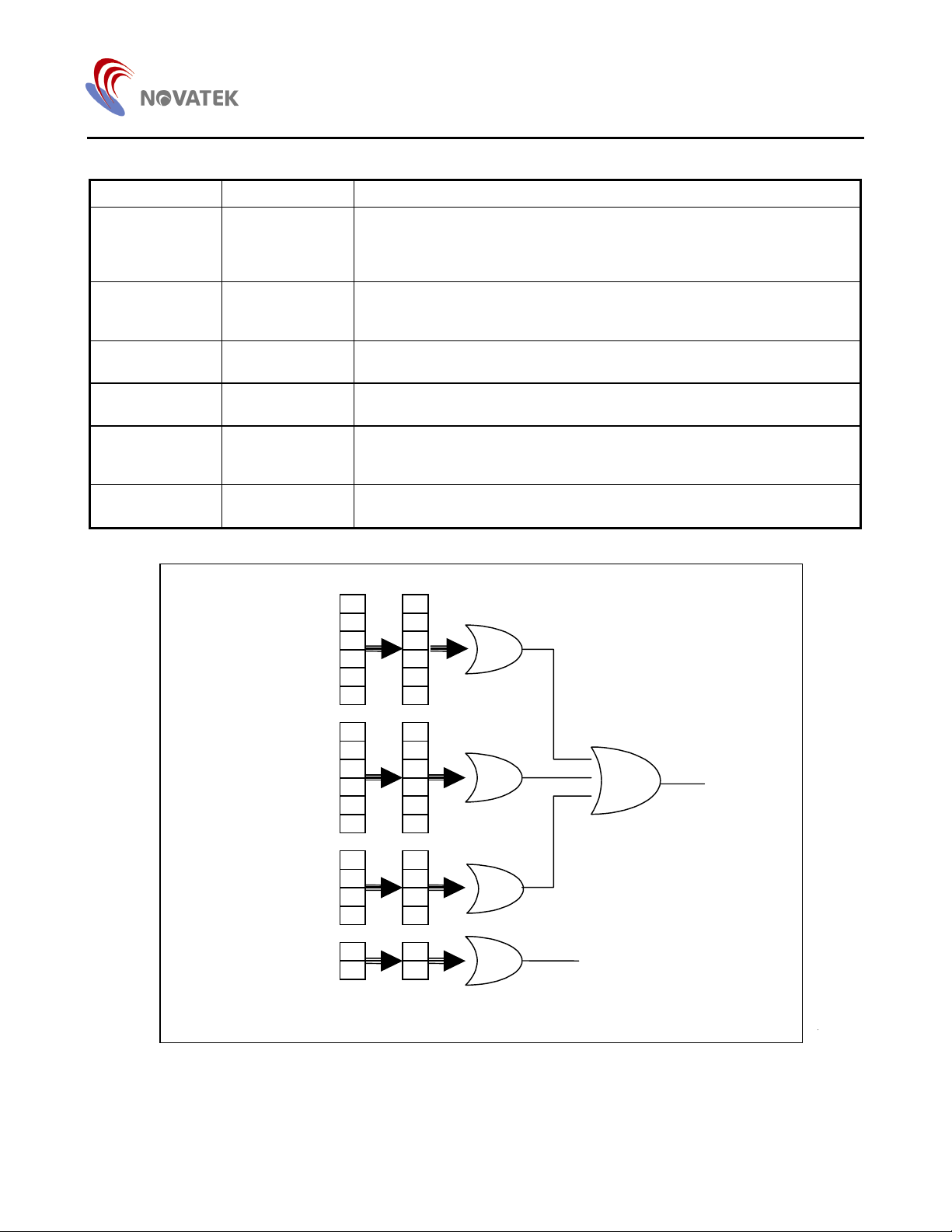

INTSTOP0

INTNAK0

INTRX0

INTTX0

INTA0

INTS0

INTSTOP1

INTNAK1

INTRX1

INTTX1

INTA1

INTS1

INTMR

INTE1

INTV

INTADC

INTMUTE

INTE0

IRQ0

IRQ1

IRQ2

NMIPOLL IENMI

IEIRQ0

IEIRQ1

IEIRQ2

IRQ0

IRQ1

IRQ (to CPU 6502)

IRQ2

NMI (to CPU 6502)

Figure 11.1. Interrupt Controller Structure

18

Loading...

Loading...