Page 1

PAMS Technical Documentation

NSB–6 Series Transceivers

System Module

Issue 1 06/2000 E Nokia Mobile Phones Ltd.

Page 2

NSB–6

System Module

PAMS Technical Documentation

CONTENTS

Transceiver NSB–6 6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Introduction 6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operation Modes 6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interconnection Diagram 7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Module 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Baseband Module 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Block Diagram 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Technical Summary 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External and Internal Signals and Connections 10. . . . . . . . .

DC (charger) connector 10. . . . . . . . . . . . . . . . . . . . . . . . . . .

Service connector 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Battery connector 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIM card connector 11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RTC backup battery 11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Distribution 12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Battery charging 12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Startup Charging 13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Battery Overvoltage Protection 13. . . . . . . . . . . . . . . . . . . .

Battery Removal During Charging 15. . . . . . . . . . . . . . . . . .

PWM 16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Battery Identification 16. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Battery Temperature 17. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Supply Voltage Regulators 18. . . . . . . . . . . . . . . . . . . . . . . .

Switched Mode Supply VSIM 20. . . . . . . . . . . . . . . . . . . . . .

Power Up and Power Down 20. . . . . . . . . . . . . . . . . . . . . . . . .

Power up with a charger 20. . . . . . . . . . . . . . . . . . . . . . . . . .

Power Up With The Power Switch (PWRONX) 21. . . . . . .

Power Up by RTC 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Up by IBI 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Down 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Modes of Operation 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Acting Dead 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Active Mode 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Sleep Mode 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Charging 24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Watchdog 24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page 2

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 3

PAMS Technical Documentation

Audio control 25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PCM serial interface 25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital Control 26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MAD2 WD1 26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Memories 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MAD memory configuration 34. . . . . . . . . . . . . . . . . . . . . . .

Memory 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Program and Data Memory 34. . . . . . . . . . . . . . . . . . . . . . .

Work Memory 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MCU Memory Requirements 34. . . . . . . . . . . . . . . . . . . . . .

MCU Memory Map 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Flash Programming 35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

COBBA GJP 36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Real Time Clock 37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RTC backup battery charging 37. . . . . . . . . . . . . . . . . . . . . .

NSB–6

System Module

Security 37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Baseband Testing 38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Alignments 38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Baseband Startup for Testing 38. . . . . . . . . . . . . . . . . . . . . .

RF Module 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Environmental specifications 39. . . . . . . . . . . . . . . . . . . . . . . . .

Main Technical specifications 39. . . . . . . . . . . . . . . . . . . . . . . .

Maximum Ratings 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RF Characteristics 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RF Frequency Plan 40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DC characteristics 40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Regulators 40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Control signals (typical current consumption in different modes) 40

Power Distribution Diagram 41. . . . . . . . . . . . . . . . . . . . . . . . . .

RF Functional Description 42. . . . . . . . . . . . . . . . . . . . . . . . . . .

Frequency synthesizer 43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmitter 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AGC strategy 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AFC function 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DC–compensation 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver characteristics 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmitter characteristics 47. . . . . . . . . . . . . . . . . . . . . . . . . . .

Parts list of UP9 (EDMS Issue 9.2) Code: 0201362 48. . . . . . . . . .

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 3

Page 4

NSB–6

System Module

Schematic Diagrams: UP9 (Section 10 at the back of the binder)

Connection between RF and BB modules (Version 12.03 Edit 12) layout 12 A–1

Baseband Block Interconnections (Version 12.03 Edit 12) for layout 12 A–2

Circuit Diagram of Power Supply (Version 12.03 Edit 16) for layout 12 A–3

Circuit Diagram of MAD Block (Version 12.03 Edit 14) for layout 12 A–4

Circuit Diagram of CPU Block (Version 12.03 Edit 14) for layout 12 A–5

Circuit Diagram of RF Block (Version 12.03 Edit 43) for layout 12 A–6

Circuit Diagram of Audio and RFI (Version 12.03 Edit 14) for layout 12 A–7

Circuit Diagram of IR Module (Version 12.03 Edit 8) for layout 12 A–8

Circuit Diagram of UI (Version 12.03 Edition 12) for layout version 12 A–9

Layout Diagram of UP9 – Top (Version 12) A–10. . . . . . . . . . . . . . . . .

Layout Diagram of UP9 – Bottom (Version 12) A–10. . . . . . . . . . . . . .

PAMS Technical Documentation

Testpoints of UP9 – Top (Version 12) A–11. . . . . . . . . . . . . . . . . . . . . .

Testpoints of UP9 – Bottom (Version 12) A–11. . . . . . . . . . . . . . . . . . .

RF Testpoints of UP9 – Circuit Diagram (Version 12) A–12. . . . . . . .

RF Testpoints of UP9 – Layout (Version 12) A–13. . . . . . . . . . . . . . . .

Page 4

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 5

PAMS Technical Documentation

NSB–6

System Module

This page intentionally left blank.

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 5

Page 6

NSB–6

System Module

Transceiver NSB–6

Introduction

The NSB–6 is a dual band transceiver unit designed for the GSM900 (in-

cluding EGSM) and GSM1900 networks. It is both GSM900 phase 2 power

class 4 transceiver (2W) and GSM1900 power class 1 (1W) transceiver.

The transceiver consists of System/RF module (UP9), Display module

(UX7) and assembly parts.

The transceiver has a full graphic display and the user interface is based

on a Jack style UI with two soft keys.

The NSB–6 transceiver uses internal PIFA antenna combined with ex-

tractable whip antenna.

The transceiver has a low leakage tolerant earpiece and an omnidirec-

tional microphone located to a slide, providing an excellent audio quality.

The transceiver supports a full rate, an enhanced full rate and a half rate

speech decoding.

PAMS Technical Documentation

An integrated IR link provides a connection between two NSB–6 trans-

ceivers or a transceiver and a PC (internal data), or a transceiver and a

printer.

The small SIM ( Subscriber Identity Module ) card is located underneath

the back cover of the phone.

Operation Modes

There are five different operation modes:

– power off mode

– idle mode

– active mode

– charge mode

– local mode

In the power off mode only the circuits needed for power up are supplied.

In the idle mode circuits are powered down and only sleep clock is run-

ning.

Page 6

In the active mode all the circuits are supplied with power although some

parts might be in the idle state part of the time.

The charge mode is effective in parallel with all previous modes. The

charge mode itself consists of two different states, i.e. the fast charge and

the maintenance mode.

The local mode is used for alignment and testing.

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 7

PAMS Technical Documentation

Interconnection Diagram

NSB–6

System Module

Keyboard

module

14

LCD

module

9

64

SIM Battery

Radio

Module

2+2

2

UP9

Charger

Antenna

2

3

2

4

Slide (mic.)

IR Link

Earpiece

HF/HS

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 7

Page 8

NSB–6

System Module

System Module

Baseband Module

The baseband architecture supports a power saving function called ”sleep

mode”. This sleep mode shuts off the VCTCXO, which is used as system

clock source for both RF and baseband. During the sleep mode the sys-

tem runs from a 32 kHz crystal. The phone is waken up by a timer run-

ning from this 32 kHz clock supply. The sleeping time is determined by

some network parameters. The sleep mode is entered when both the

MCU and the DSP are in standby mode and the normal VCTCXO clock

has been switched off.

The battery charging is controlled by a PWM signal from the CCONT. The

PWM duty cycle is determined by a charging software and is fed to the

CHAPS charging switch.

PAMS Technical Documentation

Two types of chargers can be connected to the phone. Standard chargers

(two wires) provide coarse supply power, which is switched by the

CHAPS for suitable charging voltage and current. Advanced chargers

(three wires) are equipped with a control input. Three wire chargers are

treated like two wire ones.

Block Diagram

TX/RX SIGNALS

UI

COBBA SUPPLY

COBBA

RF SUPPLIES

CCONT

BB SUPPLY

PA SUPPL Y

32kHz

CLK

SLEEP CLOCK

SIM

13MHz

CLK

SYSTEM CLOCK

IR

Page 8

BASEBAND

MAD

+

MEMORIES

CHAPS

EXT. AUDIO

HS–connector

Charger

connector

E Nokia Mobile Phones Ltd.

VBAT

BATTERY

Issue 1 06/2000

Page 9

PAMS Technical Documentation

Technical Summary

The baseband module consists four ASICs; CHAPS, CCONT, COBBA–

GJP and MAD2WD1, which take care of the baseband functions of the

engine.

The baseband is running from a 2.8V power rail, which is supplied by a

power controlling ASIC CCONT. MAD2WD1 supply voltages are VBB and

VCORE (V2V), VBB feeds I/O pins so that MAD2WD1 is externally fully

compatible with old versions. VCORE feeds MAD2WD1 internal fuctions

supplyoltage; CPU, DSP and system logic. In the CCONT there are 6 in-

dividually controlled regulator outputs for RF–section and two outputs for

the baseband. In addition there is one +5V power supply output (V5V).

The CCONT contains also a SIM interface, which supports both 3V and

5V SIM–cards. A real time clock function is integrated into the CCONT,

which utilizes the same 32kHz clock supply as the sleep clock. A backup

power supply is provided for the RTC, which keeps the real time clock

running when the main battery is removed. The backup power supply is a

rechargable battery. The backup time with the battery is ten minutes mini-

mum.

NSB–6

System Module

The interface between the baseband and the RF section is mainly han-

dled by a COBBA ASIC. COBBA provides A/D and D/A conversion of the

in–phase and quadrature receive and transmit signal paths and also A/D

and D/A conversions of received and transmitted audio signals to and

from the user interface. The COBBA supplies the analog TXC and AFC

signals to RF section according to the MAD DSP digital control. Data

transmission between the COBBA and the MAD is implemented using se-

rial bus for high speed signalling and for PCM coded audio signals. Digital

speech processing is handled by the MAD ASIC. COBBA is a dual volt-

age circuit, the digital parts are running from the baseband supply VBB

and the analog parts are running from the analog supply VCOBBA.

The baseband supports both internal and external microphone inputs and

speaker outputs. Input and output signal source selection and gain control

is done by the COBBA according to control messages from the MAD.

Keypad tones, DTMF, and other audio tones are generated and encoded

by the MAD and transmitted to the COBBA for decoding. A buzzer and an

external vibra alert control signals are generated by the MAD with sepa-

rate PWM outputs.

EMC shielding is implemented using a metallized plastic frame. On the

other side the engine is shielded with PCB grounding. Heat generated by

the circuitry will be conducted out via the PCB ground planes.

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 9

Page 10

NSB–6

System Module

PAMS Technical Documentation

External and Internal Signals and Connections

This section describes the external electrical connection and interface lev-

els on the baseband. The electrical interface specifications are collected

into tables that covers a connector or a defined interface.

DC (charger) connector

DC (charger) connector is physically integrated in the same component

with the accessory interface connector. DC connector has both jack and

contact pads for desk stand.

Service connector

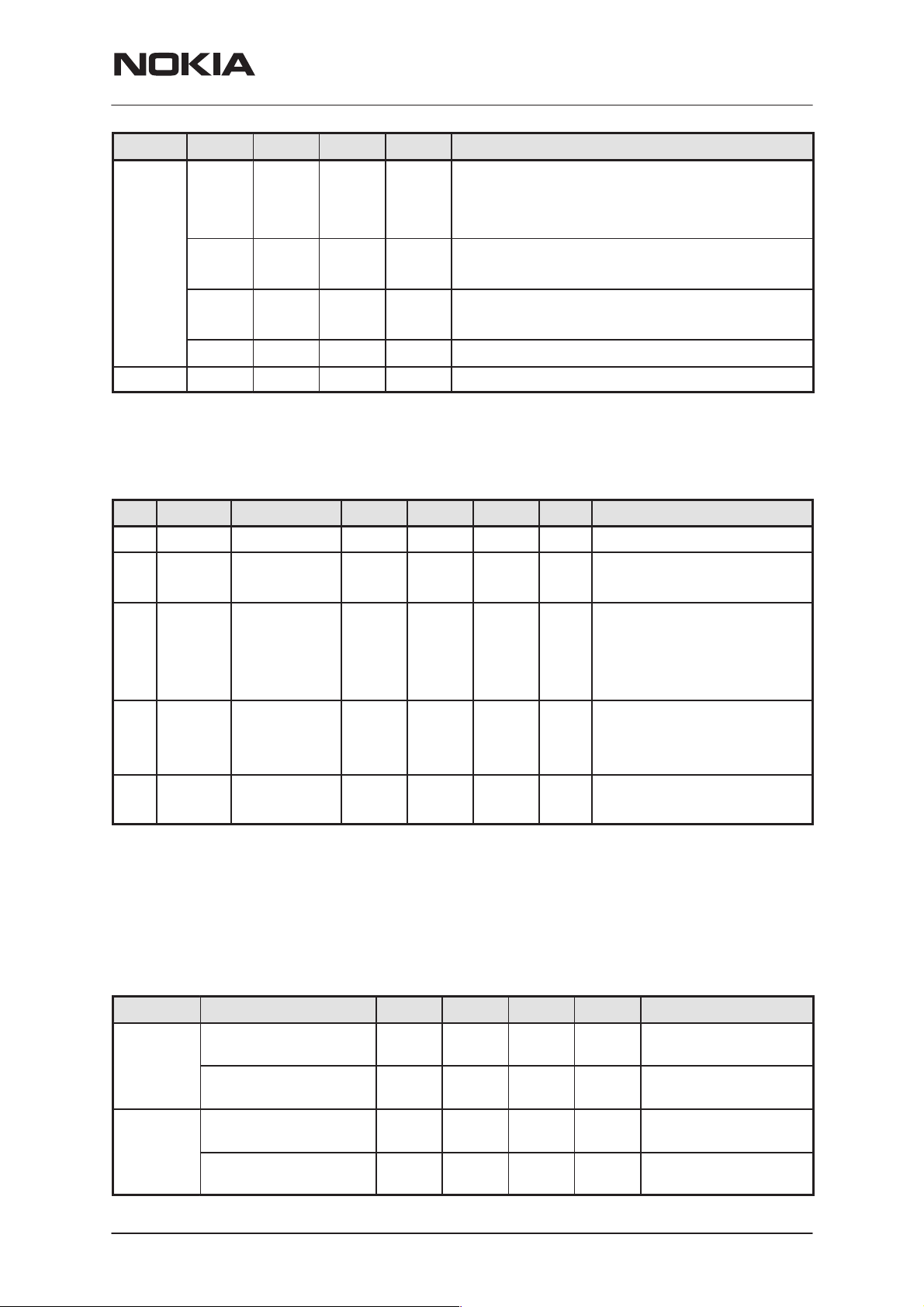

Name Parameter Min Typ Max Unit Remark

MBUS Serial clock

from the

Prommer

FBUS_RX Serial data

from the

Prommer

FBUS_TX Data ac-

knowledge to

the Prommer

GND GND 0 0 V Ground

0

2.0

0

2.0

0

2.0

logic low

logic low

logic low

logic high

logic low

logic high

0.8

2.85

0.8

2.85

0.5

2.85

V Prommer detection and Seri-

al Clock for synchronous

communication

V Receive Data from

Prommer to Baseband

V Transmit Data from Base-

band to Prommer

The service connector is used as a flash programming interface for updating (i.e. re–programming) the flash program memory and an electrical

access for services to the engine.

When the flash prommer is connected to the phone supply power is provided through the battery contacts and the phone is powered up with a

pulse given to the BTEMP line.

Battery connector

The BSI contact on the battery connector is used to detect when the battery is to be removed to be able to shut down the operations of the SIM

card before the power is lost if the battery is removed with power on. The

BSI contact disconnects earlier than the supply power contacts to give

enough time for the SIM and LCD shut down.

Name Min Typ Max Unit Notes

VBATT 3.0 3.9 4.2 V Battery voltage

BSI

Page 10

0 2.85 V Battery size indication

Phone has 100kohm pull up resistor.

SIM Card removal detection

(Treshold is 2.4V@VBB=2.8V)

68 kohm Battery indication resistor (BLB–2)

22 kohm Battery indication resistor (service battery)

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 11

PAMS Technical Documentation

NSB–6

System Module

NotesUnitMaxTypMinName

BTEMP

BGND 0 0 V Battery ground

0 1.4 V Battery temperature indication

Phone has a 100k (+–5%) pullup resistor,

Battery package has a NTC pulldown resistor:

47k+–5%@+25C , B=4050+–3%

2.1

5 10

1.9

90 100

0 1 kohm Local mode initialization (in production)

3

20

2.85

200

V

ms

V

ms

Phone power up by battery (input)

Power up pulse width

Battery power up by phone (output)

Power up pulse width

SIM card connector

The SIM card connector is located on the engine board beside the battery

pack.

Pin Name Parameter Min Typ Max Unit Notes

4 GND GND 0 0 V Ground

3, 5 VSIM 5V SIM Card

3V SIM Card

6 DATA 5V Vin/Vout

3V Vin/Vout

2 SIMRST 5V SIM Card

3V SIM Card

4.8

2.8

4.0

0

2.8

0

4.0

2.8

5.0

3.0

”1”

”0”

”1”

”0”

”1”

”1”

5.2

3.2

VSIM

0.5

VSIM

0.5

VSIM

VSIM

V Supply voltage

V SIM data

Trise/Tfall max 1us

V SIM reset

1 SIMCLK Frequency

Trise/Tfall

3.25

25

MHz

ns

SIM clock

RTC backup battery

The RTC block in CCONT needs a power backup to keep the clock running when the phone battery is disconnected. The backup power is supplied from a rechargable polyacene battery that can keep the clock running ten minutes minimum. The backup battery is charged from the main

battery through CHAPS.

Signal Parameter Min Typ Max Unit Notes

VBACK

VBACK

Backup battery charging from CHAPS

Backup battery charging from CHAPS

Backup battery supply

to CCONT

Backup battery supply

to CCONT

3.02 3.15 3.28 V

100 200 500 uA Vout@VBAT–0.2V

2 3.28 V

80 uA

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 11

Page 12

NSB–6

System Module

Power Distribution

In normal operation the baseband is powered from the phone‘s battery.

The battery consists of one Lithium–Ion cell. An external charger can be

used for recharging the battery and supplying power to the phone.

The baseband contains parts that control power distribution to whole

phone excluding those parts that use continuous battery supply. The battery feeds power directly to the CCONT and UI (buzzer and display and

keyboard lights).

The power management circuit CHAPS provides protection against overvoltages, charger failures and pirate chargers etc. that would otherwise

cause damage to the phone.

PAMS Technical Documentation

UI

(LCD,

backlights,

buzzer)

Baseband

RF

MAD2 +

MEMORY

RF supply voltages

VCobba

Vbb

CHRG_CTRL

VCORE

RTC backup

Battery connector

VB

CCONTCOBBA GJP

Vbatt

CHAPS

VChar

Charger & headset connector

Battery charging

The electrical specifications give the idle voltages produced by the acceptable chargers at the DC connector input. The absolute maximum input voltage is 30V due to the transient suppressor that is protecting the

charger input. At phone end there is no difference between a plug–in

charger or a desktop charger. The DC–jack pins and bottom connector

charging pads are connected together inside the phone.

Page 12

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 13

PAMS Technical Documentation

NSB–6

System Module

MAD

VBAT

MAD

CCONTINT

CCONT

Startup Charging

LIM

0R22

PWM_OUT

GND

ICHAR

VCHAR

VOUT

CHAPS

RSENSE

PWM

22k

VCH

GND

1n

TRANSCEIVER

1u

100k

10k

30V

2A

VIN

L_GND

CHARGER

When a charger is connected, the CHAPS is supplying a startup current

minimum of 130mA to the phone. The startup current provides initial

charging to a phone with an empty battery. Startup circuit charges the

battery until the battery voltage level is reaches 3.0V (+/– 0.1V) and the

CCONT releases the PURX reset signal and program execution starts.

Charging mode is changed from startup charging to PWM charging that is

controlled by the MCU software. If the battery voltage reaches 3.55V

(3.75V maximum) before the program has taken control over the charging, the startup current is switched off. The startup current is switched on

again when the battery voltage is sunken 100mV (nominal).

Parameter Symbol Min Typ Max Unit

VOUT Start– up mode cutoff limit Vstart 3.45 3.55 3.75 V

VOUT Start– up mode hysteresis

Vstarthys 80 100 200 mV

NOTE: Cout = 4.7 uF

Start–up regulator output current

Istart 130 165 200 mA

VOUT = 0V ... Vstart

Battery Overvoltage Protection

Output overvoltage protection is used to protect phone from damage.

The power switch is immediately turned OFF if the voltage in VOUT rises

above the selected limit VLIM1 or VLIM2.

Parameter Symbol LIM input Min Typ Max Unit

Output voltage cutoff limit

(during transmission or Li–

battery)

VLIM LOW 4.4 4.6 4.8 V

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 13

Page 14

NSB–6

System Module

The voltage limit (VLIM1 or VLIM2) is selected by logic LOW or logic

HIGH on the CHAPS (N101) VLIM input pin. VLIM is fixed low in hardware.

When the switch in output overvoltage situation has once turned OFF, it

stays OFF until the the battery voltage falls below VLIM and PWM = LOW

is detected. The switch can be turned on again by setting PWM = HIGH.

VCH

VCH<VOUT

VOUT

VLIM

PAMS Technical Documentation

t

SWITCH

PWM (32Hz)

ON OFF

t

ON

Page 14

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 15

PAMS Technical Documentation

Battery Removal During Charging

Output overvoltage protection is also needed in case the main battery is

removed when charger connected or charger is connected before the battery is connected to the phone.

With a charger connected, if VOUT exceeds VLIM, CHAPS turns switch

OFF until the charger input has sunken below Vpor (nominal 3.0V, maximum 3.4V). MCU software will stop the charging (turn off PWM) when it

detects that battery has been removed. The CHAPS remains in protection

state as long as PWM stays HIGH after the output overvoltage situation

has occured.

NSB–6

System Module

VCH

(Standard

Charger)

VOUT

PWM

SWITCH

Vpor

VLIM

4V

Vstart

”1”

”0”

ON

OFF

Droop depends on load

& C in phone

2

5

4

6

7

Istart off due to VCH<Vpor

Vstarthys

t

t

t

1.1Battery removed, (standard) charger connected, VOUT rises (follows charger voltage)

2. VOUT exceeds limit VLIM(X), switch is turned immediately OFF

3.3VOUT falls (because no battery) , also VCH<Vpor (standard chargers full–rectified

output). When VCH > Vpor and VOUT < VLIM(X) –> switch turned on again (also PWM

is still HIGH) and VOUT again exceeds VLIM(X).

4. Software sets PWM = LOW –> CHAPS does not enter PWM mode

5. PWM low –> Startup mode, startup current flows until Vstart limit reached

6. VOUT exceeds limit Vstart, Istart is turned off

7. VCH falls below Vpor

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 15

Page 16

NSB–6

System Module

PAMS Technical Documentation

PWM

When a charger is used, the power switch is turned ON and OFF by the

PWM input. PWM rate is 1Hz. When PWM is HIGH, the switch is ON and

the output current Iout = charger current – CHAPS supply current. When

PWM is LOW, the switch is OFF and the output current Iout = 0. To prevent the switching transients inducing noise in audio circuitry of the phone

soft switching is used.

Battery Identification

Different battery types are identified by a pulldown resistor inside the battery pack. The BSI line inside transceiver has a 100k pullup to VBB. The

MCU can identify the battery by reading the BSI line DC–voltage level

with a CCONT (N100) A/D–converter.

Name Min Typ Max Unit Notes

BSI

0 2.8 V Battery size indication

100k pullup resistor to VBB in phone

SIM Card removal detection

(Treshold is 2.4V@VBB=2.8V)

68 kohm Indication of a BLB–2 battery (600 mAh Li–Ion)

22 kohm Indication resistor for a service battery

VBATT

BATTERY

BTEMP

BSI

R

s

BGND

2.8V

100k

10k

BSI

10n

SIMCardDetX

TRANSCEIVER

CCONT

MAD

Page 16

The battery identification line is used also for battery removal detection.

The BSI line is connected to a SIMCardDetX line of MAD2. SIMCardDetX

is a threshold detector with a nominal input switching level 0.85xVcc for a

rising edge and 0.55xVcc for a falling edge. The battery removal detection

is used as a trigger to power down the SIM card before the power is lost.

The BSI contact in the battery contact disconnects before the other contacts so that there is a delay between battery removal detection and supply power off.

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 17

PAMS Technical Documentation

Vcc

0.850.05 Vcc

0.550.05 Vcc

SIMCARDDETX

GND

Battery Temperature

The battery temperature is measured with a NTC inside the battery pack.

The BTEMP line inside transceiver has a 100k pullup to VREF. The MCU

can calculate the battery temperature by reading the BTEMP line DC–

voltage level with a CCONT (N100) A/D–converter.

NSB–6

System Module

S

IGOUT

Pin Name Min Typ Max Unit Notes

3 BTEMP

0 1.4 V Battery temperature indication

100k pullup resistor to VREF in phone

Battery package has NTC pull down resis-

tor:

47k +/–5%@+25C , B=4050+/–3%

2.1

5

–5 5 % 100k pullup resistor tolerance

10

47 kohm Service battery value

BATTERY

3

20

VBATT

BSI

BTEMP

V

ms

Phone power up by battery (input)

Power up pulse width

TRANSCEIVER

VREF

100k

10k

BTEMP

CCONT

Issue 1 06/2000

R

NTC

T

BGND

E Nokia Mobile Phones Ltd.

Page 17

Page 18

NSB–6

System Module

Supply Voltage Regulators

The heart of the power distrubution is the CCONT. It includes all the voltage regulators and feeds the power to the whole system. The baseband

digital parts are powered from the VBB regulator which provides 2.8V

baseband supply. The baseband regulator is active always when the

phone is powered on. The VBB baseband regulator feeds MAD and memories, COBBA digital parts and the LCD driver in the UI section. There is

a separate regulator for a SIM card. The regulator is selectable between

3V and 5V and controlled by the SIMPwr line from MAD to CCONT. The

COBBA analog parts are powered from a dedicated 2.8V supply VCOBBA. The CCONT supplies also 5V for RF and for flash VPP. The CCONT

contains a real time clock function, which is powered from a RTC backup

when the main battery is disconnected. The RTC backup is rechargable

polyacene battery. The battery is charged from the main battery voltage

by the CHAPS when the main battery voltage is over 3.2V.

PAMS Technical Documentation

Operating mode

V ref

RF REG VCOBBA VBB VSIM SIMIF

Power off Off Off Off Off Off Pull

down

Power on On On/Off On On On On/Off

Reset On Off

VR1 On

On On Off Pull

down

Sleep On Off Off On On On/Off

NOTE: COBBA regulator is off in SLEEP mode. Its output pin may be fed

from VBB in SLEEP mode by setting bit RFReg(5) to ’1’ (default).

CCONT includes also five additional 2.8V regulators providing power to

the RF section. These regulators can be controlled either by the direct

control signals from MAD or by the RF regulator control register in

CCONT which MAD can update. Below are the listed the MAD control

lines and the regulators they are controlling.

– TxPwr controls VTX regulator (VR5)

– RxPwr controls VRX regulator (VR2)

Page 18

– SynthPwr controls all the rf regulators except VR1

– VCXOPwr controls VXO regulator (VR1)

In additon to the above mentioned signals MAD includes also TXP control

signal which goes to HAGAR power control block. The transmitter power

control TXC is led from COBBA to HAGAR.

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 19

PAMS Technical Documentation

Regulators output voltage characteristics:

Characteristics Condition Min Typ Max Unit

Output current VR1–VR6 Vout@2.8V 100 mA

System Module

NSB–6

Output current VR7

Depends on external BJT

Output current VR7BASE

Base current limit

Output current VBB On

Current limit 250mA

Output current VBB Sleep

Current limit 5mA

Output voltage VR1–VR7 over full tempera-

Output voltage VBB over full tempera-

Output voltage V2V (VCORE) Programmable:

Output voltage V2V (VCORE) tolerance

Line regulation (not VBB) F v 10kHz,

Line regulation (not VBB) F v 100kHz,

Line regulation VBB, V2V (VCORE) F v 100kHz

Load regulation T = 25_C 0.6 1 mV/mA

Vout@2.8V

Vout@2.8V

Vout@2.8V

Vout@2.8V

2.7 2.8 2.85 V

ture, input voltage

and load range

2.7 2.8 2.85 V

ture, input voltage

and load range

1.30 2.65 V

Vout=1.3V+225mV

*n

N = 0,1,2,3,4,5,6

–5 +5 %

49 DB

2) VBA T>3.15V

40 DB

2) VBA T>3.15v

30 DB

2)

150 mA

–10 mA

125

1

mA

mA

Supply current (each regulator)

VR1...VR7

Supply current VBB ON mode I

Supply current VBB SLEEP mode I

Output voltage V2V (VCORE) MAD2WD1 C10

ON mode I

MAD2WD1 C07

MAD2WD1 C05

NOTE 1: Characteristics above are NOT valid if Vbat < 3.0V.

NOTE 2: Line regulation is 20dB for f<100kHz when battery voltage is

lower than 3.1V.

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

out

330

out

250

out

100

2.65

1.75

1.75

/60+

/60+

/60+

I

I

I

out

out

out

/10+

540

/10+

400

/10+

150

mA

mA

mA

V

Page 19

Page 20

NSB–6

System Module

Switched Mode Supply VSIM

There is a switched mode supply for SIM–interface. SIM voltage is selected via serial IO. The 5V SMR can be switched on independently of the

SIM voltage selection, but can’t be switched off when VSIM voltage value

is set to 5V.

NOTE: VSIM and V5V can give together a total of 30mA.

In the next figure the principle of the SMR / VSIM–functions is shown.

CCONT External

VBAT

PAMS Technical Documentation

V5V_4

V5V_3

V5V_2

VSIM

5V reg

Power Up and Power Down

The baseband is powered up by:

1. Pressing the power key, that generates a PWRONX interrupt

signal from the power key to the CCONT, which starts the power up procedure.

2. Connecting a charger to the phone. The CCONT recognizes

the charger from the VCHAR voltage and starts the power up

procedure.

3. A RTC interrupt. If the real time clock is set to alarm and the

phone is switched off, the RTC generates an interrupt signal,

when the alarm is gone off. The RTC interrupt signal is connected to the PWRONX line to give a power on signal to the

CCONT just like the power key.

V5V

5V

5/3V

4. A battery interrupt. Intelligent battery packs have a possibility

to power up the phone. When the battery gives a short (10ms)

voltage pulse through the BTEMP pin, the CCONT wakes up

and starts the power on procedure.

Power up with a charger

When the charger is connected CCONT will switch on the CCONT digital

voltage as soon as the battery voltage exceeds 3.0V. The reset for

Page 20

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 21

PAMS Technical Documentation

CCONT’s digital parts is released when the operating voltage is stabilized

( 50 us from switching on the voltages). Operating voltage for VCXO is

also switched on. The counter in CCONT digital section will keep MAD in

reset for 62 ms (PURX) to make sure that the clock provided by VCXO is

stable. After this delay MAD reset is relased, and VCXO –control

(SLEEPX) is given to MAD. The next diagram explains the power on procedure with charger ( the picture assumes empty battery, but the situation

would be the same with full battery):

NSB–6

System Module

SLEEPX

PURX

CCPURX

12 3

1: Battery voltage over 3.0==>Digital voltages to CCONT (VBB)

2: CCONT digital reset released. VCXO turned on

3: 62ms delay before PURX released

When the phone is powered up with an empty battery pack using the

standard charger, the charger may not supply enough current for standard powerup procedure and the powerup must be delayed.

Power Up With The Power Switch (PWRONX)

When the power on switch is pressed the PWRONX signal will go low.

CCONT will switch on the CCONT digital section and VCXO as was the

case with the charger driven power up. If PWRONX is low when the 64

ms delay expires, PURX is released and SLEEPX control goes to MAD. If

PWRONX is not low when 64 ms expires, PURX will not be released, and

CCONT will go to power off ( digital section will send power off signal to

analog parts)

Vbat

VR6

VR1

VBB (2.8V)

Vchar

Vref

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 21

Page 22

NSB–6

System Module

12 3

1:Power switch pressed ==> Digital voltages on in CCONT (VBB)

2: CCONT digital reset released. VCXO turned on

3: 62 ms delay to see if power switch is still pressed.

PAMS Technical Documentation

SLEEPX

PURX

CCPURX

PWRONX

VR1,VR6

VBB (2.8V)

Vchar

Power Up by RTC

RTC (internal in CCONT) can power the phone up by changing RTCPwr

to logical 1.

Power Up by IBI

IBI can power CCONT up by giving a short pulse (10ms) through the

BTEMP line. After powerup BTEMP will act as any other input channel for

ADC.

When the PURX reset is released, the MAD releases the system reset

ExtSysResetX and the internal MCUResetX signals and starts the boot

program execution from MAD bootrom if MAD GenSDIO pin is pulled low

or from external memory if GenSDIO pin is pulled high. In normal operation the program execution continues from the flash program memory. If

the MBUS line is pulled low during the power up the bootrom starts a

flash programming sequence and waits for the prommer response

through FBUS_RX line.

Power Down

The baseband is powered down by:

Page 22

1. Pressing the power key, that is monitored by the MAD, which

starts the power down procedure.

2. If the battery voltage is dropped below the operation limit, either by not charging it or by removing the battery.

3. Letting the CCONT watchdog expire, which switches off all

CCONT regulators and the phone is powered down.

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 23

PAMS Technical Documentation

4. Setting the real time clock to power off the phone by a timer.

The RTC generates an interrupt signal, when the alarm is gone

off. The RTC interrupt signal is connected to the PWRONX line

to give a power off signal to the CCONT just like the power key.

The power down is controlled by the MAD. When the power key has been

pressed long enough or the battery voltage is dropped below the limit the

MCU initiates a power down procedure and disconnects the SIM power.

Then the MCU outputs a system reset signal and resets the DSP. If there

is no charger connected the MCU writes a short delay to CCONT watchdog and resets itself. After the set delay the CCONT watchdog expires,

which activates the PURX and all regulators are switched off and the

phone is powered down by the CCONT.

If a charger is connected when the power key is pressed the phone enters into the acting dead mode.

Modes of Operation

NSB–6

System Module

Acting Dead

If the phone is off when the charger is connected, the phone is powered

on but enters a state called ”acting dead”. To the user the phone acts as if

it was switched off. A battery charging alert is given and/or a battery

charging indication on the display is shown to acknowledge the user that

the battery is being charged.

Active Mode

In the active mode the phone is in normal operation, scanning for channels, listening to a base station, transmitting and processing information.

All the CCONT regulators are operating. There are several substates in

the active mode depending on if the phone is in burst reception, burst

transmission, if DSP is working etc.

Sleep Mode

In the sleep mode all the regulators except the baseband VBB and the

SIM card VSIM regulators are off. Sleep mode is activated by the MAD

after MCU and DSP clocks have been switched off. The voltage regulators for the RF section are switched off and the VCXO power control,

VCXOPwr is set low. In this state only the 32 kHz sleep clock oscillator in

CCONT is running. The flash memory power down input is connected to

the ExtSysResetX signal, and the flash is deep powered down during the

sleep mode.

The sleep mode is exited either by the expiration of a sleep clock counter

in the MAD or by some external interrupt, generated by a charger connection, key press, headset connection etc. The MAD starts the wake up

sequence and sets the VCXOPwr and ExtSysResetX control high. After

VCXO settling time other regulators and clocks are enabled for active

mode.

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 23

Page 24

NSB–6

System Module

If the battery pack is disconnect during the sleep mode, the CCONT pulls

the SIM interface lines low as there is no time to wake up the MCU.

Charging

Charging can be performed in any operating mode.The battery type/size

is indicated by a resistor inside the battery pack. The resistor value corresponds to a specific battery capacity. This capacity value is related to the

battery technology as different capacity values are achieved by using different battery technology.

The battery voltage, temperature, size and current are measured by the

CCONT controlled by the charging software running in the MAD.

The power management circuitry controls the charging current delivered

from the charger to the battery. Charging is controlled with a PWM input

signal, generated by the CCONT. The PWM pulse width is controlled by

the MAD and sent to the CCONT through a serial data bus. The battery

voltage rise is limited by turning the CHAPS switch off when the battery

voltage has reached 4.2 V. Charging current is monitored by measuring

the voltage drop across a 220 mohm resistor.

PAMS Technical Documentation

Watchdog

The Watchdog block inside CCONT contains a watchdog counter and

some additional logic which are used for controlling the power on and

power off procedures of CCONT. The WD-counter runs during that time,

though. Watchdog counter is reset internally to 32 s at power up. Normally it is reset by MAD writing a control word to the WDReg.

Page 24

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 25

PAMS Technical Documentation

Audio control

PCM serial interface

The interface consists of following signals: a PCM codec master clock

(PCMDClk), a frame synchronization signal to DSP (PCMSClk), a codec

transmit data line (PCMTX) and a codec receive data line (PCMRX). The

COBBA–GJP generates the PCMDClk clock, which is supplied to DSP

SIO. The COBBA–GJP also generates the PCMSClk signal to DSP by dividing the PCMDClk. The PCMDClk frequency is 512 kHz. PCMSClk frequency is 8.0 kHz.

PCMDClk

PCMSClk

NSB–6

System Module

PCMTxData

PCMRxData

sign extended

MSB

15 14 13 12 011 10

sign extended

MSB

LSB

LSB

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 25

Page 26

NSB–6

System Module

Digital Control

The baseband functions are controlled by the MAD asic, which consists of

a MCU, a system ASIC and a DSP.

MAD2 WD1

MAD2 WD1 contains following building blocks:

– ARM RISC processor with both 16–bit instruction set (THUMB mode)

and 32–bit instruction set (ARM mode)

– TI Lead DSP core with peripherials:

PAMS Technical Documentation

– API (Arm Port Interface memory) for MCU–DSP commu-

nication, DSP code download, MCU interrupt handling vec-

tors (in DSP RAM) and DSP booting.

– Serial port (connection to PCM)

– Timer

– DSP memory

– BUSC (BusController for controlling accesses from ARM to API, Sys-

tem Logic and MCU external memories, both 8– and 16–bit memories)

– System Logic

– CTSI (Clock, Timing, Sleep and Interrupt control)

– MCUIF (Interface to ARM via B

USC). Contains MCU Boo-

tROM

– DSPIF (Interface to DSP)

– MFI (Interface to COBBA AD/DA Converters)

– CODER (Block encoding/decoding and A51&A52 ciphering)

– AccIF(Accessory Interface)

– SCU (Synthesizer Control Unit for controlling 2 separate

synthesizer)

– UIF (Keyboard interface, serial control interface for COBBA

PCM Codec, LCD Driver and CCONT)

– SIMI (SimCard interface with enhanched features)

– PUP (Parallel IO, USART and PWM control unit for vibra

and buzzer)

Page 26

– Flexpool

The MAD2 operates from a 13 MHz system clock, which is generated

from the 13Mhz VCXO frequency. The MAD2 supplies a 6,5 MHz or a 13

MHz internal clock for the MCU and system logic blocks and a 13 MHz

clock for the DSP, where it is multiplied to 45.5 MHz DSP clock. The system clock can be stopped for a system sleep mode by disabling the

VCXO supply power from the CCONT regulator output. The CCONT provides a 32 kHz sleep clock for internal use and to the MAD2, which is

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 27

PAMS Technical Documentation

used for the sleep mode timing. The sleep clock is active when there is a

battery voltage available i.e. always when the battery is connected.

MAD2WD1 supply voltages are VBB and VCORE (V2V), VBB feed I/O

pins so that MAD2WD1 is externally fully compatible with old versions.

VCORE feed MAD2WD1 internal fuctions supplyoltage; CPU, DSP and

system logic.

NSB–6

System Module

Pin

N:o

A1 MCUGemIO 0 O 2 0 MCU General

C2

D2 Col4 I/O UIF 2 Input Program-

D3 Col3 I/O UIF 2 Input Program-

H11 MCUGenIO1 I/O 2 Input,

E4 GND Ground

D4 Col2 I/O UIF 2 Input Program-

C4 Col1 I/O UIF 2 Input program-

C3 Col0 I/O UIF 2 Input program-

D1 LCDCSX I/O UIF 2 Input external

E1

F12

E3 Row5LCDCD I/O UIF 2 Input,

N4 VCC_CORE Core VCC in

E2 Row4 I/O UIF 2 Input,

Pin Name Pin

T ype

LEADGND

LEADVCC

LoByteSelX

Connected

to/from

Drive

req.

mA

Reset

State

pullup

pullup

pullup

Note Explanation

purpose output

Lead Ground

I/O line for key-

mable pullup

PR0201

mable pullup

PR0201

Pullup

PR0201

mable pullup

PR0201

mable pullup

PR0201

mable pullup

PR0201

pullup/down

pullup

PR0201

3325c10

pullup

PR0201

board column 4

I/O line for keyboard column 3

General purpose

I/O port

I/O line for keyboard column 2

I/O line for keyboard column 1

I/O line for keyboard column 0

serial LCD driver

chip select, par-

allel LCD driver

enable

Lead Power

Keyboard row5

data I/O , serial

LCD driver com-

mand/data indi-

cator, parallel

LCD driver read/

write select

Power

I/O line for key-

board row 4, par-

allel LCD driver

register selection

control

port

NC

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 27

Page 28

NSB–6

System Module

PAMS Technical Documentation

Pin NamePin

N:o

F4 Row3 I/O UIF 2 Input,

F3 Row2 I/O UIF 2 Input,

F2 Row1 I/O UIF 2 Input,

F1 Row0 I/O UIF 2 Input,

L11 JTDO O 2 Tri–

L5 GND Ground

N12 JTRst I Input,

M12 JTClk I Input pulldown

N13 JTDI I Input,

M13 JTMS I Input,

G13 VCC_IO IO VCC in

L12 CoEmu0 I/O 2 Input,

L13 CoEmu1 I/O 2 Input,

H4

L1

N3 MCUAd0 O MCU

K4

N2 MCUAd1 O MCU

N1 MCUAd2 O MCU

M4 MCUAd3 O MCU

M3 MCUAd4 O MCU

M2 MCUAd5 O MCU

LEADGND

ARMGND

ARMVCC

Pin

Type

Connected

to/from

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

Drive

req.

mA

State

pullup

pullup

pullup

pullup

pullup

state

pull-

down

pullup

pullup

pullup

pullup

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

PR0201

pullup

PR0201

pullup

PR0201

pullup

PR0201

pulldown

PD0201

PD0201

pullup

PR0201

pullup

PR0201

3325c10

pullup

PR0201

pullup

PR0201

ExplanationNoteReset

I/O line for key-

board row 3, par-

allel LCD driver

data

I/O line for key-

board row 2, par-

allel LCD driver

data

I/O line for key-

board row 1, par-

allel LCD driver

data

I/O line for key-

board row 0, par-

allel LCD driver

data

JTAG data out

JTAG reset

JT AG Clock

JTAG data in

JTAG mode se-

lect

Power

DSP/MCU

emulation port 0

DSP/MCU

emulation port 1

Lead Ground

ARM Ground

bus

ARM Power

bus

bus

bus

bus

bus

Page 28

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 29

PAMS Technical Documentation

NSB–6

System Module

Pin NamePin

N:o

M1 MCUAd6 O MCU

H1 VCC_IO IO VCC in

L4 MCUAd7 O MCU

L3 MCUAd8 O MCU

L2 MCUAd9 O MCU

K5 MCUAd10 O MCU

J4 GND Ground

K3 MCUAd11 O MCU

K2 MCUAd12 O MCU

K1 MCUAd13 O MCU

J3 MCUAd14 O MCU

J2 MCUAd15 O MCU

J1 MCUAd16 O MCU

M10 VCC_CORE Core VCC in

H3 MCUAd17 O MCU

H2 MCUAd18 O MCU

G4 MCUAd19 O MCU

G3 MCUAd20 O MCU

G2 VCONT O

K6 ExtMCUDa0 I/O MCU

K9 GND Ground

L6 ExtMCUDa1 I/O MCU

M6 ExtMCUDa2 I/O MCU

N6 ExtMCUDa3 I/O MCU

L7 ExtMCUDa4 I/O MCU

Pin

Type

Connected

to/from

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

Drive

req.

mA

State

2 0 MCU address

3325c10

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

3325c10

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 Input MCU data bus

2 Output MCU data bus

2 Output MCU data bus

2 Output MCU data bus

2 Output MCU data bus

ExplanationNoteReset

bus

Power

bus

bus

bus

bus

bus

bus

bus

bus

bus

bus

Power

bus

bus

bus

bus

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 29

Page 30

NSB–6

System Module

PAMS Technical Documentation

Pin NamePin

N:o

M7 ExtMCUDa5 I/O MCU

N7 ExtMCUDa6 I/O MCU

N8 ExtMCUDa7 I/O MCU

M8 MCUGenIODa0 I/O 2 Input MCU Data in

L8 MCUGenIODa1 I/O 2 Input MCU Data in

K8 MCUGenIODa2 I/O 2 Input MCU Data in

N9 MCUGenIODa3 I/O 2 Input MCU Data in

E10 GND Ground

M9 MCUGenIODa4 I/O 2 Input MCU Data in

L9 MCUGenIODa5 I/O 2 Input MCU Data in

N10 MCUGenIODa6 I/O 2 Input MCU Data in

L10 MCUGenIODa7 I/O 2 Input MCU Data in

M5 MCURdX O MCU

G11 VCC_CORE Core VCC in

N5 MCUWrX O MCU

N11 ROM1SelX O MCU ROM 2 1 ROM chip select

M11 RAMSelX O MCU RAM 2 1 RAM chip select

J11 IRON O IR Mod 2 1 IR control

A1 MCUGenIO1 I/O 2 Input,

D8 DSPXF O 2 1 External flag

K10

K11 RFClk I VCXO Input System clock

K12 RFClkGnd Input System clock

K13 SIMCardDetX I Input SIM card detec-

J10

SCVCC

SCGND

Pin

Type

Connected

to/from

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

Drive

req.

mA

State

2 Output MCU data bus

2 Output MCU data bus

2 Output MCU data bus

16–bit mode

16–bit mode

16–bit mode

16–bit mode

16–bit mode

16–bit mode

16–bit mode

16–bit mode

2 1 MCU Read

3325c10

2 1 MCU write

pullup

pullup

PR0201

ExplanationNoteReset

General purpose

I/O port

General purpose

I/O port

General purpose

I/O port

General purpose

I/O port

General purpose

I/O port

General purpose

I/O port

General purpose

I/O port

General purpose

I/O port

strobe

Power

strobe

General purpose

I/O port

Special cell Pow-

er

from VCTCXO

reference ground

input

tion

Special cell

Ground

Page 30

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 31

PAMS Technical Documentation

NSB–6

System Module

Pin NamePin

N:o

D9 BuzzPWM O BUZZER 2 0 Buzzer PWM

D11

G12 VibraPWM O VIBRA 2 0 Vibra PWM con-

C9 GND Ground

E12 MCUGenIO3 I/O 2 Input,

E13 MCUGenIO2 I/O 2 Input,

J13 KBLights O UIF 2 1

C5 AccTxData I/O 4 Tri–

B6 VCC_IO IO VCC in

F11 HookDet I Input Non–MBUS ac-

F10 HeadDet I Input Headset detec-

D6 AccRxData I Input Accessory RX

D5 GND Ground

G10 MCUGenIO4 I/O 2 Input,

B5 MBUS I/O 2 Input,

E11 VCXOPwr O CCONT 2 1 VCXO regulator

D13 SynthPwr O CCONT 2 0 Synthesizer reg-

B7 VCC_CORE Core VCC in

C10 GenCCONTCSX O CCONT 2 1 Chip select to

F13

B10 GenSDIO I/O CCONT, UIF 2 Input,

A10 GenSClk O CCONT, UIF 2 0 Serial clock

C11 SIMCardData I/O CCONT 2 0 SIM data

J12 GND Ground

LEADVCC

LEADGND

Pin

Type

Connected

to/from

Drive

req.

mA

State

pullup

pullup

State

pull-

down

exter-

nal

pullup

exter-

nal

pullup/

down

pullup

PR1001

pullup

PR1001

external

pullup

3325c10

pulldown

PD1001

external

pullup

3325c10

external

pullup/down

depending

on how to

boot

ExplanationNoteReset

control

LEAD Power

trol

General purpose

I/O port

General purpose

I/O port

Accessory TX

data, Flash_TX

Power

cessory connec-

tion detector

tion interrupt

data, Flash_RX

General purpose

I/O port

MBUS, Flash

clock

control

ulator control

Power

CCONT

LEAD Ground

Serial data in/out

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 31

Page 32

NSB–6

System Module

PAMS Technical Documentation

Pin NamePin

N:o

B13 PURX I CCONT Input Power Up Reset

B12 CCONTInt I CCONT Input CCONT interrupt

A13 Clk32k I CCONT Input Sleep clock os-

D10 VCC_IO IO VCC in

A12 SIMCardClk O CCONT 2 0 SIM clock

B11 SIMCardRstX O CCONT 2 0 SIM reset

A11 SIMCardIOC O CCONT 2 0 SIM data in/out

D12 SIMCardPwr O CCONT 2 0 SIM power con-

H10

C13 RxPwr O 2 0 (RX regulator

C12 TxPwr O 2 0 (TX regulator

H12 TestMode I Input,

H13 ExtSysResetX O 2 0 System Reset

B9 PCMTxData O COBBA 2 0 Transmit data,

K7 VCC_IO IO VCC in

A9 PCMRxData I COBBA Input Receive data,

B8 PCMDClk I COBBA Input Transmit clock,

A8 PCMSClk I COBBA Input Transmitframe

C6 COBBAClk O COBBA 4 1 COBBA clock,

A6 COBBACSX COBBA COBBA

A7 COBBASD COBBA COBBA

C7 IData COBBA COBBA

D7 QData COBBA COBBA

G1 VCC_CORE Core VCC in

C1 DSPGenOut3 O RF 2 0 DSP general

B4 DSPGenOut2 O RF 2 0 DSP general

A4 DSPGenOut1 O RF 2 0 DSP general

LEADVCC

Pin

Type

Connected

to/from

Drive

req.

mA

State

pull-

down

3325c10

pulldown

PD0201

3325c10

3325c10

ExplanationNoteReset

cillator input

Power

control

trol

LEAD Power

control)

control)

Test mode select

DX

Power

RX

CLKX

sync, FSX

13 MHz

Power

purpose output

purpose output

purpose output

Page 32

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 33

PAMS Technical Documentation

NSB–6

System Module

Pin NamePin

N:o

A5 DSPGenOut0 O CRFU 2 0 DSP general

A3 FrACtrl O RF 2 0 RF front amplifi-

B3 SynthEna O HAGAR 2 0 Synthesizer data

B1 SynthClk O HAGAR 2 0 Synthesizer

B2 SynthData O HAGAR 2 0 Synthesizer data

A2 TxPA O HAGAR 2 0 Power amplifier

Pin

Type

Connected

to/from

Drive

req.

mA

State

ExplanationNoteReset

purpose output

er control

enable

clock

control

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 33

Page 34

NSB–6

System Module

Memories

MAD memory configuration

The MAD2WD1 used in NSB–6 contains 16 kW RAM, and 80 kW ROM

memory.

Memory

The MCU program code resides in an external flash program memory,

which size is 16Mbits (1024k x 16bit). The MCU work (data) memory size

is 2048 kbits (256k x 16bit). Flash and SRAM memory chips are packed

in same combo memory package.

The BusController (BUSC) section in the MAD decodes the chip select

signals for the external memory devices and the system logic. BUSC controls internal and external bus drivers and multiplexers connected to the

MCU data bus. The MCU address space is divided into access areas with

separate chip select signals. BUSC supports a programmable number of

wait states for each memory range.

PAMS Technical Documentation

Program and Data Memory

The MCU program code resides in the program memory. The program

memory is 16Mbits (1024k x 16bit) Flash memory.

The flash memory has a power down pin that should be kept low, during

the power up phase of the flash to ensure that the device is powered up

in the correct state, read only. The power down pin is utilized in the system sleep mode by connecting the ExtSysResetX to the flash power down

pin to minimize the flash power consumption during the sleep.

Nonvolatile data memory is implemented with program (Flash) memory.

Special EEPROM emulation (EEEMmu) software is utilized.

Work Memory

The work memory is a static RAM of size 2096k (256k x 16). The memory

contents are lost when the baseband voltage is switched off. All retainable

data must be stored into the data memory when the phone is powered

down.

MCU Memory Requirements

Device Organization Access Time ns Wait States Used Remarks

FLASH 1024kx16 120 1 uBGA 48

SRAM 256kx16 120 1 uBGA 48

MCU Memory Map

MAD2 supports maximum of 4GB internal and 4MB external address

space. External memories use address lines MCUAd0 to MCUAd21 and

Page 34

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 35

PAMS Technical Documentation

8–bit/16–bit databus. The BUSC bus controller supports 8– and 16–bit

access for byte, double byte, word and double word data. Access wait

states (0, 1 or 2) and used databus width can be selected separately for

each memory block.

Flash Programming

The phone have to be connected to the flash loading adapter so that supply voltage for the phone and data transmission lines can be supplied

from/to the adapter. When adapter switches supply voltage to the phone,

the program execution starts from the BOOT ROM and the MCU investigates in the early start–up sequence if the flash prommer is connected.

This is done by checking the status of the MBUS–line. Normally this line

is high but when the flash prommer is connected the line is forced low by

the prommer.

The flash prommer serial data receive line is in receive mode waiting for

an acknowledgement from the phone. The data transmit line from the

baseband to the prommer is initially high. When the baseband has recognized the flash prommer, the TX–line is pulled low. This acknowledgement is used to start to toggle MBUS (FCLK) line three times in order that

MAD2 gets initialized. This must be happened within 15 ms after TX line

is pulled low. After that the data transfer of the first two bytes from the

flash prommer to the baseband on the RX–line must be done within 1 ms.

NSB–6

System Module

When MAD2 has received the secondary boot byte count information, it

forces TX line high. Now, the secondary boot code must be sent to the

phone within 10 ms per 16 bit word. If these timeout values are exceeded,

the MCU (MAD2) starts normal code execution from flash. After this, the

timing between the phone and the flash prommer is handled with dummy

bites.

A 5V programming voltage is supplied inside the transceiver from the battery voltage with a switch mode regulator (5V/30mA) of the CCONT. The

5V is connected to VPP pin of the flash.

Characteristcs Min Typ Max Unit

Time from boot indication to MAD2

initialization sequence

Time from MAD2 initialization sequence to byte lenght information

Time from byte lenght information to

end of secondary boot code loading.

15 ms

1 ms

10 per16

bit word

ms

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 35

Page 36

NSB–6

System Module

Flash Programming Sequence

PAMS Technical Documentation

CCONT pin

(PurX)

MAD pin

(FCLK (MBUS))

MAD pin 109

(FRX (FRxData))

MAD pin

(FTX (FTxData))

SRAM D221 (Chip Sel)

FLASH D210 (Chip Sel)

COBBA GJP

COBBA GJP ASIC provides an interface between the baseband and the

RF–circuitry. COBBA performs analogue to digital conversion of the receive signal. For transmit path COBBA performs digital to analogue conversion of the transmit amplifier power control ramp and the in–phase and

CCONT pin

(PurX)

MAD pin

(FCLK (MBUS))

MAD pin

(FRX (FRxData))

MAD pin

(FTX (FTxData))

Page 36

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 37

PAMS Technical Documentation

quadrature signals. A slow speed digital to analogue converter will provide automatic frequency control (AFC).

COBBA is at any time connected to MAD asic with two interfaces, one for

transferring TX and RX data between MAD and COBBA and one for

transferring codec RX/TX samples.

Real Time Clock

Requirements for a real time clock implementation are a basic clock

(hours and minutes), a calender and a timer with alarm and power on/off

–function and miscellaneous calls. The RTC will contain only the time

base and the alarm timer but all other functions (e.g. calendar) will be implemented with the MCU software. The RTC needs a power backup to

keep the clock running when the phone battery is disconnected. The

backup power is supplied from a rechargable polyacene battery that can

keep the clock running some ten minutes. If the backup has expired, the

RTC clock restarts after the main battery is connected. The CCONT

keeps MCU in reset until the 32kHz source is settled (1s max).

NSB–6

System Module

The CCONT is an ideal place for an integrated real time clock as the asic

already contains the power up/down functions and a sleep control with

the 32kHz sleep clock, which is running always when the phone battery is

connected. This sleep clock is used for a time source to a RTC block.

RTC backup battery charging

CHAPS has a current limited voltage regulator for charging a backup battery. The regulator derives its power from VOUT so that charging can take

place without the need to connect a charger. The backup battery is only

used to provide power to a real time clock when VOUT is not present so it

is important that power to the charging circuitry is derived from VOUT and

that the charging circuitry does not present a load to the backup battery

when VOUT is not present.

It should not be possible for charging current to flow from the backup battery into VOUT if VOUT happens to be lower than VBACK. Charging current will gradually diminish as the backup battery voltage reaches that of

the regulation voltage.

Security

The phone flash program and IMEI code are software protected using an

external security device that is connected between the phone and a PC.

The security device uses the phone given IMEI number, the software version number and a 24bit hardware random serial number that is read

from the COBBA and calculates a flash authority identification number

that is stored into the phone (emulated) EEPROM.

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

Page 37

Page 38

NSB–6

System Module

Baseband Testing

The MCU software enters a local mode at startup if a dummy battery is

attached and the battery temperature value is high enough. This means

that the fixed resistor on the BTEMP line must correspond to a temperature higher than +85 C. In the local mode the baseband can be controlled

through MBUS or FBUS connections by a PC–locals software. Baseband

internal connections are tested with self tests if possible. By connecting

MAD2 pin ROW5 to ground, MAD2 pins are toggled as a daisy chain,

which can be used for detecting short circuits in MAD2 pins. Test pads will

be placed on engine pcb for service and production trouble shooting purposes in some supply voltage and signal lines.

Alignments

Within alignment those parameters are adjusted, that cannot be set accurate enough by design, because of component tolerances.

Due to use of 5% resistor values, the channels of the CCONT A/D converters need to be aligned in the production phase.

PAMS Technical Documentation

Within battery voltage VBATT tuning the MCU software reads the A/D

reading from CCONT at 3.6V and stores this reading to EEPROM

memory as a reference point. Another reference point is created by assuming that when the input voltage is zero, A/D reading is also zero. Now

the slope is known and A/D readings can be calibrated. Calibration is included in VBATT A/D reading task.

Battery charging voltage VCHAR and current ICHAR are calibrated using

one test setting. Test jig in production line must have a connection to battery terminals. ICHAR is adjusted to 500mA and VCHAR to 8.4V with appropriate load connected to the battery terminals.

BTEMP is calibrated with 47kohm resistor.

BSI is calibrated with 22kohm resistor.

Baseband Startup for Testing

When an unprogrammed module is powered up the first time the MCU

starts from the boot rom inside the MAD2. The MBUS line is to be kept

low to inform the MCU that the flash prommer is connected and the MCU

should stop after the boot and wait for a download code.

When the flash programming is performed successfully the MCU switches

to flash prom software. If the baseband is powered up for the first time the

MCU will remain in local mode as the factory set has not been executed.

To allow re–programming of working modules the MCU is at startup

forced into local mode by connecting the BSI and BTEMP signals to

ground using specified resistors.

Page 38

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 39

PAMS Technical Documentation

RF Module

This RF module takes care of all RF functions of EGSM/GSM1900 dualband engine. RF circuitry is located on one side of the 8 layer tranceiver–

PCB. PCB area for the RF circuitry is about 15 cm2. The RF design is

based on the first dualband direct conversion RF–IC ”Hagar”. So there is

no intermediate frequency and that means the number of component is

much lower than before and there shall be much less interference problems than previously.

EMC emissions are taken care of using metallized plastic shield, which

screens the whole transceiver. Internal screening is realized with isolated

partitions. VCO is isolated in it’s own locker. PA and some surrounding

components are covered with metal can. The baseband circuitry is located on the same side of the same board.

Environmental specifications

Normal and extreme voltages

NSB–6

System Module

Lithium–ion battery ( 1 cell )

Nominal voltage: 3.9 V

Lower extreme voltage: 0.85 x 3.9 = 3.31 V

Higher extreme voltage: same as nominal

Absolute maximum voltage: 4.8 V

Software cut–off voltage: 3.1 V (during TX burst)

Main Technical specifications

Maximum Ratings

Parameter Rating

Battery voltage, idle mode 3.9 V

Regulated supply voltage 2.8 +/– 3% V

Voltage reference 1.5 +/– 1.5% V

Operating temperature range –10...+55 deg. C

Absolute maximum battery voltage 4.8 V

RF Characteristics

Receive frequency range 925 ... 960 MHz / 1930 ... 1990 MHz

Transmit frequency range 880 ... 915 MHz / 1850 ... 1910 MHz

Duplex spacing 45 MHz / 80 MHz

Channel spacing 200 kHz

Number of RF channels 174 / 299

Power class 4 (EGSM900) / 1 (GSM1900)

Number of power levels 15 / 16

Issue 1 06/2000

Item Values (EGSM / GSM1900)

E Nokia Mobile Phones Ltd.

Page 39

Page 40

NSB–6

System Module

RF Frequency Plan

PAMS Technical Documentation

925–960

MHz

1930–1990

MHz

880–915

MHz

1850–1910

MHz

f/2

f/2

f/2

HAGAR

I–signalI–signalI–signal

I–signal

Q–signal

f

f

RX

f/2

f

3520–

PLL

f

f

3980

MHz

26 MHz

VCTCXO

13 MHz

f/2

I–signal

Q–signal

TX

DC characteristics

Regulators

Transceiver has a multi function power management IC at baseband section, which contains among other functions, also 7 pcs of 2.8 V regulators.

All regulators can be controlled individually with 2.8 V logic directly or

through control register. In GSM direct controls are used to get fast

switching, because regulators are used to enable RF–functions.

VREF_2 from CCONT IC and RXREF from COBBA IC are used as the

reference voltages for HAGAR RF–IC, VREF_2 (1.5V) for bias reference

and RXREF (1.2V) for RX ADC’s reference.

Control signals (typical current consumption in different modes)

VXCOPWR

L L L L L <10 uA Leakage current ( PA )

H H L L L 28 mA Synthesizer

H H H L L 81 mA RX active

H H L H L 138 mA TX active except PA

H H L H H 1900 mA TX active, full power

SYNTHPWR

RXPWR TXPWR TXP Typ. cur-

rent cons.

Notes

Page 40

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 41

PAMS Technical Documentation

Power Distribution Diagram

NSB–6

System Module

1.57 A

BATTERY

3.6 V

Vpc

(Hagar)

PA

SYNPWRVXOENAVBATT

vcp

V5V

extreg

4V5

15 mA

VCO

TXC TXP

VR

7

20 mA

VR

6

COBBA

analog

VR

vtx

5

HAGAR

RF–IC

VR

3

vsyn_1

LNA

VREF

HAGAR

bias ref

6 mA

PLL

VR

VR

4

2

20 mA

vsyn_2

TX: 100 mA

RX: 53 mA

vrx

1 mA

RX / TX

parts

Issue 1 06/2000

2 mA

VCTCXO

+buff.

VR

1

vxo

E Nokia Mobile Phones Ltd.

Page 41

Page 42

NSB–6

System Module

RF Functional Description

Architecture contains one RF–IC, dualband PA module, VCO–module,

VCTCXO module and discrete LNA stages for both receive bands.

PAMS Technical Documentation

HAGAR

RX_I

RX_Q

RXref 1.2V

ANT

SW

EGSM

PCS

Bias crtl

Low pwr crtl

Dual PA

PCS

EGSM

SAW

EGSM

BIAS

VCTCXO

SHF

VCO

PLL

Vref_2 1.5V

Serial CTRL BUS

AFC

RFC

TXC

TXP

TXIP

TXIN

TXQP

TXQN

Page 42

E Nokia Mobile Phones Ltd.

Issue 1 06/2000

Page 43

PAMS Technical Documentation

Frequency synthesizer

VCO frequency is locked with PLL into stable frequency source, which is

a VCTCXO–module ( voltage controlled temperature compensated crystal

oscillator ). VCTCXO is running at 26 MHz. Temperature effect is controlled with AFC ( automatic frequency control ) voltage. VCTCXO is

locked into frequency of the base station. AFC is generated by baseband

with a 11 bit conventional DAC in COBBA.

PLL is located in HAGAR RF–IC and is controled via serial bus from

COBBA–IC (baseband).

There are 64/65 (P/P+1) prescaler, N– and A–divider, reference divider,

phase detector and charge pump for the external loop filter. SHF local signal, generated by a VCO–module ( VCO = voltage controlled oscillator ),

is fed to prescaler. Prescaler is a dual modulus divider. Output of the

prescaler is fed to N– and A–divider, which produce the input to phase

detector. Phase detector compares this signal to reference signal

(400kHz), which is divided with reference divider from VCTCXO output.

Output of the phase detector is connected into charge pump, which

charges or discharges integrator capacitor in the loop filter depending on

the phase of the measured frequency compared to reference frequency.

NSB–6

System Module

Loop filter filters out the pulses and generates DC control voltage to VCO.

Loop filter defines step response of the PLL ( settling time ) and effects to

stability of the loop. That is why integrator capacitor has a resistor for

phase compensation. Other filter components are for sideband rejection.

Dividers are controlled via serial bus. SDATA is for data, SCLK is serial

clock for the bus and SENA1 is a latch enable, which stores new data into

dividers.

freq.

R

f

ref

f_out /

M

PHASE

DET.

CHARGE

PUMP

Kd

reference

AFC–controlled VCTCXO

LP

VCO

Kvco

f_out

LO–signal is generated by SHF VCO module. VCO has double frequency

in GSM1900 and x 4 frequency in EGSM compared to actual RF channel

frequency. LO signal is divided by two or four in HAGAR (depending on

system mode).

Issue 1 06/2000

E Nokia Mobile Phones Ltd.

M

M = A(P+1) + (N–A)P=

= NP+A

Page 43

Page 44

NSB–6

System Module

Receiver

Receiver is a direct conversion, dualband linear receiver. Received RF–

signal from the antenna is fed via RF–antenna switch to 1st RX dualband

SAW filter and discrete LNAs (low noise amplifier), separate LNA

branches for EGSM900 and GSM1900. Gain selection control of LNAs

comes from HAGAR IC. Gain step is activated when RF–level in antenna

is about –40 dBm.

After the LNA amplified signal (with low noise level) is fed to bandpass

filter (2nd RX dualband SAW filter). RX bandpass filters defines how good

are the blocking characteristics against spurious signals outside receive

band and the protection against spurious responses.

These bandpass filtered signals are then balanced with baluns. Differential RX signal is amplified and mixed directly down to BB frequency in HAGAR. Local signal is generated with external VCO. VCO signal is divided

by 2 (GSM1900) or by 4 (EGSM900). PLL and dividers are in HAGAR–IC.

From the mixer output to ADC input RX signal is divided into I– and Qsignals. Accurate phasing is generated in LO dividers. After the mixer DTOS

amplifiers convert the differential signals to single ended. DTOS has two

gain stages. The first one has constant gain of 12dB and 85kHz cut off

frequency. The gain of second stage is controlled with control signal g10.

If g10 is high (1) the gain is 6dB and if g10 is low (0) the gain of the stage

is –4dB.

PAMS Technical Documentation

The active channel filters in HAGAR provides selectivity for channels

(–3dB @ +/–91 kHz typ.). Integrated base band filter is active–RC–filter