Page 1

PAMS Technical Documentation

NHM-8NX Series Transceivers

System Module & UI

Issue 1 05/02 ãNokia Corporation

Page 2

NHM-8NX

System Module & UI PAMS Technical Documentation

Table of Contents

Abbreviations ................................................................................................................. 4

Transceiver NHM-8NX - Baseband Module BF4A ...................................................... 5

Hardware characteristics in brief .................................................................................5

Technical Summary .....................................................................................................6

Technical Specifications ..............................................................................................7

Operating conditions ................................................................................................. 7

DC Characteristics.................................................................................................... 8

Internal Signals and Connections.............................................................................. 9

Current consumption during sleep .......................................................................... 15

External Signals and Connections........................................................................... 16

Functional Description ...............................................................................................18

Modes of Operation................................................................................................. 18

Charging ................................................................................................................. 21

Charging Circuitry Electrical Characteristics ......................................................... 23

Power Up and Reset ................................................................................................ 24

A/D Channels .......................................................................................................... 26

LCD & Keyboard Backlight ................................................................................... 28

LCD cell .................................................................................................................. 29

SIM Interface........................................................................................................... 31

Internal Audio ......................................................................................................... 32

Accessories.............................................................................................................. 35

Keyboard ................................................................................................................. 40

RF Interface Block .................................................................................................. 41

Memory Module...................................................................................................... 42

Flash Programming ................................................................................................. 54

EMC Strategy ............................................................................................................57

PWB strategy........................................................................................................... 57

LCD metal frame..................................................................................................... 59

Bottom connector .................................................................................................... 59

Mechanical shielding............................................................................................... 60

Security ......................................................................................................................60

Test Interfaces ............................................................................................................60

Production / After Sales Interface ........................................................................... 60

FLASH Interface ..................................................................................................... 61

FBUS Interface........................................................................................................ 61

MBUS Interface ...................................................................................................... 61

JTAG & Ostrich Interface ....................................................................................... 62

DAI.......................................................................................................................... 62

Test modes (SW dependant) ................................................................................... 62

Test points ............................................................................................................... 63

List of unused UEM pins ..........................................................................................64

List of unused UPP pins ............................................................................................65

Transceiver NHM-8NX - RF Module.......................................................................... 67

Main Technical specifications ...................................................................................68

Temperature conditions........................................................................................... 68

Nominal and maximum ratings ............................................................................... 68

Page 2 ãNokia Corporation Issue 1 05/02

Page 3

NHM-8NX

PAMS Technical Documentation System Module & UI

RF frequency plan ................................................................................................... 68

DC characteristics ................................................................................................... 68

Functional descriptions ..............................................................................................71

RF block diagram .................................................................................................... 71

Frequency synthesizers ........................................................................................... 71

Receiver................................................................................................................... 73

Transmitter .............................................................................................................. 75

Synthesizer and RF Control .................................................................................... 76

RF characteristics .......................................................................................................77

Channel numbers and frequencies........................................................................... 77

Main RF characteristics........................................................................................... 77

Transmitter characteristics ...................................................................................... 77

Receiver characteristics........................................................................................... 81

List of Figures

Page No

Fig 1 NHM-8NX baseband block diagram..........................................................................6

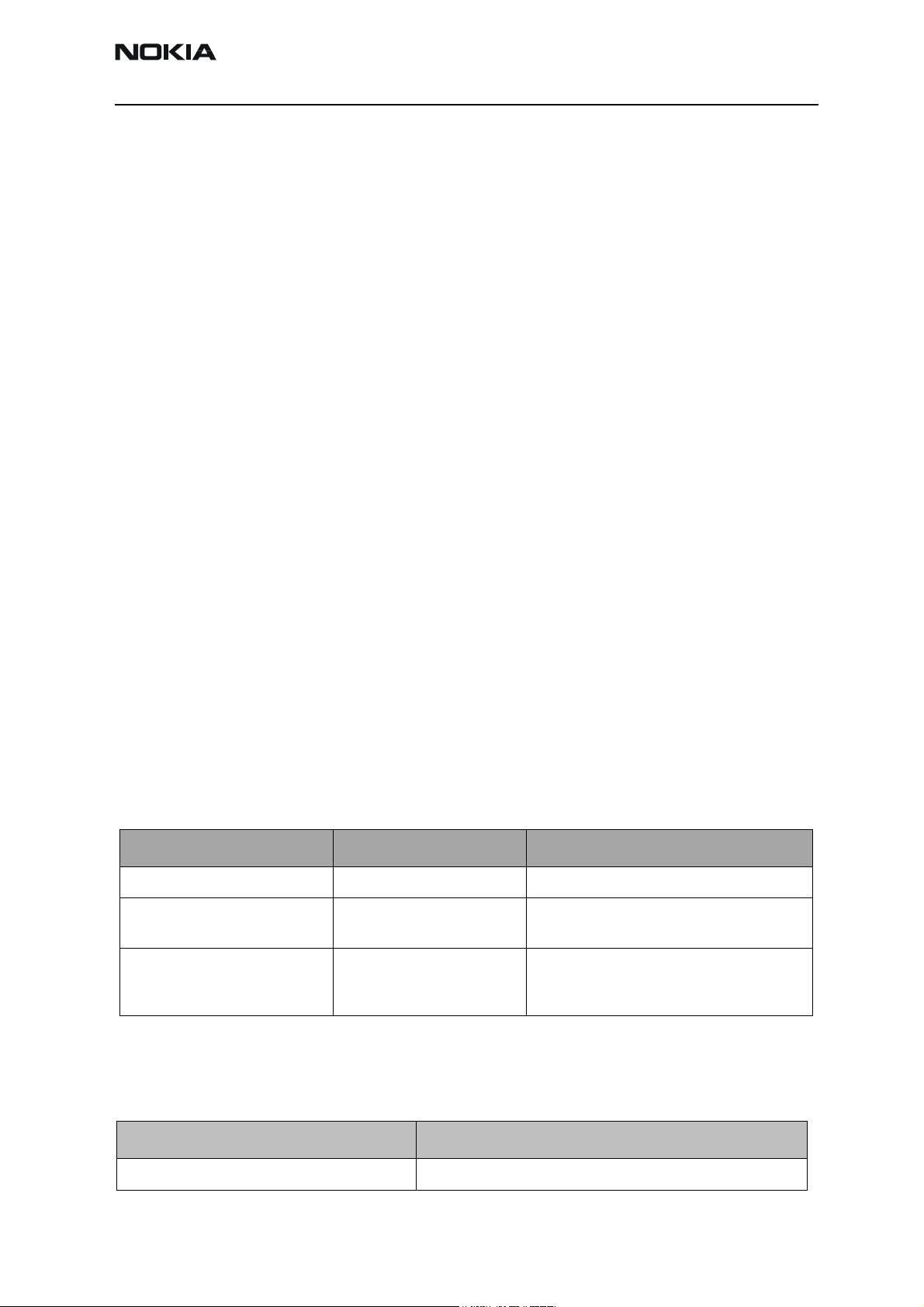

Fig 2 UEM charging circuitry..............................................................................................21

Fig 3 Shared LED driver circuit for LCD and Keyboard backlight ....................................29

Fig 4 Complete overview of LCD module ..........................................................................29

Fig 5 BW4 LCD module......................................................................................................30

Fig 6 BSI Detection .............................................................................................................31

Fig 7 UEM & UPP SIM connections...................................................................................32

Fig 8 Speaker Interface ........................................................................................................33

Fig 9 Internal microphone electrical interface .....................................................................34

Fig 10 Interface between the MIDI-circuit and the UEM....................................................35

Fig 11 Mechanical layout and interconnections of DCT-4 battery......................................36

Fig 12 Headset interface ......................................................................................................37

Fig 13 DC-OUT Interface....................................................................................................39

Fig 14 Keyboard layout .......................................................................................................40

Fig 15 Intel-AMD signal deviations description .................................................................45

Fig 16 An XOR comparison of the data indicates more equal bits .....................................46

Fig 17 An XOR comparison indicates more unequal bits ...................................................46

Fig 18 Intel Asynchronous Read .........................................................................................50

Fig 19 Intel Synchronous Four-Word Burst Read ...............................................................51

Fig 20 Intel Write.................................................................................................................52

Fig 21 AMD Asynchronous Read .......................................................................................53

Fig 22 AMD Synchronous Burst Read ................................................................................53

Fig 23 Production/Test/After sales interface .......................................................................60

Fig 24 RF Frequency plan ...................................................................................................68

Fig 25 Power distribution diagram ......................................................................................70

Fig 26 Block Schematic.......................................................................................................71

Fig 27 Simplified Synthesizer..............................................................................................73

Fig 28 Simplified Mjoelner BB, either I or Q channel ........................................................73

Fig 29 Gain control ..............................................................................................................74

Fig 30 DC compensation principle ......................................................................................75

Fig 31 Power Loop ..............................................................................................................76

Issue 1 05/02 ãNokia Corporation Page 3

Page 4

NHM-8NX

System Module & UI PAMS Technical Documentation

Abbreviations

BSI Battery Size Indicator

CTI Cover Type Indicator

DCT4 Digital Core Technology, 4th Generation

DSP Digital Signal Processor

MCU MicroController Unit

NO_SUPPLY UEM state where UEM has no supply what so ever

PDM Pulse Density Modulation

PWR_OFF UEM state where phone is off

PWRONX Signal from power on key. '1' = key

RESET UEM state where regulators are enabled

RTC UEM internal Real Time Clock

SIM Subscriber Identity Module

SLEEP UEM power saving state controlled by UPP

SLEEPX SLEEP control signal from UPP

TBSF Through the Board Side Firing

UEM Universal Energy Management

UPP Universal Phone Processor

VBAT Main battery voltage

VBAT LIM2+ Charging cut–off limit (Max)

VCHAR Charger input voltage

VCHARDET Charger detection threshold level

VMSTR+, VMSTR Master Reset threshold level (2.1 V / 1.9 V)

Page 4 ãNokia Corporation Issue 1 05/02

Page 5

NHM-8NX

PAMS Technical Documentation System Module & UI

Transceiver NHM-8NX - Baseband Module BF4A

This section specifies the baseband module for the NHM-8NX transceiver. The transceiver

board is named BF4A, and all board references used refer to the board version BF4A_20.

The baseband module includes the baseband engine chipset, the UI components and the

acoustical parts for the transceiver.

NHM-8NX is a hand-portable dualband EGSM900/GSM1800 phone, with GPRS (Class-4)

for the Basic/Expression segment, having the DCT4 generation baseband (UEM/UPP) and

RF(MJOELNER) circuitry.

The baseband module is developed, as part of the DCT4 common Baseband. It is based

very much upon the NPE-4 and NHM-7 products, main difference being UI and the audio

circuits.

The mechanical construction is based on the NHM-5 phone.

New features in NHM-8NX are MIDI (polyphonic ringing tones) and DC-out (electrical

interface to A-cover).

NHM-8NX supports both three and two wire type DCT3 chargers. Three wire chargers are

treated like two wire ones. There is no separate PWM output for controlling charger but

it is connected to GND inside the bottom connector.

BLC-2 Li-ion battery is used as main power source for NHM-8. BLC-2 has nominal

capacity of 900 mAh.

Hardware characteristics in brief

• Hi-Res (96x65) illuminated B&W display (BW4)

• Active LCD area: width 30,609mm, height 24.10 mm (pixel size

0.304mm*0.356mm, pixel gap 0,015)

• ESD-proof keymat, with 5 individual keys for multiple key pressing

• Support for internal semi-fixed batteries (Janette type)

• No RTC battery

• Plug-in SIM, supporting 1.8 & 3.0V

• Audio amplifier and SALT speaker for MIDI support

• Ringing volume 100dB @ 5cm (MIDI tones through SALT speaker)

• Internal vibra

• Supports voice dial activation via headset button

• DC-out feature for supporting electrical A-covers

• Only 4 (2+2) TBSF LEDs for keyboard & LCD backlight

• 6-layer PWB, only SMD components on one side

• Li-Ion is the only supported battery technology

Note: 5V SIM cards are no longer supported by DCT-4 generation baseband.

Issue 1 05/02 ãNokia Corporation Page 5

Page 6

NHM-8NX

System Module & UI PAMS Technical Documentation

Technical Summary

The baseband module contains 2 main ASICs named the UEM and UPP. The baseband

module furthermore contains an audio amplifier LM4890 for MIDI support and a 64Mbit

Flash IC. The baseband is based on the DCT4 engine program.

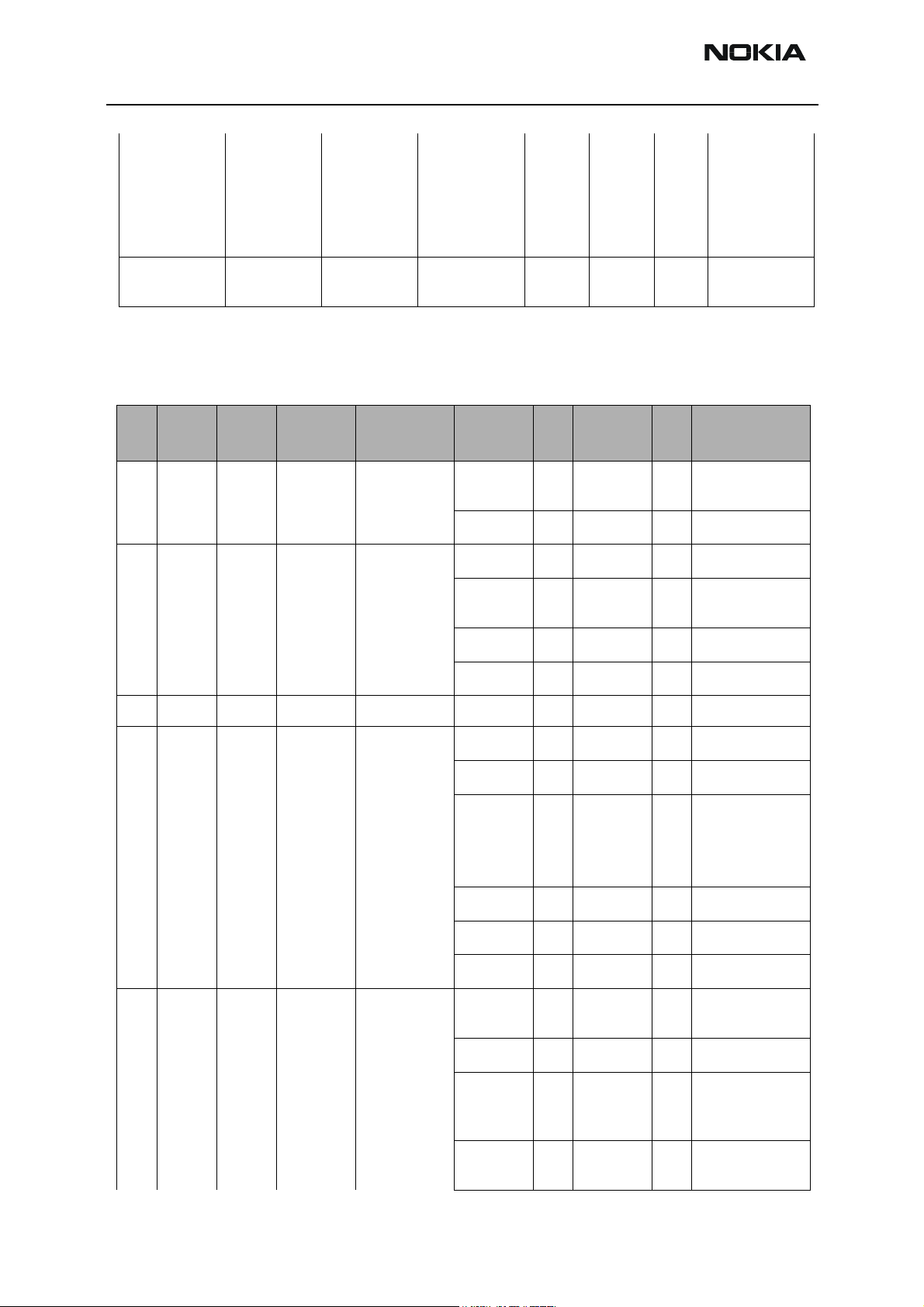

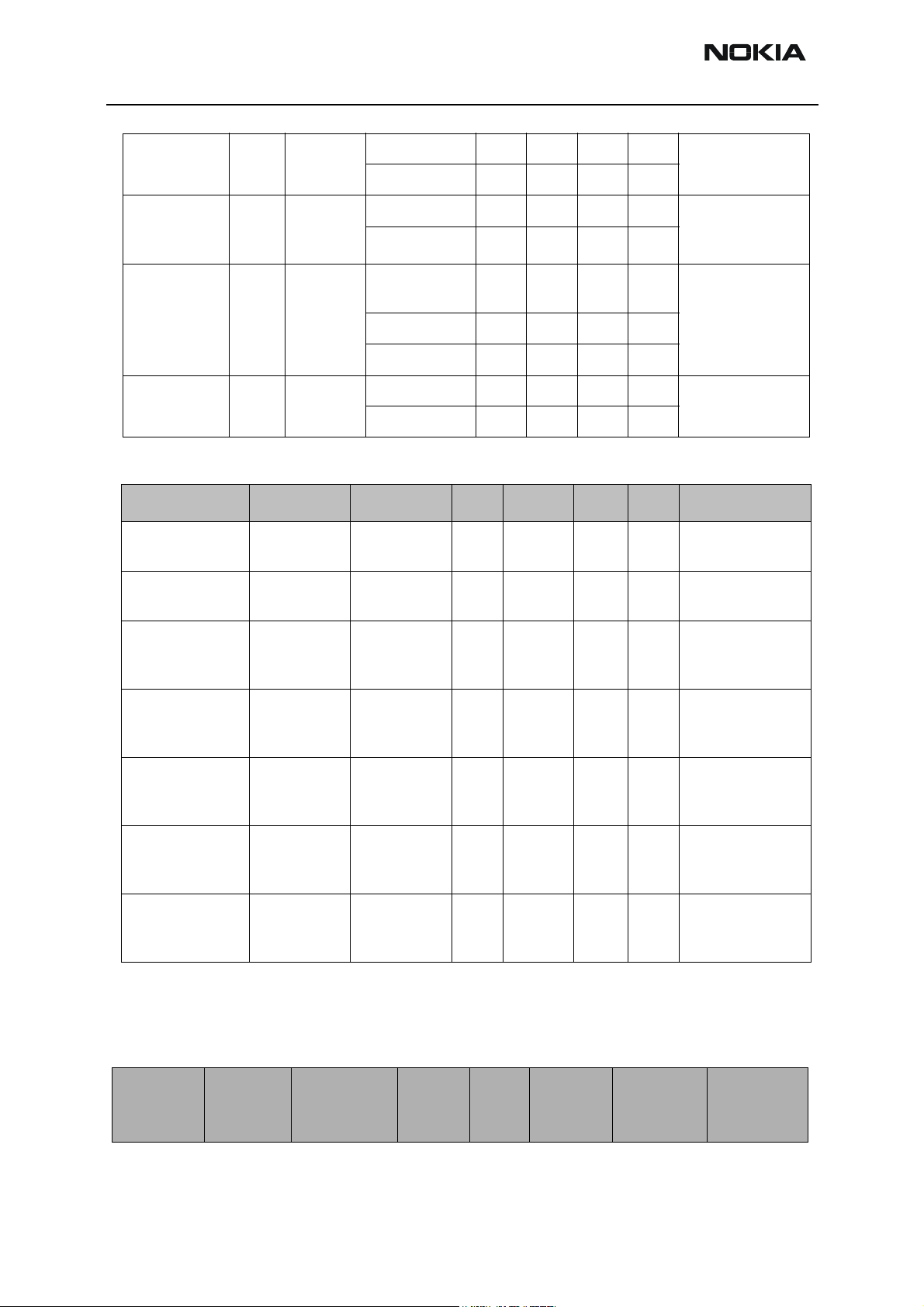

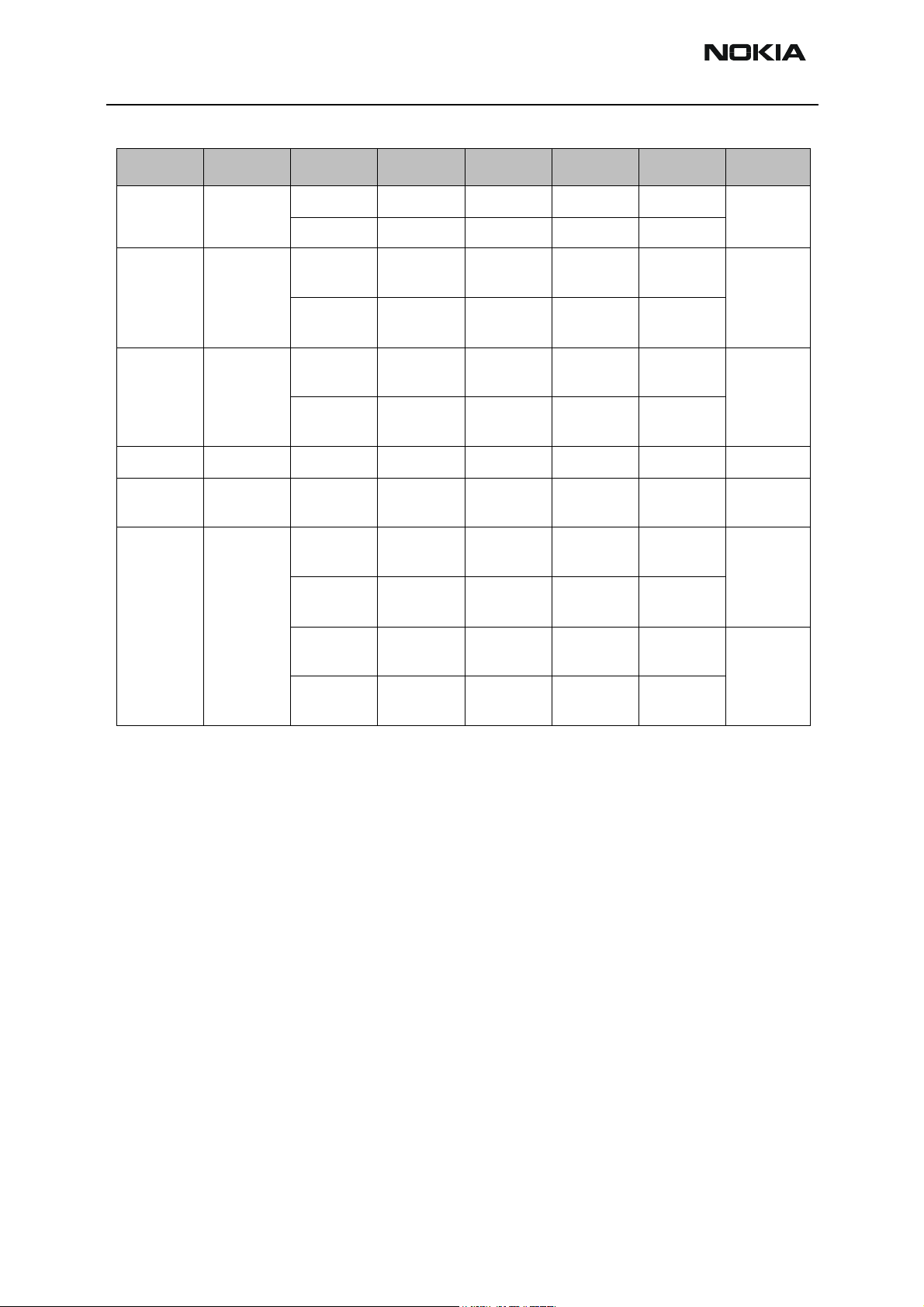

Figure 1: NHM-8NX baseband block diagram

RFBUS

Battery

UI

Mjoelner

PA S upply

RF Supplies

RF RX/TX

SIM

EAR

MIC

LM4890

VIBRA

M

UEM

HF

DCT4 Janette connector

External Audio

Charger connection

Baseband

DLIGHT

SLEEPCLK

32kHz

CBUS/

DBUS

BB

Supplies

MBus/FBus

26MHz

UPP

MEMADDA

FLASH

The UEM supplies both the baseband module as well as the RF module with a series of

voltage regulators. Both the RF and Baseband modules are supplied with regulated voltages of 2.78 V and 1.8V. UEM includes 6 linear LDO (low drop-out) regulators for baseband and 7 regulators for RF. BB regulator VFLASH1, RF regulators VR1B, VR4 as well as

the current sources IPA1 and IPA2 must be kept disabled by SW, as they are left unconnected on the PWB. The UEM is furthermore supplying the baseband SIM interface with a

programmable voltage of either 1.8 V or 3.0 V. The core of the UPP is supplied with a

programmable voltage of 1.0 V, 1.3 V, 1.5 V or 1.8 V.

UPP operates from a 26MHz clock, coming from the RF ASIC MJOELNER (see chapter 7.11

for details), the 26 MHz clock is internally divided by two, to the nominal system clock of

13MHz. DSP and MCU contain phase locked loop (PLL) clock multipliers, which can multiply the system frequency by factors from 0.25 to 31. Practical speed limitations is

depending on memory configuration and process size (Max. DSP speed for C035 process

is ~ 200MHz)

The UEM contains a real-time clock, sliced down from the 32768 Hz crystal oscillator.

Page 6 ãNokia Corporation Issue 1 05/02

Page 7

NHM-8NX

PAMS Technical Documentation System Module & UI

The 32768 Hz clock is fed to the UPP as a sleep clock.

The communication between the UEM and the UPP is done via the bi-directional serial

buses CBUS and DBUS. The CBUS is controlled by the MCU and operates at a speed of 1

MHz. The DBUS is controlled by the DSP and operates at a speed of 13 MHz. Both processors are located in the UPP.

The interface between the baseband and the RF section is mainly handled by the UEM

ASIC. UEM provides A/D and D/A conversion of the in-phase and quadrature receive and

transmit signal paths and also A/D and D/A conversions of received and transmitted

audio signals to and from the user interface. The UEM supplies the analog signals to RF

section according to the UPP DSP digital control. RF ASIC MJOELNER is controlled

through UPP RFBUS serial interface. There are also separate signals for PDM coded audio.

Digital speech processing is handled by the DSP inside UPP ASIC. UEM is a dual voltage

circuit, the digital parts are running from the baseband supply 1.8V and the analog parts

are running from the analog supply 2.78V also VBAT is directly used by some blocks.

The baseband supports both internal and external microphone inputs and speaker outputs. Input and output signal source selection and gain control is done by the UEM

according to control messages from the UPP. Keypad tones, DTMF, and other audio tones

are generated and encoded by the UPP and transmitted to the UEM for decoding. NHM8NX has two external serial control interfaces: FBUS and MBUS. These busses can be

accessed only through production test pattern as described in section Test Interfaces.

NHM-8NX transceiver module is implemented on 6 layer selective OSP/Gold coated PWB.

Technical Specifications

Operating conditions

Temperature Conditions

Table 1: Temperature conditions for NHM-8

Environmental condition Ambient temperature Remarks

Normal operation -25 ° C … +55 °C Specifications fulfilled

Reduced performance -40 °C ..-25 °C

and +55 °C … +85 °C

No operation and/or storage < -40 °C or > +85 °C No storage or operation. An attempt to

operate may damage the phone permanently

Absolute Maximum Ratings

Table 2: Absolute Maximum Ratings

Signal Rating

Battery Voltage -0.3 ... 5.4V (VBAT LIM2H+))

Issue 1 05/02 ãNokia Corporation Page 7

Page 8

NHM-8NX

System Module & UI PAMS Technical Documentation

Charger Input Voltage -0.3 ... 20V

DC Characteristics

Regulators and Supply Voltage Ranges

Table 3: Battery voltage range

Signal Min Nom Max Note

VBAT 3.1V 3.6V 4.235V 3.1V SW cut off

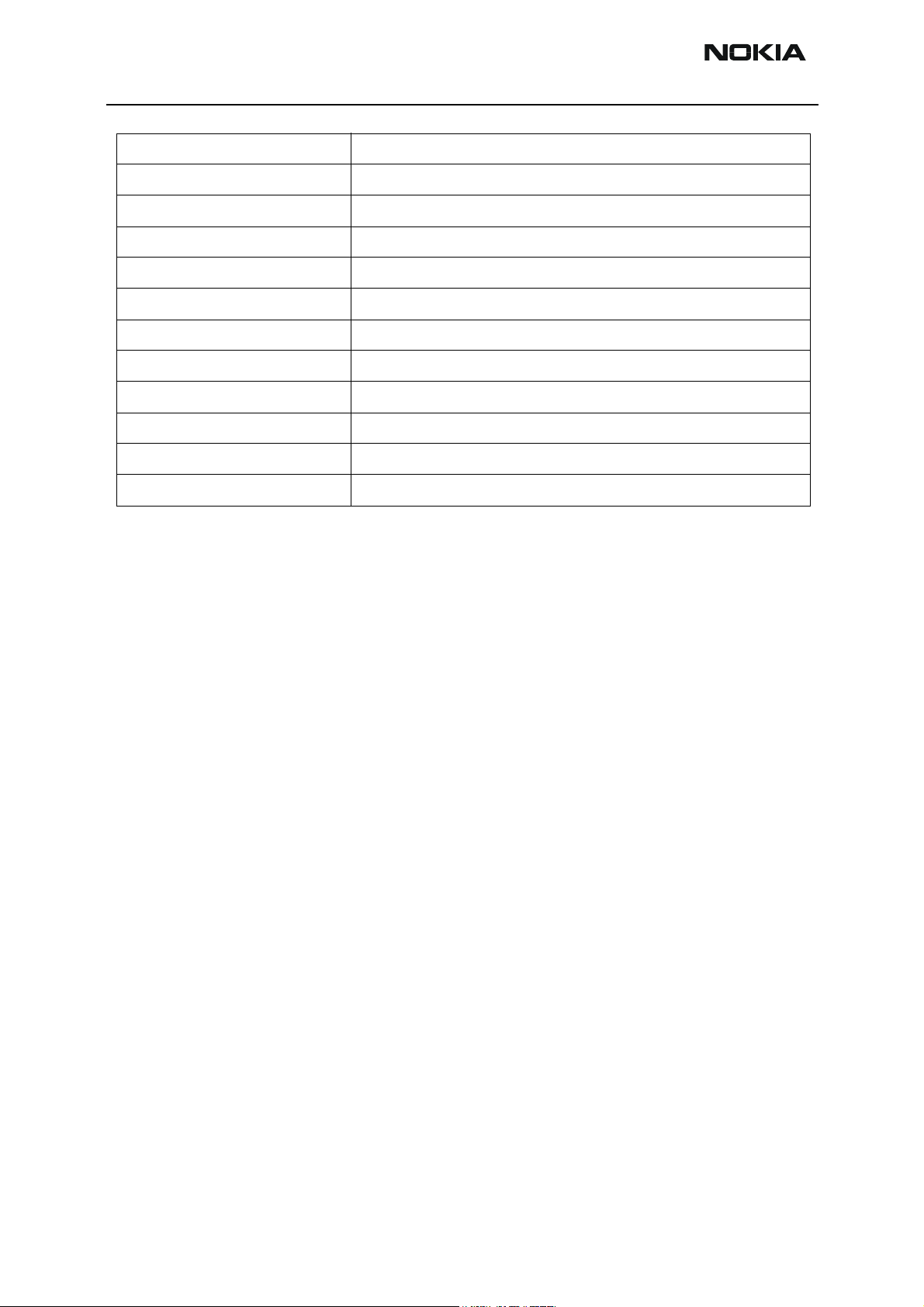

Table 4: BB regulators

Signal Min Nom Max Note

VANA 2.70V 2.78V 2.86V I

VFLASH1 2.70V 2.78V 2.86V I

max

max

I

Sleep

= 80mA

= 70mA

= 1.5mA

VFLASH2 2.70V 2.78V 2.86V Not used

VSIM 1.745V

2.91V

VIO 1.72V 1.8V 1.88V I

VCORE 1.0V

1.235V

1.425V

1.710V

1.8V

3.0V

1.053V

1.3V

1.5V

1.8V

1.855V

3.09V

1.106V

1.365V

1.575V

1.890V

I

= 25mA

max

= 0.5mA

I

Sleep

= 150mA

max

I

= 0.5mA

Sleep

I

= 200mA

max

= 0.2mA

I

Sleep

Used voltages:

(c05) = 1.8V

(c035) = 1.5V

Table 5: RF regulators

Signal Min Nom Max Note

VR1A 4.6V 4.75V 4.9V Imax = 10mA

VR1B 4.6V 4.75V 4.9V Not used

VR2 2.70V

3.20V

VR3 2.70V 2.78V 2.86V I

2.78V

3.3V

2.86V

3.40V

I

max

max

= 100mA

= 20mA

VR4 2.70V 2.78V 2.86V Not used

VR5 2.70V 2.78V 2.86V I

VR6 2.70V 2.78V 2.86V I

max

I

Sleep

max

I

Sleep

= 50mA

= 0.1mA

= 50mA

= 0.1mA

Page 8 ãNokia Corporation Issue 1 05/02

Page 9

NHM-8NX

PAMS Technical Documentation System Module & UI

VR7 2.70V 2.78V 2.86V I

Table 6: Current sources

Signal Min Nom Max Note

IPA1 and IPA2 0mA - 5mA Not used

max

Internal Signals and Connections

The tables below describe internal signals. The signal names can be found on the schematic for the bf4a PWB.

Audio

Table 7: Internal microphone

Signal Min Nom Max Condition Note

MIC1P (Differential input P) - - 100mV

MIC1N (Differential input N) - - 100mV

G=20dB 1kΩ to MIC1B

pp

G=20dB 1kΩ to GND

pp

(RC filtered by 220R/4.7uF)

= 45mA

MICB1 (Microphone Bias) 2.0 V 2.1 V 2.25 V DC

External loading of MICB1 - - 600uA DC

Table 8: Internal speaker (Differential output EARP & EARN)

Signal Min

Output voltage swing 4.0 - - Vpp Differential output

Load Resistance (EARP to EARN) 26 32 - W

Load Capacitance (EARP to EARN) - - 50 nF

No

Max Units Note

m

MIDI

Table 9: Connections between UPP and LM4890

Signal From To Parameter Min. Max. Unit Notes

Shutdown GENIO[14] Shutdown

(p. 5)

Vih

Vil

1.2

-

-

0.4

V

V

LM4890 detections treshold

levels

Table 10: Connections between UEM/Battery and LM4890

Signal name From To Parameter Min. Max. Unit Notes

Issue 1 05/02 ãNokia Corporation Page 9

Page 10

NHM-8NX

System Module & UI PAMS Technical Documentation

XAUDIO[1]

Filtered signal

UEM, HF No

direct con-

LM4890 Output Swing 1.0 - Vpp with 60 dB

nection

between

UEM and

LM4890

VBAT Battery LM4890

Supply 3.1 4.2 V Lower limit is

(p. 6)

LCD

Table 11: LCD connector interface

Pin Signal

NMP

net

Symbol Parameter Min.

1 /RES XRES Reset - - 0.3 x V

t

rw

1000 - - ns For valid reset

2 /SCE XCS Chip Select 0.7 x V

- - 0.3 x V

Ty

Max.

p.

- - V Logic High

DDI

Un

it

V Logic Low,

DDI

V Logic Low,

DDI

signal to total

distortion

ratio

SW cut-off

Notes

active

active

t

S2

t

H2

60 - - ns Setup time

100 - - ns Hold time

3 VSS VSS GND Ground - 0 - V

4 SDATA SDA Input 0.7 x V

- - 0.3 x V

Output @

I

= 0.5mA,

OL

I

= -

OH

0.7 x V

- - V Logic High

DDI

DDI

- - V Logic High

DDI

0.5mA

t

s1

t

H1

5 SCLK SCLK Serial clock

- - 0.3 x V

100 - - ns Data setup time

100 - - ns Data hold time

0.7 x V

- - V Logic High

DDI

DDI

input

- - 0.3 x V

t

cyc

153,8 - - ns Serial clock

DDI

V Logic Low

V Logic Low

V Logic Low

cycle (max. 4

MHz)

t

PWH1

50 - - ns Serial clock high

pulse width

Page 10 ãNokia Corporation Issue 1 05/02

Page 11

NHM-8NX

PAMS Technical Documentation System Module & UI

6 VDD

7 VDD

8 VLCD-

1

2in

out

t

PWL1

VDDI VDD digital

power supply

VDD Booster

power supply

VOUT Booster out-

put

50 - - ns Serial clock low

pulse width

1.72 1.8 1.88 V

2.6 2.782.86 V VFLASH1

- - 12 V Decoupled to

GND on PCB

with 1uF

Baseband – RF interface

Table 12: BB – RF interface description

Signal name From To Parameter Min. Typ. Max. Unit Notes

RFICCNTRL (2:0) MJOELNER control bus

RFBUSEN1X UPP MJOEL-

NER

RFBUSDA UPP MJOEL-

NER

Logic "1" 1.38 - 1.80 V RF Chip select

Logic "0" 0 - 0.4 V

Logic "1" 1.38 - 1.80 V RF serial control

Logic "0" 0 - 0.4 V

bus (bi-directional)

RFBUSCLK UPP MJOEL-

NER

Clock System clock for phone

RFCLK MJOE

LNER

RFCONV (9:0) RF / BB analogue signals

RXIINP MJOE

LNER

UPP Frequency - 26 - MHz System clock

UEM Voltage swing 1.35 1.4 1.45 V Positive in-phase

Logic "1" 1.38 - 1.80 V RF bus clock

Logic "0" 0 - 0.4 V

Signal amplitude

Duty cycle

(Mjoelner

spec.)

DC level 1.3 1.35 1.4 V

I/Q amplitude

mismatch

I/Q phase mismatch

Data clock rate - - 13 MHz

0.3 1 1.376Vpp

40 - 60 %

- - 0.2 dB

-5 - 5 Deg.

UPP minimum

recommended

amplitude is

0.3Vpp.

Waveform: Sinus/

triangle

Rx signal

Issue 1 05/02 ãNokia Corporation Page 11

Page 12

NHM-8NX

System Module & UI PAMS Technical Documentation

RXIINN MJOE

LNER

RXQINP MJOE

LNER

RXQINN MJOE

LNER

UEM Voltage swing 1.35 1.4 1.45 V Negative in-phase

DC level 1.3 1.35 1.4 V

I/Q amplitude

mismatch

I/Q phase mismatch

Data clock rate - - 13 MHz

UEM Voltage swing 1.35 1.4 1.45 V Positive quadra-

DC level 1.3 1.35 1.4 V

I/Q amplitude

mismatch

I/Q phase mismatch

Data clock rate - - 13 MHz

UEM Voltage swing 1.35 1.4 1.45 V Negative quadra-

DC level 1.3 1.35 1.4 V

I/Q amplitude

mismatch

- - 0.2 DB

-5 - 5 Deg.

- - 0.2 dB

-5 - 5 Deg.

- - 0.2 dB

Rx signal

ture phase

nal

ture phase RX signal

RX sig-

TXIOUTP UEM MJOEL-

NER

TXIOUTN UEM MJOEL-

NER

I/Q phase mismatch

Data clock rate - - 13 MHz

Diff. Voltage

swing

DC level 1.10 1.20 1.25 V

Source impedance

Data clock rate - - 13 MHz

Differential

voltage swing

DC level 1.17 1.20 1.23 V

Source impedance

Data clock rate - - 13 MHz

-5 - 5 Deg.

2.15 2.2 2.25 Vpp Positive TX signal

- - 200 W

2.15 2.2 2.25 Vpp Negative TX sig-

- - 200 W

(program-able

voltage swing)

nal (program-able

voltage swing)

Page 12 ãNokia Corporation Issue 1 05/02

Page 13

NHM-8NX

PAMS Technical Documentation System Module & UI

TXQOUTP UEM MJOEL-

NER

TXQOUTN UEM MJOEL-

NER

GENIO (28:0) General purpose I/O

GENIO5

(TXP)

GENIO6

(RESETX_MJO

EL)

UPP MJOEL-

NER

UPP MJOEL-

NER

Differential

voltage swing

DC level 1.17 1.20 1.23 V

Source impedance

Data clock rate - - 13 MHz

Differential

voltage swing

DC level 1.17 1.20 1.23 V

Source impedance

Data clock rate - - 13 MHz

Logic "1" 1.38 - 1.80 V Transmitter power

Logic "0" 0 - 0.4 V

Logic "1" 1.38 - 1.80 V Reset to RF chip

Logic "0" 0 - 0.4 V

2.15 2.2 2.25 Vpp Positive TX signal

(program-able

voltage swing)

- - 200 W

2.15 2.2 2.25 Vpp Negative TX signal (program-able

voltage swing)

- - 200 W

control enable

RFAUXCONV(2:0) RF / BB analogue control signals

AUXOUT UEM MJOEL-

NER

Regulators RF regulators (currents are max. according to UEM spec.)

VBAT

(VBATREGS)

VR1A UEM Mjoelner Output voltage 4.6 4.75 4.9 V

VR2 UEM MJOEL-

VR3 UEM MJOEL-

Battery

PA / UEM Output voltage 2.9 3.6 4.2 V Battery cut-off is

NER

NER

Output voltage 0.12 - 2.50 V Transmitter power

Source impedance

Resolution - 10 - Bits

Current 0 - 10 mA

Output voltage 2.64 2.78 2.86 V Supply to:

Current 0.1 - 100 mA

Output voltage 2.64 2.78 2.86 V Supply to:

Current 0.1 - 20 mA

- - 200 W

control

set by UEM to 2.9

V

TX – chain, Power

Loop Control and

Digital logic

Ref. Osc.

VR5 UEM MJOEL-

NER

Output voltage 2.64 2.78 2.86 V Supply to:

Current 0.1 - 50 mA

PLL, Divider, LO

buffers

Issue 1 05/02 ãNokia Corporation Page 13

Page 14

NHM-8NX

System Module & UI PAMS Technical Documentation

VR6 UEM MJOEL-

NER

VR7 UEM VCO Output voltage 2.64 2.78 2.86 V Supply to:

VREFRF01 UEM MJOEL-

NER

VIO UEM MJOEL-

NER

Signal name From To Min. Typ. Max. Unit Notes

RFCLK MJOELNER UPP - 26 - MHz Active when

SLEEPCLK UEM UPP - 32.768 - kHz Active when VBAT

Output voltage 2.64 2.78 2.86 V Supply to:

Current 0.1 - 50 mA

Current 0.1 - 45 mA

Output voltage 1.3341.35 1.366V Used in MJOEL-

Current - - 100 µA

Current - - 100 µA

Output voltage 1.71 1.8 1.88 V Supply to:

Current 0.1 - 150 mA

Table 13: Board Clocks

LNA's, Pregain

LO buffers, Local

oscillators

NER (VBEXT) as

1.35V reference

BB buffer

SLEEPX is high

is supplied

RFCONVCLK UPP UEM 13 - MHz Active when RF

converters are

active

RFBUSCLK UPP MJOELNER - 13 13 MHz Only active when

bus-enable is

active

DBUSCLK UPP (DSP) UEM - 13 13 MHz Only active when

bus-enable is

active

CBUSCLK UPP (MCU) UEM - 1 1 MHz Only active when

bus-enable is

active

LCDCAMCLK UPP

(Write)

(Read)

LCD 0.3

3.25

0.650

4 MHz Only active when

bus-enable is

active

Connection for regulators active during sleep

Table 14: Connections for regulators active during sleep

Regulators UEM UPP FLASH LCD

X387

(SIM

con.)

MJOELNER

Externally

circuit

Page 14 ãNokia Corporation Issue 1 05/02

Page 15

NHM-8NX

PAMS Technical Documentation System Module & UI

VIO

[1,8V]

VCORE

[1,8V]

VFLASH1

[2,78V]

VSIM

[1,8V / 3V]

VR2

[2,78V]

VDD18 VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDA

VDDSP1

VDDSP2

VDDSP3

VDDMCU

VDDCORE1

VDDCORE2

VDDPDRAM1

VDDPDRAM2

VDD28

BSI(pull

up)

PATEMP

(pull up)

VDD VDDI VDDDL

SELADDR

VDD

VSIM

VDDDIG

VDDTX

TX section of

MJOELNER

sheet

Current consumption during sleep

Following section state the different regulators current consumption (theoretically

excluding leakage in decoupling capacitors) in sleep mode.

VIO

1,8V PINS Current consumption in sleep (SLEEPX = low)

UEM VDD18 < 5 µA

UPP VDDIO1-4 < 400uA

(depends on I/O config)

VDDA < 5uA

FLASH VDD 20 µA

LCD VDDI 40 µA

MJOELNER VDDDL 5 µA

SELADDR 0uA

Totally Specification: Max: 500uA <475

Issue 1 05/02 ãNokia Corporation Page 15

Page 16

NHM-8NX

System Module & UI PAMS Technical Documentation

VCORE

1,8V PINS Current consumption in sleep (SLEEPX = low)

UPP VDDSP1-3, VDDMCU,

VDDCORE1-2

VDDPDRAM1-2

To tal ly Specification: Max: 200uA Measured value < 120uA

< 9 µA

(Measured value < 120uA)

VFLASH1

2,78V PINS Current consumption in sleep (SLEEPX = low)

UEM VDD28 < 5 µA

BSI (pull up) < 30 µA

PATEMP (pull up) < 25 µA

LCD VDD <1100 µA

Totally Specification: Max: 1500uA <1160 µA

VSIM

1,8V / 3V PINS Current consumption in sleep (SLEEPX = low)

X387 (SIM con) VSIM < 200 µA

Totally Specification: Max: 500uA < 200 µA

VR2

2,78V PINS Current consumption in sleep (SLEEPX = low)

MJOELNER VDDDIG 70 µA

VDDTX 0 µA

Totally Specification: Max: 100uA 70uA

External Signals and Connections

System connector (X102)

Table 15: DC connector

Pin Signal Min Nom Max Condition Note

2 VCHAR - 11 .1 V

7.0

V

RMS

8.4 V

peak

RMS

16.9 V

7.9 V

1.0 A

9.2 V

850 mA

peak

RMS

peak

RMS

Standard

charger

(ACP-7)

Fast

charger

Charger positive

input

Page 16 ãNokia Corporation Issue 1 05/02

Page 17

NHM-8NX

PAMS Technical Documentation System Module & UI

1 CHGND - 0 - Charger ground

Table 16: External microphone

Signal Min Nom Max Condition Note

MIC2P (Differential input P) - - 100mV

MIC2N (Differential input N) - - 100mV

MICB2 (Microphone Bias) 2.0 V 2.1 V 2.25 V DC Unloaded

External loading of MICB2 - - 600uA DC

Table 17: External speaker, differential output XEARP(HF) & XEARN (HFCM)

Signal Min

Output voltage swing*

* seen from transducer side

Common voltage level for

HF output (HF & HFCM) VCMHF

Load Resistance (HF to HFCM) 30 - - W

Load Capacitance (HF to HFCM) - - 10 nF

2.0 - - Vpp Differential output, with 60 dB

0.75 0.8 0.85 V

Table 18: Headset detection

No

Max Units Note

m

G=20dB 1kΩ to MIC1B

pp

G=20dB 1kΩ to GND

pp

signal to total distortion ratio

Signal Min Nom Max Condition Note

HookInt 0V - 2.86V (VANA) Headset button call control, connected

to UEM AD-converter

HeadInt 0V - 2.86V (VANA) Accessory detection, connected to

UEM AD-converter

DC-OUT (J307,J308 & J309)

Table 19: DC-OUT Connections

Pad Name Parameter Min Typ Max Unit Notes

J307 Power Voltage (open) - - Vbat V Output power line

Current (short) 56 64 72 mA

J308 CTI(Input) Resistor value 30.9 - 750 kΩ Cover detection

J309 GND - - - - - Ground

SIM (X387)

Issue 1 05/02 ãNokia Corporation Page 17

Page 18

NHM-8NX

System Module & UI PAMS Technical Documentation

Table 20: SIM Connector

Pin Name Parameter Min Typ Max Unit Notes

1 CLK Frequency - 3.25 - MHz SIM clock

Trise/Tfall - - 50 ns

2 RST 1.8V SIM

Card

3V SIM

Card

3 VCC 1.8V SIM

Card

3V SIM

Card

4 GND GND - 0 - V Ground

5 VCC - - - Not con-

6 I/O 1.8V Voh

1.8V Vol

3 Voh

3 Vol

1.8V Vih

1.8V Vil

3V Vil

3V Vil

1.62

0

2.7

0

1.6 1.8 2.0 V Supply

2.8 3.0 3.2 V

1.62

0

2.7

0

1.26

0

2.1

0

”1”

”0”

”1”

”0”

”1”

”0”

”1”

”0”

”1”

”0”

”1”

”0”

VSIM

0.27

VSIM

0.45

VSIM

0.27

VSIM

0.45

VSIM

0.27

VSIM

0.45

V SIM reset

(output)

V

voltage

nected

V SIM data

(output)

V

V SIM data

(input)

V

Trise/Tfall

max 1us

Functional Description

Modes of Operation

NHM-8NX baseband engine has six different operating modes (in normal mode):

• No supply

•Power_off

•Acting Dead

•Active

•Sleep

• Charging

Additionally two modes exist for product verification: 'testmode' and 'local mode'.

No supply

In NO_SUPPLY mode, the phone has no supply voltage. This mode is due to disconnection

of main battery or low battery voltage level.

Page 18 ãNokia Corporation Issue 1 05/02

Page 19

NHM-8NX

PAMS Technical Documentation System Module & UI

Phone is exiting from NO_SUPPLY mode when sufficient battery voltage level is detected.

Battery voltage can rise either by connecting a new battery with VBAT > V

connecting charger and charging the battery above V

Power_off

MSTR+

.

MSTR+

or by

In this state the phone is powered off, but supplied. VRTC regulator is active (enabled)

having supply voltage from main battery. Note, the RTC status in PWR_OFF mode

depends on whether RTC was enabled or not when entering PWR_OFF. From Power_off

mode UEM enters RESET mode (after 20ms delay), if any of following statements is true

(logical OR –function):

• Power_on button detected (PWROFFX)

• Charger connection detected (VCHARDET)

• RTC_ALARM detected

The Phone enters POWER_OFF mode from all the other modes except NO_SUPPLY if

internal watchdog elapses.

Acting Dead

If the phone is off when the charger is connected, the phone is powered on but enters a

state called ”Acting Dead”, in this mode no RF parts are powered. To the user, the phone

acts as if it was switched off. A battery charging alert is given and/or a battery charging

indication on the display is shown to acknowledge the user that the battery is being

charged.

Active

In the active mode the phone is in normal operation, scanning for channels, listening to

a base station, transmitting and processing information. There are several sub-states in

the active mode depending on if the phone is in burst reception, burst transmission, if

DSP is working etc.

In active mode the RF regulators are controlled by SW writing into UEM’s registers

wanted settings: VR1A/B must be kept disabled. VR2 can be enabled or forced into low

quiescent current mode. VR3 is always enabled in active mode. VR4 -VR7 can be enabled,

disabled or forced into low quiescent current mode.

Table 21: Regulator controls

Regulator NOTE

VFLASH1 Enabled; Low Iq mode during sleep

VFLASH2 Not used in NHM-8, must be kept disabled

VANA Enabled; Disabled in sleep mode

Issue 1 05/02 ãNokia Corporation Page 19

Page 20

NHM-8NX

System Module & UI PAMS Technical Documentation

VIO Enabled; Low Iq mode during sleep

VCORE Enabled; Low Iq mode during sleep

VSIM Controlled by register writing.

VR1A Enabled; Disabled in sleep mode

VR1B Not used in NHM-8, must be kept disabled

VR2 Controlled by register writing; Enabled in sleep mode

VR3 Enabled; Disabled in sleep mode

VR4 Not used in NHM-8, must be kept disabled

VR5 Enabled; Disabled in sleep mode

VR6 Enabled; Disabled in sleep mode

VR7 Enabled; Disabled in sleep mode

IPA1-2 Not used in NHM-8, must be kept disabled

Sleep mode

Sleep mode is entered when both MCU and DSP are in stand-by mode. Sleep is controlled

by both processors. When SLEEPX low signal is detected UEM enters SLEEP mode. VCORE,

VIO and VFLASH1 regulators are put into low quiescent current mode. All RF regulators,

except VR2, are disabled in SLEEP. When SLEEPX=1 is detected UEM enters ACTIVE mode

and all functions are activated.

The sleep mode is exited either by the expiration of a sleep clock counter in the UEM or

by some external interrupt, generated by a charger connection, key press, headset connection etc.

In sleep mode the main oscillator (26MHz) is shut down and the 32 kHz sleep clock oscillator is used as reference clock for the baseband.

Charging

Charging can be performed in parallel with any other operating mode. A BSI resistor

inside the battery pack indicates the battery type/size. The resistor value corresponds to

a specific battery capacity and technology.

The battery voltage, temperature, size and current are measured by the UEM controlled

by the charging software running in the UPP.

The charging control circuitry (CHACON) inside the UEM controls the charging current

delivered from the charger to the battery. The battery voltage rise is limited by turning

the UEM switch off when the battery voltage has reached VBATLim (programmable

charging cut-off limits 3.6V / 5.0V / 5.25V). Charging current is monitored by measuring

the voltage drop across a 220 mOhm resistor. Detailed description of the charging func-

Page 20 ãNokia Corporation Issue 1 05/02

Page 21

NHM-8NX

V

PAMS Technical Documentation System Module & UI

tionality can be found in next section.

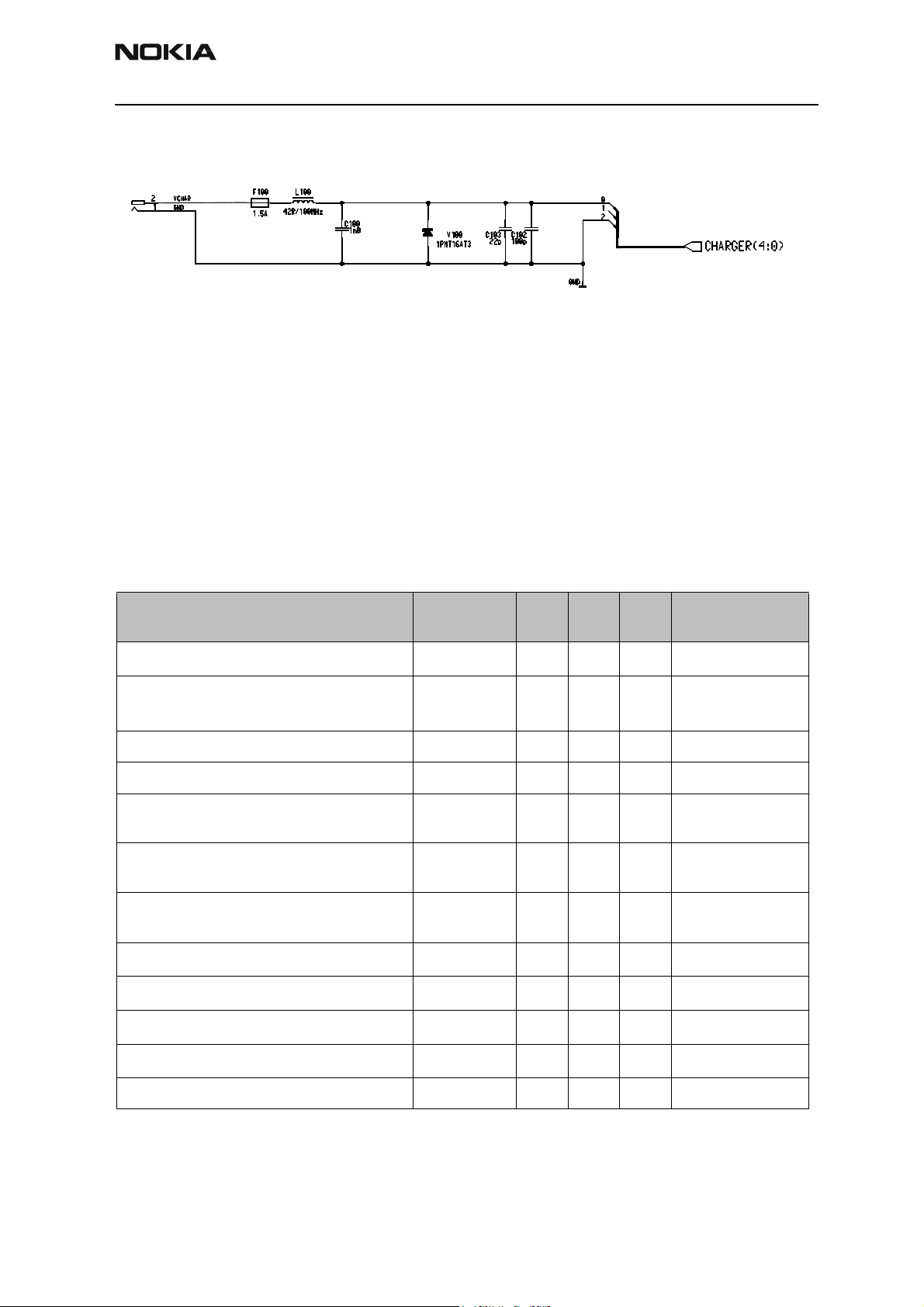

Charging

NHM-8NX supports the NMP Janette Charger interface.

Charging is controlled by the UEM ASIC, and external components are mounted for EMC,

reverse polarity and transient protection of the input to the baseband module. The

charger connection is through the system connector interface. Both 2- and 3-wire type

chargers are supported.

The operation of the charging circuit has been specified in such a way as to limit the

power dissipation across the charge switch and to ensure safe operation in all modes.

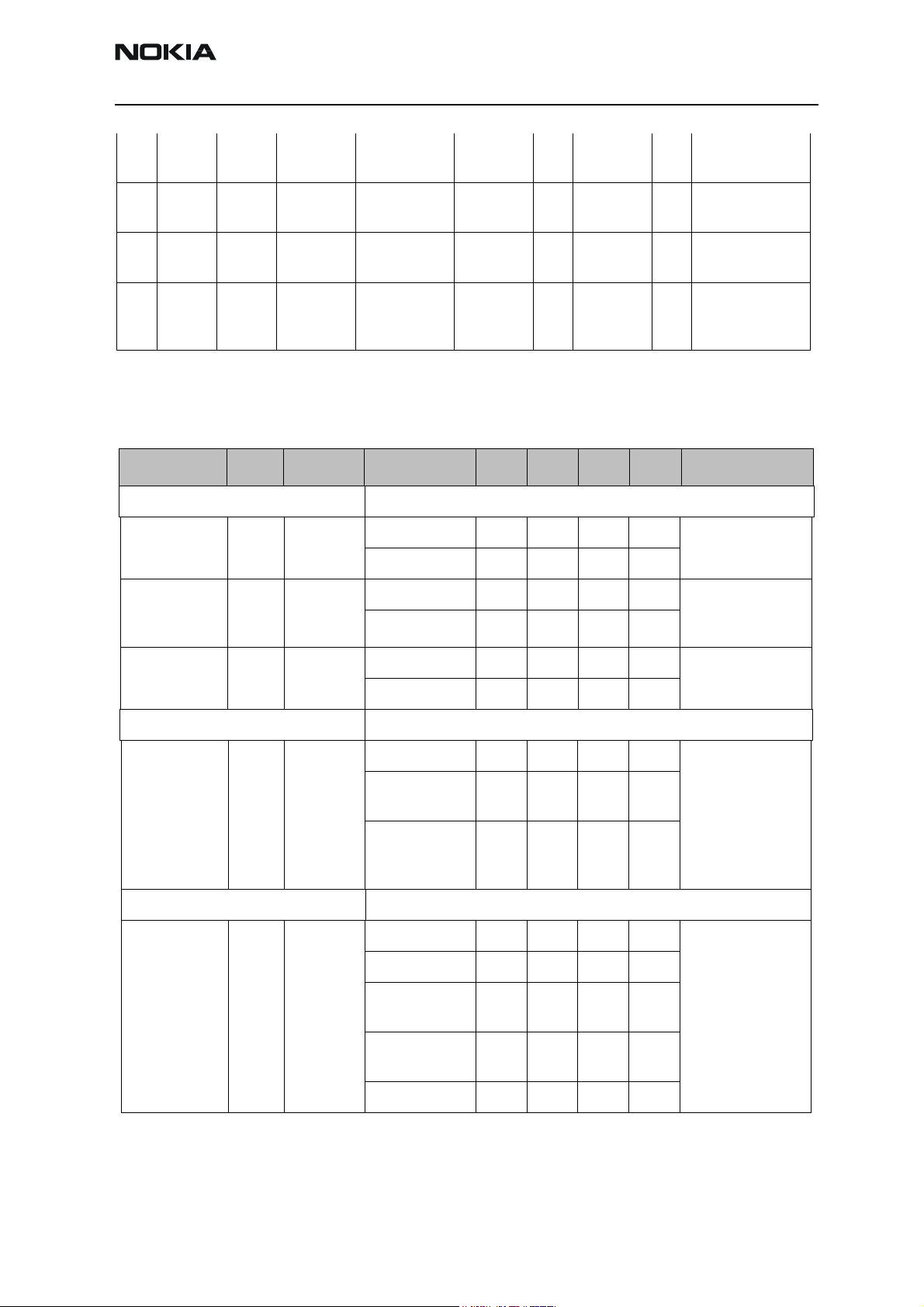

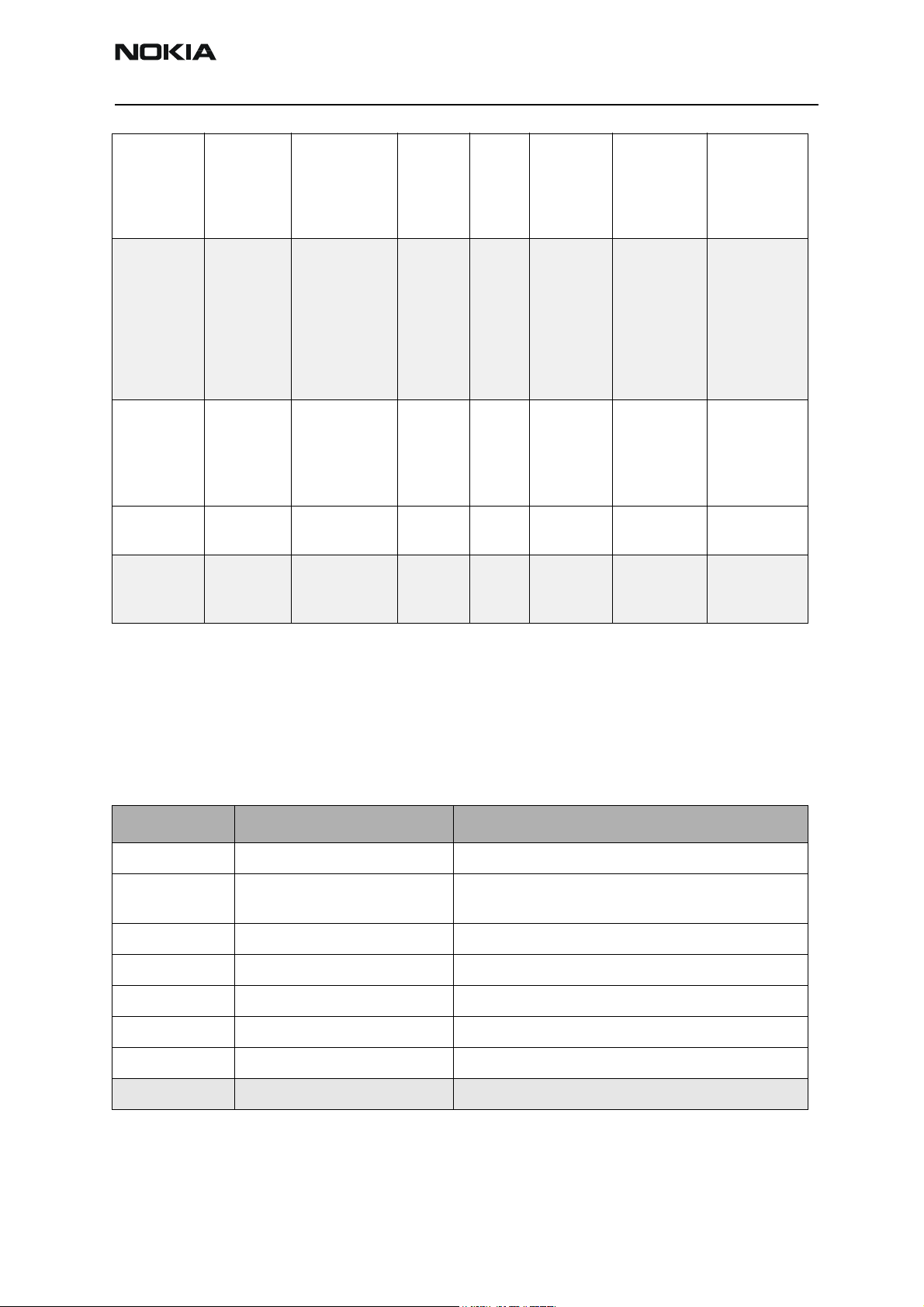

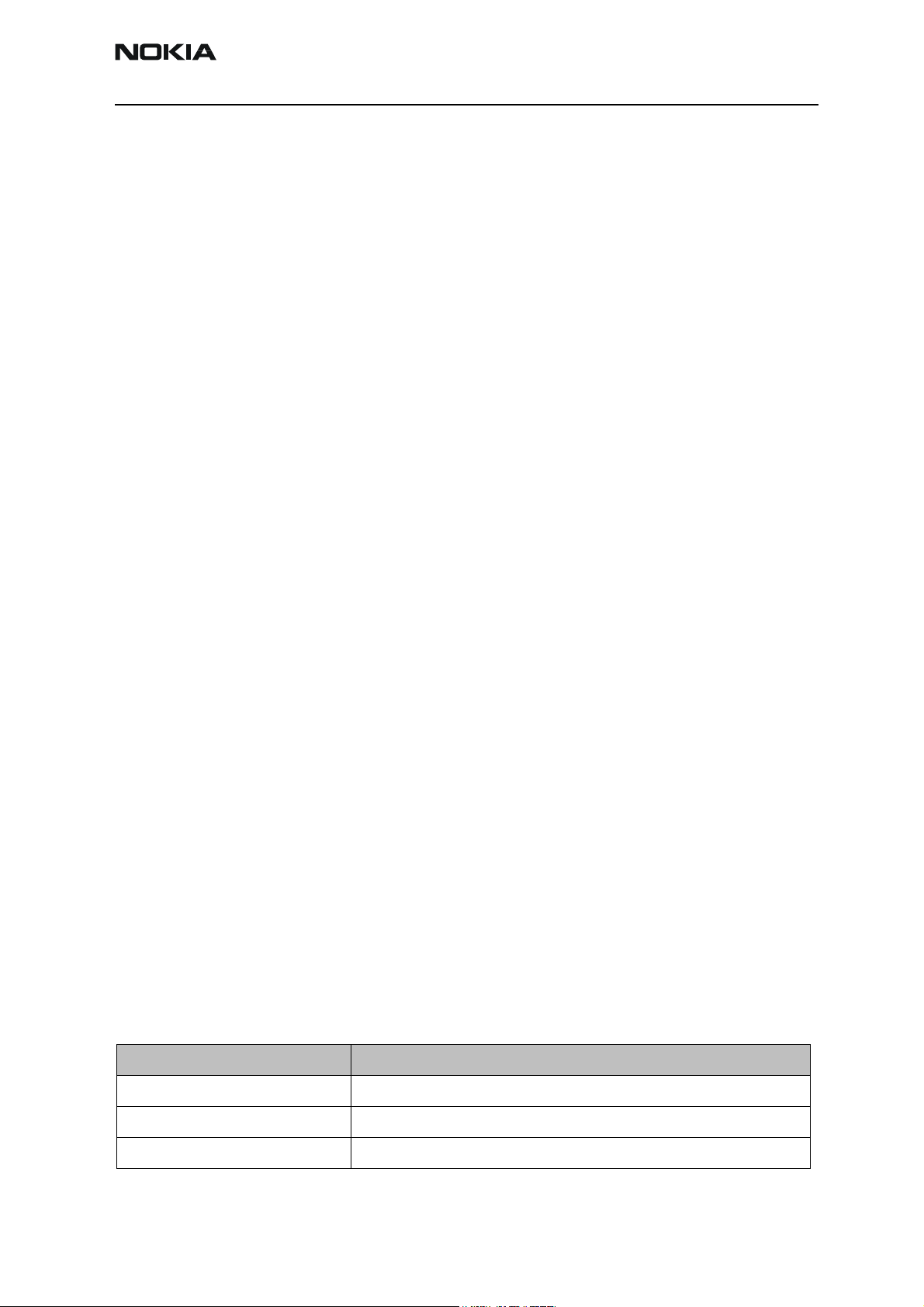

Figure 2: UEM charging circuitry

UEM

CHAR

PWM

VCHARin

Over

Temp.

Detection

WatchDog

PWM

Generator

Switch

Driver

Ctrl

Logic

Comp

Vmstr

Current

Sensing/

Limit

+

-

VCHARout

VBATT

VB ATT lim

VBATT

Charger Detection

Connecting a charger creates voltage on VCHAR input of the UEM. When VCHAR input

voltage level is detected to rise above VCH

threshold by UEM charging starts.

DET+

VCHARDET signal is generated to indicate the presence of the charger for the SW.

The charger identification/acceptance is controlled by EM SW.

The charger recognition is initiated when the EM SW receives a ”charger connected”

interrupt. The algorithm basically consists of the following three steps:

1. Check that the charger output (voltage and current) is within safety limits.

2. Identify the charger.

3. Check that the charger is within the charger window.

If the charger is accepted and identified, the appropriate charging algorithm is initiated.

Issue 1 05/02 ãNokia Corporation Page 21

Page 22

NHM-8NX

System Module & UI PAMS Technical Documentation

Charge Control

In active mode charging is controlled by UEM’s digital part. Charging voltage and current

monitoring is used to limit charge into safe area. For that reason UEM has programmable

charging cut-off limits VBATLim

(3.6V / 5.0V / 5.25V). Maximum charging current

1,2L,2H

is limited to 1.2 A. Default for VBATLim is 3.6V (used for Initial charging of empty battery).

VBATLim

VBATLim

are designed with hysteresis. When the voltage rises above

1,2L,2H

+ charging is stopped by turning charging switch OFF. No change in oper-

1,2L,2H

ational mode is done. After voltage has decreased below VBATLim- charging re-starts.

If VBAT is detected to rise above the programmed limit, the output signal OVV is set to ‘1’

by CHACON. If charging current limit is reached OVC output is set ‘1’ by CHACON.

Pulse-width-Modulated (PWM) control signals PWM1 and PWM32 are generated by

UEM’s digital part to CHACON block.

In principle there are two PWM frequencies in use depending on the type of the charger

(standard charger 1Hz, fast charger 32Hz. Duty cycle range is 0% to 100%), but in NHM8NX only the 1Hz mode will be used, as all charger will be treated as standard charges

(2-wire types).

Supported Chargers

Supported chargers are:

• 2-wire chargers: ACP-7, ACP-8 and ACP-12.

• 3-wire chargers: PPH-1, ACP-9,, ACT-1, LCH-8 and LCH-9.

The 3-wire chargers have a 3 wire interface to the phone, 2 power and 1 control. The

control wire carries the 32Hz digital pulse width modulated signal which must be generated by the phone to control the charger output voltage. In NHM-8NX the 32Hz PWM

for the charger is connected to GND inside the bottom connector. This sets full charger

output voltage and equals 0% PWM from charger point of view.

Charger Interface Protection

In order to ensure safe operation with all chargers and in misuse/fail situations charger

interface is protected using transient voltage suppressor (TVS) and 1.5A fuse. TVS used in

NHM-8NX is 16V@175W device.

Page 22 ãNokia Corporation Issue 1 05/02

Page 23

NHM-8NX

PAMS Technical Documentation System Module & UI

Table 22: Charger interface

TVS characteristics:

Breakdown voltage (V

Reverse standoff voltage (V

Max reverse leakage current at V

Max peak impulse current (I

Max clamping voltage at I

) 17.8Vmin (at IT 1.0mA)

BR

) 16V

R

(IR) 5uA

R

) 7A (at Ta=25*C, current waveform: 10/1000us)

pp

(Vc) 26V

pp

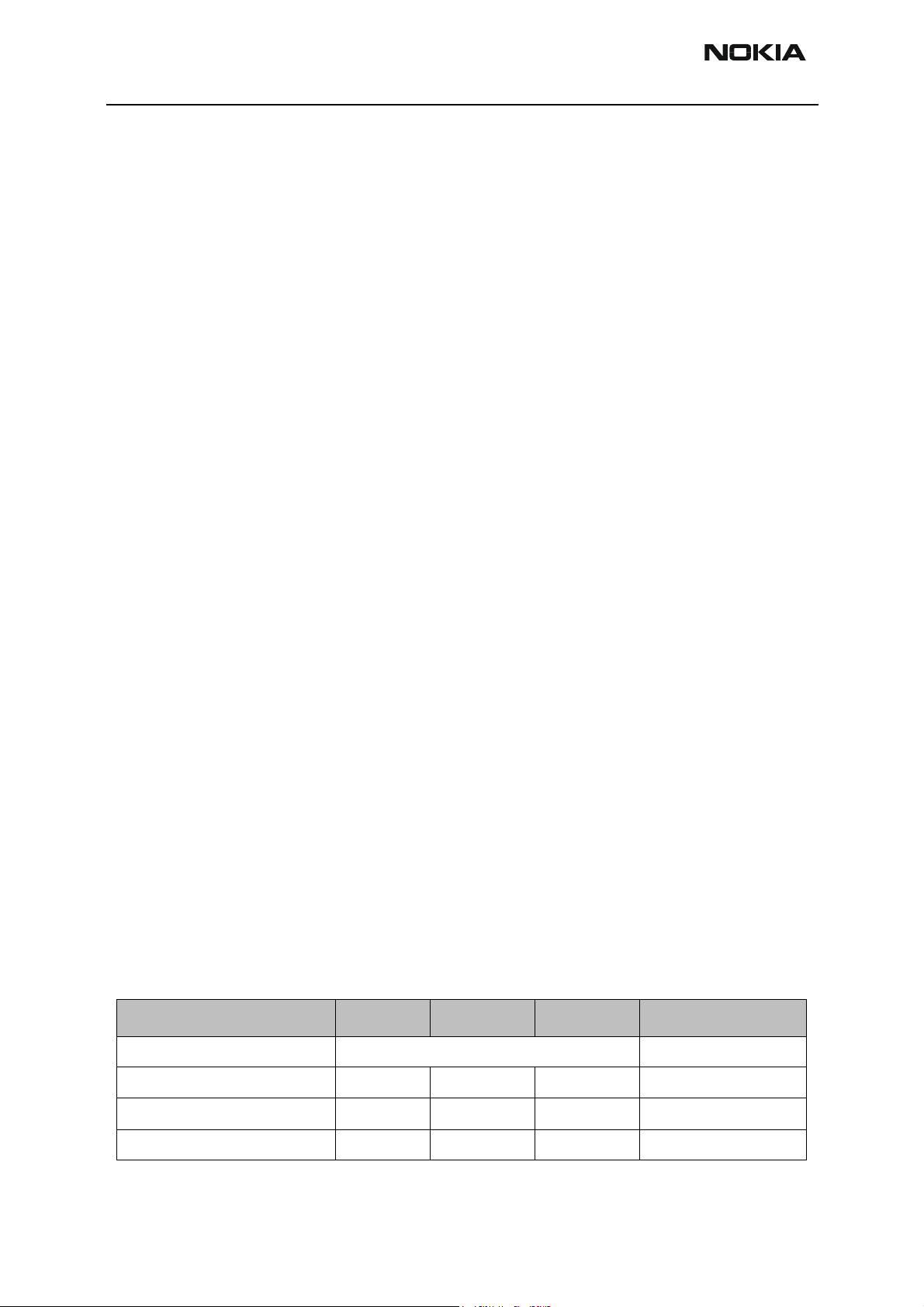

Charging Circuitry Electrical Characteristics

Table 23: Electrical Characteristics

Parameter

Test conditions

Input voltage range (fast charger, no load) VCHAR 7.0 8.4 9.2 V

Input voltage range (std charger, no load) - 11 .1

Absolute Maximum VCHAR voltage -0.3 - +20 V

Input resistance from VCharIn to ground Rin 2 4 6 kΩ

Master reset threshold level

VCOFFX threshold levels

VCHAR detection threshold level

Continuous input current (fast charger) I

Symbol Min Typ Max Units

16.9 V

7.9

V

MSTR+

VMSTR-

V

COFF+

VCOFF-

VCH

DET+

VCHDET-

CH

2.0

1.8

3.0

2.7

1.9

1.7

2.1

1.9

3.1

2.8

2.0

1.8

2.2

2.0

3.2

2.9

2.1

1.9

- - 850 mA

V

V

V

V

RMS

peak

RMS

Maximum input current (std charger) I

Start-up mode charging current I

PWM mode charge current I

CH

START

LIM

- - 1.0 A

100 - 150 mA

1.1 1.2 1.45 A

peak

Output voltage (Battery voltage) VBAT 0 3.6 4.2 V

Issue 1 05/02 ãNokia Corporation Page 23

Page 24

NHM-8NX

System Module & UI PAMS Technical Documentation

Charging cut-off limits (programmable) VBATLim

VBATLim1VBATLim2L+

VBATLim2LVBATLim2H+

VBATLim2H-

Charging switch resistance

(includes bonding and leads)

Temp =65°C (ambient)

PWM frequency (std charger) 0.5 1 1.5 Hz

PWM duty cycle 0 - 100 %

Switch output current slew rate SR 0.4 0.6 0.8 A/ms

Charging thermal shutdown threshold TjsdC+

VFLASH1 supply voltage input VFLASH1 2.7 2.78 2.88 V

R

TjsdC-

1+

SW

3.54

3.32

4.85

4.65

5.10

4.90

- - 0.3 W

140

120

3.65

3.50

5.0

4.85

5.25

5.10

150

130

3.76

3.66

5.15

5.05

5.40

5.30

160

140

Note: VCHAR is used as a supply voltage for charging control parts

Power Up and Reset

Power up and reset is controlled by the UEM ASIC. NHM-8NX baseband can be powered

up in following ways:

V

°C

1 Press power button, which means grounding the PWRONX pin of the UEM

2 Connect the charger to the charger input

3 Supply battery voltage to the battery pin

4 RTC Alarm, the RTC has been programmed to give an alarm

After receiving one of the above signals, the UEM counts a 20ms delay and then enters

it’s reset mode. The watchdog starts up, and if the battery voltage is greater than Vcoff+

a 200ms delay is started to allow references etc. to settle. After this delay elapses the

VFLASH1 regulator is enabled. 500us later VR3, VANA, VIO and VCORE are enabled.

Finally the PURX line is held low for 20 ms. This reset, PURX, is fed to the baseband ASIC

UPP, resets are generated for the DSP and the MCU. During this reset phase the UEM

forces the VCXO regulator on regardless of the status of the sleep control input signal to

the UEM. All baseband regulators are switched on at the UEM power on except for the

SIM regulator that is controlled by the MCU. The UEM internal watchdog is running during the UEM reset state, with the longest watchdog time selected. If the watchdog

expires the UEM returns to power off state. The UEM watchdog is internally acknowledged at the rising edge of the PURX signal in order to always give the same watchdog

response time to the MCU.

Power up with PWR key

When the Power on key is pressed the UEM enters the power up sequence as described in

Page 24 ãNokia Corporation Issue 1 05/02

Page 25

NHM-8NX

PAMS Technical Documentation System Module & UI

the section Power Up and Reset. Pressing the power key causes the PWRONX pin on the

UEM to be grounded. The UEM PWRONX signal is not part of the keypad matrix. The

power key is only connected to the UEM. This means that when pressing the power key

an interrupt is generated to the UPP that starts the MCU. The MCU then reads the UEM

interrupt register and notice that it is a PWRONX interrupt. The MCU now reads the status of the PWRONX signal using the UEM control bus, CBUS. If the PWRONX signal stay

low for a certain time the MCU accepts this as a valid power on state and continues with

the SW initialization of the baseband. If the power on key does not indicate a valid

power on situation the MCU powers off the baseband.

Power up when charger is connected

In order to be able to detect and start charging in a case where the main battery is fully

discharged (empty) and hence UEM has no supply (NO_SUPPLY mode of UEM) charging

is controlled by START-UP CHARGING circuitry.

Whenever VBAT level is detected to be below master reset threshold (V

MSTR-

) charging is

controlled by START_UP charge circuitry. Connecting a charger forces VCHAR input to

rise above charger detection threshold, VCH

. By detection start-up charging is

DET+

started. UEM generates 100mA constant output current from the connected charger’s

output voltage. As battery charges its voltage rises, and when VBAT voltage level higher

than master reset threshold limit (V

) is detected START_UP charge is terminated.

MSTR+

Monitoring the VBAT voltage level is done by charge control block (CHACON). MSTRX=‘1’

output reset signal (internal to UEM) is given to UEM’s RESET block when VBAT>V

MSTR+

and UEM enters into the reset sequence described in section Power Up and Reset.

If VBAT is detected to fall below V

during start-up charging, charging is cancelled.

MSTR-

It will restart if new rising edge on VCHAR input is detected (VCHAR rising above VCH-

).

DET+

Power up when battery is connected

Baseband can be powered up by connecting battery with sufficient voltage. Battery voltage has to be over UEM internal comparator threshold level, V

. Battery low limit is

coff+

specified in Table 2. When battery proper voltage is detected UEM enters to reset

sequence as described in section Power Up and Reset. This power up sequence is meant

for test purposes, in normal use (Btemp resistor > 1kΩ) the phone will power off again

immediately, without noticing the user.

RTC alarm power up

If phone is in POWER_OFF mode when RTC alarm occurs the wake up procedure is as

described in section Power Up and Reset. After baseband is powered on an interrupt is

given to MCU. When RTC alarm occurs during ACTIVE mode the interrupt for MCU is

generated.

Issue 1 05/02 ãNokia Corporation Page 25

Page 26

NHM-8NX

System Module & UI PAMS Technical Documentation

A/D Channels

The UEM contains the following A/D converter channels that are used for several measurement purposes. The general slow A/D converter is a 10 bit converter using the UEM

interface clock for the conversion. An interrupt will be given at the end of the measurement.

The UEM’s 11-channel analog to digital converter is used to monitor charging functions,

battery functions, voltage levels in external accessory detection inputs, user interface

and RF functions.

When the conversion is started the converter input is selected. Then the signal processing block creates a data with MSB set to ’1’ and others to ’0’. In the D/A converter this

data controls the switches which connect the input reference voltage (VrefADC) to the

resistor network. The generated output voltage is compared with the input voltage under

measurement and if the latter is greater, MSB remains ’1’ else it is set ’0’. The following

step is to test the next bit and the next., until LSB is reached. The result is then stored to

ADCR register for UPP to read.

The monitored battery functions are battery voltage (VBATADC), battery type (BSI) and

battery temperature (BTEMP) indication.

The battery type is recognized through a resistive voltage divider. In phone there is a

100kOhm pull up resistor in the BSI line and the battery has a pull down resistor in the

same line. Depending on the battery type the pull down resistor value is changed. The

battery temperature is measured equivalently except that the battery has a NTC pull

down resistor in the BTEMP line.

KEYB1&2 inputs are made for keyboard scanning purposes. These inputs are also routed

internally to the miscellaneous block. KEYB1&2 inputs are not used In NHM-8, and the

connected interrupts must be kept disabled by SW.

The HEADINT and HOOKINT are external accessory detection inputs used for monitoring

voltage levels in these inputs. They are routed internally from the miscellaneous block

and they are connected to the converter through a 2:1 multiplexer.

PATEMP and VCXOTEMP channels are not used as originally intended. PATEMP input is

used for detection of accessory covers (CTI), VCXOTEMP is not used in NHM-8.

Table 24: Slow A/D converter characteristics

Characteristics Min Typ Max Unit

Number of bits 10 bits

Integral non linearity - - +/- 2 LSB

Differential non linearity - - +/- 2.5 LSB

Conversion time - - 11 µs

Page 26 ãNokia Corporation Issue 1 05/02

Page 27

NHM-8NX

PAMS Technical Documentation System Module & UI

Input voltage range

Input capacitance 4 5 6 pF

Signal Min Typ Max Unit Note

VBATADC 2.7 - 5.25 V Physical input on UEM is

ICHAR VBATADC - VBATADC+0.316 V

VCHARADC 0.1 - 1.35 V

BSI 0 - 2.7 V

BTEMP 0 - 2.7 V

PATEMP 0 - 2.7 V Used for CTI

VCXOTEMP 0 - 2.7 V Not used in NHM-8

HEADINT 0 - 2.7 V

HOOKINT 0 - 2.7 V

(1)

0 - 2.7 V

.

Table 25: Slow A/D converter input ranges

VBATREGS

LS 0 - 2.7 V Not used in NHM-8

KEYB1 0 - 2.7 V Not used in NHM-8

KEYB2 0 - 2.7 V Not used in NHM-8

AD converter is calibrated in production.

Battery Voltage Measurement A/D Channel (

VBATADC)

The battery voltage is scaled inside the UEM in order to avoid external components. The

maximum battery voltage that gives a full A/D reading is 5.25V.

Battery voltage can be connected to sample and hold circuit either through a resistive

voltage divider or through a voltage scaling circuit. The voltage scaling circuit is used to

get larger input voltage range for the converter than what is achieved with the resistive

divider. The sample and hold circuit is used to measure the battery voltage during transmit burst. Otherwise the S/H circuit is bypassed. Note that both the battery voltage

(VBATADC) and the charger voltage (VCHARADC) are sampled whenever the sampling

function is used.

Charger Voltage Measurement A/D Channel (VCHARADC)

This channel is used to measure the charger input voltage VCHAR. The charger input idle

voltage is measured to identify the charger. Associated with the charger voltage measurement an envelope detector is used to detect a rectifier bridge type of charger. Connection of the charger is performed by the rising edge of the charger input. The charger

must be a full wave rectifier. A half wave rectifier charger have to be rejected.

Issue 1 05/02 ãNokia Corporation Page 27

Page 28

NHM-8NX

System Module & UI PAMS Technical Documentation

This A/D channel has a feature built into it that the charger voltage measurement can be

specified to be performed when the charger switch is closed or open. This information is

provided by the MCU when this channel is addressed.

The charger measurement A/D channel can also be timed to the charger envelop detector

in order to measure the standard charger peak voltage.

Charger Current Measurement A/D Channel (

ICHAR)

This A/D channel is used to measure the charger current ICHAR. The current sensor is

implemented using 0.22 Ω resistor in series between UEM charging voltage output and

battery voltage. The voltage drop over the resistor is examined. The charger current measurement is used for charger detection and maintenance charging PWM calculations.

Battery Temperature Measurement A/D Channel (BTEMP)

The temperature of the battery pack is monitored during charging. The battery pack is

equipped with an NTC resistor, value is 47kOhm at 25oC. The BTEMP signal is connected

on the baseband to the UEM. An external 100kOhm pull-up is needed.

Battery Size Measurement A/D Channel (BSI)

This channel is used to identify the battery. The battery pack BLC-2 has a resistor

75kOhm connected to ground. An external 100kOhm pull-up resistor is on the phone

side. The BSI signal is connected to UEM.

External Accessory Detection A/D Channel (

HEADINT, HOOKINT)

In order to be able to detect DCT4 type of accessories an A/D converter channel is used to

measure the DC level on the external microphone. The detection is implemented using a

pull-down resistor in the accessory and a pull-up on the baseband side. The pull-up

resistor on the baseband side is internal to the UEM. This A/D channel is internally connected to either HeadInt or HookInt.

PA Temperature measurement A/D Channel (PATEMP)

In NHM-8NX this A/D channel is used for Cover Type Detection (CTI) in conjunction with

DC-OUT covers.The detection is implemented using a pull-down resistor in the accessory

and a pull-up on the baseband side.

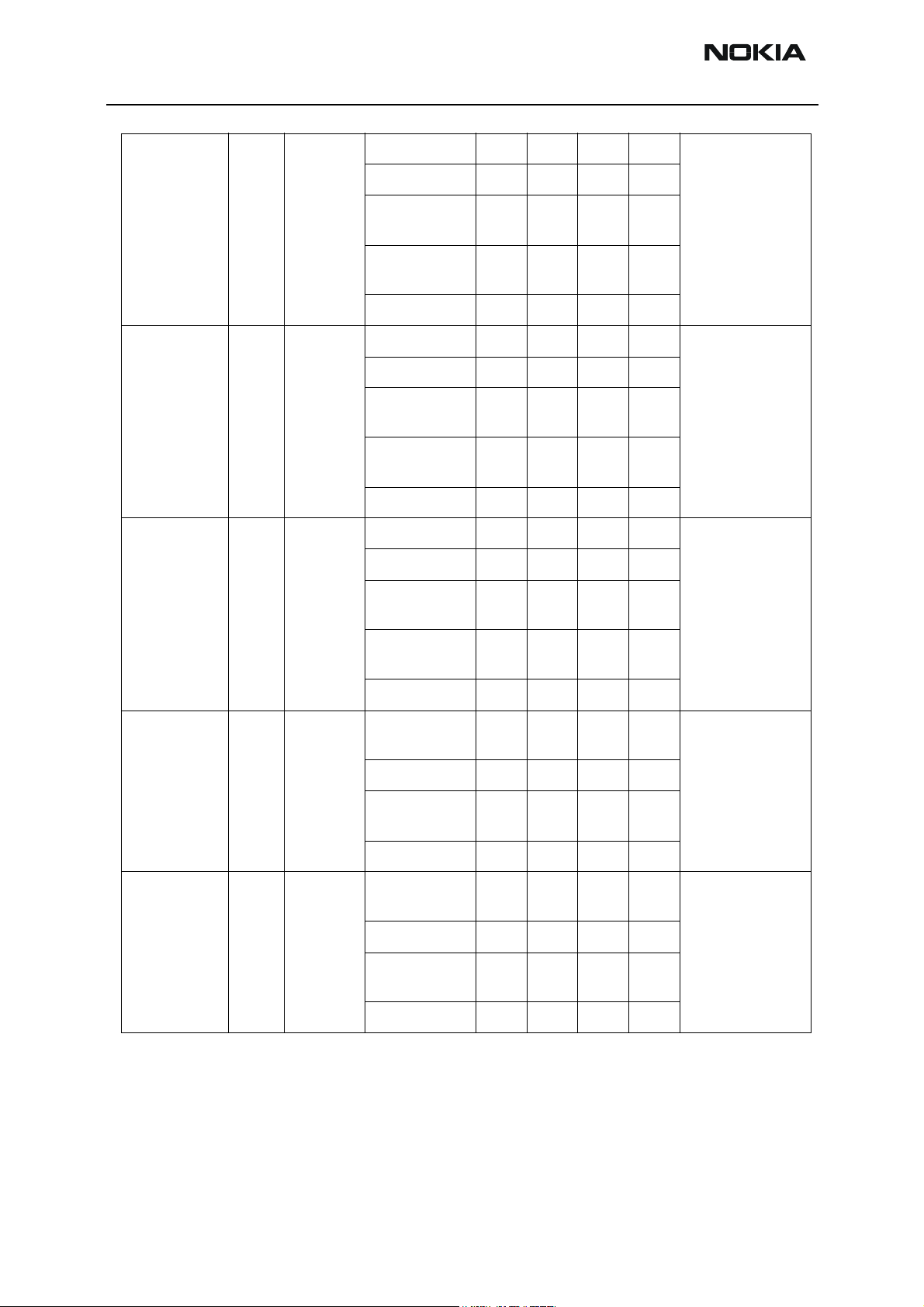

LCD & Keyboard Backlight

LCD Backlight

LCD Backlight consists of 2 TBSF (Through the Board Side Firing) yellow/green LED's

which are placed on the main PWB below the LCD area. They lit into the light guide

where the light is distributed to generate sufficient backlight for the LCD.

Keyboard light

Page 28 ãNokia Corporation Issue 1 05/02

Page 29

NHM-8NX

r

PAMS Technical Documentation System Module & UI

The keyboard light consists of 2 TBSF yellow/green LED's, which are placed under the

keyboard and use the light guide to distribute the light

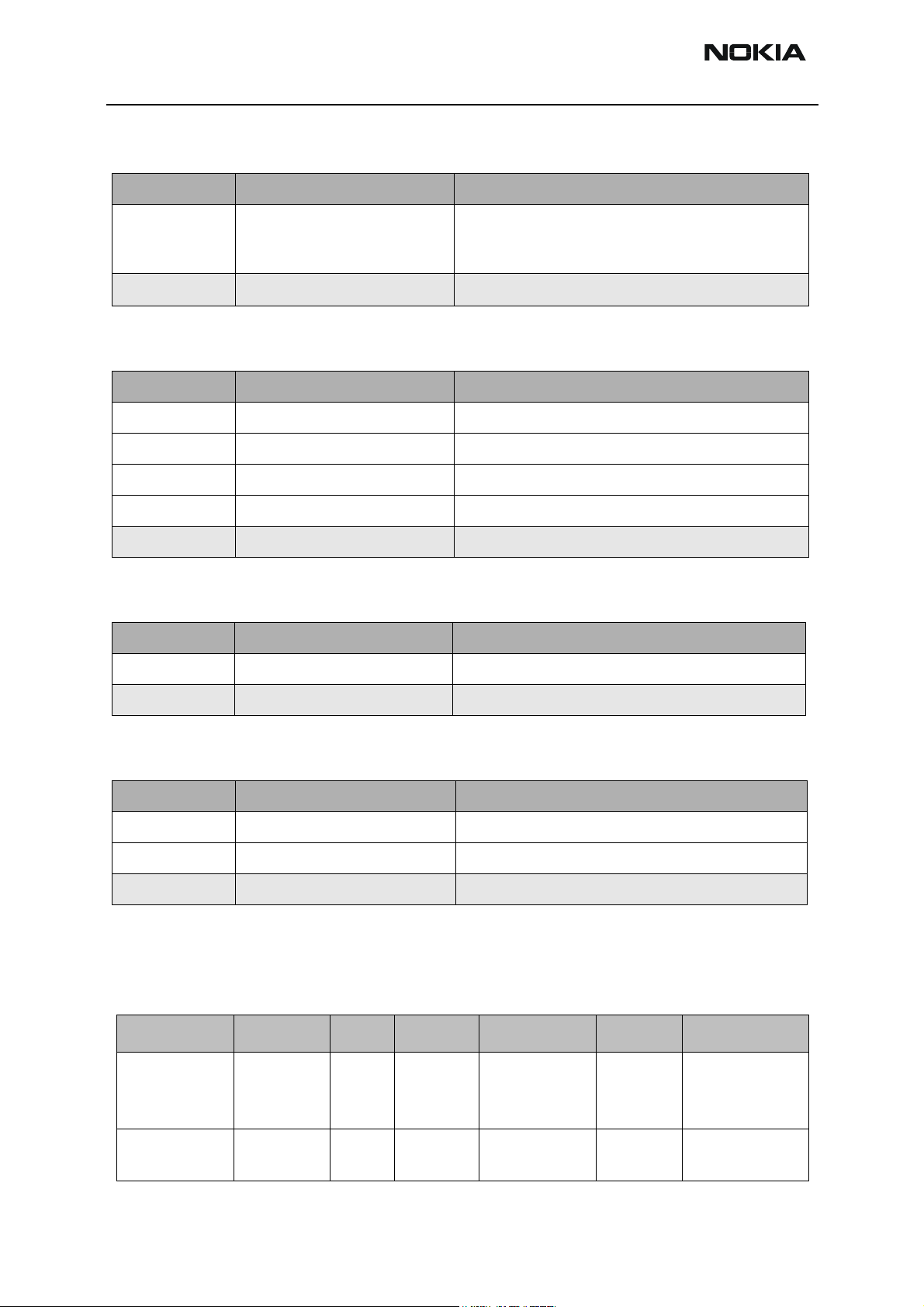

LED driver circuit

The LED drivers for LCD & Keyboard backlight are shared as shown below in Figure 4

Shared LED driver circuit for LCD and Keyboard backlight.The driver circuit is controlled

by the UEM output pin [DLIGHT] and drive current is 15mA pr. LED. By appropriate SW

the driver can be PWM controlled for dimming purpose.

Figure 3: Shared LED driver circuit for LCD and Keyboard backlight

LCD cell

LCD Glass

Lightguide

Domesheet

Figure 4: Complete overview of LCD module

Metal frame

Speake

Issue 1 05/02 ãNokia Corporation Page 29

Page 30

NHM-8NX

A

System Module & UI PAMS Technical Documentation

The LCD is a black and white 96x65 full dot matrix display. The LCD has a standard DCT4

interface. The LCD interface between the LCD cell and the main PWB can be viewed in

section LCD. The LCD cell is part of the complete LCD module, which includes metal

frame, gasket, light guide, spring connector, transflector, dome sheet and earpiece. The

figure below illustrates the complete overview of the LCD module.

The general specifications are listed below:

• Glass size, width x height x thickness : 38.4mm x

37.6mm x 1.70mm; Philips

• Glass size, width x height x thickness : 38.4mm x

37.6mm x 1.70mm; Samsung

• Glass size, width x height x thickness (incl.caps) : 38.4mm x

37.6mm x 2.75mm; Seiko E.

• Glass thickness : 0.55mm

• Viewing area (width x height) : 35.4mm x

27.7mm

• Active pixel area (width x height) : 30.609mm x

24.1mm

• Number of pixels : 96 columns x 65

rows

• Pixel height to width ratio : 1.17:1

• Pixel gap : 0.015mm

• Technology : FSTN

• Operating temperature range : -25°C to +70°C

• Multiplex ratio : 1:65

• Display type : Positive

• Main viewing direction : 6 o’clock

• Illumination Mode : Transflective

• Front Surface : Glossy

• Colour Tone: Active pixels : Black

• Background : Neutral/White

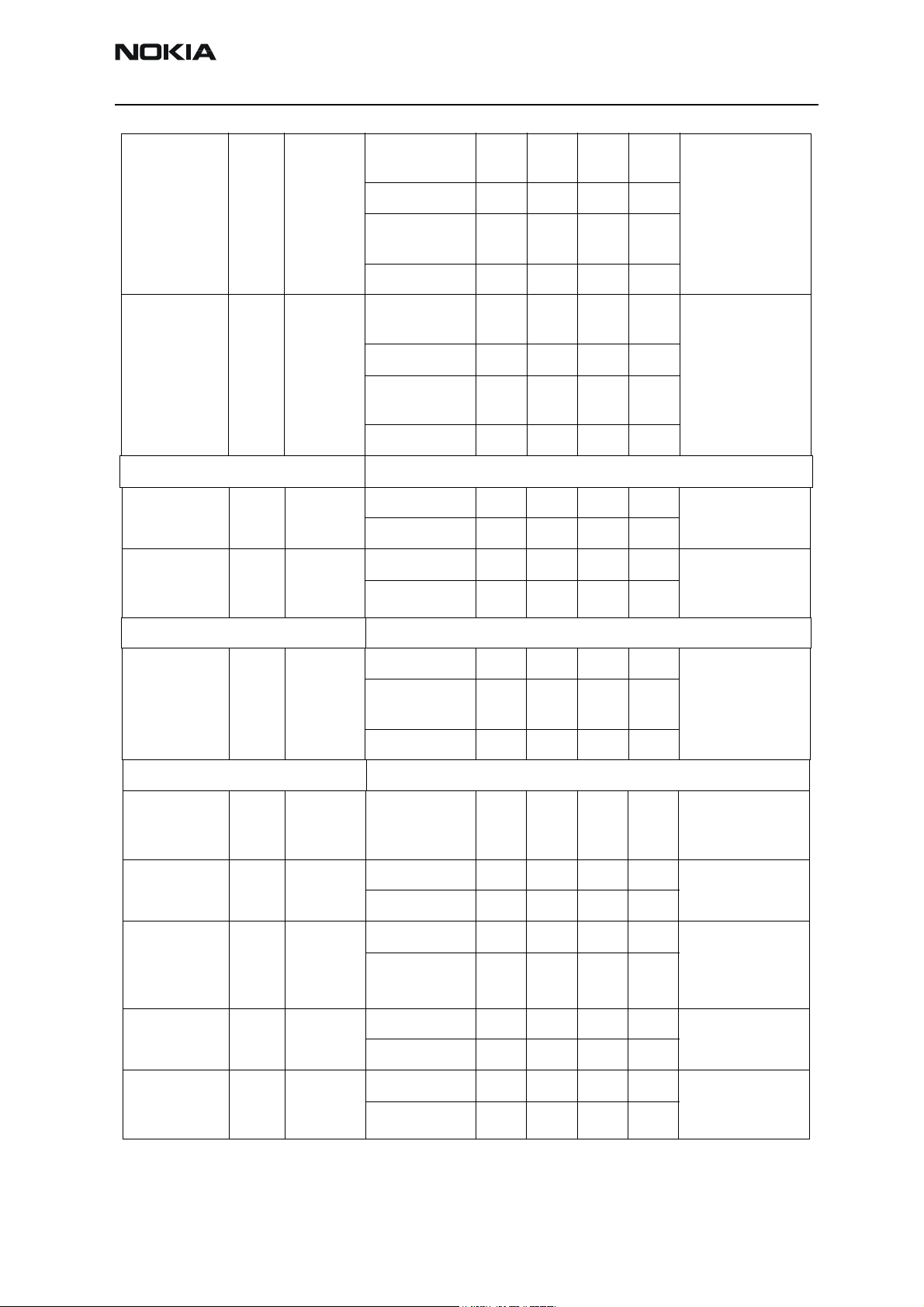

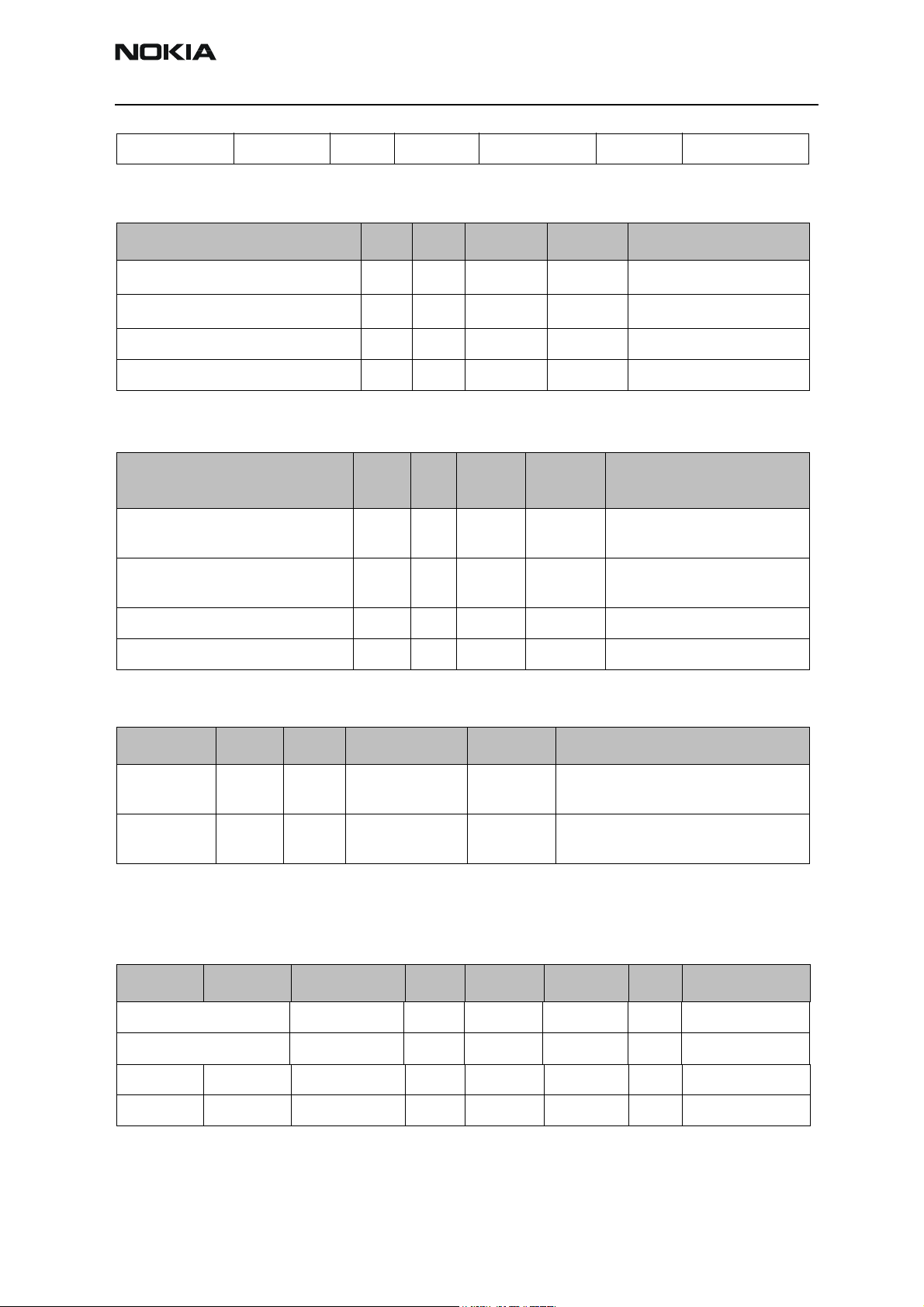

Figure 5: BW4 LCD module

u Connector pads

C

Driver

Viewing area

Active area

96 x 65

SE

Top View

FLASH1

R 0

R

64

and VIO. V

C C

C 0 C 95

FLASH1

Driver

C

Top View

Active area

96 x 65

Philips/Samsung

is used for the boosting circuit

FPC

CC

SEG 0 SEG 95

CO

M

0

CO

M

64

The LCD is powered from both V

Page 30 ãNokia Corporation Issue 1 05/02

Page 31

NHM-8NX

V

PAMS Technical Documentation System Module & UI

and VIO for the driver chip.

SIM Interface

The UEM contains the SIM interface logic level shifting. The SIM supports 3V and 1.8V

SIMs. SIM supply voltage is selected by a register in the UEM. It is only allowed to

change the SIM supply voltage when the SIM IF is initialized.

The SIM power up/down sequence is generated in the UEM. This means that the UEM

generates the RST signal to the SIM. Also the SIMCardDet signal is connected to UEM.

The card detection is taken from the BSI signal, which detects the removal of the battery.

The monitoring of the BSI signal is done by a comparator inside UEM. The comparator

offset is such that the comparator output does not alter state as long as the battery is

connected. The threshold voltage is calculated from the battery size specifications.

The SIM interface is powered up when the SIMCardDet signal indicates ”card in”. This

signal is derived from the BSI signal.

Table 26: BSI Detection

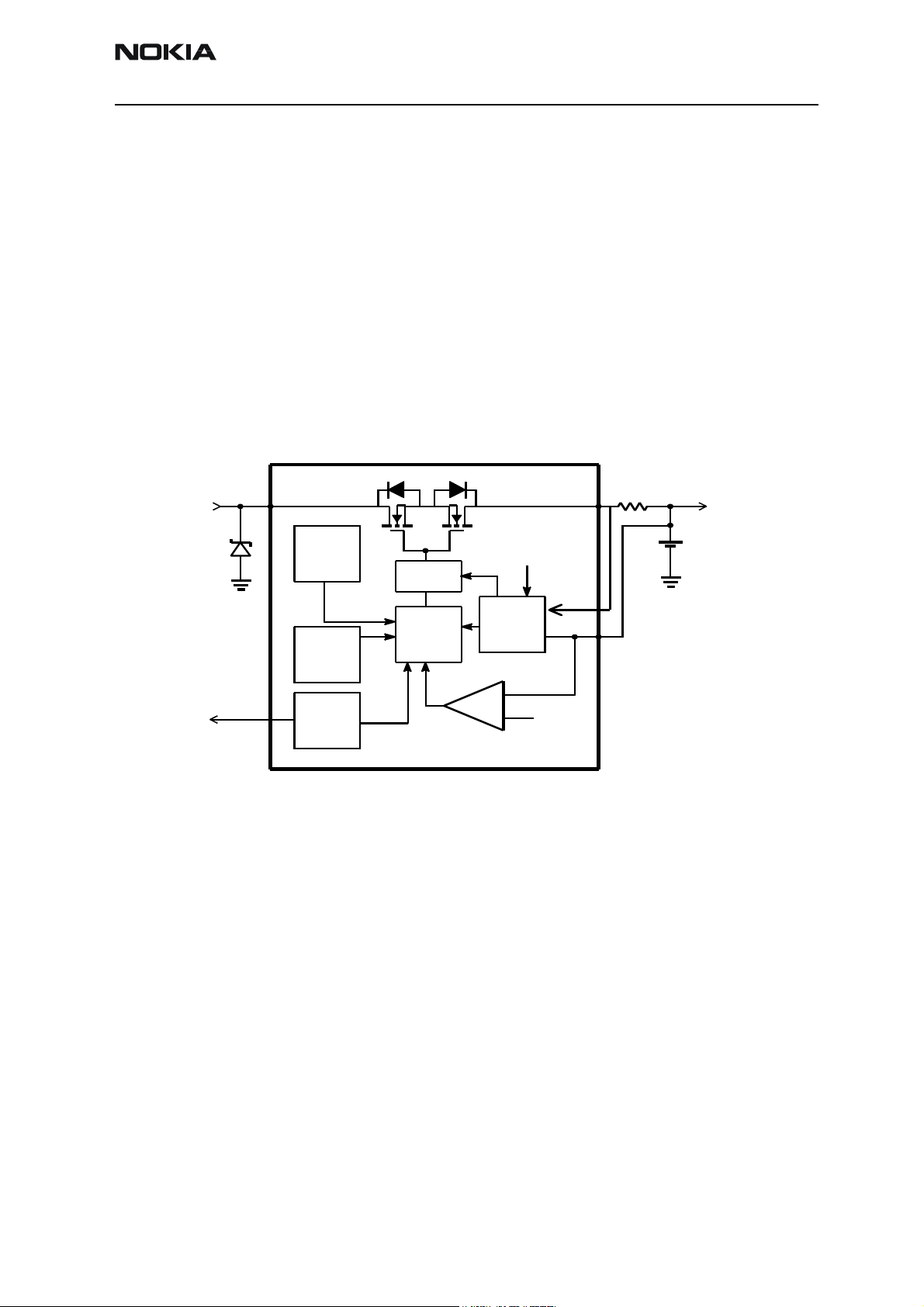

Parameter Variable Min Typ Max Unit

BSI comparator Threshold Vkey 1.94 2.1 2.26 V

BSI comparator Hysteresis (1) Vsimhyst 50 75 100 mV

Note: (1) Hysteresis is defined as [Vkey(+)-Vkey(-)] / 2

Figure 6: BSI Detection

Example of BSI detection

FLASH1

BSI

Vkey(+)

Vkey

Vkey(-)

GND

The whole SIM interface is located in the two ASICs, UPP and UEM.

The SIM interface in the UEM contains power up/down, port gating, card detect, data

receiving, ATR-counter, registers and level shifting buffers logic. The SIM interface is the

electrical interface between the Subscriber Identity Module Card (SIM Card) and mobile

phone (via UEM device).

Issue 1 05/02 ãNokia Corporation Page 31

Page 32

NHM-8NX

System Module & UI PAMS Technical Documentation

The data communication between the card and the phone is asynchronous half duplex.

The clock supplied to the card is 3.25 MHz. The data baudrate is SIM card clock frequency divided by 372 (by default), 64, 32 or 16. The protocol type, that is supported, is

T=0 (asynchronous half duplex character transmission as defined in ISO 7816-3).

Figure 7: UEM & UPP SIM connections

GND

UPP

SIM

C5 C6 C7

C1C2C3

From Battery Type

GND

SIMDATA

SIMIF

register

UEM

digital

logic

SIMIO

SIMClk

Data

C8

C4

SIMCLK

SIMRST

VSIM

UEM

BSI

SIMIO

SIMClk

Data

UIF Block

UEMInt

CBusDa

CBusEnX

CBusClk

The internal clock frequency from UPP CTSI block is 13 MHz in GSM. Thus to achieve the

minimum starting SIMCardClk rate of 3.25 MHz (as is required by the authentication

procedure) and the duty cycle requirement of between 40% and 60% then the slowest

possible clock supplied to the SIM has to be in the GSM system clock rate of 13/4 MHz.

Internal Audio

Earpiece

The earpiece selected for NHM-8NX is the standard DCT3 13-mm earpiece from PSS

(previously used for 3210, 3310, 6210, 7110 among others). The earpiece design is leak

tolerant.

The internal earpiece is a dynamic earpiece with an impedance of 32 ohms. The earpiece

is a low impedance type, since the sound pressure is to be generated using current and

not voltage as the supply voltage is restricted to 2.7V. The earpiece is driven directly by

the UEM and the earpiece driver in UEM is a bridge amplifier.

Page 32 ãNokia Corporation Issue 1 05/02

Page 33

NHM-8NX

PAMS Technical Documentation System Module & UI

Figure 8: Speaker Interface

UEM

EARP

EARN

10

10

EARP

EARN

Earpiece Acoustic Design

The earpiece acoustics is designed to be type approved by type 3.2, low leak artificial ear

(Ear Simulator Type 4195, Low Leakage).

Three different types of A-covers is used for NHM-8NX: Standard cover, gaming cover

and DC-out cover. The gaming and DC-out covers is accessory covers. The std. A-cover

and the gaming cover comply with the same TA rules since they cannot be identified

HW- and SW-wise; this means that they match acoustical wise. However, the DC-out

cover can be identified, meaning that this type of cover is equalised separately.

In the assembly process the earpiece is placed into the lightguide from the front of the

phone. On top of this the metal frame is mounted.

The lightguide have stoppers in the bottom which lift the earpiece 0.3mm from the PWB

to provide leakage to the back.

On top of the lightguide is a metal frame which is the only visible part (in the earpiece

area) when the A-cover is removed. The metal frame covers the front of the earpiece to

provide protection against damage from fingers etc. The metal frame contain two acoustical holes in the area over the earpiece. These are placed as close to the vertical centre

of the phone as the design allows, in order to secure a sufficient sound pressure.

The metal frame have double-sided sealing in the earpiece area 1) downwards in order to

provide sealing and pressure against the top of the earpiece 2) upwards to provide sealing to the A-cover. There is an opening in this gasket in the area on top of the metal

frame to provide better leakage to the internal volume.

The A-cover have a total of 5 acoustical holes positioned on a straight vertical line

through the centre of the phone. All holes are equal in size, elliptical in shape (each hole

approximates the area of a Ø1.3 hole). The three holes in top of the A-cover are positioned close to the metal frame hole in order to control loudness.

The A-cover includes a ring underneath which seals against the metal frame gasket. The

ring has a well defined opening of 5 mm (width). The opening has one main purpose: to

allow a dust shield to be mounted. Secondly the opening will provide better conditions

for obtaining good leak tolerant performance, than if only one A-cover hole was present.

All covers are optimised for the use of a dust shield, the specific type is Saatitech

PEC120/41.

Issue 1 05/02 ãNokia Corporation Page 33

Page 34

NHM-8NX

System Module & UI PAMS Technical Documentation

Below the earpiece is the PWB, where 4 holes will secure proper leakage to the volume

between the PWB and the internal antenna. However since the PWB doesn't stretch all

the way up to the top of the phone there will also be some natural leakage where the

PWB is missing.

Microphone electrical interface

In NHM-8NX a differential bias circuit, driven directly from the MICB1 bias output with

external RC-filters is chosen. This is a solution that has previously been used with suc-

cess in other phones. The RC filter (220 Ω, 4.7µF) is scaled to provide damping at 217 Hz.

217 Hz audible noise (TDMA) will occur if the bias output MICB1 demodulates in-coming

radio frequencies.

Common DCT4 BB specifies filtering of the reference voltage for the microphone bias

generators. In below figure this filtering is included on the MICBCAP pin.

Besides pure bias purposes also EMC and ESD protection is shown in figure 11. The RC-

filter 2.2 kΩ and 1nF are EMC-component, while the remaining 10 nF and 1 nF capaci-

tors near the bottom connector are for ESD.

The 33nF and 100nF series-capacitors and 12kΩ parallel resistor create a 2'nd order high

pass filter. The input impedance of the gain stage at MIC1P/N is part of the 2'nd stage of

the RC-circuit. The high pass filter is required due to low-frequency noise, which is one

phenomenon identified as a problem when the internal microphone is used as handsfree

microphone (PPH-1/carkit mode).

The microphone bias is controlled in the 8 bit AudioBiasR register.

Figure 9: Internal microphone electrical interface

Placed near

connector

10n 10n

bottom

MIC+

1n

MIC-

UEM

MICB1

MIC1P

MIC1N

MICBCAP

1u

2*33n

Placed near

UEM

1n 1n

1k

2k2

2k2

1k

220

4.7uF

12k

2*100n

Ringer

A speaker is used to generate alerting tones and melodies to indicate incoming call, as

well as used to generate game sound, keypress and warning tones for the user

Page 34 ãNokia Corporation Issue 1 05/02

Page 35

NHM-8NX

PAMS Technical Documentation System Module & UI

A new type of component is used for ringer melodies: a speaker.

The speaker is a 13 mm device from PSS. It's inherited from the 13mm earpiece (also

used by NHM-8) however with more height to provide opportunities for more displacement for the speaker diaphragm. The speaker have a protective shield directly in front of

the diaphragm.

The speaker substitutes the original buzzer.

Alerting tones and MIDI melodies is generated by the speaker, which is controlled by a

sine driven output from UEM and an external amplifier.

The speaker implementation have two main resonances: 1.8 kHz and 2.9 kHz. The ringer

melodies is optimised for the given response so that the best possible (and loudest possible) tones will be implemented.

Acoustical wise the back of the speaker is designed to be completely tight, with a welldefined volume. The volume is kept under control by a semi-adhesive gasket mounted on

the back of the speaker, and the PWB.

A double-adhesive gasket is being used on the front of the speaker to provide sealed

conditions from front to back. In front of the speaker there is a well-defined volume

which connects into the sound-port holes in the D-cover.

The speaker is electrically connected to the PWB by spring contacts (similar to that for

the internal earpiece).

Figure 10: Interface between the MIDI-circuit and the UEM

UEM

HEADINT

HFCM

UPP

HF

GENIO14

10

10

1u

10n

10n

47k

47k

100k

1u

External audio interface

1u

10n 10n

Vbat

100k

Vdd

IN-

IN+

BYPASS

SHUTDOWN

GND

27p

Vo1

Vo2

10n 10n

42 ohm / 100 MHz

42 ohm / 100 MHz

100k

INT

XEARP

XEARN

Interface to

DC-out

SALT

Placed near

UEM

Placed outside

BB-can, near

SALT

Accessories

Batteries

Issue 1 05/02 ãNokia Corporation Page 35

Page 36

NHM-8NX

System Module & UI PAMS Technical Documentation

NHM-8NX supports Li-Ion batteries.

Figure 11: Mechanical layout and interconnections of DCT-4 battery

Table 27: Pin numbering of battery pack

Signal name Pin number Function

VBAT 1 Positive battery terminal

BSI 2 Battery capacity measurement

(fixed resistor, connected to GND, inside the battery pack)

BTEMP 3 Battery temperature measurement

(measured by ntc resistor connected to GND inside pack)

GND 4 Negative/common battery terminal

The BSI fixed resistor value indicates type and default capacity of a battery. NTC-resistor

BTEMP measures the battery temperature.

Temperature and capacity information are needed for charge control. These resistors are

connected to BSI and BTEMP pins of battery connector. Phone has 100 kΩ pull-up resis-

tors for these lines so that they can be read by A/D inputs in the phone.

External Audio

NHM-8NX is designed to support fully differential external audio accessory connection.

A headset and PPH-1 can be directly connected to system connector. Detection of the

different accessories is made in analog way by reading the DC voltage value of EAD converter.

Page 36 ãNokia Corporation Issue 1 05/02

Page 37

NHM-8NX

PAMS Technical Documentation System Module & UI

Figure 12: Headset interface

2.7V

Hookint

/MBUS

EAD

HeadintHeadint

Mic_bias

HF

HFCM

UEM

MICB2

MIC2P

MIC2N

3...25k

2.1V

33N

0.8V

0.8V

Not all components are shown

1k0

1.8V

33N

1k0

0.3V

Button

MicGnd

Analog Audio Accessory Detection

The accessory is detected by the HeadInt signal when the plug is inserted. Normally when

no plug is present, the internal pull-down on the HF pin pulls down the HeadInt signal.

HeadInt comparator value is 1.9V. When the plug is inserted the switch in the connector

is opened and the HeadInt signal is pulled up by the internal pull-up. The 1.9V threshold

level is reached and the comparator output changes to low state causing an interrupt.

Vice versa when the accessory is disconnected the HeadInt switch is closed and the

HeadInt is pulled down.

Table 28: Truth table for HookInt and HeadInt

HookInt HeadInt

Basic Headset, fully differential H H

Button Headset (Switch closed) L H

Button Headset (Switch open) H H

PPH-1 H H

No accessory H L

HeadInt signal is used to detect when the accessory is connected.

HookInt signal is used to detect when the button of the headset is pressed.

Note: Charging must be disabled during identification of PPH-1.

Headset Detection

Supported headsets are 4-wire fully differential accessories. Detection of the headset

can be split into five main phases:

Issue 1 05/02 ãNokia Corporation Page 37

Page 38

NHM-8NX

System Module & UI PAMS Technical Documentation

1 Micbias is set to high impedance state

2 HeadInt interrupt is detected

3 EAD reading below 0.35V

4 Micbias is set active 2.1V

5 EAD reading 1.0V - 2.2V -> Headset connected

Table 29: Headset identification

Name Function Min Typ Max UnitDescription

Headint Accessory detection 2.2 2.78 2.86 V Accessory connected

Ead / hookint Micbias=High-Z 0.35 V Headset

Micbias active 2.1V 1.009 1.07 1.163 V Headset button closed

1.596 1.85 2.140 V Headset button open

The hook signal is generated by creating a short circuit between the headset microphone

signals. When no accessory is present the HookInt signal is pulled up by the UEM. When

the accessory is inserted and the microphone path is biased the HookInt signal decreases

to 1.8V due to the microphone bias current flowing through the upper bias resistor network. When the button is pressed the microphone signals are connected together and

the HookInt will fall below trigger treshold level 1.35V. This change in DC level will cause

the HookInt comparator output to change state.

HeadInt comparator reference level is 1.90 V +-0.15 V. HookInt comparator reference is

selected by SW. Used trigger level is 1.35 V +/- 10mV.

PPH-1 Detection

PPH-1 accessory uses 4-wire fully differential audio connection. The accessory is