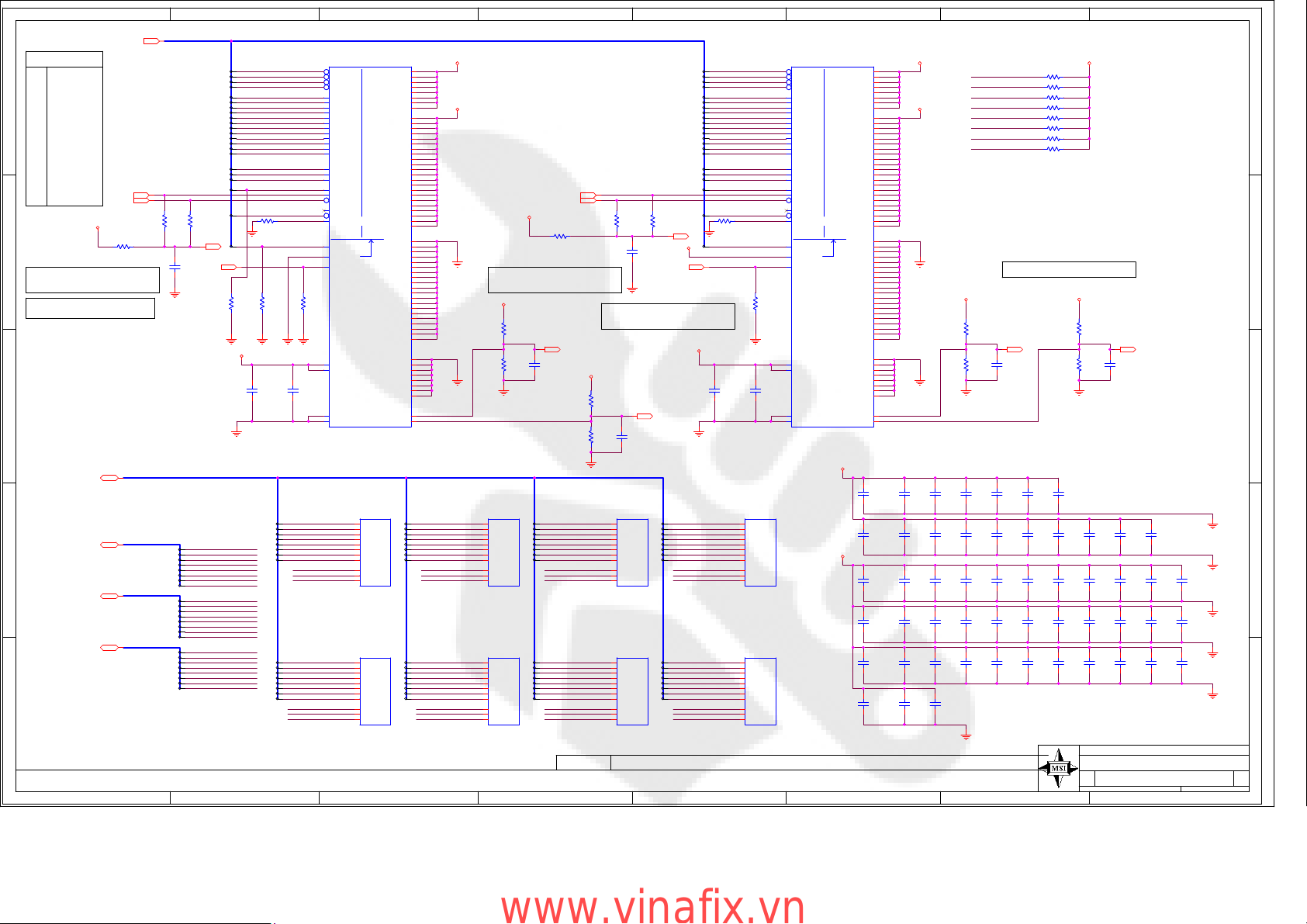

MSI MS-V154 Schematic 1.0

A B C D E F G H

P392-B01 Board

1

P392-B01, G92, 16Mx32 GDDR3 (1200MHz),

DVI-I-DL, DVI-I-DL, HDTVout, 3Way SLI

Table of Contents:

Page 1: Overview

Page 2: PCI Express 1.0

2

Page 3: MEMORY: GPU Partition A/B

Page 4: MEMORY: GPU Partition C/D

Page 5: FBA Partition

Page 6: FBB Partition

Page 7: FBC Partition

Page 8: FBD Partition

Page 9: FrameBuffer Net Rules

Page 10: DACA Interface

Page 11: DACC Interface

Page 12: IFP A/B and C/D Interface

3

Page 13: DACB HDTV Interface

Page 14: Multi-use IO(MIO) Interface

Page 15: MISC: GPIO, I2C, BIOS, PLL, and XTAL

Page 16: SPDIF, Thermal Control & TMDS Backdrive Protection

Page 17: Configuration Straps and Mechanical

Page 18: Power/GND and Decoupling

Page 19: Power Supply: 5V, 2V5

Page 20: Power Supply: 1V2, 1V8

Page 21: Power Supply: FBVDD, FBVDDQ, 8V5

Page 22: Power Supply: NVVDD Regulator

4

Page 23: Power Supply: NVVDD Phase 1, 2

Page 24: Power Supply: NVVDD Phase 3, 4

Page 25: Power Supply: Filter/Detection 12V & 12V_PEX

Page 26: Power Supply: Filter/Isolation of 3V3 & Hybird

5

V154-0A Bason on P392 modify

1.page 10,11 add sline D-SUB

2.page 12 add EMI bridge RESISTOR

3.page 19 modify 5V circuit, add 1V8 circuit

4.page 19 remove 1V2,1V8 circuit

5.page 21 remove FBVDDQ/FBVDD and 8V5 circuir ,modify APM7067N FBVDDQ and 1V2 circuit

6.page 22,23,24 remove NVVDDcircuir ,modify uP6206 NVVDD circuit

7.page 25 remove boost circuit fom PEX_EXT circuit , remove power LED

8.page 26 add power filter 3V3 cap 0.1uF

VARIANT ASSEMBLY

SKU

BASE

B

SKU0001

1

2

<UNDEFINED>

<UNDEFINED>

3

<UNDEFINED>

4

<UNDEFINED>

5

<UNDEFINED>

6

<UNDEFINED>

7

<UNDEFINED>

8

9

<UNDEFINED>

10

<UNDEFINED>

11

<UNDEFINED>

<UNDEFINED>

12

<UNDEFINED>

13

<UNDEFINED>

14

15

<UNDEFINED>

NVPN

600-10392-base-200

600-10392-0001-200

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

P392 - BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

P392 - SKU1

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

1

2

3

4

5

ASSEMBLY P392 - BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C GE

PAGE DETAIL

www.vinafix.vn

Overview

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date:

Date:

Date:

<Doc>

<Doc>

<Doc>

Tuesday, July 22, 2008

Tuesday, July 22, 2008

Tuesday, July 22, 2008

MS-V154

Sheet of

Sheet of

Sheet of

HFDBA

126

126

126

<RevCode>

<RevCode>

<RevCode>

A B C D E F G H

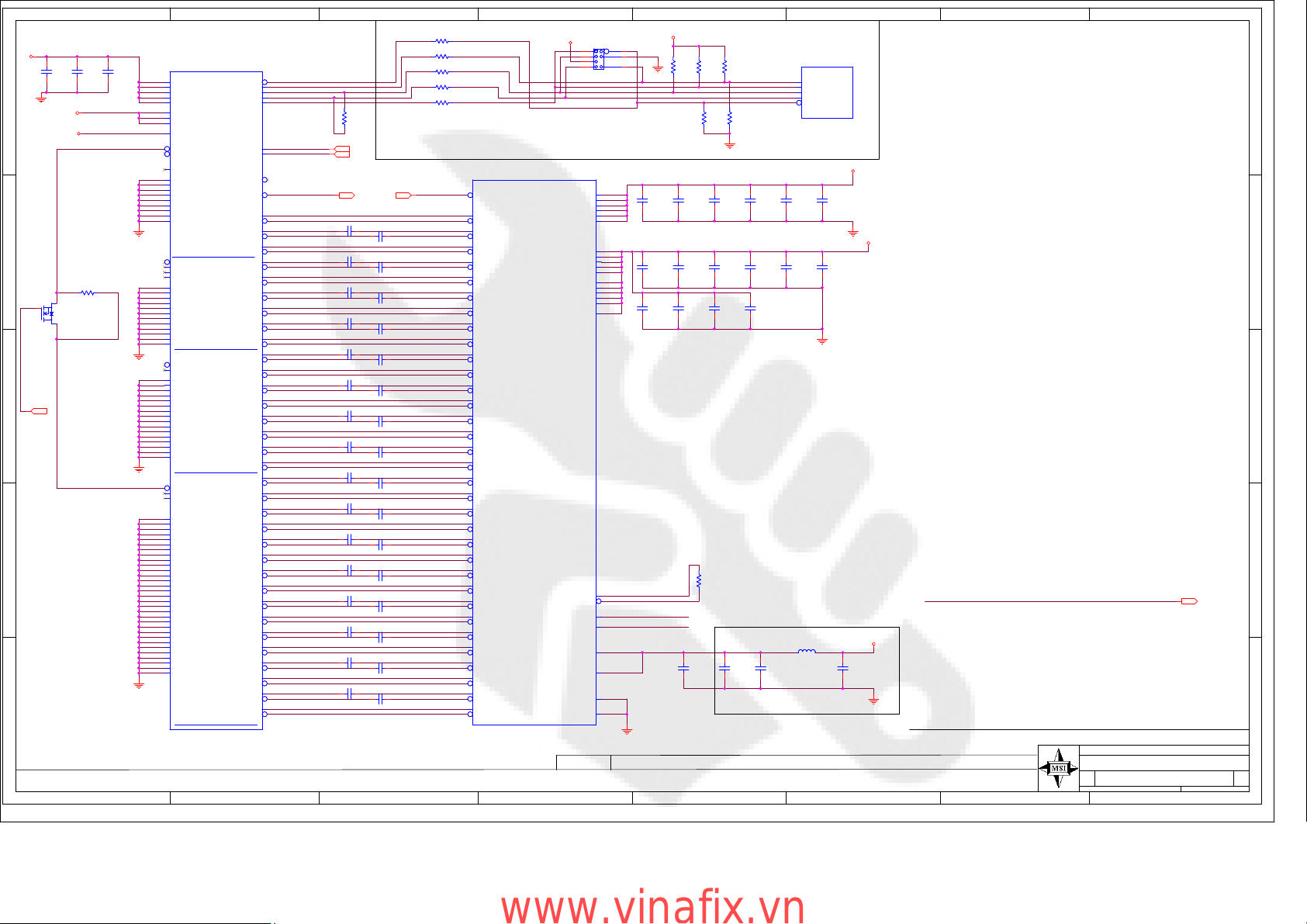

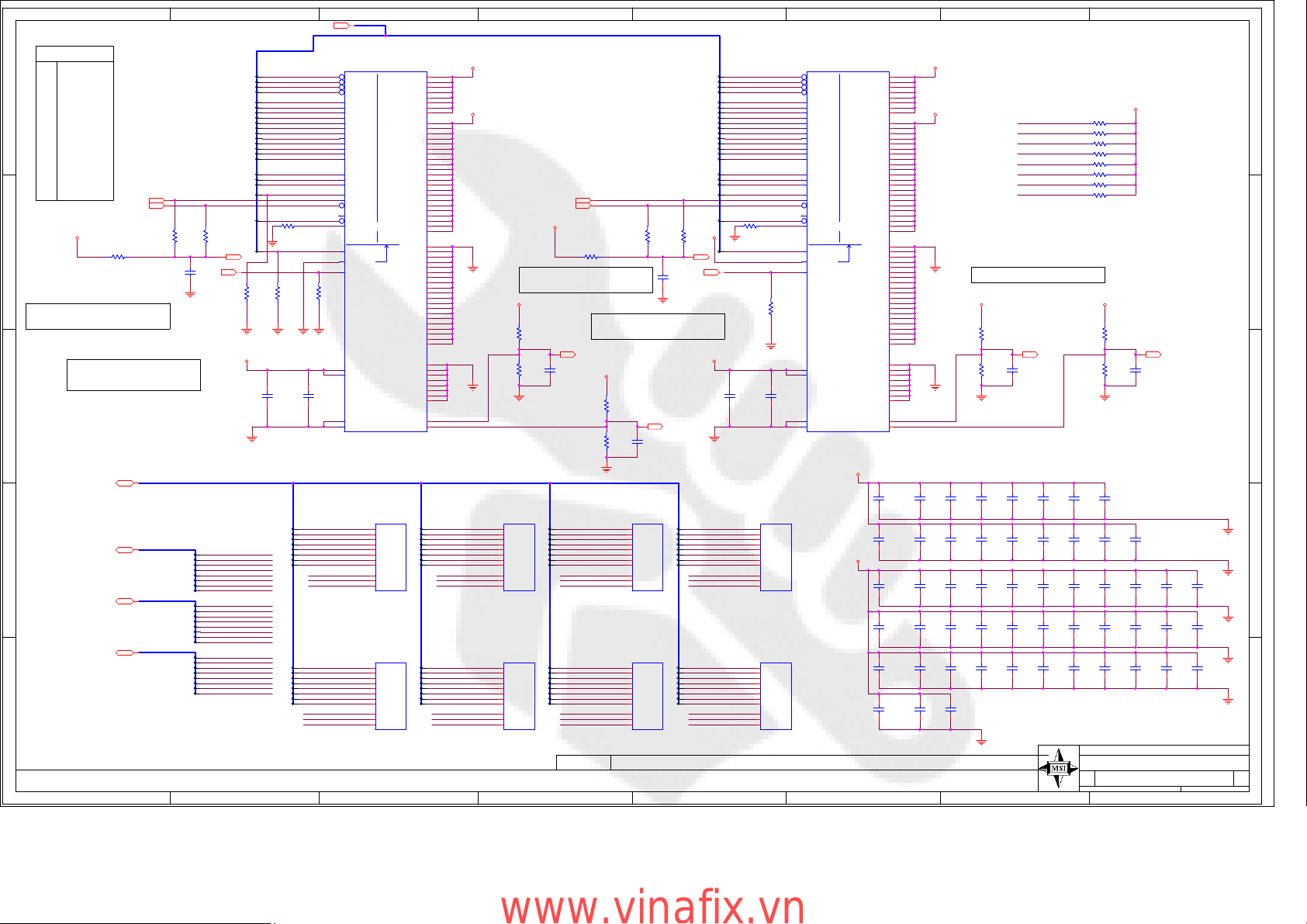

Page2: PCI Express 1.0 JTAG

CN3

12V

1

GND

C23

C23

4.7UF

4.7UF

16V

16V

10%

10%

X7R

X7R

1206

1206

COMMON

COMMON

C22

C22

C20

C20

4.7UF

4.7UF

.1UF

.1UF

16V

16V

16V

16V

10%

10%

10%

10%

X7R

X7R

X7R

X7R

0402

0402

1206

1206

COMMON

COMMON

COMMON

COMMON

3V3

3V3_AUX

PEX_PRSNT1*

2

R719

0R719

0

S

0402 DNI

0402 DNI

5%

5%

(OPT)

2

COMMON

COMMON

SOT23

SOT23

D

+/-20V

+/-20V

Q523

Q523

0.36W@25C

0.36W@25C

0.88A

0.88A

3.5R

3.5R

3

0.22A@31C

0.22A@31C

BSS138

50V

50V

26

PEX_PRSNT2*

3

G

1

1G1D1S

1G1D1S

IN

PEX_REFCLK_EN

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

CN3

CON_X16

CON_X16

COMMON

COMMON

SMCLK

SMDAT

PERST

REFCLK

REFCLK

PERP0

PERN0

PETP0

PETN0

PERP1

PERN1

PETP1

PETN1

PERP2

PERN2

PETP2

PETN2

PERP3

PERN3

PETP3

PETN3

PERP4

PERN4

PETP4

PETN4

PERP5

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PERN8

PETP8

PETN8

PERP9

PERN9

PETP9

PETN9

PERP10

PERN10

PETP10

PETN10

PERP11

PERN11

PETP11

PETN11

PERP12

PERN12

PETP12

PETN12

PERP13

PERN13

PETP13

PETN13

PERP14

PERN14

PETP14

PETN14

PERP15

PERN15

PETP15

PETN15

PEX_TRST*

B9

PEX_TCLK

A5

PEX_TDI

A6

PEX_TDO

A7

PEX_TMS

A8

I2CS_SCL_Q

B5

I2CS_SDA_Q

B6

B11

WAKE

PEX_RST*

A11

PEX_REFCLK

A13

PEX_REFCLK*

A14

PEX_TX0_C

A16

PEX_TX0_C*

A17

PEX_RX0

B14

PEX_RX0*

B15

PEX_TX1_C

A21

PEX_TX1_C*

A22

PEX_RX1

B19

PEX_RX1*

B20

PEX_TX2_C

A25

PEX_TX2_C*

A26

PEX_RX2

B23

PEX_RX2*

B24

PEX_TX3_C

A29

PEX_TX3_C*

A30

PEX_RX3

B27

PEX_RX3*

B28

PEX_TX4_C

A35

PEX_TX4_C*

A36

PEX_RX4

B33

PEX_RX4*

B34

PEX_TX5_C

A39

PEX_TX5_C*

A40

PEX_RX5

B37

PEX_RX5*

B38

PEX_TX6_C

A43

PEX_TX6_C*

A44

PEX_RX6

B41

PEX_RX6*

B42

PEX_TX7_C

A47

PEX_TX7_C*

A48

PEX_RX7

B45

PEX_RX7*

B46

PEX_TX8_C

A52

PEX_TX8_C*

A53

PEX_RX8

B50

PEX_RX8*

B51

PEX_TX9_C

A56

PEX_TX9_C*

A57

PEX_RX9

B54

PEX_RX9*

B55

PEX_TX10_C

A60

PEX_TX10_C*

A61

PEX_RX10

B58

PEX_RX10*

B59

PEX_TX11_C

A64

PEX_TX11_C*

A65

PEX_RX11

B62

PEX_RX11*

B63

PEX_TX12_C

A68

PEX_TX12_C*

A69

PEX_RX12

B66

PEX_RX12*

B67

PEX_TX13_C

A72

PEX_TX13_C*

A73

PEX_RX13

B70

PEX_RX13*

B71

PEX_TX14_C

A76

PEX_TX14_C*

A77

PEX_RX14

B74

PEX_RX14*

B75

PEX_TX15_C

A80

PEX_TX15_C*

A81

PEX_RX15

B78

PEX_RX15*

B79

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

C959

C947

C938

C927

C915

C895

C882

C865

C848

C815

C779

C754

C715

C697

C684

C680

IN

IN

OUT

0402 10V

0402 10V

X5R

X5R

0402 10V

0402 10V

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

0402

0402

X5R

X5R

R712

R712

0

0

5%

5%

0402

0402

DNI

DNI

(OPT)

26

26

2,26

.1UFC959

.1UF

C956

10%

10%

0402

0402

.1UFC947

.1UF

C943

10%

10%

0402

0402

.1UFC938

.1UF

C928

10V

10V

10%

10%

0402

0402

.1UFC927

.1UF

C926

10V

10V

10%

10%

0402 10V

0402 10V

.1UFC915

.1UF

C909

10V

10V

10%

10%

0402 10V

0402 10V

.1UFC895

.1UF

C888

10V

10V

10%

10%

0402

0402

.1UFC882

.1UF

C879

10V

10V

10%

10%

.1UFC865

.1UF

C861

10V

10V

10%

10%

0402

0402

.1UFC848

.1UF

C840

10V

10V

10%

10%

0402 10V

0402 10V

.1UFC815

.1UF

C811

10V

10V

10%

10%

0402 10V

0402 10V

.1UFC779

.1UF

C777

10V

10V

10%

10%

0402 10V

0402 10V

.1UFC754

.1UF

C741

10V

10V

10%

10%

0402 10V

0402 10V

.1UFC715

.1UF

C710

10V

10V

10%

10%

0402

0402

.1UFC697

.1UF

C693

10V

10V

10%

10%

0402

0402

.1UFC684

.1UF

C681

10V

10V

10%

10%

0402

0402

.1UFC680

.1UF

C678

10V

10V

10%

10%

0402

0402

GPU_RST*

16,26

IN

PEX_TX0

.1UFC956

.1UF

PEX_TX0*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX1

.1UFC943

.1UF

PEX_TX1*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX2

.1UFC928

.1UF

PEX_TX2*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX3

.1UFC926

.1UF

PEX_TX3*

10%

10%

COMMON

COMMON

X5R

X5R

PEX_TX4

.1UFC909

.1UF

PEX_TX4*

10%

10%

COMMON

COMMON

X5R

X5R

PEX_TX5

.1UFC888

.1UF

PEX_TX5*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX6

.1UFC879

.1UF

PEX_TX6*

10%

10%

10V0402

10V0402

COMMON

COMMON

X5R

X5R

PEX_TX7

.1UFC861

.1UF

PEX_TX7*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX8

.1UFC840

.1UF

PEX_TX8*

10%

10%

COMMON

COMMON

X5R

X5R

PEX_TX9

.1UFC811

.1UF

PEX_TX9*

10%

10%

COMMON

COMMON

X5R

X5R

PEX_TX10

.1UFC777

.1UF

PEX_TX10*

10%

10%

COMMON

COMMON

X5R

X5R

PEX_TX11

.1UFC741

.1UF

PEX_TX11*

10%

10%

COMMON

COMMON

X5R

X5R

PEX_TX12

.1UFC710

.1UF

PEX_TX12*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX13

.1UFC693

.1UF

PEX_TX13*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX14

.1UFC681

.1UF

PEX_TX14*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX15

.1UFC678

.1UF

PEX_TX15*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

B1

+12V

B2

+12V

A2

+12V

A3

+12V

B3

+12V/RSVD

B8

+3V3

A9

+3V3

A10

+3V3

B10

+3V3AUX

A1

PRSNT1

B17

PRSNT2

B12

RSVD

B4

GND

A4

GND

B7

GND

A12

GND

B13

GND

A15

GND

B16

GND

B18

GND

A18

GND

GND

B31

PRSNT2

A19

RSVD

B30

RSVD

A32

RSVD

A20

GND

B21

GND

B22

GND

A23

GND

A24

GND

B25

GND

B26

GND

A27

GND

A28

GND

B29

GND

A31

GND

B32

GND

GND

B48

PRSNT2

A33

RSVD

A34

GND

B35

GND

B36

GND

A37

GND

A38

GND

B39

GND

B40

GND

A41

GND

A42

GND

B43

GND

B44

GND

A45

GND

A46

GND

B47

GND

B49

GND

A49

GND

GND

B81

PRSNT2

A50

RSVD

B82

RSVD

A51

GND

B52

GND

B53

GND

A54

GND

A55

GND

B56

GND

B57

GND

A58

GND

A59

GND

B60

GND

B61

GND

A62

GND

A63

GND

B64

GND

B65

GND

A66

GND

A67

GND

B68

GND

B69

GND

A70

GND

A71

GND

B72

GND

B73

GND

A74

GND

A75

GND

B76

GND

B77

GND

A78

GND

A79

GND

B80

GND

A82

GND

GND

END OF X1

END OF X1

END OF X4

END OF X4

END OF X8

END OF X8

END OF X16

END OF X16

TRST* JTAG1

TCLK JTAG2

TDI JTAG3

TDO JTAG4

TMS JTAG5

C GE

R77

04025%DNI

04025%DNI

R693

04025%DNI

04025%DNI

R75

04025%DNI

04025%DNI

R688

04025%DNI

04025%DNI

R678

0402 DNI

0402 DNI

(OPT)

(OPT)

(OPT)

(OPT)

5%

5%

(OPT)

0R77

0

0R693

0

0R75

0

0R688

0

0R678

0

AR9

AK10

AL10

AM11

AM10

AP9

AP10

AN10

AN11

AR10

AR11

AN12

AM12

AT11

AT12

AL12

AK12

AP12

AP13

AM14

AM13

AR13

AR14

AN13

AN14

AT14

AT15

AN15

AM15

AP15

AP16

AL15

AK15

AR16

AR17

AM16

AN16

AT17

AT18

AN17

AN18

AP18

AP19

AM18

AM17

AR19

AR20

AL18

AK18

AT20

AT21

AM19

AN19

AP21

AP22

AN20

AN21

AR22

AR23

AM21

AM20

AT23

AT24

AL21

AK21

AR24

AR25

JTAG_TRST*

JTAG_TCLK

JTAG_TDI

JTAG_TDO

JTAG_TMS

G1A

G1A

BGA_1148_P100_375X375_G3_256B

BGA_1148_P100_375X375_G3_256B

COMMON

COMMON

1/24 PCI EXPRESS

1/24 PCI EXPRESS

PEX_RST

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_RX0

PEX_RX0

PEX_TX1

PEX_TX1

PEX_RX1

PEX_RX1

PEX_TX2

PEX_TX2

PEX_RX2

PEX_RX2

PEX_TX3

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX4

PEX_TX4

PEX_RX4

PEX_RX4

PEX_TX5

PEX_TX5

PEX_RX5

PEX_RX5

PEX_TX6

PEX_TX6

PEX_RX6

PEX_RX6

PEX_TX7

PEX_TX7

PEX_RX7

PEX_RX7

PEX_TX8

PEX_TX8

PEX_RX8

PEX_RX8

PEX_TX9

PEX_TX9

PEX_RX9

PEX_RX9

PEX_TX10

PEX_TX10

PEX_RX10

PEX_RX10

PEX_TX11

PEX_TX11

PEX_RX11

PEX_RX11

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX14

PEX_TX14

PEX_RX14

PEX_RX14

PEX_TX15

PEX_TX15

PEX_RX15

PEX_RX15

PEX_TEST_PLL_CLK_OUT

PEX_TEST_PLL_CLK_OUT

J501

J501

FEMALE

FEMALE

1.274MM

1.274MM

0

0

(OPT)

3V3_F

CON_HDR_002X004_TH_ST_F_PI050_K

CON_HDR_002X004_TH_ST_F_PI050_K

DNI

DNI

TMS2TRST*

1

TDI4GND

3

KEY

KEY

VCC

5

TDO8TCK

7

AH21

PEX_IOVDD

AJ21

PEX_IOVDD

AH22

PEX_IOVDD

AJ22

PEX_IOVDD

AH23

PEX_IOVDD

AJ23

PEX_IOVDD

AH16

PEX_IOVDDQ

AF17

PEX_IOVDDQ

AH17

PEX_IOVDDQ

AF18

PEX_IOVDDQ

AH18

PEX_IOVDDQ

AF19

PEX_IOVDDQ

AH19

PEX_IOVDDQ

AE20

PEX_IOVDDQ

AF20

PEX_IOVDDQ

AH20

PEX_IOVDDQ

AJ20

PEX_IOVDDQ

AM9

AN9

AK19

RFU

AK20

RFU

AE15

PEX_PLLAVDD

AE17

PEX_PLLDVDD

AF15

PEX_PLLAGND

AE16

PEX_PLLDGND

ASSEMBLY P392 - BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

PAGE DETAIL

PCI Express 1.0

GND

C759

C759

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C775

C775

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C776

C776

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

PEX_TEST_PLL_CLK_OUT Termination = 200ohm

PEX_PLL_CLK_OUT

PEX_PLL_CLK_OUT*

SNN_PEXCAL_PD_VDDQ

SNN_PEXCAL_PD_GND

GND

3V3_F

R683

R683

10K

10K

5%

5%

0402

0402

COMMON

COMMON

PEX_PLLAVDD

C753

C753

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C798

C798

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C800

C800

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

NEAR PAD

NEAR PAD

C816

C816

.1UF

.1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

R681

R681

10K

10K

5%

5%

0402

0402

COMMON

COMMON

R672

R672

10K

10K

5%

5%

0402

0402

COMMON

COMMON

GND

C752

C752

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C778

C778

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C792

C792

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

R643

R643

200

200

PLACE ON BACKSIDE OF BOARD

PLACE ON BACKSIDE OF BOARD

5%

5%

0402

0402

COMMON

COMMON

Place components within 750 mils from pad

Place components within 750 mils from pad

R691

R691

180

180

5%

5%

0402

0402

COMMON

COMMON

C818

C818

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

R692

R692

270

270

5%

5%

0402

0402

COMMON

COMMON

C735

C735

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C809

C809

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C758

C758

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C60

C60

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

G1B

G1B

BGA_1148_P100_375X375_G3_256B

BGA_1148_P100_375X375_G3_256B

COMMON

COMMON

23/24 JTAG

23/24 JTAG

AK6

JTAG_TCLK

AL8

JTAG_TMS

AL7

JTAG_TDI

AK7

JTAG_TDO

AL9

JTAG_TRST

C734

C734

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

C732

C732

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

LB503

IND_SMD_0402COMMON

IND_SMD_0402COMMON

1

1V2

C716

C716

10UF

10UF

6.3V

6.3V

20%

20%

X5R

X5R

0805

0805

COMMON

COMMON

1V2

GND

C824

C824

10UF

10UF

6.3V

6.3V

20%

20%

X5R

X5R

0805

0805

COMMON

COMMON

GND

2

3

4

PEX_RST*

C803

C803

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

1V2

GND

10nHLB503

10nH

50OHM3

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

Custom

<Doc>

Custom

<Doc>

Custom

Date:

Thursday, July 24, 2008

Date:

Thursday, July 24, 2008

Date:

Thursday, July 24, 2008

OUT

Sheet of

Sheet of

Sheet of

HFDBA

2,26

226

226

226

5

<RevCode>

<RevCode>

<RevCode>

www.vinafix.vn

A B C D E F G H

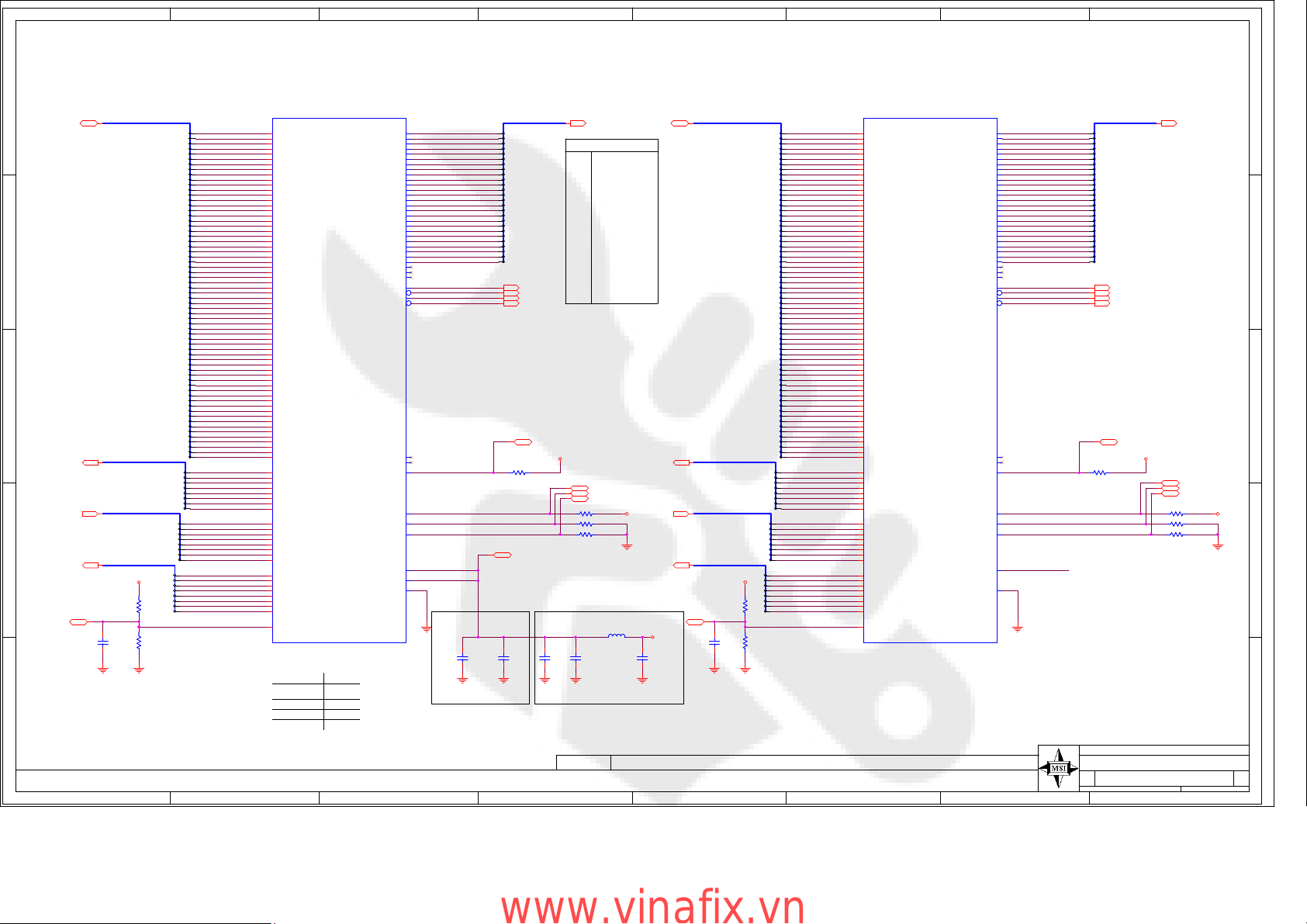

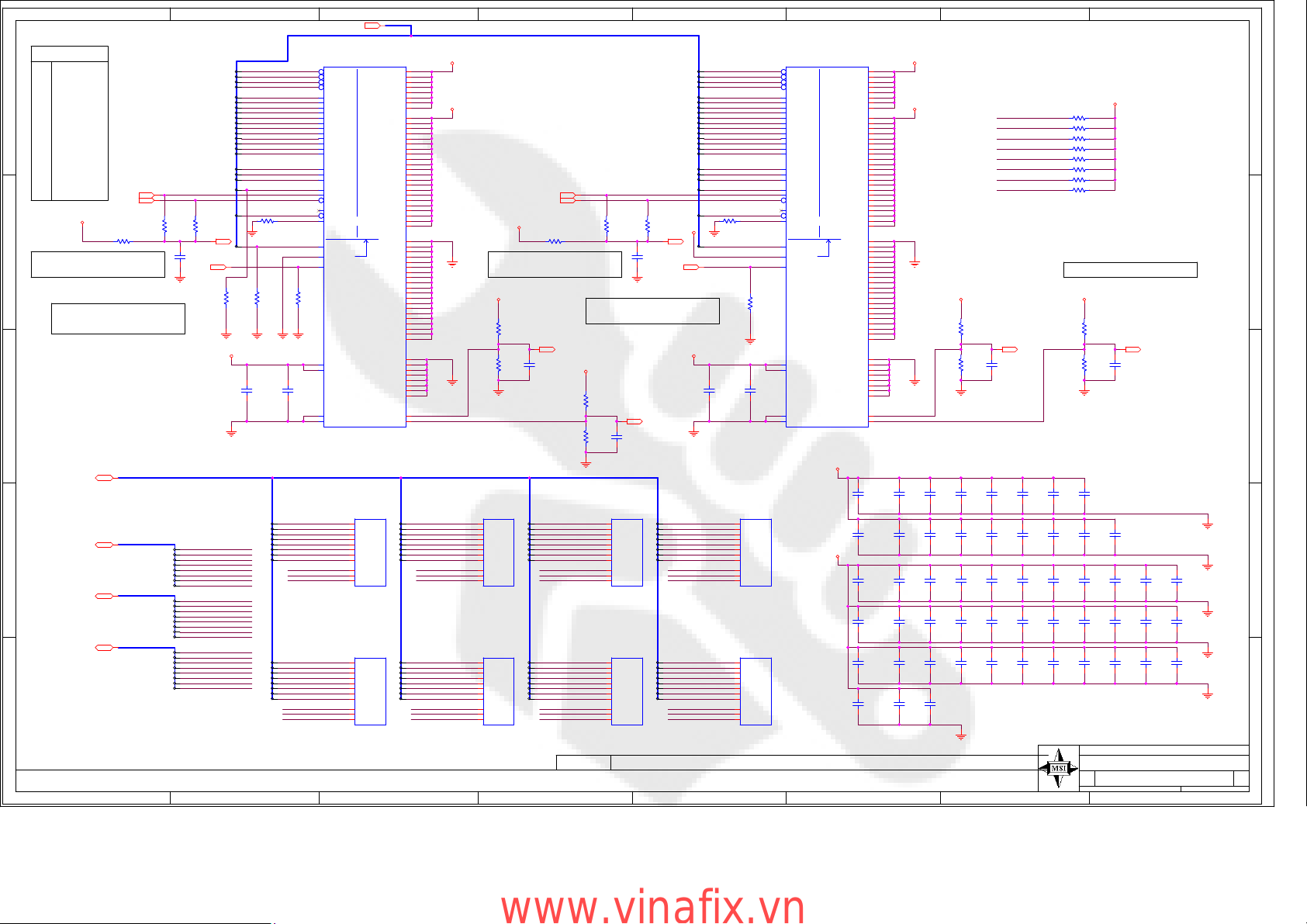

Page3: MEMORY: GPU Partition A/B

1

FBA_D[63..0]

5,9

BI

2

3

5,9 FBA_DQM[7..0]

OUT

5,9 FBA_DQS_RN[7..0]

IN

4

5

5,9 FBA_DQS_WP[7..0]

OUT

9

BI

C695

C695

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

GND GND

FBVDDQ

R619

R619

549

549

1%

1%

0402

0402

COMMON

COMMON

R618

R618

1.33K

1.33K

1%

1%

0402

0402

COMMON

COMMON

G1C

G1C

BGA_1148_P100_375X375_G3_256B

BGA_1148_P100_375X375_G3_256B

COMMON

COMMON

2/24 MEM_A

FBA_D0

0

FBA_D1

1

FBA_D2

2

FBA_D3

3

FBA_D4

4

FBA_D5

5

FBA_D6

6

FBA_D7

7

FBA_D8

8

FBA_D9

9

FBA_D10

10

FBA_D11

11

FBA_D12

12

FBA_D13

13

FBA_D14

14

FBA_D15

15

FBA_D16

16

FBA_D17

17

FBA_D18

18

FBA_D19

19

FBA_D20

20

FBA_D21

21

FBA_D22

22

FBA_D23

23

FBA_D24

24

FBA_D25

25

FBA_D26

26

FBA_D27

27

FBA_D28

28

FBA_D29

29

FBA_D30

30

FBA_D31

31

FBA_D32

32

FBA_D33

33

FBA_D34

34

FBA_D35

35

FBA_D36

36

FBA_D37

37

FBA_D38

38

FBA_D39

39

FBA_D40

40

FBA_D41

41

FBA_D42

42

FBA_D43

43

FBA_D44

44

FBA_D45

45

FBA_D46

46

FBA_D47

47

FBA_D48

48

FBA_D49

49

FBA_D50

50

FBA_D51

51

FBA_D52

52

FBA_D53

53

FBA_D54

54

FBA_D55

55

FBA_D56

56

FBA_D57

57

FBA_D58

58

FBA_D59

59

FBA_D60

60

FBA_D61

61

FBA_D62

62

FBA_D63

63

FBA_DQM0

0

FBA_DQM1

1

FBA_DQM2

2

FBA_DQM3

3

FBA_DQM4

4

FBA_DQM5

5

FBA_DQM6

6

FBA_DQM7

7

FBA_DQS_RN0

0

FBA_DQS_RN1

1

FBA_DQS_RN2

2

FBA_DQS_RN3

3

FBA_DQS_RN4

4

FBA_DQS_RN5

5

FBA_DQS_RN6

6

FBA_DQS_RN7

7

FBA_DQS_WP0

0

FBA_DQS_WP1

1

FBA_DQS_WP2

2

FBA_DQS_WP3

3

FBA_DQS_WP4

4

FBA_DQS_WP5

5

FBA_DQS_WP6

6

FBA_DQS_WP7

7

FB_VREF1

2/24 MEM_A

AH35

FBAD0

AH36

FBAD1

AH34

FBAD2

AJ34

FBAD3

AK36

FBAD4

AJ36

FBAD5

AK34

FBAD6

AL34

FBAD7

AH32

FBAD8

AK33

FBAD9

AJ33

FBAD10

AH33

FBAD11

AL33

FBAD12

AN32

FBAD13

AN33

FBAD14

AN31

FBAD15

AE32

FBAD16

AF30

FBAD17

AF32

FBAD18

AE30

FBAD19

AE31

FBAD20

AC30

FBAD21

AC32

FBAD22

AD30

FBAD23

AG36

FBAD24

AG34

FBAD25

AG35

FBAD26

AF36

FBAD27

AD36

FBAD28

AD34

FBAD29

AD35

FBAD30

AE34

FBAD31

AP36

FBAD32

AN35

FBAD33

AM34

FBAD34

AP35

FBAD35

AP34

FBAD36

AP33

FBAD37

AT34

FBAD38

AR34

FBAD39

AM22

FBAD40

AM25

FBAD41

AN26

FBAD42

AN24

FBAD43

AK24

FBAD44

AL22

FBAD45

AK23

FBAD46

AM23

FBAD47

AT32

FBAD48

AT33

FBAD49

AR33

FBAD50

AP31

FBAD51

AR30

FBAD52

AT30

FBAD53

AP30

FBAD54

AT29

FBAD55

AP26

FBAD56

AP27

FBAD57

AT25

FBAD58

AP25

FBAD59

AR28

FBAD60

AP28

FBAD61

AT28

FBAD62

AP29

FBAD63

AK35

FBADQM0

AM33

FBADQM1

AF33

FBADQM2

AF34

FBADQM3

AN34

FBADQM4

AM24

FBADQM5

AP32

FBADQM6

AR27

FBADQM7

AL35

FBADQS_RN0

AK32

FBADQS_RN1

AG33

FBADQS_RN2

AE36

FBADQS_RN3

AM36

FBADQS_RN4

AN22

FBADQS_RN5

AR31

FBADQS_RN6

AT27

FBADQS_RN7

AL36

FBADQS_WP0

AL32

FBADQS_WP1

AG32

FBADQS_WP2

AE35

FBADQS_WP3

AN36

FBADQS_WP4

AN23

FBADQS_WP5

AT31

FBADQS_WP6

AT26

FBADQS_WP7

J29

FB_VREF1

CALIBRATION PIN

FB_CALx_PD_VDDQ

FB_CALx_PU_GND

FB_CALx_TERM_GND

VREF RATIO 0.7 FBVDDQ

DDR3

60

40

40

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_DEBUG

FBCAL0_PD_VDDQ

FBCAL0_PU_GND

FBCAL0_TERM_GND

FBA_DLLAVDD

FBA_PLLAVDD

FBA_PLLGND

FBA_CMD0

AK28

FBA_CMD1

AK29

FBA_CMD2

AN30

FBA_CMD3

AM27

FBA_CMD4

AN28

FBA_CMD5

AL29

FBA_CMD6

AM30

FBA_CMD7

AJ31

FBA_CMD8

AK31

FBA_CMD9

AH31

FBA_CMD10

AK25

FBA_CMD11

AM26

FBA_CMD12

AL31

FBA_CMD13

AN29

FBA_CMD14

AK27

FBA_CMD15

AK26

FBA_CMD16

AN27

FBA_CMD17

AL25

FBA_CMD18

AJ30

FBA_CMD19

AM31

FBA_CMD20

AH30

FBA_CMD21

AL30

FBA_CMD22

AH29

FBA_CMD23

AL28

FBA_CMD24

AH28

FBA_CMD25

AM28

AG30

AG28

AF28

FBA_CLK0

AH26

FBA_CLK0*

AH27

FBA_CLK1

AJ29

FBA_CLK1*

AJ28

AJ24

RFU

AH24

RFU

FBA_DEBUG

AH25

FB_CAL_PD_VDDQ0

J28

FB_CAL_PU_GND0

H28

FB_CAL_TERM_GND0

H29

AC29

FBAB_PLLAVDD

AD29

AE29

GND

Place components as close as possible to pad

Place components as close as possible to pad

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

5,9

OUT

5,9

OUT

5,9

OUT

5,9

OUT

9

BI

R627 60.4

R627 60.4

04021%DNI

04021%DNI

(OPT) (OPT)

9

BI

C711

C711

C708

C708

.1UF

.1UF

.1UF

.1UF

6.3V

6.3V

10V

10V

10%

10%

10%

10%

X5R

X5R

X5R

X5R

0402

0402

0402

0402

COMMON

COMMON

COMMON

GND GND GND

COMMON

OUT

136BGA CMD Mapping

CMD

CMD0

CMD2

CMD3

CMD4

CMD5

CMD6

CMD7

CMD8

CMD9

CMD10

CMD11

CMD12

CMD13

CMD14

CMD15

CMD16

CMD18

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25

CMD26

CMD27

CMD28

FBVDDQ

BI

BI

BI

R623 60.4

R623 60.4

0402

0402

1%

1%

R620 40.2

R620 40.2

0402

0402

1%

1%

R617 40.2

R617 40.2

0402

0402

1%

1%

C679

C679

C676

C676

4.7UF

4.7UF

1UF

1UF

6.3V

6.3V

6.3V

6.3V

10%

10%

10%

10%

X5R

X5R

X5R

X5R

0402

0402

0603

0603

COMMON

COMMON

COMMON

COMMON

GND

Place components within 750 mils of pad

Place components within 750 mils of pad

5,9FBA_CMD[25..0]

ADDR

A<4>

RAS*CMD1

A<5>

BA1

A<2>

A<4>

A<3>

BA2

CS0*

A<11>

CAS*

WE*

BA0

A<5>

A<12>

RST

A<7>

A<10>CMD17

CKE

A<0>

A<9>

A<6>

A<2>

A<8>

A<3>

A<1>

A<13>

N/A

N/A

9

9

9

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

LB501

LB501

IND_SMD_0402

IND_SMD_0402

FBVDDQ

GND

240R@100MHz

240R@100MHz

COMMON

COMMON

GND

6,9 FBB_D[63..0]

BI

6,9 FBB_DQM[7..0]

OUT

6,9 FBB_DQS_RN[7..0]

IN

6,9 FBB_DQS_WP[7..0]

OUT

9

BI

1V2

C677

C677

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

GND GND

C712

C712

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

FBVDDQ

R631

R631

549

549

1%

1%

0402

0402

COMMON

COMMON

R630

R630

1.33K

1.33K

1%

1%

0402

0402

COMMON

COMMON

FBB_D0

0

FBB_D1

1

FBB_D2

2

FBB_D3

3

FBB_D4

4

FBB_D5

5

FBB_D6

6

FBB_D7

7

FBB_D8

8

FBB_D9

9

FBB_D10

10

FBB_D11

11

FBB_D12

12

FBB_D13

13

FBB_D14

14

FBB_D15

15

FBB_D16

16

FBB_D17

17

FBB_D18

18

FBB_D19

19

FBB_D20

20

FBB_D21

21

FBB_D22

22

FBB_D23

23

FBB_D24

24

FBB_D25

25

FBB_D26

26

FBB_D27

27

FBB_D28

28

FBB_D29

29

FBB_D30

30

FBB_D31

31

FBB_D32

32

FBB_D33

33

FBB_D34

34

FBB_D35

35

FBB_D36

36

FBB_D37

37

FBB_D38

38

FBB_D39

39

FBB_D40

40

FBB_D41

41

FBB_D42

42

FBB_D43

43

FBB_D44

44

FBB_D45

45

FBB_D46

46

FBB_D47

47

FBB_D48

48

FBB_D49

49

FBB_D50

50

FBB_D51

51

FBB_D52

52

FBB_D53

53

FBB_D54

54

FBB_D55

55

FBB_D56

56

FBB_D57

57

FBB_D58

58

FBB_D59

59

FBB_D60

60

FBB_D61

61

FBB_D62

62

FBB_D63

63

FBB_DQM0

0

FBB_DQM1

1

FBB_DQM2

2

FBB_DQM3

3

FBB_DQM4

4

FBB_DQM5

5

FBB_DQM6

6

FBB_DQM7

7

FBB_DQS_RN0

0

FBB_DQS_RN1

1

FBB_DQS_RN2

2

FBB_DQS_RN3

3

FBB_DQS_RN4

4

FBB_DQS_RN5

5

FBB_DQS_RN6

6

FBB_DQS_RN7

7

FBB_DQS_WP0

0

FBB_DQS_WP1

1

FBB_DQS_WP2

2

FBB_DQS_WP3

3

FBB_DQS_WP4

4

FBB_DQS_WP5

5

FBB_DQS_WP6

6

FBB_DQS_WP7

7

FB_VREF2

G1D

G1D

BGA_1148_P100_375X375_G3_256B

BGA_1148_P100_375X375_G3_256B

COMMON

COMMON

3/24 MEM_B

3/24 MEM_B

G36

FBBD0

G35

FBBD1

H36

FBBD2

H34

FBBD3

J35

FBBD4

J34

FBBD5

K34

FBBD6

K35

FBBD7

J31

FBBD8

K32

FBBD9

J30

FBBD10

H30

FBBD11

L32

FBBD12

K30

FBBD13

M31

FBBD14

L30

FBBD15

G31

FBBD16

J32

FBBD17

J33

FBBD18

F33

FBBD19

H31

FBBD20

E33

FBBD21

F31

FBBD22

F32

FBBD23

F35

FBBD24

G34

FBBD25

F36

FBBD26

F34

FBBD27

C35

FBBD28

D34

FBBD29

C36

FBBD30

D35

FBBD31

N35

FBBD32

M34

FBBD33

L34

FBBD34

N36

FBBD35

P36

FBBD36

P34

FBBD37

R36

FBBD38

R34

FBBD39

AC33

FBBD40

Y33

FBBD41

Y30

FBBD42

AB30

FBBD43

AA32

FBBD44

AD32

FBBD45

AD33

FBBD46

AA33

FBBD47

T36

FBBD48

R35

FBBD49

T34

FBBD50

U36

FBBD51

W35

FBBD52

U34

FBBD53

V34

FBBD54

W36

FBBD55

AC36

FBBD56

AA36

FBBD57

AC34

FBBD58

AB34

FBBD59

AA35

FBBD60

Y34

FBBD61

Y36

FBBD62

W34

FBBD63

J36

FBBDQM0

M32

FBBDQM1

H33

FBBDQM2

E34

FBBDQM3

N34

FBBDQM4

Y32

FBBDQM5

T35

FBBDQM6

AA34

FBBDQM7

L36

FBBDQS_RN0

K33

FBBDQS_RN1

G32

FBBDQS_RN2

E36

FBBDQS_RN3

M36

FBBDQS_RN4

AB32

FBBDQS_RN5

V35

FBBDQS_RN6

AB35

FBBDQS_RN7

K36

FBBDQS_WP0

L33

FBBDQS_WP1

G33

FBBDQS_WP2

D36

FBBDQS_WP3

M35

FBBDQS_WP4

AB31

FBBDQS_WP5

V36

FBBDQS_WP6

AB36

FBBDQS_WP7

J27

FB_VREF2

FBB_CMD27

FBB_CMD28

FBCAL1_PD_VDDQ

FBCAL1_PU_GND

FBCAL1_TERM_GND

FBB_PLLVDD_NC

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD7

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CLK0

FBB_CLK0

FBB_CLK1

FBB_CLK1

FBB_DEBUG

FBB_PLLGND

1

6,9FBB_CMD[25..0]

FBB_CMD0

P33

FBB_CMD1

N33

FBB_CMD2

R31

FBB_CMD3

U33

FBB_CMD4

V30

FBB_CMD5

T33

FBB_CMD6

T30

FBB_CMD7

N32

FBB_CMD8

R32

FBB_CMD9

P32

FBB_CMD10

U32

FBB_CMD11

U30

FBB_CMD12

P30

FBB_CMD13

V31

FBB_CMD14

T28

FBB_CMD15

W30

FBB_CMD16

V32

FBB_CMD17

T32

FBB_CMD18

N30

FBB_CMD19

P28

FBB_CMD20

P29

FBB_CMD21

U29

FBB_CMD22

N28

FBB_CMD23

R30

FBB_CMD24

M30

FBB_CMD25

T29

N29

AA30

Y29

FBB_CLK0

M28

FBB_CLK0*

L28

FBB_CLK1

W31

FBB_CLK1*

W32

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

6,9

OUT

6,9

OUT

6,9

OUT

6,9

OUT

OUT

2

3

9

BI

R28

RFU

K29

RFU

FBB_DEBUG

C34

FB_CAL_PD_VDDQ1

H27

FB_CAL_PU_GND1

H26

FB_CAL_TERM_GND1

J26

SNN_FBB_PLLVDD

AB28

R615

04021%DNI

04021%DNI

FBVDDQ

60.4R615

60.4

BI

BI

BI

R633 60.4

R633 60.4

0402

0402

1%

1%

R635 40.2

R635 40.2

0402

0402

1%

1%

R636 40.2

R636 40.2

0402

0402

1%

1%

9

9

9

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

FBVDDQ

GND

4

AC28

GND

5

ASSEMBLY P392 - BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C GE

PAGE DETAIL

www.vinafix.vn

MEMORY: GPU Partition A/B

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

Custom

<Doc>

Custom

<Doc>

Date:

Date:

Date:

Custom

Thursday, July 24, 2008

Thursday, July 24, 2008

Thursday, July 24, 2008

Sheet of

Sheet of

Sheet of

HFDBA

326

326

326

<RevCode>

<RevCode>

<RevCode>

A B C D E F G H

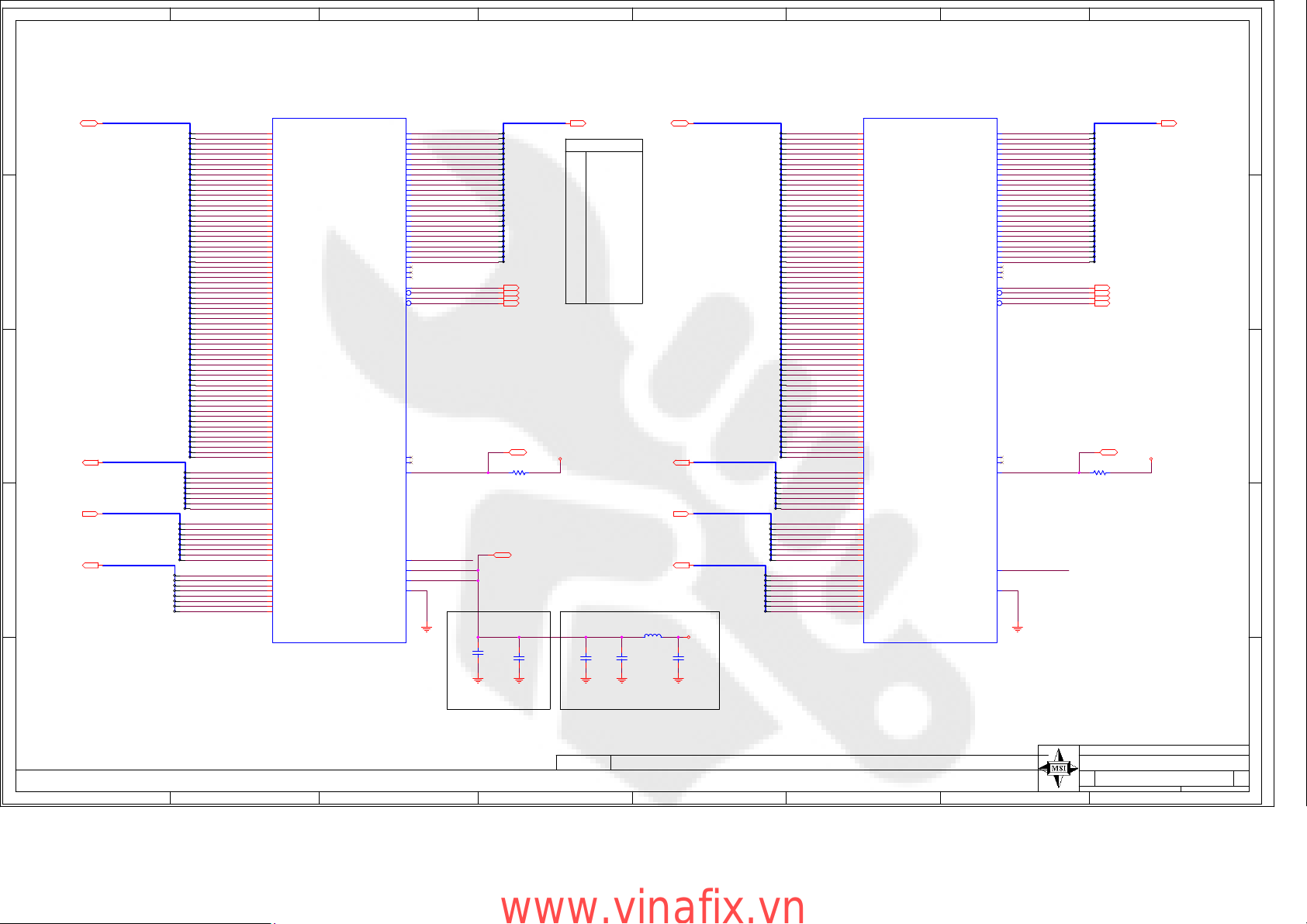

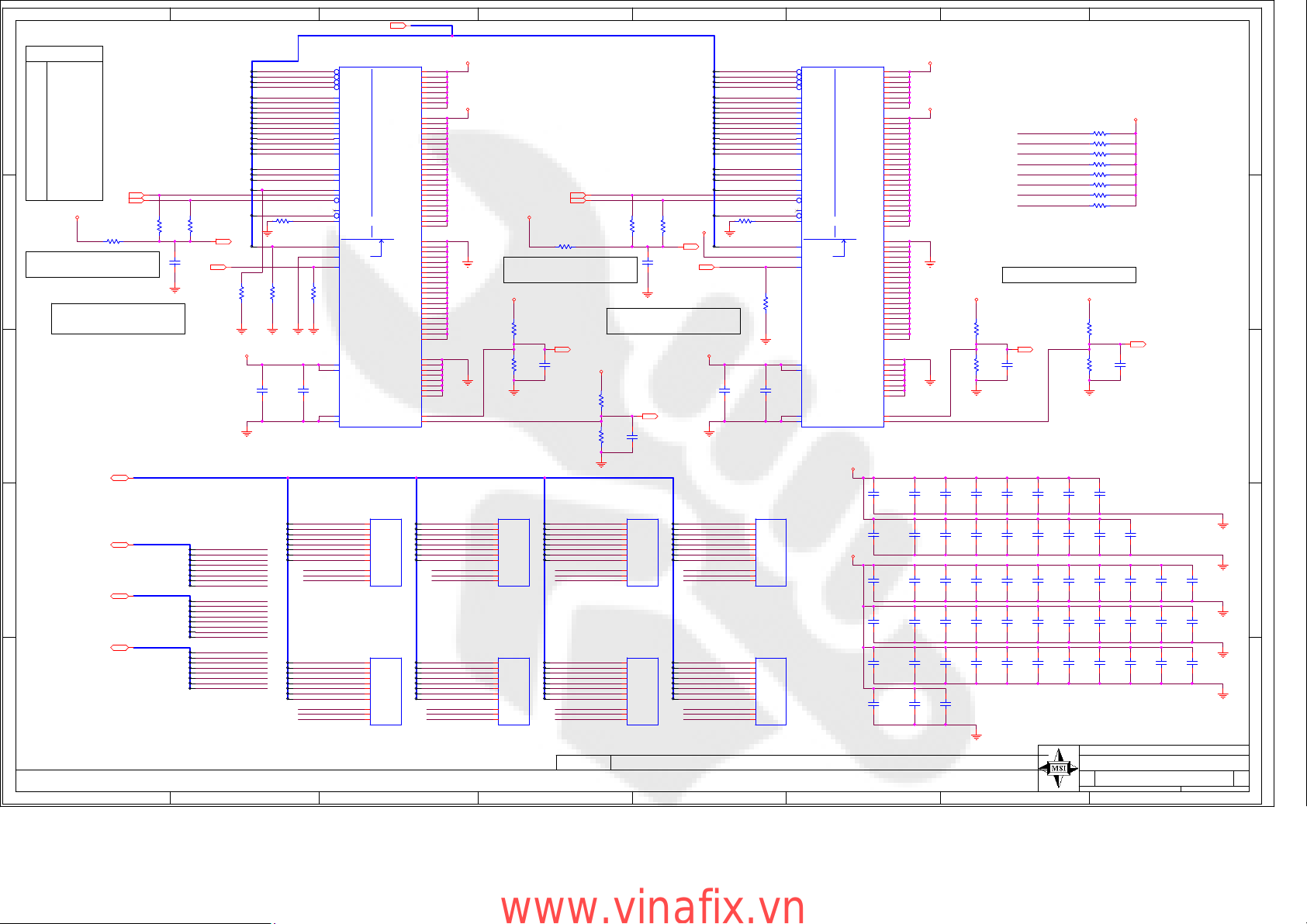

Page4: MEMORY: GPU Partition C/D

1

7,9 FBC_D[63..0]

BI

2

3

7,9 FBC_DQM[7..0]

OUT

7,9 FBC_DQS_RN[7..0]

IN

4

5

7,9 FBC_DQS_WP[7..0]

OUT

G1E

G1E

BGA_1148_P100_375X375_G3_256B

BGA_1148_P100_375X375_G3_256B

COMMON

COMMON

4/24 MEM_C

FBC_D0

0

FBC_D1

1

FBC_D2

2

FBC_D3

3

FBC_D4

4

FBC_D5

5

FBC_D6

6

FBC_D7

7

FBC_D8

8

FBC_D9

9

FBC_D10

10

FBC_D11

11

FBC_D12

12

FBC_D13

13

FBC_D14

14

FBC_D15

15

FBC_D16

16

FBC_D17

17

FBC_D18

18

FBC_D19

19

FBC_D20

20

FBC_D21

21

FBC_D22

22

FBC_D23

23

FBC_D24

24

FBC_D25

25

FBC_D26

26

FBC_D27

27

FBC_D28

28

FBC_D29

29

FBC_D30

30

FBC_D31

31

FBC_D32

32

FBC_D33

33

FBC_D34

34

FBC_D35

35

FBC_D36

36

FBC_D37

37

FBC_D38

38

FBC_D39

39

FBC_D40

40

FBC_D41

41

FBC_D42

42

FBC_D43

43

FBC_D44

44

FBC_D45

45

FBC_D46

46

FBC_D47

47

FBC_D48

48

FBC_D49

49

FBC_D50

50

FBC_D51

51

FBC_D52

52

FBC_D53

53

FBC_D54

54

FBC_D55

55

FBC_D56

56

FBC_D57

57

FBC_D58

58

FBC_D59

59

FBC_D60

60

FBC_D61

61

FBC_D62

62

FBC_D63

63

FBC_DQM0

0

FBC_DQM1

1

FBC_DQM2

2

FBC_DQM3

3

FBC_DQM4

4

FBC_DQM5

5

FBC_DQM6

6

FBC_DQM7

7

FBC_DQS_RN0

0

FBC_DQS_RN1

1

FBC_DQS_RN2

2

FBC_DQS_RN3

3

FBC_DQS_RN4

4

FBC_DQS_RN5

5

FBC_DQS_RN6

6

FBC_DQS_RN7

7

FBC_DQS_WP0

0

FBC_DQS_WP1

1

FBC_DQS_WP2

2

FBC_DQS_WP3

3

FBC_DQS_WP4

4

FBC_DQS_WP5

5

FBC_DQS_WP6

6

FBC_DQS_WP7

7

C18

C17

A17

B16

C14

A16

C15

A14

A18

A19

B19

B18

B21

C19

B22

C21

E15

D16

D17

G16

E16

E14

G13

D13

A22

C22

C23

A23

A24

C24

C25

B24

C28

B27

C27

B28

C29

A29

B30

A30

E31

E28

D28

F29

F30

D33

D32

D31

G27

F25

G26

D26

G29

G28

E27

F28

A34

C32

B34

C33

C31

B31

A31

C30

C16

C20

G14

C26

A28

D29

D27

B33

B15

A21

D14

B25

A27

E30

E25

A33

A15

A20

E13

A25

A26

D30

E26

A32

4/24 MEM_C

FBCD0

FBCD1

FBCD2

FBCD3

FBCD4

FBCD5

FBCD6

FBCD7

FBCD8

FBCD9

FBCD10

FBCD11

FBCD12

FBCD13

FBCD14

FBCD15

FBCD16

FBCD17

FBCD18

FBCD19

FBCD20

FBCD21

FBCD22

FBCD23

FBCD24

FBCD25

FBCD26

FBCD27

FBCD28

FBCD29

FBCD30

FBCD31

FBCD32

FBCD33

FBCD34

FBCD35

FBCD36

FBCD37

FBCD38

FBCD39

FBCD40

FBCD41

FBCD42

FBCD43

FBCD44

FBCD45

FBCD46

FBCD47

FBCD48

FBCD49

FBCD50

FBCD51

FBCD52

FBCD53

FBCD54

FBCD55

FBCD56

FBCD57

FBCD58

FBCD59

FBCD60

FBCD61

FBCD62

FBCD63

FBCDQM0

FBCDQM1

FBCDQM2

FBCDQM3

FBCDQM4

FBCDQM5

FBCDQM6

FBCDQM7

FBCDQS_RN0

FBCDQS_RN1

FBCDQS_RN2

FBCDQS_RN3

FBCDQS_RN4

FBCDQS_RN5

FBCDQS_RN6

FBCDQS_RN7

FBCDQS_WP0

FBCDQS_WP1

FBCDQS_WP2

FBCDQS_WP3

FBCDQS_WP4

FBCDQS_WP5

FBCDQS_WP6

FBCDQS_WP7

FBC_CMD0

FBC_CMD1

FBC_CMD2

FBC_CMD3

FBC_CMD4

FBC_CMD5

FBC_CMD6

FBC_CMD7

FBC_CMD8

FBC_CMD9

FBC_CMD10

FBC_CMD11

FBC_CMD12

FBC_CMD13

FBC_CMD14

FBC_CMD15

FBC_CMD16

FBC_CMD17

FBC_CMD18

FBC_CMD19

FBC_CMD20

FBC_CMD21

FBC_CMD22

FBC_CMD23

FBC_CMD24

FBC_CMD25

FBC_CMD26

FBC_CMD27

FBC_CMD28

FBC_CLK0

FBC_CLK0

FBC_CLK1

FBC_CLK1

FBC_DEBUG

FBC_PLLVDD_NC

FBC_DLLAVDD

FBC_PLLAVDD

FBC_PLLGND

FBC_CMD0

F18

FBC_CMD1

H20

FBC_CMD2

E18

FBC_CMD3

E20

FBC_CMD4

D23

FBC_CMD5

G24

FBC_CMD6

D24

FBC_CMD7

G23

FBC_CMD8

D20

FBC_CMD9

E22

FBC_CMD10

J21

FBC_CMD11

E21

FBC_CMD12

G20

FBC_CMD13

F22

FBC_CMD14

H21

FBC_CMD15

E17

FBC_CMD16

E19

FBC_CMD17

D21

FBC_CMD18

E23

FBC_CMD19

F19

FBC_CMD20

E24

FBC_CMD21

G21

FBC_CMD22

G19

FBC_CMD23

G25

FBC_CMD24

G18

FBC_CMD25

G22

G17

F15

G15

FBC_CLK0

H17

FBC_CLK0*

J16

FBC_CLK1

J24

FBC_CLK1*

H23

H24

RFU

J25

RFU

FBC_DEBUG

H16

SNN_FBC_PLLVDD

H13

J11

FBCD_PLLAVDD

J12

J13

GND

GND GND

Place components as close as possible to pad

Place components as close as possible to pad

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

7,9

OUT

7,9

OUT

7,9

OUT

7,9

OUT

BI

R637 60.4

R637 60.4

DNI1%0402

DNI1%0402

(OPT) (OPT)

9

BI

C847

C847

.1UF

.1UF

C830

C830

.1UF

.1UF

10V

10V

10%

10%

6.3V

6.3V

X5R

X5R

10%

10%

0402

0402

X5R

X5R

COMMON

COMMON

0402

0402

COMMON

COMMON

7,9FBC_CMD[25..0]

OUT

136BGA CMD Mapping

ADDR

CMD

CMD0 A<4>

CMD1 RAS*

A<5>

CMD2

CMD3

BA1

A<2>

CMD4

A<4>

CMD5

CMD6

A<3>

CMD7

BA2

CS0*

CMD8

CMD9

A<11>

CMD10

CAS*

CMD11

WE*

CMD12

BA0

CMD13

A<5>

CMD14

A<12>

RST

CMD15

CMD16

A<7>

CMD17

A<10>

CMD18

CKE

CMD19

A<0>

CMD20

A<9>

CMD21

A<6>

A<2>

CMD22

A<8>

CMD23

A<3>

CMD24

A<1>

CMD25

A<13>

CMD26

CMD27

N/A

N/A

CMD28

9

FBVDDQ

C829

C829

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

GND GND GND

Place components within 750 mils of pad

Place components within 750 mils of pad

8,9 FBD_D[63..0]

8,9 FBD_DQM[7..0]

8,9 FBD_DQS_RN[7..0]

8,9 FBD_DQS_WP[7..0]

240R@100MHz

240R@100MHz

LB504

LB504

IND_SMD_0402COMMON

IND_SMD_0402COMMON

C836

C836

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

BI

OUT

IN

OUT

1V2

C850

C850

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

FBD_D0

0

FBD_D1

1

FBD_D2

2

FBD_D3

3

FBD_D4

4

FBD_D5

5

FBD_D6

6

FBD_D7

7

FBD_D8

8

FBD_D9

9

FBD_D10

10

FBD_D11

11

FBD_D12

12

FBD_D13

13

FBD_D14

14

FBD_D15

15

FBD_D16

16

FBD_D17

17

FBD_D18

18

FBD_D19

19

FBD_D20

20

FBD_D21

21

FBD_D22

22

FBD_D23

23

FBD_D24

24

FBD_D25

25

FBD_D26

26

FBD_D27

27

FBD_D28

28

FBD_D29

29

FBD_D30

30

FBD_D31

31

FBD_D32

32

FBD_D33

33

FBD_D34

34

FBD_D35

35

FBD_D36

36

FBD_D37

37

FBD_D38

38

FBD_D39

39

FBD_D40

40

FBD_D41

41

FBD_D42

42

FBD_D43

43

FBD_D44

44

FBD_D45

45

FBD_D46

46

FBD_D47

47

FBD_D48

48

FBD_D49

49

FBD_D50

50

FBD_D51

51

FBD_D52

52

FBD_D53

53

FBD_D54

54

FBD_D55

55

FBD_D56

56

FBD_D57

57

FBD_D58

58

FBD_D59

59

FBD_D60

60

FBD_D61

61

FBD_D62

62

FBD_D63

63

FBD_DQM0

0

FBD_DQM1

1

FBD_DQM2

2

FBD_DQM3

3

FBD_DQM4

4

FBD_DQM5

5

FBD_DQM6

6

FBD_DQM7

7

FBD_DQS_RN0

0

FBD_DQS_RN1

1

FBD_DQS_RN2

2

FBD_DQS_RN3

3

FBD_DQS_RN4

4

FBD_DQS_RN5

5

FBD_DQS_RN6

6

FBD_DQS_RN7

7

FBD_DQS_WP0

0

FBD_DQS_WP1

1

FBD_DQS_WP2

2

FBD_DQS_WP3

3

FBD_DQS_WP4

4

FBD_DQS_WP5

5

FBD_DQS_WP6

6

FBD_DQS_WP7

7

G1F

G1F

BGA_1148_P100_375X375_G3_256B

BGA_1148_P100_375X375_G3_256B

COMMON

COMMON

5/24 MEM_D

5/24 MEM_D

H3

FBDD0

J3

FBDD1

J1

FBDD2

J2

FBDD3

M3

FBDD4

K3

FBDD5

L3

FBDD6

M1

FBDD7

H1

FBDD8

G3

FBDD9

G1

FBDD10

G2

FBDD11

F3

FBDD12

E1

FBDD13

D1

FBDD14

D2

FBDD15

P4

FBDD16

N7

FBDD17

M7

FBDD18

N5

FBDD19

P5

FBDD20

R7

FBDD21

T7

FBDD22

P7

FBDD23

C1

FBDD24

C5

FBDD25

C2

FBDD26

B4

FBDD27

A3

FBDD28

B3

FBDD29

C4

FBDD30

C3

FBDD31

A8

FBDD32

C6

FBDD33

C7

FBDD34

A7

FBDD35

C8

FBDD36

C9

FBDD37

A9

FBDD38

B9

FBDD39

E12

FBDD40

E9

FBDD41

F9

FBDD42

G10

FBDD43

D10

FBDD44

G12

FBDD45

F12

FBDD46

D11

FBDD47

F4

FBDD48

E4

FBDD49

D4

FBDD50

D5

FBDD51

D8

FBDD52

E7

FBDD53

D7

FBDD54

D9

FBDD55

B13

FBDD56

C11

FBDD57

A13

FBDD58

C13

FBDD59

A11

FBDD60

A10

FBDD61

B10

FBDD62

C10

FBDD63

K2

FBDDQM0

E3

FBDDQM1

N4

FBDDQM2

D3

FBDDQM3

B7

FBDDQM4

G11

FBDDQM5

F5

FBDDQM6

C12

FBDDQM7

K1

FBDDQS_RN0

F2

FBDDQS_RN1

R6

FBDDQS_RN2

A4

FBDDQS_RN3

B6

FBDDQS_RN4

E10

FBDDQS_RN5

E6

FBDDQS_RN6

A12

FBDDQS_RN7

L1

FBDDQS_WP0

F1

FBDDQS_WP1

R5

FBDDQS_WP2

A5

FBDDQS_WP3

A6

FBDDQS_WP4

E11

FBDDQS_WP5

D6

FBDDQS_WP6

B12

FBDDQS_WP7

FBD_CMD0

FBD_CMD1

FBD_CMD2

FBD_CMD3

FBD_CMD4

FBD_CMD5

FBD_CMD6

FBD_CMD7

FBD_CMD8

FBD_CMD9

FBD_CMD10

FBD_CMD11

FBD_CMD12

FBD_CMD13

FBD_CMD14

FBD_CMD15

FBD_CMD16

FBD_CMD17

FBD_CMD18

FBD_CMD19

FBD_CMD20

FBD_CMD21

FBD_CMD22

FBD_CMD23

FBD_CMD24

FBD_CMD25

FBD_CMD26

FBD_CMD27

FBD_CMD28

FBD_CLK0

FBD_CLK0

FBD_CLK1

FBD_CLK1

FBD_DEBUG

FBD_PLLVDD_NC

FBD_PLLGND

1

8,9FBD_CMD[25..0]

FBD_CMD0

M6

FBD_CMD1

G5

FBD_CMD2

L7

FBD_CMD3

K5

FBD_CMD4

J10

FBD_CMD5

G8

FBD_CMD6

F8

FBD_CMD7

G6

FBD_CMD8

H6

FBD_CMD9

F6

FBD_CMD10

K8

FBD_CMD11

L5

FBD_CMD12

H4

FBD_CMD13

G4

FBD_CMD14

K9

FBD_CMD15

L4

FBD_CMD16

K4

FBD_CMD17

K7

FBD_CMD18

G7

FBD_CMD19

J4

FBD_CMD20

F7

FBD_CMD21

J5

FBD_CMD22

J6

FBD_CMD23

H7

FBD_CMD24

L8

FBD_CMD25

J7

M5

H9

G9

FBD_CLK0

L9

FBD_CLK0*

M9

FBD_CLK1

J9

FBD_CLK1*

J8

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

8,9

OUT

8,9

OUT

8,9

OUT

8,9

OUT

OUT

2

3

9

BI

H10

RFU

L11

RFU

FBD_DEBUG

N8

SNN_FBD_PLLVDD

H11

R644 60.4

R644 60.4

FBVDDQ

DNI1%0402

DNI1%0402

4

H12

GND

5

ASSEMBLY P392 - BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C GE

PAGE DETAIL

www.vinafix.vn

MEMORY: GPU Partition C/D

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

Custom

<Doc>

Custom

<Doc>

Date:

Date:

Date:

Custom

Thursday, July 24, 2008

Thursday, July 24, 2008

Thursday, July 24, 2008

Sheet of

Sheet of

Sheet of

HFDBA

426

426

426

<RevCode>

<RevCode>

<RevCode>

A B C D E F G H

Page5: FBA Partition

136BGA CMD Mapping

136MAP

ADDR

CMD1

RAS*

CMD10

CAS*

CMD11

WE*

CMD8

CS0*

CMD12

BA0

CMD3

BA1

1

CMD7

BA2

CMD19

A<0>

CMD25

A<1>

CMD22

0A<2>

CMD24

0A<3>

CMD0

0A<4>

CMD2

0A<5>

CMD4

1A<2>

CMD6

1A<3>

CMD5

1A<4>

CMD13

1A<5>

A<6> CMD21

CMD16

A<7>

CMD23

A<8>

CMD20

A<9>

CMD17

A<10>

CMD9

A<11>

CMD14

A<12>

CMD18

CKE

CMD15

RST

2

MUST BE PLACED as close as possible to

the BGA memory on the line AFTER the

MEMORY pin!!

Minimize the stub length!!

DDR3: ZQ = 6x desired output

impedance of DQ drivers

Impedance = 240 / 6 = 40 ohm

3,9

IN

3,9 FBA_CLK0

IN

3,9 FBA_CLK0*

IN

FBVDDQ

R584 121

R584 121

(OPT)

COMMON

COMMON

DNI1%0402

DNI1%0402

3

FBA_D[63..0]

3,9

BI

FBA_DQM[7..0]

3,9

BI

4

FBA_DQS_RN[7..0]

3,9

BI

FBA_DQS_WP[7..0]

3,9

BI

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

FBA_CMD[25..0]

FBA_CMD1

1

FBA_CMD10

10

FBA_CMD11

11

FBA_CMD8

8

FBA_CMD19

19

FBA_CMD25

25

22

FBA_CMD24

24

FBA_CMD0

0

2

FBA_CMD21

21

FBA_CMD16

16

FBA_CMD23

23

FBA_CMD20

20

FBA_CMD17

17

FBA_CMD9

9

FBA_CMD12

12

FBA_CMD3

3

FBA_CMD7

7

FBA_CMD18

18

FBA_CMD18

R592

R592

R586

R586

243

243

1%

1%

0402

0402

COMMON

COMMON

243

243

1%

1%

0402

0402

C587

C587

.1UF

.1UF

6.3V

6.3V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

A12

9FBA_CLK0_MIDPT

OUT

9 FBA_ZQ0

IN

FBA_DQM0

FBA_DQM1

FBA_DQM2

FBA_DQM3

FBA_DQM5

FBA_DQM6

FBA_DQM7

FBA_DQS_RN0

FBA_DQS_RN1

FBA_DQS_RN2

FBA_DQS_RN3

FBA_DQS_RN4

FBA_DQS_RN5

FBA_DQS_RN6

FBA_DQS_RN7

FBA_DQS_WP0

FBA_DQS_WP1

FBA_DQS_WP2

FBA_DQS_WP3

FBA_DQS_WP4

FBA_DQS_WP5

FBA_DQS_WP6

FBA_DQS_WP7

FBA_CMD14 FBA_CMD14

14

R121 1K

R121 1K

COMMON

0402

COMMON

0402

5%

5%

GND

15

FBA_CMD15 FBA_CMD15

R129

R129

R124

R124

10K

10K

10K

10K

5%

5%

5%

5%

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

GND

GND GND GND

FBVDDQ

C95

C95

.047UF

.047UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

FBA_SEN0

0

1

2

3

4

5

6

7

32

33

34

35

36

37

38

39

H11

K10

K11

H10

J11

J10

R126

R126

243

243

1%

1%

0402

0402

COMMON

COMMON

K12

C84

C84

.047UF

.047UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

J12

FBA_D0

FBA_D2

FBA_D4

FBA_D5

FBA_D6

FBA_DQM0

FBA_DQS_RN0

FBA_DQS_WP0

FBA_D33

FBA_D34

FBA_DQM4

FBA_DQS_RN4

FBA_DQS_WP4

M6E

M6E

BGA_0136_P080_140X110

BGA_0136_P080_140X110

BGA136

BGA136

COMMON

COMMON

H3

F4

H9

F9

CS0 CAS

K4

H2

K3

M4

K9

L9

A8/AP A10

M9

K2

L4

G4

G9

H4

CKE WE

CLK

CLK

J2

NC/RFU

J3

NC/CS1 NC/CS1

V4

SEN (GND)

NONMIRROR

NONMIRROR

V9

RESET

A9

MIRROR

A4

ZQ

K1

VDDA

VDDA

J1

VSSA

VSSA

*CS1 is required 32Mx32 Memories

*CS1 is required 32Mx32 Memories

FBA_D7

FBA_D1

FBA_D3

FBA_D38

FBA_D39

FBA_D37

FBA_D35

FBA_D32

FBA_D36

M6A

M6A

BGA_0136_P080_140X110

BGA_0136_P080_140X110

BGA136

BGA136

COMMON

COMMON

L10

DQ0

M11

DQ1

M10

DQ2

R10

DQ3

T10

DQ4

N11

DQ5

R11

DQ6

T11

DQ7

N10

DQM

P10

RDQS

P11

WDQS

M7E

M7E

BGA_0136_P080_140X110

BGA_0136_P080_140X110

BGA136

BGA136

COMMON

COMMON

R2

DQ0

T2

DQ1

T3

DQ2

R3

DQ3

N2

DQ4

M3

DQ5

L3

DQ6

M2

DQ7

N3

DQM

P3

RDQS

P2

WDQS

BA2RAS

CS0CAS

CKEWE

A4A0

A5A1

A6A2

A9A3

A0A4

A1A5

A2A6

A11A7

A3A9

A8/APA10

A7A11

BA1BA0

BA0BA1

RASBA2

MIRROR

MIRROR

FBVDDQ

F1

VDD

M1

VDD

A2

VDD

V2

VDD

A11

VDD

V11

VDD

F12

VDD

M12

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VREF

VREF

FBVDDQ

A1

C1

E1

N1

R1

V1

C4

E4

J4

N4

R4

C9

E9

J9

N9

R9

A12

C12

E12

N12

R12

V12

B1

D1

P1

T1

G2

L2

GND

B4

D4

P4

T4

B9

D9

P9

T9

G11

L11

B12

D12

P12

T12

G1

L1

A3

V3

A10

V10

GND

G12

L12

FBA_VREF0

H1

FBA_VREF2

H12

FBA_D8

8

FBA_D9

9

FBA_D10

10

FBA_D11

11

FBA_D12

12

FBA_D13

13

FBA_D14

14

FBA_D15

15

FBA_DQM1

FBA_DQS_RN1

FBA_DQS_WP1

40

FBA_D44

FBA_D45

FBA_D43

FBA_D41

FBA_D46

FBA_D40

FBA_D47

FBA_D42

C11

G10

C10

E11

F10

B10

B11

F11

E10

D10

D11

41

42

43

44

45

46

47

FBA_DQM5

FBA_DQS_RN5

FBA_DQS_WP5

MUST BE PLACED as close as possible to

the BGA memory on the line AFTER the

MEMORY pin!!

Minimize the stub length!!

FBVDDQ

R119

R119

549

549

1%

1%

0402

0402

COMMON

COMMON

R117

R117

1.33K

1.33K

1%

1%

0402

0402

COMMON

COMMON

GND

M6B

M6B

BGA_0136_P080_140X110

BGA_0136_P080_140X110

BGA136

BGA136

COMMON

COMMON

L3

DQ0

N2

DQ1

M2

DQ2

M3

DQ3

R2

DQ4

R3

DQ5

T3

DQ6

T2

DQ7

N3

DQM

P3

RDQS

P2

WDQS

M7A

M7A

BGA_0136_P080_140X110

BGA_0136_P080_140X110

BGA136

BGA136

COMMON

COMMON

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQM

RDQS

WDQS

FBVDDQ

R597 121

R597 121

1%

1%

(OPT)

R1

OUT

C83

C83

.1UF

.1UF

R2

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

FBA_D16

16

FBA_D17

17

FBA_D18

18

FBA_D19

19

FBA_D20

20

FBA_D21

21

FBA_D22

22

FBA_D23

23

FBA_DQM2

FBA_DQS_RN2

FBA_DQS_WP2

48

49

50

51

52

53

54

55

C GE

M7D

M7D

BGA_0136_P080_140X110

BGA_0136_P080_140X110

BGA136

BGA136

COMMON

R128

R128

243

243

1%

1%

0402

0402

COMMON

COMMON

GND

C92

C92

.047UF

.047UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

M6D

M6D

BGA_0136_P080_140X110

BGA_0136_P080_140X110

BGA136

BGA136

COMMON

COMMON

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQM

RDQS

WDQS

M7C

M7C

BGA_0136_P080_140X110

BGA_0136_P080_140X110

BGA136

BGA136

COMMON

COMMON

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQM

RDQS

WDQS

COMMON

H3

F4

H9

F9

CS0 CAS

K4

H2

K3

M4

K9

H11

K10

L9

K11

A8/AP A10

M9

K2

L4

G4

G9

H10

H4

CKE WE

J11

CLK

J10

CLK

J2

NC/RFU

J3

NC/CS1 NC/CS1

V4

SEN (GND)

NONMIRROR

NONMIRROR

V9

RESET

A9

MIRROR

A4

ZQ

K1

VDDA

K12

VDDA

J1

VSSA

J12

VSSA

*CS1 is required 32Mx32 Memories

*CS1 is required 32Mx32 Memories

BA2RAS

CS0CAS

CKEWE

A4A0

A5A1

A6A2

A9A3

A0A4

A1A5

A2A6

A11A7

A3A9

A8/APA10

A7A11

BA1BA0

BA0BA1

RASBA2

MIRROR

MIRROR

FBA_CMD7

7

FBA_CMD8

8

FBA_CMD18

18

FBA_CMD10

10

FBA_CMD5 FBA_CMD5

5

FBA_CMD13

13

FBA_CMD21FBA_CMD22

21

FBA_CMD20

20

FBA_CMD19

19

FBA_CMD25FBA_CMD2

25

FBA_CMD4

4

FBA_CMD9

9

FBA_CMD17

17

FBA_CMD6

6

FBA_CMD23

23

FBA_CMD16

16

FBA_CMD3

3

FBA_CMD12

12

FBA_CMD1

1

FBA_CMD11

3,9 FBA_CLK1

IN

3,9 FBA_CLK1*

IN

R603

R603

R606

R606

243

243

243

243

1%

1%

1%

1%

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

DNI0402

DNI0402

9

DDR3:

C609

C609

.1UF

.1UF

6.3V

6.3V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

ZQ = 6x desired output

impedance of DQ drivers

Impedance = 240 / 6 = 40 ohm

FBVDDQ

R137

R137

549

549

R1

1%

1%

0402

0402

COMMON

COMMON

R141

R141

1.33K

1.33K

R2

1%

1%

0402

0402

COMMON

COMMON

GND

E2

G3

F2

B2

C2

B3

F3

C3

E3

D3

D2

FBA_D62

T11

FBA_D60

T10

FBA_D63

R10

FBA_D61

R11

FBA_D59

M10

FBA_D57

N11

FBA_D56

M11

FBA_D58

L10

FBA_DQM7

N10

FBA_DQS_RN7

P10

FBA_DQS_WP7

P11

ASSEMBLY P392 - BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

PAGE DETAIL

C94

C94

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

M6C

M6C

BGA_0136_P080_140X110

BGA_0136_P080_140X110

BGA136

BGA136

COMMON

COMMON

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQM

RDQS

WDQS

M7B

M7B

BGA_0136_P080_140X110

BGA_0136_P080_140X110

BGA136

BGA136

COMMON

COMMON

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQM

RDQS

WDQS

FBA Partition

9

OUT

11

A12

14

R134 1K

R134 1K

0402

0402

5%

5%

9FBA_CLK1_MIDPT

OUT

GND

15

FBVDDQ

9 FBA_ZQ1

IN

FBVDDQ

C85

C85

.047UF

.047UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

FBA_D24

24

FBA_D25

25

FBA_D26

26

FBA_D27

27

28

FBA_D29

29

FBA_D28

FBA_D30

30

FBA_D31

31

FBA_DQM3FBA_DQM4

FBA_DQS_RN3

FBA_DQS_WP3

56

FBA_D53

57

FBA_D48

58

FBA_D54

59

FBA_D51

60

FBA_D49

61

FBA_D55

62

FBA_D50

63

FBA_D52

FBA_DQM6

FBA_DQS_RN6

FBA_DQS_WP6

COMMON

COMMON

FBA_CMD15

G10

C10

F11

F10

C11

B10

B11

E11

E10

D10

D11

C2

C3

B2

B3

E2

F2

F3

G3

E3

D3

D2

FBA_SEN1

FBVDDQ

F1

VDD

M1

VDD

A2

VDD

V2

VDD

A11

VDD

V11

VDD

F12

VDD

M12

FBVDDQ

A1

C1

E1

N1

R1

V1

C4

E4

J4

N4

R4

C9

E9

J9

N9

R9

A12

C12

E12

N12

R12

V12

B1

D1

P1

T1

G2