MSI MS-V154 Schematic 20

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

ASSEMBLYNVPNVARIANT

B

1

2

SKU

3

4

5

6

12

13

14

7

8

9

10

11

15

P391-A00 Base Design

P391-A00, G92, 8Mx32/16Mx32 GDDR3

DVI-I-DL, DVI-I-DL, HDTVout

Table of Contents:

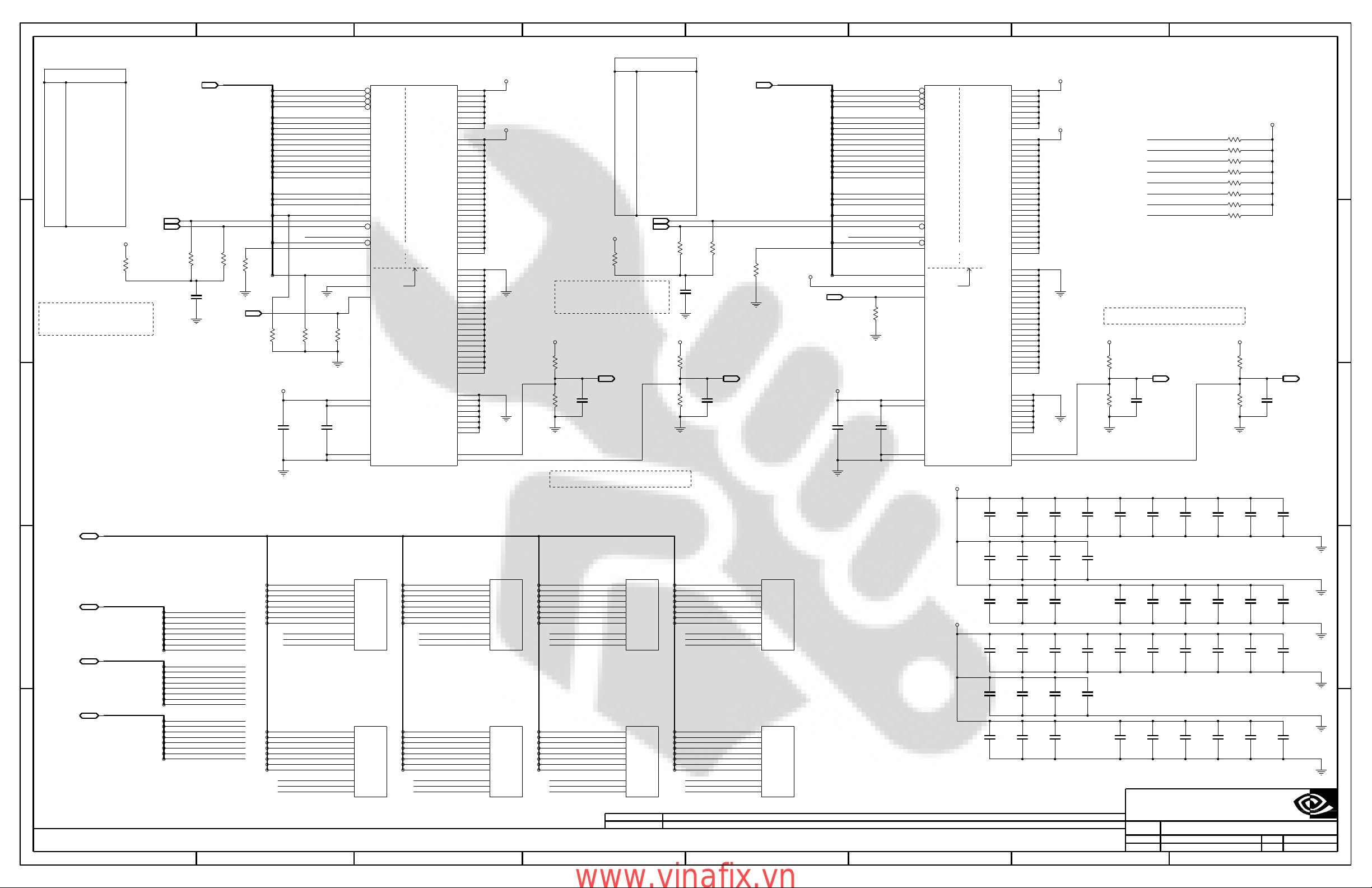

Page 1: Overview

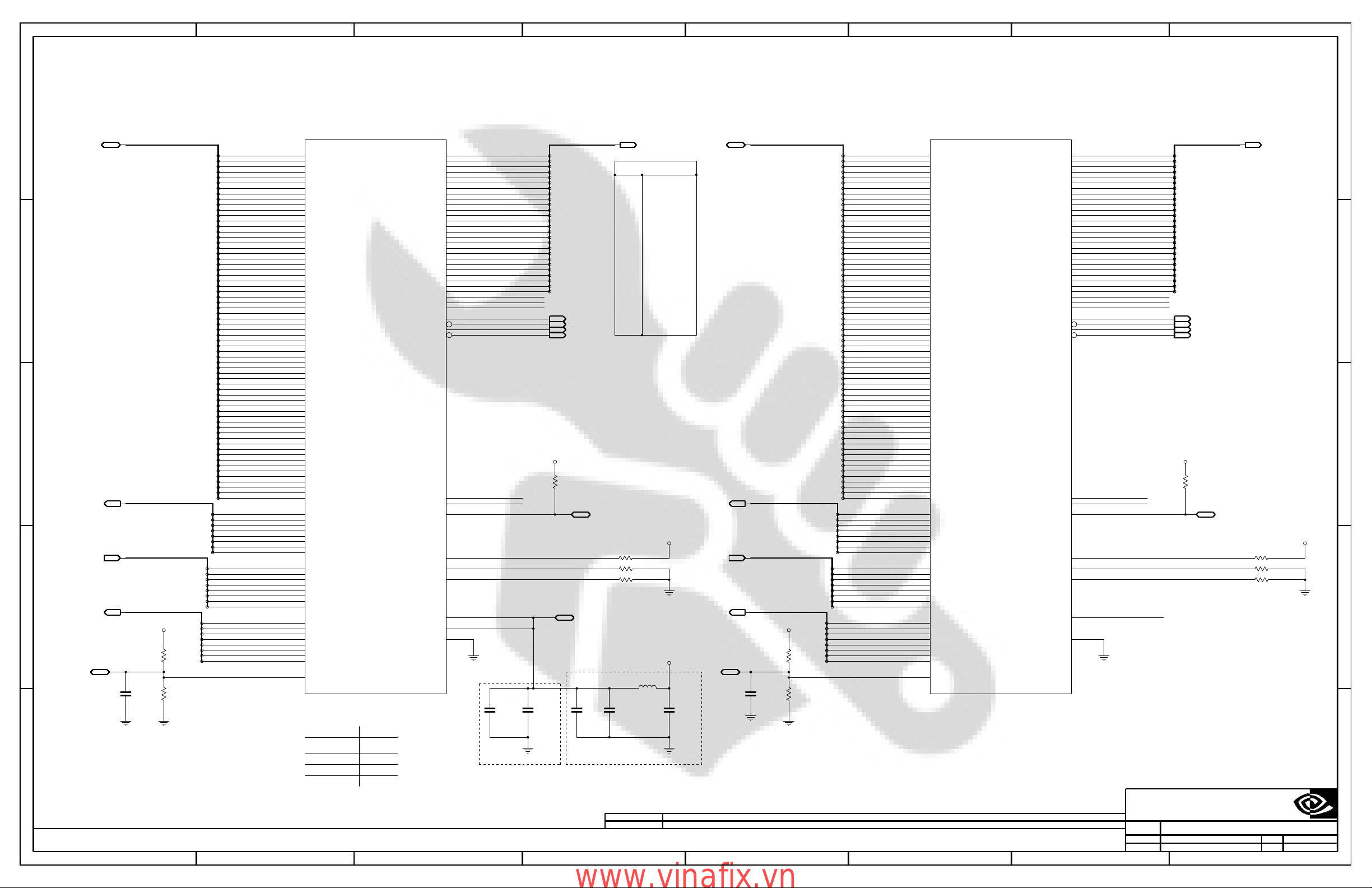

Page 2: PCI Express 1.0

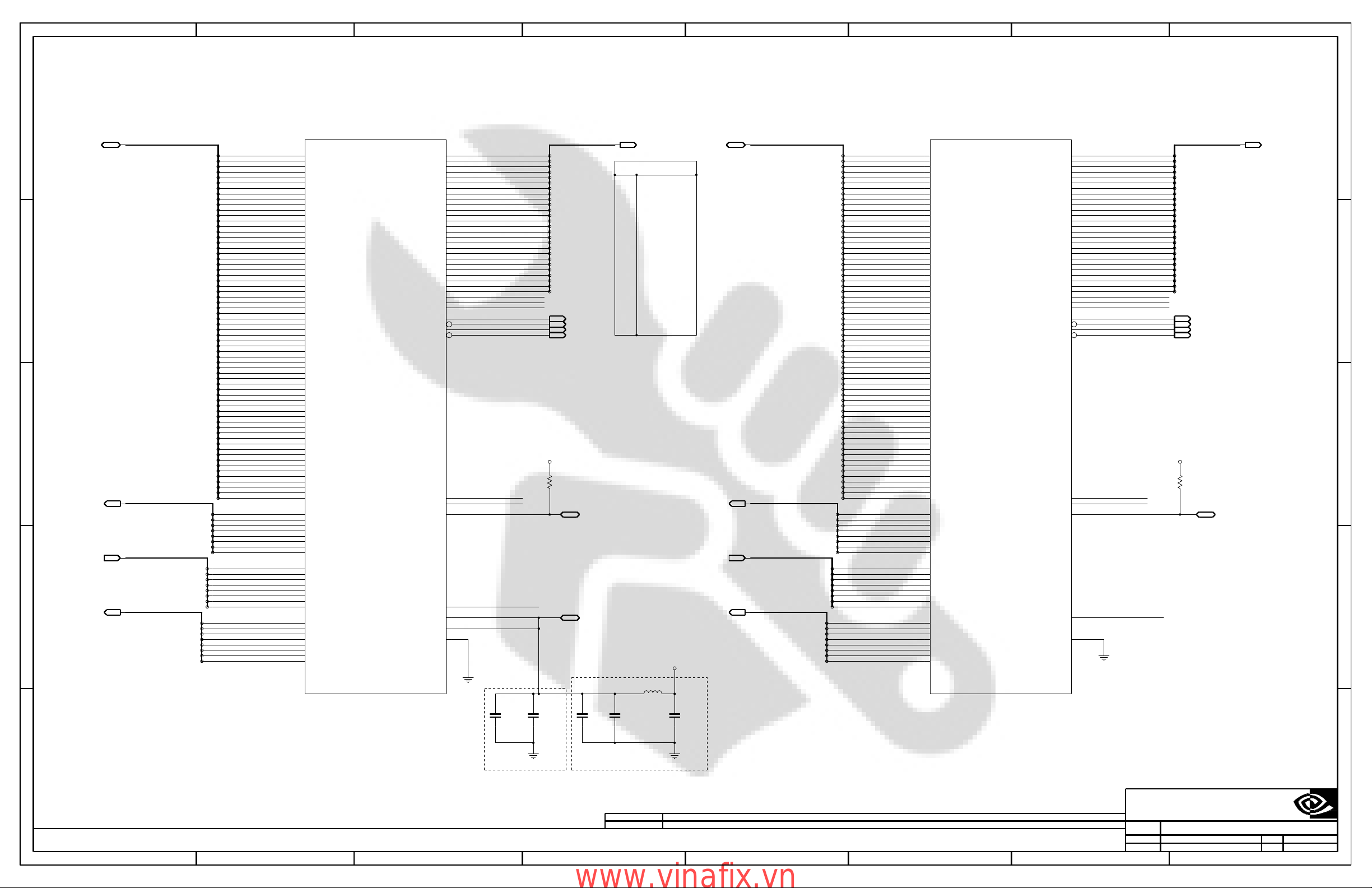

Page 3: MEMORY: GPU Partition A/B

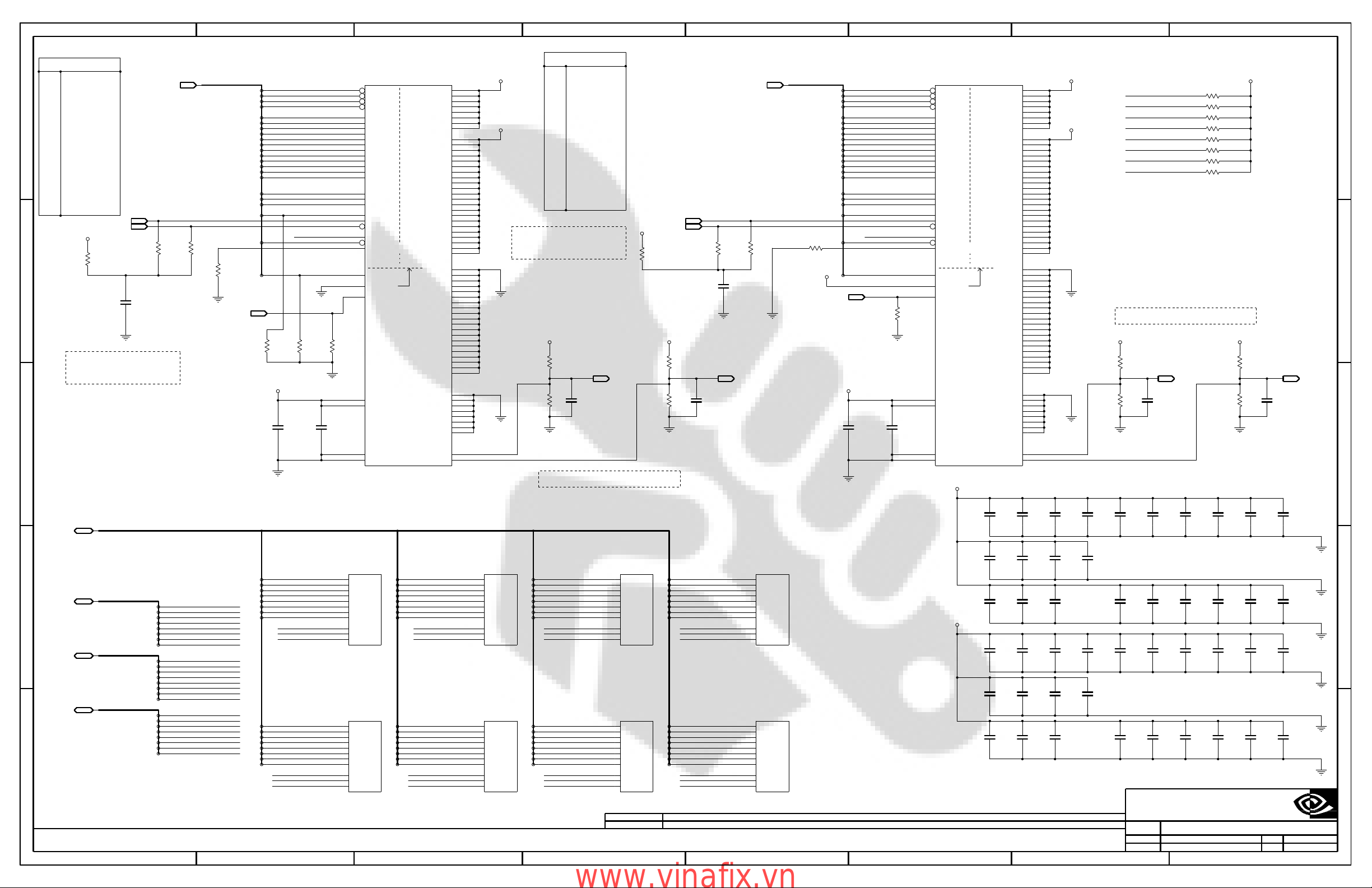

Page 4: MEMORY: GPU Partition C/D

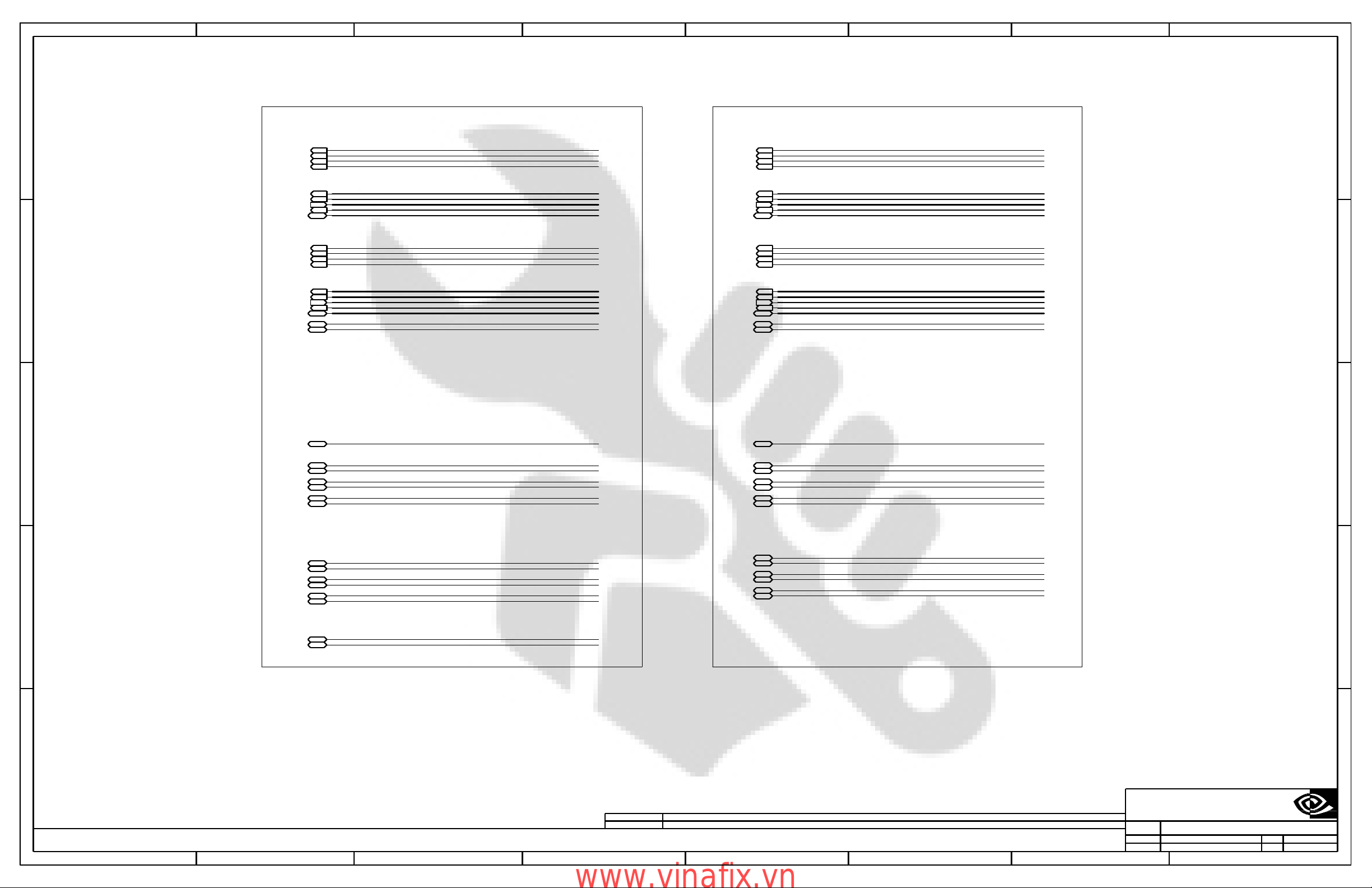

Page 5: FBA Partition

Page 6: FBB Partition

Page 7: FBC Partition

Page 8: FBD Partition

Page 9: FrameBuffer Net Rules

Page 10: DACA Interface

Page 11: DACC Interface

Page 12: IFP A/B and C/D Interface

Page 13: DACB

Page 14: Multi-use IO(MIO) Interface

Page 15: MISC: GPIO, I2C, BIOS, and PLL

Page 16: Thermal Control/Protection, XTAL and SPDIF Input

Page 17: Power/GND and Decoupling

Page 18: Configuration Straps and Mechanical

Page 19: Power Supply: 5V, and 8V5

Page 20: Power Supply: 2V5 and 1V8

Page 21: Power Supply: FBVDD/Q, PEXVDD

Page 22: Power Supply: NVVDD Regulator

Page 23: Power Supply: NVVDD Phase 1 & 2

Page 24: Power Supply: NVVDD Phase 3

Page 25: Power Supply: Filter/Detection of 3V3, 12V, 12V_PEX6

Page 26: Cref 1

Page 27: Cref 2

Page 28: Cref 3

Page 29: Cref 4

BASE

SKU0050

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

P391 G92 512MB GDDR3 16Mx32 DVI-I+DVI-I

Overview

www.vinafix.vn

600-10391-base-000

600-10391-0050-000

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

P391 - BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

P391 G92 512MB GDDR3 16Mx32 DVI-I+DVI-I

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

600-10391-0050-000 A

p391_a00

gachen

1 OF 29

08-AUG-2008

J501

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTININ

23/24 JTAG

JTAG_TDI

JTAG_TCLK

JTAG_TMS

JTAG_TDO

JTAG_TRST

KEY

TRST*

TCK

GND

TMS

TDO

VCC

TDI

1/24 PCI EXPRESS

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

RFU

RFU

PEX_PLLAVDD

PEX_PLLDGND

PEX_PLLAGND

PEX_PLLDVDD

PEX_TEST_PLL_CLK_OUT

PEX_TEST_PLL_CLK_OUT

PEX_TX0

PEX_REFCLK

PEX_REFCLK

PEX_RST

PEX_TX0

PEX_RX1

PEX_TX1

PEX_RX0

PEX_TX2

PEX_TX2

PEX_RX2

PEX_TX3

PEX_RX1

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX1

PEX_RX0

PEX_RX2

PEX_RX5

PEX_TX6

PEX_RX6

PEX_RX6

PEX_TX7

PEX_TX4

PEX_TX4

PEX_RX4

PEX_TX6

PEX_RX5

PEX_RX4

PEX_TX5

PEX_TX5

PEX_TX7

PEX_TX9

PEX_RX8

PEX_TX8

PEX_RX9

PEX_RX7

PEX_TX9

PEX_TX10

PEX_RX7

PEX_TX8

PEX_TX10

PEX_RX9

PEX_RX8

PEX_RX10

PEX_RX11

PEX_RX10

PEX_TX12

PEX_TX12

PEX_RX11

PEX_RX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX11

PEX_TX11

PEX_TX14

PEX_RX15

PEX_RX15

PEX_TX15

PEX_TX15

PEX_RX14

PEX_RX14

PEX_TX14

OUTBIOUT

END OF X8

END OF X16

END OF X1

END OF X4

TCLK JTAG2

TMS JTAG5

TDO JTAG4

TDI JTAG3

WAKE

SMDAT

SMCLK

PERN0

PERP0

REFCLK

PERST

REFCLK

PETN1

PERP2

PETN0

PERP1

PERN1

PETP0

PETP1

PERN3

PETP3

PETN3

PETP2

PERP3

PETN2

PERN2

PERP4

PERN4

PETN4

PERP5

PETP4

PERN5

PETP5

PETP6

PERN6

PERP6

PETN5

PERP7

PETN6

PERN7

PETN8

PETP8

PERP8

PETN7

PETP7

PERN8

PERN9

PERP9

PERP10

PERN10

PETP10

PETP9

PETN9

PETN10

PETN11

PERP12

PERN12

PERP11

PERN11

PETP11

PETN12

PETP12

PETN13

PERP13

PERN13

PETP13

PERP14

PERN15

PETP15

PETN15

PERN14

PETN14

PETP14

PERP15

TRST* JTAG1+12V

+12V/RSVD

+3V3AUX

+12V

+12V

+12V

+3V3

+3V3

+3V3

PRSNT2

PRSNT1

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

GND

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

HDR_2F4

FEMALE

3V3_F

1

3

5

7

1.274MM

0

KEY6_JTAG_SMALL

NO STUFF

2

4

8

AH21

AJ21

AH22

AJ22

AH23

AJ23

AH16

AF17

AH17

AF18

AH18

AF19

AH19

AE20

AF20

AH20

AJ20

PEX_PLL_CLK_OUT

AM9

PEX_PLL_CLK_OUT*

AN9

SNN_PEXCAL_PD_VDDQ

AK19

SNN_PEXCAL_PD_GND

AK20

PEX_PLLAVDD

AE15

AE17

Fix for G92 NC pin issue

AF15

AE16

GND

P391 G92 512MB GDDR3 16Mx32 DVI-I+DVI-I

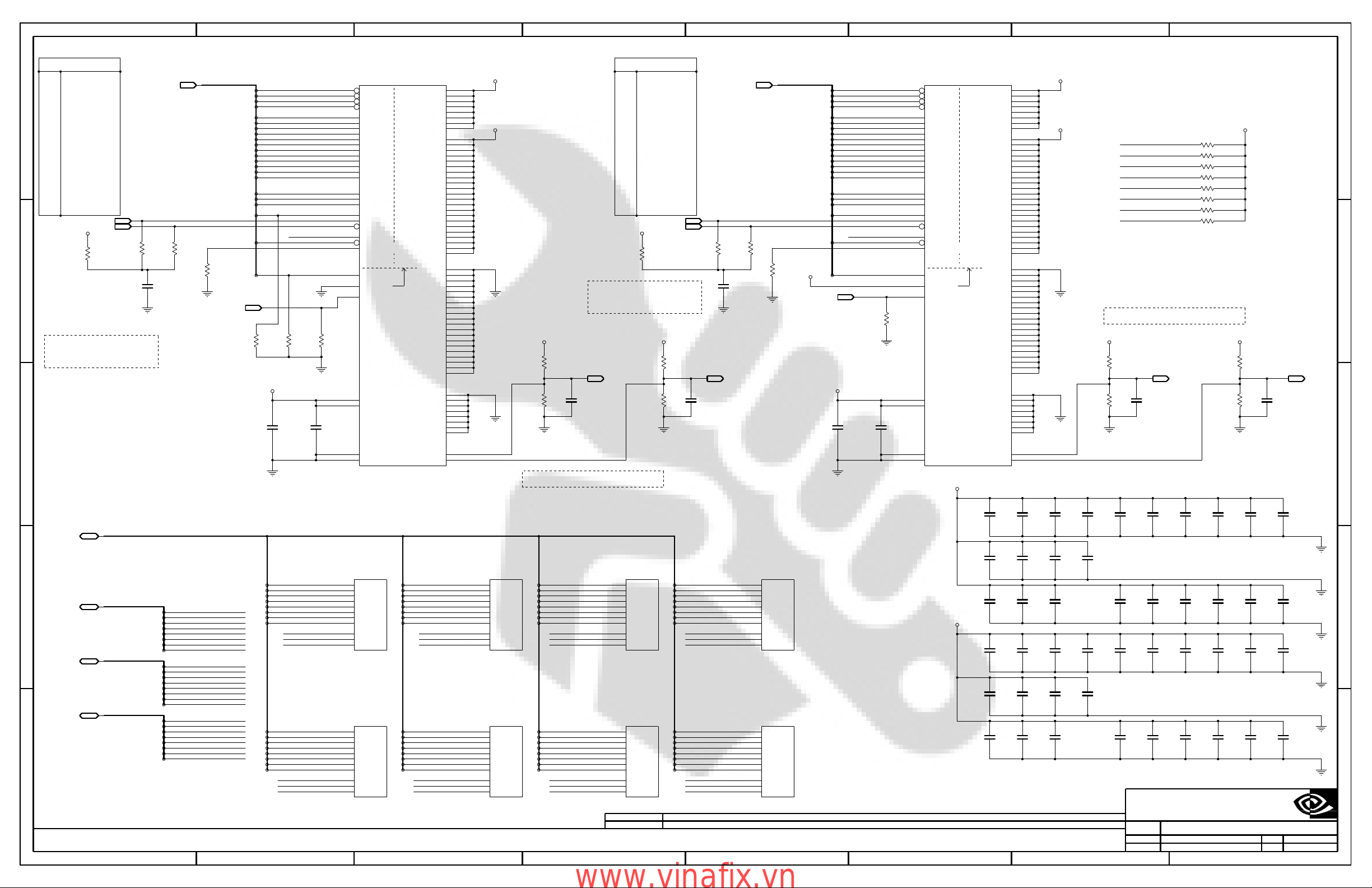

PCI Express 1.0

www.vinafix.vn

.1UF

C896

10V

10%

0402

.1UF

10V0402 .1UFC890

10%

0402

.1UF

C881

10V

10%

0402

.1UF

C872

10V

10%

0402

.1UF

C850

10V

10%

0402

.1UF

C830

10V

10%

0402

.1UF

C809

10V

10%

0402 10V

.1UF

C783

10V

10%

0402

.1UFC768

C763

10V

10%

0402

.1UF

C729

10V

10%

0402

.1UF

C697

10V

10%

0402

.1UF

C675

10V

10%

0402

.1UF

C665

10V

10%

0402

.1UF

10V

10%

0402

.1UF

C645

10V

10%

0402

.1UF

C63810V

10%

0402

15.2F< 15.1G<

15.2F<> 15.1G<

R724

0402

0402

R738

0402

R732

0402

R728

0402

2.4H>

16.5A<

5%

5%

5%

5%

5%

0

NO STUFF

0R740

NO STUFF

0

NO STUFF

0

NO STUFF

0

NO STUFF

16.2A<

JTAG_TRST*

JTAG_TCLK

JTAG_TDI

JTAG_TDO

JTAG_TMS

G1

G92-270-A2

BGA1148

COMMON

AR9

AK10

AL10

.1UF

10V

10V

.1UF

10V

.1UF

10V

.1UF

10V

.1UF

10V

.1UF

.1UF

10V

.1UF

10V

.1UF

10V

.1UF

10V

.1UF

10V

.1UF

10V

.1UFC649

10V

.1UF

10V

.1UF

10V

10%

X5R

10%

X5R

10%

X5R

10%

X5R

10%

X5R

10%

X5R

10%

X5R

10%

X5R

10%

X5R

10%

X5R

10%

X5R

10%

10%

X5R

10%

X5R

10%

X5R

10%

X5R

PEX_TX0

PEX_TX0*

COMMON

PEX_TX1

PEX_TX1* AN11

COMMON

PEX_TX2

PEX_TX2*

COMMON

PEX_TX3

PEX_TX3*

COMMON

PEX_TX4

PEX_TX4*

COMMON

PEX_TX5

PEX_TX5*

COMMON

PEX_TX6

PEX_TX6*

COMMON

PEX_TX7

PEX_TX7*

COMMON

PEX_TX8 AM16

PEX_TX8*

COMMON

PEX_TX9

PEX_TX9*

COMMON

PEX_TX10

PEX_TX10*

COMMON

PEX_TX11

PEX_TX11*

COMMON

PEX_TX12

PEX_TX12*

COMMON

PEX_TX13

PEX_TX13*

COMMON

PEX_TX14

PEX_TX14*

COMMON

PEX_TX15

PEX_TX15*

COMMON

AM11

AM10

AP9

AP10

AN10

AR10

AR11

AN12

AM12

AT11

AT12

AL12

AK12

AP12

AP13

AM14

AM13

AR13

AR14

AN13

AN14

AT14

AT15

AN15

AM15

AP15

AP16

AL15

AK15

AR16

AR17

AN16

AT17

AT18

AN17

AN18

AP18

AP19

AM18

AM17

AR19

AR20

AL18

AK18

AT20

AT21

AM19

AN19

AP21

AP22

AN20

AN21

AR22

AR23

AM21

AM20

AT23

AT24

AL21

AK21

AR24

AR25

Page2: PCI Express 1.0

12V

3V3

SNN_PEX_PRSNT2_C

SNN_PEX_RSVD5

SNN_PE_RSVD6

SNN_PE_RSVD7

C31

10UF

16V

20%

X5R

1206

NO STUFF

GND

SNN_3V3_AUX

PEX_PRSNT1*

SNN_PEX_PRSNT2_A

SNN_PEX_RSVD1

SNN_PEX_PRSNT2_B

SNN_PEX_RSVD2

SNN_PEX_RSVD3

SNN_PEX_RSVD4

CN2

NONPHY-X16-B

CON_X16

CON_PCIEXP_X16_EDGE

NO STUFF

PEX_TRST*

B1

B2

A2

A3

B3

B8

A9

A10

B10

A1

B17

B12

B4

A4

B7

A12

B13

A15

B16

B18

A18

GND

B31

A19

B30

A32

A20

B21

B22

A23

A24

B25

B26

A27

A28

B29

A31

B32

B48

GND

A33

A34

B35

B36

A37

A38

B39

B40

A41

A42

B43

B44

A45

A46

B47

B49

A49

GND

B81

A50

B82

A51

B52

B53

A54

A55

B56

B57

A58

A59

B60

B61

A62

A63

B64

B65

A66

A67

B68

B69

A70

A71

B72

B73

A74

A75

B76

B77

A78

A79

B80

A82

GND

B9

A5

A6

A7

A8

B5

B6

B11

A11

A13

A14

A16

A17

B14

B15

A21

A22

B19

B20

A25

A26

B23

B24

A29

A30

B27

B28

A35

A36

B33

B34

A39

A40

B37

B38

A43

A44

B41

B42

A47

A48

B45

B46

A52

A53

B50

B51

A56

A57

B54

B55

A60

A61

B58

B59

A64

A65

B62

B63

A68

A69

B66

B67

A72

A73

B70

B71

A76

A77

B74

B75

A80

A81

B78

B79

PEX_TCLK

PEX_TDI

PEX_TDO

PEX_TMS

I2CS_SCL_R

I2CS_SDA_R

SNN_PEX_WAKE*

PEX_RST*

PEX_REFCLK

PEX_REFCLK*

PEX_TX0_C

PEX_TX0_C*

PEX_RX0

PEX_RX0*

PEX_TX1_C

PEX_TX1_C*

PEX_RX1

PEX_RX1*

PEX_TX2_C

PEX_TX2_C*

PEX_RX2

PEX_RX2*

PEX_TX3_C

PEX_TX3_C*

PEX_RX3

PEX_RX3*

PEX_TX4_C

PEX_TX4_C*

PEX_RX4

PEX_RX4*

PEX_TX5_C

PEX_TX5_C*

PEX_RX5

PEX_RX5*

PEX_TX6_C

PEX_TX6_C*

PEX_RX6

PEX_RX6*

PEX_TX7_C

PEX_TX7_C*

PEX_RX7

PEX_RX7*

PEX_TX8_C

PEX_TX8_C*

PEX_RX8

PEX_RX8*

PEX_TX9_C

PEX_TX9_C*

PEX_RX9

PEX_RX9*

PEX_TX10_C

PEX_TX10_C*

PEX_RX10

PEX_RX10*

PEX_TX11_C

PEX_TX11_C*

PEX_RX11

PEX_RX11*

PEX_TX12_C

PEX_TX12_C*

PEX_RX12

PEX_RX12*

PEX_TX13_C

PEX_TX13_C*

PEX_RX13

PEX_RX13*

PEX_TX14_C

PEX_TX14_C*

PEX_RX14

PEX_RX14*

PEX_TX15_C

PEX_TX15_C*

PEX_RX15

PEX_RX15*

R739

0

5%

0402

COMMON

C899

0402

COMMON

X5R

C891

COMMON

X5R

C882

0402

COMMON

X5R

C874

0402

COMMON

X5R

C852

0402

COMMON

X5R

C835

0402

COMMON

X5R

C817

0402

COMMON

X5R

C792

0402

COMMON

X5R

0402

COMMON

X5R

C738

0402

COMMON

X5R

C706

0402

COMMON

X5R

C681

0402

COMMON

X5R X5R

C667

0402

COMMON

X5R

C652

0402

COMMON

X5R

C646

0402

COMMON

X5R

C643

0402

COMMON

X5R

3V3_F

GND

C722

.1UF

10V

10%

X5R

0402

COMMON

C723

10V

10%

X5R

0402

COMMON

C708

.1UF

10V

10%

X5R

0402

COMMON

PEX_TEST_PLL_CLK_OUT

Termination = 200ohm

Place on bottom side

for test access

R729

10K

5%

0402

NO STUFF

C754

.1UF

10V

10%

X5R

0402

COMMON

C737

.1UF.1UF

10V

10%

X5R

0402

COMMON

C731

.1UF

10V

10%

X5R

0402

COMMON

R733

R727

180

10K

5%

5%

0402

0402

NO STUFF

NO STUFF

R682

200

5%

0402

NO STUFF

JTAG_TCLK

JTAG_TMS

JTAG_TDI

JTAG_TDO

R737

R723

270

10K

5%

5%

0402

0402

COMMON

NO STUFF

GND

.1UF

10V

10%

X5R

0402

C746

1UF

6.3V

10%

X5R

0402

C745

1UF 4.7UF

6.3V

10%

X5R

0402

COMMON

C701

1UF

6.3V

10%

X5R

0402

COMMON

C762

1UF

6.3V

10%

X5R

0402

COMMON

C707

1UF

6.3V

10%

X5R

0402

COMMON

C748

1UF

6.3V

10%

X5R

0402

COMMON

Place components within 750mils from pad

Replaced bead with 10nH inductor per SI recommendation

C760C769

1UF

6.3V

10%

X5R

0402

JTAG

G1

G92-270-A2

BGA1148

COMMON

AK6

AL8

AL7

AK7

AL9JTAG_TRST*

C873

4.7UF

6.3V

10%

X5R

0603

COMMONCOMMON

C699

6.3V

10%

X5R

0603

COMMON

C52

4.7UF

6.3V

10%

X5R

0603

COMMONCOMMONCOMMON

PEX NET RULES

NET

PEX_REFCLK

PEX_REFCLK*

PEX_TX0_C

PEX_TX0_C*

PEX_TX1_C

PEX_TX1_C*

PEX_TX2_C

PEX_TX2_C*

PEX_TX3_C

PEX_TX3_C*

PEX_TX4_C

PEX_TX4_C*

PEX_TX5_C

PEX_TX5_C*

PEX_TX6_C

PEX_TX6_C*

PEX_TX7_C

PEX_TX7_C*

1V2

C670

10UF

6.3V

20%

X5R

0805

COMMON

1V2

GND

C51

10UF

6.3V

20%

X5R

0805

COMMON

GND

1V2

10nH

L6

COMMON0402

C53

4.7UF

6.3V

10%

X5R

0603

COMMON

GND

PEX_TX8_C

PEX_TX8_C*

PEX_TX9_C

PEX_TX9_C*

PEX_TX10_C

PEX_TX10_C*

PEX_TX11_C

PEX_TX11_C*

PEX_TX12_C

PEX_TX12_C*

PEX_TX13_C

PEX_TX13_C*

PEX_TX14_C

PEX_TX14_C*

PEX_TX15_C

PEX_TX15_C*

PEX_RX0

PEX_RX1

PEX_RX1*

PEX_RX2

PEX_RX2*

PEX_RX3

PEX_RX3*

PEX_RX4

PEX_RX4*

PEX_RX5

PEX_RX5*

PEX_RX6

PEX_RX6*

PEX_RX7

PEX_RX7*

PEX_RX8

PEX_RX8*

PEX_RX9

PEX_RX9*

PEX_RX10

PEX_RX10*

PEX_RX11

PEX_RX11*

PEX_RX12

PEX_RX12*

PEX_RX13

PEX_RX13*

PEX_RX14

PEX_RX14*

PEX_RX15

PEX_RX15*

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4* 1

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

PEX_PLL_CLK_OUT

PEX_PLL_CLK_OUT*

PEX_RST*

PEX_TRST*

PEX_TCLK

PEX_TDI

PEX_TDO

PEX_TMS

JTAG_TCLK

JTAG_TMS

JTAG_TDI

JTAG_TDO

JTAG_TRST*

PEX_PLLAVDD

PEX_PLLDVDD

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1PEX_RX0*

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

3

3

3

3

3

3

3

3

3

3

3

1.2V

1.2V

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

0.25A

0.10A

600-10391-0050-000 A

p391_a00

gachen

DIFFPAIRNV_IMPEDANCENV_CRITICAL

PEX_REFCLK

PEX_REFCLK

PEX_TX0_C

PEX_TX0_C

PEX_TX1_C

PEX_TX1_C

PEX_TX2_C

PEX_TX2_C

PEX_TX3_C

PEX_TX3_C

PEX_TX4_C

PEX_TX4_C

PEX_TX5_C

PEX_TX5_C

PEX_TX6_C

PEX_TX6_C

PEX_TX7_C

PEX_TX7_C

PEX_TX8_C

PEX_TX8_C

PEX_TX9_C

PEX_TX9_C

PEX_TX10_C

PEX_TX10_C

PEX_TX11_C

PEX_TX11_C

PEX_TX12_C

PEX_TX12_C

PEX_TX13_C

PEX_TX13_C

PEX_TX14_C

PEX_TX14_C

PEX_TX15_C

PEX_TX15_C

PEX_RX0

PEX_RX0

PEX_RX1

PEX_RX1

PEX_RX2

PEX_RX2

PEX_RX3

PEX_RX3

PEX_RX4

PEX_RX4

PEX_RX5

PEX_RX5

PEX_RX6

PEX_RX6

PEX_RX7

PEX_RX7

PEX_RX8

PEX_RX8

PEX_RX9

PEX_RX9

PEX_RX10

PEX_RX10

PEX_RX11

PEX_RX11

PEX_RX12

PEX_RX12

PEX_RX13

PEX_RX13

PEX_RX14

PEX_RX14

PEX_RX15

PEX_RX15

PEX_TX0

PEX_TX0

PEX_TX1

PEX_TX1

PEX_TX2

PEX_TX2

PEX_TX3

PEX_TX3

PEX_TX4

PEX_TX4

PEX_TX5

PEX_TX5

PEX_TX6

PEX_TX6

PEX_TX7

PEX_TX7

PEX_TX8

PEX_TX8

PEX_TX9

PEX_TX9

PEX_TX10

PEX_TX10

PEX_TX11

PEX_TX11

PEX_TX12

PEX_TX12

PEX_TX13

PEX_TX13

PEX_TX14

PEX_TX14

PEX_TX15

PEX_TX15

PEX_PLL_CLK_OUT

PEX_PLL_CLK_OUT

MIN_WIDTHMAX_CURRENTVOLTAGENET

12MIL

12MIL

2.1C>

16.5A<

2 OF 29

08-AUG-2008

16.2A<

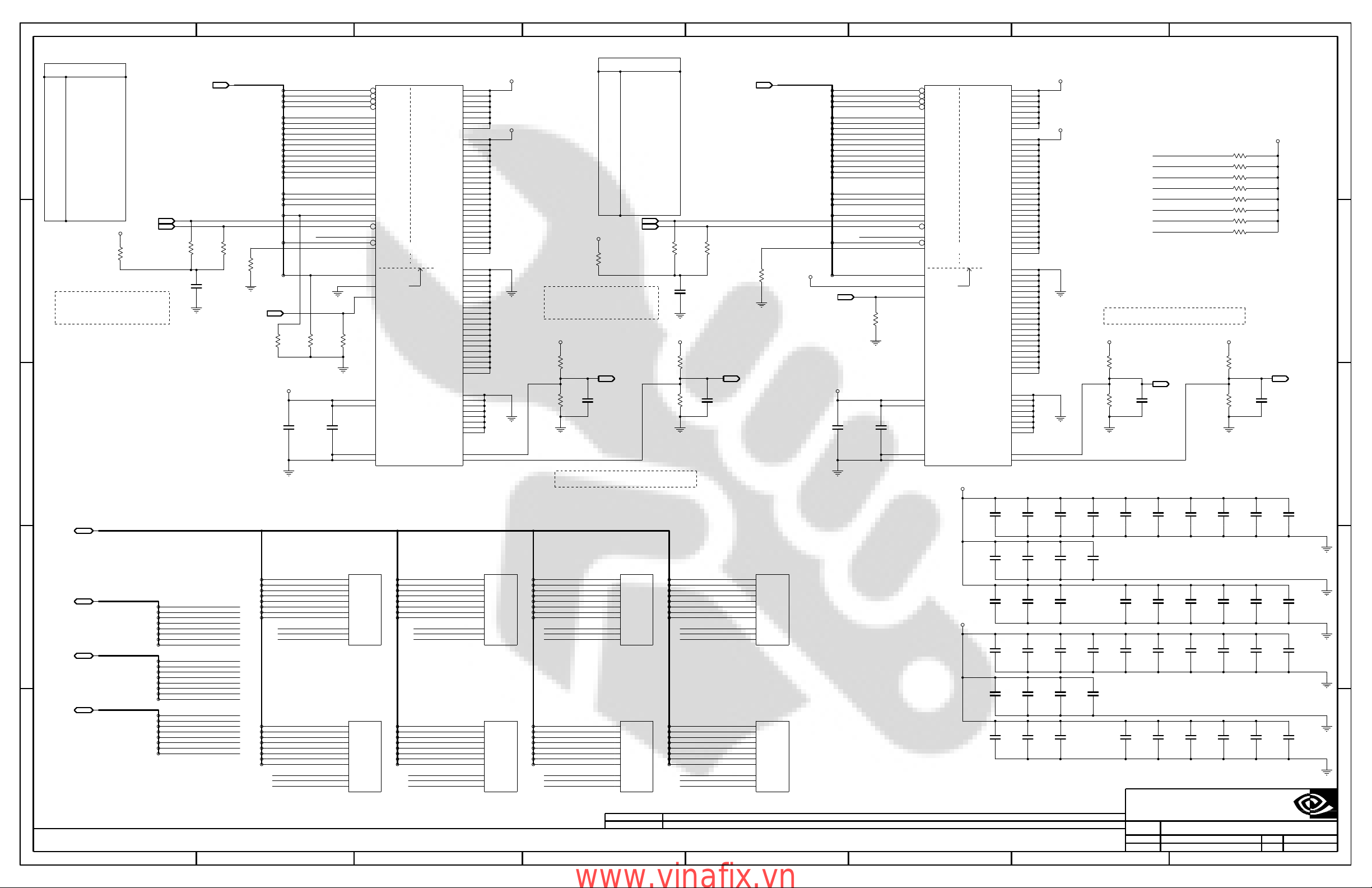

Page3: MEMORY: GPU Partition A/B

OUT

OUT

OUT

OUT

OUT

BI

3/24 MEM_B

FBB_CMD6

FBB_CMD4

FBB_CMD5

FBB_CMD3

FBB_CMD1

FBB_CMD2

FBB_CMD0

FBB_CMD7

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CMD27

FBB_CMD19

FBB_CMD18

FBB_CMD17

FBB_CMD16

FBB_CMD14

FBB_CMD15

FBB_CMD13

FBB_CMD12

FBB_CMD11

FBB_CMD9

FBB_CMD10

FBB_CMD8

FBB_CLK1

FBB_CLK0

FBB_CLK0

FBB_CMD28

FBB_CLK1

RFU

RFU

FBB_DEBUG

FBCAL1_PD_VDDQ

FBCAL1_PU_GND

FBB_PLLVDD_NC

FBCAL1_TERM_GND

FBB_PLLGND

FBBD6

FBBD4

FBBD5

FBBD3

FBBD2

FBBD1

FBBD0

FBBD7

FBBD27

FBBD26

FBBD25

FBBD24

FBBD23

FBBD22

FBBD21

FBBD19

FBBD20

FBBD17

FBBD16

FBBD15

FBBD13

FBBD12

FBBD11

FBBD9

FBBD10

FBBD8

FBBD14

FBBD18

FBBD47

FBBD46

FBBD45

FBBD44

FBBD42

FBBD43

FBBD41

FBBD40

FBBD39

FBBD37

FBBD38

FBBD36

FBBD35

FBBD34

FBBD32

FBBD33

FBBD31

FBBD30

FBBD29

FBBD28

FBBD48

FBBDQM2

FBBDQM1

FBBDQM0

FBBD62

FBBD63

FBBD60

FBBD61

FBBD59

FBBD57

FBBD58

FBBD55

FBBD56

FBBD54

FBBD53

FBBD52

FBBD50

FBBD51

FBBD49

FBBDQS_RN6

FBBDQS_WP2

FBBDQS_WP1

FBBDQS_WP0

FBBDQS_RN7

FBBDQS_RN4

FBBDQS_RN5

FBBDQS_RN3

FBBDQS_RN2

FBBDQS_RN1

FBBDQS_RN0

FBBDQM7

FBBDQM6

FBBDQM4

FBBDQM5

FBBDQM3

FBBDQS_WP3

FB_VREF2

FBBDQS_WP7

FBBDQS_WP6

FBBDQS_WP5

FBBDQS_WP4

BI

OUT

OUT

OUT

OUT

OUT

OUTINOUTBIBIBIBI

2/24 MEM_A

FBA_CMD6

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD7

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD19

FBA_CMD18

FBA_CMD17

FBA_CMD16

FBA_CMD14

FBA_CMD15

FBA_CMD13

FBA_CMD12

FBA_CMD11

FBA_CMD9

FBA_CMD10

FBA_CMD8

FBA_CMD22

FBA_CMD21

FBA_CMD20

FBA_CMD28

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

RFU

RFU

FBA_DEBUG

FBCAL0_PU_GND

FBCAL0_TERM_GND

FBCAL0_PD_VDDQ

FBA_PLLAVDD

FBA_DLLAVDD

FBA_PLLGND

FBAD6

FBAD4

FBAD5

FBAD3

FBAD2

FBAD1

FBAD0

FBAD7

FBAD20

FBAD21

FBAD26

FBAD25

FBAD24

FBAD23

FBAD22

FBAD19

FBAD17

FBAD15

FBAD12

FBAD13

FBAD11

FBAD9

FBAD10

FBAD8

FBAD27

FBAD14

FBAD16

FBAD18

FBAD45

FBAD44

FBAD42

FBAD41

FBAD37

FBAD38

FBAD36

FBAD35

FBAD32

FBAD33

FBAD31

FBAD30

FBAD29

FBAD28

FBAD46

FBAD40

FBAD39

FBAD43

FBAD34

FBAD47

FBAD48

FBAD60

FBADQM2

FBADQM1

FBAD61

FBAD58

FBAD57

FBAD55

FBAD56

FBAD54

FBAD53

FBAD52

FBAD51

FBAD50

FBAD49

FBAD59

FBADQM0

FBAD63

FBAD62

FBADQS_WP2

FBADQS_RN7

FBADQS_RN5

FBADQS_RN3

FBADQS_RN2

FBADQM4

FBADQM3

FBADQS_RN6

FBADQS_RN4

FBADQM7

FBADQM6

FBADQM5

FBADQS_RN1

FBADQS_RN0

FBADQS_WP0

FBADQS_WP1

FBADQS_WP3

FBADQS_WP5

FBADQS_WP4

FBADQS_WP7

FBADQS_WP6

FB_VREF1

OUTINOUT

BI

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

G1

G92-270-A2

BGA1148

AH35

AH36

AH34

AJ34

AK36

AJ36

AK34

AL34

AH32

AK33

AJ33

AH33

AL33

AN32

AN33

AN31

AE32

AF30

AF32

AE30

AE31

AC30

AC32

AD30

AG36

AG34

AF36

AD36

AD34

AD35

AE34

AP36

AN35

AM34

AP35

AP34

AP33

AT34

AR34

AM22

AM25

AN26

AN24

AK24

AL22

AK23

AM23

AT32

AT33

AR33

AP31

AR30

AT30

AP30

AT29

AP26

AP27

AT25

AP25

AR28

AP28

AT28

AP29

AK35

AF33

AF34

AN34

AM24

AP32

AR27

AL35

AK32

AG33

AE36

AM36

AN22

AR31

AT27FBA_DQS_RN<7>

AL36

AL32

AG32

AE35

AN36

AN23

AT31

AT26

J29

COMMON

CALIBRATION PIN

FB_CALx_PD_VDDQ

FB_CALx_PU_GND

FB_CALx_TERM_GND

VREF RATIO

DDR3

60

40

40

0.7 FBVDDQ

FBA_CMD<0>

AK28

FBA_CMD<1>

AK29

FBA_CMD<2>

AN30

FBA_CMD<3>

AM27

FBA_CMD<4>

AN28

FBA_CMD<5>

AL29

AM30

FBA_CMD<6>

FBA_CMD<7>

AJ31

FBA_CMD<8>

AK31

FBA_CMD<9>

AH31

FBA_CMD<10>

AK25

FBA_CMD<11>

AM26

FBA_CMD<12>

AL31

FBA_CMD<13>

AN29

FBA_CMD<14>

AK27

FBA_CMD<15>

AK26

FBA_CMD<16>

AN27

FBA_CMD<17>

AL25

FBA_CMD<18>

AJ30

FBA_CMD<19>

AM31

FBA_CMD<20>

AH30

FBA_CMD<21>

AL30

FBA_CMD<22>

AH29

FBA_CMD<23>

AL28

FBA_CMD<24>

AH28

FBA_CMD<25>

AM28

SNN_FBA_CMD_26AG30

SNN_FBA_CMD_27

AG28

SNN_FBA_CMD_28

AF28

FBA_CLK0

AH26

FBA_CLK0*

AH27

FBA_CLK1

AJ29

FBA_CLK1*

AJ28

SNN_FBA_RFU0

AJ24

SNN_FBA_RFU1AH24

FBA_DEBUG

AH25

FB_CAL_PD_VDDQ0

J28

FB_CAL_PU_GND0

H28

FB_CAL_TERM_GND0

H29

FBAB_PLLAVDD

AC29

AD29

AE29

GND

Place components as close

as possible to the pad

C687

.1UF

10V

10%

X5R

0402

COMMON

GND

C668

.1UF

10V

10%

X5R

0402

COMMON

GND

FBA_D<63..0>

FBA_DQM<7..0>

FBA_DQS_RN<7..0>

FBA_DQS_WP<7..0>

FBVDD

R657

549

1%

0402

COMMON

R647

1.33K

1%

0402

COMMON

GND

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

FBA_D<0>

FBA_D<1>

FBA_D<2>

FBA_D<3>

FBA_D<4>

FBA_D<5>

FBA_D<6>

FBA_D<7>

FBA_D<8>

FBA_D<9>

FBA_D<10>

FBA_D<11>

FBA_D<12>

FBA_D<13>

FBA_D<14>

FBA_D<15>

FBA_D<16>

FBA_D<17>

FBA_D<18>

FBA_D<19>

FBA_D<20>

FBA_D<21>

FBA_D<22>

FBA_D<23>

FBA_D<24>

FBA_D<25>

FBA_D<26> AG35

FBA_D<27>

FBA_D<28>

FBA_D<29>

FBA_D<30>

FBA_D<31>

FBA_D<32>

FBA_D<33>

FBA_D<34>

FBA_D<35>

FBA_D<36>

FBA_D<37>

FBA_D<38>

FBA_D<39>

FBA_D<40>

FBA_D<41>

FBA_D<42>

FBA_D<43>

FBA_D<44>

FBA_D<45>

FBA_D<46>

FBA_D<47>

FBA_D<48>

FBA_D<49>

FBA_D<50>

FBA_D<51>

FBA_D<52>

FBA_D<53>

FBA_D<54>

FBA_D<55>

FBA_D<56>

FBA_D<57>

FBA_D<58>

FBA_D<59>

FBA_D<60>

FBA_D<61>

FBA_D<62>

FBA_D<63>

FBA_DQM<0>

FBA_DQM<1> AM33

FBA_DQM<2>

FBA_DQM<3>

FBA_DQM<4>

FBA_DQM<5>

FBA_DQM<6>

FBA_DQM<7>

FBA_DQS_RN<0>

FBA_DQS_RN<1>

FBA_DQS_RN<2>

FBA_DQS_RN<3>

FBA_DQS_RN<4>

FBA_DQS_RN<5>

FBA_DQS_RN<6>

FBA_DQS_WP<0>

FBA_DQS_WP<1>

FBA_DQS_WP<2>

FBA_DQS_WP<3>

FBA_DQS_WP<4>

FBA_DQS_WP<5>

FBA_DQS_WP<6>

FBA_DQS_WP<7>

FB_VREF1

9.2B<> 5.4A<>

9.2B> 5.4A<>

9.2B< 5.4A<>

9.2B> 5.5A<>

9.4B<>

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

C686

.1UF

10V

10%

X5R

0402

COMMON

0

1

2

3

4

5

6

7

8

9

FBA_CMD<28..0>

FBVDD

R667

60.4

1%

0402

NO STUFF

5.2A<

5.2A<

5.2D<

5.2D<

9.3B<>

136BGA CMD Mapping

CMD

CMD0

CMD1 RAS*

CMD2

CMD3

CMD4

CMD5

CMD6

CMD8

CMD9

CMD10

CMD12

CMD13

CMD14

CMD15

CMD16

CMD17

CMD18

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25

9.1B>

CMD26

9.1B>

CMD27

9.1B>

CMD28

9.1B>

9.2B<>

R656

0402

1%

R655

0402

1%

R652

0402

1%

240R@100MHz

LB501

C705

C676

4.7UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0402

COMMON

COMMON

Place these components within

750 mils of the pad

60.4

COMMON

40.2

COMMON

40.2

COMMON

5.1E< 5.1A<

ADDR

A<4>

A<5>

BA1

A<2>

A<4>

A<3>

BA2CMD7

CS0*

A<11>

CAS*

WE*CMD11

BA0

A<5>

A<12>

RST

A<7>

A<10>

CKE

A<0>

A<9>

A<6>

A<2>

A<8>

A<3>

A<1>

A<13>

BA2

N/A

FBVDD

GND

1V2

COMMONBEAD_0402

GND

P391 G92 512MB GDDR3 16Mx32 DVI-I+DVI-I

MEMORY: GPU Partition A/B

C703

4.7UF

6.3V

10%

X5R

0603

COMMON

6.4A<> 9.2B<> 9.1B>

9.2B> 6.4A<>

6.4A<>

9.2B<

6.5A<>

9.2B>

9.4B<>

www.vinafix.vn

FBB_D<63..0>

FBB_DQM<7..0>

FBB_DQS_RN<7..0>

FBB_DQS_WP<7..0>

C685

.1UF

10V

10%

X5R

0402

COMMON

GND

FBVDD

GND

R665

549

1%

0402

COMMON

R664

1.33K

1%

0402

COMMON

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

FBB_D<0>

0

FBB_D<1>

1

FBB_D<2>

2

FBB_D<3>

3

FBB_D<4>

4

FBB_D<5>

5

FBB_D<6>

6

FBB_D<7>

7

FBB_D<8>

8

FBB_D<9>

9

FBB_D<10>

10

FBB_D<11>

11

FBB_D<12>

12

FBB_D<13>

13

FBB_D<14>

14

FBB_D<15>

15

FBB_D<16>

16

FBB_D<17>

17

FBB_D<18>

18

FBB_D<19>

19

FBB_D<20>

20

FBB_D<21>

21

FBB_D<22>

22

FBB_D<23>

23

FBB_D<24>

24

FBB_D<25>

25

FBB_D<26>

26

FBB_D<27>

27

FBB_D<28>

28

FBB_D<29>

29

FBB_D<30>

30

FBB_D<31>

31

FBB_D<32>

32

FBB_D<33>

33

FBB_D<34>

34

FBB_D<35>

35

FBB_D<36>

36

FBB_D<37>

37

FBB_D<38>

38

FBB_D<39>

39

FBB_D<40>

40

FBB_D<41>

41

FBB_D<42>

42

FBB_D<43>

43

FBB_D<44>

44

FBB_D<45>

45

FBB_D<46>

46

FBB_D<47>

47

FBB_D<48>

48

FBB_D<49>

49

FBB_D<50>

50

FBB_D<51>

51

FBB_D<52>

52

FBB_D<53>

53

FBB_D<54>

54

FBB_D<55>

55

FBB_D<56>

56

FBB_D<57>

57

FBB_D<58>

58

FBB_D<59>

59

FBB_D<60>

60

FBB_D<61>

61

FBB_D<62>

62

FBB_D<63>

63

FBB_DQM<0>

FBB_DQM<1>

FBB_DQM<2>

FBB_DQM<3>

FBB_DQM<4>

FBB_DQM<5>

FBB_DQM<6>

FBB_DQM<7>

FBB_DQS_RN<0>

FBB_DQS_RN<1>

FBB_DQS_RN<2>

FBB_DQS_RN<3>

FBB_DQS_RN<4>

FBB_DQS_RN<5>

FBB_DQS_RN<6>

FBB_DQS_RN<7>

FBB_DQS_WP<0>

FBB_DQS_WP<1>

FBB_DQS_WP<2>

FBB_DQS_WP<3>

FBB_DQS_WP<4>

FBB_DQS_WP<5>

FBB_DQS_WP<6>

FBB_DQS_WP<7>

FB_VREF2

G1

G92-270-A2

BGA1148

COMMON

G36

G35

H36

H34

J35

J34

K34 T30

K35

J31

K32

J30

H30

L32

K30

M31

L30

G31

J32

J33

F33

H31

E33

F31

F32

F35

G34

F36

F34

C35

D34

C36

D35

N35

M34

L34

N36

P36

P34

R36

R34

AC33

Y33

Y30

AB30

AA32

AD32

AD33

AA33

T36

R35

T34

U36

W35

U34

V34

W36

AC36

AA36

AC34

AB34

AA35

Y34

Y36

W34

J36

M32

H33

E34

N34

Y32

T35

AA34

L36

K33

G32

E36

M36

AB32

V35

AB35

K36

L33

G33

D36

M35

AB31

V36

AB36

J27

FBB_CMD<0>

P33

FBB_CMD<1>

N33

FBB_CMD<2>

R31

FBB_CMD<3>

U33

FBB_CMD<4>

V30

FBB_CMD<5>

T33

FBB_CMD<6>

FBB_CMD<7>

N32

FBB_CMD<8>

R32

FBB_CMD<9>

P32

FBB_CMD<10>

U32

FBB_CMD<11>

U30

FBB_CMD<12>

P30

FBB_CMD<13>

V31

FBB_CMD<14>

T28

FBB_CMD<15>

W30

FBB_CMD<16>

V32

FBB_CMD<17>

T32

FBB_CMD<18>

N30

FBB_CMD<19>

P28

FBB_CMD<20>

P29

FBB_CMD<21>

U29

FBB_CMD<22>

N28

FBB_CMD<23>

R30

FBB_CMD<24>

M30

FBB_CMD<25>

T29

SNN_FBB_CMD_26

N29

SNN_FBB_CMD_27

AA30

SNN_FBB_CMD_28

Y29

FBB_CLK0

M28

FBB_CLK0*

L28

FBB_CLK1

W31

FBB_CLK1*

W32

SNN_FBB_RFU0

R28

SNN_FBB_RFU1

K29

FBB_DEBUG

C34

FB_CAL_PD_VDDQ1

H27

FB_CAL_PU_GND1

H26

FB_CAL_TERM_GND1

J26

SNN_FBB_PLLVDD_NC

AB28

AC28

GND

FBB_CMD<28..0>

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

9.2B>

6.2A<

9.2B>

6.2A<

9.2B>

6.2D<

9.2B>

6.2D<

FBVDD

R648

60.4

1%

0402

NO STUFF

9.2B<>

60.4

R660

COMMON

0402

1%

40.2

R663

COMMON

0402

1%

40.2

R661

COMMON

0402

1%

600-10391-0050-000 A

p391_a00

gachen

9.2B> 6.1E< 6.1B<

FBVDD

GND

3 OF 29

08-AUG-2008

Page4: MEMORY: GPU Partition C/D

OUT

OUT

OUT

OUT

OUT

BI

5/24 MEM_D

FBD_CMD0

FBD_CMD1

FBD_CMD2

FBD_CMD3

FBD_CMD5

FBD_CMD4

FBD_CMD6

FBD_CMD7

FBD_CMD21

FBD_CMD20

FBD_CMD19

FBD_CMD8

FBD_CMD10

FBD_CMD9

FBD_CMD11

FBD_CMD12

FBD_CMD13

FBD_CMD14

FBD_CMD15

FBD_CMD16

FBD_CMD17

FBD_CMD18

FBD_CMD23

FBD_CMD22

FBD_CMD27

FBD_CMD26

FBD_CMD25

FBD_CMD24

FBD_CLK1

FBD_CLK1

FBD_CLK0

FBD_CLK0

FBD_CMD28

RFU

RFU

FBD_DEBUG

FBD_PLLVDD_NC

FBD_PLLGND

FBDD0

FBDD1

FBDD2

FBDD3

FBDD4

FBDD5

FBDD6

FBDD7

FBDD9

FBDD21

FBDD25

FBDD8

FBDD10

FBDD11

FBDD12

FBDD13

FBDD15

FBDD14

FBDD16

FBDD17

FBDD18

FBDD20

FBDD19

FBDD22

FBDD23

FBDD24

FBDD26

FBDD27

FBDD28

FBDD29

FBDD30

FBDD31

FBDD33

FBDD32

FBDD36

FBDD35

FBDD38

FBDD37

FBDD40

FBDD41

FBDD39

FBDD42

FBDD43

FBDD44

FBDD45

FBDD46

FBDD47

FBDD34

FBDD48

FBDD57

FBDD58

FBDD59

FBDD60

FBDD49

FBDD50

FBDD51

FBDD52

FBDD53

FBDD54

FBDD56

FBDD55

FBDD61

FBDD62

FBDD63

FBDDQM0

FBDDQM2

FBDDQM1

FBDDQM3

FBDDQM5

FBDDQM4

FBDDQM6

FBDDQM7

FBDDQS_RN0

FBDDQS_RN1

FBDDQS_RN2

FBDDQS_RN3

FBDDQS_RN6

FBDDQS_RN4

FBDDQS_RN7

FBDDQS_WP0

FBDDQS_WP1

FBDDQS_WP2

FBDDQS_RN5

FBDDQS_WP3

FBDDQS_WP4

FBDDQS_WP5

FBDDQS_WP6

FBDDQS_WP7

BI

OUT

OUT

OUT

OUT

OUT

OUTINOUTBIBI

BI

4/24 MEM_C

FBC_CMD6

FBC_CMD5

FBC_CMD4

FBC_CMD3

FBC_CMD2

FBC_CMD1

FBC_CMD0

FBC_CMD7

FBC_CMD24

FBC_CMD25

FBC_CMD21

FBC_CMD22

FBC_CMD23

FBC_CMD20

FBC_CMD19

FBC_CMD18

FBC_CMD17

FBC_CMD16

FBC_CMD15

FBC_CMD14

FBC_CMD13

FBC_CMD12

FBC_CMD11

FBC_CMD10

FBC_CMD9

FBC_CMD8

FBC_CMD26

FBC_CMD27

FBC_CMD28

FBC_CLK1

FBC_CLK1

FBC_CLK0

FBC_CLK0

RFU

RFU

FBC_DEBUG

FBC_DLLAVDD

FBC_PLLAVDD

FBC_PLLVDD_NC

FBC_PLLGND

FBCD5

FBCD3

FBCD1

FBCD6

FBCD4

FBCD2

FBCD0

FBCD7

FBCD16

FBCD19

FBCD27

FBCD26

FBCD25

FBCD22

FBCD23

FBCD20

FBCD13

FBCD9

FBCD8

FBCD14

FBCD15

FBCD17

FBCD12

FBCD24

FBCD21

FBCD18

FBCD11

FBCD10

FBCD29

FBCD28

FBCD33

FBCD35

FBCD47

FBCD45

FBCD46

FBCD44

FBCD43

FBCD42

FBCD39

FBCD41

FBCD40

FBCD37

FBCD32

FBCD30

FBCD36

FBCD34

FBCD31

FBCD38

FBCD48

FBCD60

FBCD63

FBCDQM0

FBCDQM2

FBCDQM1

FBCD62

FBCD61

FBCD57

FBCD58

FBCD59

FBCD55

FBCD56

FBCD53

FBCD54

FBCD51

FBCD50

FBCD49

FBCD52

FBCDQM5

FBCDQM4

FBCDQM6

FBCDQM7

FBCDQS_RN0

FBCDQS_RN1

FBCDQS_RN2

FBCDQS_RN4

FBCDQS_RN5

FBCDQS_RN6

FBCDQS_RN7

FBCDQS_WP0

FBCDQS_WP1

FBCDQS_WP2

FBCDQS_RN3

FBCDQM3

FBCDQS_WP3

FBCDQS_WP4

FBCDQS_WP5

FBCDQS_WP6

FBCDQS_WP7

OUTINOUT

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

G1

G92-270-A2

BGA1148

C18

C17

A17

B16

C14

A16

C15

A14

A18

A19

B19

B18

B21

C19

B22

C21

E15

D16

D17

G16

E16

E14

G13

D13

A22

C22

A23

A24

C24

C25

B24

C28

B27

C27

B28

C29

A29

B30

A30

E31

E28

D28

F29

F30

D33

D32

D31

G27

F25

G26

D26

G29

G28

E27

F28

A34

C32

B34

C33

C31

B31

A31

C30

C16

G14

C26

A28

D29

D27

B33

B15

A21

D14

B25

A27

E30

E25

A33

A15

A20

E13

A25

A26

D30

E26

A32FBC_DQS_WP<7>

COMMON

F18

H20

E18

E20

D23

G24

D24

G23

D20

E22

J21

E21

G20

F22

H21

E17

E19

D21

E23

F19

E24

G21

G19

G25

G18

G22

F15

G15

J16

J24

H23

H24

J25

H16

H13

J12

J13

GND

FBC_CMD<0>

FBC_CMD<1>

FBC_CMD<2>

FBC_CMD<3>

FBC_CMD<4>

FBC_CMD<5>

FBC_CMD<6>

FBC_CMD<7>

FBC_CMD<8>

FBC_CMD<9>

FBC_CMD<10>

FBC_CMD<11>

FBC_CMD<12>

FBC_CMD<13>

FBC_CMD<14>

FBC_CMD<15>

FBC_CMD<16>

FBC_CMD<17>

FBC_CMD<18>

FBC_CMD<19>

FBC_CMD<20>

FBC_CMD<21>

FBC_CMD<22>

FBC_CMD<23>

FBC_CMD<24>

FBC_CMD<25>

SNN_FBC_CMD_26G17

SNN_FBC_CMD_27

SNN_FBC_CMD_28

FBC_CLK0H17

FBC_CLK0*

FBC_CLK1

FBC_CLK1*

SNN_FBC_RFU0

SNN_FBC_RFU1

FBC_DEBUG

SNN_FBC_PLLVDD_NC

FBCD_PLLAVDDJ11

C802

.1UF

10V

10%

X5R

0402

COMMON

Place components as close

as possible to the pad

FBC_D<63..0>

FBC_DQM<7..0>

FBC_DQS_RN<7..0>

FBC_DQS_WP<7..0>

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

FBC_D<0>

FBC_D<1>

FBC_D<2>

FBC_D<3>

FBC_D<4>

FBC_D<5>

FBC_D<6>

FBC_D<7>

FBC_D<8>

FBC_D<9>

FBC_D<10>

FBC_D<11>

FBC_D<12>

FBC_D<13>

FBC_D<14>

FBC_D<15>

FBC_D<16>

FBC_D<17>

FBC_D<18>

FBC_D<19>

FBC_D<20>

FBC_D<21>

FBC_D<22>

FBC_D<23>

FBC_D<24>

FBC_D<25>

FBC_D<26> C23

FBC_D<27>

FBC_D<28>

FBC_D<29>

FBC_D<30>

FBC_D<31>

FBC_D<32>

FBC_D<33>

FBC_D<34>

FBC_D<35>

FBC_D<36>

FBC_D<37>

FBC_D<38>

FBC_D<39>

FBC_D<40>

FBC_D<41>

FBC_D<42>

FBC_D<43>

FBC_D<44>

FBC_D<45>

FBC_D<46>

FBC_D<47>

FBC_D<48>

FBC_D<49>

FBC_D<50>

FBC_D<51>

FBC_D<52>

FBC_D<53>

FBC_D<54>

FBC_D<55>

FBC_D<56>

FBC_D<57>

FBC_D<58>

FBC_D<59>

FBC_D<60>

FBC_D<61>

FBC_D<62>

FBC_D<63>

FBC_DQM<0>

FBC_DQM<1> C20

FBC_DQM<2>

FBC_DQM<3>

FBC_DQM<4>

FBC_DQM<5>

FBC_DQM<6>

FBC_DQM<7>

FBC_DQS_RN<0>

FBC_DQS_RN<1>

FBC_DQS_RN<2>

FBC_DQS_RN<3>

FBC_DQS_RN<4>

FBC_DQS_RN<5>

FBC_DQS_RN<6>

FBC_DQS_RN<7>

FBC_DQS_WP<0>

FBC_DQS_WP<1>

FBC_DQS_WP<2>

FBC_DQS_WP<3>

FBC_DQS_WP<4>

FBC_DQS_WP<5>

FBC_DQS_WP<6>

9.2E<> 7.4A<>

9.2E> 7.4A<>

9.2E< 7.4A<>

9.2E> 7.5A<>

GND

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

FBVDD

C815

.1UF

10V

10%

X5R

0402

COMMON

FBC_CMD<28..0>

7.2A<

7.2D<

7.2D<

R669

60.4

1%

0402

NO STUFF

136BGA CMD Mapping

CMD

CMD0

CMD1 RAS*

CMD2

CMD3

CMD4

CMD5

CMD6

CMD7

CMD8

CMD9

CMD10

CMD11 WE*

CMD12

CMD13

CMD14

CMD15

CMD16

CMD17

CMD18

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25

9.1E> 7.2A<

CMD26

9.1E>

CMD27

9.1E>

CMD28

9.1E>

9.2E<>

9.3E<>

240R@100MHz

C814

1UF

6.3V

10%

X5R

0402

COMMON

Place these components within

750 mils of the pad

LB503

BEAD_0402

C793

4.7UF

6.3V

10%

X5R

0603

COMMON

7.1E< 7.1A<

ADDR

A<4>

A<5>

BA1

A<2>

A<4>

A<3>

BA2

CS0*

A<11>

CAS*

BA0

A<5>

A<12>

RST

A<7>

A<10>

CKE

A<0>

A<9>

A<6>

A<2>

A<8>

A<3>

A<1>

A<13>

BA2

N/A

1V2

COMMON

GND

P391 G92 512MB GDDR3 16Mx32 DVI-I+DVI-I

MEMORY: GPU Partition C/D

C772

4.7UF

6.3V

10%

X5R

0603

COMMON

8.4A<> 9.2E<> 9.1E>

9.2E> 8.4A<>

8.4A<>

9.2E<

8.5A<>

9.2E>

www.vinafix.vn

FBD_D<63..0>

FBD_DQM<7..0>

FBD_DQS_RN<7..0>

FBD_DQS_WP<7..0>

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

FBD_D<0>

0

FBD_D<1>

1

FBD_D<2>

2

FBD_D<3>

3

FBD_D<4>

4

FBD_D<5>

5

FBD_D<6>

6

FBD_D<7>

7

FBD_D<8>

8

FBD_D<9>

9

FBD_D<10>

10

FBD_D<11>

11

FBD_D<12>

12

FBD_D<13>

13

FBD_D<14>

14

FBD_D<15>

15

FBD_D<16>

16

FBD_D<17>

17

FBD_D<18>

18

FBD_D<19>

19

FBD_D<20>

20

FBD_D<21>

21

FBD_D<22>

22

FBD_D<23>

23

FBD_D<24>

24

FBD_D<25>

25

FBD_D<26>

26

FBD_D<27>

27

FBD_D<28>

28

FBD_D<29>

29

FBD_D<30>

30

FBD_D<31>

31

FBD_D<32>

32

FBD_D<33>

33

FBD_D<34>

34

FBD_D<35>

35

FBD_D<36>

36

FBD_D<37>

37

FBD_D<38>

38

FBD_D<39>

39

FBD_D<40>

40

FBD_D<41>

41

FBD_D<42>

42

FBD_D<43>

43

FBD_D<44>

44

FBD_D<45>

45

FBD_D<46>

46

FBD_D<47>

47

FBD_D<48>

48

FBD_D<49>

49

FBD_D<50>

50

FBD_D<51>

51

FBD_D<52>

52

FBD_D<53>

53

FBD_D<54>

54

FBD_D<55>

55

FBD_D<56>

56

FBD_D<57>

57

FBD_D<58>

58

FBD_D<59>

59

FBD_D<60>

60

FBD_D<61>

61

FBD_D<62>

62

FBD_D<63>

63

FBD_DQM<0>

FBD_DQM<1>

FBD_DQM<2>

FBD_DQM<3>

FBD_DQM<4>

FBD_DQM<5>

FBD_DQM<6>

FBD_DQM<7>

FBD_DQS_RN<0>

FBD_DQS_RN<1>

FBD_DQS_RN<2>

FBD_DQS_RN<3>

FBD_DQS_RN<4>

FBD_DQS_RN<5>

FBD_DQS_RN<6>

FBD_DQS_RN<7>

FBD_DQS_WP<0>

FBD_DQS_WP<1>

FBD_DQS_WP<2>

FBD_DQS_WP<3>

FBD_DQS_WP<4>

FBD_DQS_WP<5>

FBD_DQS_WP<6>

FBD_DQS_WP<7>

G1

G92-270-A2

BGA1148

COMMON

H3

J3

J1

J2

M3

K3

L3 F8

M1

H1

G3

G1

G2

F3

E1

D1

D2

P4

N7

M7

N5

P5

R7

T7

P7

C1

C5

C2

B4

A3

B3

C4

C3

A8

C6

C7

A7

C8

C9

A9

B9

E12

E9

F9

G10

D10

G12

F12

D11

F4

E4

D4

D5

D8

E7

D7

D9

B13

C11

A13

C13

A11

A10

B10

C10

K2

E3

N4

D3

B7

G11

F5

C12

K1

F2

R6

A4

B6

E10

E6

A12

L1

F1

R5

A5

A6

E11

D6

B12

FBD_CMD<0>

M6

FBD_CMD<1>

G5

FBD_CMD<2>

L7

FBD_CMD<3>

K5

FBD_CMD<4>

J10

FBD_CMD<5>

G8

FBD_CMD<6>

FBD_CMD<7>

G6

FBD_CMD<8>

H6

FBD_CMD<9>

F6

FBD_CMD<10>

K8

FBD_CMD<11>

L5

FBD_CMD<12>

H4

FBD_CMD<13>

G4

FBD_CMD<14>

K9

FBD_CMD<15>

L4

FBD_CMD<16>

K4

FBD_CMD<17>

K7

FBD_CMD<18>

G7

FBD_CMD<19>

J4

FBD_CMD<20>

F7

FBD_CMD<21>

J5

FBD_CMD<22>

J6

FBD_CMD<23>

H7

FBD_CMD<24>

L8

FBD_CMD<25>

J7

SNN_FBD_CMD_26

M5

SNN_FBD_CMD_27

H9

SNN_FBD_CMD_28

G9

FBD_CLK0

L9

FBD_CLK0*

M9

FBD_CLK1

J9

FBD_CLK1*

J8

SNN_FBD_RFU0

H10

SNN_FBD_RFU1

L11

FBD_DEBUG

N8

SNN_FBD_PLLVDD_NC

H11

H12

GND

FBD_CMD<28..0>

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

9.2E>

8.2A<

9.2E>

8.2A<

9.2E>

8.2D<

9.2E>

8.2D<

FBVDD

R678

60.4

1%

0402

NO STUFF

9.2E<>

600-10391-0050-000 A

p391_a00

gachen

9.2E> 8.1E< 8.1B<

4 OF 29

08-AUG-2008

Page5: FBA Partition

OUT

OUTININININ

MIRROR

*CS1 is required 32Mx32 Memories

NONMIRROR

VDD

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSSQ

VSS

VREF

VREF

VSS

CKE

BA2

CAS

WE

CS0

RAS

BA0

BA1

A7

A8/AP

A3

A10

A11

A2

A1

A0

A9

A6

A5

A4

NC/CS1

RAS

CAS

CS0

A0

WE

A5

A4

A3

A2

A1

A8/AP

A10

A11

BA0

BA1

A7

A6

A9

BA2

NC/CS1

CKE

CLK

CLK

NC/RFU

SEN (GND)

MIRROR

RESET

ZQ

VDDA

VDDA

VSSA

VSSA

OUT

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

IN

OUT

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

MIRROR

*CS1 is required 32Mx32 Memories

NONMIRROR

VDD

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSSQ

VSS

VREF

VREF

VSS

CKE

BA2

CAS

WE

CS0

RAS

BA0

BA1

A7

A8/AP

A3

A10

A11

A2

A1

A0

A9

A6

A5

A4

NC/CS1

RAS

CAS

CS0

A0

WE

A5

A4

A3

A2

A1

A8/AP

A10

A11

BA0

BA1

A7

A6

A9

BA2

NC/CS1

CKE

CLK

CLK

NC/RFU

SEN (GND)

MIRROR

RESET

ZQ

VDDA

VDDA

VSSA

VSSA

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

INININBIBIBIBI

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

136BGA CMD Mapping

ADDR

RAS*

CAS*

WE*

CS0*

BA2

BA0

BA1

A<12>

A<0>

A<1>

0A<2> CMD22

0A<3>

0A<4>

0A<5>

1A<2>

1A<3>

1A<4>

1A<5>

A<6>

A<7>

A<8>

A<9>

A<10>

A<11>

CKE

RST

136MAP

CMD1

CMD10

CMD11

CMD8

CMD7

CMD12

CMD3

CMD14

CMD19

CMD25

CMD24

CMD0

CMD2

CMD4

CMD6

CMD5

CMD13

CMD21

CMD16

CMD23

CMD20

CMD17

CMD9

CMD18

CMD15

3.1D> 9.1B> 5.1E<

3.2D>

9.1B>

3.2D>

9.1B>

FBVDD

243

R600

121

1%

0402

NO STUFF

FBA_CLK0_MIDPT

COMMON

C541

.01UF

16V

10%

X7R

0402

COMMON

0402

1%

GND

Clock Term MUST BE PLACED as close

as possible to the BGA memory on

the line AFTER the memory pin!

Minimize STUB length!

R602R604

243

0402

COMMON

1%

FBA_CMD<28..0>

R617

1K

5%

0402

COMMON

GND

9.3B<>

1

10

11

8

19

25

22

24

0

2

21

16

23

20

17

9

12

3

7

18

14

15

FBVDD

R611

10K

5%

COMMON

GND

FBA_CMD<1>

FBA_CMD<10>

FBA_CMD<11>

FBA_CMD<8>

FBA_CMD<19>

FBA_CMD<25>

FBA_CMD<22>

FBA_CMD<24>

FBA_CMD<0>

FBA_CMD<2>

FBA_CMD<21>

FBA_CMD<16>

FBA_CMD<23>

FBA_CMD<20>

FBA_CMD<17>

FBA_CMD<9>

FBA_CMD<12>

FBA_CMD<3>

FBA_CMD<7>

FBA_CMD<18>

FBA_CLK0

FBA_CLK0*

SNN_FBA_NC0

FBA_CMD<14>

FBA_DEBUG_SEN0

FBA_CMD<15>

FBA_ZQ0

R601

10K

5%

COMMON

C62

.047UF

16V

10%

X7R

COMMON

GND

GND

C579

.047UF

16V

10%

X7R

04020402

COMMON

R80

243

1%

040204020402

COMMON

H11

K10

K11

H10

J11

J10

K12

J12

M6

H5RS5223CFR-N2C

PACK_TYPE=BGA136_V2

VERSION=BGA136

CHANGED

H3

F4

H9

F9

K4

H2

K3

M4

K9

L9

M9

K2

L4

G4

G9

H4

J2

J3

V4

V9

A9

A4

K1

1%

1%

1%

1%

1%

1%

1%

1%

121

COMMON

121

COMMON

121

COMMON

121

COMMON

121

COMMON

121

COMMON

121

COMMON

121

COMMON

R619

549

0402

COMMON

R620

1.33K

0402

COMMON

FBVDD

1%

1%

GND

FBVDD

R1

R2

C592

.1UF

10V

10%

X5R

0402

COMMON

9.3B<>

FBVDD

F1

M1

A2

V2

A11

V11

F12

M12

A1

C1

E1

N1

R1

V1

C4

E4

J4

N4

R4

C9

E9

J9

N9

R9

A12

C12

E12

N12

R12

V12

B1

D1

P1

T1

G2

L2

B4

D4

P4

T4

B9

D9

P9

T9

G11

L11

B12

D12

P12

T12

G1

L1

A3

V3

A10

V10

G12

L12

H1J1

H12

FBA_VREF0

FBA_VREF2

FBVDD

GND

GND

136BGA CMD Mapping

ADDR

RAS*

CAS*

WE*

CS0*

BA2

BA0

BA1

A<12>

A<0>

A<1>

0A<2>

0A<3> CMD24

0A<4>

0A<5>

1A<2>

1A<3>

1A<4>

1A<5>

A<6>

A<7>

A<8>

A<9>

A<10>

A<11>

CKE

RST

Clock Term MUST BE PLACED as close

as possible to the BGA memory on

the line AFTER the memory pin!

Minimize STUB length!

549

1%

0402

COMMON

R626

1.33K

1%

0402

COMMON

GND

GDDR3:

136MAP

CMD1

CMD10

CMD11

CMD8

CMD7

CMD12

CMD3

CMD14

CMD19

CMD25

CMD22

CMD0

CMD2

CMD4

CMD6

CMD5

CMD13

CMD21

CMD16

CMD23

CMD20

CMD17

CMD9

CMD18

CMD15

3.2D>

9.1B>

3.2D>

9.1B>

FBVDD

R633

121

1%

0402

NO STUFF

FBA_CLK1_MIDPT

FBVDDFBVDD

R85R618

549

R1

9.3B<>

C596

.1UF

R2

10V

10%

X5R

0402

COMMON

0402

COMMON

R86

1.33K

0402

COMMON

R1

1%

R2

1%

GND

VREF = 0.70 * FBVDDQ

1.41V = 2.0V * 1.33K/(549 + 1.33K)

243

0402

COMMON

1%

C63

.1UF

10V

10%

X5R

0402

COMMON

GND

R634R635

243

0402

COMMON

C611

.01UF

16V

10%

X7R

0402

COMMON

1%

9.3B<>

M7

H5RS5223CFR-N2C

PACK_TYPE=BGA136_V2

VERSION=BGA136

R81

243

1%

0402

COMMON

H11

K10

K11

H10

J11

J10

K12

J12

CHANGED

H3

F4

H9

F9

K4

H2

K3

M4

K9

L9

M9

K2

L4

G4

G9

H4

J2

J3

V4

V9

A9

A4

K1

J1

F1

M1

A2

V2

A11

V11

F12

M12

A1

C1

E1

N1

R1

V1

C4

E4

J4

N4

R4

C9

E9

J9

N9

R9

A12

C12

E12

N12

R12

V12

B1

D1

P1

T1

G2

L2

B4

D4

P4

T4

B9

D9

P9

T9

G11

L11

B12

D12

P12

T12

G1

L1

A3

V3

A10

V10

G12

L12

H1

H12

FBVDD

3.1D> 5.1A< 9.1B>

FBA_CMD<28..0>

R609

0402

5%

FBVDD

1K

COMMON

9.3B<>

7

8

18

10

5

13

21

20

19

25

4

9

17

6

23

16

3

12

1

11

14

FBA_DEBUG_SEN1

15

FBA_CMD<7>

FBA_CMD<8>

FBA_CMD<18>

FBA_CMD<10>

FBA_CMD<5>

FBA_CMD<13>

FBA_CMD<21>

FBA_CMD<20>

FBA_CMD<19>

FBA_CMD<25>

FBA_CMD<4>

FBA_CMD<9>

FBA_CMD<17>

FBA_CMD<6>

FBA_CMD<23>

FBA_CMD<16>

FBA_CMD<3>

FBA_CMD<12>

FBA_CMD<1>

FBA_CMD<11>

FBA_CLK1

FBA_CLK1*

SNN_FBA_NC1

FBA_CMD<14>

FBA_CMD<15>

FBA_ZQ1

GND

GND

FBVDD

C558

.047UF

16V

10%

X7R

0402

COMMON

C64

.047UF

16V

10%

X7R

0402

COMMON

GND

FBA_VREF1

FBA_VREF3

FBVDD

FBVDD

GND

GND

R87

549

0402

COMMON

R88

1.33K

0402

COMMON

FBA_CMD<4>

FBA_CMD<6>

FBA_CMD<5>

FBA_CMD<13>

FBA_CMD<22>

FBA_CMD<24>

FBA_CMD<0>

FBA_CMD<2>

VREF = 0.70 * FBVDDQ

GDDR3:

1.41V = 2.0V * 1.33K/(549 + 1.33K)

FBVDD

R1

1%

C65

.1UF

R2

1%

10V

10%

X5R

0402

COMMON

GND

9.3B<>

R631

0402

R621

0402

R610

0402

R605

0402

R622

0402

R629

0402

R616

0402

R612

0402

3.1A<> 9.2B<>

3.3A>

3.4A<

3.4A> 9.2B>

FBA_D<63..0>

FBA_DQM<7..0>

FBA_DQS_RN<7..0>

FBA_DQS_WP<7..0>

M6

H5RS5223CFR-N2C

PACK_TYPE=BGA136_V2

VERSION=BGA136

CHANGED

FBA_D<0>

0

FBA_D<1>

1

FBA_D<2>

2

FBA_D<3>

3

FBA_D<4>

4

FBA_DQM<0>

0

FBA_DQM<1>

1

FBA_DQM<2>

2

FBA_DQM<3>

3

FBA_DQM<4>

4

FBA_DQM<5>

5

FBA_DQM<6>

6

FBA_DQM<7>

7

FBA_DQS_RN<0>

0

FBA_DQS_RN<1>

1

FBA_DQS_RN<2>

2

FBA_DQS_RN<3>

3

FBA_DQS_RN<4>

4

FBA_DQS_RN<5>

5

FBA_DQS_RN<6>

6

FBA_DQS_RN<7>

7

FBA_DQS_WP<0>

0

FBA_DQS_WP<1>

1

FBA_DQS_WP<2>

2

FBA_DQS_WP<3>

3

FBA_DQS_WP<4>

4

FBA_DQS_WP<5>

5

FBA_DQS_WP<6>

6

FBA_DQS_WP<7>

7

5

6

7

32

33

34

35

36

37

38

39

FBA_D<5>

FBA_D<6>

FBA_D<7>

FBA_DQM<0>

FBA_DQS_RN<0>

FBA_DQS_WP<0>

FBA_D<32>

FBA_D<33>

FBA_D<34>

FBA_D<35>

FBA_D<36>

FBA_D<37>

FBA_D<38>

FBA_D<39>

FBA_DQM<4>

FBA_DQS_RN<4>

FBA_DQS_WP<4>

N2

M3

L3

M2

T2

R3

R2

T3

N3

P3

P2

M7

H5RS5223CFR-N2C

PACK_TYPE=BGA136_V2

VERSION=BGA136

CHANGED

T11

R10

T10

R11

N11

M11

L10

M10

N10

P10

P11

8

9

10

11

12

13

14

15

40

41

42

43

44

45

46

47

FBA_D<8>

FBA_D<9>

FBA_D<10>

FBA_D<11>

FBA_D<12>

FBA_D<13>

FBA_D<14>

FBA_D<15>

FBA_DQM<1>

FBA_DQS_RN<1>

FBA_DQS_WP<1>

FBA_D<40>

FBA_D<41>

FBA_D<42>

FBA_D<43>

FBA_D<44>

FBA_D<45>

FBA_D<46>

FBA_D<47>

FBA_DQM<5>

FBA_DQS_RN<5>

FBA_DQS_WP<5>

M6

H5RS5223CFR-N2C

PACK_TYPE=BGA136_V2

VERSION=BGA136

CHANGED

L10

M10

M11

N11

R10

T11

R11

T10

N10

P10

P11

M7

H5RS5223CFR-N2C

PACK_TYPE=BGA136_V2

VERSION=BGA136

CHANGED

E2

F3

G3

B3

C2

B2

C3

F2

E3

D3

D2

16

17

18

19

20

21

22

23

48

49

50

51

52

53

54

55

FBA_D<16>

FBA_D<17>

FBA_D<18>

FBA_D<19>

FBA_D<20>

FBA_D<21>

FBA_D<22>

FBA_D<23>

FBA_DQM<2>

FBA_DQS_RN<2>

FBA_DQS_WP<2>

FBA_D<48>

FBA_D<49>

FBA_D<50>

FBA_D<51>

FBA_D<52>

FBA_D<53>

FBA_D<54>

FBA_D<55>

FBA_DQM<6>

FBA_DQS_RN<6>

FBA_DQS_WP<6>

M6

H5RS5223CFR-N2C

PACK_TYPE=BGA136_V2

VERSION=BGA136

CHANGED

F10

E11

C10

G10

F11

B10

B11

C11

E10

D10

D11

M7

H5RS5223CFR-N2C

PACK_TYPE=BGA136_V2

VERSION=BGA136

CHANGED

E11

F10

G10

F11

B10

B11

C11

C10

E10

D10

D11

24

25

26

27

28

29

30

31

56

57

58

59

60

61

62

63

FBA_D<24>

FBA_D<25>

FBA_D<26>

FBA_D<27>