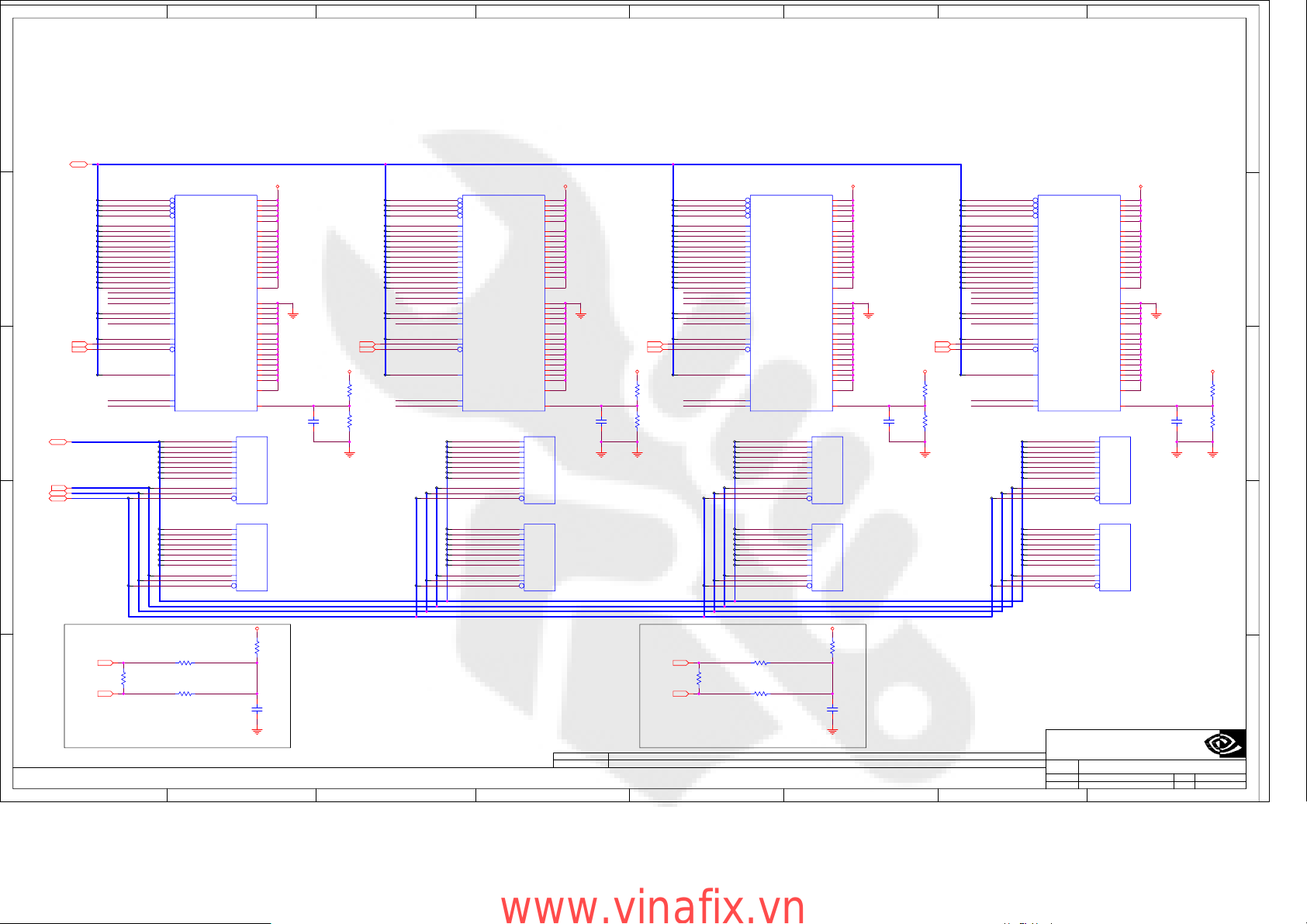

MSI MS-V133 Schematic 0A

A B C D E F G H

V133-0A

1

P729: G96, DDR2 MEMORY 32MX16/16MX16

Page 1: P729 Overview

Page 2: PCI Express Interface

Page 3: Partition A Frame Buffer Interface

Page 4: Partition C Frame Buffer Interface

Page 5: Partition A Memories

2

Page 6: Partition C Memories

Page 7: Decoupling Caps

Page 8: DACA

Page 9: DACC, Slim DB15 Connector

Page 10: Internal TMDS .. Link A & B

Page 11: Internal TMDS .. Link C & D

Page 12: DACB, MINIDIN Connector

Page 13: MIOA, MIOB Interface

3

Page 14: Thermal Sensors, GPIOs, XTAL, JTAG, Fan

Page 15: BIOS, HDCP, SPDIF, HDA, Mechanical

REV HISTORY

Modify Power Sequencing

01/21 : PAGE 19.Add R100 R102 R103 R104 R105 Q100

PAGE 20.Add R101 R106 R107

PAGE 15.Add U100 U101 U102 U103 for EMI solution

PAGE 19.Add C100 C101 C102 C103 C104 to 12V_F power reserve

01/22 : PAGE 10.Add R111 R112 R113 R114 R115 R116 R117 for EMI bridge

PAGE 11.Add R121 R122 R123 R124 R125 R126 R127 for EMI bridge

PAGE 19.Add FBCDDQ to GND CAP C105 C106 C107 C108

C109 C110 C111 C112 for EMI solution

PAGE 19.Add 12V_F to GND CAP C113 C114 C115 C116 C117 for EMI solution

PAGE 18.Add 3V3_PEX to GND CAP C118 C119 for EMI solution

Nvidia updata Circuit

01/22 : PAGE 18 : remove PEX_RST

PAGE 11 : Add bias voltage resistor R130 R131

Link GPIO10_IFPCD_PD

PAGE 13 : Change new SLI connector for better EMI.

(please refer to the symbol/part on P545)

PAGE 14 : revise fan circuit . Add C120 J9

PAGE 16 : change strape power to 2.5V

1

2

3

Page 16: Straps

Page 17: Hybrid Power

Page 18: Power Supply I: 2V5, 3V3, 5V, IFP_IOVDD

Page 19: Power Supply II: FBVDDQ

Nvidia modify Power circuit

01/22 : PAGE 19 : remove R100 R101 R102 R103 R628 R633 C85 Q13 L12

PAGE 19 : Add C121 C122

PAGE 19 : change P.20 LDO to P.19

Page 20: Power Supply III: NVVDD, PEX_VDD

4

4

VARIANT ASSEMBLY

SKU

BASE

B

SKU0000

1

2

<UNDEFINED>

3

<UNDEFINED>

4

<UNDEFINED>

5

<UNDEFINED>

<UNDEFINED>

6

<UNDEFINED>

7

<UNDEFINED>

8

<UNDEFINED>

9

<UNDEFINED>

10

<UNDEFINED>

11

<UNDEFINED>

12

<UNDEFINED>

13

5

<UNDEFINED>

14

<UNDEFINED>

15

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR O THERWISE, AND EXPRESSLY DISCLAIMS ALL

NVPN

600-10729-xxxx-000

600-10729-0000-000

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

G96-300-A1, 550/500MHz, 512MB 32Mx16 DDR2 BGA84 DVI-DL+VGA+HDTV

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

C GE

www.vinafix.vn

ASSEMBLY

PAGE DETAIL

Nvidia updata Circuit

01/29 : PAGE 15 : Change R602 to 2.2k ohm, C727 to 10k ohm, R598 to 75 ohm

PAGE 16 : Straps ROM_SI, ROM_SO,ROM_SCLK should still pull high to 3V3_PEX

PAGE 14 : Please use correct BJT for Q23, Q24,Q25,Q31,Q32

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

P729 Overview

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10729-xxxx-000 A

NAMEIMPLIED WARR ANTIES INCLU DING, WITHO UT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

5

PAGEID

DATE

26-OCT-2007

HFDBA

A B C D E F G H

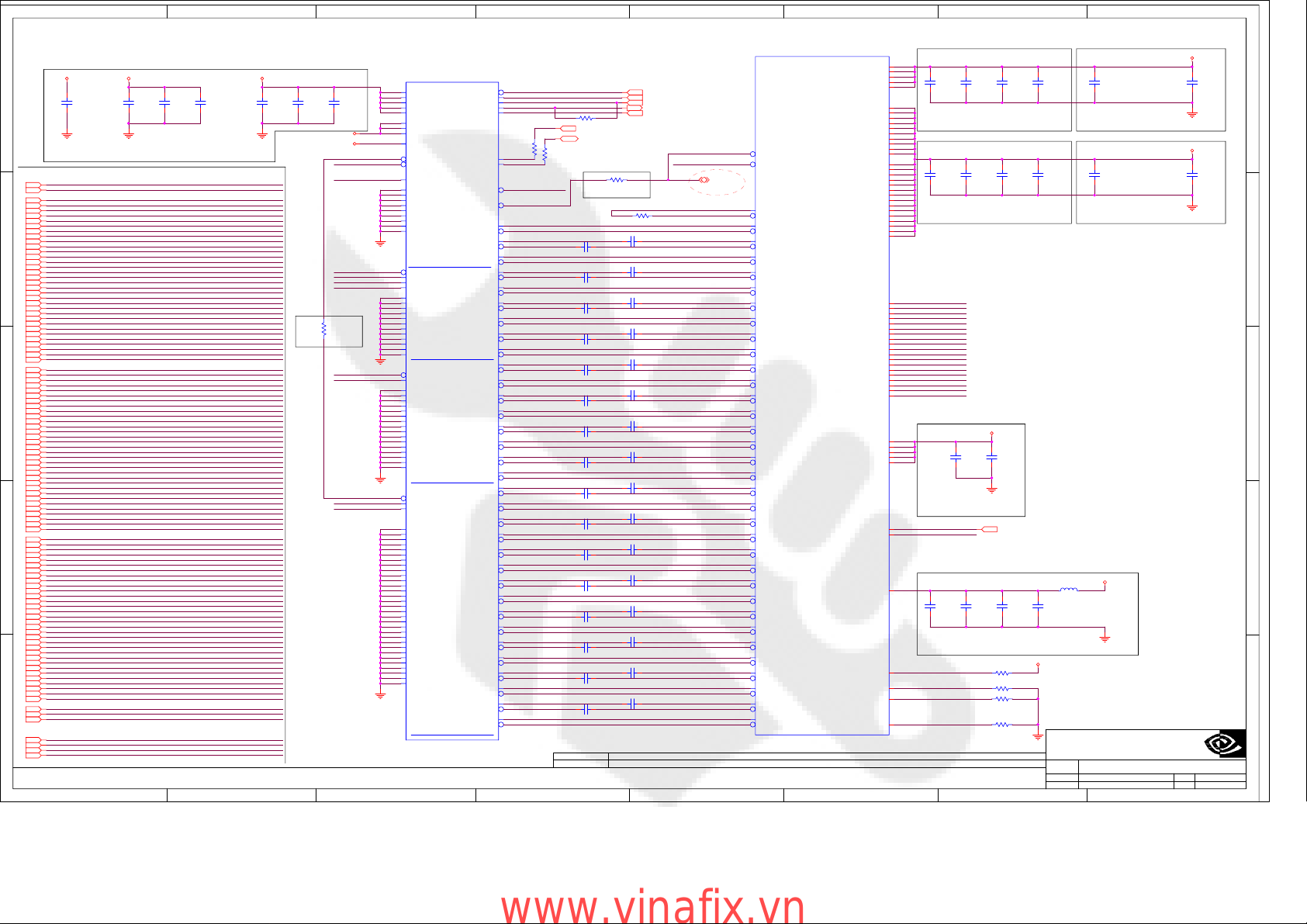

PCI Express Interface

C54

.01UF

16V

10%

X7R

0402

C11-1032012-W08

3V3_PEX

C45

10UF

6.3V

20%

X5R

0805

C11-1067014-T04

C729

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

3V3_PEX

1

GND GND

PLACE NEAR FINGERS

Net Name

PEX_PLL_CLK_OUT

IN

PEX_PLL_CLK_OUT*

IN

PEX_TXX0

IN

PEX_TXX0*

IN

PEX_TXX1

IN

PEX_TXX1*

IN

PEX_TXX2

IN

PEX_TXX2*

IN

PEX_TXX3

IN

PEX_TXX3*

IN

PEX_TXX4

IN

2

3

4

5

PEX_TXX4*

IN

PEX_TXX5

IN

PEX_TXX5*

IN

PEX_TXX6

IN

PEX_TXX6*

IN

PEX_TXX7

IN

PEX_TXX7*

IN

PEX_TXX8

IN

PEX_TXX8*

IN

PEX_TXX9

IN

PEX_TXX9*

IN

PEX_TXX10

IN

PEX_TXX10*

IN

PEX_TXX11

IN

PEX_TXX11*

IN

PEX_TXX12

IN

PEX_TXX12*

IN

PEX_TXX13

IN

PEX_TXX13*

IN

PEX_TXX14

IN

PEX_TXX14*

IN

PEX_TXX15

IN

PEX_TXX15*

IN

PEX_TX0

IN

PEX_TX0*

IN

PEX_TX1

IN

PEX_TX1*

IN

PEX_TX2

IN

PEX_TX2*

IN

PEX_TX3

IN

PEX_TX3*

IN

PEX_TX4

IN

PEX_TX4*

IN

PEX_TX5

IN

PEX_TX5*

IN

PEX_TX6

IN

PEX_TX6*

IN

PEX_TX7

IN

PEX_TX7*

IN

PEX_TX8

IN

PEX_TX8*

IN

PEX_TX9

IN

PEX_TX9*

IN

PEX_TX10

IN

PEX_TX10*

IN

PEX_TX11

IN

PEX_TX11*

IN

PEX_TX12

IN

PEX_TX12*

IN

PEX_TX13

IN

PEX_TX13*

IN

PEX_TX14

IN

PEX_TX14*

IN

PEX_TX15

IN

PEX_TX15*

IN

PEX_RX0

IN

PEX_RX0*

IN

PEX_RX1

IN

PEX_RX1*

IN

PEX_RX2

IN

PEX_RX2*

IN

PEX_RX3

IN

PEX_RX3*

IN

PEX_RX4

IN

PEX_RX4*

IN

PEX_RX5

IN

PEX_RX5*

IN

PEX_RX6

IN

PEX_RX6*

IN

PEX_RX7

IN

PEX_RX7*

IN

PEX_RX8

IN

PEX_RX8*

IN

PEX_RX9

IN

PEX_RX9*

IN

PEX_RX10

IN

PEX_RX10*

IN

PEX_RX11

IN

PEX_RX11*

IN

PEX_RX12

IN

PEX_RX12*

IN

PEX_RX13

IN

PEX_RX13*

IN

PEX_RX14

IN

PEX_RX14*

IN

PEX_RX15

IN

PEX_RX15*

IN

PEX_REFCLK

IN

PEX_REFCLK*

IN

GPU_TESTMODE

IN

Net Name

PEX_PLLVDD

IN

PEX_CAL_PD_VDD Q

IN

PEX_CAL_PU_GN D

IN

PEX_TERMP

IN

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR O THERWISE, AND EXPRESSLY DISCLAIMS ALL

PEX_PLL_CLK_OUT 90DIFF1

PEX_PLL_CLK_OUT 1 90DIFF

PEX_TXX0 1 90DIFF

PEX_TXX0 1 90DIFF

PEX_TXX1 1 90DIFF

PEX_TXX1 1 90DIFF

PEX_TXX2 1 90DIFF

PEX_TXX2 1 90DIFF

PEX_TXX3 1 90DIFF

PEX_TXX3 1 90DIFF

PEX_TXX4 1 90DIFF

PEX_TXX4 1 90DIFF

PEX_TXX5 1 90DIFF

PEX_TXX5 1 90DIFF

PEX_TXX6 1 90DIFF

PEX_TXX6 1 90DIFF

PEX_TXX7 1 90DIFF

PEX_TXX7 1 90DIFF

PEX_TXX8 1 90DIFF

PEX_TXX8 1 90DIFF

PEX_TXX9 1 90DIFF

PEX_TXX9 1 90DIFF

PEX_TXX10 1 90DIFF

PEX_TXX11 1 90DIFF

PEX_TXX11 1 90DIFF

PEX_TXX12 1 90DIFF

PEX_TXX12 1 90DIFF

PEX_TXX13 1 90DIFF

PEX_TXX13 1 90DIFF

PEX_TXX14 1 90DIFF

PEX_TXX14 1 90DIFF

PEX_TXX15 1 90DIFF

PEX_TXX15 1 90DIFF

PEX_TXX0 1 90DIFF

PEX_TXX0 1 90DIFF

PEX_TXX1 1 90DIFF

PEX_TXX1 1 90DIFF

PEX_TXX2 1 90DIFF

PEX_TXX2 1 90DIFF

PEX_TXX3 1 90DIFF

PEX_TXX3 1 90DIFF

PEX_TXX4 1 90DIFF

PEX_TXX4 1 90DIFF

PEX_TXX5 1 90DIFF

PEX_TXX5 1 90DIFF

PEX_TXX6 1 90DIFF

PEX_TXX6 1 90DIFF

PEX_TXX7 1 90DIFF

PEX_TXX7 1 90DIFF

PEX_TXX8 1 90DIFF

PEX_TXX8 1 90DIFF

PEX_TXX9 1 90DIFF

PEX_TXX9 1 90DIFF

PEX_TXX10 90DIFF1

PEX_TXX10 1 90DIFF

PEX_TXX11 1 90DIFF

PEX_TXX11 1 90DIFF

PEX_TXX12 1 90DIFF

PEX_TXX13 1 90DIFF

PEX_TXX14 1 90DIFF

PEX_TXX14 1 90DIFF

PEX_TXX15 1 90DIFF

PEX_TXX15 1 90DIFF

PEX_RX0 1 90DIFF

PEX_RX0 1 90DIFF

PEX_RX1 1 90DIFF

PEX_RX1 1 90DIFF

PEX_RX2 1 90DIFF

PEX_RX2 1 90DIFF

PEX_RX3 1 90DIFF

PEX_RX3 1 90DIFF

PEX_RX4 1 90DIFF

PEX_RX4 1 90DIFF

PEX_RX5 1 90DIFF

PEX_RX5 1 90DIFF

PEX_RX6 1 90DIFF

PEX_RX6 1 90DIFF

PEX_RX7 1 90DIFF

PEX_RX7 1 90DIFF

PEX_RX8 1 90DIFF

PEX_RX8 1 90DIFF

PEX_RX9 1 90DIFF

PEX_RX9 1 90DIFF

PEX_RX10 1 90DIFF

PEX_RX10 1 90DIFF

PEX_RX11 1 90DIFF

PEX_RX11 1 90DIFF

PEX_RX12 1 90DIFF

PEX_RX12 1 90DIFF

PEX_RX13 1 90DIFF

PEX_RX13 1 90DIFF

PEX_RX14 1 90DIFF

PEX_RX15 1 90DIFF

PEX_RX15 1 90DIFF

MIN_LINE_WIDTH VOLTAGE MAX_CURRENT

12MIL

12MIL

12MIL

NV_CRITICAL_NETDIFF_PAIR

1PEX_TXX12 90DIFF

1PEX_TXX13 90DIFF

3 50OHM

1.1V12MIL 0.12A

C50

.01UF

16V

10%

X7R

0402

C11-1032012-W08

NV_IMPEDANCE

90DIFFPEX_TXX10 1

90DIFFPEX_RX14 1

100DIFF1PEX_REFCLK

100DIFFPEX_REFCLK 1

12V_PEX

GND

C30

10UF

16V

10%

X5R

0805

C11-1067527-T04

C737

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

R620

0

5%

0402

R11-0000012-Y01

C735

.01UF

16V

10%

X7R

0402

C11-1032012-W08

3V3_PEX

3V3_PEX

SNN_PE_RSVD1

SNN_PE_PRSNT2_B

SNN_PE_RSVD2

SNN_PE_RSVD3

SNN_PE_RSVD4

Hybrid

Power

Bypass

SNN_PE_PRSNT2_C

SNN_PE_RSVD5

SNN_PE_RSVD6

SNN_PE_RSVD7

GND

GND

GND

GND

CN2

CON_FINGER_PEX_164_B

CON_X16

B1

+12V

B2

+12V

A2

+12V

A3

+12V

B3

+12V/RSVD

B8

+3V3

A9

+3V3

A10

+3V3

B10

+3V3AUX

A1

PRSNT1

B17

PRSNT2

B12

RSVD

B4

GND

A4

GND

B7

GND

A12

GND

B13

GND

A15

GND

B16

GND

B18

GND

A18

GND

B31

PRSNT2

A19

RSVD

B30

RSVD

A32

RSVD

A20

GND

B21

GND

B22

GND

A23

GND

A24

GND

B25

GND

B26

GND

A27

GND

A28

GND

B29

GND

A31

GND

B32

GND

B48

PRSNT2

A33

RSVD

A34

GND

B35

GND

B36

GND

A37

GND

A38

GND

B39

GND

B40

GND

A41

GND

A42

GND

B43

GND

B44

GND

A45

GND

A46

GND

B47

GND

B49

GND

A49

GND

B81

PRSNT2

A50

RSVD

B82

RSVD

A51

GND

B52

GND

B53

GND

A54

GND

A55

GND

B56

GND

B57

GND

A58

GND

A59

GND

B60

GND

B61

GND

A62

GND

A63

GND

B64

GND

B65

GND

A66

GND

A67

GND

B68

GND

B69

GND

A70

GND

A71

GND

B72

GND

B73

GND

A74

GND

A75

GND

B76

GND

B77

GND

A78

GND

A79

GND

B80

GND

A82

GND

END OF X1

END OF X4

END OF X8

END OF X16

TRST* JTAG1

TCLK JTAG2

TDI JTAG3

TDO JTAG4

TMS JTAG5

SMCLK

SMDAT

REFCLK

REFCLK

PERP10

PERN10

PETP10

PETN10

PERP11

PERN11

PETP11

PETN11

PERP12

PERN12

PETP12

PETN12

PERP13

PERN13

PETP13

PETN13

PERP14

PERN14

PETP14

PETN14

PERP15

PERN15

PETP15

PETN15

PERST

PERP0

PERN0

PETP0

PETN0

PERP1

PERN1

PETP1

PETN1

PERP2

PERN2

PETP2

PETN2

PERP3

PERN3

PETP3

PETN3

PERP4

PERN4

PETP4

PETN4

PERP5

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PERN8

PETP8

PETN8

PERP9

PERN9

PETP9

PETN9

PEX_TRST*

B9

PEX_TCLK

A5

PEX_TDI

A6

PEX_TDO

A7

PEX_TMS

A8

R27

0

5%

0402

B5

<New PN>

B6

SNN_PEX_WAKE*

B11

WAKE

PEX_RST*

A11

PEX_REFCLK

A13

PEX_REFCLK*

A14

PEX_TXX0

A16

PEX_TXX0*

A17

PEX_RX0

B14

PEX_RX0*

B15

PEX_TXX1

A21

PEX_TXX1*

A22

PEX_RX1

B19

PEX_RX1*

B20

PEX_TXX2

A25

PEX_TXX2*

A26

PEX_RX2

B23

PEX_RX2*

B24

PEX_TXX3

A29

PEX_TXX3*

A30

PEX_RX3

B27

PEX_RX3*

B28

PEX_TXX4

A35

PEX_TXX4*

A36

PEX_RX4

B33

PEX_RX4*

B34

PEX_TXX5

A39

PEX_TXX5*

A40

PEX_RX5

B37

PEX_RX5*

B38

PEX_TXX6

A43

PEX_TXX6*

A44

PEX_RX6

B41

PEX_RX6*

B42

PEX_TXX7

A47

PEX_TXX7*

A48

PEX_RX7

B45

PEX_RX7*

B46

PEX_TXX8

A52

PEX_TXX8*

A53

PEX_RX8

B50

PEX_RX8*

B51

PEX_TXX9

A56

PEX_TXX9*

A57

PEX_RX9

B54

PEX_RX9*

B55

PEX_TXX10

A60

PEX_TXX10*

A61

PEX_RX10

B58

PEX_RX10*

B59

PEX_TXX11

A64

PEX_TXX11*

A65

PEX_RX11

B62

PEX_RX11*

B63

PEX_TXX12

A68

PEX_TXX12*

A69

PEX_RX12

B66

PEX_RX12*

B67

PEX_TXX13

A72

PEX_TXX13*

A73

PEX_RX13

B70

PEX_RX13*

B71

PEX_TXX14

A76

PEX_TXX14*

A77

PEX_RX14

B74

PEX_RX14*

B75

PEX_TXX15

A80

PEX_TXX15*

A81

PEX_RX15

B78

PEX_RX15*

B79

C GE

R25

0

5%

0402

<New PN>

ASSEMBLY

PAGE DETAIL

14,14

IN

14,14

IN

14,14

IN

14,14

OUT

14,14

R612

0402

5%

IN

I2CS_SCL_R

BI

I2CS_SDA_R

C720

0402 X5R

C702

0402 X5R

C693

0402

C690

0402

C680

0402

C670

0402

C654

0402

C638

C621

0402 X5R

C609

0402

C590

C577

C575

0402

C573

0402

C568

0402

C559

0402

IN

0

14,14

<New PN>

14

200

5%

<New PN>

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

.1UF

C11-1047522-Y01

SNN_PEX_CLKREQ*SNN_PE_PRSNT2_A

PEX_RST

PEX_PLL_CLK_OUT

PEX_PLL_CLK_OUT*

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

PEX_RST 2

R595 0

0402

5%

R11-0000012-Y01

Hybrid Power Bypass

R545

0402

16V

X5R10%0402

.1UF

C719

16V 10%

C11-1047522-Y01

16V

X5R0402 10%

.1UF

C703

16V 10%

C11-1047522-Y01

16V

X5R10%0402

.1UF

C697

16V X5R10%

C11-1047522-Y01

16V

X5R10%0402

.1UF

C691

16V X5R10%

C11-1047522-Y01

16V X5R10%0402

.1UF

C682

16V X5R10%

C11-1047522-Y01

16V

X5R10%0402

.1UF

C673

16V X5R10%

C11-1047522-Y01

16V

X5R10%0402

C662

.1UF

16V X5R10%

C11-1047522-Y01

16V

X5R10%0402

C640

.1UF

16V X5R10%0402

C11-1047522-Y01

16V

X5R0402 10%

C627

.1UF

16V 10%

C11-1047522-Y01

16V X5R10%

0402

C614

.1UF

16V X5R10%

C11-1047522-Y01

16V

X5R10%0402

C591

.1UF

16V X5R10%0402

C11-1047522-Y01

16V

X5R10%0402

C580

.1UF

16V X5R0402 10%

C11-1047522-Y01

16V

0402 X5R10%

C576

.1UF

16V X5R10%

C11-1047522-Y01

16V

10%0402 X5R

C574

.1UF

16V X5R10%

C11-1047522-Y01

16V

X5R10%0402

C569

.1UF

16V X5R10%

C11-1047522-Y01

16V

X5R10%0402

C563

.1UF

16V X5R10%

C11-1047522-Y01

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

PCI Express Interface

AM16

AR13

AJ17

AJ18

AR16

AR17

AL17

AM17

AP17

AN17

AM18

AM19

AN19

AP19

AL19

AK19

AR19

AR20

AL20

AM20

AP20

AN20

AM21

AM22

AN22

AP22

AL22

AK22

AR22

AR23

AL23

AM23

AP23

AN23

AM24

AM25

AN25

AP25

AL25

AK25

AR25

AR26

AL26

AM26

AP26

AN26

AM27

AM28

AN28

AP28

AL28

AK28

AR28

AR29

AK29

AL29

AP29

AN29

AM29

AM30

AN31

AP31

AM31

AM32

AR31

AR32

AN32

AP32

AR34

AP34

G1A

BGA_0969_P080_290X290

1/16 PCI_EXPRESS

PEX_RST

PEX_CLKREQ

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_RX0

PEX_RX0

PEX_TX1

PEX_TX1

PEX_RX1

PEX_RX1

PEX_TX2

PEX_TX2

PEX_RX2

PEX_RX2

PEX_TX3

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX4

PEX_TX4

PEX_RX4

PEX_RX4

PEX_TX5

PEX_TX5

PEX_RX5

PEX_RX5

PEX_TX6

PEX_TX6

PEX_RX6

PEX_RX6

PEX_TX7

PEX_TX7

PEX_RX7

PEX_RX7

PEX_TX8

PEX_TX8

PEX_RX8

PEX_RX8

PEX_TX9

PEX_TX9

PEX_RX9

PEX_RX9

PEX_TX10

PEX_TX10

PEX_RX10

PEX_RX10

PEX_TX11

PEX_TX11

PEX_RX11

PEX_RX11

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX14

PEX_TX14

PEX_RX14

PEX_RX14

PEX_TX15

PEX_TX15

PEX_RX15

PEX_RX15

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

NC_17

NC_18

NC_19

VDD33_1

VDD33_2

VDD33_3

VDD33_4

VDD33_5

VDD_SENSE

GND_SENSE

PEX_PLLVDD

PEX_RFU1

PEX_RFU2

PEX_TERMP

TESTMODE

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

AK16

AK17

AK21

AK24

AK27

AG11

AG12

AG13

AG15

AG16

AG17

AG18

AG22

AG23

AG24

AG25

AG26

AJ14

AJ15

AJ19

AJ21

AJ22

AJ24

AJ25

AJ27

AK18

AK20

AK23

AK26

AL16

A2

AB7

AD6

AF6

AG6

AJ5

AK15

AL7

D35

E35

E7

F7

H32

M7

P6

P7

R7

U7

V6

J10

J11

J12

J13

J9

AD20

AD19

AG14

AG19

AG20

AG21

AP35

1.920 Amps

C626

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

PLACE NEAR BALLS

0.600 Amps

C622

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

PLACE NEAR BALLS

SNN_GPU_NC1

SNN_GPU_NC2

SNN_GPU_NC3

SNN_GPU_NC4

SNN_GPU_NC5

SNN_GPU_NC6

SNN_GPU_NC7

SNN_GPU_NC8

SNN_GPU_NC9

SNN_GPU_NC10

SNN_GPU_NC11

SNN_GPU_NC12

SNN_GPU_NC13

SNN_GPU_NC14

SNN_GPU_NC15

SNN_GPU_NC16

SNN_GPU_NC17

SNN_GPU_NC18

SNN_GPU_NC19

0.140 Amps

C651

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

PLACE NEAR BALLS

NVVDD_SENSE

SNN_GND_SENSE

0.120 Amps

PEX_PLLVDD

C646

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

PLACE NEAR BALLS

PEX_CAL_PD_VDD Q

PEX_CAL_PU_GN D

PEX_TERMP

GPU_TESTMODE

C613

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

C631

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

3V3_PEX

GND

IN

C647

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

R546

0402

R544

0402

R540

0402

R531

0402

C606

1UF

6.3V

10%

X5R

0402

C11-1057322-T04

C635

1UF

6.3V

10%

X5R

0402

C11-1057322-T04

C641

1UF

6.3V

10%

X5R

0402

C11-1057322-T04

20

C648

1UF

6.3V

10%

X5R

0402

C11-1057322-T04

2.49K

1%

<New PN>

2.49K

1%

2.49K

<New PN>

1%

R11-2491T12-Y01

10K

5%

R11-0103012-Y01

C599

1UF

6.3V

10%

X5R

0402

C11-1057322-T04

PLACE NEAR GPU

C628

1UF

6.3V

10%

X5R

0402

C11-1057322-T04

PLACE NEAR GPU

LB503 10nH

IND_SMD_0603

C645

L01-10CA013-T34

1UF

6.3V

10%

X5R

0402

C11-1057322-T04

PEX_VDD

NVIDIA CORPORATION

GND

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10729-xxxx-000 A

NAMEIMPLIED WARR ANTIES INCLU DING, WITHO UT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C82

4.7UF

6.3V

10%

X5R

0603

C11-4757013-T04

C79

4.7UF

6.3V

20%

X5R

0603

<New PN>

PEX_VDD

GND

PEX_VDD

C78

10UF

6.3V

20%

X5R

0805

<New PN>

1

GND

PEX_VDD

C80

10UF

6.3V

20%

X5R

0805

C11-1067014-T04

GND

2

3

4

5

PAGEID

26-OCT-2007

DATE

HFDBA

www.vinafix.vn

A B C D E F G H

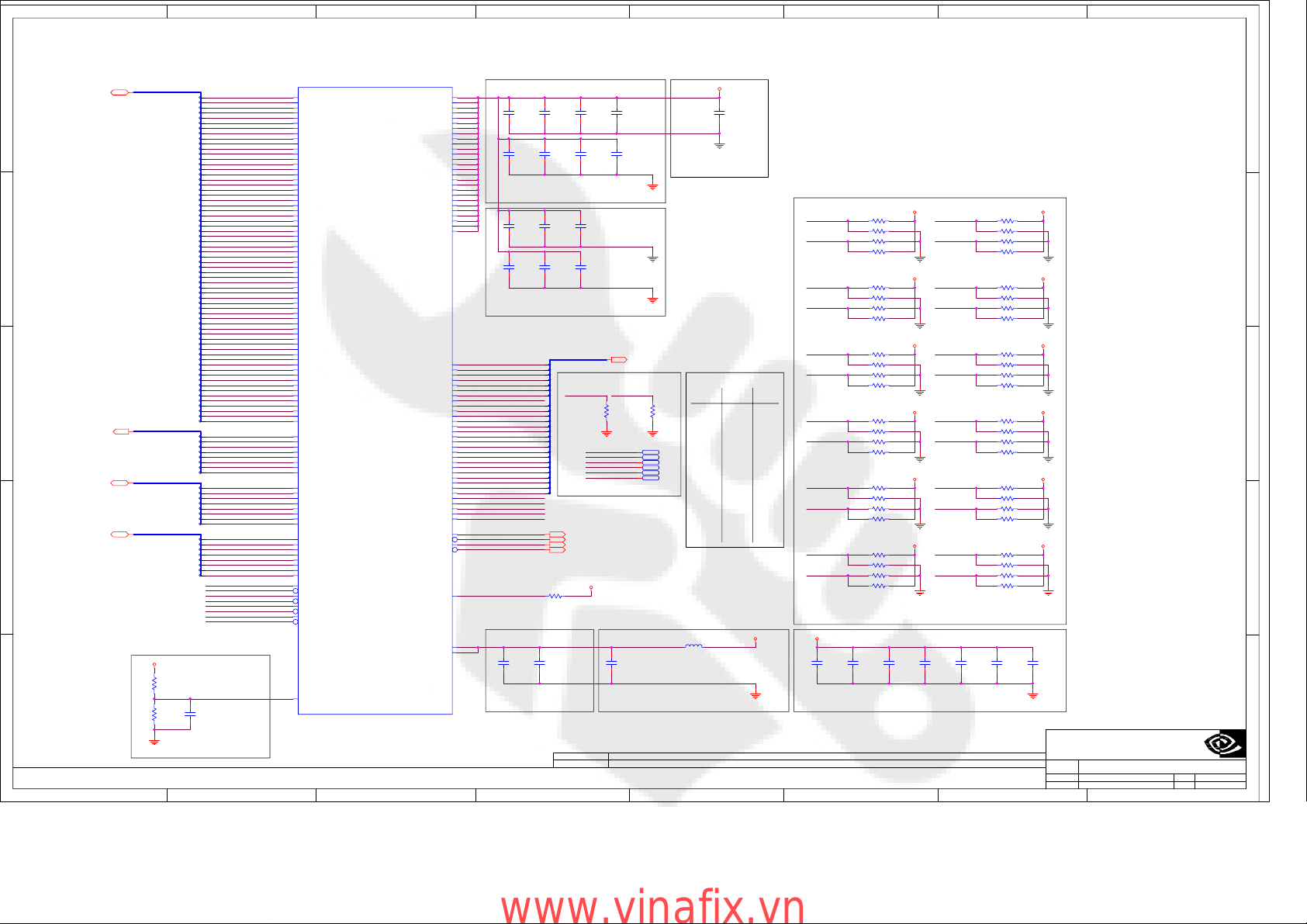

Partition A Frame Buffer Interface

G1B

AG30

AH31

AG32

AF31

AF30

AD30

AC32

AE30

AE32

AF33

AF34

AE35

AE33

AE34

AC35

AB32

AN33

AK32

AL33

AM33

AL31

AK30

AJ30

AH30

AM35

AH33

AH35

AH32

AH34

AM34

AL35

AJ33

AF32

AF35

AL32

AL34

AE31

AC33

AJ32

AJ34

AD32

AC34

AJ31

AJ35

AD29

AE29

AG29

AH29

R30

R32

P31

N30

L31

M32

M30

L30

P33

P34

N35

P35

N34

L33

L32

N33

K31

K30

G30

K32

G32

H30

F30

G31

H33

K35

K33

G34

K34

E33

E34

G33

P30

P32

J30

H34

N31

L34

J32

H35

N32

L35

H31

G35

P29

R29

L29

M29

J27

BGA_0969_P080_290X290

2/16 FBA

FBA_D0

FBA_D1

FBA_D2

FBA_D3

FBA_D4

FBA_D5

FBA_D6

FBA_D7

FBA_D8

FBA_D9

FBA_D10

FBA_D11

FBA_D12

FBA_D13

FBA_D14

FBA_D15

FBA_D16

FBA_D17

FBA_D18

FBA_D19

FBA_D20

FBA_D21

FBA_D22

FBA_D23

FBA_D24

FBA_D25

FBA_D26

FBA_D27

FBA_D28

FBA_D29

FBA_D30

FBA_D31

FBA_D32

FBA_D33

FBA_D34

FBA_D35

FBA_D36

FBA_D37

FBA_D38

FBA_D39

FBA_D40

FBA_D41

FBA_D42

FBA_D43

FBA_D44

FBA_D45

FBA_D46

FBA_D47

FBA_D48

FBA_D49

FBA_D50

FBA_D51

FBA_D52

FBA_D53

FBA_D54

FBA_D55

FBA_D56

FBA_D57

FBA_D58

FBA_D59

FBA_D60

FBA_D61

FBA_D62

FBA_D63

FBA_DQM0

FBA_DQM1

FBA_DQM2

FBA_DQM3

FBA_DQM4

FBA_DQM5

FBA_DQM6

FBA_DQM7

FBA_DQS_WP0

FBA_DQS_WP1

FBA_DQS_WP2

FBA_DQS_WP3

FBA_DQS_WP4

FBA_DQS_WP5

FBA_DQS_WP6

FBA_DQS_WP7

FBA_DQS_RN0

FBA_DQS_RN1

FBA_DQS_RN2

FBA_DQS_RN3

FBA_DQS_RN4

FBA_DQS_RN5

FBA_DQS_RN6

FBA_DQS_RN7

RFU

RFU

RFU

RFU

RFU

RFU

RFU

RFU

FB_VREF

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

J23

J24

J29

AA27

AA29

AA31

AB27

AB29

AC27

AD27

AE27

AJ28

B18

E21

G17

G18

G22

G8

G9

H29

J14

J15

J16

J17

J20

J21

J22

3.200 Amps

C653

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

C587

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

PLACE BELOW GPU

C509

4.7UF

6.3V

20%

X5R

0603

<New PN>

C558

4.7UF

6.3V

20%

X5R

0603

<New PN>

PLACE NEXT TO SUPPLY

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_DEBUG

FB_DLLAVDD

FB_PLLAVDD

FBA_CMD1

W31

FBA_CMD2

U31

FBA_CMD3

Y32

FBA_CMD4

AB35

FBA_CMD5

AB34

FBA_CMD6

W35

SNN_FBA_CMD7

W33

FBA_CMD8

W30

FBA_CMD9

T34

FBA_CMD10

T35

FBA_CMD11

AB31

FBA_CMD12

Y30

FBA_CMD13

Y34

FBA_CMD14

W32

FBA_CMD15

AA30

FBA_CMD16

AA32

FBA_CMD17

Y33

FBA_CMD18

U32

FBA_CMD19

Y31

FBA_CMD20

U34

FBA_CMD21

Y35

FBA_CMD22

W34

FBA_CMD23

V30

FBA_CMD24

U35

FBA_CMD25

U30

SNN_FBA_CMD26

U33

SNN_FBA_CMD27

AB30

SNN_FBA_CMD28

AB33

SNN_FBA_CMD29

T33

SNN_FBA_CMD30

W29

FBA_CLK0

T32

FBA_CLK0*

T31

FBA_CLK1

AC31

FBA_CLK1*

AC30

FBA_DEBUG

T30

AG27

AF27

FBA_PLLAVDD

0.038 Amps

C589

.1UF

16V

10%

X5R

0402

<New PN>

0

1

2

3

4

5

6

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

R534

0402

FBA_CMD0

V32

PLACE NEAR BALLS

C GE

FBA_D[63..0]

3,5

1

BI

2

3

FBA_DQM[7..0]

3,5

OUT

FBA_DQS_WP[7..0]

5

BI

FBA_DQS_RN[7..0]

5

BI

4

FBA_D0

0

FBA_D1

1

FBA_D2

2

FBA_D3

3

FBA_D4

4

FBA_D5

5

FBA_D6

6

FBA_D7

7

FBA_D8

8

FBA_D9

9

FBA_D10

10

FBA_D11

11

FBA_D12

12

FBA_D13

13

FBA_D14

14

FBA_D15

15

FBA_D16

16

FBA_D17

17

FBA_D18

18

FBA_D19

19

FBA_D20

20

FBA_D21

21

FBA_D22

22

FBA_D23

23

FBA_D24

24

FBA_D25

25

FBA_D26

26

FBA_D27

27

FBA_D28

28

FBA_D29

29

FBA_D30

30

FBA_D31

31

FBA_D32

32

FBA_D33

33

FBA_D34

34

FBA_D35

35

FBA_D36

36

FBA_D37

37

FBA_D38

38

FBA_D39

39

FBA_D40

40

FBA_D41

41

FBA_D42

42

FBA_D43

43

FBA_D44

44

FBA_D45

45

FBA_D46

46

FBA_D47

47

FBA_D48

48

FBA_D49

49

FBA_D50

50

FBA_D51

51

FBA_D52

52

FBA_D53

53

FBA_D54

54

FBA_D55

55

FBA_D56

56

FBA_D57

57

FBA_D58

58

FBA_D59

59

FBA_D60

60

FBA_D61

61

FBA_D62

62

FBA_D63

63

FBA_DQM0

0

FBA_DQM1

1

FBA_DQM2

2

FBA_DQM3

3

FBA_DQM4

4

FBA_DQM5

5

FBA_DQM6

6

FBA_DQM7

7

FBA_DQS_WP0

0

FBA_DQS_WP1

1

FBA_DQS_WP2

2

FBA_DQS_WP3

3

FBA_DQS_WP4

4

FBA_DQS_WP5

5

FBA_DQS_WP6

6

FBA_DQS_WP7

7

FBA_DQS_RN0

0

FBA_DQS_RN1

1

FBA_DQS_RN2

2

FBA_DQS_RN3

3

FBA_DQS_RN4

4

FBA_DQS_RN5

5

FBA_DQS_RN6

6

FBA_DQS_RN7

7

SNN_FBA_WDS0

SNN_FBA_WDS0*

SNN_FBA_WDS1

SNN_FBA_WDS1*

SNN_FBA_WDS2

SNN_FBA_WDS2*

SNN_FBA_WDS3

SNN_FBA_WDS3*

FBVDDQ

R535

1K

1%

Rt

0402

R11-0102T12-Y01

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR O THERWISE, AND EXPRESSLY DISCLAIMS ALL

Rb

GND

R537

1K

1%

0402

R11-0102T12-Y01

FBVREF = FBVDDQ * Rb/(Rt + Rb)

DDR2: 0.9V = 1.8V * 1K/(1K + 1 K)

C594

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

VREF = 0.5 * FBVDD Q

FB_VREF

C636

.47UF

6.3V

10%

X5R

0402

C11-4747312-T04

C582

.47UF

6.3V

10%

X5R

0402

C11-4747312-T04

C511

10UF

6.3V

20%

X5R

0805

<New PN>

C501

10UF

6.3V

20%

X5R

0805

<New PN>

FBA_CMD[25..0]

OUT

OUT

OUT

OUT

10K

5%

<New PN>

C583

.1UF

16V

10%

X5R

0402

<New PN>

ASSEMBLY

PAGE DETAIL

FBVDDQ

C632

C603

4.7UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0603

C11-4747312-T04

C11-4757013-T04

C586

C588

4.7UF

1UF

6.3V

10%

X5R

0402

C11-1057322-T04

6.3V

10%

X5R

0603

C11-4757013-T04

GND

PLACE NEAR GPU

GND

C556

47UF

6.3V

20%

X5R

1206

<New PN>

C93

100UF

6.3V

20%

X5R

1210

<New PN>

GND

GND

3,5

OUT

R514

10K

5%

0402

R11-0103012-Y01

<New PN>

<New PN>

<New PN>

<New PN>

<New PN>

<New PN>

CMD-Addr Map

BGA84

<31..0>

CMD1

CMD3

CMD2

CMD0

CMD24

CMD22

CMD21

CMD23

CMD19

CMD20

CMD17

CMD16

CMD14

CMD10

CMD18

CMD27

CMD15

CMD25

CMD9

CMD8

CMD7

CMD11

CMD12

CMD26

CMD28

CMD29

CMD30

PD REQUIRED FOR INITIALIZATION

CKE

FBA_CMD11

GND GND

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FBA_DQS_WP0

FBA_DQS_RN0

LAB TESTPOINTS

3,5

3,5

3,5

3,5

RSET/ODT

FBA_CMD12

R504

10K

5%

0402

R11-0103012-Y01

TP504

TP502

TP503

TP501

TP506

TP505

FBVDDQ

LB501

240R@100MHz

IND_SMD_0402

C584

1UF

6.3V

10%

X5R

0402

<New PN>

<New PN>

PLACE NEAR GPU

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

Partition A Frame Buffer Interface

C557

47UF

6.3V

20%

X5R

1206

<New PN>

BGA84

<63..32>

ADDR

CMD1

A<0>

A<1>

CMD3

CMD13

A<2>

CMD4 A<3>

CMD5 A<4>

CMD6

A<5>

CMD21

A<6>

CMD23

A<7>

CMD19

A<8>

CMD20

A<9>

CMD17

A<10>

CMD16

A<11>

CMD14

A<12>

BA0CMD10

BA1

CMD18

BA2

CMD27

RAS*

CMD15

CAS*

CMD25

WE*

CMD9

CS0*

CMD8

CMD7

CS1*

CKE

CMD11

RST/ODT

CMD12

A<13>

CMD26

RFU0CMD28

CMD29

RFU1

CMD30

RFU2

PEX_VDD FBVDDQ

GND

FBVDDQ

RP13D

FBA_CMD0

FBA_CMD1

FBA_CMD4

FBA_CMD5

FBA_CMD9

FBA_CMD10

FBA_CMD15

FBA_CMD16

FBA_CMD19

FBA_CMD20

FBA_CMD23

FBA_CMD24

4 5

RPAK_PAR_4_2010

+/-5%

RP13C

3 6

RPAK_PAR_4_2010

+/-5%

RP15C

3 6

RPAK_PAR_4_2010

+/-5%

RP15D

4 5

RPAK_PAR_4_2010

+/-5%

RP18C

3 6

RPAK_PAR_4_2010

+/-5%

RP18D

4 5

RPAK_PAR_4_2010

+/-5%

RP19B

2 7

RPAK_PAR_4_2010

+/-5%

RP19A

1 8

RPAK_PAR_4_2010

+/-5%

RP21A

1 8

RPAK_PAR_4_2010

+/-5%

RP21B

2 7

RPAK_PAR_4_2010

+/-5%

RP21C

3 6

RPAK_PAR_4_2010

+/-5%

RP21D

4 5

RPAK_PAR_4_2010

+/-5%

RP17A

1 8

RPAK_PAR_4_2010

+/-5%

RP17B

2 7

RPAK_PAR_4_2010

+/-5%

RP17C

3 6

RPAK_PAR_4_2010

+/-5%

RP17D

4 5

RPAK_PAR_4_2010

+/-5%

RP16D

4 5

RPAK_PAR_4_2010

+/-5%

RP16C

3 6

RPAK_PAR_4_2010

+/-5%

RP22B

2 7

RPAK_PAR_4_2010

+/-5%

RP22A

1 8

RPAK_PAR_4_2010

+/-5%

RP15A

1 8

RPAK_PAR_4_2010

+/-5%

RP15B

2 7

RPAK_PAR_4_2010

+/-5%

RP20B

2 7

RPAK_PAR_4_2010

+/-5%

RP20A 150

1 8

RPAK_PAR_4_2010

+/-5%

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

R31-0151012-Y01

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

GND

GND

GND

GND

GND

GND

FBA CMD/Addr Terminations

C504

.01UF

16V

10%

X7R

0402

C11-1032012-W08

C506

.01UF

16V

10%

X7R

0402

C11-1032012-W08

C503

.01UF

16V

10%

X7R

0402

C11-1032012-W08

PLACE NEXT TO TERMINATION RESISTORS

FBA_CMD2

FBA_CMD3

FBA_CMD6

FBA_CMD8

FBA_CMD13

FBA_CMD14

FBA_CMD17

FBA_CMD18

FBA_CMD21

FBA_CMD22

FBA_CMD25

FBA_CMD_NC

C92

.01UF

16V

10%

X7R

0402

C11-1032012-W08

4 5

3 6

2 7

1 8

2 7

1 8

3 6

4 5

4 5

3 6

2 7

1 8

4 5

3 6

2 7

1 8

1 8

2 7

2 7

1 8

4 5

3 6

3 6

4 5

C91

.01UF

16V

10%

X7R

0402

C11-1032012-W08

RP20D

RPAK_PAR_4_2010

+/-5%

RP20C

RPAK_PAR_4_2010

+/-5%

RP16B

RPAK_PAR_4_2010

+/-5%

RP16A

RPAK_PAR_4_2010

+/-5%

RP18B

RPAK_PAR_4_2010

+/-5%

RP18A

RPAK_PAR_4_2010

+/-5%

RP23C

RPAK_PAR_4_2010

+/-5%

RP23D

RPAK_PAR_4_2010

+/-5%

RP19D

RPAK_PAR_4_2010

+/-5%

RP19C

RPAK_PAR_4_2010

+/-5%

RP23B

RPAK_PAR_4_2010

+/-5%

RP23A

RPAK_PAR_4_2010

+/-5%

RP24D

RPAK_PAR_4_2010

+/-5%

RP24C

RPAK_PAR_4_2010

+/-5%

RP14B

RPAK_PAR_4_2010

+/-5%

RP14A

RPAK_PAR_4_2010

+/-5%

RP24A

RPAK_PAR_4_2010

+/-5%

RP24B

RPAK_PAR_4_2010

+/-5%

RP13B

RPAK_PAR_4_2010

+/-5%

RP13A

RPAK_PAR_4_2010

+/-5%

RP14D

RPAK_PAR_4_2010

+/-5%

RP14C

RPAK_PAR_4_2010

+/-5%

RP22C

RPAK_PAR_4_2010

+/-5%

RP22D

RPAK_PAR_4_2010

+/-5%

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

C507

.01UF

16V

10%

X7R

0402

C11-1032012-W08

GND

FBVDDQ

GND

FBVDDQ

GND

FBVDDQ

GND

FBVDDQ

GND

FBVDDQ

GND

FBVDDQ

GND

C505

1UF

6.3V

10%

X5R

0402

C11-1057322-T04

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10729-xxxx-000 A

NAMEIMPLIED WARR ANTIES INCLU DING, WITHO UT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

1

2

3

4

5

PAGEID

26-OCT-2007

DATE

HFDBA

www.vinafix.vn

A B C D E F G H

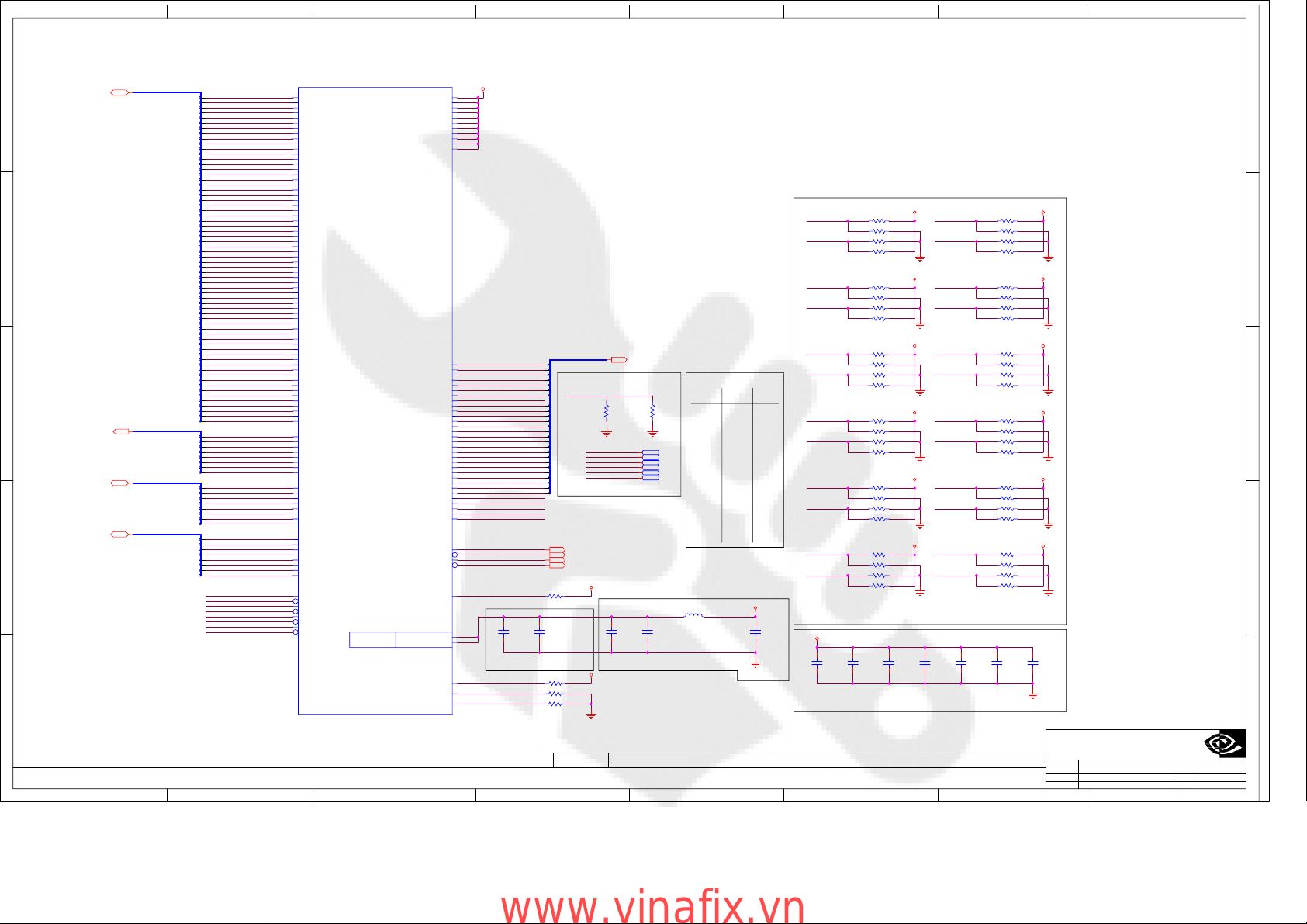

Partition C Frame Buffer Interface

G1C

FBC_D[63..0]

4,6

1

BI

2

3

FBC_DQM[7..0]

4,6

OUT

FBC_DQS_WP[7..0]

6

BI

FBC_DQS_RN[7..0]

6

BI

4

FBC_D0

0

FBC_D1

1

FBC_D2

2

FBC_D3

3

FBC_D4

4

FBC_D5

5

FBC_D6

6

FBC_D7

7

FBC_D8

8

FBC_D9

9

FBC_D10

10

FBC_D11

11

FBC_D12

12

FBC_D13

13

FBC_D14

14

FBC_D15

15

FBC_D16

16

FBC_D17

17

FBC_D18

18

FBC_D19

19

FBC_D20

20

FBC_D21

21

FBC_D22

22

FBC_D23

23

FBC_D24

24

FBC_D25

25

FBC_D26

26

FBC_D27

27

FBC_D28

28

FBC_D29

29

FBC_D30

30

FBC_D31

31

FBC_D32

32

FBC_D33

33

FBC_D34

34

FBC_D35

35

FBC_D36

36

FBC_D37

37

FBC_D38

38

FBC_D39

39

FBC_D40

40

FBC_D41

41

FBC_D42

42

FBC_D43

43

FBC_D44

44

FBC_D45

45

FBC_D46

46

FBC_D47

47

FBC_D48

48

FBC_D49

49

FBC_D50

50

FBC_D51

51

FBC_D52

52

FBC_D53

53

FBC_D54

54

FBC_D55

55

FBC_D56

56

FBC_D57

57

FBC_D58

58

FBC_D59

59

FBC_D60

60

FBC_D61

61

FBC_D62

62

FBC_D63

63

FBC_DQM0

0

FBC_DQM1

1

FBC_DQM2

2

FBC_DQM3

3

FBC_DQM4

4

FBC_DQM5

5

FBC_DQM6

6

FBC_DQM7

7

FBC_DQS_WP0

0

FBC_DQS_WP1

1

FBC_DQS_WP2

2

FBC_DQS_WP3

3

FBC_DQS_WP4

4

FBC_DQS_WP5

5

FBC_DQS_WP6

6

FBC_DQS_WP7

7

FBC_DQS_RN0

0

FBC_DQS_RN1

1

FBC_DQS_RN2

2

FBC_DQS_RN3

3

FBC_DQS_RN4

4

FBC_DQS_RN5

5

FBC_DQS_RN6

6

FBC_DQS_RN7

7

SNN_FBC_WDS0

SNN_FBC_WDS0*

SNN_FBC_WDS1

SNN_FBC_WDS1*

SNN_FBC_WDS2

SNN_FBC_WDS2*

SNN_FBC_WDS3

SNN_FBC_WDS3*

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR O THERWISE, AND EXPRESSLY DISCLAIMS ALL

D11

E11

F10

D8

F8

F9

E8

F12

B11

C13

A11

B8

A8

C8

C11

C10

D12

E13

F17

F15

F16

E16

F14

F13

D13

A13

B13

A14

C16

A17

B16

D16

D24

D26

E25

F25

F27

E28

F28

D29

A25

B25

D25

C26

C28

B28

A28

A29

E29

F29

D30

E31

C33

D33

F32

E32

B29

C29

B31

C31

B32

C32

B34

B35

F11

D10

D15

A16

D27

D28

D34

A34

E10

A10

D14

C14

E26

B26

D32

A32

D9

B10

E14

B14

F26

A26

D31

A31

G11

G12

G14

G15

G24

G25

G27

G28

BGA_0969_P080_290X290

3/16 FBC

FBC_D0

FBC_D1

FBC_D2

FBC_D3

FBC_D4

FBC_D5

FBC_D6

FBC_D7

FBC_D8

FBC_D9

FBC_D10

FBC_D11

FBC_D12

FBC_D13

FBC_D14

FBC_D15

FBC_D16

FBC_D17

FBC_D18

FBC_D19

FBC_D20

FBC_D21

FBC_D22

FBC_D23

FBC_D24

FBC_D25

FBC_D26

FBC_D27

FBC_D28

FBC_D29

FBC_D30

FBC_D31

FBC_D32

FBC_D33

FBC_D34

FBC_D35

FBC_D36

FBC_D37

FBC_D38

FBC_D39

FBC_D40

FBC_D41

FBC_D42

FBC_D43

FBC_D44

FBC_D45

FBC_D46

FBC_D47

FBC_D48

FBC_D49

FBC_D50

FBC_D51

FBC_D52

FBC_D53

FBC_D54

FBC_D55

FBC_D56

FBC_D57

FBC_D58

FBC_D59

FBC_D60

FBC_D61

FBC_D62

FBC_D63

FBC_DQM0

FBC_DQM1

FBC_DQM2

FBC_DQM3

FBC_DQM4

FBC_DQM5

FBC_DQM6

FBC_DQM7

FBC_DQS_WP0

FBC_DQS_WP1

FBC_DQS_WP2

FBC_DQS_WP3

FBC_DQS_WP4

FBC_DQS_WP5

FBC_DQS_WP6

FBC_DQS_WP7

FBC_DQS_RN0

FBC_DQS_RN1

FBC_DQS_RN2

FBC_DQS_RN3

FBC_DQS_RN4

FBC_DQS_RN5

FBC_DQS_RN6

FBC_DQS_RN7

RFU

RFU

RFU

RFU

RFU

RFU

RFU

RFU

G96 only

FBC_CMD0

FBC_CMD1

FBC_CMD2

FBC_CMD3

FBC_CMD4

FBC_CMD5

FBC_CMD6

FBC_CMD7

FBC_CMD8

FBC_CMD9

FBC_CMD10

FBC_CMD11

FBC_CMD12

FBC_CMD13

FBC_CMD14

FBC_CMD15

FBC_CMD16

FBC_CMD17

FBC_CMD18

FBC_CMD19

FBC_CMD20

FBC_CMD21

FBC_CMD22

FBC_CMD23

FBC_CMD24

FBC_CMD25

FBC_CMD26

FBC_CMD27

FBC_CMD28

FBC_CMD29

FBC_CMD30

FBC_CLK0

FBC_CLK0

FBC_CLK1

FBC_CLK1

FBC_DEBUG

FBAC_DLLAVDD

FBAC_PLLAVDD

FBCAL_PD_VDDQ

FBCAL_PU_GND

FBCAL_TERM_GND

C GE

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

N27

P27

R27

T27

U27

U29

V27

V29

V34

W27

Y27

C17

B19

D18

F21

A23

D21

B23

E20

G21

F20

F19

F23

A22

C22

B17

F24

C25

E22

C20

B22

A19

D22

D20

E19

D19

F18

C19

F22

C23

B20

A20

E17

D17

D23

E23

G19

J19

J18

K27

L27

M27

FBC_CMD0

FBC_CMD1

FBC_CMD2

FBC_CMD3

FBC_CMD4

FBC_CMD5

FBC_CMD6

SNN_FBC_CMD7

FBC_CMD8

FBC_CMD9

FBC_CMD10

FBC_CMD11

FBC_CMD12

FBC_CMD13

FBC_CMD14

FBC_CMD15

FBC_CMD16

FBC_CMD17

FBC_CMD18

FBC_CMD19

FBC_CMD20

FBC_CMD21

FBC_CMD22

FBC_CMD23

FBC_CMD24

FBC_CMD25

SNN_FBC_CMD26

SNN_FBC_CMD27

SNN_FBC_CMD28

SNN_FBC_CMD29

SNN_FBC_CMD30

FBC_CLK0

FBC_CLK0*

FBC_CLK1

FBC_CLK1*

FBC_DEBUG

0.038 Amps

FBC_PLLAVDD

C624

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

PLACE NEAR BALLS

FB_CAL_PD_VDDQ

FB_CAL_PU_GND

FB_CAL_TERM_GND

0

1

2

3

4

5

6

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

R541 10K

0402

R536 30.1

0402

R538 24.3

0402

R539 40.2

0402

FBC_CMD[25..0]

PD REQUIRED FOR INITIALIZATION

4,6

OUT

4,6

OUT

4,6

OUT

4,6

OUT

5%

<New PN>

C615

.1UF

16V

10%

X5R

0402

C11-1047522-Y01

1%

R11-301AT12-Y01

1%

R11-243AT12-Y01

1%

R11-402AT12-Y01

ASSEMBLY

PAGE DETAIL

4,6

OUT

FBC_CMD11

RSET/ODTCKE

FBC_CMD12

R542

10K

5%

0402

R11-0103012-Y01

GND GND

FBC_CLK0

FBC_CLK0*

FBC_CLK1

FBC_CLK1*

FBC_DQS_WP0

FBC_DQS_RN0

TP510

TP509

TP508

TP507

TP511

TP512

R543

10K

5%

0402

R11-0103012-Y01

<New PN>

<New PN>

<New PN>

<New PN>

<New PN>

<New PN>

CMD-Addr Map

BGA84

<31..0>

CMD1

CMD3

CMD2

CMD0

CMD24

CMD22

CMD21

CMD23

CMD19

CMD20

CMD17

CMD16

CMD10

CMD18

CMD27

CMD15LAB TESTPOINTS

CMD25

CMD9

CMD8

CMD7

CMD11

CMD12

CMD26

CMD28

CMD29

CMD30

FBVDDQ

LB502

240R@100MHz

IND_SMD_0402

L02-2418032-T34

PLACE NEAR GPU

FBVDDQ

C616

1UF

6.3V

10%

X5R

0402

C11-1057322-T04

C620

1UF

6.3V

10%

X5R

0402

C11-1057322-T04

GND

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

Partition C Frame Buffer Interface

1

FBVDDQ

RP3A

FBC_CMD0

FBC_CMD1

FBC_CMD4

FBC_CMD5

FBC_CMD9

FBC_CMD10

BGA84

<63..32>

ADDR

CMD1

A<0>

CMD3

A<1>

A<2>

CMD13

CMD4

A<3>

CMD5

A<4>

A<5>

CMD6

CMD21

A<6>

A<7>

CMD23

CMD19

A<8>

CMD20

A<9>

CMD17

A<10>

CMD16

A<11>

A<12>

CMD14CMD14

CMD10

BA0

BA1

CMD18

BA2

CMD27

RAS*

CMD15

CAS*

CMD25

WE*

CMD9

CS0*

CMD8

CS1*

CMD7

CKE

CMD11

CMD12

RST/ODT

CMD26

A<13>

RFU0

CMD28

RFU1

CMD29

RFU2

CMD30

FBC_CMD15

FBC_CMD16

FBC_CMD19

FBC_CMD20

FBC_CMD23

FBC_CMD24

PEX_VDD

FBC CMD/Addr Terminations

C625

4.7UF

6.3V

FBVDDQ

20%

X5R

0603

<New PN>

GND

C81

.01UF

16V

10%

X7R

0402

C11-1032012-W08

1 8

RPAK_PAR_4_2010

+/-5%

RP3B

2 7

RPAK_PAR_4_2010

+/-5%

RP11B 150

2 7

RPAK_PAR_4_2010

+/-5%

RP11A

1 8

RPAK_PAR_4_2010

+/-5%

RP10A

1 8

RPAK_PAR_4_2010

+/-5%

RP10B 150

2 7

RPAK_PAR_4_2010

+/-5%

RP11C

3 6

RPAK_PAR_4_2010

+/-5%

RP11D

4 5

RPAK_PAR_4_2010

+/-5%

RP6A

1 8

RPAK_PAR_4_2010

+/-5%

RP6B

2 7

RPAK_PAR_4_2010

+/-5%

RP5C

3 6

RPAK_PAR_4_2010

+/-5%

RP5D

4 5

RPAK_PAR_4_2010

+/-5%

RP9D

4 5

RPAK_PAR_4_2010

+/-5%

RP9C

3 6

RPAK_PAR_4_2010

+/-5%

RP10C

3 6

RPAK_PAR_4_2010

+/-5%

RP10D

4 5

RPAK_PAR_4_2010

+/-5%

RP7A

1 8

RPAK_PAR_4_2010

+/-5%

RP7B

2 7

RPAK_PAR_4_2010

+/-5%

RP4B

2 7

RPAK_PAR_4_2010

+/-5%

RP4A

1 8

RPAK_PAR_4_2010

+/-5%

RP4D

4 5

RPAK_PAR_4_2010

+/-5%

RP4C

3 6

RPAK_PAR_4_2010

+/-5%

RP1B 150

2 7

RPAK_PAR_4_2010

+/-5%

RP1A

1 8

RPAK_PAR_4_2010

+/-5%

C675

.01UF

16V

10%

X7R

0402

C11-1032012-W08

150

150

R31-0151012-Y01

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

150

150

R31-0151012-Y01

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

C655

.01UF

16V

10%

X7R

0402

C11-1032012-W08

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

GND

GND

GND

GND

GND

GND

FBC_CMD2

FBC_CMD3

FBC_CMD6

FBC_CMD8

FBC_CMD13

FBC_CMD14

FBC_CMD17

FBC_CMD18

FBC_CMD21

FBC_CMD22

FBC_CMD25

FBC_CMD_NC

C637

.01UF

16V

10%

X7R

0402

C11-1032012-W08

C619

.01UF

16V

10%

X7R

0402

C11-1032012-W08

PLACE NEXT TO TERMINATION RESISTORS

RP1D

4 5

RPAK_PAR_4_2010

+/-5%

RP1C

3 6

RPAK_PAR_4_2010

+/-5%

RP8B

2 7

RPAK_PAR_4_2010

+/-5%

RP8A

1 8

RPAK_PAR_4_2010

+/-5%

RP12D

4 5

RPAK_PAR_4_2010

+/-5%

RP12C

3 6

RPAK_PAR_4_2010

+/-5%

RP7C

3 6

RPAK_PAR_4_2010

+/-5%

RP7D

4 5

RPAK_PAR_4_2010

+/-5%

RP12A 150

1 8

RPAK_PAR_4_2010

+/-5%

RP12B

2 7

RPAK_PAR_4_2010

+/-5%

RP2C

3 6

RPAK_PAR_4_2010

+/-5%

RP2D

4 5

RPAK_PAR_4_2010

+/-5%

RP9A

1 8

RPAK_PAR_4_2010

+/-5%

RP9B

2 7

RPAK_PAR_4_2010

+/-5%

RP5B

2 7

RPAK_PAR_4_2010

+/-5%

RP5A

1 8

RPAK_PAR_4_2010

+/-5%

RP8D

4 5

RPAK_PAR_4_2010

+/-5%

RP8C

3 6

RPAK_PAR_4_2010

+/-5%

RP2B

2 7

RPAK_PAR_4_2010

+/-5%

RP2A

1 8

RPAK_PAR_4_2010

+/-5%

RP3D

4 5

RPAK_PAR_4_2010

+/-5%

RP3C

3 6

RPAK_PAR_4_2010

+/-5%

RP6C

3 6

RPAK_PAR_4_2010

+/-5%

RP6D

4 5

RPAK_PAR_4_2010

+/-5%

C600

.01UF

16V

10%

X7R

0402

C11-1032012-W08

FBVDDQ

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

GND

FBVDDQ

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

GND

FBVDDQ

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

GND

FBVDDQ

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

GND

FBVDDQ

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

GND

FBVDDQ

150

150

R31-0151012-Y01

150

R31-0151012-Y01

150

R31-0151012-Y01

R31-0151012-Y01

GND

C83

1UF

6.3V

10%

X5R

0402

C11-1057322-T04

GND

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

NAMEIMPLIED WARR ANTIES INCLU DING, WITHO UT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

600-10729-xxxx-000 A

2

3

4

5

PAGEID

26-OCT-2007

DATE

HFDBA

www.vinafix.vn

A B C D E F G H

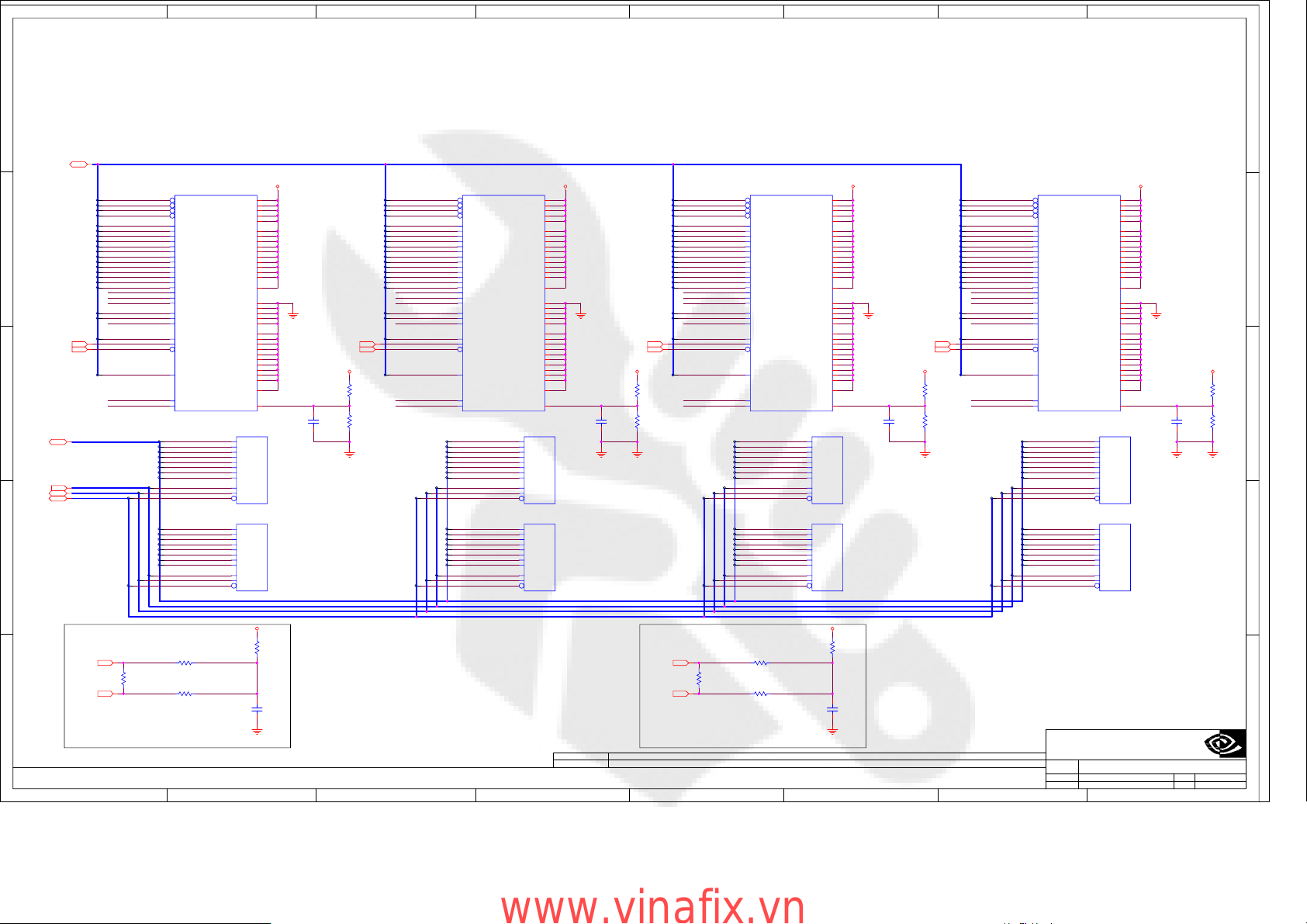

Partition A Memories

1

FBA_CMD[25..0]

3,3

BI

FBA_CMD15 FBA_CMD15 FBA_CMD15 FBA_CMD15

15

FBA_CMD25 FBA_CMD25 FBA_CMD25 FBA_CMD25

25

FBA_CMD9 FBA_CMD9 FBA_CMD9 FBA_CMD9

9

FBA_CMD8 FBA_CMD8 FBA_CMD8 FBA_CMD8

8

FBA_CMD1 FBA_CMD1 FBA_CMD1 FBA_CMD1

1

FBA_CMD3 FBA_CMD3 FBA_CMD3 FBA_CMD3

3

FBA_CMD2 FBA_CMD2

2

FBA_CMD0 FBA_CMD0

0

2

3,5

3,5

3

3

BI

3

IN

3,5

BI

3,5

BI

FBA_CMD24 FBA_CMD24

24

FBA_CMD22 FBA_CMD22

22

FBA_CMD21 FBA_CMD21 FBA_CMD21 FBA_CMD21

21

FBA_CMD23 FBA_CMD23 FBA_CMD23 FBA_CMD23

23

FBA_CMD19 FBA_CMD19 FBA_CMD19 FBA_CMD19

19

FBA_CMD20 FBA_CMD20 FBA_CMD20 FBA_CMD20

20

FBA_CMD17 FBA_CMD17 FBA_CMD17 FBA_CMD17

17

FBA_CMD16 FBA_CMD16 FBA_CMD16 FBA_CMD16

16

FBA_CMD14 FBA_CMD14 FBA_CMD14 FBA_CMD14

14

SNN_FBA1_NC_R8

SNN_FBA1_NC_R3

SNN_FBA1_NC_R7

FBA_CMD10 FBA_CMD10 FBA_CMD10 FBA_CMD10

10

FBA_CMD18 FBA_CMD18 FBA_CMD18 FBA_CMD18

18

SNN_FBA1_NC_L1

FBA_CMD11 FBA_CMD11 FBA_CMD11 FBA_CMD11

11

FBA_CLK0

IN

FBA_CLK0*

IN

FBA_CMD12 FBA_CMD12 FBA_CMD12 FBA_CMD12

12

SNN_FBA1_NC_A2

SNN_FBA1_NC_E2

FBA_D[63..0]

FBA_DQM[7..0]

FBA_DQS_WP[7..0]

FBA_DQS_RN[7..0]

4

M6C

BGA_0084_P080_140X120

1/2

K7

RAS

L7

CAS

K3

WE

L8

CS

M8

A<0>

M3

A<1>

M7

A<2>

N2

A<3>

N8

A<4>

N3

A<5>

N7

A<6>

P2

A<7>

P8

A<8>

P3

A<9>

M2

A<10>

P7

A<11>

R2

A<12>

R8

NC/A<13>

R3

NC/A<14>

R7

NC/A<15>

L2

BA<0>

L3

BA<1>

L1

NC/BA<2>

K2

CKE

J8

CLK

K8

CLK

K9

ODT

A2

NC

E2

NC

FBA_D0

0

FBA_D1

1

FBA_D2

2

FBA_D3

3

FBA_D4

4

FBA_D5

5

FBA_D6

6

FBA_D7

7

FBA_DQM0

0

FBA_DQS_WP0

0

FBA_DQS_RN0

0

FBA_D8

8

FBA_D9

9

FBA_D10

10

FBA_D11

11

FBA_D12

12

FBA_D13

13

FBA_D14

14

FBA_D15

15

FBA_DQM1 FBA_DQM 3

1

FBA_DQS_WP1

1

FBA_DQS_RN1

1

D1

C2

B1

D3

D7

C8

B9

D9

B3

B7

A8

H1

F1

H3

G2

H7

F9

H9

G8

F3

F7

E8

FBVDDQ

A1

VDD

E1

VDD

J9

VDD

M9

VDD

R1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E9

VDDQ

G1

VDDQ

G3

VDDQ

G7

VDDQ

G9

VDDQ

J1

VDDL

A3

VSS

E3

VSS

J3

VSS

N1

VSS

GND

P9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

VSSQ

F2

VSSQ

F8

VSSQ

H2

VSSQ

H8

VSSQ

J7

VSSL

FB_VREF_A FB_VREF_B FB_VREF_C FB_VREF_D

J2

Vref

M6B

BGA_0084_P080_140X120

2/2

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQM

DQS

DQS

M6A

BGA_0084_P080_140X120

2/2

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

M12-5PS12B5-H23

DQM

DQS

DQS

FBVDDQ

C522

.047UF

16V

10%

X7R

0402

C11-4732012-T04

3,5

3,5

R508

1K

5%

0402

R11-0102032-Y01

R512

1K

5%

0402

R11-0102032-Y01

GND

IN

IN

15

25

9

8

1

3

2

0

24

22

21

23

19

20

17

16

14

10

18

11

12

SNN_FBA2_NC_R8

SNN_FBA2_NC_R3

SNN_FBA2_NC_R7

SNN_FBA2_NC_L1

FBA_CLK0

FBA_CLK0*

SNN_FBA2_NC_A2

SNN_FBA2_NC_E2

M5C

BGA_0084_P080_140X120

1/2

K7

RAS

L7

CAS

K3

WE

L8

CS

M8

A<0>

M3

A<1>

M7

A<2>

N2

A<3>

N8

A<4>

N3

A<5>

N7

A<6>

P2

A<7>

P8

A<8>

P3

A<9>

M2

A<10>

P7

A<11>

R2

A<12>

R8

NC/A<13>

R3

NC/A<14>

R7

NC/A<15>

L2

BA<0>

L3

BA<1>

L1

NC/BA<2>

K2

CKE

J8

CLK

K8

CLK

K9

ODT

A2

NC

E2

NC

FBA_D16

16

FBA_D17

17

FBA_D18

18

FBA_D19

19

FBA_D20

20

FBA_D21

21

FBA_D22

22

FBA_D23

23

FBA_DQS2

FBA_DQM2

2

FBA_DQS_WP2

2

FBA_DQS_RN2

2

FBA_D24

24

FBA_D25

25

FBA_D26

26

FBA_D27

27

FBA_D28

28

FBA_D29

29

FBA_D30

30

FBA_D31

31

3

FBA_DQS_WP3

3

FBA_DQS_RN3

3

C2

D1

B9

B1

C8

D3

D9

D7

B3

B7

A8

H3

H1

F1

H7

G2

G8

H9

F9

F3

F7

E8

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSL

Vref

M5B

BGA_0084_P080_140X120

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQM

DQS

DQS

M5A

BGA_0084_P080_140X120

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQM

DQS

DQS

FBVDDQ

A1

E1

J9

M9

R1

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

J1

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

J2

2/2

2/2

M12-5PS12B5-H23

GND

C524

.047UF

16V

10%

X7R

0402

C11-4732012-T04

GND GND

FBVDDQ

3,5

IN

3,5

IN

R513

1K

5%

0402

R11-0102032-Y01

R519

1K

5%

0402

R11-0102032-Y01

15

25

9

8

1

3

FBA_CMD13 FBA_CMD13

13

FBA_CMD4 FBA_CMD4

4

FBA_CMD5 FBA_CMD5

5

FBA_CMD6 FBA_CMD6

6

21

23

19

20

17

16

14

SNN_FBA3_NC_R8

SNN_FBA3_NC_R3

SNN_FBA3_NC_R7

10

18

SNN_FBA3_NC_L1

11

FBA_CLK1

FBA_CLK1*

12

SNN_FBA3_NC_A2

SNN_FBA3_NC_E2

M8C

BGA_0084_P080_140X120

1/2

K7

RAS

L7

CAS

K3

WE

L8

CS

M8

A<0>

M3

A<1>

M7

A<2>

N2

A<3>

N8

A<4>

N3

A<5>

N7

A<6>

P2

A<7>

P8

A<8>

P3

A<9>

M2

A<10>

P7

A<11>

R2

A<12>

R8

NC/A<13>

R3

NC/A<14>

R7

NC/A<15>

L2

BA<0>

L3

BA<1>

L1

NC/BA<2>

K2

CKE

J8

CLK

K8

CLK

K9

ODT

A2

NC

E2

NC

FBA_D32

32

FBA_D33

33

FBA_D34

34

FBA_D35

35

FBA_D36

36

FBA_D37

37

FBA_D38

38

FBA_D39

39

FBA_DQM4

4

FBA_DQS_WP4

4

FBA_DQS_RN4

4

FBA_D40

40

FBA_D41

41

FBA_D42

42

FBA_D43

43

FBA_D44

44

FBA_D45

45

FBA_D46

46

FBA_D47

47

FBA_DQM5 FBA_DQM 7

5

FBA_DQS_WP5

5

FBA_DQS_RN5

5

B1

D1

C2

D3

D7

B9

D9

C8

B3

B7

A8

G2

H1

F1

H3

G8

H7

F9

H9

F3

F7

E8

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSL

Vref

M7A

BGA_0084_P080_140X120

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQM

DQS

DQS

M7C

BGA_0084_P080_140X120

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQM

DQS

DQS

FBVDDQ

A1

E1

J9

M9

R1

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

J1

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

J2

2/2

2/2

M12-5PS12B5-H23

GND

3,5

IN

3,5

IN

FBVDDQ

R521

1K

5%

0402

R11-0102032-Y01

R511

C521

1K

.047UF

5%

16V

0402

10%

X7R

R11-0102032-Y01

0402

C11-4732012-T04

GND

15

25

9

8

1

3

13

4

5

6

21

23

19

20

17

16

14

10

18

11

12

SNN_FBA4_NC_R8

SNN_FBA4_NC_R3

SNN_FBA4_NC_R7

SNN_FBA4_NC_L1

FBA_CLK1

FBA_CLK1*

SNN_FBA4_NC_A2

SNN_FBA4_NC_E2

M7B

BGA_0084_P080_140X120

1/2

K7

RAS

L7

CAS

K3

WE

L8

CS

M8

A<0>

M3

A<1>

M7

A<2>

N2

A<3>

N8

A<4>

N3

A<5>

N7

A<6>

P2

A<7>

P8

A<8>

P3

A<9>

M2

A<10>

P7

A<11>

R2

A<12>

R8

NC/A<13>

R3

NC/A<14>

R7

NC/A<15>

L2

BA<0>

L3

BA<1>

L1

NC/BA<2>

K2

CKE

J8

CLK

K8

CLK

K9

ODT

A2

NC

E2

NC

FBA_D48

48

FBA_D49

49

FBA_D50

50

FBA_D51

51

FBA_D52

52

FBA_D53

53

FBA_D54

54

FBA_D55

55

FBA_DQS6

FBA_DQM6

6

FBA_DQS_WP6

6

FBA_DQS_RN6

6

FBA_D56

56

FBA_D57

57

FBA_D58

58

FBA_D59

59

FBA_D60

60

FBA_D61

61

FBA_D62

62

FBA_D63

63

7

FBA_DQS_WP7

7

FBA_DQS_RN7

7

D1

D7

C2

B1

D3

C8

B9

D9

B3

B7

A8

F1

H9

F9

H7

G8

H1

G2

H3

F3

F7

E8

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSL

Vref

M8B

BGA_0084_P080_140X120

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQM

DQS

DQS

M8A

BGA_0084_P080_140X120

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQM

DQS

DQS

FBVDDQ

A1

E1

J9

M9

R1

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

J1

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

J2

2/2

2/2

M12-5PS12B5-H23

GND

C519

.047UF

16V

10%

X7R

0402

C11-4732012-T04

GND GND

FBVDDQ

R507

1K

5%

0402

R11-0102032-Y01

R510

1K

5%

0402

R11-0102032-Y01

1

2

3

4

FBVDDQ

C528

0

5%

0402

M12-5PS12B5-H23

R520

FBA_CLK0

3,5

IN

R515

475

1%

0402

R11-4750T12-Y01

FBA_CLK0*

3,5

IN

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR O THERWISE, AND EXPRESSLY DISCLAIMS ALL

243

0402

1%

<New PN>

R509

243

0402

1%

<New PN>

<New PN>

C518

.01UF

16V

10%

X7R

0402

<New PN>

GND

M12-5PS12B5-H23

C GE

www.vinafix.vn

M12-5PS12B5-H23

M12-5PS12B5-H23

ASSEMBLY

PAGE DETAIL

IN

3,5

IN

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

Partition A Memories

0402

R522

475

1%

0402

R11-4750T12-Y01

FBA_CLK1*FBA_CLK_C0 FBA_CLK_C1

1%

<New PN>

R518

243

0402

1%

<New PN>

R523 243

FBA_CLK1

3,5

FBVDDQ

C535

0

5%

0402

<New PN>

GND

M12-5PS12B5-H23

M12-5PS12B5-H23

C523

.01UF

16V

10%

X7R

0402

<New PN>

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

M12-5PS12B5-H23

600-10729-xxxx-000 A