MSI MS-V130 Schematic 1.2

5

Title

Title

Title

RH PCIE RV635 2x256MB DDR2 DUAL DL-DVI-I DL-DVI-I VO FH Wednesday, January 09, 2008

RH PCIE RV635 2x256MB DDR2 DUAL DL-DVI-I DL-DVI-I VO FH Wednesday, January 09, 2008

RH PCIE RV635 2x256MB DDR2 DUAL DL-DVI-I DL-DVI-I VO FH Wednesday, January 09, 2008

REVISION HISTORY

REVISION HISTORY

REVISION HISTORY

D D

Sch

Sch

Sch

Rev

Rev

Rev

PCB

PCB

PCB

Rev

Rev

Rev

0

00A

1

00

Date

Date

Date

16/10/07

Initial design for RV635 GDDR3

Release to Production20/12/07

4

NOTE:

NOTE:

NOTE:

3

105-B382xx-10

105-B382xx-10

105-B382xx-10

This schematic represents the PCB, it does not represent any specific SKU.

This schematic represents the PCB, it does not represent any specific SKU.

This schematic represents the PCB, it does not represent any specific SKU.

For Stuffing options (component values, DNI’s, …) please consult the product specific BOM.

For Stuffing options (component values, DNI’s, …) please consult the product specific BOM.

For Stuffing options (component values, DNI’s, …) please consult the product specific BOM.

Please contact AMD representative to obtain latest BOM closest to the application desired.

Please contact AMD representative to obtain latest BOM closest to the application desired.

Please contact AMD representative to obtain latest BOM closest to the application desired.

REVISION DESCRIPTION

REVISION DESCRIPTION

REVISION DESCRIPTION

2

Date:Schematic No.

Date:Schematic No.

Date:Schematic No.

1

Rev

Rev

Rev

2

2

2

210

C C

B B

04/01/08 HDMI J2001 connector changed from 61400515G to 6140024800G

A A

5

4

3

2

1

www.vinafix.vn

5

4

3

2

1

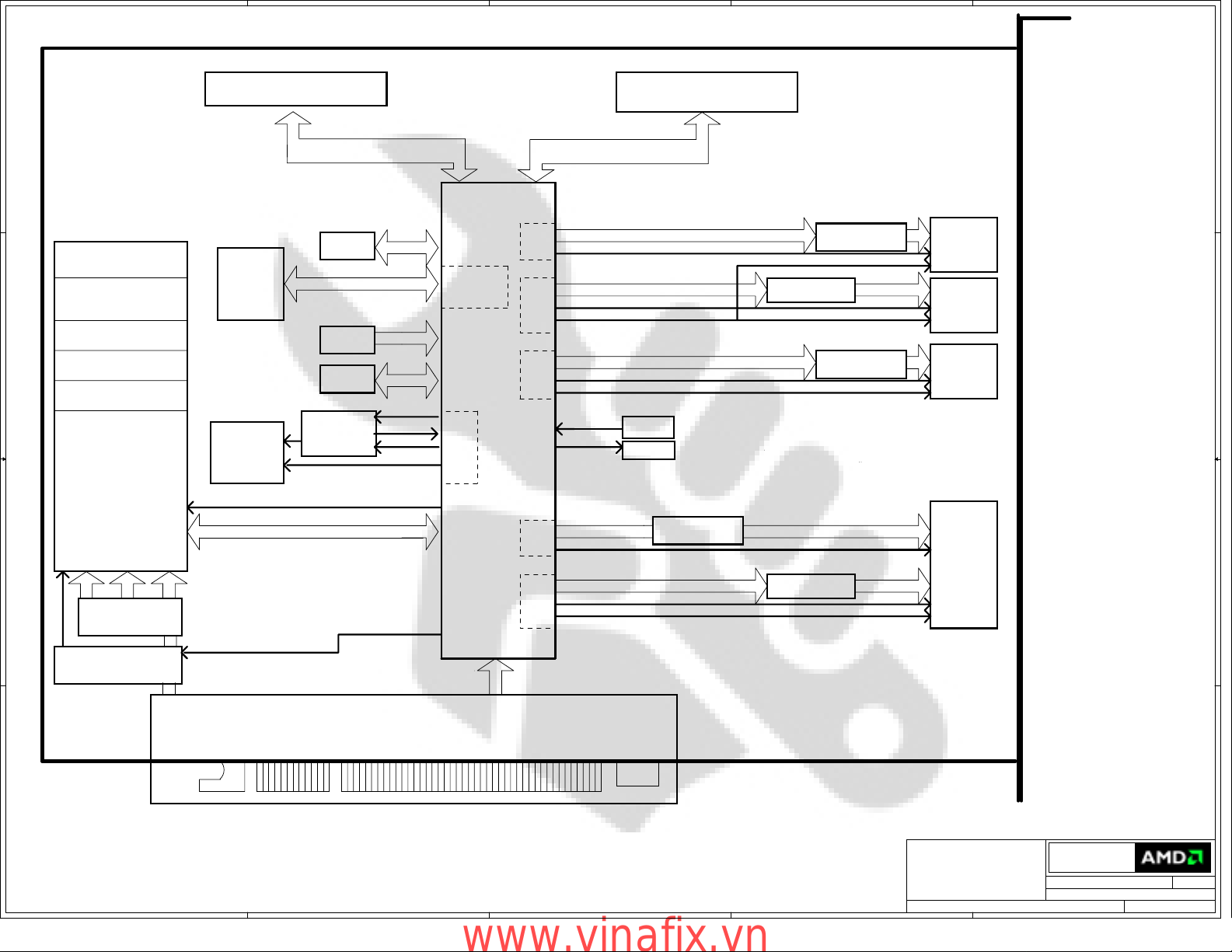

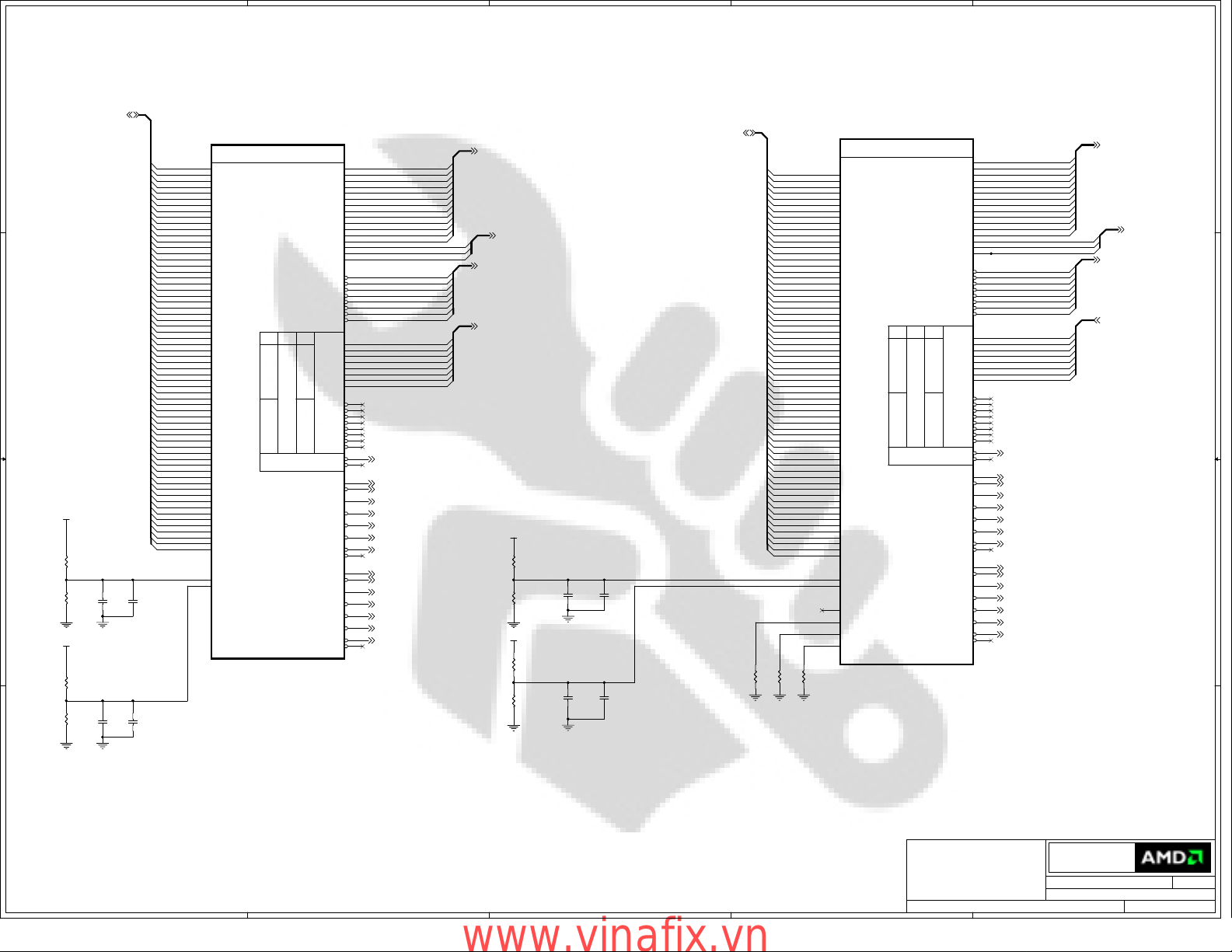

MEMORY CHANNEL A & B - RANK0

DDR2 4pcs 16Mx32 (256MB)

D D

MEMORY CHANNEL A & B - RANK1

DDR2 4pcs 16Mx32 (256MB)

RANK0 RANK1

TMDP

Debug

POWER REGULATORS

From +12V

+VDDC (MPVDD, VDDCI),

+MVDD

From +12V LINEAR:

C C

B B

+5V, +5V_VESA,

From +12V DIRECT:

FAN

From +MVDD Linear (1.1V):

PCIE_VDDC, DPLL_VDDC

From +3.3V:

Direct or Linear (1.8V)

VDD_CT, DPLL_PVDD,

DPA_PVDD, DPB_PVDD,

PVDD, DPA_VDDR,

DPB_VDDR,

T2XVDDR(LTVDD33),

VDDC(LTVDD18), AVDD,

A2VDD, A2VDDQ, VDD1DI,

VDD2DI, PCIE_VDDR,

PCIE_PVDD, VDDR3, VDDR4,

VDDR5

+PCIE_SOURCE

+3.3V

3.3V_BUS

delayed circuit

SMPS Enable

Circuit

+12V_BUS

CrossFire

Interlink

Header

FAN

POWER DELIVERY

Connector

Straps

BIOS

Speed control

& temperature

sense

INTERRUPT

Temp. Sensing

Built-in PWM

Dynamic VDDC

Temperature Critical

CrossFire

DVOCLK

DVPCNTL_[0..2]

DVPDATA[23:0]

DVP_MVP_CNTL[1:0]

GPIO[6:3]

GENERICB, DVALID

GPIO

ROM

Thermal

DDC2

GPIO17

D+/D-

TS_FDO

GPIO20

RV635

CTF

PCI-Express

DPA

HPD1

DAC2

CRT2

H/V2Sync

AUX_DDC3

TMDP

DPA

HPD3

AUX_DDC4

XTALIN

XTALOUT

TMDS2

DL TMDS2

HPD2

(GPIO14)

DAC1

CRT1

H/VSync

DDC1

RBG Filters

Oscillator

XTAL

Shunt Resistors

RBG Filters

AC Coupling Caps

AC Coupling Caps

HDMI

Connector

Slim-VGA

Connector

DisplayPort

Connector

HPD2

DVI-I

Slim-VGA

Connector

5V_VESA

&

+3.3V_BUS

+12V_BUS

PCI-Express Bus

RH PCIE RV635 2x256MB DDR2

DL-DVI-I DP DP FH

REV 0

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RV635 DDR2 - BLOCK DIAGRAM

RV635 DDR2 - BLOCK DIAGRAM

5

4

3

2

RV635 DDR2 - BLOCK DIAGRAM

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Wednesday, January 09, 2008

Wednesday, January 09, 2008

Wednesday, January 09, 2008

Sheet

Sheet

Sheet

of

21 21

of

21 21

of

21 21

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

2

2

2

105-B382xx-10

105-B382xx-10

105-B382xx-10

www.vinafix.vn

8

7

6

5

4

3

2

1

+12V_BUS

C1

CAP CER 10UF 20% 16V X5R

10UFC110UF

(1206)1.8MM H MAX

+12V_BUS

+12V_BUS

C3

D D

C C

B B

C2

150nF_16VC3150nF_16V

150nF_16VC2150nF_16V

CAP CER 10UF 10% 6.3V X6S

(0805)1.4MM MAX THICK

Overlap footprints

+3.3V_BUS

MC4

MC4

C4

DNI

+3.3V_BUS

4.7uF_6.3V

4.7uF_6.3V

10uF_X6SC410uF_X6S

C6

C5

1uF_6.3VC61uF_6.3V

100nF_6.3VC5100nF_6.3V

Place these caps as close to the PCIE

connector as possible

SMBCLK(7)

SMBDATA(7) DDC1DATA_TDI (3)

PETn0_GFXRn0(2)

PETp1_GFXRp1(2)

PETn1_GFXRn1(2)

PETp2_GFXRp2(2)

PETn2_GFXRn2(2)

PETp3_GFXRp3(2)

C0

10nFC010nF

PETn3_GFXRn3(2)

PETp4_GFXRp4(2)

PETn4_GFXRn4(2)

PETp5_GFXRp5(2)

PETn5_GFXRn5(2)

PETp6_GFXRp6(2)

PETn6_GFXRn6(2)

PETp7_GFXRp7(2)

PETn7_GFXRn7(2)

PETp8_GFXRp8(2)

PETn8_GFXRn8(2)

PETp9_GFXRp9(2)

PETn9_GFXRn9(2)

PETp10_GFXRp10(2)

PETn10_GFXRn10(2)

PETp11_GFXRp11(2)

PETn11_GFXRn11(2)

PETp12_GFXRp12(2)

PETn12_GFXRn12(2)

PETp13_GFXRp13(2)

PETn13_GFXRn13(2)

PETp14_GFXRp14(2)

PETn14_GFXRn14(2)

PETp15_GFXRp15(2)

PETn15_GFXRn15(2)

TEST_EN_J

JTAG_TRST#

R10RR1

0R

PRESENCE

PCI-EXPRESS EDGE CONNECTOR

+3.3V_BUS

+12V_BUS

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

+12V#B1

+12V#B2

+12V#B3

GND#B4

SMCLK

SMDAT

GND#B7

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

x16 PCIe

x16 PCIe

Mechanical Key

Mechanical Key

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

JTAG2

JTAG3

JTAG4

JTAG5

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLKGND#A15

PERp0

PERn0

GND#A18

RSVD#A19

GND#A20

PERp1

PERn1

GND#A23

GND#A24

PERp2

PERn2

GND#A27

GND#A28

PERp3

PERn3

GND#A31

RSVD#A32

RSVD#A33

GND#A34

PERp4

PERn4

GND#A37

GND#A38

PERp5

PERn5

GND#A41

GND#A42

PERp6

PERn6

GND#A45

GND#A46

PERp7

PERn7

GND#A49

RSVD#A50

GND#A51

PERp8

PERn8

GND#A54

GND#A55

PERp9

PERn9

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

MPCIE1

MPCIE1

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

+3.3V_BUS+12V_BUS

PRESENCE

JTCK

JTDI

JTDO

JTMS

TEST_EN_J

JTAG_TRST#

C7

100nF_6.3VC7100nF_6.3V

C9

100nF_6.3VC9100nF_6.3V

C11

C11

100nF_6.3V

100nF_6.3V

C13

C13

100nF_6.3V

100nF_6.3V

C15

C15

100nF_6.3V

100nF_6.3V

C17

C17

100nF_6.3V

100nF_6.3V

C19

C19

100nF_6.3V

100nF_6.3V

C21

C21

100nF_6.3V

100nF_6.3V

C23

C23

100nF_6.3V

100nF_6.3V

C25

C25

100nF_6.3V

100nF_6.3V

C27

C27

100nF_6.3V

100nF_6.3V

C29

C29

100nF_6.3V

100nF_6.3V

C31

C31

100nF_6.3V

100nF_6.3V

C33

C33

100nF_6.3V

100nF_6.3V

C35

C35

100nF_6.3V

100nF_6.3V

C37

C37

100nF_6.3V

100nF_6.3V

PERST#

TP4TP4

TP3TP3

C8

100nF_6.3VC8100nF_6.3V

C10

C10

100nF_6.3V

100nF_6.3V

C12

C12

100nF_6.3V

100nF_6.3V

C14

C14

100nF_6.3V

100nF_6.3V

C16

C16

100nF_6.3V

100nF_6.3V

C18

C18

100nF_6.3V

100nF_6.3V

C20

C20

100nF_6.3V

100nF_6.3V

C22

C22

100nF_6.3V

100nF_6.3V

C24

C24

100nF_6.3V

100nF_6.3V

C26

C26

100nF_6.3V

100nF_6.3V

C28

C28

100nF_6.3V

100nF_6.3V

C30

C30

100nF_6.3V

100nF_6.3V

C32

C32

100nF_6.3V

100nF_6.3V

C34

C34

100nF_6.3V

100nF_6.3V

C36

C36

100nF_6.3V

100nF_6.3V

C38

C38

100nF_6.3V

100nF_6.3V

TP1TP1

TP2TP2

PCIE_REFCLKP (2)

PCIE_REFCLKN (2)PETp0_GFXRp0(2)

GFXTp0_PERp0 (2)

GFXTn0_PERn0 (2)

GFXTp1_PERp1 (2)

GFXTn1_PERn1 (2)

GFXTp2_PERp2 (2)

GFXTn2_PERn2 (2)

GFXTp3_PERp3 (2)

GFXTn3_PERn3 (2)

GFXTp4_PERp4 (2)

GFXTn4_PERn4 (2)

GFXTp5_PERp5 (2)

GFXTn5_PERn5 (2)

GFXTp6_PERp6 (2)

GFXTn6_PERn6 (2)

GFXTp7_PERp7 (2)

GFXTn7_PERn7 (2)

GFXTp8_PERp8 (2)

GFXTn8_PERn8 (2)

GFXTp9_PERp9 (2)

GFXTn9_PERn9 (2)

GFXTp10_PERp10 (2)

GFXTn10_PERn10 (2)

GFXTp11_PERp11 (2)

GFXTn11_PERn11 (2)

GFXTp12_PERp12 (2)

GFXTn12_PERn12 (2)

GFXTp13_PERp13 (2)

GFXTn13_PERn13 (2)

GFXTp14_PERp14 (2)

GFXTn14_PERn14 (2)

GFXTp15_PERp15 (2)

GFXTn15_PERn15 (2)

No JTAG

R2 0RR2 0R

TDA08H0SB1R

TDA08H0SB1R

21345678

21345678

ON

ON

TSW1

TSW1

98

107

116

125

134

143

152

161

TP6TP6

TEST_EN_R (3)

HSYNC1_TRST (3)

VSYNC1_TCK (3)

GEN_D_HPD4_TDO (7)

DDC1CLK_TMS (3)

+3.3V

53

1

2

R_RST

R3 0RR3 0R

Table 1: Connection for JTAG

Production

(No JTAG)

Internal Use Only

TSW1 & R2 are located on the bottom side of the board close to PCIE connector.

Install R1 & R2 .Don't Install TSW1

Install TSW1 & Don't Install R2

TSW1 Switch #1, 2, 3, 4, 5 and 6 closed (ON)

JTAG

#7,8 open

TSW1 Switch #1, 2, 3, 4, 5 and 6 open

NO JTAG

#7,8 closed (ON)

C39

C39

100nF_6.3V

100nF_6.3V

NC7SZ08P5X_NL

NC7SZ08P5X_NL

4

U5

U5

Place R3 in U5

PERST#_buf (2)

SYMBOL LEGEND

DO NOT

DNI

INSTALL

ACTIVE

#

LOW

DIGITAL

GROUND

ANALOG

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RV635 DDR2 - PCI-E Edge Connector

RV635 DDR2 - PCI-E Edge Connector

8

7

6

5

4

3

RV635 DDR2 - PCI-E Edge Connector

2

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Wednesday, January 09, 2008

Wednesday, January 09, 2008

Wednesday, January 09, 2008

Sheet

Sheet

Sheet

of

121

of

121

of

121

GROUND

BUO BRING UP

ONLY

Doc No.

Doc No.

Doc No.

105-B382xx-10

105-B382xx-10

105-B382xx-10

1

RevDate:

RevDate:

RevDate:

2

2

2

www.vinafix.vn

5

D D

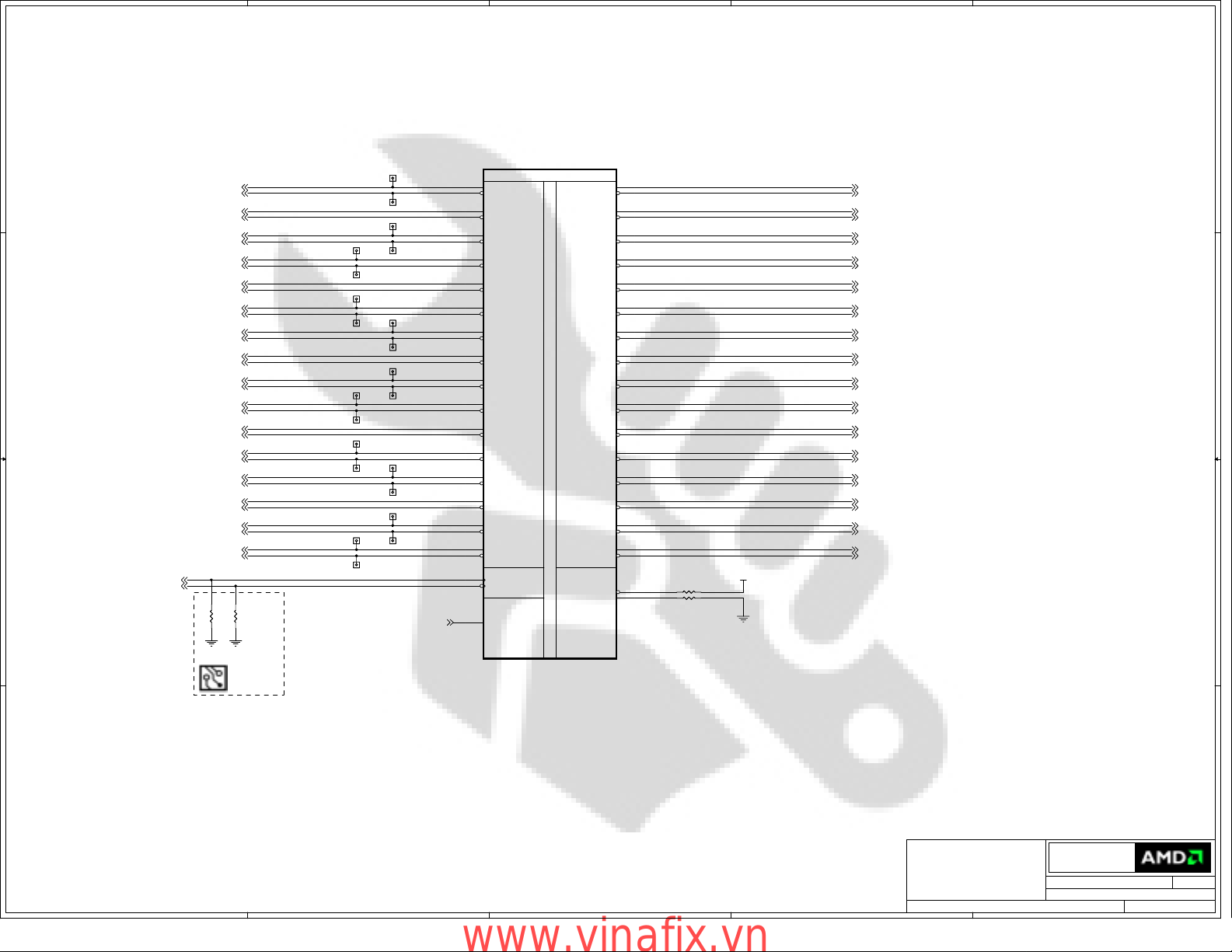

NOTE: some of the PCIE testpoints will

be available trought via on traces.

PETp0_GFXRp0(1)

PETn0_GFXRn0(1)

PETp1_GFXRp1(1)

PETn1_GFXRn1(1)

PETp2_GFXRp2(1)

PETn2_GFXRn2(1)

PETp3_GFXRp3(1)

PETn3_GFXRn3(1)

PETp4_GFXRp4(1)

PETn4_GFXRn4(1)

PETp5_GFXRp5(1)

PETn5_GFXRn5(1)

PETp6_GFXRp6(1)

C C

B B

PCIE_REFCLKP(1)

PCIE_REFCLKN(1)

PETn6_GFXRn6(1)

PETp7_GFXRp7(1)

PETn7_GFXRn7(1)

PETp8_GFXRp8(1)

PETp9_GFXRp9(1)

PETn9_GFXRn9(1)

PETp10_GFXRp10(1)

PETn10_GFXRn10(1)

PETp11_GFXRp11(1)

PETn11_GFXRn11(1)

PETp12_GFXRp12(1)

PETn12_GFXRn12(1)

PETp13_GFXRp13(1)

PETn13_GFXRn13(1)

PETp14_GFXRp14(1)

PETn14_GFXRn14(1)

PETp15_GFXRp15(1)

PETn15_GFXRn15(1)

DNI DNI

R14

R14

R13

R13

51R

51R

51R

51R

402 402

TP12TP12

TP13TP13

TP14TP14

TP19TP19

TP20TP20

TP21TP21

TP22TP22

TP27TP27

TP28TP28

4

U1A

TP7TP7

TP8TP8

TP9TP9

TP10TP10TP11TP11

TP15TP15

TP16TP16

TP17TP17

TP18TP18

TP23TP23

TP24TP24

TP25TP25

TP26TP26

U1A

AK33

AJ33

AJ35

AJ34

AH35

AH34

AG35

AG34

AF33

AE33

AE35

AE34

AD35

AD34

AC35

AC34

AB33

AA33

AA35

AA34

Y35

Y34

W35

W34

V33

U33

U35

U34

T35

T34

R35

R34

AJ31

AJ30

PERST#_buf(1)

AM32

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

Clock

Clock

PCIE_REFCLKP

PCIE_REFCLKN

PERSTB

PART 1 OF 7

PART 1 OF 7

P

P

C

C

I

I

-

E

E

X

X

P

P

R

R

E

E

S

S

S

S

I

I

N

N

T

T

E

E

R

R

F

F

A

A

C

C

E

E

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

Calibration

Calibration

PCIE_CALRN

PCIE_CALRP

3

AG31

AG30

AF31

AF30

AF28

AF27

AD31

AD30

AD28

AD27

AB31

AB30

AB28

AB27

AA31

AA30

AA28

AA27

W31

W30

W28

W27

V31

V30

V28

V27

U31

U30

U28

U27

R31

R30

+PCIE_VDDC

402

AG26

AJ27

R9

1.27KR91.27K

R82.0K R82.0K

402

2

GFXTp0_PERp0 (1)

GFXTn0_PERn0 (1)

GFXTp1_PERp1 (1)

GFXTn1_PERn1 (1)

GFXTp2_PERp2 (1)

GFXTn2_PERn2 (1)

GFXTp3_PERp3 (1)

GFXTn3_PERn3 (1)

GFXTp4_PERp4 (1)

GFXTn4_PERn4 (1)

GFXTp5_PERp5 (1)

GFXTn5_PERn5 (1)

GFXTp6_PERp6 (1)

GFXTn6_PERn6 (1)

GFXTp7_PERp7 (1)

GFXTn7_PERn7 (1)

GFXTp8_PERp8 (1)

GFXTn8_PERn8 (1)PETn8_GFXRn8(1)

GFXTp9_PERp9 (1)

GFXTn9_PERn9 (1)

GFXTp10_PERp10 (1)

GFXTn10_PERn10 (1)

GFXTp11_PERp11 (1)

GFXTn11_PERn11 (1)

GFXTp12_PERp12 (1)

GFXTn12_PERn12 (1)

GFXTp13_PERp13 (1)

GFXTn13_PERn13 (1)

GFXTp14_PERp14 (1)

GFXTn14_PERn14 (1)

GFXTp15_PERp15 (1)

GFXTn15_PERn15 (1)

1

For Tektronix LA only

Place close

to ASIC

A A

5

4

RV635 XT A11

RV635 XT A11

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RV635 DDR2 - ASIC PCIE_Interface

RV635 DDR2 - ASIC PCIE_Interface

3

2

RV635 DDR2 - ASIC PCIE_Interface

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Wednesday, January 09, 2008

Wednesday, January 09, 2008

Wednesday, January 09, 2008

Sheet

Sheet

Sheet

of

221

of

221

of

221

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

2

2

2

105-B382xx-10

105-B382xx-10

105-B382xx-10

www.vinafix.vn

5

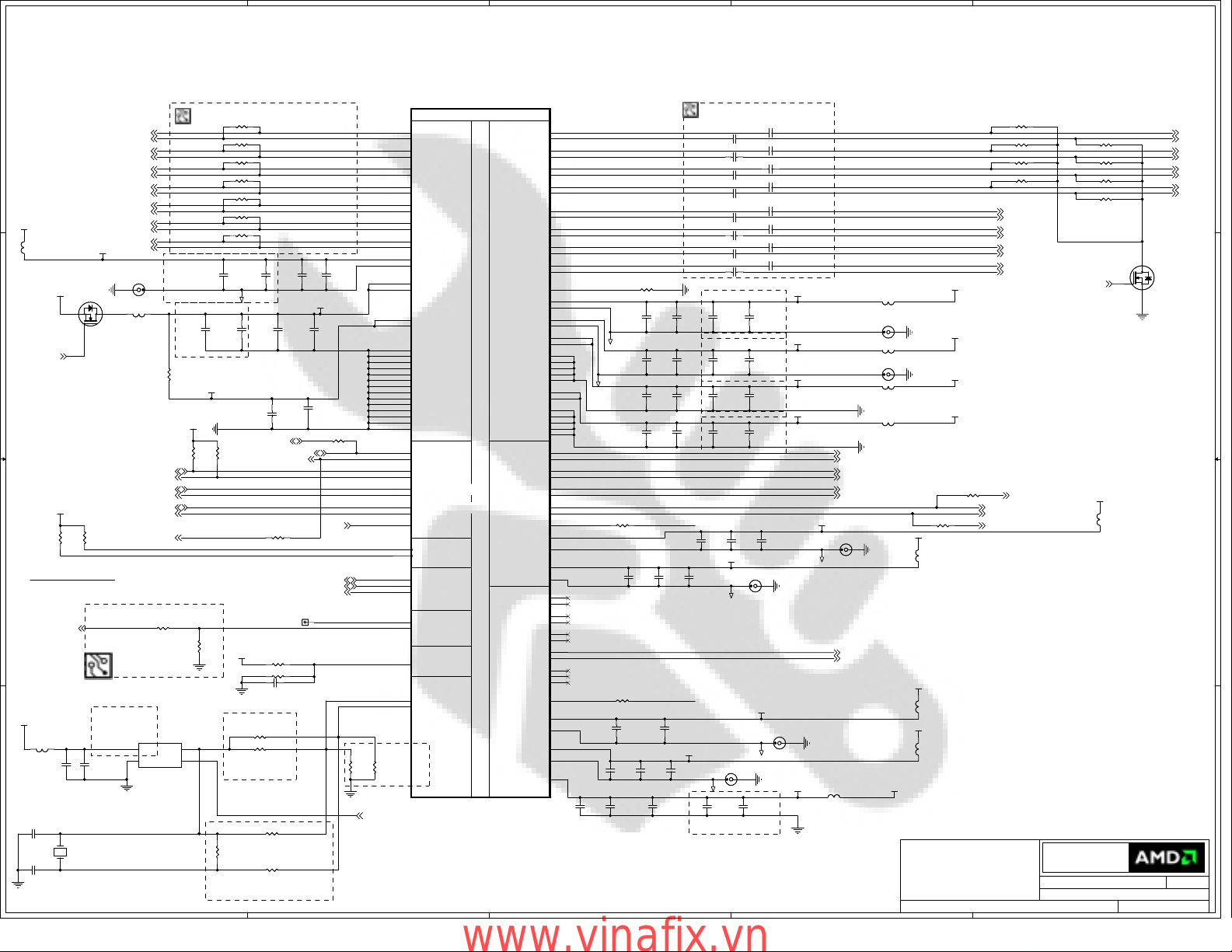

Recommended caps:

(see BOM for qualified values/vendors)

10uF , X6S, 0805, 6.3V, 1.4MM MAX THICK

1uF, X6S, 0402, 6.3V

100nF, X7R, 0402

10nF , X7R, 0402

Overlap footprints

4.7uF_6.3V

4.7uF_6.3V

R1090RR109

0R

R71KR7

1K

DNI

OUT

E/D

Place close to ASIC

R106 100RR106 100R

R100 100RR100 100R

R101 100RR101 100R

R102 100RR102 100R

R103 100RR103 100R

R104 100RR104 100R

R105 100RR105 100R

MC100

MC100

4.7uF_6.3V

4.7uF_6.3V

MC103

MC103

+3.3V

3

1

10uF_X6S

10uF_X6S

GND_T2PVSS

C103

C103

10uF_X6S

10uF_X6S

+LTVDD33

R41

R41

R40

R40

4.7K

4.7K

4.7K

4.7K

402 402

DDC2DATA

DDC2CLK

SDA

SCL

MR71KMR7

1K

+1.8V

NR81 182RNR81 182R

R81 182RR81 182R

R841MR84

1M

Place R_RTCLK close to XTAL so the

main clock line has shortest stub

C100

C100

C108

C108

1uF_6.3V

1uF_6.3V

C107

C107

1uF_6.3V

1uF_6.3V

DDC1DATA_TDI(1)

CRT1DDCDATA(15)

CRT1DDCCLK(15)

TR12 0RTR12 0R

R43 221RR43 221R

R44 110RR44 110R

Share one pad

OSC_EN

R85 0RR85 0R

R_RTCLK

MR86 0RMR86 0R

C101

C101

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

DNI

C46

C46

100nF_6.3V

100nF_6.3V

C109

C109

+LTVDD18

C105

C105

100nF_6.3V

100nF_6.3V

TR13 0RTR13 0R

GPU_DMINUS(18)

GPU_DPLUS(18)

TS_FDO(18)

TP42

TP42

35mil

35mil

PLL_TEST

TEST_EN

D D

+1.8V

B889

B889

BLM15BD121SN1

BLM15BD121SN1

C C

LVT_EN(13)

I2C DEVICE ADDRESS' ON DDC2

B B

DEVICE

LM63

DP

+1.8V

+3.3V

R35

R35

4.7K

4.7K

ADDRESS

x100 1100

TBD

+T2PVDD

Q100

Q100

SI2304DS

SI2304DS

1

R36

R36

4.7K

4.7K

T2XCM(15)

T2XCP(15)

T2X0M(15)

T2X0P(15)

T2X1M(15)

T2X1P(15)

T2X2M(15)

T2X2P(15)

T2X3M(15)

T2X3P(15)

T2X4M(15)

T2X4P(15)

T2X5M(15)

T2X5P(15)

NS100

NS100

NS_VIA

NS_VIA

1 2

Use 0R

B100

B100

32

BLM15BD121SN1

BLM15BD121SN1

DDC2DATA(13,18)

DDC2CLK(13,18)

DDC3_DATA_DP3_AUXN(16)

DDC3_CLK_DP3_AUXP(16)

DDC4_DATA_DP4_AUXN(17)

DDC4_CLK_DP4_AUXP(17)

DDC1CLK_TMS(1)

What happens to all the JTAG resistors especially R7 and also the TRs?

Do Not Share PADs

TEST_EN_R(1)

XTALOUT_S

C80

C80

100nF_6.3V

100nF_6.3V

Y82

Y82

27.000MHz_10PPM

27.000MHz_10PPM

XTALOUT_S

is done for

ease of layout

5

Y81

Y81

4

VCC

2

GND

27.000MHz

27.000MHz

XTALIN_S

XTALOUT_S

+3.3V_BUS

B80

B80

BLM15BD121SN1

BLM15BD121SN1

C81

C81

1uF_6.3V

1uF_6.3V

A A

C82

C82

12pF_50V

12pF_50V

2 1

C83

C83

12pF_50V

12pF_50V

HPD1(16)

T2XCM

T2XCP

T2X0M

T2X0P

T2X1M

T2X1P

T2X2M

T2X2P

T2X3M

T2X3P

T2X4M

T2X4P

T2X5M

T2X5P

C102

C102

1uF_6.3V

1uF_6.3V

DNI

VREFG

XTALIN

XTALOUT

R82

R82

221R

221R

4

AP22

AR22

AN22

AN23

AR23

AP23

AR24

AP24

AR25

AP25

AN26

AN27

AR27

AP27

AL22

AK22

AK27

AL27

AJ26

AH26

AJ22

AN21

AN24

AN25

AN28

AP21

AP26

AR21

AR26

AJ24

AM22

AM24

AM26

AM27

AM29

AL29

AJ15

AH15

AJ5

AJ4

AH14

AG14

AG6

AK6

AM6

AK4

AM4

AG21

AH19

AM30

AD12

AR33

AP33

MR82

MR82

221R

221R

Share one pad

OSC_EN (13,14)

4

U1B

U1B

Integrated

Integrated

LVTM/TMDS2

LVTM/TMDS2

T2XCM

T2XCP

T2X0M

T2X0P

T2X1M

T2X1P

T2X2M

T2X2P

T2X3M

T2X3P

T2X4M

T2X4P

T2X5M

T2X5P

T2PVDD

T2PVSS

T2XVDDC_1

T2XVDDC_2

T2XVDDR_1

T2XVDDR_2

T2XVSSR_1

T2XVSSR_2

T2XVSSR_3

T2XVSSR_4

T2XVSSR_5

T2XVSSR_6

T2XVSSR_7

T2XVSSR_8

T2XVSSR_9

T2XVSSR_10

T2XVSSR_11

T2XVSSR_12

T2XVSSR_13

T2XVSSR_14

Monitor

Monitor

DDC1DATA

Interface

Interface

DDC1CLK

DDC2DATA

DDC2CLK

DDC3DATA_DP3_AUXN

DDC3CLK_DP3_AUXP

DDC4DATA_DP4_AUXN

DDC4CLK_DP4_AUXP

HPD1

SDA

MMI2C

MMI2C

SCL

DMINUS

Thermal

Thermal

DPLUS

Diode

Diode

TS_FDO

PLLTEST

Test

Test

TESTEN

VREFG

XTALIN

XTALOUT

RV635 XT A11

RV635 XT A11

PART 2 OF 7

PART 2 OF 7

V

V

I

I

D

D

E

E

O

O

&

&

M

M

U

U

L

L

T

T

I

I

M

M

E

E

D

D

I

I

A

A

Integrated

Integrated

DP/TMDS

DP/TMDS

TXCAM_DPA3N

TXCAP_DPA3P

TX0M_DPA2N

TX0P_DPA2P

TX1M_DPA1N

TX1P_DPA1P

TX2M_DPA0N

TX2P_DPA0P

TXCBM_DPB3N

TXCBP_DPB3P

TX3M_DPB2N

TX3P_DPB2P

TX4M_DPB1N

TX4P_DPB1P

TX5M_DPB0N

TX5P_DPB0P

DPA_PVDD

DPA_PVSS

DPB_PVDD

DPB_PVSS

DPA_VDDR_1

DPA_VDDR_2

DPA_VSSR_1

DPA_VSSR_2

DPA_VSSR_3

DPA_VSSR_4

DPA_VSSR_5

DPB_VDDR_1

DPB_VDDR_2

DPB_VSSR_1

DPB_VSSR_2

DPB_VSSR_3

DPB_VSSR_4

DPB_VSSR_5

DAC / CRT

DAC / CRT

DAC2 (TV/CRT2)

DAC2 (TV/CRT2)

DP_CALR

HSYNC

VSYNC

RSET

AVDD

AVSSQ

VDD1DI

VSS1DI

H2SYNC

V2SYNC

COMP

R2SET

A2VDDQ

A2VSSQ

VDD2DI

VSS2DI

A2VDD

AN9

AN10

AR10

AP10

AR11

AP11

AR12

AP12

AR14

AP14

AR15

AP15

AR16

AP16

AR17

AP17

DP_CALR

AG15

AM14

AL14

AH17

AG17

AP19

AR19

AN11

AN12

AN13

AN14

AN15

AN19

AN20

AN16

AN17

AN18

AR18

AP18

AR31

R

AP31

RB

AR30

G

AP30

GB

AR29

B

AP29

BB

AN29

AN30

AN31

AR32

AP32

AR28

AP28

AM19

R2

AL19

R2B

AM18

G2

AL18

G2B

AM17

B2

AL17

B2B

AM15

AL15

AK18

Y

AK19

C

AK17

R2SET GND_A2VSSQ

AJ21

AL21

AK21

AH22

AG22

AM21

C2030

C2030

10nF

10nF

3

R128 150RR128 150R

GND_DPAVSS

GND_DBPVSS

R1030 499RR1030 499R

C1023

C1023

10nF

10nF

R2030 715RR2030 715R

C2021

C2021

100nF_6.3V

100nF_6.3V

C2024

C2024

10nF

10nF

C2031

C2031

100nF_6.3V

100nF_6.3V

3

DPA_C_3N

DPA_C_3P

DPA_C_2N

DPA_C_2P

DPA_C_1N

DPA_C_1P

DPA_C_0N

DPA_C_0P

DPB_C_3N

DPB_C_3P

DPB_C_2N

DPB_C_2P

DPB_C_1N

DPB_C_1P

DPB_C_0N

DPB_C_0P

C111

C111

100nF

100nF

C190

C190

100nF

100nF

C115

C115

100nF

100nF

C193

C193

100nF

100nF

C2025

C2025

100nF_6.3V

100nF_6.3V

GND_AVSSQRSET

C1024

C1024

100nF_6.3V

100nF_6.3V

C2032

C2032

1uF_6.3V

1uF_6.3V

C112

C112

1uF_6.3V

1uF_6.3V

C191

C191

1uF_6.3V

1uF_6.3V

C116

C116

1uF_6.3V

1uF_6.3V

C194

C194

1uF_6.3V

1uF_6.3V

C2022

C2022

1uF_6.3V

1uF_6.3V

+VDD2DI

C2026

C2026

1uF_6.3V

1uF_6.3V

GND_VSS2DI

Place close to Connector

C1126 100nF_6.3VC1126 100nF_6.3V

C1124 100nF_6.3VC1124 100nF_6.3V

C1122 100nF_6.3VC1122 100nF_6.3V

C1120 100nF_6.3VC1120 100nF_6.3V

C1136 100nF_6.3VC1136 100nF_6.3V

C1134 100nF_6.3VC1134 100nF_6.3V

C1132 100nF_6.3VC1132 100nF_6.3V

C1130 100nF_6.3VC1130 100nF_6.3V

Overlap footprints

C113

C113

10uF_X6S

10uF_X6S

Overlap footprints

C192

C192

10uF_X6S

10uF_X6S

Overlap footprints

C117

C117

10uF_X6S

10uF_X6S

Overlap footprints

C195

C195

10uF_X6S

10uF_X6S

C1021

C1021

C1020

C1020

100nF_6.3V

100nF_6.3V

10nF

10nF

+VDD1DI

NS1021 NS_VIANS1021 NS_VIA

C1025

C1025

1uF_6.3V

1uF_6.3V

GND_VSS1DI

NS2021 NS_VIANS2021 NS_VIA

12

C2033

C2033

10uF_X6S

10uF_X6S

Overlap footprints

C1127 100nF_6.3VC1127 100nF_6.3V

C1125 100nF_6.3VC1125 100nF_6.3V

C1123 100nF_6.3VC1123 100nF_6.3V

C1121 100nF_6.3VC1121 100nF_6.3V

C1137 100nF_6.3VC1137 100nF_6.3V

C1135 100nF_6.3VC1135 100nF_6.3V

C1133 100nF_6.3VC1133 100nF_6.3V

C1131 100nF_6.3VC1131 100nF_6.3V

MC113

MC113

4.7uF_6.3V

4.7uF_6.3V

MC192

MC192

4.7uF_6.3V

4.7uF_6.3V

MC117

MC117

4.7uF_6.3V

4.7uF_6.3V

MC195

MC195

4.7uF_6.3V

4.7uF_6.3V

C1022

C1022

1uF_6.3V

1uF_6.3V

12

+A2VDDQ

NS2020 NS_VIANS2020 NS_VIA

12

GND_A2VSSQ

+A2VDD

MC2033

MC2033

4.7uF_6.3V

4.7uF_6.3V

2

+DPA_PVDD

+DPB_PVDD

+DPA_VDDR

+DPB_VDDR

+AVDD

NS1020 NS_VIANS1020 NS_VIA

B887 BLM15BD121SN1B887 BLM15BD121SN1

NS110

NS110

NS_VIA

NS_VIA

12

B890 BLM15BD121SN1B890 BLM15BD121SN1

NS190

NS190

NS_VIA

NS_VIA

12

B881 BLM15BD121SN1B881 BLM15BD121SN1

B892 BLM15BD121SN1B892 BLM15BD121SN1

A_DAC1_R (15)

A_DAC1_RB (15)

A_DAC1_G (15)

A_DAC1_GB (15)

A_DAC1_B (15)

A_DAC1_BB (15) HSYNC1_TRST (1)

12

GND_AVSSQ

HSYNC_DAC2 (7)

VSYNC_DAC2 (7)

B2030 26R_600mAB2030 26R_600mA

+3.3V

Title

Title

2

Title

+1.8V

+1.8V

+1.1V

+1.1V

DNI

TR14 0RTR14 0R

DNI

TR10 0RTR10 0R

+1.8V

B884

B884

BLM15BD121SN1

BLM15BD121SN1

+1.8V

B883

B883

BLM15BD121SN1

BLM15BD121SN1

+1.8V

B885

B885

BLM15BD121SN1

BLM15BD121SN1

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

RV635 DDR2 - ASIC MAIN

RV635 DDR2 - ASIC MAIN

RV635 DDR2 - ASIC MAIN

R120 499RR120 499R

R122 499RR122 499R

R124 499RR124 499R

R126 499RR126 499R

DPB_3N (17)

DPB_3P (17)

DPB_2N (17)

DPB_2P (17)

DPB_1N (17)

DPB_1P (17)

DPB_0N (17)

DPB_0P (17)

HSYNC_DAC1 (7,15)

VSYNC_DAC1 (7,15)

VSYNC1_TCK (1)

1

R121 499RR121 499R

R123 499RR123 499R

R125 499RR125 499R

R127 499RR127 499R

DP_GND

LVT_EN(13)

+1.8V

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Wednesday, January 09, 2008

Wednesday, January 09, 2008

Wednesday, January 09, 2008

Sheet

Sheet

Sheet

of

321

of

321

of

321

1

1

B882

B882

BLM15BD121SN1

BLM15BD121SN1

Doc No.

Doc No.

Doc No.

T1XCM (16)

T1XCP (16)

T1X0M (16)

T1X0P (16)

T1X1M (16)

T1X1P (16)

T1X2M (16)

T1X2P (16)

32

Q110

Q110

SI2304DS

SI2304DS

RevDate:

RevDate:

RevDate:

2

2

2

105-B382xx-10

105-B382xx-10

105-B382xx-10

www.vinafix.vn

C151

C151

1uF_6.3V

1uF_6.3V

C131

C131

100nF_6.3V

100nF_6.3V

C141

C141

1uF_6.3V

1uF_6.3V

5

C152

C152

1uF_6.3V

1uF_6.3V

C132

C132

100nF_6.3V

100nF_6.3V

C142

C142

1uF_6.3V

1uF_6.3V

C133

C133

100nF_6.3V

100nF_6.3V

C143

C143

1uF_6.3V

1uF_6.3V

C154

C154

1uF_6.3V

1uF_6.3V

C134

C134

100nF_6.3V

100nF_6.3V

C144

C144

1uF_6.3V

1uF_6.3V

C155

C155

1uF_6.3V

1uF_6.3V

C135

C135

100nF_6.3V

100nF_6.3V

C145

C145

1uF_6.3V

1uF_6.3V

C136

C136

100nF_6.3V

100nF_6.3V

C146

C146

1uF_6.3V

1uF_6.3V

C157

C157

1uF_6.3V

1uF_6.3V

C137

C137

100nF_6.3V

100nF_6.3V

C147

C147

1uF_6.3V

1uF_6.3V

C158

C158

1uF_6.3V

1uF_6.3V

C138

C138

100nF_6.3V

100nF_6.3V

Recommended caps:

(see BOM for qualified values/vendors)

10uF , X6S, 0805, 6.3V, 1.4MM MAX THICK

1uF, X6S, 0402, 6.3V

100nF, X7R, 0402

10nF , X7R, 0402

+MVDD

C150

C150

1uF_6.3V

1uF_6.3V

D D

C156

C156

100nF_6.3V

100nF_6.3V

C153

C153

1uF_6.3V

1uF_6.3V

C130

C130

100nF_6.3V

100nF_6.3V

C140

C140

1uF_6.3V

1uF_6.3V

Overlap cap pair foorprints (0805 with 0603)

C126

C125

C125

10uF_X6S

10uF_X6S

MC125

MC125

4.7uF_6.3V

4.7uF_6.3V

+1.8V

C126

10uF_X6S

10uF_X6S

MC126

MC126

4.7uF_6.3V

4.7uF_6.3V

C121

C121

1uF_6.3V

1uF_6.3V

NS120 NS_VIANS120 NS_VIA

+3.3V

+1.8V

B886

B886

BLM15BD121SN1

BLM15BD121SN1

NS70 NS_VIANS70 NS_VIA

1 2

GND_PVSS

C127

C127

10uF_X6S

10uF_X6S

MC127

MC127

4.7uF_6.3V

4.7uF_6.3V

C120

C120

1uF_6.3V

1uF_6.3V

1 2

GND_VSSRHA_1

C90

C90

1uF_6.3V

1uF_6.3V

Overlap footprints

MC94

MC94

4.7uF_6.3V

4.7uF_6.3V

Overlap footprints

MC70

MC70

4.7uF_6.3V

4.7uF_6.3V

C91

C91

100nF_6.3V

100nF_6.3V

C94

C94

10uF_X6S

10uF_X6S

C124

C124

10uF_X6S

10uF_X6S

MC124

MC124

4.7uF_6.3V

4.7uF_6.3V

+MVDD

B120

B120

BLM15BD121SN1

BLM15BD121SN1

B121

B121

BLM15BD121SN1

C C

B B

A A

BLM15BD121SN1

NS121 NS_VIANS121 NS_VIA

1 2

GND_VSSRHA_2

B122

B122

BLM15BD121SN1

BLM15BD121SN1

B123

B123

BLM15BD121SN1

BLM15BD121SN1

C128

C128

10uF_X6S

10uF_X6S

MC128

MC128

4.7uF_6.3V

4.7uF_6.3V

NS122 NS_VIANS122 NS_VIA

1 2

GND_VSSRHB_1

C92

C92

1uF_6.3V

1uF_6.3V

+DPLL_PVDD

C70

C70

10uF_X6S

10uF_X6S

C129

C129

10uF_X6S

10uF_X6S

MC129

MC129

4.7uF_6.3V

4.7uF_6.3V

C122

C122

1uF_6.3V

1uF_6.3V

NS123 NS_VIANS123 NS_VIA

1 2

GND_VSSRHB_2

C95

C95

1uF_6.3V

1uF_6.3V

C71

C71

100nF_6.3V

100nF_6.3V

C93

C93

100nF_6.3V

100nF_6.3V

C97

C97

100nF_6.3V

100nF_6.3V

C72

C72

1uF_6.3V

1uF_6.3V

C148

C148

1uF_6.3V

1uF_6.3V

C123

C123

1uF_6.3V

1uF_6.3V

C96

C96

1uF_6.3V

1uF_6.3V

C159

C159

1uF_6.3V

1uF_6.3V

+DPLL_PVDD

GND_PVSS

4

C98

C98

100nF_6.3V

100nF_6.3V

AE14

AE15

AE17

AF12

AR20

AP20

AR35

H35

L22

M10

M35

P10

A12

A16

A20

A24

A28

B35

D35

K10

K12

K24

K26

L14

L15

L17

L18

L19

L21

A25

A32

B25

B32

AP2

AR2

AN1

AP1

A35

AR1

U1E

U1E

A8

M1

T1

Y1

B1

D1

H1

B2

L1

C2

L2

RV635 XT A11

RV635 XT A11

VDDR1_1

VDDR1_2

VDDR1_3

VDDR1_4

VDDR1_5

VDDR1_6

VDDR1_7

VDDR1_8

VDDR1_9

VDDR1_10

VDDR1_11

VDDR1_12

VDDR1_13

VDDR1_14

VDDR1_15

VDDR1_16

VDDR1_17

VDDR1_18

VDDR1_19

VDDR1_20

VDDR1_21

VDDR1_22

VDDR1_23

VDDR1_24

VDDR1_25

VDDR1_26

VDDR1_27

VDDR1_28

VDDR1_29

VDDRHA_1

VDDRHA_2

VDDRHB_1

VDDRHB_2

VSSRHA_1

VSSRHA_2

VSSRHB_1

VSSRHB_2

VDDR3_1

VDDR3_2

VDDR3_3

VDDR3_4

VDDR4_1

VDDR4_2

VDDR5_1

VDDR5_2

DPLL_PVDD

DPLL_PVSS

MECH_1

MECH_2

MECH_3

PART 5 OF 7

PART 5 OF 7

Memory I/O

Memory I/O

Selected PLL's

Selected PLL's

Mechanical Pins

Mechanical Pins

3

+MPVDD

GND_MPVSS

+DPLL_VDDC

+PCIE_PVDD

C930

C930

10nF

10nF

C900

C900

10nF

10nF

C161

C161

1uF_6.3V

1uF_6.3V

C171

C171

1uF_6.3V

1uF_6.3V

C160

C160

1uF_6.3V

1uF_6.3V

Overlap cap pair foorprints (0805 with 0603)

+VDDC

C78

C78

1uF_6.3V

1uF_6.3V

C64

C64

C65

C65

10nF

10nF

100nF_6.3V

100nF_6.3V

GND_PVSS

AM35

PCIE_PVDD

R26

PCIE_VDDC_1

W25

PCIE_VDDC_2

W26

PCIE_VDDC_3

AA25

PCIE_VDDC_4

AA26

PCIE_VDDC_5

AB25

PCIE_VDDC_6

AB26

PCIE_VDDC_7

AD26

PCIE_VDDC_8

AF26

PCIE_VDDC_9

U26

PCIE_VDDC_10

V25

PCIE_VDDC_11

V26

PCIE_VDDC_12

AL33

PCIE_VDDR_1

AM33

PCIE_VDDR_2

AN33

PCIE_VDDR_3

AN34

PCIE_VDDR_4

AN35

PCIE_VDDR_5

AP34

PCIE_VDDR_6

AP35

PCIE_VDDR_7

AR34

P

P

O

O

W

W

E

E

R

R

PCIE_VDDR_8

N13

VDDC_1

Core PCI-Express

Core PCI-Express

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDC_9

VDDC_10

VDDC_11

VDDC_12

VDDC_13

VDDC_14

VDDC_15

VDDC_16

VDDC_17

VDDC_18

VDDC_19

VDDC_20

VDDC_21

VDDC_22

VDDC_23

VDDC_24

VDDC_25

VDDC_26

VDDC_27

VDDC_28

VDDC_29

VDDC_30

VDDC_31

VDDC_32

VDDC_33

VDDC_34

VDDC_35

VDDC_36

VDDC_37

VDDC_38

VDDC_39

VDDC_40

VDDC_41

VDDC_42

VDDC_43

VDDC_44

BBP_1

BBP_2

VDDCI_1

VDDCI_2

VDDCI_3

VDDCI_4

VDD_CT_1

VDD_CT_2

VDD_CT_3

VDD_CT_4

VDD_CT_5

VDD_CT_6

VDD_CT_7

VDD_CT_8

MPVDD

MPVSS

DPLL_VDDC

R18

W11

AB19

AC23

AE18

AE19

AE21

AE22

N15

N18

N21

N23

P14

P17

P19

P22

R13

R15

R21

R23

U14

U17

U19

U22

V15

V18

V21

V23

W14

W17

W19

W22

AA15

AA18

AA21

AA23

AB14

AB17

AB22

AC13

AC15

AC18

AC21

U13

V13

M12

M24

P11

P25

R11

R25

U11

U25

AA11

AB11

AD10

AF10

A14

B15

AG19

C931

C931

100nF_6.3V

100nF_6.3V

C162

C162

1uF_6.3V

1uF_6.3V

C172

C172

1uF_6.3V

1uF_6.3V

C184

C184

1uF_6.3V

1uF_6.3V

C181

C181

10uF_X6S

10uF_X6S

MC181

MC181

4.7uF_6.3V

4.7uF_6.3V

C68

C68

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C61

C61

100nF_6.3V

100nF_6.3V

Overlap footprints

C932

C932

1uF_6.3V

1uF_6.3V

C920

C920

1uF_6.3V

1uF_6.3V

C901

C901

100nF_6.3V

100nF_6.3V

C163

C163

1uF_6.3V

1uF_6.3V

C173

C173

1uF_6.3V

1uF_6.3V

C69

C69

100nF_6.3V

100nF_6.3V

+MPVDD

C66

C66

C62

C62

1uF_6.3V

1uF_6.3V

C933

C933

10uF_X6S

10uF_X6S

C921

C921

1uF_6.3V

1uF_6.3V

C902

C902

1uF_6.3V

1uF_6.3V

C164

C164

1uF_6.3V

1uF_6.3V

C174

C174

1uF_6.3V

1uF_6.3V

C185

C185

1uF_6.3V

1uF_6.3V

C182

C182

10uF_X6S

10uF_X6S

MC182

MC182

4.7uF_6.3V

4.7uF_6.3V

+VDD_CT

BLM15BD121SN1

BLM15BD121SN1

Overlap footprints

C67

C67

10uF_X6S

10uF_X6S

Overlap footprints

C922

C922

1uF_6.3V

1uF_6.3V

C903

C903

10nF

10nF

C165

C165

1uF_6.3V

1uF_6.3V

C175

C175

1uF_6.3V

1uF_6.3V

C186

C186

1uF_6.3V

1uF_6.3V

B69

B69

C63

C63

10uF_X6S

10uF_X6S

MC933

MC933

4.7uF_6.3V

4.7uF_6.3V

C183

C183

10uF_X6S

10uF_X6S

MC183

MC183

4.7uF_6.3V

4.7uF_6.3V

2

B930

B930

BLM15BD121SN1

BLM15BD121SN1

NS18 NS_VIANS18 NS_VIA

GND_PCIE_PVSS

C923

C923

1uF_6.3V

1uF_6.3V

C904

C904

100nF_6.3V

100nF_6.3V

C166

C166

1uF_6.3V

1uF_6.3V

C176

C176

1uF_6.3V

1uF_6.3V

C944

C944

1uF_6.3V

1uF_6.3V

+1.8V

MC67

MC67

4.7uF_6.3V

4.7uF_6.3V

MC63

MC63

4.7uF_6.3V

4.7uF_6.3V

+PCIE_VDDC

C924

C924

1uF_6.3V

1uF_6.3V

C905

C905

1uF_6.3V

1uF_6.3V

C167

C167

1uF_6.3V

1uF_6.3V

C177

C177

1uF_6.3V

1uF_6.3V

C187

C187

10uF_X6S

10uF_X6S

MC187

MC187

4.7uF_6.3V

4.7uF_6.3V

NS64NS_VIA NS64NS_VIA

GND_MPVSS

+1.8V

12

C925

C925

1uF_6.3V

1uF_6.3V

C906

C906

1uF_6.3V

1uF_6.3V

C168

C168

1uF_6.3V

1uF_6.3V

C178

C178

1uF_6.3V

1uF_6.3V

C946

C946

C945

C945

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C188

C188

10uF_X6S

10uF_X6S

MC188

MC188

4.7uF_6.3V

4.7uF_6.3V

C74

C74

100nF_6.3V

100nF_6.3V

C73

C73

100nF_6.3V

100nF_6.3V

B67 60R_700mAB67 60R_700mA

12

+DPLL_VDDC

Overlap footprints

C926

C926

10uF_X6S

10uF_X6S

C907

C907

1uF_6.3V

1uF_6.3V

C169

C169

C170

C170

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C179

C179

C180

C180

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C947

C947

1uF_6.3V

1uF_6.3V

C189

C189

10uF_X6S

10uF_X6S

MC189

MC189

4.7uF_6.3V

4.7uF_6.3V

Overlap footprints

C75

C75

C77

C77

1uF_6.3V

1uF_6.3V

10uF_X6S

10uF_X6S

+VDDCI_2

C76

C76

1uF_6.3V

1uF_6.3V

+VDDC

Install only one of these two

MC926

MC926

4.7uF_6.3V

4.7uF_6.3V

+PCIE_VDDR

C941

C941

C942

C942

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C948

C948

1uF_6.3V

1uF_6.3V

MC77

MC77

4.7uF_6.3V

4.7uF_6.3V

Overlap footprints

C79

C79

10uF_X6S

10uF_X6S

B60

B60

BLM15BD121SN1

BLM15BD121SN1

MB60

MB60

BLM15BD121SN1

BLM15BD121SN1

1

B921 220R_2AB921 220R_2A

Share one pad

Install only one of these two

+1.8V

R9000RR900

0R

+VDDC

C943

C943

1uF_6.3V

1uF_6.3V

+VDDCI_1

MC79

MC79

4.7uF_6.3V

4.7uF_6.3V

R922

R922

1.5R

1.5R

R921

R921

0.1R

0.1R

R9200RR920

0R

B77 220R_2AB77 220R_2A

B78 220R_2AB78 220R_2A

+1.1V

+VDDC

+VDDC

+1.1V

+VDDC

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RV635 DDR2 - ASIC Power

RV635 DDR2 - ASIC Power

5

4

3

2

RV635 DDR2 - ASIC Power

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Wednesday, January 09, 2008

Wednesday, January 09, 2008

Wednesday, January 09, 2008

Sheet

Sheet

Sheet

of

421

of

421

of

421

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

2

2

2

105-B382xx-10

105-B382xx-10

105-B382xx-10

www.vinafix.vn

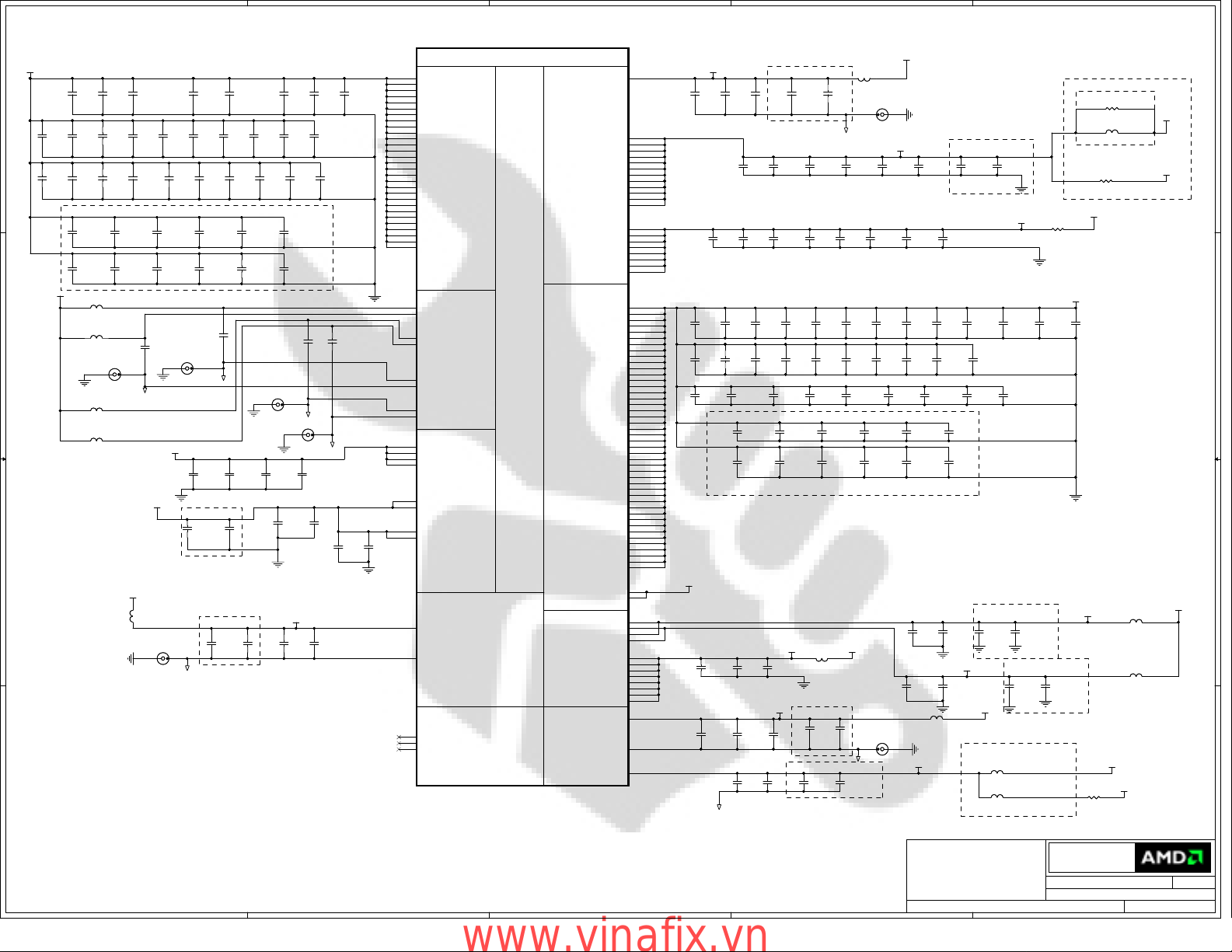

5

4

3

2

1

+MVDD

+MVDD

R291

R291

100R

100R

1%

R292

R292

100R

100R

1%

R293

R293

100R

100R

1%

R294

R294

100R

100R

1%

DQA_[63..0](8)

C291

C291

100nF

100nF

C293

C293

100nF

100nF

C292

C292

10nF

10nF

C294

C294

10nF

10nF

DQA_0

DQA_1

DQA_2

DQA_3

DQA_4

DQA_5

DQA_6

DQA_7

DQA_8

DQA_9

DQA_10

DQA_11

DQA_12

DQA_13

DQA_14

DQA_15

DQA_16

DQA_17

DQA_18

DQA_19

DQA_20

DQA_21

DQA_22

DQA_23

DQA_24

DQA_25

DQA_26

DQA_27

DQA_28

DQA_29

DQA_30

DQA_31

DQA_32

DQA_33

DQA_34

DQA_35

DQA_36

DQA_37

DQA_38

DQA_39

DQA_40

DQA_41

DQA_42

DQA_43

DQA_44

DQA_45

DQA_46

DQA_47

DQA_48

DQA_49

DQA_50

DQA_51

DQA_52

DQA_53

DQA_54

DQA_55

DQA_56

DQA_57

DQA_58

DQA_59

DQA_60

DQA_61

DQA_62

DQA_63

MVREFS_0

P27

P28

P31

P32

M27

K29

K31

K32

M33

M34

L34

L35

J33

J34

H33

H34

K27

J29

J30

J31

F29

F32

D30

D32

G33

G34

G35

F34

D34

C34

C35

B34

C24

B24

B23

A23

C21

B21

C20

B20

J22

H22

F22

D21

J19

G19

F19

D19

C19

B19

A19

B18

C16

B16

C15

A15

H18

F18

E18

D18

J17

G15

E15

D15

N35

N34

U1C

U1C

DQA_0

DQA_1

DQA_2

DQA_3

DQA_4

DQA_5

DQA_6

DQA_7

DQA_8

DQA_9

DQA_10

DQA_11

DQA_12

DQA_13

DQA_14

DQA_15

DQA_16

DQA_17

DQA_18

DQA_19

DQA_20

DQA_21

DQA_22

DQA_23

DQA_24

DQA_25

DQA_26

DQA_27

DQA_28

DQA_29

DQA_30

DQA_31

DQA_32

DQA_33

DQA_34

DQA_35

DQA_36

DQA_37

DQA_38

DQA_39

DQA_40

DQA_41

DQA_42

DQA_43

DQA_44

DQA_45

DQA_46

DQA_47

DQA_48

DQA_49

DQA_50

DQA_51

DQA_52

DQA_53

DQA_54

DQA_55

DQA_56

DQA_57

DQA_58

DQA_59

DQA_60

DQA_61

DQA_62

DQA_63

MVREFDA

MVREFSA

RV635 XT A11

RV635 XT A11

Part 3 of 7

Part 3 of 7

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

MAA_10

MAA_11

MAA_A12

MAA_BA0

MAA_BA1

MAA_BA2

DQMAB_0

DQMAB_1

DQMAB_2

DQMAB_3

DQMAB_4

DQMAB_5

DQMAB_6

MEMORY INTERFACE A

MEMORY INTERFACE A

DQMAB_7

DDR1 DDR2 DDR3

DDR1 DDR2 DDR3

Not used

Not used

bidir. strobe

bidir. strobe

bidir. differential strobe

bidir. differential strobe

For DDR2

For DDR2

write strobe

write strobe

read strobe

read strobe

QSA_0

QSA_1

QSA_2

QSA_3

QSA_4

QSA_5

QSA_6

QSA_7

QSA_0B

QSA_1B

QSA_2B

QSA_3B

QSA_4B

QSA_5B

QSA_6B

QSA_7B

ODTA0

ODTA1

CLKA0

CLKA0B

CKEA0

RASA0B

CASA0B

WEA0B

CSA0B_0

CSA0B_1

CLKA1

CLKA1B

CKEA1

RASA1B

CASA1B

WEA1B

CSA1B_0

CSA1B_1

DQB_[63..0](9)

MAA_0

C27

MAA_1

B28

MAA_2

B27

MAA_3

G26

MAA_4

F27

MAA_5

E27

MAA_6

D27

MAA_7

J27

MAA_8

E29

MAA_9

C30

MAA_10

E26

MAA_11

A27

MAA_12

G27

MAA_BA0

C28

MAA_BA1

B29

MAA_BA2

D26

DQMAb_0

M29

DQMAb_1

K33

DQMAb_2

G30

DQMAb_3

E33

DQMAb_4

C22

DQMAb_5

H21

DQMAb_6

C17

DQMAb_7

G17

QSA_0

M30

QSA_1

K34

QSA_2

G31

QSA_3

E34

QSA_4

B22

QSA_5

F21

QSA_6

B17

QSA_7

D17

M31

K35

G32

E35

A22

E21

A17

E17

C31

ODTA0 (8)

C25

A33

CLKA0 (8)

B33

CLKA0b (8)

B31

CKEA0 (8)

A31

RASA0b (8)

C32

CASA0b (8)

C29

WEA0b (8)

A30

CSA0b_0 (8)

B30

A26

CLKA1 (8)

B26

CLKA1b (8)

F24

CKEA1 (8)

D24

RASA1b (8)

H26

CASA1b (8)

D22

WEA1b (8)

G24

CSA1b_0 (8)

H24

MAA_[12..0] (8)

MAA_BA[2..0] (8)

DQMAb_[7..0] (8)

QSA_[7..0] (8)

+MVDD

+MVDD

R391

R391

100R

100R

1%

R392

R392

100R

100R

1%

R393

R393

100R

100R

1%

R394

R394

100R

100R

1%

C391

C391

100nF

100nF

C393

C393

100nF

100nF

C392

C392

10nF

10nF

C394

C394

10nF

10nF

MVREFD_1MVREFD_0

MVREFS_1

R296

R296

4.7K

4.7K

DQB_0

DQB_1

DQB_2

DQB_3

DQB_4

DQB_5

DQB_6

DQB_7

DQB_8

DQB_9

DQB_10

DQB_11

DQB_12

DQB_13

DQB_14

DQB_15

DQB_16

DQB_17

DQB_18

DQB_19

DQB_20

DQB_21

DQB_22

DQB_23

DQB_24

DQB_25

DQB_26

DQB_27

DQB_28

DQB_29

DQB_30

DQB_31

DQB_32

DQB_33

DQB_34

DQB_35

DQB_36

DQB_37

DQB_38

DQB_39

DQB_40

DQB_41

DQB_42

DQB_43

DQB_44

DQB_45

DQB_46

DQB_47

DQB_48

DQB_49

DQB_50

DQB_51

DQB_52

DQB_53

DQB_54

DQB_55

DQB_56

DQB_57

DQB_58

DQB_59

DQB_60

DQB_61

DQB_62

DQB_63

R297

R297

4.7K

4.7K

R298

R298

243R

243R

H15

G14

E14

D14

H12

G12

F12

D10

B13

C12

B12

B11

C9

B9

A9

B8

J10

H10

F10

D9

G7

G6

F6

D6

C8

C7

B7

A7

B5

A5

C4

B4

M3

M2

N2

N1

R3

R2

T3

T2

M8

M7

P5

P4

R9

R8

R6

U4

U3

U2

U1

V2

Y3

Y2

AA2

AA1

U9

U7

U6

V4

W9

W7

W6

W4

B14

A13

AA4

AA8

AA7

AA5

U1D

U1D

DQB_0

DQB_1

DQB_2

DQB_3

DQB_4

DQB_5

DQB_6

DQB_7

DQB_8

DQB_9

DQB_10

DQB_11

DQB_12

DQB_13

DQB_14

DQB_15

DQB_16

DQB_17

DQB_18

DQB_19

DQB_20

DQB_21

DQB_22

DQB_23

DQB_24

DQB_25

DQB_26

DQB_27

DQB_28

DQB_29

DQB_30

DQB_31

DQB_32

DQB_33

DQB_34

DQB_35

DQB_36

DQB_37

DQB_38

DQB_39

DQB_40

DQB_41

DQB_42

DQB_43

DQB_44

DQB_45

DQB_46

DQB_47

DQB_48

DQB_49

DQB_50

DQB_51

DQB_52

DQB_53

DQB_54

DQB_55

DQB_56

DQB_57

DQB_58

DQB_59

DQB_60

DQB_61

DQB_62

DQB_63

MVREFDB

MVREFSB

DRAM_RST

TEST_MCLK

TEST_YCLK

MEMTEST

RV635 XT A11

RV635 XT A11

Part 4 of 7

Part 4 of 7

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

MAB_10

MAB_11

MAB_A12

MAB_BA0

MAB_BA1

MAB_BA2

DQMBB_0

DQMBB_1

DQMBB_2

DQMBB_3

DQMBB_4

DQMBB_5

DQMBB_6

MEMORY INTERFACE B

MEMORY INTERFACE B

DQMBB_7

DDR1 DDR2 DDR3

DDR1 DDR2 DDR3

Not used

Not used

bidir. strobe

bidir. strobe

bidir. differential strobe

bidir. differential strobe

For DDR2

For DDR2

write strobe

write strobe

read strobe

read strobe

QSB_0

QSB_1

QSB_2

QSB_3

QSB_4

QSB_5

QSB_6

QSB_7

QSB_0B

QSB_1B

QSB_2B

QSB_3B

QSB_4B

QSB_5B

QSB_6B

QSB_7B

ODTB0

ODTB1

CLKB0

CLKB0B

CKEB0

RASB0B

CASB0B

WEB0B

CSB0B_0

CSB0B_1

CLKB1

CLKB1B

CKEB1

RASB1B

CASB1B

WEB1B

CSB1B_0

CSB1B_1

MAB_0

H2

MAB_1

H3

MAB_2

J3

MAB_3

J5

MAB_4

J4

MAB_5

J6

MAB_6

G5

MAB_7

J9

MAB_8

F3

MAB_9

F4

MAB_10

J1

MAB_11

J2

MAB_12

J7

MAB_BA0

G2

MAB_BA1

G3

MAB_BA2

F1

DQMBb_0

D12

DQMBb_1

C10

DQMBb_2

E7

DQMBb_3

C6

DQMBb_4

P3

DQMBb_5

R4

DQMBb_6

W3

DQMBb_7

V8

QSB_0

J14

QSB_1

B10

QSB_2

F9

QSB_3

B6

QSB_4

P2

QSB_5

P8

QSB_6

W2

QSB_7

V6

H14

A10

E9

A6

P1

P7

W1

V5

D2

ODTB0 (9)

K5

A3

CLKB0 (9)

B3

CLKB0b (9)

E3

CKEB0 (9)

D3

RASB0b (9)

C1

CASB0b (9)

F2

WEB0b (9)

E1

CSB0b_0 (9)

E2

K1

CLKB1 (9)

K2

CLKB1b (9)

K8

CKEB1 (9)

K7

RASB1b (9)

K4

CASB1b (9)

M6

WEB1b (9)

L3

CSB1b_0 (9)

M4

MAB_[12..0] (9)

MAB_BA[2..0] (9)

DQMBb_[7..0] (9)

QSB_[7..0] (9)

D D

C C

B B

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RV635 DDR2 - ASIC Memory Interface (Channel A & B)

RV635 DDR2 - ASIC Memory Interface (Channel A & B)

5

4

3

2

RV635 DDR2 - ASIC Memory Interface (Channel A & B)

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Wednesday, January 09, 2008

Wednesday, January 09, 2008

Wednesday, January 09, 2008

Sheet

Sheet

Sheet

of

521

of

521

of

521

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

2

2

2

105-B382xx-10

105-B382xx-10

105-B382xx-10

www.vinafix.vn

Loading...

Loading...