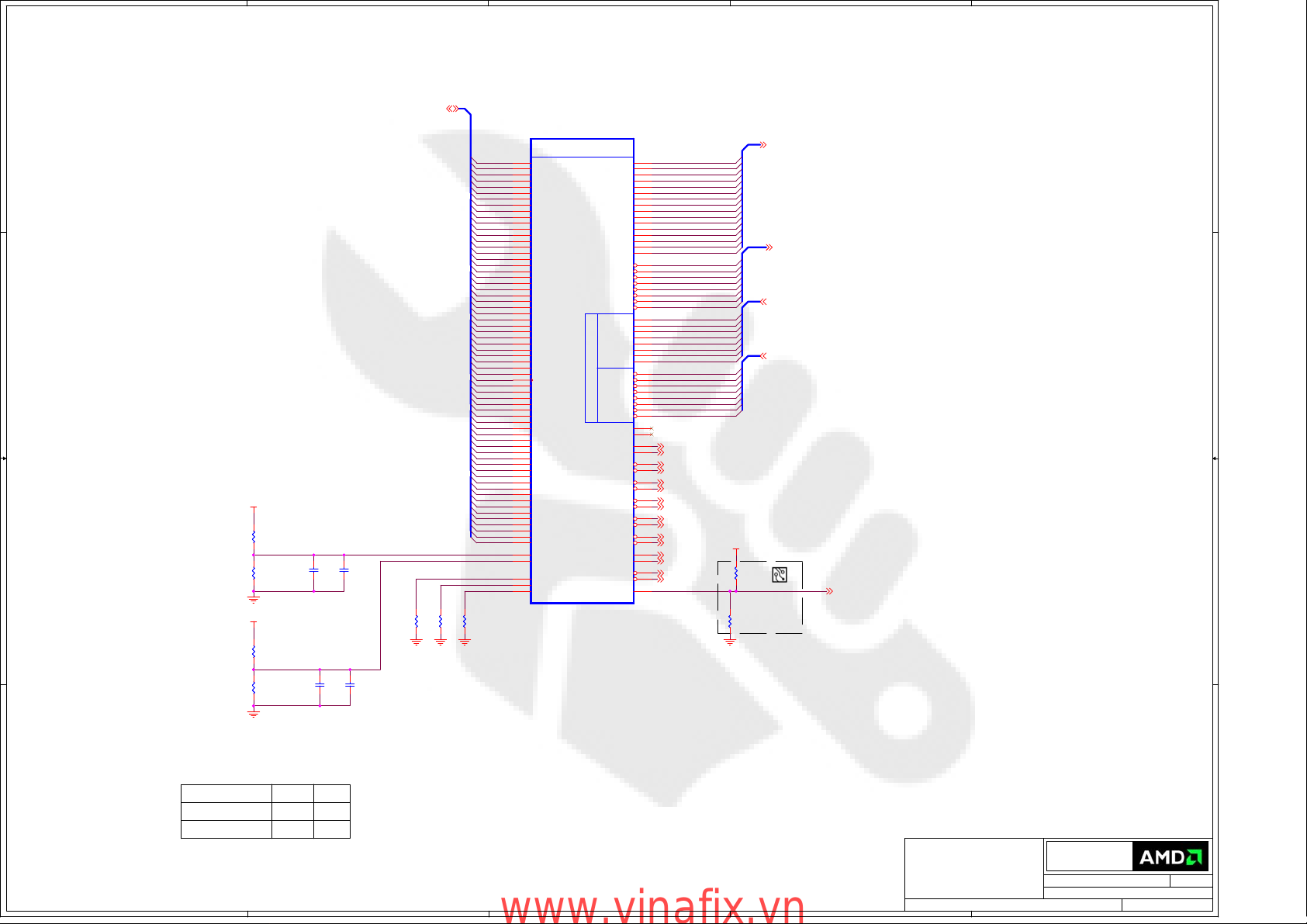

MSI MS-V128 Schematic

8

7

6

5

4

3

2

1

D D

R1 0RR1 0R

No JTAG

PETn0_GFXRn0<2>

PETp1_GFXRp1<2>

PETn1_GFXRn1<2>

PETp2_GFXRp2<2>

C C

+12V_BUS

C1

MC1

MC1

470uF

470uF

B B

+3.3V

+3.3V

10UFC110UF

C2

150nF_16VC2150nF_16V

C4

470uFC4470uF

C5

1uF_6.3VC51uF_6.3V

CAP CER 10UF 20% 16V X5R

(1206)1.8MM H MAX

+12V_BUS+12V_BUS

C3

C3

150nF_16V

150nF_16V

LF CAP CER 150NF 10% 16V X7R (0603)

LF CAP CER 150NF 10% 16V X7R (0603)

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

C6

1uF_6.3VC61uF_6.3V

PETn2_GFXRn2<2>

PETp3_GFXRp3<2>

PETn3_GFXRn3<2>

PETp4_GFXRp4<2>

PETn4_GFXRn4<2>

PETp5_GFXRp5<2>

PETn5_GFXRn5<2>

PETp6_GFXRp6<2>

PETn6_GFXRn6<2>

PETp7_GFXRp7<2>

PETn7_GFXRn7<2>

PETp8_GFXRp8<2>

PETn8_GFXRn8<2>

PETp9_GFXRp9<2>

PETn9_GFXRn9<2>

PETp10_GFXRp10<2>

PETn10_GFXRn10<2>

PETp11_GFXRp11<2>

PETn11_GFXRn11<2>

PETp12_GFXRp12<2>

PETn12_GFXRn12<2>

PETp13_GFXRp13<2>

PETn13_GFXRn13<2>

PETp14_GFXRp14<2>

PETn14_GFXRn14<2>

PETp15_GFXRp15<2>

PETn15_GFXRn15<2>

PRESENCE

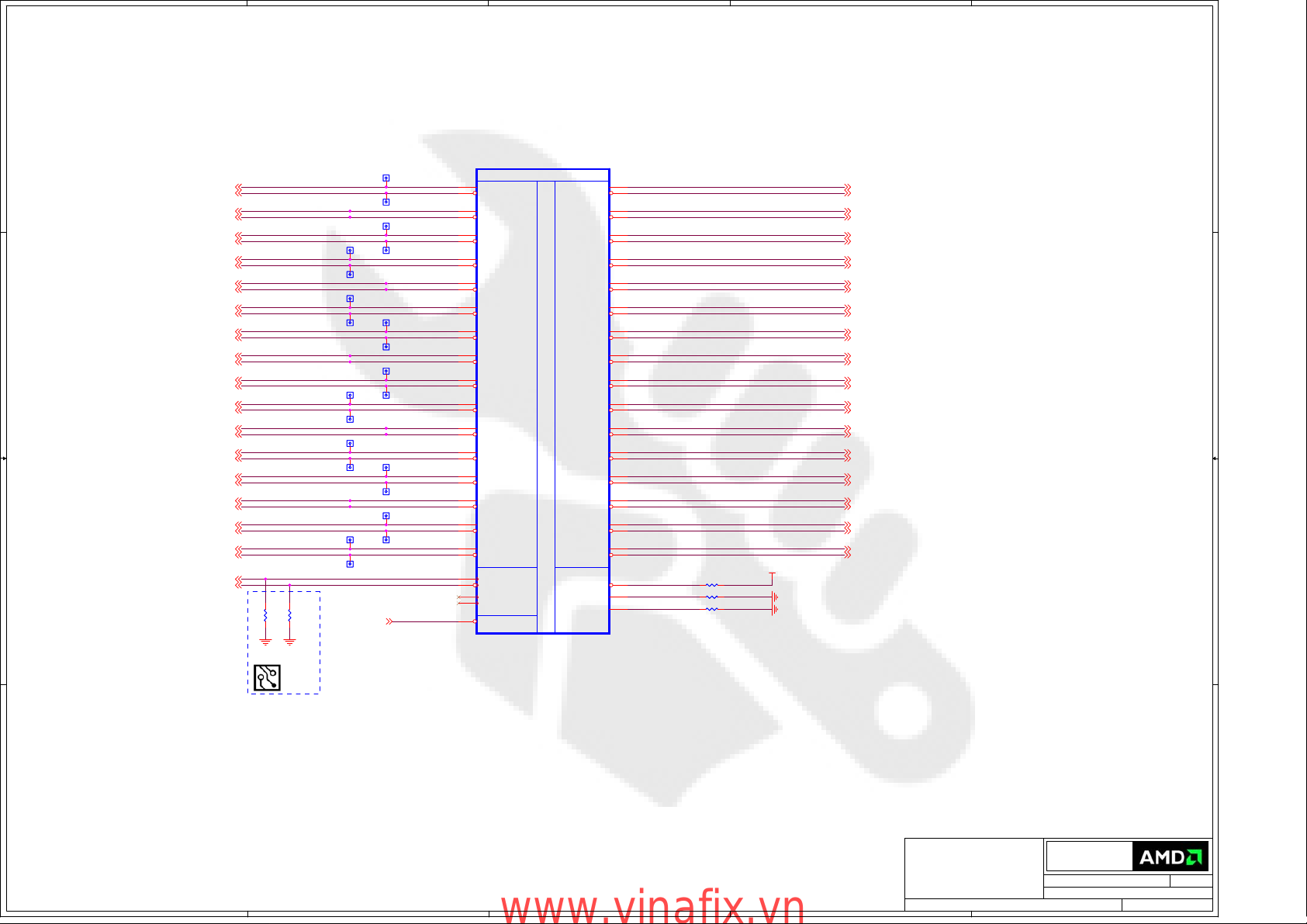

PCI-EXPRESS EDGE CONNECTOR

+3.3V_BUS

JTESTEN

+12V_BUS

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

+12V#B1

+12V#B2

+12V#B3

GND#B4

SMCLK

SMDAT

GND#B7

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

Mechanical Key

Mechanical Key

x16 PCIe

x16 PCIe

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

JTAG2

JTAG3

JTAG4

JTAG5

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLKGND#A15

PERp0

PERn0

GND#A18

RSVD#A19

GND#A20

PERp1

PERn1

GND#A23

GND#A24

PERp2

PERn2

GND#A27

GND#A28

PERp3

PERn3

GND#A31

RSVD#A32

RSVD#A33

GND#A34

PERp4

PERn4

GND#A37

GND#A38

PERp5

PERn5

GND#A41

GND#A42

PERp6

PERn6

GND#A45

GND#A46

PERp7

PERn7

GND#A49

RSVD#A50

GND#A51

PERp8

PERn8

GND#A54

GND#A55

PERp9

PERn9

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

MPCIE1

MPCIE1

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

+3.3V_BUS+12V_BUS

PRESENCE

C7

100nFC7100nF

C9

100nFC9100nF

C11

C11

100nF

100nF

C13

C13

100nF

100nF

C15

C15

100nF

100nF

C17

C17

100nF

100nF

C19

C19

100nF

100nF

C21

C21

100nF

100nF

C23

C23

100nF

100nF

C25

C25

100nF

100nF

C27

C27

100nF

100nF

C29

C29

100nF

100nF

C31

C31

100nF

100nF

C33

C33

100nF

100nF

C35

C35

100nF

100nF

C37

C37

100nF

100nF

C8

100nFC8100nF

C10

C10

100nF

100nF

C12

C12

100nF

100nF

C14

C14

100nF

100nF

C16

C16

100nF

100nF

C18

C18

100nF

100nF

C20

C20

100nF

100nF

C22

C22

100nF

100nF

C24

C24

100nF

100nF

C26

C26

100nF

100nF

C28

C28

100nF

100nF

C30

C30

100nF

100nF

C32

C32

100nF

100nF

C34

C34

100nF

100nF

C36

C36

100nF

100nF

C38

C38

100nF

100nF

JTDI

JTDO

PCIE_REFCLKP <2>

PCIE_REFCLKN <2>PETp0_GFXRp0<2>

GFXTp0_PERp0 <2>

GFXTn0_PERn0 <2>

GFXTp1_PERp1 <2>

GFXTn1_PERn1 <2>

GFXTp2_PERp2 <2>

GFXTn2_PERn2 <2>

GFXTp3_PERp3 <2>

GFXTn3_PERn3 <2>

GFXTp4_PERp4 <2>

GFXTn4_PERn4 <2>

GFXTp5_PERp5 <2>

GFXTn5_PERn5 <2>

GFXTp6_PERp6 <2>

GFXTn6_PERn6 <2>

GFXTp7_PERp7 <2>

GFXTn7_PERn7 <2>

GFXTp8_PERp8 <2>

GFXTn8_PERn8 <2>

GFXTp9_PERp9 <2>

GFXTn9_PERn9 <2>

GFXTp10_PERp10 <2>

GFXTn10_PERn10 <2>

GFXTp11_PERp11 <2>

GFXTn11_PERn11 <2>

GFXTp12_PERp12 <2>

GFXTn12_PERn12 <2>

GFXTp13_PERp13 <2>

GFXTn13_PERn13 <2>

GFXTp14_PERp14 <2>

GFXTn14_PERn14 <2>

GFXTp15_PERp15 <2>

GFXTn15_PERn15 <2>

JTDI

JTDO

No JTAG

R2 0RR2 0R

PERST#

+3.3V

C39

C39

100nF

100nF

53

1

4

2

U5

U5

NC7SZ08P5X_NL

NC7SZ08P5X_NL

PERST#_buf <2>

Table 1: Connection for JTAG

Production

(No JTAG)

Internal Use Only

TSW1, R1 & R2 are located on the bottom side of the board close to PCIE connector.

Install R1, R2 & Don't Install TSW1

Install TSW1 & Don't Install R1 or R2

TSW1 Switch #1, 2, 3, 4, 5 and 6 closed (ON)

JTAG

#8 AND #7 open

TSW1 Switch #1, 2, 3, 4, 5 and 6 open

NO JTAG

#8 & #7 closed (ON)

Place these caps last,

ideally as close to the bus

connector as possible

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

?2007 Advanced Micro Devices

?2007 Advanced Micro Devices

?2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH RV620 - PCI-E Edge Connector

RH RV620 - PCI-E Edge Connector

8

7

6

5

www.vinafix.vn

4

3

RH RV620 - PCI-E Edge Connector

2

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Thursday, March 20, 2008

Thursday, March 20, 2008

Thursday, March 20, 2008

Sheet

Sheet

Sheet

of

121

of

121

of

121

SYMBOL LEGEND

DNI

#

Doc No.

Doc No.

Doc No.

105-B408xx-00C

105-B408xx-00C

105-B408xx-00C

1

DO NOT

INSTALL

ACTIVE

LOW

DIGITAL

GROUND

ANALOG

GROUND

RevDate:

RevDate:

RevDate:

12

12

12

5

D D

4

3

2

1

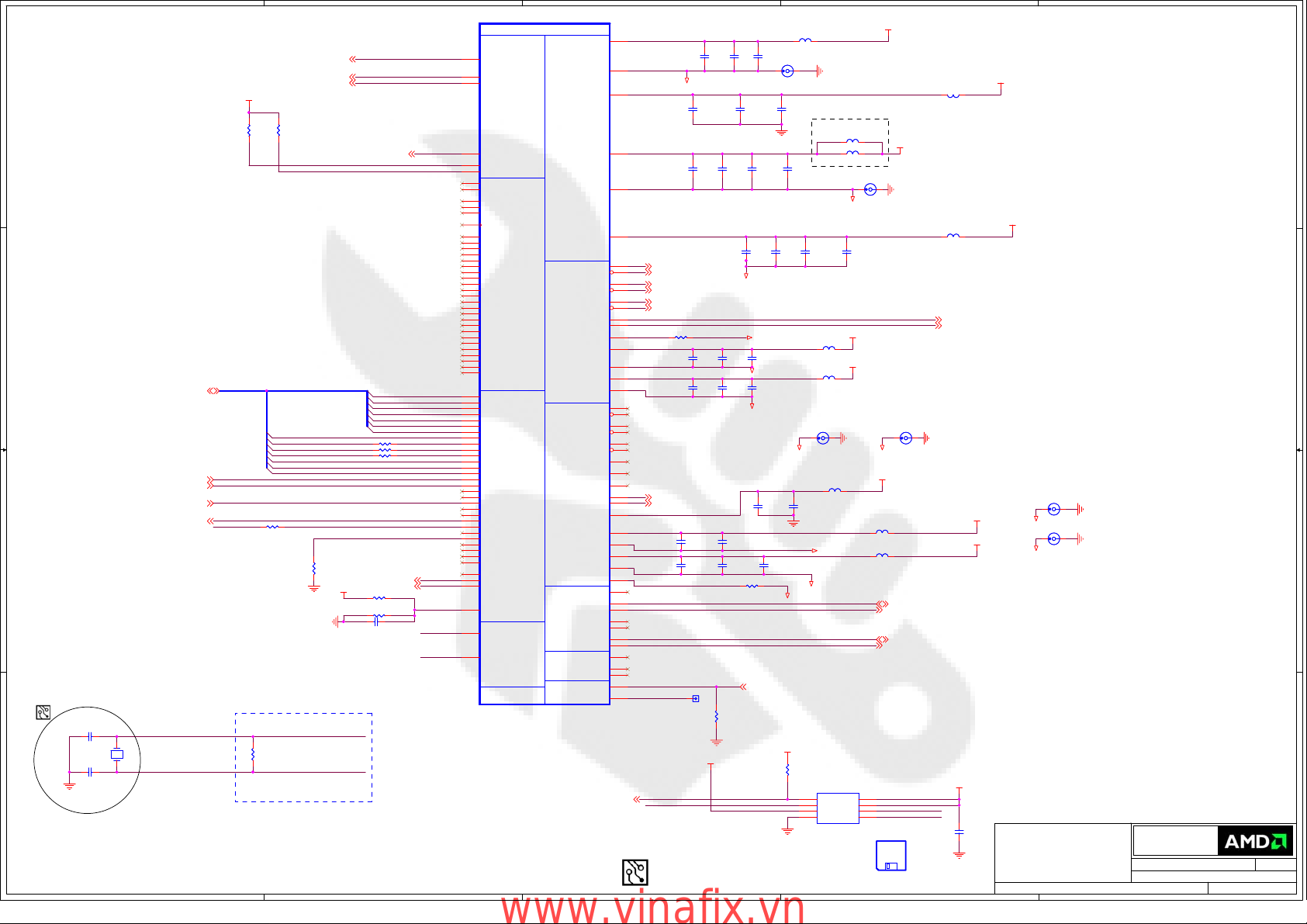

NOTE: some of the PCIE testpoints will

be available through via on traces.

PETp0_GFXRp0<1>

PETn0_GFXRn0<1>

PETp1_GFXRp1<1>

PETn1_GFXRn1<1>

PETp2_GFXRp2<1>

PETn2_GFXRn2<1>

PETp3_GFXRp3<1>

PETn3_GFXRn3<1>

PETp4_GFXRp4<1>

PETn4_GFXRn4<1>

PETp5_GFXRp5<1>

PETn5_GFXRn5<1>

PETp6_GFXRp6<1>

C C

B B

PETn6_GFXRn6<1>

PETp7_GFXRp7<1>

PETn7_GFXRn7<1>

PETp8_GFXRp8<1>

PETn8_GFXRn8<1>

PETp9_GFXRp9<1>

PETn9_GFXRn9<1>

PETp10_GFXRp10<1>

PETn10_GFXRn10<1>

PETp11_GFXRp11<1>

PETn11_GFXRn11<1>

PETp12_GFXRp12<1>

PETn12_GFXRn12<1>

PETp13_GFXRp13<1>

PETn13_GFXRn13<1>

PETp14_GFXRp14<1>

PETn14_GFXRn14<1>

PETp15_GFXRp15<1>

PETn15_GFXRn15<1>

PCIE_REFCLKP<1>

PCIE_REFCLKN<1>

DNI DNI

R13

R13

51R

51R

402 402

R14

R14

51R

51R

TP7TP7

TP8TP8

TP9TP9

TP10TP10

TP11TP11

TP12TP12

TP13TP13

TP14TP14

TP15TP15

TP16TP16

TP17TP17

TP19TP19

TP18TP18

TP20TP20

TP21TP21

TP23TP23TP22TP22

TP24TP24

TP25TP25

TP26TP26

TP27TP27

TP28TP28

PERST#_buf<1>

AC30

AC31

AC29

AB29

AB31

AB30

AA31

AA30

AD29

AD30

AC28

AC27

AG25

W30

W31

W29

V29

V31

V30

U31

U30

P30

P31

P29

N29

N31

N30

M31

M30

K30

K31

K29

J29

J31

J30

H31

H30

U1A

U1A

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

Clock

Clock

PCIE_REFCLKP

PCIE_REFCLKN

NC_SMBCLK

NC_SMBDATA

PERSTB

RV620 GL A11 RH

RV620 GL A11 RH

PART 1 OF 6

PART 1 OF 6

P

P

C

C

I

I

-

E

E

X

X

P

P

R

R

E

E

S

S

S

S

I

I

N

N

T

T

E

E

R

R

F

F

A

A

C

C

E

E

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

Calibration

Calibration

PCIE_CALRN

PCIE_CALRP

AA28

AA27

AA25

AA24

Y28

Y27

Y25

Y24

V28

V27

V25

V24

T28

T27

T25

T24

P28

P27

P25

P24

M28

M27

M25

M24

L28

L27

L25

L24

J28

J27

G28

G27

PCIE_CALRN

AF25

PCIE_CALRP

AE25

PCIE_CALI

AE23

NC

DNI

+1.1V

R82.0K R82.0K

R91.27K R91.27K

R1010K R1010K

GFXTp0_PERp0 <1>

GFXTn0_PERn0 <1>

GFXTp1_PERp1 <1>

GFXTn1_PERn1 <1>

GFXTp2_PERp2 <1>

GFXTn2_PERn2 <1>

GFXTp3_PERp3 <1>

GFXTn3_PERn3 <1>

GFXTp4_PERp4 <1>

GFXTn4_PERn4 <1>

GFXTp5_PERp5 <1>

GFXTn5_PERn5 <1>

GFXTp6_PERp6 <1>

GFXTn6_PERn6 <1>

GFXTp7_PERp7 <1>

GFXTn7_PERn7 <1>

GFXTp8_PERp8 <1>

GFXTn8_PERn8 <1>

GFXTp9_PERp9 <1>

GFXTn9_PERn9 <1>

GFXTp10_PERp10 <1>

GFXTn10_PERn10 <1>

GFXTp11_PERp11 <1>

GFXTn11_PERn11 <1>

GFXTp12_PERp12 <1>

GFXTn12_PERn12 <1>

GFXTp13_PERp13 <1>

GFXTn13_PERn13 <1>

GFXTp14_PERp14 <1>

GFXTn14_PERn14 <1>

GFXTp15_PERp15 <1>

GFXTn15_PERn15 <1>

For Tektronix LA only

Place close

to ASIC

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

?2007 Advanced Micro Devices

?2007 Advanced Micro Devices

?2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH RV610 - ASIC PCIE Interface

RH RV610 - ASIC PCIE Interface

5

4

www.vinafix.vn

3

2

RH RV610 - ASIC PCIE Interface

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Thursday, March 20, 2008

Thursday, March 20, 2008

Thursday, March 20, 2008

Sheet

Sheet

Sheet

of

221

of

221

of

221

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

12

12

12

105-B408xx-00C

105-B408xx-00C

105-B408xx-00C

5

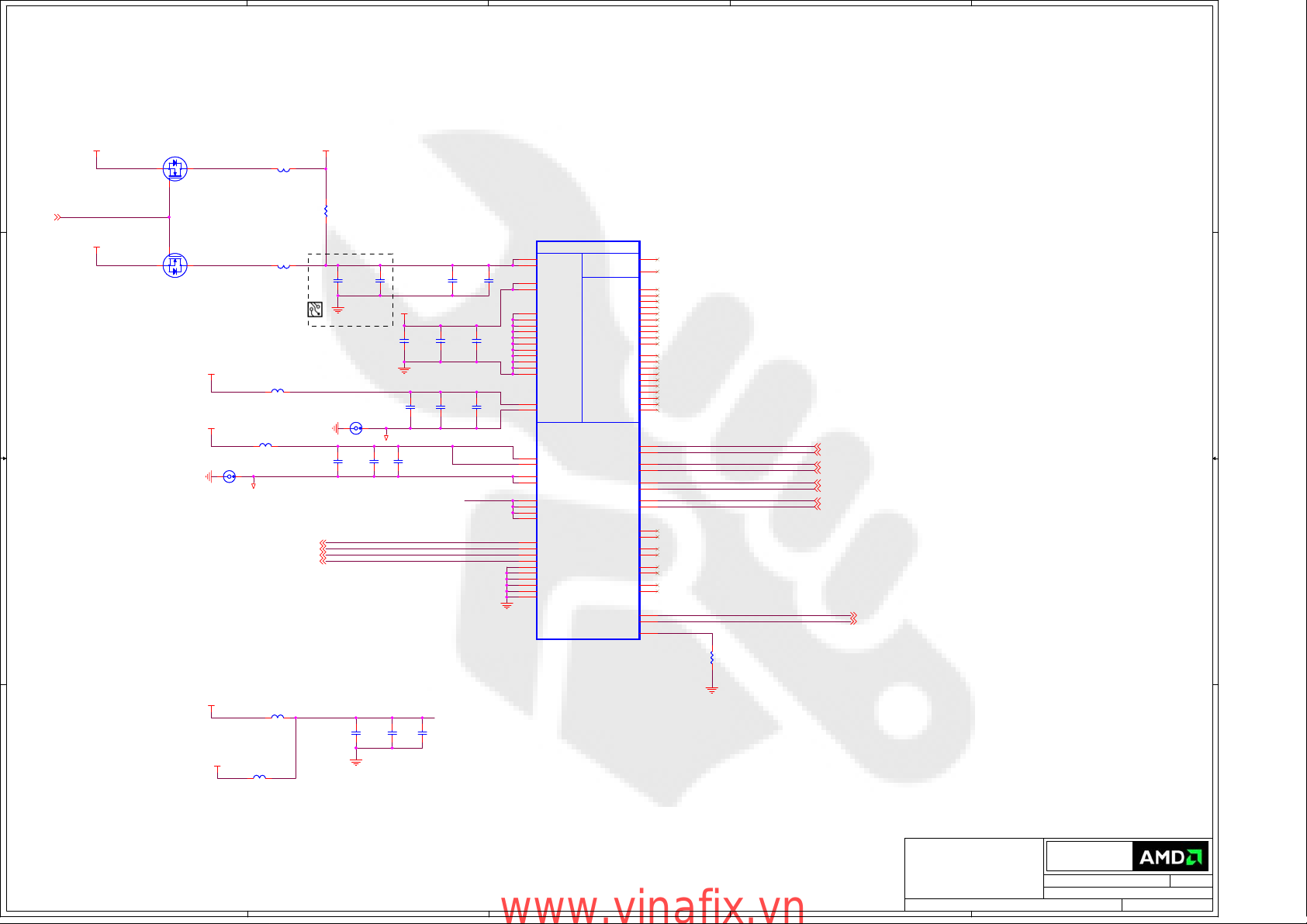

RV610: DNI TR16

RV620: TR16 TO CONNECT LEGACY TDO CONNECTION

PSYNC<13>

VID_6<13>

VID_7<13>

+3.3V

D D

C C

R47

R47

R48

R48

4.7K

4.7K

4.7K

4.7K

GPIO_[13..0]<13>

FLOW_CONTROL_1 - Lower Cable

FLOW_CONTROL_2 - Upper Cable

SWAP_LOCK_1 - Lower Cable

SWAP_LOCK_2 - Upper Cable

GPIO_8

GPIO_9

GPIO_10

GPIO14_HPD2<15>

GPIO_16 IS OUT ONLY

B B

PWRCNTL_0<13>

GPIO_18<13>

GPIO21_BB_EN<13>

GPIO_22_DBG

R33 33RR33 33R

MR51KMR5

1K

+1.8V_D2

R_RTCLK

EC82 20PFEC82 20PF

EY82

EY82

27_MHZ

27_MHZ

2 1

EC83 20PFEC83 20PF

A A

Change to 10ppm/10ppm p/n 5028270000G

5

R84

R84

1.0M

1.0M

Place R_RTCLK close to XTAL so the

main clock line has shortest stub

XTALIN

XTALOUT

4

DVALID<13>

R30 33RR30 33R

R31 33RR31 33R

R32 33RR32 33R

GENERICB<13>

GENERICC<13>

R43 221RR43 221R

R44 110RR44 110R

C46 100nFC46 100nF

4

PSYNC

VID_7

DVALID

N53817339

N53817336

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO8_SO

GPIO9_SI

GPIO10_SCK

GPIO_11

GPIO_12

GPIO_13

HPD2

PWRCNTL_0

GPIO_18

GPIO21_BB_EN

GPIO22_CS

JTAG_MODE

GENERICB

GENERICC

VREFG

XTALIN

XTALOUT

U1B

U1B

AE7

PSYNC_NEW

AH6

GEN_D_HPD4

AG6

GEN_E

AD9

DVALID

AA4

SDA

AA5

SCL

AK4

DVPCNTL_MVP_0

AL3

DVPCNTL_MVP_1

V2

DVPCNTL_0

V1

DVPCNTL_1

W3

DVPCNTL_2

W1

DVPCLK

Y1

DVPDATA_0

Y2

DVPDATA_1

Y3

DVPDATA_2

AA2

DVPDATA_3

AA3

DVPDATA_4

AB1

DVPDATA_5

AB2

DVPDATA_6

AB3

DVPDATA_7

AC1

DVPDATA_8

AC3

DVPDATA_9

AD1

DVPDATA_10

AD2

DVPDATA_11

AD3

DVPDATA_12

AF3

DVPDATA_13

AG3

DVPDATA_14

AH3

DVPDATA_15

AG1

DVPDATA_16

AH2

DVPDATA_17

AH1

DVPDATA_18

AJ3

DVPDATA_19

AJ1

DVPDATA_20

AJ2

DVPDATA_21

AK2

DVPDATA_22

AK3

DVPDATA_23

Y4

GPIO_0

V3

GPIO_1

V4

GPIO_2

V5

GPIO_3

U3

GPIO_4

U2

GPIO_5

T4

GPIO_6

T5

GPIO_7_BLON

T7

GPIO_8_ROMSO

T8

GPIO_9_ROMSI

R1

GPIO_10_ROMSCK

R2

GPIO_11

R3

GPIO_12

P1

GPIO_13

P3

GPIO_14_HPD2

N1

GPIO_15_PWRCNTL0

N2

GPIO_16_SSIN

P4

GPIO_17_THERMAL_INT

P7

GPIO_18_HPD3

P8

GPIO_19_CTFB

P5

GPIO_20_PWRCNTL1

V7

GPIO_21_BB_EN

N3

GPIO_22_ROMCSB

Y5

GPIO_23_CLKREQB

M4

GPIO_24_JMODE

M5

GPIO_25_TDI

M7

GPIO_26_TCK

M8

GPIO_27_TMS

L8

GPIO_28_TDO

Y8

GENERICA

Y7

GENERICB

V8

GENERICC

AC11

VREFG

AJ31

XTALIN

AJ30

XTALOUT

RV620 GL A11 RH

RV620 GL A11 RH

MISC/I2C

MISC/I2C

General

General

Purpose

Purpose

I/O

I/O

XTAL

XTAL

External

External

TMDS

TMDS

PART 2 OF 6

PART 2 OF 6

PLL Power

PLL Power

DAC / CRT

DAC / CRT

DAC2 (TV/CRT2)

DAC2 (TV/CRT2)

Monitor

Monitor

Interface

Interface

DDC3DATA_DP3_AUXN

DDC3CLK_DP3_AUXP

Thermal

Thermal

Test

Test

3

+DPLL_PVDD

AH12

DPLL_PVDD

GND_PVSS

AG12

DPLL_PVSS

+PCIE_PVDD

AH31

PCIE_PVDD

1uF_6.3V

1uF_6.3V

+MPVDD

A9

MPVDD

GND_MPVSS

B9

MPVSS

+DPLL_VDDC

AE12

DPLL_VDDC

AL28

A_R_DAC1 <14>

AK28

A_RB_DAC1 <14>

AL27

A_G_DAC1 <14>

AK27

A_GB_DAC1 <14>

AL26

A_B_DAC1 <14>

AK26

A_BB_DAC1 <14>

AK29

AK30

RSET

+AVDD

GND_AVSSQ

+VDD1DI

GND_VSS1DI

A_VSYNC_DAC2 <13>

A_HSYNC_DAC2 <13>

+A2VDD

+A2VDDQ

GND_A2VSSQ

+VDD2DI

GND_VSS2DI

R2SET

PLL_TEST

R1030 499RR1030 499R

AJ28

AL29

AH28

AJ27

AJ26

AL17

AK17

AL15

AK15

AL14

AK14

AJ17

AJ15

AJ14

AE16

AF16

AH14

AH16

AG16

AF18

AE18

AG14

AA8

AJ29

AH29

AC5

AC4

AF4

AH4

AE14

AE5

AE4

AH26

AD12

GPIO_8

PLACE TR46, TR58, TR59, TR60 SUCH THAT STUBS ARE NOT

CREATED ON THE MAIN FUNCTIONAL LINES;

3

HSYNC

VSYNC

RSET

AVDD

AVSSQ

VDD1DI

VSS1DI

COMP

V2SYNC

H2SYNC

A2VDD

A2VDDQ

A2VSSQ

VDD2DI

VSS2DI

R2SET

HPD1

DDC1DATA

DDC1CLK

DDC2DATA

DDC2CLK

TS_FDO

DPLUS

DMINUS

TESTEN

PLLTEST

GPIO_22_DBG<13>

R

RB

G

GB

B

BB

R2

R2B

G2

G2B

B2

B2B

C

Y

C72

C72

10uF_X6S

10uF_X6S

GND_PVSS

C933

C933

C2021

C2021

100nF

100nF

C2024

C2024

10nF

10nF

TP42TP42

C84

C84

10nF

10nF

C1020

C1020

10nF

10nF

C1023

C1023

10nF

10nF

+DPLL_PVDD

C71

C71

100nF

100nF

C932

C932

10uF_X6S

10uF_X6S

+3.3V

C70

C70

10nF

10nF

C85

C85

100nF

100nF

GND_PVSS

C1021

C1021

100nF

100nF

C1024

C1024

100nF

100nF

C2022

C2022

1uF_6.3V

1uF_6.3V

C2025

C2025

100nF

100nF

R2030 715RR2030 715R

MR71KMR7

1K

C931

C931

100nF

100nF

C86

C86

1uF_6.3V

1uF_6.3V

C60

C60

10nF

10nF

GND_AVSSQ

C1022

C1022

1uF_6.3V

1uF_6.3V

GND_AVSSQ

C1025

C1025

1uF_6.3V

1uF_6.3V

GND_VSS1DI

C2032

C2032

1uF_6.3V

1uF_6.3V

C2026

C2026

1uF_6.3V

1uF_6.3V

TESTEN

B886

B886

C61

C61

100nF

100nF

+3.3V

NS70NS_VIA NS70NS_VIA

C76

C76

10uF_X6S

10uF_X6S

GND_A2VSSQ

BLM15BD121SN1

BLM15BD121SN1

12

B882

B882

B884

B884

BLM15BD121SN1

BLM15BD121SN1

NS1021 NS_VIANS1021 NS_VIA

GND_VSS1DI

C2031

C2031

100nF

100nF

R46

R46

10K

10K

MB67220R_2A MB67220R_2A

B6760R B6760R

OVERLAP

NS64NS_VIA NS64NS_VIA

GND_MPVSS

C63

C63

C62

C62

10uF_X6S

10uF_X6S

1uF_6.3V

1uF_6.3V

+1.8V_D2

BLM15BD121SN1

BLM15BD121SN1

+1.8V_D2

12

B2030 120R_300mAB2030 120R_300mA

Possible alternate 5150005600G

B883

B883

BLM15BD121SN1

BLM15BD121SN1

GND_A2VSSQ

GND_VSS2DI

U2

U2

1

2

3

PM25LV512A-100SCE

PM25LV512A-100SCE

CE#

SO

HOLD#

WP#

GND4SI

VIDEO BIOS

FIRMWARE

B885

B885

8

VCC

7

6

SCK

5

2

+1.8V_D2

+VDDC

12

NS1020 NS_VIANS1020 NS_VIA

12

GND_AVSSQ

+3.3V

BLM15BD121SN1

BLM15BD121SN1

CRT1DDCDATA <14>

CRT1DDCCLK <14>

DDC3_DATA_DP3_AUXN <15>

DDC3_CLK_DP3_AUXP <15>

GPIO_10ROM_WP

GPIO_9

BIOS1

BIOS1

BIOS

BIOS

113-XXXXXX-XXX

113-XXXXXX-XXX

2

+1.8V_D2

B931

B931

BLM15BD121SN1

BLM15BD121SN1

B60

B60

BLM15BD121SN1

BLM15BD121SN1

A_HSYNC_DAC1 <13,14>

A_VSYNC_DAC1 <13,14>

+1.8V_D2

+3.3V

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

?2007 Advanced Micro Devices

?2007 Advanced Micro Devices

?2007 Advanced Micro Devices

C47

C47

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

100nF

100nF

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

+1.1V

NS2020 NS_VIANS2020 NS_VIA

12

GND_A2VSSQ+1.8V_D2

NS2021 NS_VIANS2021 NS_VIA

12

GND_VSS2DI

RH RV620 - ASIC Main

RH RV620 - ASIC Main

RH RV620 - ASIC Main

1

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Thursday, March 20, 2008

Thursday, March 20, 2008

Thursday, March 20, 2008

Sheet

Sheet

Sheet

of

321

of

321

of

321

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

12

12

12

105-B408xx-00C

105-B408xx-00C

105-B408xx-00C

www.vinafix.vn

5

D D

+1.8V_D2

SI2304DS

SI2304DS

1

Q100

Q100

LTVDD18_IN

B100

32

B100

BLM15BD121SN1

BLM15BD121SN1

+LTVDD18

LVT_EN<9>

SI2304DS

+3.3V_BUS

SI2304DS

1

Q101

Q101

LTVDD33_IN

32

B101

B101

BLM15BD121SN1

BLM15BD121SN1

MC118

MC118

4.7uF_6.3V

4.7uF_6.3V

OVERLAP C119 & C118

C C

+1.8V_D2

+1.8V_D2

1 2

GND_TPVSS

B B

NS110NS_VIA NS110NS_VIA

B889

B889

BLM15BD121SN1

BLM15BD121SN1

B887

B887

BLM15BD121SN1

BLM15BD121SN1

DPAVSS-VID5<13>

DPAVSS-VID4<13>

DPVSS-VID0<13>

DPAVSS-VID3<13>

C115

C115

10uF_X6S

10uF_X6S

4

R1180RR118

RV610: DNI R118

0R

RV620: INSTALL R118; DNI B101, Q101, C103, C108, C109

+T2XVDDR

C106

C118

C118

10uF_X6S

10uF_X6S

C106

1uF_6.3V

1uF_6.3V

+LTVDD18

C103

C103

C108

C108

1uF_6.3V

1uF_6.3V

10uF_X6S

10uF_X6S

+T2PVDD

C102

C102

C101

C101

10uF_X6S

10uF_X6S

100nF

C110

C110

100nF

100nF

100nF

GND_T2PVSS

1 2

C116

C116

1uF_6.3V

1uF_6.3V

NS100NS_VIA NS100NS_VIA

C109

C109

C100

C100

1uF_6.3V

1uF_6.3V

C105

C105

100nF

100nF

100nF

100nF

+DPAB_PVDD

GND_TPVSS

+DPAB_VDDR

DPAVSS-VID5

DPAVSS-VID4

DPVSS-VID0

DPAVSS-VID3

AF20

AG20

AJ18

AH20

AF23

AF21

AL18

AJ22

AJ25

AK18

AK23

AK25

AJ21

AL23

AL25

AG18

AH18

AE11

AF11

AJ12

AJ13

AK13

AL13

AG7

AH11

AL12

AJ11

AK12

AL7

AK7

AF7

AH7

AJ7

AJ8

AH9

U1F

U1F

PART 6 OF 6

PART 6 OF 6

T2XVDDR_1

T2XVDDR_2

T2XVDDC_1

T2XVDDC_2

T2XVSSR_1

T2XVSSR_2

T2XVSSR_3

T2XVSSR_4

T2XVSSR_5

T2XVSSR_6

T2XVSSR_7

T2XVSSR_8

T2XVSSR_9

T2XVSSR_10

T2XVSSR_11

T2PVDD

T2PVSS

Integrated TMDP

Integrated TMDP

DPA_PVDD

DPB_PVDD

DPA_PVSS

DPB_PVSS

DPA_VDDR_1

DPA_VDDR_2

DPB_VDDR_2

DPB_VDDR_1

DPA_VSSR_1

DPA_VSSR_2

DPA_VSSR_3

DPA_VSSR_4

DPA_VSSR_5

DPB_VSSR_1

DPB_VSSR_2

DPB_VSSR_3

DPB_VSSR_4

DPB_VSSR_5

RV620 GL A11 RH

RV620 GL A11 RH

3

RSVD_7

Control

Control

RSVD

LVTM channel

LVTM channel

RSVD_1

RSVD_2

T2X4P

T2X4M

T2X5P

T2X5M

RSVD_4

RSVD_3

RSVD_6

RSVD_5

T2XCP

T2XCM

T2X0P

T2X0M

T2X1P

T2X1M

T2X2P

T2X2M

T2X3P

T2X3M

TXCM_DPA3N

TXCP_DPA3P

TX0M_DPA2N

TX0P_DPA2P

TX1M_DPA1N

TX1P_DPA1P

TX2M_DPA0N

TX2P_DPA0P

TXCM_DPB3N

TXCP_DPB3P

TX0M_DPB2N

TX0P_DPB2P

TX1M_DPB1N

TX1P_DPB1P

TX2M_DPB0N

TX2P_DPB0P

DDC4CLK_DP4_AUXP

DDC4DATA_DP4_AUXN

DP_CALR

AA7

AC6

AD21

AE21

AJ24

AJ23

AK24

AL24

AG21

AH21

AG23

AH23

AL19

AK19

AJ20

AJ19

AK20

AL20

AK21

AL21

AK22

AL22

AJ4

AJ5

AL5

AK5

AL6

AK6

AK8

AL8

AK9

AL9

AJ9

AJ10

AL10

AK10

AL11

AK11

AG9

AF9

AG11

DPX-VID1

DPX-VID2

DP_CALR

RV610 - INSTALL R100-R106;

RV620 - DO NOT INSTALL R100-R106;

R153

R153

RV610: DNI R153

150R

150R

2

DPA_TX3N <15>

DPA_TX3P <15>

DPA_TX2N <15>

DPA_TX2P <15>

DPA_TX1N <15>

DPA_TX1P <15>

DPA_TX0N <15>

DPA_TX0P <15>

DPX-VID1 <13>

DPX-VID2 <13>

1

+1.1V

B892

B892

BLM15BD121SN1

+1.8V_D2

BLM15BD121SN1

DNI

BLM15BD121SN1

BLM15BD121SN1

B888

B888

RV610: DNI B892

RV620: DNI B888

A A

5

C150

C150

10uF_X6S

10uF_X6S

+DPAB_VDDR

C151

C151

1uF_6.3V

1uF_6.3V

4

C152

C152

100nF

100nF

R113-115 are legacy shunt terminations for RV610.

R110-112, R116 footprints are kept not for RV610 (since it is single-link

TMDS2), but rather so that TMDP link A and B have similar signal

degredations due to stubs.

They may be removed on future production boards.

www.vinafix.vn

3

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

?2007 Advanced Micro Devices

?2007 Advanced Micro Devices

?2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH RV620 - ASIC TMDP/LVTM Interface

RH RV620 - ASIC TMDP/LVTM Interface

2

RH RV620 - ASIC TMDP/LVTM Interface

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Thursday, March 20, 2008

Thursday, March 20, 2008

Thursday, March 20, 2008

Sheet

Sheet

Sheet

of

421

of

421

of

421

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

12

12

12

105-B408xx-00C

105-B408xx-00C

105-B408xx-00C

5

D D

C C

B B

A A

5

4

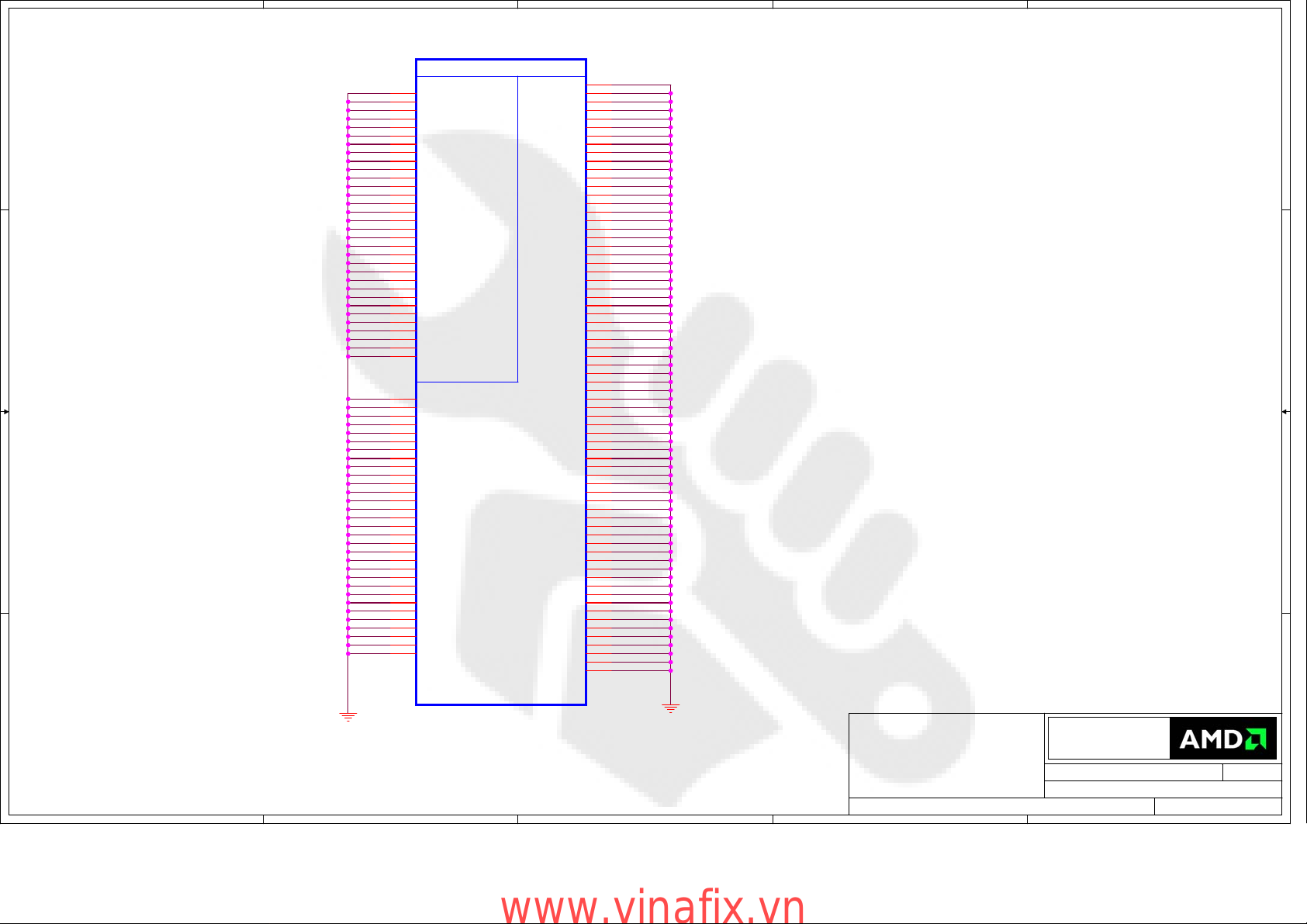

U1E

U1E

AA26

PCIE_VSS_1

AA29

PCIE_VSS_2

AC26

PCIE_VSS_3

AD31

PCIE_VSS_4

AE29

PCIE_VSS_5

AE30

PCIE_VSS_6

AE31

PCIE_VSS_7

F28

PCIE_VSS_8

G26

PCIE_VSS_9

G29

PCIE_VSS_10

G30

PCIE_VSS_11

G31

PCIE_VSS_12

H29

PCIE_VSS_13

J25

PCIE_VSS_14

J26

PCIE_VSS_15

L26

PCIE_VSS_16

L29

PCIE_VSS_17

L30

PCIE_VSS_18

L31

PCIE_VSS_19

M26

PCIE_VSS_20

M29

PCIE_VSS_21

P26

PCIE_VSS_22

R29

PCIE_VSS_23

R30

PCIE_VSS_24

R31

PCIE_VSS_25

T26

PCIE_VSS_26

U29

PCIE_VSS_27

V26

PCIE_VSS_28

Y26

PCIE_VSS_29

Y29

PCIE_VSS_30

Y30

PCIE_VSS_31

Y31

PCIE_VSS_32

A13

VSS_1

A2

VSS_2

C18

VSS_3

A24

VSS_4

A30

VSS_5

AA1

VSS_6

AA11

VSS_7

AA14

VSS_8

AA17

VSS_9

AA20

VSS_10

AA6

VSS_11

AC2

VSS_12

AC7

VSS_13

AE3

VSS_15

AL4

VSS_16

AD14

VSS_17

AF12

VSS_18

AF14

VSS_19

AD16

VSS_20

AD18

VSS_21

AE6

VSS_22

AG2

VSS_23

AE9

VSS_24

AH25

VSS_25

AK1

VSS_26

AK31

VSS_27

AJ6

VSS_28

AL2

VSS_29

AL30

VSS_30

B1

VSS_31

C13

VSS_32

CORE GND

CORE GND

RV620 GL A11 RH

RV620 GL A11 RH

4

Part 5 of 6

Part 5 of 6

PCI-Express GND

PCI-Express GND

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

B25

J8

B5

D11

C17

C22

C27

D29

C3

C6

D3

D28

F29

D4

F11

F12

F14

F16

F18

F20

F21

F23

F25

F7

F9

G3

G6

H23

J3

J4

J6

K1

L12

L15

L18

L21

L6

M11

M14

M17

M20

M6

P12

P15

P18

P21

P6

AC21

R14

R17

R20

T6

U1

U12

U15

U18

U21

AE20

V14

V17

V20

P2

V6

W2

Y12

Y15

Y18

Y21

Y6

M9

3

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

?2007 Advanced Micro Devices

?2007 Advanced Micro Devices

?2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

3

2

RH RV620 - ASIC Ground

RH RV620 - ASIC Ground

RH RV620 - ASIC Ground

2

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Thursday, March 20, 2008

Thursday, March 20, 2008

Thursday, March 20, 2008

Sheet

Sheet

Sheet

of

521

of

521

of

521

1

Doc No.

Doc No.

Doc No.

105-B408xx-00C

105-B408xx-00C

105-B408xx-00C

1

RevDate:

RevDate:

RevDate:

12

12

12

www.vinafix.vn

5

4

3

2

1

D D

C C

PLACE MVREF DIVIDERS

AND CAPS CLOSE TO ASIC

+MVDD

R291

R291

100R

100R

1%

C296

R292

+MVDD

R292

100R

100R

1%

R293

R293

100R

100R

1%

R294

R294

100R

100R

1%

B B

C295

C295

100nF

100nF

C297

C297

100nF

100nF

C296

10nF

10nF

C298

C298

10nF

10nF

M_MDA[63..0]<8>

U1C

MVREFD_0

MVREFS_0

R296

R296

4.7K

4.7K

R297

R297

4.7K

4.7K

M_MDA0

M_MDA1

M_MDA2

M_MDA3

M_MDA4

M_MDA5

M_MDA6

M_MDA7

M_MDA8

M_MDA9

M_MDA10

M_MDA11

M_MDA12

M_MDA13

M_MDA14

M_MDA15

M_MDA16

M_MDA17

M_MDA18

M_MDA19

M_MDA20

M_MDA21

M_MDA22

M_MDA23

M_MDA24

M_MDA25

M_MDA26

M_MDA27

M_MDA28

M_MDA29

M_MDA30

M_MDA31

M_MDA32

M_MDA33

M_MDA34

M_MDA35

M_MDA36

M_MDA37

M_MDA38

M_MDA39

M_MDA40

M_MDA41

M_MDA42

M_MDA43

M_MDA44

M_MDA45

M_MDA46

M_MDA47

M_MDA48

M_MDA49

M_MDA50

M_MDA51

M_MDA52

M_MDA53

M_MDA54

M_MDA55

M_MDA56

M_MDA57

M_MDA58

M_MDA59

M_MDA60

M_MDA61

M_MDA62

M_MDA63

TEST_MCLK

TEST_YCLK

MEMTEST

R298

R298

243R

243R

U1C

E29

DQ_0

E30

DQ_1

E31

DQ_2

D31

DQ_3

C29

DQ_4

B29

DQ_5

B30

DQ_6

A29

DQ_7

E26

DQ_8

D26

DQ_9

E25

DQ_10

D25

DQ_11

G23

DQ_12

G21

DQ_13

E21

DQ_14

D21

DQ_15

C28

DQ_16

B28

DQ_17

B27

DQ_18

A27

DQ_19

C25

DQ_20

A25

DQ_21

C24

DQ_22

B24

DQ_23

C23

DQ_24

B23

DQ_25

A23

DQ_26

B22

DQ_27

C20

DQ_28

B20

DQ_29

A20

DQ_30

C19

DQ_31

C8

DQ_32

C7

DQ_33

B7

DQ_34

A7

DQ_35

A5

DQ_36

C4

DQ_37

B4

DQ_38

A3

DQ_39

G9

DQ_40

E9

DQ_41

D9

DQ_42

G7

DQ_43

G5

DQ_44

F5

DQ_45

G4

DQ_46

F4

DQ_47

B3

DQ_48

B2

DQ_49

C2

DQ_50

C1

DQ_51

E3

DQ_52

F3

DQ_53

F2

DQ_54

F1

DQ_55

G2

DQ_56

G1

DQ_57

H3

DQ_58

H2

DQ_59

K2

DQ_60

L3

DQ_61

L2

DQ_62

L1

DQ_63

F30

MVREFD

F31

MVREFS

L5

TEST_MCLK

L7

TEST_YCLK

J7

MEMTEST

RV620 GL A11 RH

RV620 GL A11 RH

Part 3 of 6

Part 3 of 6

MEMORY

MEMORY

INTERFACE

INTERFACE

write strobe read strobe

write strobe read strobe

MA_0

MA_1

MA_2

MA_3

MA_4

MA_5

MA_6

MA_7

MA_8

MA_9

MA_10

MA_11

MA_BA0

MA_BA1

MA_A12

MA_BA2

DQMb_0

DQMb_1

DQMb_2

DQMb_3

DQMb_4

DQMb_5

DQMb_6

DQMb_7

QS_0

QS_1

QS_2

QS_3

QS_4

QS_5

QS_6

QS_7

QS_0B

QS_1B

QS_2B

QS_3B

QS_4B

QS_5B

QS_6B

QS_7B

ODT0

ODT1

CLK0

CLK1

CLK0b

CLK1b

RAS0b

RAS1b

CAS0b

CAS1b

CS0b_0

CS0b_1

CS1b_0

CS1b_1

CKE0

CKE1

WE0b

WE1b

DRAM_RST

B14

A14

B13

E14

B17

A17

C15

G16

E16

C14

A12

B12

C12

D14

B15

G14

D30

G25

C26

C21

C5

D6

D2

K3

C30

D23

B26

B21

B6

E7

E2

J2

C31

E23

A26

A21

A6

D7

E1

J1

E20

C11

A18

A11

B18

B11

G20

D12

D20

E12

E18

G18

G11

E11

D18

G12

D16

C10

J5

M_MAA0

M_MAA1

M_MAA2

M_MAA3

M_MAA4

M_MAA5

M_MAA6

M_MAA7

M_MAA8

M_MAA9

M_MAA10

M_MAA11

M_MAA14

M_MAA15

M_MAA12

M_MAA13

M_DQMA#0

M_DQMA#1

M_DQMA#2

M_DQMA#3

M_DQMA#4

M_DQMA#5

M_DQMA#6

M_DQMA#7

M_QSA0

M_QSA1

M_QSA2

M_QSA3

M_QSA4

M_QSA5

M_QSA6

M_QSA7

M_QSA#0

M_QSA#1

M_QSA#2

M_QSA#3

M_QSA#4

M_QSA#5

M_QSA#6

M_QSA#7

CLKA0 <8>

CLKA1 <8>

CLKA#0 <8>

CLKA#1 <8>

RASA#0 <8>

RASA#1 <8>

CASA#0 <8>

CASA#1 <8>

CSA#0_0 <8>

CSA#0_1 <8>

CSA#1_0 <8>

CSA#1_1 <8>

CKEA0 <8>

CKEA1 <8>

WEA#0 <8>

WEA#1 <8>

DRAM_RST

+MVDD

DNI

MR295

MR295

4.7K

4.7K

R295

R295

2.0K

2.0K

M_MAA[15..0] <8>

M_DQMA#[7..0] <8>

M_QSA[7..0] <8>

M_QSA#[7..0] <8>

Overlap

DRAM_RST <8>

A A

5

DIVIDER RESISTORS DDR2 GDDR3

MVREF TO 1.8V

MVREF TO GND

40.2R100R

100R100R

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

?2007 Advanced Micro Devices

?2007 Advanced Micro Devices

?2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH RV620 - ASIC Memory Interface

RH RV620 - ASIC Memory Interface

4

www.vinafix.vn

3

2

RH RV620 - ASIC Memory Interface

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Thursday, March 20, 2008

Thursday, March 20, 2008

Thursday, March 20, 2008

Sheet

Sheet

Sheet

of

621

of

621

of

621

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

12

12

12

105-B408xx-00C

105-B408xx-00C

105-B408xx-00C

Loading...

Loading...