MSI MS-V123 Schematic _0a

A B C D E F G H

co-layout co-layout

1

1

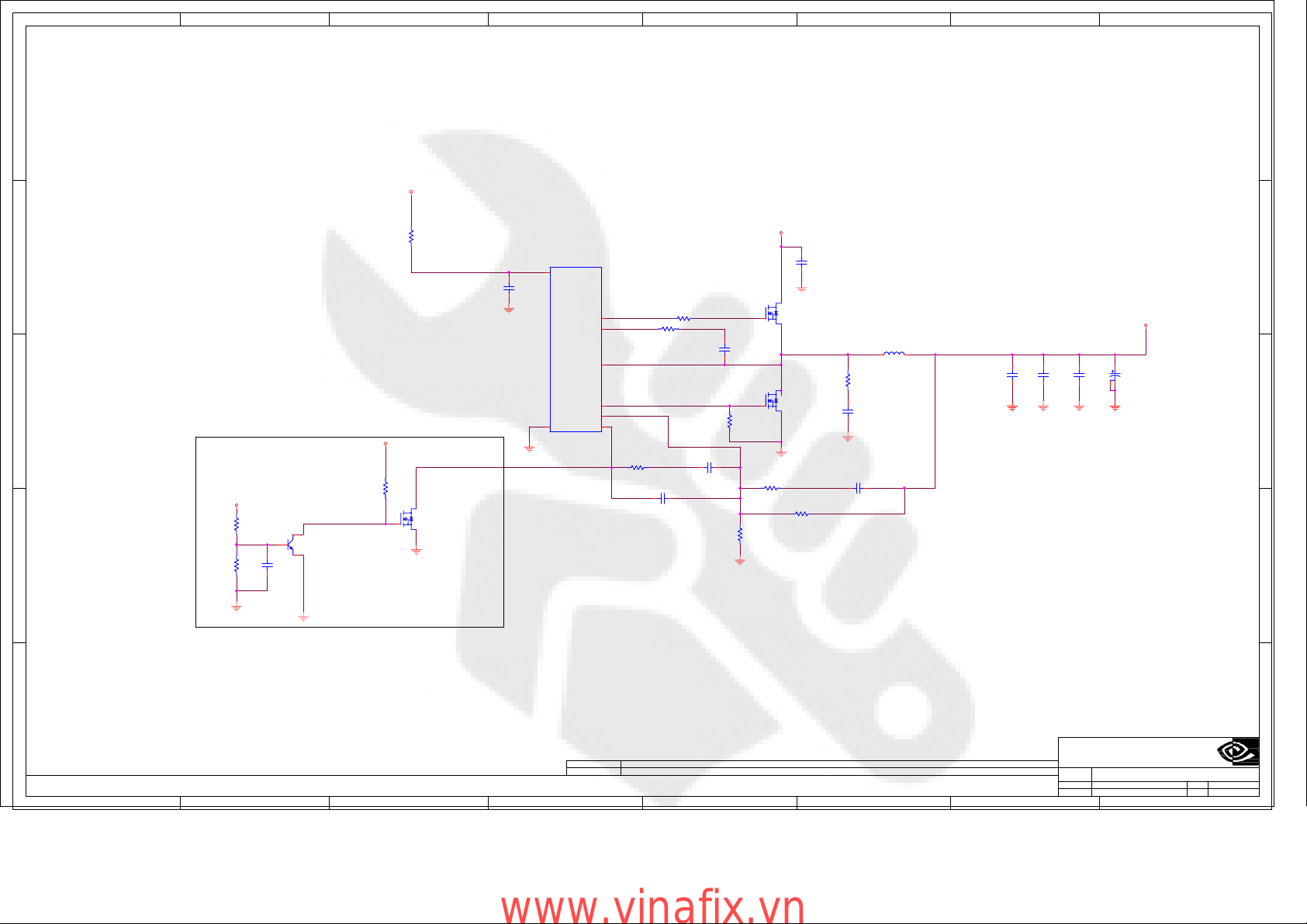

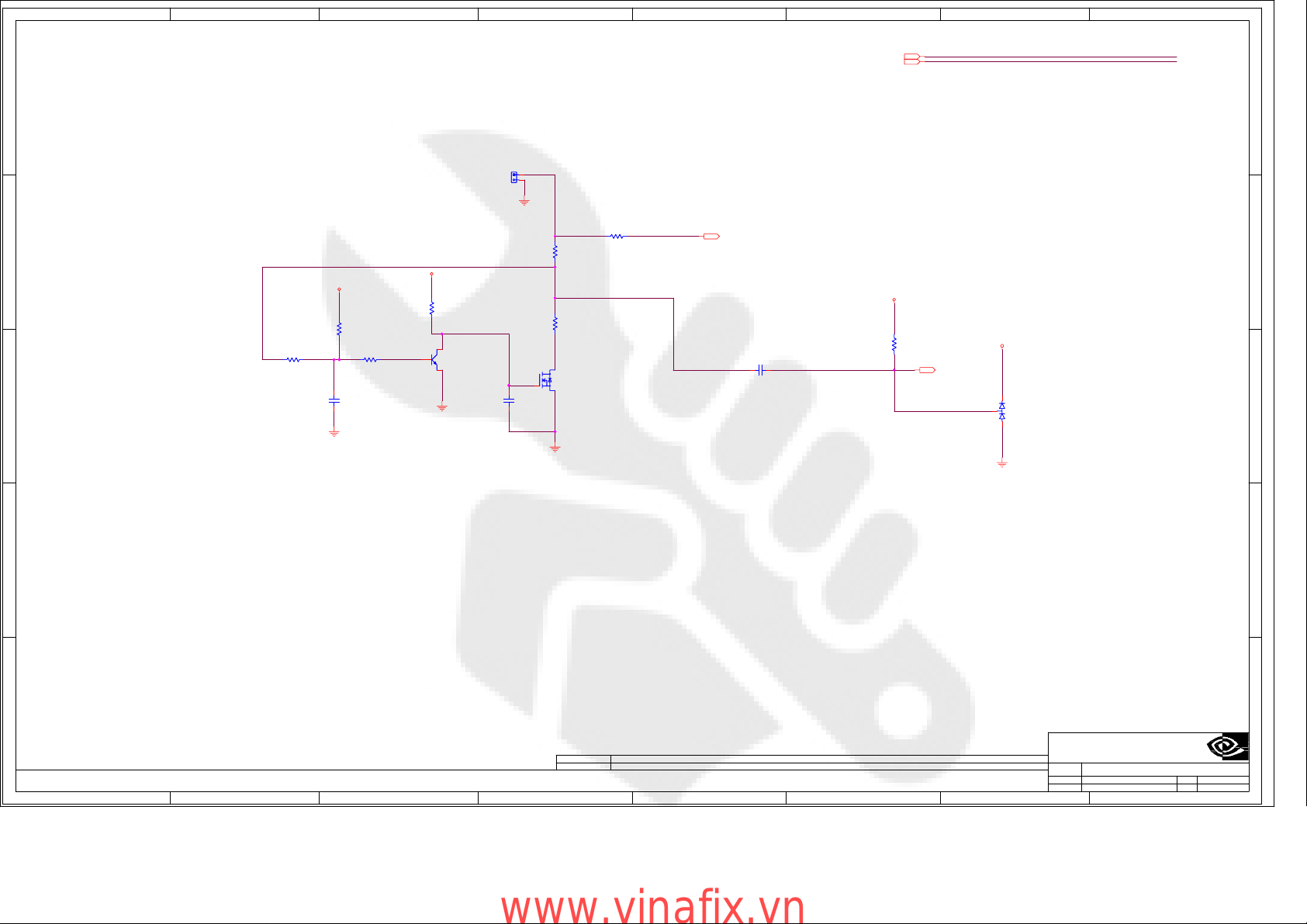

PowerSupplyII: FBVDDQ

CAP for EMI

APW7065 I32-0706502-A30

12V_PEX

COMMON

COMMON

5%

5%

0603

0603

R630 2.2

2

R630 2.2

3

Power Sequence

NVVDD

R531

R531

1K

1K

5%

5%

0402

0402

COMMON

COMMON

NVVDD_TH_EN

R621

R621

3K

4

3K

5%

5%

0402

0402

NC

NC

FBVDDQ_EN*

1B1C1E

1B1C1E

3

C

Q511

Q511

B

1

SOT23

SOT23

COMMON

COMMON

E

2

C731

C731

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

12V_PEX

R521 10K

R521 10K

1G1D1S

1G1D1S

COMMON

COMMON

5%

5%

0402

0402

3

D

Q19

Q19

MMBT2222A

MMBT2222A

G

SOT23

SOT23

1

D02-2222A49-O05

D02-2222A49-O05

S

2

50V

50V

0.22A@31C

0.22A@31C

3.5R

3.5R

0.88A

0.88A

0.36W@25C

0.36W@25C

+/-20V

+/-20V

uP6101BS8 I32-0610112-U33

L6783A I32-L678303-S10

U506

U506

VR_SW=0.8V, VR_LD=0.8V

VR_SW=0.8V, VR_LD=0.8V

SOIC8

SOIC8

SO8

C809

C809

1UF

1UF

25V

25V

10%

10%

X7R

X7R

0805

0805

COMMON

COMMON

SO8

COMMON

COMMON

5

VCC12

SW_GH

BOOT

PHASE

SW_GL

SW_FB

3

COMP

GND

SW12V_C

16.0

12V_PEX

C16

C16

10UF

10UF

16V

16V

20%

20%

X7R

X7R

C1206_113

C1206_113

COMMON

COMMON

D

D

Q3

Q3

?

?

?

?

?

?

DPAKSGD

DPAKSGD

?

R774

0R

R774

COMMON

COMMON

0R

5%

5%

FB_RC_FB

10.0

2.2PFC810

2.2PF

16V

16V

10%

10%

X7R

X7R

COMMON

COMMON

R0805_67

R0805_67

0R

0R

COMMON

COMMON

FB_UG_C

COMMON

COMMON

5%

5%

FB_BOOT_C

16.0

C839

C839

.1UF

.1UF

25V

25V

10%

10%

X7R

X7R

0603

0603

COMMON

COMMON

R626

R626

10k

10k

5%

5%

0402

0402

COMMON

COMMON

C837

1nFC837

1nF

16V0402

16V0402

10%

10%

X7R

X7R

COMMON

COMMON

COMMON

COMMON

1%

1%

Rbot

0402

0402

R623 4.7K

R623 4.7K

16.0

R622

R622

R0805_67

R0805_67

16.0

16.0

C810

0402

0402

FB_UG

2

FB_BOOT

1

16.0

STUFF 0 OHM RISISTOR

8

FB_BG

4

FB_FB

6

7

R590

47K

R590

47K

0402

0402

1%

1%

FB_COMP

10.0

?

G

G

STUFF

STUFF

S

S

1G1D1S

1G1D1S

?

?

?

?

FB_PHASE

16.0

D

Q4

Q4

?

?

?

?

?

?

DPAKSGD

DPAKSGD

?

?

G

STUFF

STUFF

S

1G1D1S

1G1D1S

?

?

?

?

NC NC

R624

0402

0402

FB_RC_IN

49.9NCR624

49.9

NC

5%

5%

10.0

Rtop

R625

5.9K

R625

5.9K

COMMON

COMMON

0603

0603

1%

1%

FBVDD 1.8 = 0.8 * (1+Rtop/Rbot)

FBVDD 1.8 = 0.8 * ( 1+ 5.9k / 4.7k )

1.5

1.5

R27

R27

C841

C841

0402

0402

COMMON

COMMON

5%

5%

R1206_113

R1206_113

FB_SNUBBER

10.0

C41

C41

1000PF

1000PF

50V

50V

10%

10%

X7R

X7R

0603

0603

0.015uF

0.015uF

16V

16V

10%

10%

X7R

X7R

NC

NC

COMMON

COMMON

EL65

EL65

Dip 1.6uH

Dip 1.6uH

C88

C88

4.7UF

4.7UF

25V

25V

10%

10%

X7R

X7R

C0805_67

C0805_67

COMMON

COMMON

FBVDDQ

C39

C39

1

C60

C60

C58

C58

1UF

1UF

50V

50V

10%

10%

X7R

X7R

0603

0603

.1UF

.1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

1500UF

1500UF

COMMON

COMMON

20%

20%

6.3V

6.3V

2

3

ALE

ALE

1.34A@105C

1.34A@105C

0.021

0.021

1500UF_6_3V

1500UF_6_3V

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

C GE

www.vinafix.vn

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

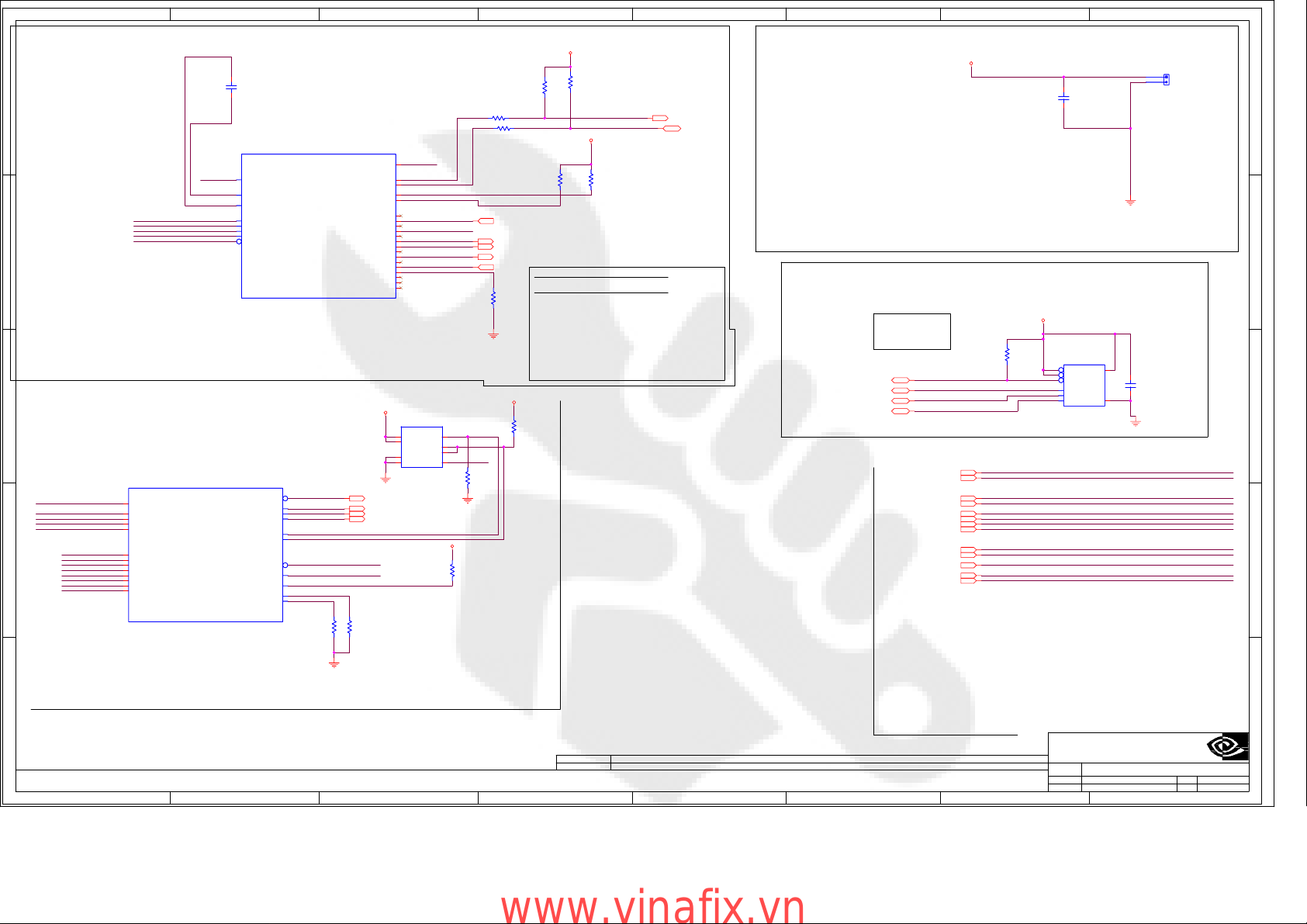

PowerSupplyI: NVVDD

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10403-0000-200 A

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

5

PAGEID

12-JAN-2007

DATE

HFDBA

A B C D E F G H

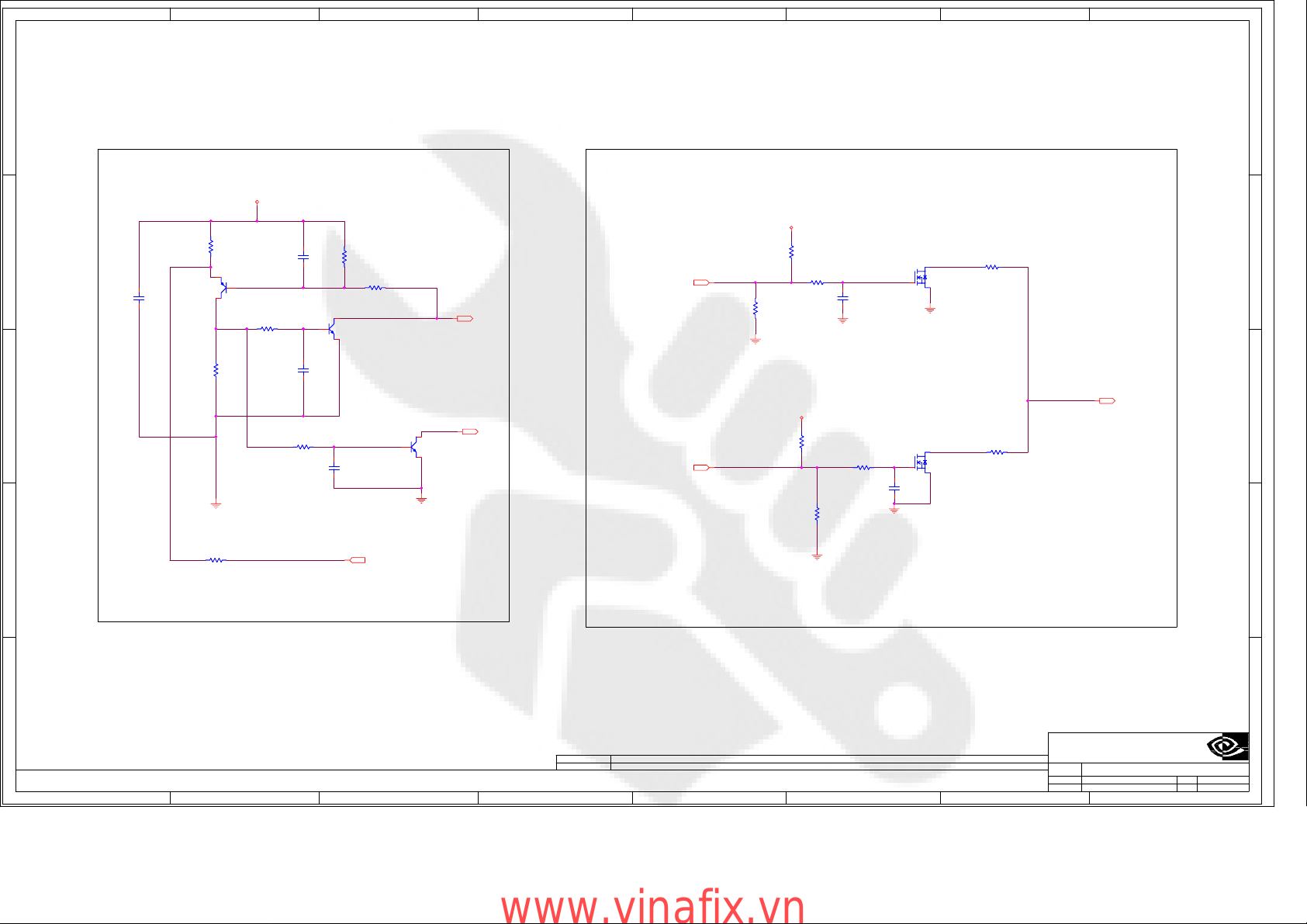

thermal protection and dynamic NVVDD

1

A3V3

COMMON0402

COMMON0402

2KR592

2K

5%

2

C812

C812

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

5%

R592

1B1C1E

1B1C1E

2

E

Q508

Q508

THERMAL_P*

B

1

SOT23

SOT23

COMMON

COMMON

C

3

THERMAL_NB

R600

0402 COMMON

0402 COMMON

COMMON

COMMON

33K

33K

5%

5%

0402

0402

R598

R598

C836

C836

COMMON

COMMON

2K

2K

.1UF

.1UF

16V

16V

5%

5%

10%

10%

X7R

X7R

0603

0603

0402

0402

R602

R602

COMMON

COMMON

1B1C1E

1B1C1E

THERMAL_N

10K5%R600

10K

5%

C811

C811

1000PF

1000PF

50V

50V

10%

10%

X7R

X7R

0603

0603

COMMON

COMMON

R596

2KR596

2K

COMMON0402

COMMON0402

5%

5%

3

C

Q509

Q509

B

1

SOT23

SOT23

COMMON

COMMON

E

2

GPIO8_THERM_ALERT*

16

OUT

GPIO6_NVVDDCTRL1

16,16

IN

3

3V3_TH_EN

1B1C1E

1B1C1E

3

C

Q506

R597

PEX_RST_P_C

THERMAL_N_C

10K5%R597

10K

COMMON0402

COMMON0402

5%

C806

C806

1000PF

1000PF

50V

50V

10%

10%

X7R

X7R

0603

0603

COMMON

COMMON

Q506

B

1

SOT23

SOT23

COMMON

COMMON

E

2

21

OUT

16,16

GPIO5_NVVDDCTRL0

IN

A3V3

10K

10K

5%

5%

0402 NC

0402 NC

R577

R577

R576 10K

R576 10K

0402 COMMON

0402 COMMON

10K

10K

5%

5%

0402 NC

0402 NC

R578

R578

A3V3

10K

10K

5%

5%

0402 COMMON

0402 COMMON

R574

R574

NVVDDCTRL1

5%

5%

C797

C797

.1UF

.1UF

25V

25V

10%

10%

X7R

X7R

0603

0603

NC

NC

NVVDDCTRL0

R573

10KR573

10K

0402 COMMON

0402 COMMON

5%

5%

5%

5%

0402 NC

0402 NC

R571 10K

R571 10K

NVVDDCTRL1_C

R581 6.19K

3

2

60V

60V

0.115A

0.115A

7.5R

7.5R

0.8A

0.8A

0.2W

0.2W

20V

20V

NVVDDCTRL0_C

3

2

60V

60V

0.115A

0.115A

7.5R

7.5R

0.8A

0.8A

0.2W

0.2W

20V

20V

R581 6.19K

0402 NC

0402 NC

1%

1%

R582 16.9K

R582 16.9K

0402 COMMON

0402 COMMON

1%

1%

NV_FB

20,21

OUT

1G1D1S

1G1D1S

D

Q504

Q504

SOT23

SOT23

G

1

NC

NC

S

1G1D1S

1G1D1S

D

Q503

Q503

SOT23

SOT23

G

1

COMMON

COMMON

S

C792

C792

.1UF

.1UF

25V

25V

10%

10%

X7R

X7R

0603

0603

COMMON

COMMON

1

2

3

R591

0R591

4

0

COMMON0402

COMMON0402

5%

5%

PEX_RST*

IN

2

Thermal protection

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

C GE

www.vinafix.vn

ASSEMBLY

PAGE DETAIL

dynamic NVVDD

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

thermal protection and dynamic NVVDD

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10403-0000-200 A

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

4

5

PAGEID

DATE

12-JAN-2007

HFDBA

A B C D E F G H

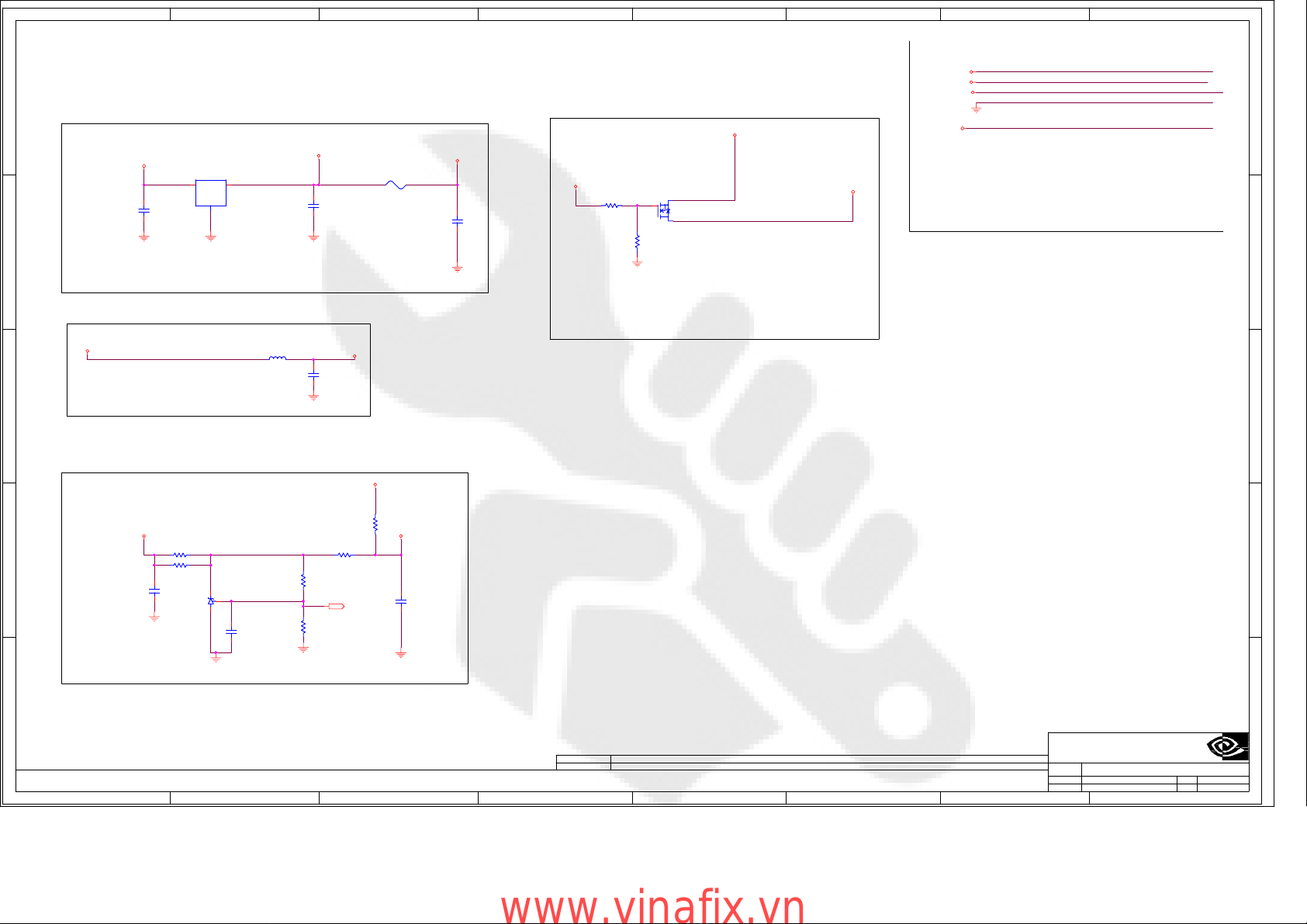

Power SupplyI:TMDS_IOVDD A3V3 DDC_5V IFP_PLLVDD FBVDDQ

1

U1

U1

VR=5V

VR=5V

IGO,IGOI

C21

C21

1UF

1UF

16V

16V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

1

IGO,IGOI

DPAK312_TO252

DPAK312_TO252

COMMON

COMMON

IN

3

OUT

GND

2

12V_PEX

2

A3V3 Power Supply

3V3_PEX

A3V3 = 3.3V @1.5A

3

IFP_PLL SUPPLY

3V3_PEX

R5695%100

4

R5695%100

R570

0603 NC

0603 NC

C789

C789

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

NC

NC

NC0603

NC0603

1005%R570

100

5%

VR=1.240V

VR=1.240V

IFPAB_PLLVDD_C

U503

U503

23

1

SOT23

SOT23

SOT23

SOT23

NC

NC

C787

C787

.047UF

.047UF

16V

16V

10%

10%

X7R

X7R

0402

0402

NC

NC

LB6

L0805_67 COMMON

L0805_67 COMMON

DAC_VREF

DDC 5V

5V

0.3A 16

C15

C15

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

C0805_67

C0805_67

COMMON

COMMON

220R@100MHzLB6

220R@100MHz

C30

C30

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

R568NC0

R568NC0

0402

0402

R566

0402

R566

0402

Rt

1%

1%

NC

NC

442

442

R565

R565

OUT

0402

0402

1%

1%

Rb

NC

NC

976

976

F1

F1

200mA

200mA

POLYSW2_P2_8

POLYSW2_P2_8

COMMON

COMMON

1 2

POLYSWITCH

POLYSWITCH

A3V3

FBVDDQ

COMMON

COMMON

0R38

0

5%

5%

0603

0603

R38

IFP_PLLVDD

5%

5%

9,10,14

Vout=Vref *(1+Rt/Rb)

1.8025V=1.25*(1+442/1K)

C48

C48

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

C0805_67

C0805_67

COMMON

COMMON

@50mA

DDC_5V

C13

C13

220PF

220PF

COMMON

COMMON

50V

50V

C0G

C0G

0603

0603

5%

5%

TMDS IO SUPPLY WITH BACKDRIVE PROTECTION

A3V3

+/-12V

+/-12V

0.8W@70C

0.8W@70C

20A

20A

0.08R

0.08R

3.4A

12V_PEX

Power down option

A3V3 Rtop 15K Rbot 10K

NVVDD Rtop 1K Rbot 3K

3.4A

S

20V

20V

BK_DR_MOS

G

COMMON

COMMON

2

COMMON

COMMON

1

SOT23

SOT23

D

Q9

Q9

1G1D1S

1G1D1S

3

R45

R45

10K

10K

5%

5%

0402

0402

COMMON

COMMON

R44

2KR44

2K

0402

0402

5%

5%

NETNAME MAX_CURRENT MIN_LINE_WIDTH

DDC_5V

A3V3

IFPAB_IOVDD

GND

IFP_PLLVDD

IFPAB_IOVDD

360 mA

0.1A 12.0 5.00000V

1.5A 30.0 3.30000V

0.3A 16 3.30000V

0.3A 16 1.80000V

VOLTAGE

0.000000V35.0

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

C GE

www.vinafix.vn

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

POWER SUPPLY: TMDS IOVDD,5V,A3V3

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10403-0000-200 A

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

5

PAGEID

DATE

12-JAN-2007

HFDBA

A B C D E F G H

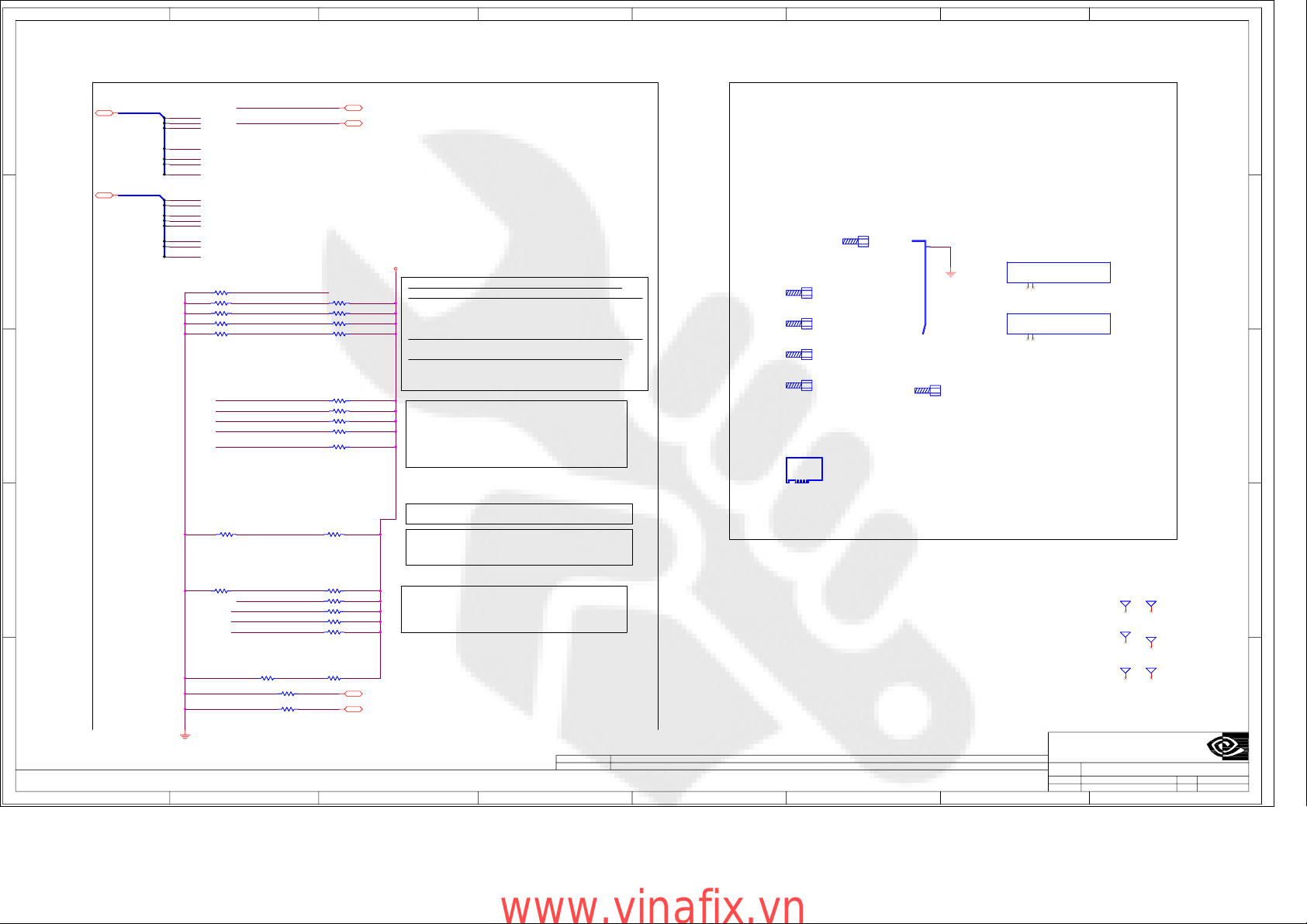

BIOS, Straps, Misc

Straps

1

13,13

13,13

2

MIOAD[14..0]

BI

MIOBD[11..0]

BI

MIOAD0

0

MIOAD1

1

MIOAD2

2

MIOAD6

6

MIOAD8

8

MIOAD9

9

MIOAD13

13

MIOBD0

0

MIOBD1

1

MIOBD3

3

MIOBD4

4

MIOBD5

5

MIOBD8

8

MIOBD9

9

MIOBD11

11

R21

R21

R62

R62

R65

R61

R5415%10K

R5415%10K

3

4

2K

2K

0402

0402

COMMON

COMMON

5%

5%

10K

10K

COMMON

COMMON

0402

0402

5%

5%

10KR65

10K

COMMON0402

COMMON0402

5%

5%

10K5%R61

10K

0402 COMMON

0402 COMMON

5%

0402 COMMON

0402 COMMON

R22

R22

0402

0402

5%

5%

MIOB_HSYNC

MIOB_CTL3

MIOAD1

MIOBD0

MIOBD1

MIOBD8

MIOBD9

MIOBD4

MIOBD5

MIOBD3

MIOBD11

MIOB_CTL3

CoMMON

CoMMON

MIOAD2

2K

2K

R57

R57

0402

0402

R56 10K

R56 10K

0402 COMMON

0402 COMMON

R55

0402

0402

R540

R540

0402

0402

R54 2K

R54 2K

0402

0402

R58 2K

R58 2K

0402 COMMON

0402 COMMON

R53 2K

R53 2K

R562

R562

0402

0402

R63

R63

0402

0402

R23

R23

5%

5%

13

BI

13

BI

REG: NV_PEXTDEV_BOOT_0

Bit Signal

A3V3

00: GV_WIDTH

01: SUB_VENDOR

10K

10K

COMMON

COMMON

5%

5%

5%

5%

10KR55

10K

COMMON

COMMON

5%

5%

10K

10K

COMMON

COMMON

5%

5%

COMMON

COMMON

5%

5%

5%

5%

COMMON0402

COMMON0402

5%

5%

2K

2K

COMMON

COMMON

5%

5%

2K

2K

COMMON

COMMON

5%

5%

2K

2K

COMMON0402

COMMON0402

02: RAM_CFG_0

03: RAM_CFG_1

04: RAM_CFG_2

05: RAM_CFG_3

06: CRYSTAL_0

07: TV_MODE_0

08: TV_MODE_1

09: TVMODE[2]

10: PCI_DEVID_0

11: PCI_DEVID_1

12: PCI_DEVID_2

13: PCI_DEVID_3

28: PCI_DEVID_EXT

14: FB[0]

15: FB[1]

16: FB[2]

22: ROM_TYPE_0

23: ROM_TYPE_1

24: USER_0

25: USER_1

26: USER_2

27: USER_3

VALUE_ID

GV_WIDTH

SUB_VENDOR

RAM_CFG[3:0]

CRYSTAL

TV_MODE[2:0]

PCI_DEVID[3:0]

PCI DevID (G9x+)

VALUEs

0=Wide (G80)

1=Narrow (all other)

0 NO_BIOS

1 read from BIOS

0001=16Mx32 DDR3 256-bit Infineon

0010=16Mx32 DDR3 256-bit Hynix

0011=16Mx32 DDR3 256-bit Samsung

0101=8Mx32 DDR3 256-bit Infineon

0110=8Mx32 DDR3 256-bit Hynix

0111=8Mx32 DDR3 256-bit Samsung

1001=16Mx32 DDR3 128-bit Infineon

1010=16Mx32 DDR3 128-bit Hynix

1011=16Mx32 DDR3 128-bit Samsung

1101=8Mx32 DDR3 128-bit Infineon

1110=8Mx32 DDR3 128-bit Hynix

1111=8Mx32 DDR3 128-bit Samsung

0=27MHz

1=14.31818MHz

000=NTSM_M

001=NTSC_J

010=PAL_M

011=PAL_N

100=PAL_CN

101=PAL_BDGHI

110=Reserved_0

Frame Buffer Max Size

000=64MB

001=128MB

010=256MB

011=512MB

100=1GB Reserved

101=2GB Reserved

110=4GB Reserved

111=Reserved

00 ParallelROM_TYPE[1:0]

01 Serial_AT25F

10 Serial_SST45VF

11 RFU

0000 (default)STRAP_USER[3:0]

Assembly: BIOS

111=Reserved_1

Mechanical parts

155-00003-0000-000

SCREW HEX JACK 4-40 x 12.1MM STANDARD

MEC1

MEC1

MEC_SCREW_HEX_JACK

MEC_SCREW_HEX_JACK

COMMON

COMMON

MEC3

MEC3

MEC_SCREW_HEX_JACK

MEC_SCREW_HEX_JACK

COMMON

COMMON

MEC4

MEC4

MEC_SCREW_HEX_JACK

MEC_SCREW_HEX_JACK

COMMON

COMMON

MEC2

MEC2

MEC_SCREW_HEX_JACK

MEC_SCREW_HEX_JACK

COMMON

COMMON

PCB

PCB

PCB

PCB

V096-20

V096-20

CABLE

CABLE

MEC_SCREW_HEX_JACK

MEC_SCREW_HEX_JACK

COMMON

COMMON

151-10001-0006-001 -- > DVI-DB15-MDIN

BKT1

BKT1

BRKT_LP_1TAB_1_DVI_DB15S_2_MDIN

BRKT_LP_1TAB_1_DVI_DB15S_2_MDIN

COMMON

COMMON

1

MECH. MOUNTING TOP

MECH. MOUNTING TOP

MC1

MC1

MEC_SCREW_PH1

MEC_SCREW_PH1

COMMON

COMMON

MEC7

MEC7

HSP_GPU_HS116_T_AL_1

HSP_GPU_HS116_T_AL_1

COMMON

COMMON

COOLING SOLUTION

COOLING SOLUTION

2 connected mounting pins

2 connected mounting pins

1

2

MEC8

MEC8

HSA_GPU_TM31-1LP_T_AL_1_V1

HSA_GPU_TM31-1LP_T_AL_1_V1

COMMON

COMMON

COOLING SOLUTION

COOLING SOLUTION

2 connected mounting pins

2 connected mounting pins

1

2

1

2

3

4

R25 2K

R77 2K

R77 2K

0402

0402

5%

5%

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

COMMON

COMMON

MIOB_HSYNC

R19

R19

0402 COMMON

0402 COMMON

5%

5%

MIOAD0

MIOAD8

2K

2K

R46 10K

R46 10K

R567

R567

MIOAD6

MIOAD9

MIOAD13

0402 COMMON

0402 COMMON

5%

5%

10K

10K

0402

COMMON

0402

COMMON

5%

5%

R25 2K

R17

R17

0402

0402

R16

R16

0402

0402

R15

R15

0402

0402

R64

0402 COMMON

0402 COMMON

R18

R18

ROM_SI

ROM_SCLK

COMMON0402

COMMON0402

5%

5%

2K

2K

COMMON

COMMON

5%

5%

2K

2K

COMMON

COMMON

5%

5%

2K

2K

COMMON

COMMON

5%

5%

2KR64

2K

5%

5%

2K

2K

COMMON0402

COMMON0402

5%

5%

BI

BI

17: PEX_PLL_EN_TERM100

18: 3GIO_PADCFG_LUT_ADR[0]

19: 3GIO_PADCFG_LUT_ADR[1]

20: 3GIO_PADCFG_LUT_ADR[2]

21: 3GIO_PADCFG_LUT_ADR[3]

31: StrapOverride per SW

REG: NV_STRAP_1

Bit Signal

15: Slot Clock Configuration

16,16,16

12: MIO_EN_33V_0

16,16,16

13: MIO_EN_33V_1

16: PCI_IOBAR

MIOB_VDDQ Voltage

VALUE_ID

MIOA_VDDQ Voltage

0 (default -- internal term on)

0000=Desktop

0001=Mobile

0011=Mobile NTHRS LAMP

0100=Mobile NTHRS HAMP

0101=Mobile NTHRS HHAMP

0110=Mobile NTHRS HHHAMP

0111=Mobile NTHRS HHHHAMP

1000=Desktop HTHRS

VALUEs

0=Disable

1=Enable

0=2.5V

1=3.3V

0=2.5V

1=3.3V

0=Disable

1=Enable

C GE

www.vinafix.vn

ASSEMBLY

PAGE DETAIL

1001=Mobile HTHRS NAMP

1010=Mobile HTHRS LLAMP0010=Mobile NTHRS LLAMP

1011=Mobile HTHRS LAMP

1100=Mobile HTHRS HAMP

1101=Mobile HTHRS HHAMP

1110=Mobile HTHRS HHHAMP

1111=Mobile HTHRS HHHHAMP

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

BIOS STRAPS & MECHANICALS

FM2FM2

1

FM4FM4

1

FM6FM6

1

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10403-0000-200 A

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

FM1FM1

1

FM3FM3

1

FM5FM5

1

5

PAGEID

DATE

12-JAN-2007

HFDBA

A B C D E F G H

0402 COMMON

0402 COMMON

SPDIF

IN

SPDIF_IN

IN

1 56OHM

56OHM1

1

2

A3V3

2,17

OUT

D5

D5

SOT23

SOT23

3

30V

30V

200MA

200MA

COMMON

COMMON

1 2

3

SPDIF

2,17

1

Place between Bracket and SLI connector

Place between Bracket and SLI connector

J8

J8

1

2

MALE

MALE

2.0MM

2.0MM

90

90

CON_WAFER232_002_TH_RA_P020

CON_WAFER232_002_TH_RA_P020

COMMON

COMMON

SPDIF_IN

2

SPDIF_IN_R

SPDIF_IN_G_C

12V_PEX

5%

5%

0402 COMMON

0402 COMMON

R35 10K

R35 10K

SPDIF_G_C

1B1C1E

1B1C1E

3

C

Q7

Q7

B

1

SOT23

SOT23

COMMON

COMMON

E

2

C49

C49

1000PF

1000PF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

R41 76.8

R41 76.8

SPDIF_T_GND

1G1D1S

1G1D1S

D

Q8

Q8

SOT23

SOT23

G

1

COMMON

COMMON

S

A3V3

COMMON

COMMON

33K

33K

5%

5%

0402

0402

R75

R75

SPDIF_IN_C

R40

1KR40

1K

04021%COMMON

04021%COMMON

3

C54

C54

1000PF

1000PF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

R39

2.2K

R39

2.2K

COMMON

COMMON

0402

0402

5%

5%

60V

60V

0.115A

0.115A

7.5R

7.5R

0.8A

0.8A

0.2W

0.2W

20V

20V

COMMON

COMMON

1%

1%

0402

0402

3

2

R783

R783

0

0

COMMON

COMMON

5%

5%

0402

0402

R784

0

R784

0

COMMON

COMMON

0402

0402

5%

5%

14,16

OUT

SPDIF

A3V3

5%

5%

R771 100K

R771 100K

SPDIF

16V

16V

X7R

10%

X7R

10%

0402

0402

C56

C56

.1UF

.1UF

COMMON

COMMON

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

C GE

www.vinafix.vn

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

SPDIF

place close to GPU

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10403-0000-200 A

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

4

5

PAGEID

DATE

12-JAN-2007

HFDBA

A B C D E F G H

Use 10MIL Guard(GND) Trace around THERMDC and THERMDA

C773

C773

1000PF

1000PF

16V

16V

10%

10%

X7R

SNN_THERMAL

THERMDC

THERMDA

AJ11

AK11

AK12

X7R

0402

0402

COMMON

COMMON

G1N

G1N

BGA_0820_P100_330X330_G3_128B

BGA_0820_P100_330X330_G3_128B

COMMON

COMMON

9/14 MISC1

9/14 MISC1

V6

THERMALSENSOR_OBS

J1

THERMDN

K1

THERMDP

JTAG_TCK

JTAG_TMS

JTAG_TDI

AL12

JTAG_TDO

AL13

JTAG_TRST

GPIO & JTAG

ROMCS

ROM_SI

ROM_SO

ROM_SCLK

I2CH_SCL

I2CH_SDA

BUFRST

STEREO

SWAPRDY_A

TESTMEMCLK

TESTMODE

AA4

W2

AA6

AA7

G3

H3

F3

T3

M6

A26

H2

ROMCS*

ROM_SI

ROM_SO

ROM_SCLK

I2CH_SCL

I2CH_SDA

SNN_RESET_BUF*

SNN_STEREO

SWAPRDY_A

TESTMEMCLK

TESTMODE

10KR555

10K

R555

5%

5%

0402 COMMON

0402 COMMON

DRA_SYNC/GPIO11

DRB_SYNC/GPIO14

OUT

OUT

OUT

OUT

COMMON

COMMON

10KR527

10K

5%

5%

0402

0402

R527

16

16,16,18

16,16

16,16,18

CLAMP

I2CS_SCL

I2CS_SDA

I2CC_SCL

I2CC_SDA

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO12

GPIO13

A3V3

GND

GND

VCC

VCC

F6

C1

B1

G2

G1

K3

H1

K5

G5

E2

J5

G6

K6

E1

D2

H5

F4

E3

U3

U4

8

7

4

1

SNN_CLAMP

I2CS_SCL_G

I2CS_SDA_G

I2CC_SCL

I2CC_SDA

DVI_SOUTH_HPD

SNN_GPIO3_BRICK_POWER

GPIO5_NVVDDCTRL0

GPIO6_NVVDDCTRL1

GPIO8_THERM_ALERT*

GPIO10_TV_LOAD_TEST

GPIO11_SLI_SYNC0

U2

U2

SOIC8

SOIC8

COMMON

COMMON

SCL

SDA

SDA

NC

R525%33

R525%33

COMMON0402

COMMON0402

R51

33

R51

33

COMMON

COMMON

0402

0402

5%

5%

11,16

IN

16,20

OUT

16,20

OUT

20

OUT

11,16

IN

10KR68

10K

5%

5%

0402 COMMON

0402 COMMON

R68

A3V3

R24

R24

10K

10K

5%

5%

0402

0402

COMMON

COMMON

COMMON

0402

0402

5%

5%

10K

10K

R26

R26

COMMON

6

5

3

SNN_CRYPT0

2

COMMON

COMMON

0402

0402

5%

5%

10K

10K

R560

R560

1

SNN_JTAG_TCLK

SNN_JTAG_TMS

SNN_JTAG_TDI

SNN_JTAG_TDO

2

SNN_JTAG_TRST*

3

G1M

G1M

BGA_0820_P100_330X330_G3_128B

BGA_0820_P100_330X330_G3_128B

COMMON

COMMON

10/14 MISC2

SNN_STRAP

SNN_MEMSTRAPSEL0

SNN_MEMSTRAPSEL1

SNN_LOFBVDDQSEL_

SNN_LOFBVDDSEL_

SNN_GPU_U3_RFU

4

SNN_GPU_V3_RFU

SNN_GPU_U6_RFU

SNN_GPU_U5_RFU

SNN_GPU_U4_RFU

SNN_GPU_V4_RFU

SNN_GPU_V6_RFU

SNN_GPU_RFU8

AE26

AD26

AH31

AH32

AM8

AM9

AC26

F1

V3

V4

B32

U6

D1

10/14 MISC2

STRAP

MEMSTRAPSEL0

MEMSTRAPSEL1

MEMSTRAPSEL2

MEMSTRAPSEL3

RFU

RFU

RFU

RFU

RFU

RFU

RFU

RFU

A3V3 12V_PEX

R43

R43

2.2K

2.2K

R42

R42

2.2K

2.2K

5%

5%

0402

0402

5%

5%

COMMON

COMMON

0402

0402

COMMON

COMMON

I2CS_SCL

2,2

OUT

R610

R610

2.2K

2.2K

5%

5%

0402

0402

COMMON

COMMON

I2CS_SDA

5V

R611

R611

2.2K

2.2K

5%

5%

0402

0402

COMMON

COMMON

2,2

BI

GPIO Assignment Table

GPIO0I/O

FUNCTION

RESERVED

IN

1

IN

DVI SOUTH HOTPLUG DET

2

IN

RESERVED

3

RESERVED

IN

IN

4

RESERVED

NVVDDCTRL0

OUT

5

OUT

6

NVVDDCTRL1

RESERVED

7

IN

RESERVED

IN

8

OUT

FAN Control(ON/OFF)

9

RESERVED

OUT

10

IN

SLI_SYNC0

11

RESERVED

IN

12

RESERVED

13

IN

RESERVED

14

IN

GPIO ON/OFF FAN Control

BIOS (serial)

SROM MAPPING

ROM

SO

SI

SCK

CS*

16

BI

16,16,18

BI

16,16

BI

16,16,18

BI

ROMCS*

ROM_SI

ROM_SO

ROM_SCLK

NV4x

ROM_SO

ROM_SI

ROM_SCK

ROM_CS*

FAN

FAN

J5

J5

+12V

1

GND

2

MALE

MALE

2.5MM

C33

C33

1UF

1UF

16V

16V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

12

2.5MM

0

0

CON_HDR_001X002

CON_HDR_001X002

COMMON

COMMON

1

2

3V3_PEX

R561

R561

10K

10K

5%

5%

0402

0402

COMMON

COMMON

NET

I2CC_SCL

IN

I2CC_SDA

IN

I2CH_SCL

IN

I2CH_SDA

IN

ROM_CS*

IN

IN

IN

IN

IN

IN

IN

IN

IN

ROM_SI

ROM_SO

ROM_SCLK

DVI_SOUTH_HPD

GPIO5_NVVDDCTRL0

GPIO6_NVVDDCTRL1

I2CS_SCL_G

I2CS_SDA_G

16,16,18

16,16

16,16,18

11,16

16,20

16,20

U502

U502

SOIC8

SOIC8

SO8

SO8

COMMON

COMMON

7

HOLD8VCC

3

WP

1

CS

5

SI

2

SO

6

GND

SCK

MISC NET RULES

NV_CRITICAL

2 50OHM

2 50OHM

2 50OHM

2 50OHM

2 50OHM

4

NV_IMPEDANCE

50OHM2

50OHM2

50OHM2

50OHM2

50OHM2

50OHM2

C50

C50

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

3

DIFFPAIR

4

10MIL

10MIL

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

C GE

www.vinafix.vn

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

JTAG, BIOS ROM, HDCP ROM, FAN CONTROL, GPIO

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-10403-0000-200 A

NAMEIMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

5

PAGEID

DATE

12-JAN-2007

HFDBA

Loading...

Loading...