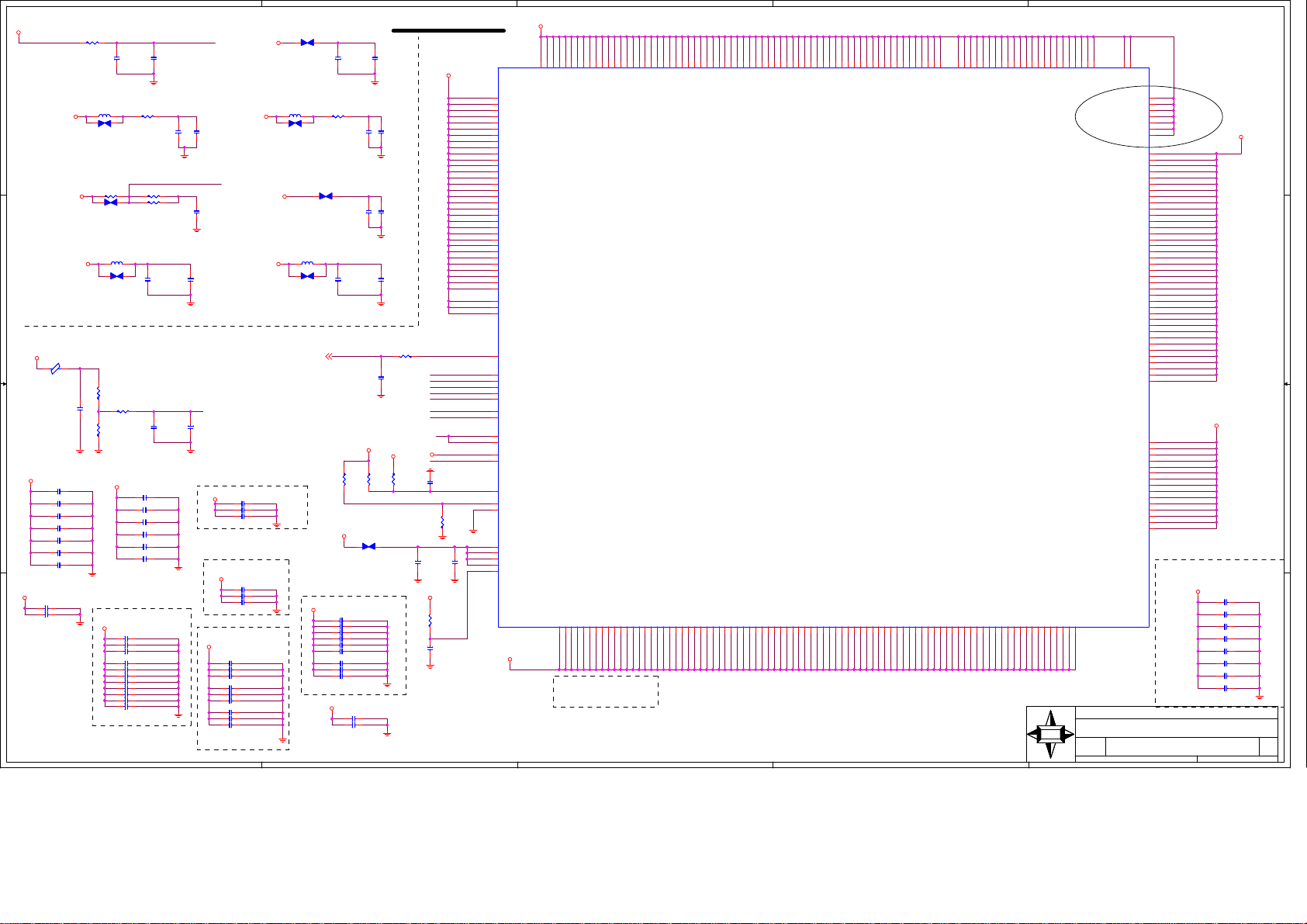

MSI MS-7565 Schematics

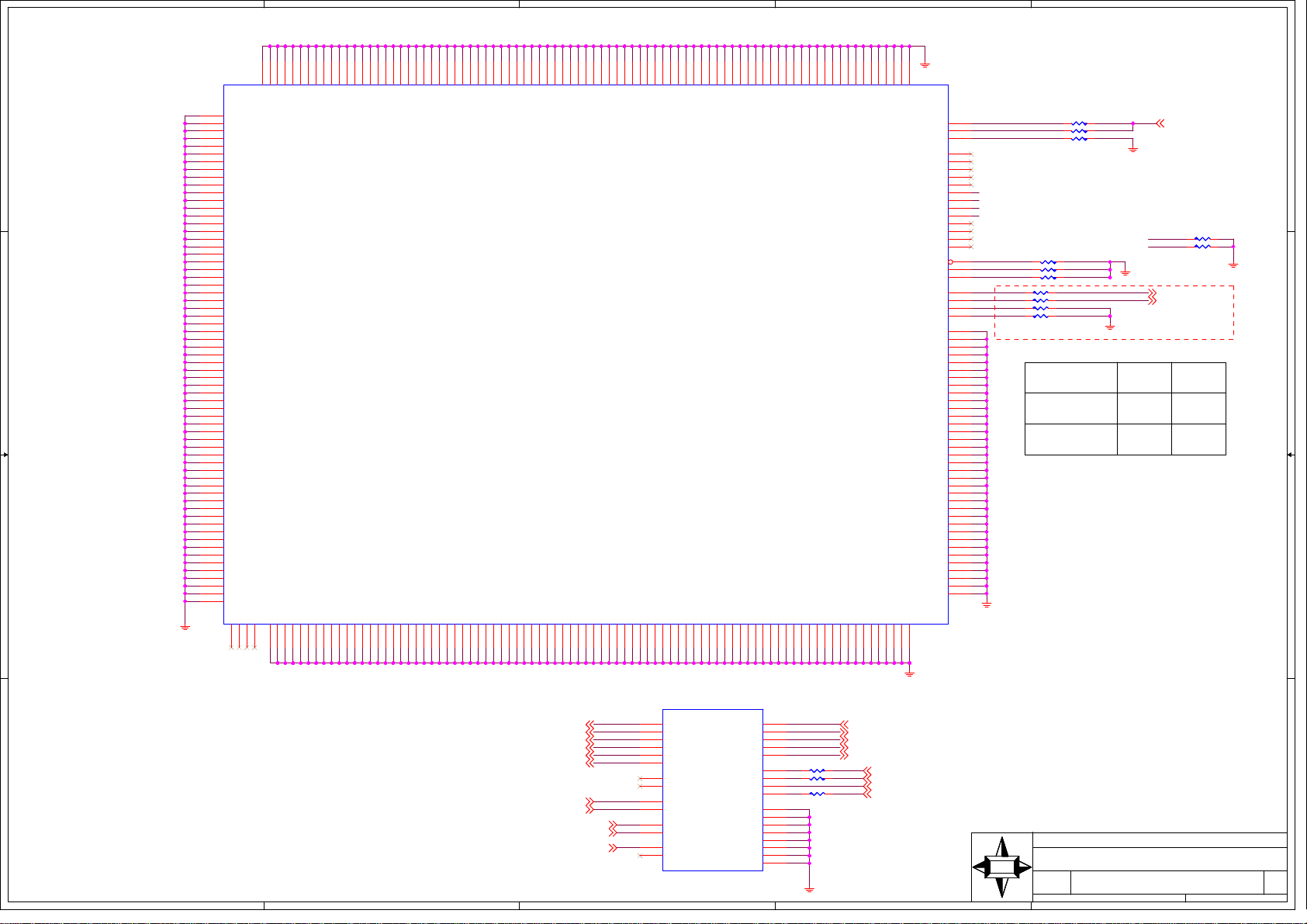

Block Diagram/Clock Map/Power Map

1Cover Sheet

2-4

1

MS-7565

Version 0B

Intel LGA775 CPU

Intel G41

5-7

8-12

CPU:

Core 2 Quad(Yorkfield)Q8xx0/Q9xx0 series(95W)

Intel ICH7 - PCI & DMI & CPU & IRQ

13

Core 2 Duo (Wolfdale) E8xx0 series (65W),

Intel ICH7 - LPC & ATA & USB & GPIO 14

Intel ICH7 - POWER

Clock - RTM875T-606

15

16

Core 2 Duo (Wolfdale-3M) E7xx0 series (65W),

Pentium Dual Core (Wolfdale) E5xx0 series (65W),

Celeron Dual Core (Conroe) E1xx0 series (65W),

Celeron (Conroe-L) 4x0 series (35W)

LPC I/O - Fintek 71858D

LAN REALTEK RTL8111DL/8102EL/8103EL

DDR II System Memory

& DDR II VTT Decoupling

17

18

19-21

System Chipset:

Intel G41 (North Bridge)

Intel ICH7R(South Bridge)

Azalia - ALC662

A A

PCI EXPRESS X16 & X1 Slot

22

23

24

On Board Chipset:

BIOS -- SPI

HD -- ALC662

SATA Connectors

USB Connectors

ATX Connetcor & Front Panel

25

26

27

LPC Super I/O -- F71858D

LAN-- REALTEK RTL8111DL/8102EL/8103EL

CLOCK -- RTM875T-606

uPI ACPI

GMCH VCORE

VGA Connector

VRM 11

DVI transfer & switch

1394 CONTROLLER-VT6315N

MANUAL PARTS

change history

BIOS Request Form

28

29

30

31

32

33

34

35

36

Main Memory:

DDR II *2 (Max 2GB)

Expansion Slots:

PCI EXPRESS X1 SLOT *3

PCI EXPRESS X16 SLOT *1

PWM:

ISL6312CRZ: 3 PHASES

1

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7565

MS-7565

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Cover Sheet

Cover Sheet

Cover Sheet

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

MS-7565

Sheet of

Sheet of

Sheet of

136

136

136

0B

0B

0B

1

Block Diagram

VRM 11

ISL6312

Vcore

Intel LGA775 Processor

3-Phase PWM

FSB

FSB 800/1066 MHz

FSB 1333 MHz for Intel Core 2

Duo processor family

Analog

Video

Out

PCI EXPRESS

X16

RGB

PCI EXPRESS X16

G41

DDRII 667/800 MHz

DDRII

2DDR II

DIMM

Modules

Connector

DMI

PCIE X1 SLOT

A A

SATA 0~3

USB Port 0~7

VT6315N

SATA

USB

1394

ICH7R

PCIE X1

PCIE X1 SLOT

PCIE X1

PCIE X1 SLOT

PCIE X1

ALC662

RTL8103EL

HD AUDIO

PCIE X1

SPI

LPC Bus

1

LPC SIO

Fintek

F71858D

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7565

MS-7565

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

MS-7565

236

236

236

Sheet of

Sheet of

Sheet of

0B

0B

0B

5

4

3

2

1

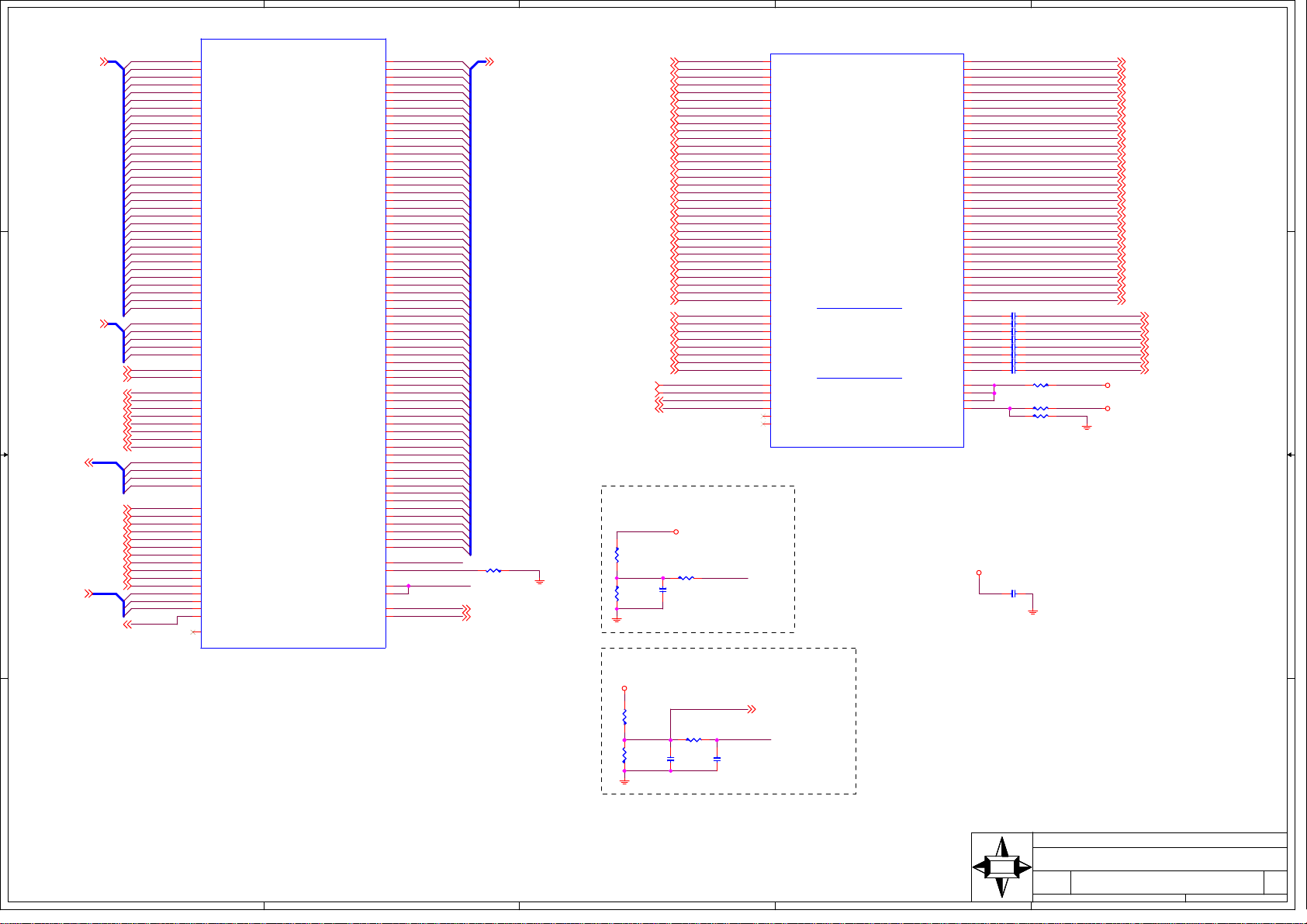

CLOCK MAP

CK_H_CPU

D D

CK_H_MCH

CK_96M_DREF

CK_PE_100M_MCH

CK_PE_100M_ICH

RTM875T-606

C C

CK_ICHSATA

ICH_PCLK

CK_48M_USB_ICH

CK_14M_ICH

200/266/333 MHz

200/266/333 MHz

96 MHz

100 MHz

100 MHz

100 MHz

33 MHz

48 MHz

14 MHz

LGA775

G41

ICH7R

FSB 1333 MHz for Intel

Core 2 Duo processor

family

DDRCLKA

DDRCLKB

HDCLK 24M

SPI_CLK

333/400 MHz

333/400 MHz

24 MHz

33MHz

CH A

ALC662

CH B

SPI

Fintek SIO

CK_P_33M_SIO

33MHz

71858D

CK_PE_100M_GLAN

B B

CK_PE_100M_16PORT

CK_PEX1_100M

CK_PEX2_100M

CK_PEX3_100M 100 MHz

A A

CK_PE_100M_1394 100 MHz

5

4

100 MHz

100 MHz

100 MHz

100 MHz

RTL8101E

PCIE X 16

PCIEX1_1

PCIEX1_2

PCIEX1_3

PCI-EX1 1394

3

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7565

MS-7565

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

CLOCK MAP

CLOCK MAP

CLOCK MAP

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

Date:

2

Wednesday, November 05, 2008

MS-7565

1

Sheet of

Sheet of

Sheet of

336

336

336

0B

0B

0B

5

4

3

2

1

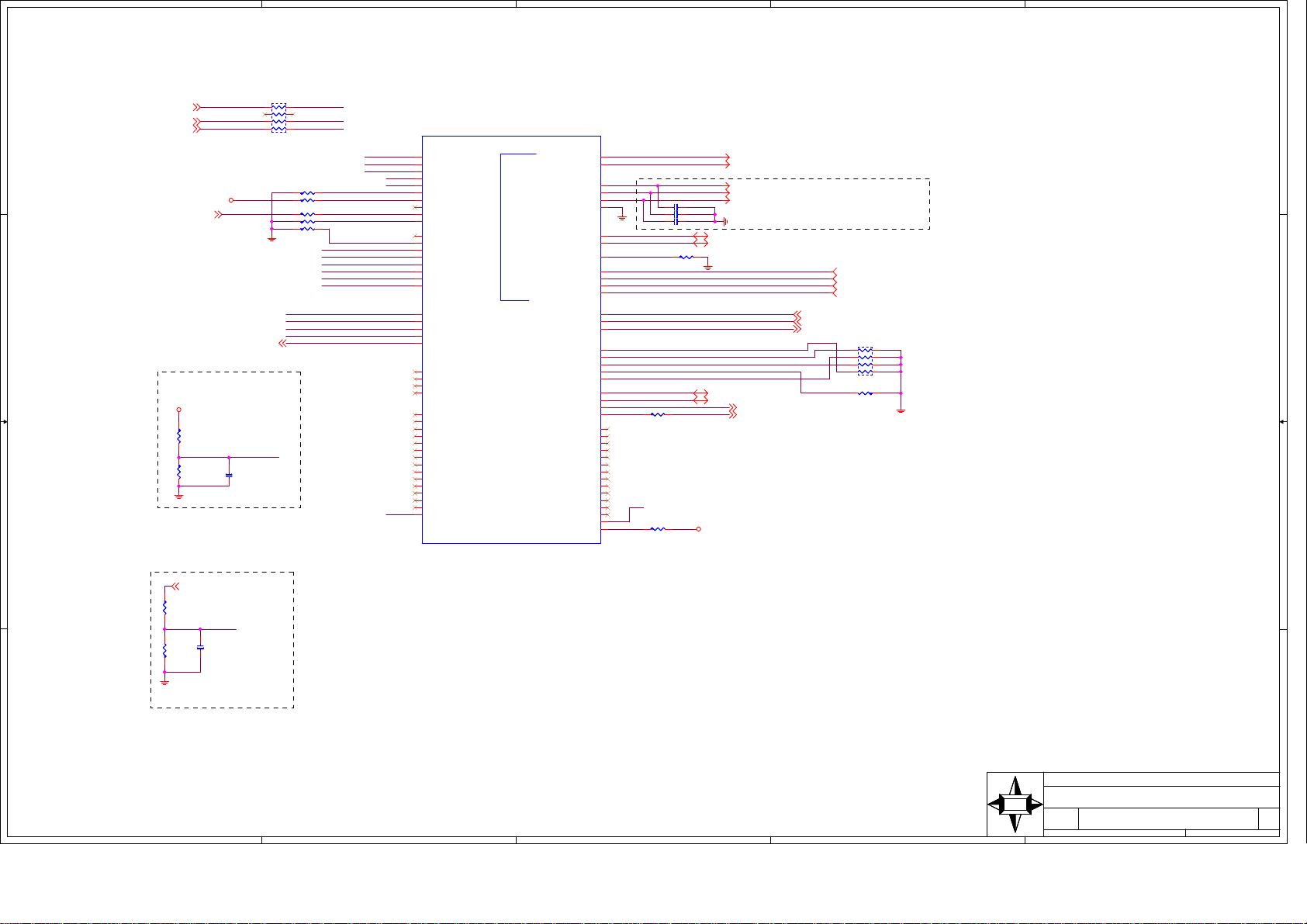

Processor

0.8375-1.6000V Core-125A

1.2V FSB Vtt-5.3A

VCCPLL

D D

VCC-IOPLL & VCCA

ISL6312 Regulator

VCCP

0.8375-1.6000V

W83310DS Regula

VTT_DDR

0.9V

DDR2 DIMM conn(4) & term

0.9V SM Vtt-1.2A(S0)

Eaglelake G41

- 1.0 A1.2V FSB_VTT

- 18.1A1.25V Core

VTT Regulator

V_FSB_VTT

1.2V

- 2.5 A1.25V DMI/PCI Exp.

(S0,S1)

- 3.2A1.8V VCC_DDR

1.8V VCC_SMCLK - TBD

3.3V VCCA_DAC

3.3V VCC33

- 66 mA

- 15.8mA

1.25V Vcc CL - TBD A

Divider

R

uP6103 Regulator

VCC_DDR

1.8V

uP6103 Regulator

V_1P25_CORE

C C

1.25V

1.8V Vdd/vddq-4.7A(S0,S1)

PCIE X16 slot(1)

+12V-5.5A

+3.3Vaux-375mA(wake)

+3.3Vaux-20mA(no wake)

+3.3V-3.0A

PCIE X1 slot(1)

+12V-0.5A

+3.3Vaux-375mA(wake)

+3.3Vaux-20mA(no wake)

+3.3V-3.0A

PCI slot slot(4)

+3.3Vaux-375mA(wake)

+3.3Vaux-20mA(no wake)

+3.3V-7.6A

+5.0V-5.0A

+12V-0.5A

ICH7

1.2V VCC_CPU-14mA

1.05V Core-0.86A

VCC1_5A*-1.01A

VCC1_5B*-0.77A

5VRef-6mA

R

5VrefSus-10mA

+3.3V-0.33A

B B

RTC-6uA(G3)

3.3V VccSus*-52mA

VccSus1_05V-See Note 1

VccUSBPLL-10mA

VccDMIPLL-50mA

VccSATAIPLL-50mA

L

L

1.05V Regulator

V_1P05_CORE

1.05V

1.5V Regulator

V_1P5_CORE

1.5V

uP7706 Regulator

3VSB

3.3V

uP7501 Regulator

5VDIMM

5V

-12V-0.1A

USB

+5V-4A(S0,S1)

PS2

+5V-345mA(S0,S1)

CLKGEN

+3.3V-560mA

LAN

3VSB-

Battery

SIO

+3.3V

3VSB-

+5VSB+12V +5V +3.3V+12V

Audio Codec

SPI ROM

ATX

A A

2x2

5

4

ATX POWER

3

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7565

MS-7565

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

Date:

2

Wednesday, November 05, 2008

MS-7565

POWER MAP

POWER MAP

POWER MAP

1

Sheet of

Sheet of

Sheet of

436

436

436

0B

0B

0B

5

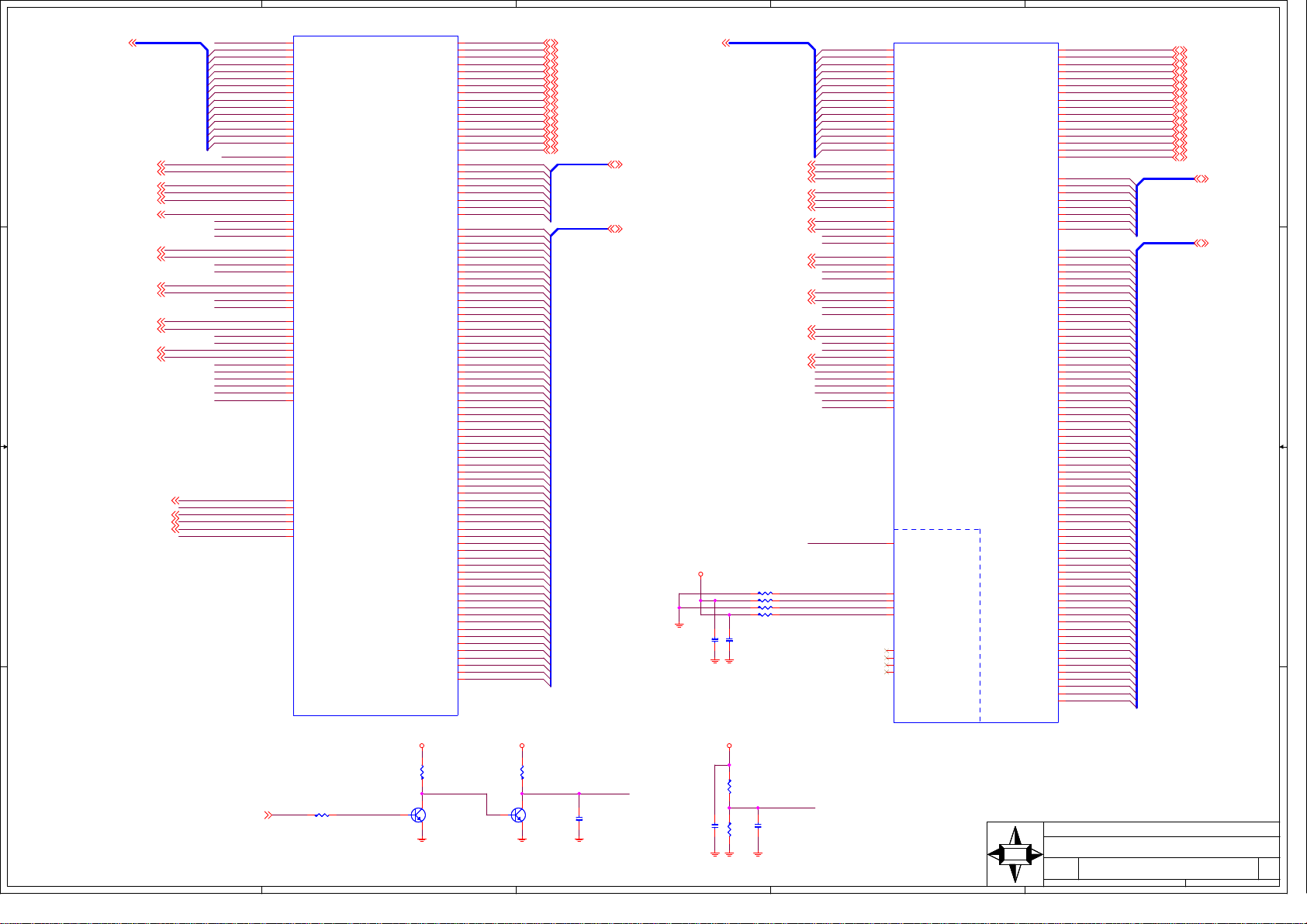

H_A#[3..35]8

D D

H_A#31

H_A#30

H_A#35

H_A#34

H_A#33

H_A#32

AJ6

AJ5

AH5

AH4

AG5

B15

AG4

A35#

A34#

A33#

A32#

A31#

A30#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

A14

C14

C15

D17

D20

G22

H_D#52

H_D#51

H_D#50

H_D#49

H_D#48

H_D#47

U1A

U1A

R12 X_0/4R12 X_0/4

R387

R387

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

PECI

VTIN1

GNDHM

H_TRMTRIP#

H_PROCHOT#

H_IGNNE#

ICH_H_SMI#

H_A20M#

H_TESTHI13

H_DBI#[0..3]8

H_IERR#6

H_FERR#13

H_STPCLK#13

H_INIT#13

H_DBSY#8

H_DRDY#8

H_TRDY#8

H_ADS#8

C C

H_CPUSLP#13

PM_SLP_N9,14

B B

A A

VTT_OUT_RIGHT

H_D#[0..63]8

H_LOCK#8

H_BNR#8

H_HIT#8

H_HITM#8

H_BPRI#8

H_DEFER#8

GNDHM17

H_TRMTRIP#13

H_PROCHOT#6

H_IGNNE#13

ICH_H_SMI#13

H_A20M#13

R11 X_0/4R11 X_0/4

H_BPM#1

Kentsfield

CPU_BSEL016

CPU_BSEL116

CPU_BSEL216

H_PWRGD6,13

H_CPURST#6,7,8

PECI17

VTIN117

R104 0/4R104 0/4

X_1KR0402

X_1KR0402

R19 51R0402R19 51R0402

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

G5

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

PECI

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

H_D#53

4

CPU SIGNAL BLOCK PULL HIGHT PULL DOWN

H_DBR#

H_A#29

AG6

D22

H_D#46

H_A#28

A29#

D46#

H_D#45

AF4

E22

H_A#27

A28#

D45#

H_D#44

AF5

G21

H_A#26

A27#

D44#

H_D#43

AB4

F21

H_A#25

A26#

D43#

H_D#42

AC5

E21

H_A#24

A25#

D42#

H_D#41

AB5

F20

H_A#23

A24#

D41#

H_D#40

AA5

E19

H_A#22

AD6

A23#

D40#

E18

H_D#39

H_A#21

A22#

D39#

H_D#38

H_A#20

AA4

A21#

D38#

F18

H_D#37

H_DBR#7,14,27

H_A#18

H_A#17

H_A#19

AB6

A20#Y4A19#Y6A18#W6A17#

D37#

D36#

D35#

F17

E16

G17

G18

H_D#34

H_D#35

H_D#36

H_A#16

H_A#15

H_A#13

H_A#14

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D34#

D33#

D32#

D31#

E15

G16

G15

H_D#30

H_D#31

H_D#32

H_D#33

H_A#12

D30#

D29#

F15

G14

H_D#29

H_A#8

H_A#10

H_A#11

H_A#9

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D28#

D27#

D26#

F14

E13

D13

G13

H_D#25

H_D#26

H_D#27

H_D#28

R13 X_0/4R13 X_0/4

H_A#5

H_A#6

H_A#7

H_A#4

D25#

D24#

D23#

D22#

D21#

F12

F11

E10

D10

H_D#21

H_D#22

H_D#23

H_D#24

H_A#3

AC2

AN3

L5

DBR#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

AN5

AN4

VSS_SENSE

VCC_SENSE

VCC_MB_REGULATION

D14#

D11

C12

H_D#13

H_D#14

H_D#15

AN6

AJ3

AK3

ITP_CLK1

ITP_CLK0

VSS_MB_REGULATION

D13#

D12#D8D11#

D10#

D9#

B12

B10

A11

C11

H_D#9

H_D#10

H_D#11

H_D#12

3

EC7

EC7

X_10U/10V/1206/X5R

X_10U/10V/1206/X5R

VID3

VID4

VID5

VID7

VID6

AM7

AM5

AL4

AK4

AL6

VID6

VID5

VID4

RSVD/VID7

FC5/CPU_GTLREF2

RSVD/CPU_GTLREF3

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A10

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

VCC_SENSE

VSS_SENSE

CK_CPUDUG# 7

CK_CPUDUG 7

VID[0..7] 31

VID2

VID1

VID0

AM3

AL5

AM2

VID3

VID2

VID1

VID0

VID_SELECT

GTLREF0

GTLREF1

GTLREF_SEL

GTLREF2

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD#G6

BCLK1#

BCLK0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_TH-2

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_TH-2

B4

H_D#0

H_D#1

H_D#2

H_D#3

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

DP3#

DP2#

DP1#

DP0#

AN7

H1

H2

H29

E24

F2

G10

AG3

AF2

AG2

AD2

AJ1

AJ2

J6

K6

M6

J5

K4

W2

P1

H5

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

G6

G28

F28

A3

F5

B3

U3

U2

F3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

V_FSB_VTT

VCC_SENSE 31

VSS_SENSE 31

R1

R1

680R0402-RH

680R0402-RH

CPU_GTLREF0

CPU_GTLREF1

GTLREF_SEL

MCH_GTLREF_CPU

CPU_GTLREF2

CPU_GTLREF3

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI8

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

FORCEPH

RSVD_G6

H_RS#2

H_RS#1

H_RS#0

TEST-U3

TEST-U2

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TEST-J17

TEST-H16

TEST-H15

TEST-J16

R633 0/4R633 0/4

R16 49.9R1%0402R16 49.9R1%0402

R17 49.9R1%0402R17 49.9R1%0402

VID_SEL 31

CPU_GTLREF0 6

CPU_GTLREF1 6

MCH_GTLREF_CPU 8

CPU_GTLREF2 6

CPU_GTLREF3 6

H_BPM#5 7

H_BPM#4 7

H_BPM#3 7

H_BPM#2 7

H_BPM#1 7

H_BPM#0 7

H_REQ#[0..4] 8

H_TESTHI12 7

R2 X_0/4R2 X_0/4

R3 X_0/4R3 X_0/4

Kentsfield

R4 51R0402R4 51R0402

R5 51R0402R5 51R0402

R6 X_130R1%0402R6 X_130R1%0402

R7 X_51R0402R7 X_51R0402

CK_H_CPU#

CK_H_CPU

CK_H_CPU# 16

CK_H_CPU 16

H_RS#[0..2] 8

H_BR#0 6,8

H_ADSTB#1 8

H_ADSTB#0 8

H_DSTBP#3 8

H_DSTBP#2 8

H_DSTBP#1 8

H_DSTBP#0 8

H_DSTBN#3 8

H_DSTBN#2 8

H_DSTBN#1 8

H_DSTBN#0 8

H_NMI 13

H_INTR 13

2

H_BPM#2H_TESTHI9

H_BPM#3

V_FSB_VTT

VTT_OUT_RIGHT

VTT_OUT_LEFT

H_COMP5_R 9,14

VTT_OUT_LEFT 6

C5

C5

0.1u/16V/4

0.1u/16V/4

V_FSB_VTT

H_TRST#7

H_TDO7

H_TCK7

H_TDI7

H_TMS7

CK_H_CPU#

CK_H_CPU

H_COMP4

H_COMP1

H_COMP3

VID5

VID4

VID2

VID0

VID7

VID3

VID6

VID1

H_BPM#1

H_BPM#0

H_BPM#5

H_TRST#

H_BPM#3

H_TDO

H_BPM#4

H_TCK

H_TDI

H_BPM#2

H_TMS

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI13

H_TESTHI1

H_TESTHI8

R8 X_0/4R8 X_0/4

R9 X_0/4R9 X_0/4

R207 X_49.9R1%0402R207 X_49.9R1%0402

R237 X_49.9R1%0402R237 X_49.9R1%0402

R21 49.9R1%0402R21 49.9R1%0402

R22 49.9R1%0402R22 49.9R1%0402

1

RN1

RN1

8P4R-680R0402-RH

8P4R-680R0402-RH

1

2

3

4

5

6

7

8

RN2

RN2

8P4R-680R0402-RH

8P4R-680R0402-RH

1

2

3

4

5

6

7

8

RN3

RN3

8P4R-51R0402

8P4R-51R0402

1

2

3

4

5

6

7

8

RN4

RN4

8P4R-51R0402

8P4R-51R0402

1

2

3

4

5

6

7

8

RN5

RN5

8P4R-51R0402

8P4R-51R0402

1

2

3

4

5

6

7

8

RN6 8P4R-51R0402RN6 8P4R-51R0402

1

2

3

4

5

6

7

8

RN14

RN14

1

2

3

4

5

6

7

8

8P4R-51R0402

8P4R-51R0402

VTT_OUT_RIGHT 6,7

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_OUT_LEFT

C4

C4

0.1u/16V/4

0.1u/16V/4

CK_CPUDUG# 7

CK_CPUDUG 7

VTT_OUT_LEFTH_COMP5

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7565

MS-7565

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

Date:

5

4

3

2

Wednesday, November 05, 2008

MS-7565

LGA775 - Signal

LGA775 - Signal

LGA775 - Signal

1

536

536

536

Sheet of

Sheet of

Sheet of

0B

0B

0B

5

VCCP

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

U1B

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

U1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y30

Y29

Y28

Y27

Y26

Y25

Y24

Y23

W30

W29

W28

W27

W26

W25

W24

W23

VCCP

D D

C C

AG8

VCC

AG9

VCC

VCCU8VCCV8VCC

AH11

VCC

VCC

U30

AH12

VCC

VCC

U29

AH14

VCC

VCC

U28

AH15

VCC

VCC

U27

4

AH18

U26

VCC

VCC

AH19

VCC

VCC

U25

AH21

VCC

VCC

U24

AH22

VCC

U23

AH25

VCC

VCCT8VCC

AH26

VCC

VCC

T30

AH27

VCC

VCC

T29

AH28

VCC

VCC

T28

AH29

VCC

VCC

T27

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

3

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCN8VCCP8VCCR8VCC

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

T23

N29

N30

N23

N24

N25

N26

N27

N28

M24

M25

M26

M27

M28

M29

M30

K27

K28

K29

K30

M23

K26

K25

K24

K23

J30

VCC

VCC

2

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCA

VSSA

VCCPLL

VCC-IOPLL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTTPWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

RSVD#F29

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J10

J11

J12

AN8

AN9

AN25

AN26

AN29

AN30

H_VCCA

A23

H_VSSA

B23

H_VCCPLL

D23

H_VCCA

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

VTT_SEL

F27

F29

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_TH-2

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_TH-2

H_VCCPLL 11

V_FSB_VTT

C10u10Y0805

C10u10Y0805

CAPS FOR FSB GENERIC

VTT_SEL 28

1

V_FSB_VTT

C6

C6

C7

C10u10Y0805

C7

C10u10Y0805

Follow Intel suggestion document to set CPU_GTLREF[3:0] to 63.5%.

* Use 57.6 Ohm 1% resistor over 100 Ohm 1% resistor.

* Divider could also be 115 Ohm 1% resistor over 200 Ohm 1% resistor.

B B

R27

R26

R25

R24

R24

115R/1%

VTT_OUT_RIGHT

VTT_OUT_RIGHT

A A

115R/1%

C9

C9

X_C10u6.3X51206-RH

X_C10u6.3X51206-RH

R32

R32

115R/1%

115R/1%

VTT_OUT_RIGHT5,7

5

GTL_REF0 VTT_OUT_LEFT

R28

R28

200R1%

200R1%

GTL_REF1

R34

R34

200R1%

200R1%

VTT_OUT_LEFT5

R25

10R1%0402

10R1%0402

C10

C10

1u/16V/6

1u/16V/6

R33

R33

10R1%0402

10R1%0402

C20

C20

1u/16V/6

1u/16V/6

CPU_GTLREF0 5

C11

C11

C220p50N0402

C220p50N0402

CPU_GTLREF1 5

C21

C21

C220p50N0402

C220p50N0402

V_FSB_VTT

PLACE AT CPU END OF ROUTE

VTT_OUT_RIGHT H_PROCHOT#

VTT_OUT_LEFT

R36 130R1%0402R36 130R1%0402

R37 62R0402R37 62R0402

R38 62R0402R38 62R0402

R40 X_100/4R40 X_100/4

R42 62R0402R42 62R0402

H_IERR#

H_CPURST#

H_PWRGD

H_BR#0

4

R26

115R/1%

115R/1%

R30

R30

115R/1%

115R/1%

H_PROCHOT# 5

H_IERR# 5

H_CPURST# 5,7,8

H_PWRGD 5,13

H_BR#0 5,8

GTL_REF3

R29

R29

200R1%

200R1%

GTL_REF2

R35

R35

200R1%

200R1%

R27

10R1%0402

10R1%0402

C12

C12

1u/16V/6

1u/16V/6

R31

R31

10R1%0402

10R1%0402

C22

C22

1u/16V/6

1u/16V/6

CPU_GTLREF2 5

C13

C13

C220p50N0402

C220p50N0402

CPU_GTLREF3 5

C23

C23

C220p50N0402

C220p50N0402

3

*PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

*TRACE WIDTH TO CAPS MUST BE NO SMALLER THAN 12MILS

V_FSB_VTT V_1P5_CORE

L1 X_10u100mA_0805-RHL1 X_10u100mA_0805-RH

21

CP2CP2

C14

C14

1u/16V/6

1u/16V/6

C15

C15

C10u10Y0805

C10u10Y0805

H_VCCA

C16

C16

X_10u/10V/8

X_10u/10V/8

H_VSSA

CP1CP1

H_VCCPLL

C17

C17

X_1u/16V/6

X_1u/16V/6

C0.01u16X0402

C0.01u16X0402

VTT_PWRGOOD

VTT_OUT_RIGHT

R39

R39

680R0402-RH

680R0402-RH

VTT_PWG

VID_GD#28,31

R43 1KR0402R43 1KR0402

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

CE

B

Q2

Q2

MSI

MSI

MSI

2

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7565

MS-7565

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

LGA775 - Power

LGA775 - Power

LGA775 - Power

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

MS-7565

1

C18

C18

Sheet of

Sheet of

Sheet of

C19

C19

C10u10Y0805

C10u10Y0805

0B

0B

636

636

636

0B

5

U1C

U1C

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

1122334

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

4

A12

D D

C C

B B

A15

A18

A21

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

AE29

AE30

AE5

AE7

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF3

AF30

AF6

AF7

A2

A6

A9

VSS

AG10

VSS

AG13

VSS

AG16

VSS

AG17

VSS

AG20

VSS

AG23

V30

VSS

AG24

VSSV3VSS

VSS

AG7

V29

AH1

VSS

V28

VSS

VSS

AH10

V27

VSS

VSS

AH13

V26

VSS

VSS

AH16

V25

VSS

VSS

AH17

V24

VSS

VSS

AH20

V23

VSS

VSS

AH23

4

U7

VSS

VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

AH3

AH6

AH7

AH24

3

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

R30

R29

R28

R27

R26

R25

R24

R23

P30

P29

P28

P27

P26

P25

P24

P23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AJ10

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

VSS

AK28

VSS

AK29

VSS

AK30

AK5

VSS

AK7

VSS

VSS

AL10

L30

VSS

AL13

VSSL3VSS

VSS

AL16

L29

VSS

AL17

L28

VSS

VSS

AL20

L27

VSS

VSS

AL23

L26

VSS

VSS

AL24

L25

VSS

VSS

AL27

L24

VSS

VSS

AL28

L23

AL7

VSS

VSS

VSSK7VSS

VSS

AM1

K2

K5

VSS

VSS

VSS

AM10

AM13

AM16

H28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AN1

AN2

AM4

AN10

AN13

AN16

AN17

AN20

AN23

AN24

AM17

AM20

AM23

AM24

AM27

AM28

AN27

VSS

VSS

H17

VSS

VSS

AN28

H14

VSS

VSSB1VSS

2

F7

H10

H11

H12

H13

VSS

VSS

VSS

VSS

VSS

Y3

COMP6

AE3

COMP7

B13

AE4

RSVD#AE4

D1

RSVD#D1

D14

RSVD#D14

E5

RSVD#E5

E6

RSVD#E6

E7

RSVD#E7

E23

RSVD#E23

F23

RSVD#F23

AL3

RSVD

J3

RSVD#J3

N4

RSVD#N4

P5

RSVD#P5

AC4

F6

IMPSEL#

V1

MSID1

W1

MSID0

U1

FC28

G1

FC27

E29

FC26

A24

FC23

F4

VSS

F22

VSS

F19

VSS

F16

VSS

F13

VSS

F10

VSS

E8

VSS

E28

VSS

E27

VSS

E26

VSS

E25

VSS

E20

VSS

E2

VSS

E17

VSS

E14

VSS

E11

VSS

D9

VSS

D6

VSS

D5

VSS

D3

VSS

D24

VSS

D21

VSS

D18

VSS

D15

VSS

D12

VSS

C7

VSS

C4

VSS

C24

VSS

C22

VSS

C19

VSS

C16

VSS

C13

VSS

C10

VSS

B8

VSS

B5

VSS

VSS

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_TH-2

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_TH-2

B24

B11

B14

VSS

B17

RSVD/COMP8

RSVD#AC4

VSS

VSS

B20

H_COMP6

H_COMP7

H_COMP8

MSID1

MSID0

FC28

FC27

R44 X_49.9R1%0402R44 X_49.9R1%0402

R45 X_49.9R1%0402R45 X_49.9R1%0402

R46 24.9R1%0402R46 24.9R1%0402

R143 49.9R1%0402R143 49.9R1%0402

R146 49.9R1%0402R146 49.9R1%0402

R144 X_49.9R1%0402R144 X_49.9R1%0402

R50 X_0/4R50 X_0/4

R51 X_0/4R51 X_0/4

R180 X_0/4R180 X_0/4

R52 X_1KR0402R52 X_1KR0402

05 Per FMB

05 Value FMB

H_TESTHI12

H_BPM#0

1

VTT_OUT_RIGHT 5,6

FC28

R97 X_0/4R97 X_0/4

FC27

R120 X_0/4R120 X_0/4

H_TESTHI12 5

H_BPM#0 5

Kentsfield

MSID1 MSID0

0

0

0

1

JDP_DEBUG

H_BPM#05

H_BPM#25

H_BPM#35

H_BPM#45

H_BPM#55

A A

5

4

CK_CPUDUG5

CK_CPUDUG#5

SMBDATA_ISO14,16,19,23,24

VTT_OUT_RIGHT5,6

H_BPM#0 H_TDO

H_BPM#1 H_TDI

H_BPM#2

H_BPM#3

H_BPM#4

H_BPM#5

CK_CPUDUG

CK_CPUDUG#

SMBCLK_ISO14,16,19,23,24

JDP_DEBUG

9

BPM0*

7

BPM1*

6

BPM2*

4

BPM3*

3

BPM4*

1

BPM5*

16

100M_CLK_DP

18

100M_CLK_DN

13

XDP_H_CLK_DP

15

XDP_H_CLK_DN

22

SCL

24

SDA

14

VTT

28

NC

3

TRST

PWRGOOD

RESET*

DBR*

TESTIN*

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

X_JCPDBG1

X_JCPDBG1

TDO

TDI

TMS

TCK

23

29

H_TMS

31

H_TCK

30

H_TRST#

25

R537 X_1.5KR1%R537 X_1.5KR1%

10

R538 X_1KRR538 X_1KR

19

21

R539 X_62/6R539 X_62/6

12

2

5

8

11

17

20

26

27

H_TDO 5

H_TDI 5H_BPM#15

H_TMS 5

H_TCK 5

H_TRST# 5

FP_RST#

VTT_OUT_RIGHT 5,6

H_CPURST# 5,6,8

FP_RST# 5,14,27

VTT_OUT_RIGHT 5,6

2

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7565

MS-7565

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

LGA775 - GND

LGA775 - GND

LGA775 - GND

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

MS-7565

1

736

736

736

Sheet of

Sheet of

Sheet of

0B

0B

0B

5

?

?

EAGLELAKE_DDR2

NB1A

NB1A

H_A#3

H_A#[3..35]5

D D

H_REQ#[0..4]5

C C

H_ADSTB#05

H_ADSTB#15

H_DSTBP#05

H_DSTBN#05

H_DSTBP#15

H_DSTBN#15

H_DSTBP#25

H_DSTBN#25

H_DSTBP#35

H_DSTBN#35

H_DBI#[0..3]5

H_ADS#5

H_TRDY#5

H_DRDY#5

H_DEFER#5

H_HITM#5

H_HIT#5

H_LOCK#5

B B

H_RS#[0..2]5

H_BR#05,6

H_BNR#5

H_BPRI#5

H_DBSY#5

H_CPURST#5,6,7

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_RS#0

H_RS#1

H_RS#2

H39

N39

N35

N37

N40

M45

R35

R36

R34

R37

R39

U38

U34

U40

U35

AA35

U37

AA37

AA36

G38

C43

G39

C39

C32

D32

D30

G44

H45

H40

H37

H42

G43

G42

D27

N25

L36

L37

J38

F40

L38

L43

J41

T36

T37

T34

Y36

Y37

Y34

Y38

K35

J39

J40

T39

B39

K31

J31

J25

K25

B40

F33

F26

J42

L40

J43

K44

L42

J44

L44

FSB_AB_3

FSB_AB_4

FSB_AB_5

FSB_AB_6

FSB_AB_7

FSB_AB_8

FSB_AB_9

FSB_AB_10

FSB_AB_11

FSB_AB_12

FSB_AB_13

FSB_AB_14

FSB_AB_15

FSB_AB_16

FSB_AB_17

FSB_AB_18

FSB_AB_19

FSB_AB_20

FSB_AB_21

FSB_AB_22

FSB_AB_23

FSB_AB_24

FSB_AB_25

FSB_AB_26

FSB_AB_27

FSB_AB_28

FSB_AB_29

FSB_AB_30

FSB_AB_31

FSB_AB_32

FSB_AB_33

FSB_AB_34

FSB_AB_35

FSB_REQB_0

FSB_REQB_1

FSB_REQB_2

FSB_REQB_3

FSB_REQB_4

FSB_ADSTBB_0

FSB_ADSTBB_1

FSB_DSTBPB_0

FSB_DSTBNB_0

FSB_DSTBPB_1

FSB_DSTBNB_1

FSB_DSTBPB_2

FSB_DSTBNB_2

FSB_DSTBPB_3

FSB_DSTBNB_3

FSB_DINVB_0

FSB_DINVB_1

FSB_DINVB_2

FSB_DINVB_3

FSB_ADSB

FSB_TRDYB

FSB_DRDYB

FSB_DEFERB

FSB_HITMB

FSB_HITB

FSB_LOCKB

FSB_BREQ0B

FSB_BNRB

FSB_BPRIB

FSB_DBSYB

FSB_RSB_0

FSB_RSB_1

FSB_RSB_2

FSB_CPURSTB

RSVD_05

ELK_CRB

ELK_CRB

EAGLELAKE_DDR2

SYM_REV = 1.5

SYM_REV = 1.5

1 OF 7

1 OF 7

FSB

FSB

FSB_ACCVREF

FSB_DB_10

FSB_DB_11

FSB_DB_12

FSB_DB_13

FSB_DB_14

FSB_DB_15

FSB_DB_16

FSB_DB_17

FSB_DB_18

FSB_DB_19

FSB_DB_20

FSB_DB_21

FSB_DB_22

FSB_DB_23

FSB_DB_24

FSB_DB_25

FSB_DB_26

FSB_DB_27

FSB_DB_28

FSB_DB_29

FSB_DB_30

FSB_DB_31

FSB_DB_32

FSB_DB_33

FSB_DB_34

FSB_DB_35

FSB_DB_36

FSB_DB_37

FSB_DB_38

FSB_DB_39

FSB_DB_40

FSB_DB_41

FSB_DB_42

FSB_DB_43

FSB_DB_44

FSB_DB_45

FSB_DB_46

FSB_DB_47

FSB_DB_48

FSB_DB_49

FSB_DB_50

FSB_DB_51

FSB_DB_52

FSB_DB_53

FSB_DB_54

FSB_DB_55

FSB_DB_56

FSB_DB_57

FSB_DB_58

FSB_DB_59

FSB_DB_60

FSB_DB_61

FSB_DB_62

FSB_DB_63

FSB_SWING

FSB_RCOMP

FSB_DVREF

HPL_CLKINP

HPL_CLKINN

FSB_DB_0

FSB_DB_1

FSB_DB_2

FSB_DB_3

FSB_DB_4

FSB_DB_5

FSB_DB_6

FSB_DB_7

FSB_DB_8

FSB_DB_9

4

F44

C44

D44

C41

E43

B43

D40

B42

B38

F38

A38

B37

D38

C37

D37

B36

E37

J35

H35

F37

G37

J33

L33

G33

L31

M31

M30

J30

G31

K30

M29

G30

J29

F29

H29

L25

K26

L29

J26

M26

H26

F25

F24

G25

H24

L24

J24

N24

C28

B31

F35

C35

B35

D35

D31

A34

B32

F31

D28

A29

C30

B30

E27

B28

B24

A23

C22

B23

CK_H_MCH

P29

CK_H_MCH#

P30

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

HXSWING

HXRCOMP

MCH_GTLREF

H_D#[0..63] 5

R677

R677

16.5R1%/2

16.5R1%/2

CK_H_MCH 16

CK_H_MCH# 16

3

EXP_A_RXP_023

EXP_A_RXN_023

EXP_A_RXP_123

EXP_A_RXN_123

EXP_A_RXP_223

EXP_A_RXN_223

EXP_A_RXP_332

EXP_A_RXN_332

EXP_A_RXP_423

EXP_A_RXN_423

EXP_A_RXP_523

EXP_A_RXN_523

EXP_A_RXP_623

EXP_A_RXN_623

EXP_A_RXP_723

EXP_A_RXN_723

EXP_A_RXP_823

EXP_A_RXN_823

EXP_A_RXP_923

EXP_A_RXN_923

EXP_A_RXP_1023

EXP_A_RXN_1023

EXP_A_RXP_1123

EXP_A_RXN_1123

EXP_A_RXP_1223

EXP_A_RXN_1223

EXP_A_RXP_1323

EXP_A_RXN_1323

EXP_A_RXP_1423

EXP_A_RXN_1423

EXP_A_RXP_1523

EXP_A_RXN_1523

DMI_ITP_MRP_013

DMI_ITN_MRN_013

DMI_ITP_MRP_113

DMI_ITN_MRN_113

DMI_ITP_MRP_213

DMI_ITN_MRN_213

DMI_ITP_MRP_313

DMI_ITN_MRN_313

CK_PE_100M_MCH16

CK_PE_100M_MCH#16

SDVOCTRLDATA23

SDVOCTRLCLK23

HXSWING 10 mil with,7 msil Space"

HXSWING S/B 1/4*VTT +/- 2%

V_FSB_VTT

R684

R684

301R1%0402

301R1%0402

R687

R687

100R1%0402

100R1%0402

V_FSB_VTT

R679

R679

57.6R1%0402-RH

57.6R1%0402-RH

R683

R683

100R1%0402

100R1%0402

EXP_A_RXP_0

EXP_A_RXN_0

EXP_A_RXP_1

EXP_A_RXN_1

EXP_A_RXP_2

EXP_A_RXN_2

EXP_A_RXP_3

EXP_A_RXN_3

EXP_A_RXP_4

EXP_A_RXN_4

EXP_A_RXP_5

EXP_A_RXN_5

EXP_A_RXP_6

EXP_A_RXN_6

EXP_A_RXP_7

EXP_A_RXN_7

EXP_A_RXP_8

EXP_A_RXN_8

EXP_A_RXP_9

EXP_A_RXN_9

EXP_A_RXP_10

EXP_A_RXN_10

EXP_A_RXP_11

EXP_A_RXN_11

EXP_A_RXP_12

EXP_A_RXN_12

EXP_A_RXP_13

EXP_A_RXN_13

EXP_A_RXP_14

EXP_A_RXN_14

EXP_A_RXP_15

EXP_A_RXN_15

DMI_ITP_MRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_1

DMI_ITP_MRP_2

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

CK_PE_100M_MCH

CK_PE_100M_MCH#

SDVOCTRLDATA

SDVOCTRLCLK

V_FSB_VTT

R686

R686

49.9R1%0402

49.9R1%0402

HXSWING

C736

C736

C0.1U/10X/2

C0.1U/10X/2

*GTLREF VOLTAGE SHOULD BE

0.635*VTT

MCH_GTLREF_CPU

R681

R681

49.9R1%0402

49.9R1%0402

C733

C733

1u/16V/6

1u/16V/6

N10

R10

U10

AA9

AA10

AA7

AA6

AB10

AB9

AB3

AA2

AD10

AD11

AD7

AD8

AE9

AE10

AE6

AE7

AF9

AF8

G13

AB13

AD13

MCH_GTLREF

C734

C734

C220p50N0402

C220p50N0402

NB1B

NB1B

F6

PEG_RXP_0

G7

PEG_RXN_0

H6

PEG_RXP_1

G4

PEG_RXN_1

J6

PEG_RXP_2

J7

PEG_RXN_2

L6

PEG_RXP_3

L7

PEG_RXN_3

N9

PEG_RXP_4

PEG_RXN_4

N7

PEG_RXP_5

N6

PEG_RXN_5

R7

PEG_RXP_6

R6

PEG_RXN_6

R9

PEG_RXP_7

PEG_RXN_7

PEG_RXP_8

U9

PEG_RXN_8

U6

PEG_RXP_9

U7

PEG_RXN_9

PEG_RXP_10

PEG_RXN_10

R4

PEG_RXP_11

P4

PEG_RXN_11

PEG_RXP_12

PEG_RXN_12

PEG_RXP_13

PEG_RXN_13

PEG_RXP_14

PEG_RXN_14

PEG_RXP_15

PEG_RXN_15

DMI_RXP_0

DMI_RXN_0

DMI_RXP_1

DMI_RXN_1

DMI_RXP_2

DMI_RXN_2

DMI_RXP_3

DMI_RXN_3

D9

EXP_CLKP

E9

EXP_CLKN

J13

SDVO_CTRLDATA

SDVO_CTRLCLK

RSVD_23

RSVD_22

ELK_CRB

ELK_CRB

MCH_GTLREF_CPU 5

EAGLELAKE_DDR2

EAGLELAKE_DDR2

SYM_REV = 1.5

SYM_REV = 1.5

?

?

2 OF 7

2 OF 7

PCIE

PCIE

DMI

DMI

2

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

PEG_TXN_2

PEG_TXP_3

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

PEG_TXP_10

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

EXP_RCOMPO

EXP_COMPI

EXP_ICOMPO

EXP_RBIAS

C11

B11

A10

B9

C9

D8

B8

C7

B7

B6

B3

B4

D2

C2

H2

G2

J2

K2

K1

L2

P2

M2

T2

R1

U2

V2

W4

V3

AA4

Y4

AC1

AB2

C363 0.1u/25v/Y5/4C363 0.1u/25v/Y5/4

AC2

C365 0.1u/25v/Y5/4C365 0.1u/25v/Y5/4

AD2

C364 0.1u/25v/Y5/4C364 0.1u/25v/Y5/4

AD4

C366 0.1u/25v/Y5/4C366 0.1u/25v/Y5/4

AE4

C369 0.1u/25v/Y5/4C369 0.1u/25v/Y5/4

AE2

C372 0.1u/25v/Y5/4C372 0.1u/25v/Y5/4

AF2

C368 0.1u/25v/Y5/4C368 0.1u/25v/Y5/4

AF4

C370 0.1u/25v/Y5/4C370 0.1u/25v/Y5/4

AG4

GRCOMP

Y7

Y8

Y6

AG1

?

?

V_1P125_CORE

EXP_A_TXP_0

EXP_A_TXN_0

EXP_A_TXP_1

EXP_A_TXN_1

EXP_A_TXP_2

EXP_A_TXN_2

EXP_A_TXP_3

EXP_A_TXN_3

EXP_A_TXP_4

EXP_A_TXN_4

EXP_A_TXP_5

EXP_A_TXN_5

EXP_A_TXP_6

EXP_A_TXN_6

EXP_A_TXP_7

EXP_A_TXN_7

EXP_A_TXP_8

EXP_A_TXN_8

EXP_A_TXP_9

EXP_A_TXN_9

EXP_A_TXP_10

EXP_A_TXN_10

EXP_A_TXP_11

EXP_A_TXN_11

EXP_A_TXP_12

EXP_A_TXN_12

EXP_A_TXP_13

EXP_A_TXN_13

EXP_A_TXP_14

EXP_A_TXN_14

EXP_A_TXP_15

EXP_A_TXN_15

R662 49.9R1%0402R662 49.9R1%0402

R663 X_750R1%0402R663 X_750R1%0402

R664 750R1%0402R664 750R1%0402

C732 C0.1U/10X/2C732 C0.1U/10X/2

DMI_MTP_IRP_0

DMI_MTN_IRN_0

DMI_MTP_IRP_1

DMI_MTN_IRN_1

DMI_MTP_IRP_2

DMI_MTN_IRN_2

DMI_MTP_IRP_3

DMI_MTN_IRN_3

V_1P125_CORE

V_1P125_CORE

1

EXP_A_TXP_0 32

EXP_A_TXN_0 32

EXP_A_TXP_1 32

EXP_A_TXN_1 32

EXP_A_TXP_2 32

EXP_A_TXN_2 32

EXP_A_TXP_3 32

EXP_A_TXN_3 32

EXP_A_TXP_4 23

EXP_A_TXN_4 23

EXP_A_TXP_5 23

EXP_A_TXN_5 23

EXP_A_TXP_6 23

EXP_A_TXN_6 23

EXP_A_TXP_7 23

EXP_A_TXN_7 23

EXP_A_TXP_8 23

EXP_A_TXN_8 23

EXP_A_TXP_9 23

EXP_A_TXN_9 23

EXP_A_TXP_10 23

EXP_A_TXN_10 23

EXP_A_TXP_11 23

EXP_A_TXN_11 23

EXP_A_TXP_12 23

EXP_A_TXN_12 23

EXP_A_TXP_13 23

EXP_A_TXN_13 23

EXP_A_TXP_14 23

EXP_A_TXN_14 23

EXP_A_TXP_15 23

EXP_A_TXN_15 23

DMI_MTP_IRP_0 13

DMI_MTN_IRN_0 13

DMI_MTP_IRP_1 13

DMI_MTN_IRN_1 13

DMI_MTP_IRP_2 13

DMI_MTN_IRN_2 13

DMI_MTP_IRP_3 13

DMI_MTN_IRN_3 13

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7565

MS-7565

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Intel Eaglelake - FSB, PCIE, DMI, VGA, MSIC

Intel Eaglelake - FSB, PCIE, DMI, VGA, MSIC

Intel Eaglelake - FSB, PCIE, DMI, VGA, MSIC

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

Date:

5

4

3

2

Wednesday, November 05, 2008

MS-7565

1

836

836

836

Sheet of

Sheet of

Sheet of

0B

0B

0B

5

RN78

RN78

8P4R-10KR0402

8P4R-10KR0402

MCH_BS1

1

D D

H_BSL116

H_BSL216

H_BSL016

DEMO BOARD CHANGE

V_1P125_CORE

EXP_EN_HDR23

C C

CL_VREF_MCH = 0.35V

Close to GMCH

V_1P125_CORE

R680

R680

1K/4

1K/4

R685

R685

464R1%0402

464R1%0402

B B

NB PIN:L17

TPM Enable:

0=Enable iTPM

1=Disable iTPM

EXP_EN_HDR EXP_EN

CHIP_PWGD14,28,32

CL_VREF_MCH

C735

C735

0.1u/25v/Y5/4

0.1u/25v/Y5/4

3

5

7

R667 X_1KR0402R667 X_1KR0402

R668 1KR0402R668 1KR0402

R669 0/4R669 0/4

R670 X_1KR0402R670 X_1KR0402

R671 X_1KR0402R671 X_1KR0402

2

4

MCH_BS2

6

MCH_BS0

8

CL_VREF_MCH

CL_RST#

CHIP_PWGD

4

?

?

EAGLELAKE_DDR2

NB1E

NB1E

MCH_BS0

F17

G16

P15

M20

N17

K16

G15

H17

M17

G20

M16

AY4

AY2

AN13

AW2

AN8

AR7

AN10

AN11

AN9

AN17

B45

AW44

AN16

AD42

W30

U32

R42

BE44

BE2

BD45

BD1

A44

AK15

B14

F15

L17

J17

J16

J15

J20

F20

ELK_CRB

ELK_CRB

BSEL0

BSEL1

BSEL2

ALLZTEST

XORTEST

RSVD_36

EXP_SLR

RSVD_17

EXP_SM

ITPM_ENB

RSVD_10

CEN

BSCANTEST

RSVD_12

RSVD_13

RSVD_14

RSVD_15

DUALX8_ENABLE

CL_DATA

CL_CLK

CL_VREF

CL_RSTB

CL_PWROK

JTAG_TDI

JTAG_TDO

JTAG_TCK

JTAG_TMS

NC_01

NC_02

NC_03

NC_04

NC_05

NC_06

NC_07

NC_08

NC_09

NC_10

NC_11

NC_12

NC_13

NC_18

NC_19

MCH_BS1 VSYNC

MCH_BS2

EXP_SLR

ITPM_EN

MCH_TCEN

EAGLELAKE_DDR2

SYM_REV = 1.5

SYM_REV = 1.5

MISC

MISC

5 OF 7

5 OF 7

CRT_DDC_DATA

VGA

VGA

CRT_DDC_CLK

DPL_REFCLKINP

DPL_REFCLKINN

DPL_REFSSCLKINP

DPL_REFSSCLKINN

DDPC_CTRLCLK

DDPC_CTRLDATA

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_IRTN

DAC_IREF

RSTINB

PWROK

ICH_SYNCB

HDA_BCLK

HDA_RSTB

HDA_SDI

HDA_SDO

HDA_SYNC

DPRSTPB

SLPB

RSVD_18

RSVD_19

RSVD_20

RSVD_21

RSVD_25

RSVD_26

RSVD_27

RSVD_28

RSVD_29

RSVD_30

RSVD_31

RSVD_32

RSVD_33

RSVD_34

RSVD_35

D14

C14

B18

D18

C18

F13

L15

M15

B15

E15

D15

G8

G9

AN6

AR4

K15

AU4

AV4

AU2

AV1

AU3

J11

F11

P43

P42

A45

B2

BE1

BE45

R15

R14

T15

T14

AB15

R32

R31

U31

U30

L11

L13

?

?

3

HSYNC

C616 X_C3.3p50N/4C616 X_C3.3p50N/4

C617 X_C3.3p50N/4C617 X_C3.3p50N/4

C615 X_C3.3p50N/4C615 X_C3.3p50N/4

DACREFSET

CHIP_PWGD

MCH_AZA_BCLK

MCH_AZA_RSTB

MCH_AZA_SDI

MCH_AZA_SDO

MCH_AZA_SYNC

H_COMP5_R

R682 0/4R682 0/4

R688 X_10K/4R688 X_10K/4

MCH_DDC_DATA 30

PM_SLP_N

VCC3

MCH_DDC_CLK 30

DDCP_CTRLCLK 23

DDCP_CTRLDATA 23

R672 1.02KR1%0402R672 1.02KR1%0402

HSYNC 30

VSYNC 30

VGA_RED 30

VGA_GREEN 30

VGA_BLUE 30

Close to GMCH within 250 mils.

CK_96M_DREF 16

CK_96M_DREF# 16

DPL_REFSSCLKIN 16

DPL_REFSSCLKIN# 16

PLTRST# 13,17,24

CHIP_PWGD 14,28,32

ICH_SYNC# 14

RN85 8P4R-0RRN85 8P4R-0R

1

3

5

7

R698 0/4R698 0/4

H_COMP5_R 5,14

PM_SLP_N 5,14

2

2

4

6

8

1

PLTRST# 13,17,24

R391

R391

1.65KR1%0402

1.65KR1%0402

CL_RST#

R378

R378

C361

C361

1KR0402

1KR0402

X_C0.01u25X0402

X_C0.01u25X0402

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7565

MS-7565

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Intel Eaglelake - FSB, PCIE, DMI, VGA, MSIC

Intel Eaglelake - FSB, PCIE, DMI, VGA, MSIC

Intel Eaglelake - FSB, PCIE, DMI, VGA, MSIC

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

Date:

5

4

3

2

Wednesday, November 05, 2008

MS-7565

1

Sheet of

Sheet of

Sheet of

936

936

936

0B

0B

0B

5

EAGLELAKE_DDR2

EAGLELAKE_DDR2

NB1C

BC41

DDR_A_MA_0

BC35

DDR_A_MA_1

BB32

DDR_A_MA_2

BC32

DDR_A_MA_3

BD32

DDR_A_MA_4

BB31

DDR_A_MA_5

AY31

DDR_A_MA_6

BA31

DDR_A_MA_7

BD31

DDR_A_MA_8

BD30

DDR_A_MA_9

AW43

DDR_A_MA_10

BC30

DDR_A_MA_11

BB30

DDR_A_MA_12

AM42

DDR_A_MA_13

BD28

DDR_A_MA_14

AW42

DDR_A_WEB

AU42

DDR_A_CASB

AV42

DDR_A_RASB

AV45

DDR_A_BS_0

AY44

DDR_A_BS_1

BC28

DDR_A_BS_2

AU43

DDR_A_CSB_0

AR40

DDR_A_CSB_1

AU44

DDR_A_CSB_2

AM43

DDR_A_CSB_3

BB27

DDR_A_CKE_0

BD27

DDR_A_CKE_1

BA27

DDR_A_CKE_2

AY26

DDR_A_CKE_3

AR42

DDR_A_ODT_0

AM44

DDR_A_ODT_1

AR44

DDR_A_ODT_2

AL40

DDR_A_ODT_3

AY37

DDR_A_CK_0

BA37

DDR_A_CKB_0

AW29

DDR_A_CK_1

AY29

DDR_A_CKB_1

AU37

DDR_A_CK_2

AV37

DDR_A_CKB_2

AU33

DDR_A_CK_3

AT33

DDR_A_CKB_3

AT30

DDR_A_CK_4

AR30

DDR_A_CKB_4

AW38

DDR_A_CK_5

AY38

DDR_A_CKB_5

BC24

DDR3_DRAMRSTB

AR6

DDR3_DRAM_PWROK

AR43

DDR3_A_CSB1

BB40

DDR3_A_MA0

AT44

DDR3_A_WEB

AV40

DDR3_B_ODT3

ELK_CRB

ELK_CRB

NB1C

DDR_A

DDR_A

CAS_A#19

RAS_A#19

SBS_A019

SBS_A119

SBS_A219

SCS_A#019

SCKE_A019

SCKE_A119

ODT_A019

ODT_A119

P_DDR0_A19

N_DDR0_A19

P_DDR2_A19

N_DDR2_A19

DDR3_SCS_A#119

DDR3_MAA_A019

DDR3_WE_A#19

DDR3_RST#19,20

MAA_A[1..14]

CAS_A#

RAS_A#

SBS_A0

SBS_A1

SBS_A2

SCS_A#0

SCKE_A0

SCKE_A1

ODT_A0

ODT_A1

P_DDR0_A

N_DDR0_A

P_DDR2_A

N_DDR2_A

MAA_A[1..14]19

D D

C C

B B

TP_MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A14

TP_WE_A#

TP_SCS_A#1

TP_SCS_A#2

TP_SCS_A#3

TP_SCKE_A2

TP_SCKE_A3

TP_ODT_A2

TP_ODT_A3

TP_P_DDR1_A

TP_N_DDR1_A

TP_P_DDR3_A

TP_N_DDR3_A

TP_P_DDR4_A

TP_N_DDR4_A

TP_P_DDR5_A

TP_N_DDR5_A

DDR3_RST#

DDR3_PWROK

DDR3_SCS_A#1

DDR3_MAA_A0

DDR3_WE_A#

TP_DDR3_B_ODT3

SYM_REV = 1.5

SYM_REV = 1.5

3 OF 7

3 OF 7

?

?

4

DDR_A_DQS_0

DDR_A_DQSB_0

DDR_A_DQS_1

DDR_A_DQSB_1

DDR_A_DQS_2

DDR_A_DQSB_2

DDR_A_DQS_3

DDR_A_DQSB_3

DDR_A_DQS_4

DDR_A_DQSB_4

DDR_A_DQS_5

DDR_A_DQSB_5

DDR_A_DQS_6

DDR_A_DQSB_6

DDR_A_DQS_7

DDR_A_DQSB_7

DDR_A_DM_0

DDR_A_DM_1

DDR_A_DM_2

DDR_A_DM_3

DDR_A_DM_4

DDR_A_DM_5

DDR_A_DM_6

DDR_A_DM_7

DDR_A_DQ_0

DDR_A_DQ_1

DDR_A_DQ_2

DDR_A_DQ_3

DDR_A_DQ_4

DDR_A_DQ_5

DDR_A_DQ_6

DDR_A_DQ_7

DDR_A_DQ_8

DDR_A_DQ_9

DDR_A_DQ_10

DDR_A_DQ_11

DDR_A_DQ_12

DDR_A_DQ_13

DDR_A_DQ_14

DDR_A_DQ_15

DDR_A_DQ_16

DDR_A_DQ_17

DDR_A_DQ_18

DDR_A_DQ_19

DDR_A_DQ_20

DDR_A_DQ_21

DDR_A_DQ_22

DDR_A_DQ_23

DDR_A_DQ_24

DDR_A_DQ_25

DDR_A_DQ_26

DDR_A_DQ_27

DDR_A_DQ_28

DDR_A_DQ_29

DDR_A_DQ_30

DDR_A_DQ_31

DDR_A_DQ_32

DDR_A_DQ_33

DDR_A_DQ_34

DDR_A_DQ_35

DDR_A_DQ_36

DDR_A_DQ_37

DDR_A_DQ_38

DDR_A_DQ_39

DDR_A_DQ_40

DDR_A_DQ_41

DDR_A_DQ_42

DDR_A_DQ_43

DDR_A_DQ_44

DDR_A_DQ_45

DDR_A_DQ_46

DDR_A_DQ_47

DDR_A_DQ_48

DDR_A_DQ_49

DDR_A_DQ_50

DDR_A_DQ_51

DDR_A_DQ_52

DDR_A_DQ_53

DDR_A_DQ_54

DDR_A_DQ_55

DDR_A_DQ_56

DDR_A_DQ_57

DDR_A_DQ_58

DDR_A_DQ_59

DDR_A_DQ_60

DDR_A_DQ_61

DDR_A_DQ_62

DDR_A_DQ_63

5VSB

BC5

BD4

BB9

BC9

BD15

BB15

AR22

AT22

AH43

AH42

AD43

AE42

Y43

Y42

T44

T43

BC3

BD9

BD14

AV22

AK42

AE45

AA45

T42

BC2

BD3

BD7

BB7

BB2

BA3

BE6

BD6

BB8

AY8

BD11

BB11

BC7

BE8

BD10

AY11

BB14

BC14

BC16

BB16

BC11

BE12

BA15

BD16

AW21

AY22

?

?

AV24

AY24

AU21

AT21

AR24

AU24

AL41

AK43

AG42

AG44

AL42

AK44

AH44

AG41

AF43

AF42

AC44

AC42

AF40

AF44

AD44

AC41

AB43

AA42

W42

W41

AB42

AB44

Y44

Y40

V42

U45

R40

P44

V44

V43

R41

R44

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

VCC_DDR

DQS_A0 19

DQS_A#0 19

DQS_A1 19

DQS_A#1 19

DQS_A2 19

DQS_A#2 19

DQS_A3 19

DQS_A#3 19

DQS_A4 19

DQS_A#4 19

DQS_A5 19

DQS_A#5 19

DQS_A6 19

DQS_A#6 19

DQS_A7 19

DQS_A#7 19

DQM_A[0..7]

DATA_A[0..63]

3

DQM_A[0..7] 19

DATA_A[0..63] 19

0.1u/25v/Y5/4

0.1u/25v/Y5/4

MAA_B[0..14]20

VCC_DDR

C739

C739

MAA_B[0..14]

R691 80.6R1%0402R691 80.6R1%0402

R692 80.6R1%0402R692 80.6R1%0402

R693 249R1%0402R693 249R1%0402

R694 80.6R1%0402R694 80.6R1%0402

C740

C740

0.1u/25v/Y5/4

0.1u/25v/Y5/4

VCC_DDR

WE_B#20

CAS_B#20

RAS_B#20

SBS_B020

SBS_B120

SBS_B220

SCS_B#020

SCS_B#120

SCKE_B020

SCKE_B120

ODT_B020

ODT_B120

P_DDR0_B20

N_DDR0_B20

P_DDR2_B20

N_DDR2_B20

SPD=249OHM

SPU=80.6OHM

RPD=80.6OHM

RPU=80.6OHM

MAA_B0

MAA_B1

MAA_B2

MAA_B3

MAA_B4

MAA_B5

MAA_B6

MAA_B7

MAA_B8

MAA_B9

MAA_B10

MAA_B11

MAA_B12

MAA_B13

MAA_B14

WE_B#

CAS_B#

RAS_B#

SBS_B0

SBS_B1

SBS_B2

SCS_B#0

SCS_B#1

TP_SCS_B#2

TP_SCS_B#3

SCKE_B0

SCKE_B1

TP_SCKE_B2

TP_SCKE_B3

ODT_B0

ODT_B1

TP_ODT_B2

TP_ODT_B3

P_DDR0_B

N_DDR0_B

TP_P_DDR1_B

TP_N_DDR1_B

P_DDR2_B

N_DDR2_B

TP_P_DDR3_B

TP_N_DDR3_B

TP_P_DDR4_B

TP_N_DDR4_B

TP_P_DDR5_B

TP_N_DDR5_B

MCH_VREF_A

SRCOMP0

SRCOMP1

SRCOMP2

SRCOMP3

BD24

BB23

BB24

BD23

BB22

BD22

BC22

BC20

BB20

BD20

BC26

BD19

BB19

BE38

BA19

BD36

BC37

BD35

BD26

BB26

BD18

BB35

BD39

BB37

BD40

BC18

AY20

BE17

BB18

BD37

BC39

BB38

BD42

AY33

AW33

AV31

AW31

AW35

AY35

AT31

AU31

AP31

AP30

AW37

AV35

BB44

AY42

BA43

BC43

BC44

AN29

AN30

AJ33

AK33

2

NB1D

NB1D

DDR_B_MA_0

DDR_B_MA_1

DDR_B_MA_2

DDR_B_MA_3

DDR_B_MA_4

DDR_B_MA_5

DDR_B_MA_6

DDR_B_MA_7

DDR_B_MA_8

DDR_B_MA_9

DDR_B_MA_10

DDR_B_MA_11

DDR_B_MA_12

DDR_B_MA_13

DDR_B_MA_14

DDR_B_WEB

DDR_B_CASB

DDR_B_RASB

DDR_B_BS_0

DDR_B_BS_1

DDR_B_BS_2

DDR_B_CSB_0

DDR_B_CSB_1

DDR_B_CSB_2

DDR_B_CSB_3

DDR_B_CKE_0

DDR_B_CKE_1

DDR_B_CKE_2

DDR_B_CKE_3

DDR_B_ODT_0

DDR_B_ODT_1

DDR_B_ODT_2

DDR_B_ODT_3

DDR_B_CK_0

DDR_B_CKB_0

DDR_B_CK_1

DDR_B_CKB_1

DDR_B_CK_2

DDR_B_CKB_2

DDR_B_CK_3

DDR_B_CKB_3

DDR_B_CK_4

DDR_B_CKB_4

DDR_B_CK_5

DDR_B_CKB_5

DDR_VREF

DDR_RPD

DDR_RPU

DDR_SPD

DDR_SPU

RSVD_01

RSVD_02

RSVD_03

RSVD_04

ELK_CRB

ELK_CRB

EAGLELAKE_DDR2

EAGLELAKE_DDR2

SYM_REV = 1.5

SYM_REV = 1.5

4 OF 7

4 OF 7

DDR_B

DDR_B

?

?

DDR_B_DQS_0

DDR_B_DQSB_0

DDR_B_DQS_1

DDR_B_DQSB_1

DDR_B_DQS_2

DDR_B_DQSB_2

DDR_B_DQS_3

DDR_B_DQSB_3

DDR_B_DQS_4

DDR_B_DQSB_4

DDR_B_DQS_5

DDR_B_DQSB_5

DDR_B_DQS_6

DDR_B_DQSB_6

DDR_B_DQS_7

DDR_B_DQSB_7

DDR_B_DM_0

DDR_B_DM_1

DDR_B_DM_2

DDR_B_DM_3

DDR_B_DM_4

DDR_B_DM_5

DDR_B_DM_6

DDR_B_DM_7

DDR_B_DQ_0

DDR_B_DQ_1

DDR_B_DQ_2

DDR_B_DQ_3

DDR_B_DQ_4

DDR_B_DQ_5

DDR_B_DQ_6

DDR_B_DQ_7

DDR_B_DQ_8

DDR_B_DQ_9

DDR_B_DQ_10

DDR_B_DQ_11

DDR_B_DQ_12

DDR_B_DQ_13

DDR_B_DQ_14

DDR_B_DQ_15

DDR_B_DQ_16

DDR_B_DQ_17

DDR_B_DQ_18

DDR_B_DQ_19

DDR_B_DQ_20

DDR_B_DQ_21

DDR_B_DQ_22

DDR_B_DQ_23

DDR_B_DQ_24

DDR_B_DQ_25

DDR_B_DQ_26

DDR_B_DQ_27

DDR_B_DQ_28

DDR_B_DQ_29

DDR_B_DQ_30

DDR_B_DQ_31

DDR_B_DQ_32

DDR_B_DQ_33

DDR_B_DQ_34

DDR_B_DQ_35

DDR_B_DQ_36

DDR_B_DQ_37

DDR_B_DQ_38

DDR_B_DQ_39

DDR_B_DQ_40

DDR_B_DQ_41

DDR_B_DQ_42

DDR_B_DQ_43

DDR_B_DQ_44

DDR_B_DQ_45

DDR_B_DQ_46

DDR_B_DQ_47

DDR_B_DQ_48

DDR_B_DQ_49

DDR_B_DQ_50

DDR_B_DQ_51

DDR_B_DQ_52

DDR_B_DQ_53

DDR_B_DQ_54

DDR_B_DQ_55

DDR_B_DQ_56

DDR_B_DQ_57

DDR_B_DQ_58

DDR_B_DQ_59

DDR_B_DQ_60

DDR_B_DQ_61

DDR_B_DQ_62

DDR_B_DQ_63

AW8

AW9

AT15

AU15

AR20

AR17

AU26

AT26

AR38

AR37

AK34

AL34

AF37

AF36

AB35

AD35

AY6

AR15

AU17

AV25

AU39

AL37

AJ35

AD37

AV7

AW4

BA9

AU11

AU7

AU8

AW7

AY9

AY13

AP15

AW15

AT16

AU13

AW13

AP16

AU16

AY17

AV17

AR21

AV20

AP17

AW16

AT20

AN20

?

?

AT25

AV26

AU29

AV29

AW25

AR25

AP26

AR29

AR36

AU38

AN35

AN37

AV39

AW39

AU40

AU41

AL35

AL36

AK36

AJ34

AN39

AN40

AK37

AL39

AJ38

AJ37

AF38

AE37

AK40

AJ40

AF34

AE35

AD40

AD38

AB40

AA39

AE36

AE39

AB37

AB38

DQS_B0

DQS_B#0

DQS_B1

DQS_B#1

DQS_B2

DQS_B#2

DQS_B3

DQS_B#3

DQS_B4

DQS_B#4

DQS_B5

DQS_B#5

DQS_B6

DQS_B#6

DQS_B7

DQS_B#7

DQM_B0

DQM_B1

DQM_B2

DQM_B3

DQM_B4

DQM_B5

DQM_B6

DQM_B7

DATA_B0

DATA_B1

DATA_B2

DATA_B3

DATA_B4

DATA_B5

DATA_B6

DATA_B7

DATA_B8

DATA_B9

DATA_B10

DATA_B11

DATA_B12

DATA_B13

DATA_B14

DATA_B15

DATA_B16

DATA_B17

DATA_B18

DATA_B19

DATA_B20

DATA_B21

DATA_B22

DATA_B23

DATA_B24

DATA_B25

DATA_B26

DATA_B27

DATA_B28

DATA_B29

DATA_B30

DATA_B31

DATA_B32

DATA_B33

DATA_B34

DATA_B35

DATA_B36

DATA_B37

DATA_B38

DATA_B39

DATA_B40

DATA_B41

DATA_B42

DATA_B43

DATA_B44

DATA_B45

DATA_B46

DATA_B47

DATA_B48

DATA_B49

DATA_B50

DATA_B51

DATA_B52

DATA_B53

DATA_B54

DATA_B55

DATA_B56

DATA_B57

DATA_B58

DATA_B59

DATA_B60

DATA_B61

DATA_B62

DATA_B63

1

DQM_B[0..7]

DATA_B[0..63]

DQS_B0 20

DQS_B#0 20

DQS_B1 20

DQS_B#1 20

DQS_B2 20

DQS_B#2 20

DQS_B3 20

DQS_B#3 20

DQS_B4 20

DQS_B#4 20

DQS_B5 20

DQS_B#5 20

DQS_B6 20

DQS_B#6 20

DQS_B7 20

DQS_B#7 20

DQM_B[0..7] 20

DATA_B[0..63] 20

R123

R123

1KR0402

B

4

1KR0402

CE

Q3

Q3

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

A A

SLP_S4#14,27,29

5

DDR3 PWROK

DDR3_PWROK_BSLP_S4#

R133 1KR0402R133 1KR0402 R690

R138

R138

10KR1%0402

10KR1%0402

DDR3_PWROKDDR3_PWROK#

CE

Q27

Q27

B

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

C72

C72

C1u6.3X50402-1

C1u6.3X50402-1

R689

R689

1K/4

1K/4

MCH_VREF_A

C738

R690

1K/4

1K/4

C738

0.1u/25v/Y5/4

0.1u/25v/Y5/4

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7565

MS-7565

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, November 05, 2008

Date:

Wednesday, November 05, 2008

Date:

2

Wednesday, November 05, 2008

MS-7565

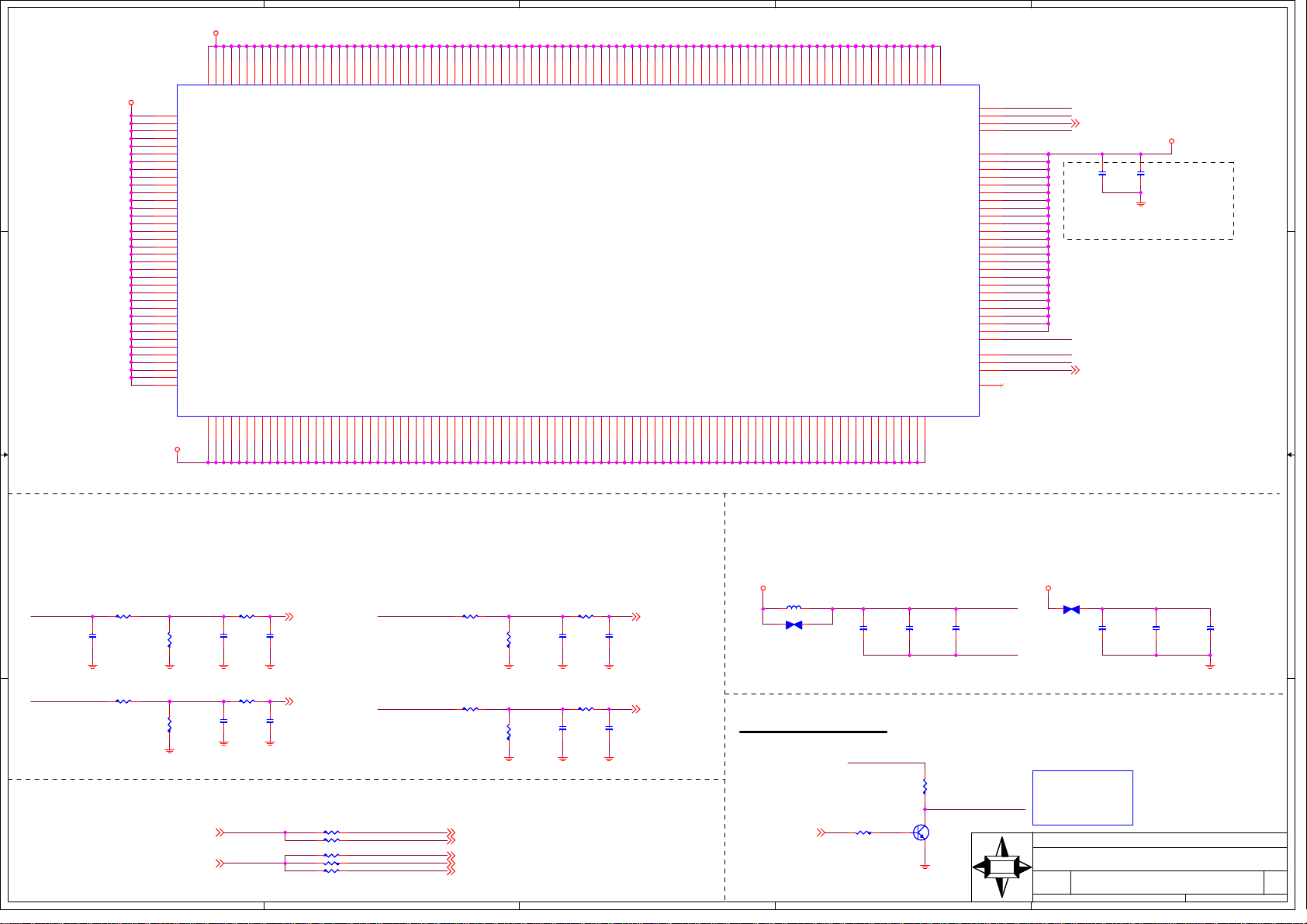

Intel Eaglelake - Memory DDR2

Intel Eaglelake - Memory DDR2

Intel Eaglelake - Memory DDR2

1

Sheet of

Sheet of

Sheet of

10 36

10 36

10 36

0B

0B

0B

C737

C737

0.1u/25v/Y5/4

0.1u/25v/Y5/4

3

5

VCC3_DAC_EXP

VCC3_DAC_EXP

D D

C C

V_FSB_VTT

B B

V_1P125_CORE

A A

R892

R892

1R1%

1R1%

C742

C742

2.2u/6

2.2u/6

0.1u/25v/Y5/4

0.1u/25v/Y5/4

L48

L48

X_10u100mA_0805-RH

X_10u100mA_0805-RH

CP42

CP42

X_COPPER

X_COPPER

R891

R891

X_0R

X_0R

CP44

CP44

X_COPPER

X_COPPER

L43

L43

X_10u100mA_0805-RH

X_10u100mA_0805-RH

CP41

CP41

X_COPPER

X_COPPER

VCC3_DAC_EXP

R704

R704

40.2R1%0402

40.2R1%0402

R705

R705

39.2R1%0402

39.2R1%0402

V_FSB_VTT

V_1P125_CORE

C303 X_10u/10V/8C303 X_10u/10V/8

C562 X_10u/10V/8C562 X_10u/10V/8

C767 X_10u/10V/8C767 X_10u/10V/8

C307 X_1u/6.3V/Y5/4C307 X_1u/6.3V/Y5/4

C340 X_1u/6.3V/Y5/4C340 X_1u/6.3V/Y5/4

C382 X_1u/6.3V/Y5/4C382 X_1u/6.3V/Y5/4

C501 X_1u/6.3V/Y5/4C501 X_1u/6.3V/Y5/4

C884 X_1u/6.3V/Y5/4C884 X_1u/6.3V/Y5/4

C975 X_1u/6.3V/Y5/4C975 X_1u/6.3V/Y5/4

C977 X_1u/6.3V/Y5/4C977 X_1u/6.3V/Y5/4

C371 X_1u/6.3V/Y5/4C371 X_1u/6.3V/Y5/4

21

C10u10Y0805

C10u10Y0805

V_1P125_CORE V_1P125_CORE

V_1P125_CORE V_1P125_CORE

V_1P125_CORE

VCC3

L46

L46

600L200mA-450

600L200mA-450

C612

C612

C1U10X

C1U10X

C298 X_1u/6.3V/4C298 X_1u/6.3V/4

C230 X_1u/6.3V/4C230 X_1u/6.3V/4

C357 1u/6.3V/Y5/4C357 1u/6.3V/Y5/4

C355 X_1u/6.3V/4C355 X_1u/6.3V/4

C299 X_1u/6.3V/4C299 X_1u/6.3V/4

C296 X_1u/6.3V/4C296 X_1u/6.3V/4

C358 X_1u/6.3V/4C358 X_1u/6.3V/4

C342 0.1u/25v/Y5/4C342 0.1u/25v/Y5/4

C883 0.1u/25v/Y5/4C883 0.1u/25v/Y5/4

C743

C743

R897 1R1%R897 1R1%

C744

C744

X_10u/10V/8

X_10u/10V/8

R896 1R1%R896 1R1%

R895 1R1%R895 1R1%

VCCA_DPLLA VCCA_DPLLBVCCA_DPLLA

21

C751

C751

X_10u/10V/8

X_10u/10V/8

R915

R915

1R1%

1R1%

VCCA_EXP

C757

C757

0.1u/25v/Y5/4

0.1u/25v/Y5/4

C354 C10u10Y0805C354 C10u10Y0805

C304 X_1u/6.3V/4C304 X_1u/6.3V/4

C297 1u/6.3V/Y5/4C297 1u/6.3V/Y5/4

C359 X_0.1u/16V/4C359 X_0.1u/16V/4

C356 X_0.1u/16V/4C356 X_0.1u/16V/4

C306 X_0.1u/16V/4C306 X_0.1u/16V/4

near NB

BOTTOM

5

DAC_FILTERED

VCCA_GPLL

VCCA_MPLL

C746

C746

C10u10Y0805

C10u10Y0805

C758

C758

V_1P125_CORE

C745

C745

0.1u/25v/Y5/4

0.1u/25v/Y5/4

V_1P125_CORE

C752

C752

0.1u/25v/Y5/4

0.1u/25v/Y5/4

near NB VTT ball

V_FSB_VTT

C988 X_C2.2u6.3YC988 X_C2.2u6.3Y

C989 X_C2.2u6.3YC989 X_C2.2u6.3Y

C990 X_C2.2u6.3YC990 X_C2.2u6.3Y

near NB FOR EXP power

V_1P125_CORE

C994 X_C2.2u6.3YC994 X_C2.2u6.3Y

C995 X_C2.2u6.3YC995 X_C2.2u6.3Y

C996 X_C2.2u6.3YC996 X_C2.2u6.3Y

V_1P125_CORE

near NB

C991 C22u6.3X50805-RHC991 C22u6.3X50805-RH

C992 X_C22u6.3X50805-RHC992 X_C22u6.3X50805-RH

C993 X_C22u6.3X50805-RHC993 X_C22u6.3X50805-RH

C763 C10u10Y0805C763 C10u10Y0805

C765 C10u10Y0805C765 C10u10Y0805

C762 X_10u/10V/8C762 X_10u/10V/8

C976 1u/6.3V/Y5/4C976 1u/6.3V/Y5/4

C302 1u/6.3V/Y5/4C302 1u/6.3V/Y5/4

C343 1u/6.3V/Y5/4C343 1u/6.3V/Y5/4

CP43

CP43

X_COPPER

X_COPPER

L44

L44

X_10u100mA_0805-RH

X_10u100mA_0805-RH

R893 1R1%R893 1R1%

21

CP48

CP48

X_COPPER

X_COPPER

CP51

CP51

X_COPPER

X_COPPER

L45

L45

X_10u100mA_0805-RH

X_10u100mA_0805-RH

21

CP52

CP52

X_COPPER

X_COPPER

H_VCCPLL6

VCC_DDR

V_1P125_CORE

H_VCCPLL

R706

R706

X_0/4