5

4

3

2

1

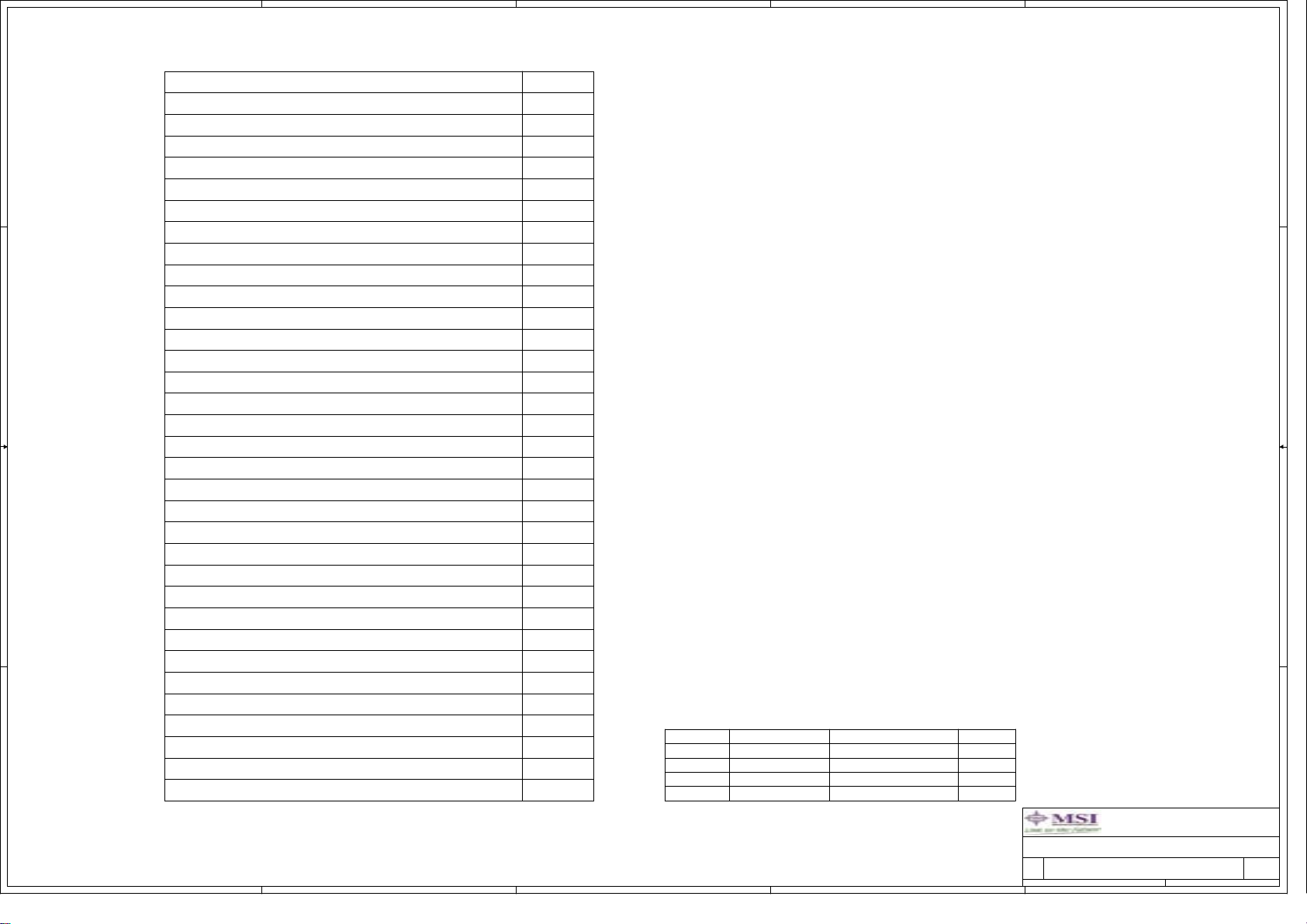

Cover Sheet 1

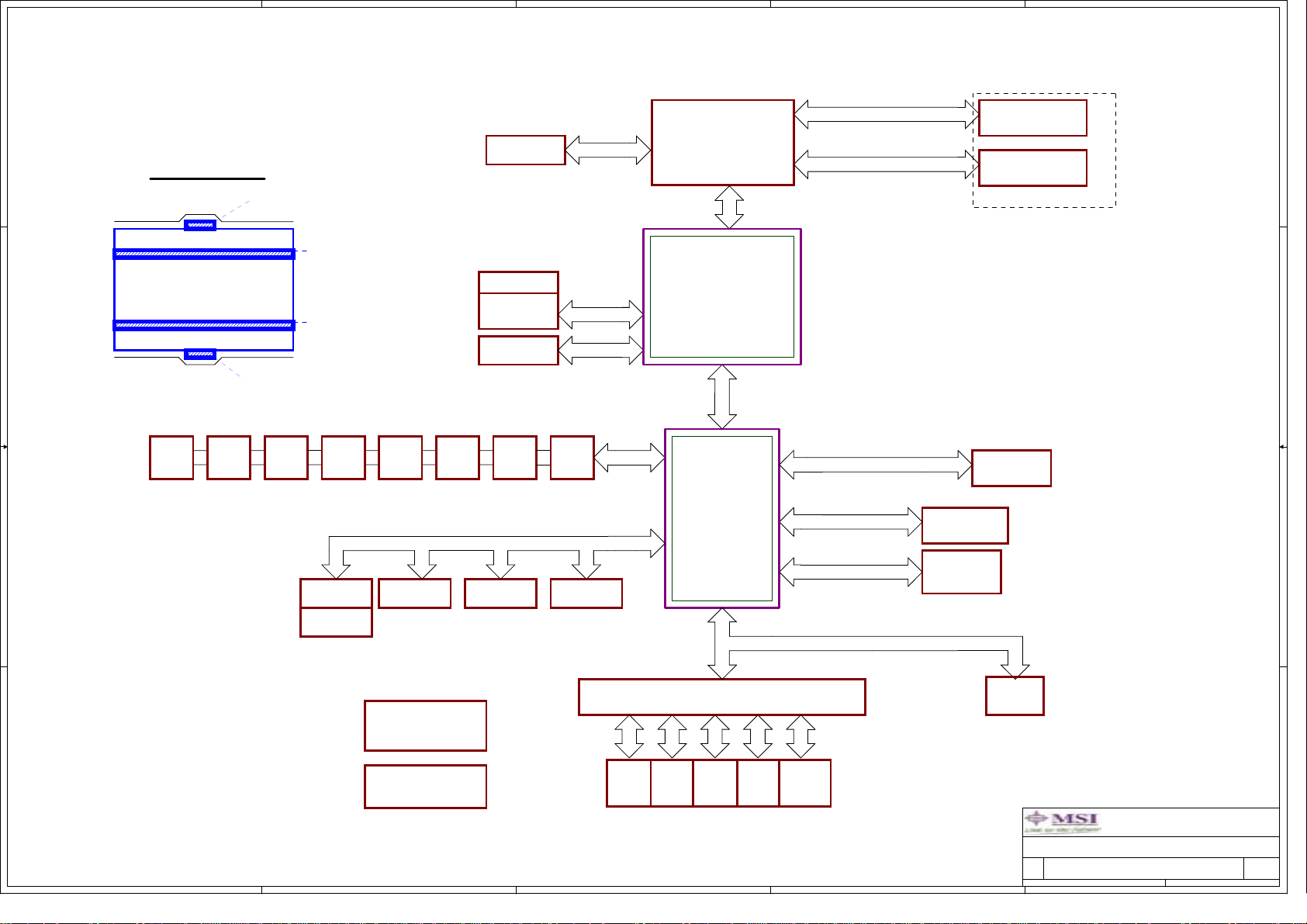

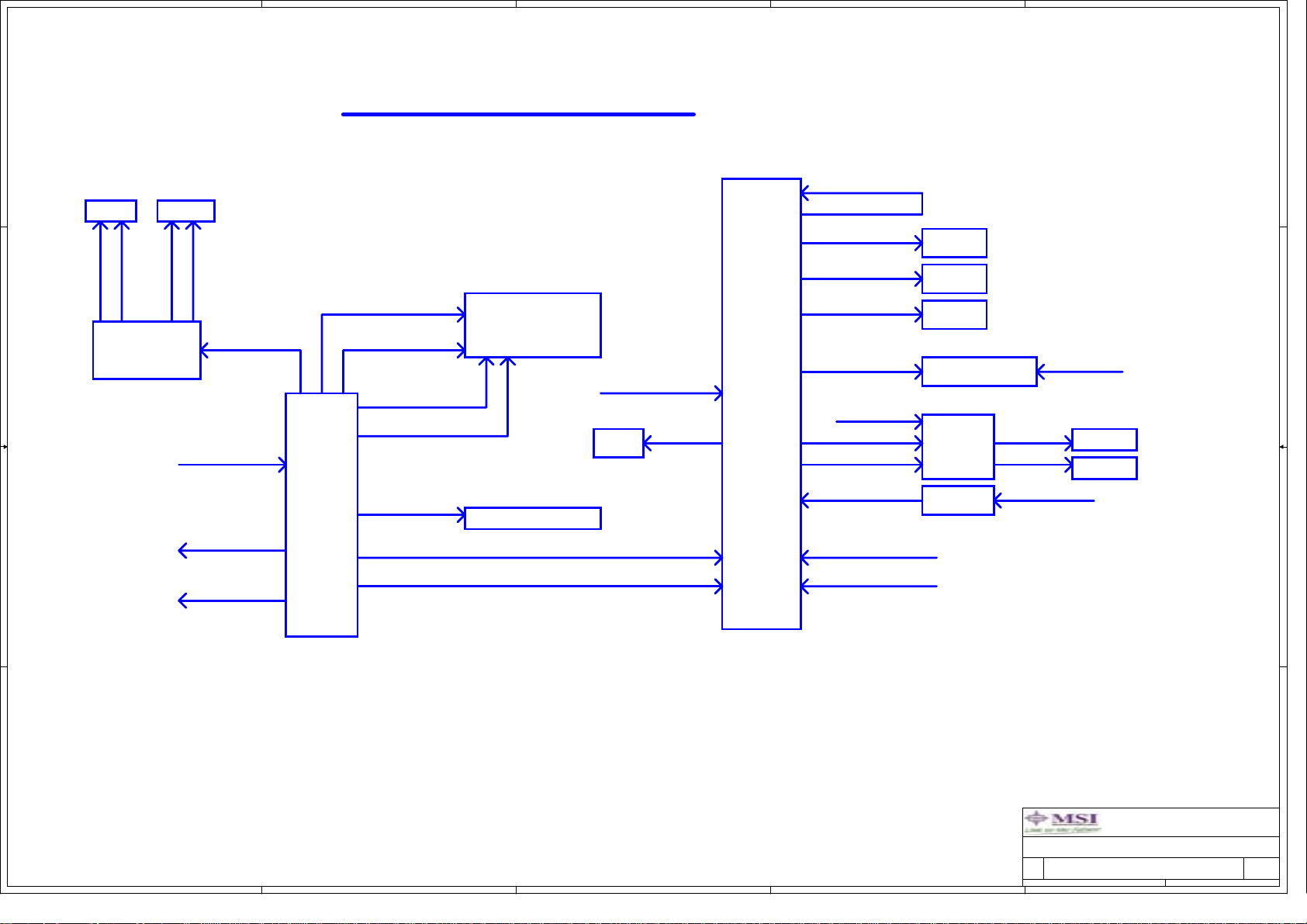

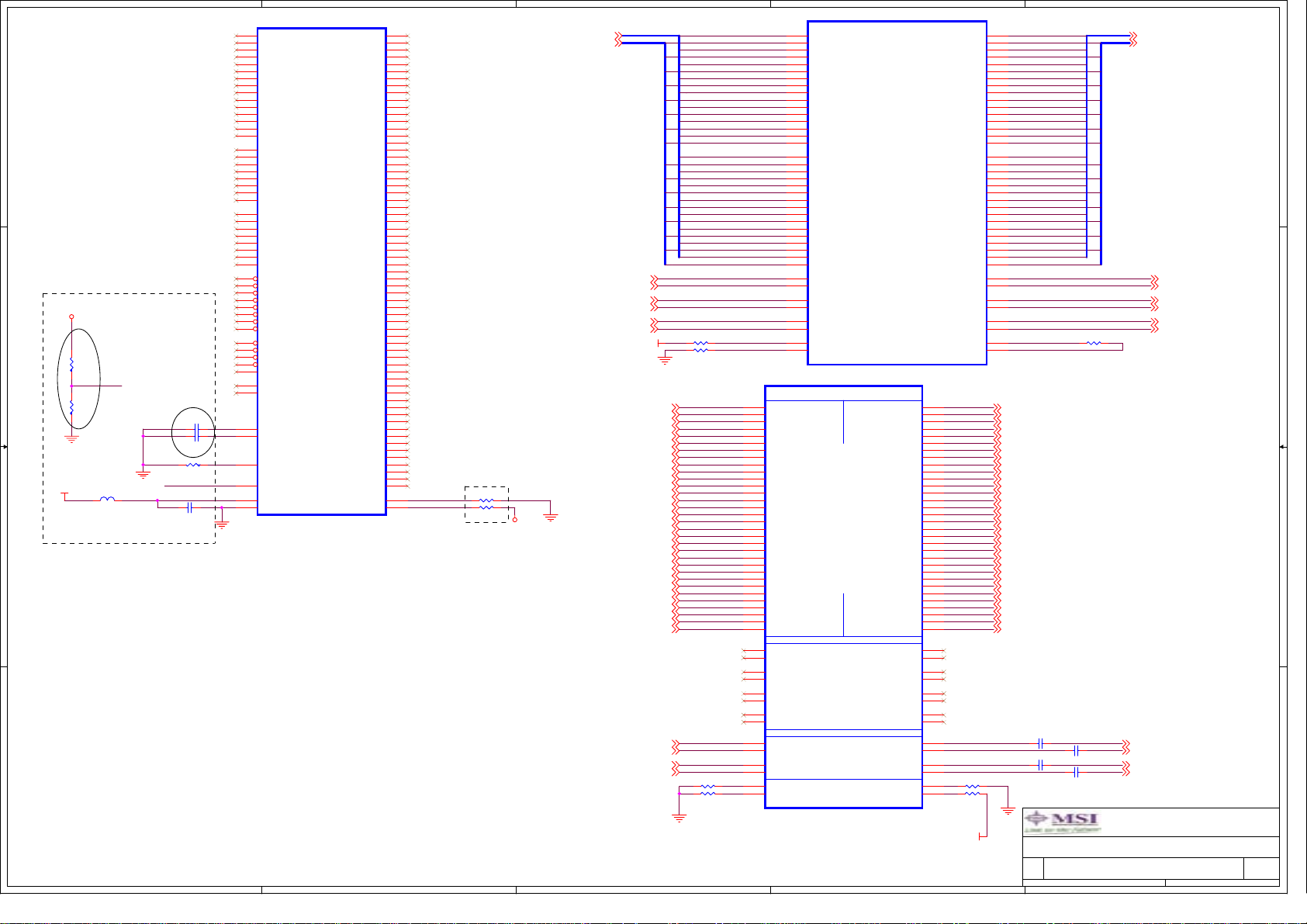

Block Diagram

D D

GPIO SETTING

POWER DELIVERY CHART

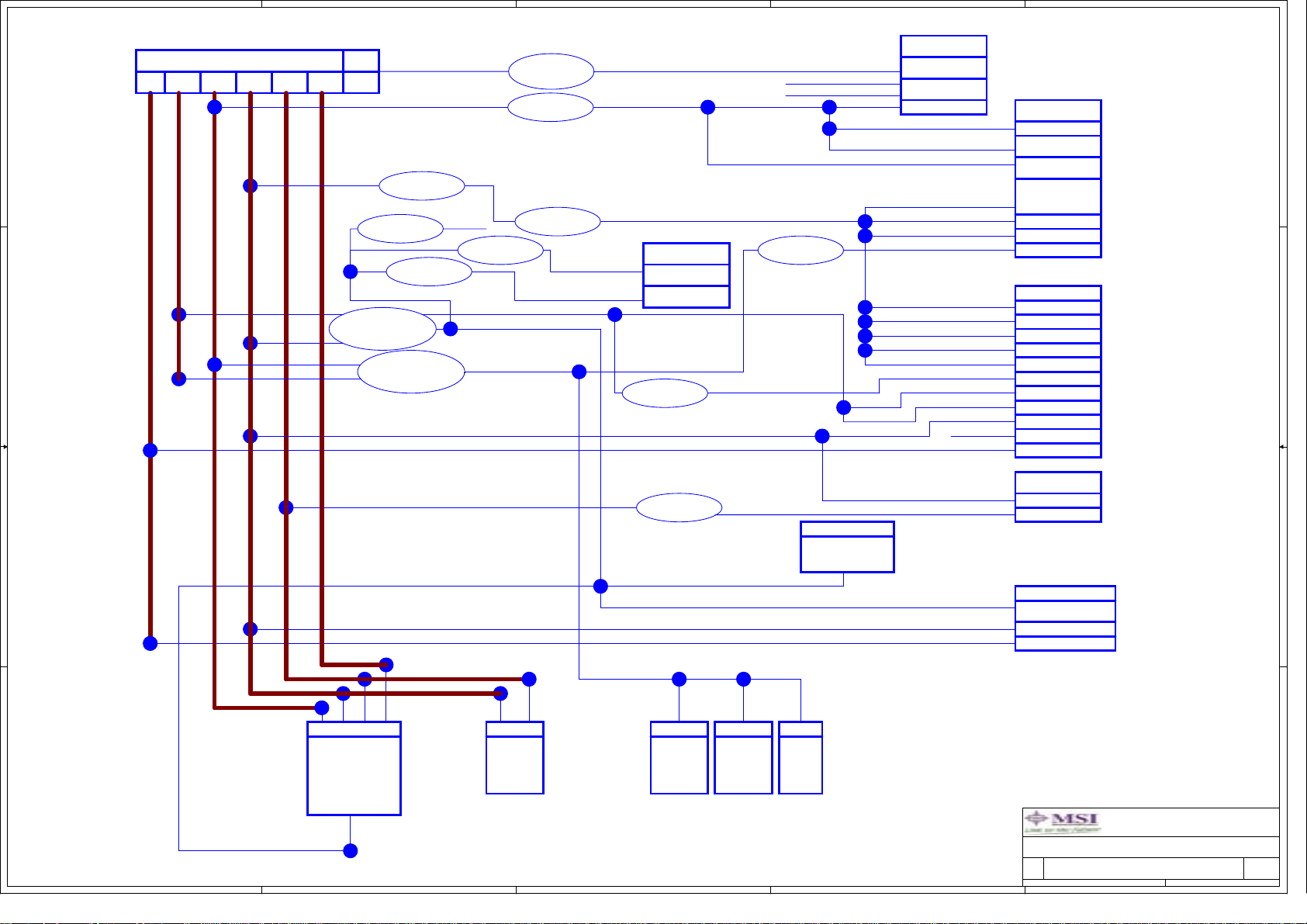

CLOCK DISTRIBUTION

ATHLON64 HT I/F,CTRL&DEBUG

ATHLON64 DDR MEMORY I/F

ATHLON64 PWR & GND

FIRST LOGICAL DDR DIMM

SECOND LOGICAL DDR DIMM

RS480-HT LINK,PCIE,SIDEMEM

RS480-VIDEO I/F,CLK,STRAP

C C

RS480-POWER

CLOCK GENERATOR - ICS951412A

K8 CORE POWER - ISL6559CB

SB400-PCI/CPU/LPC/RTC

SB400-ACPI/GPIO/AC97/USB

SB400-SATA/IDE

SB400-PWR & DECOUPLING

SB400-STRAPS

AC'97 Audio - ALC655

USB CONNECTORS

B B

W83627THF & FDD & KBMS

PCI SLOTS 1 & 2

PCIE X 16 & PCI SLOT 3

ATA 33/66/100/133 IDE & SATA

FAN, COM PORT, LPT

LAN RTL8110SB/8100C

LAN CONNECTORS

MS6 ACPI CONTROLLER

VCCA1V_2 & VGA CONNECTOR

ATX CONN, FAN, FRONT PANEL

A A

MANUAL PARTS

CHANGE HISTORY

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

MS(7093)

ATI RS480/RX480 (North Bridge) +SB400 (South Bridge)

AMD Socket 939 800MHz

CPU:

AMD Socket 939 (Athlon 64)

System Chipset:

ATI RS480/RX480 (North Bridge)

SB400 (South Bridge)

On Board Chipset:

BIOS -- 32 Lead PLCC (4M)

AC'97 Codec -- ALC655

LPC Super I/O -- W83627THF Ver:E

LAN --RTL8110SB + RTL8100C (Dual Layout)

CLOCK --ICS951412AG

Main Memory:

DDR * 4 (DDR400MHz)

Expansion Slots:

PCI Express (X16) SLOT * 1

PCI SLOT * 3

PWM:

Controller: ISL6559CB+HIP6614-ACB+HIP6612-ACB

ACPI:

WINBOND / MS6 Ver: RBF

MS7093-200 Config setting:

Opt Name

GL

GF

DL

DF

Function

RS480 + RTL8100C

RS480 + RTL8110SB

RX480 + RTL8100C

RX480 + RTL8110SB

ERP BOM Date

mATX

Version 200

Circuit Config Default: cfg7093-RS480-STD

2004/11/16

Title

Cover Sheet

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7093 200

1

of

134Tuesday, November 16, 2004

5

4

BLOCK DIAGRAM

3

2

1

D D

CORE POWER

60A

VRM10.0

15

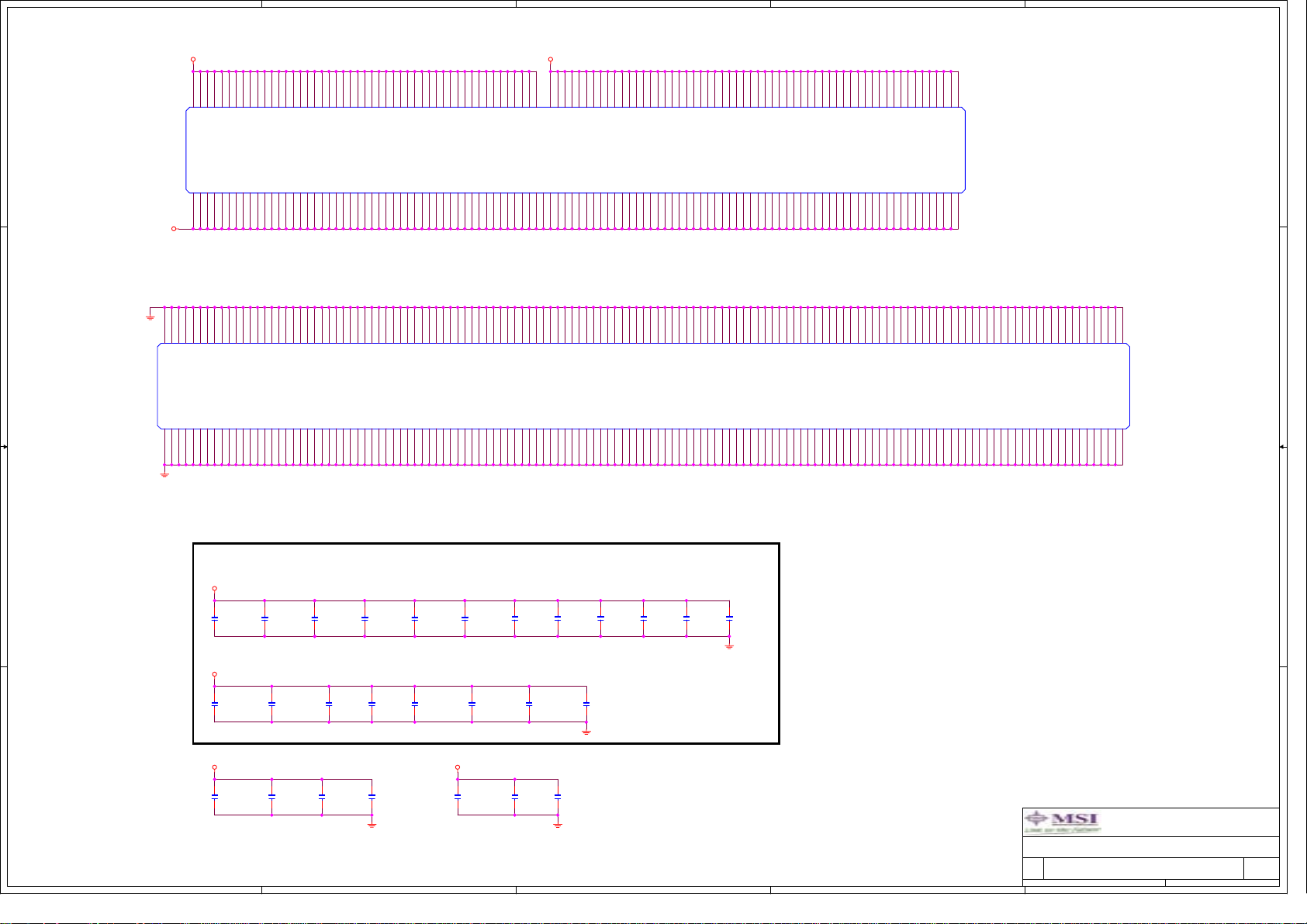

Board Stack-up

1/2 oz. Cu plus

plating

Solder

Mask

PREPREG 4.7mils

CORE 47mils

C C

Solder

Mask

PREPREG 4.7mils

USB-7

USB-6

1/2 oz. Cu plus

plating

1 oz. Cu Power

Plane

1 oz. Cu Ground

Plane

USB-5 USB-0

USB-4

USB-3

External Clock Generator

ICS951412

VGA CON

PCIE 16X

USB-2 USB-1

14

31

25

22 22 22 22 22 22 22 22

HyperTranspor t LINK0

CRT

PCIE 16X

USB 2.0

DESKTOP ATHLON64

939-Pin uFCPGA 939

6,7,8

LINK0

16x16

ATI NB

DESKTOP RS480

HyperTransport LINK0 CPU I/F

INTEGRATED GRAPHICS

2X PCI Express Link

DESKTOP RX480

Non-INTEGRAT ED GRAPHI CS

11,12,13

2X PCIE

ATI SB

DESKTOP SB400

USB2.0 (4+4)

AC LINK

DDR200,266,333,400

128bit

DDR200,266,333,400

UNBUFFERED DDR

DIMM1,2

184-PIN DDR FIRST LOGICAL DIMM

UNBUFFERED DDR

DIMM3,4

184-PIN DDR SECOND LOGICAL DIMM

AC97 CODEC

ALC655

9,10

9,10

21

SATA

AC97 2.2

ATA 33/66/100/ 133

PCI BUS

B B

RTL8110SB

1000

RTL8110C

10/100

28

28

PCI SLOT 3

PCI SLOT 1

24

PCI SLOT 0

2424

ACPI 1.1

LPC I/F

INT RTC

PCI/PCI BDGE

16,17,18,19,20

SATA Link

ATA 33/66/100/133

LPC I/F

SATA Port #1~#4

26

IDE1

IDE2

26

ACPI MS6

Winbond LPC SIO W83627THF Ver:E

CONTROLLER &

DDR MEMORY POWER

A A

5

RS480 CORE & PCIE

POWER

& NB,SB POWER

SEQUENCE

4

30

SERIAL FAN

KBD

FLOPPY

LPT

MOUSE

27

23

3

23

PORTS

2731

CONTROL

23

27

2

FLASH

BIOS

23

Title

BLOCK DIAGRAM

Size Document Number Re v

Custom

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7093 200

1

of

234Thursday, November 11, 2004

5

4

3

2

1

SB400 GPIO SETTING

GPIO Pin

GPIO 0

GPIO 1

D D

GPIO 2

GPIO 3

GPIO 4

GPIO 6

GPIO 7

GPIO 8

GPIO 9

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16

GPIO 17

C C

GPIO 18

GPIO 19

GPIO 20

GPIO 21

GPIO 22

GPIO 23

GPIO 24

GPIO 25

GPIO 26

GPIO 27

GPIO 28

GPIO 29

GPIO 30

GPIO 31

GPIO 32

B B

GPIO 33

GPIO 34

GPIO 35

GPIO 36

GPM0#

GPM1#

GPM2#

GPM3#

GPM4#

GPM5#

GPM6#

GPM7#

Power Function

LDT_PG

S0

BIOS_WP#

S0

SPKR

S0

BIOS_TBL#

S0

Unused, Pull-Down 10K to GND

S0

Unused, Pull-Up 4.7K to +3.3VGPIO 5

S0

S0

Unused, Pull-Down 10K to GND

S0

Unused, Pull-Down 10K to GND

S0

Unused, Pull-Down 10K to GND

S0

Unused, Pull-Down 10K to GND

S5

THERM_ALERT#

S0

PDMA66

S0

SDMA66

S0

PCI_REQ#5

S0

PCI_GNT#5

SDD_R0

S0

SDD_R1

S0

SDD_R2

S0

SDD_R3

S0

SDD_R4

S0

SDD_R5

S0

SDD_R6

S0

SDD_R7

S0

SDD_R8

S0

SDD_R9

S0

SDD_R10

S0

SDD_R11

S0

SDD_R12

S0

SDD_R13

S0

SDD_R14

S0

SDD_R15

S0

PCI_REQ#6

S0

PCI_GNT#6

S0

S0

PCI_INTE#

S0

PCI_INTF#

S0

PCI_INTG#

S0

PCI_INTH#

S5

USB_OCP#1

S5

USB_OCP#1

S5

USB_OCP#1

S5

USB_OCP#1

S5

USB_OCP#4

S5

USB_OCP#4

S5

USB_OCP#4

S5

USB_OCP#4

Secondary IDE

USB OC#

Defult Type Type

Inpute

Inpute

Inpute

Inpute

Tri-state

Tri-state

Tri-state if used as GPIO

Tri-state if used as GPIO

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

High

High

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

I/OD

I/O

I/O

I/O

I/O

I/O

I/OD

I/O

I/O

I/O

I/O

I/O

I/O

OD

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

PCI Config.

DEVICE

INT#

REQ#/GNT#

IDSEL

INTE#

PCI Slot 1

INTF#

INTG#

PCI_REQ#0

PCI_GNT#0

PCI_AD16

INTH#

INTF#

PCI Slot 2

INTG#

INTH#

PCI_REQ#1

PCI_GNT#1

PCI_AD17

INTE#

INTG#

PCI Slot 3

INTH# PCI_REQ#2

INTE#

PCI_GNT#2

PCI_AD18

INTF#

LAN

INTH#

PCI_REQ#3

PCI_GNT#3

PCI_AD19

BIOS PCI_CLK5

SIO PCI_CLK6

CLOCK

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

DDR DIMM Config.

DEVICE

DIMM 1

DIMM 2

DIMM 3

DIMM 4

A0H

1010000B

A2H

1010001B

A4H

1010010B

A6H

1010011B

CLOCKADDRESS

MCLK_1L0/MCLK_1L#0

MCLK_1L1/MCLK_1L#1

MCLK_1L2/MCLK_1L#2

MCLK_1H0/MCLK_1H#0

MCLK_1H1/MCLK_1H#1

MCLK_1H2/MCLK_1H#2

MCLK_2L0/MCLK_2L#0

MCLK_2L1/MCLK_2L#1

MCLK_2L2/MCLK_2L#2

MCLK_2H0/MCLK_2H#0

MCLK_2H1/MCLK_2H#1

MCLK_2H2/MCLK_2H#2

PCI RESET DEVICE

Signals

PCIRST#

A_RST# MS6, NB

HDD_RST# Primary, Scon dary IDE

DEV_RST#

Target

PCI slot 1-3, LAN

SIO,BIOS

PCI_E_RST# PCI-EX16 slot

A A

Title

GPIO SETTING

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7093 200

1

of

334Thursday, November 11, 2004

5

4

3

2

1

ATHLON 64

VDDCORE

0.8-1.55V 60A

DDR400 MEM I/F

VTT 2A, VDD 2A

VLDT 1.2V 0.5A

VDDHT

PCIE_VDD12

VCC_NB (S0, S1)

LVDDR18

PCIE_VDD18

VDD18

+1.8VDUAL_SPMEM(S0,S1,S3)

+1.8V_S3 (S0,S1,S3)

NB RS480M

VDDHT 1.2V 0.5A

PCI-E CORE

&VCO 2.25A

NB CORE VDDC

1.0-1.2V 5A

PLL & DAC-Q 0.1A

PCI-E I/O 750mA

LVDS 1.8V 100mA

SIDE PORT MEM I/F 2A

SB SB400

X4 PCI-E 0.8A

ATA I/O 0.2A

ATA PLL 0.01A

PCI-E PVDD 80mA

SB CORE 0.6A

1.8V S5 PW 0.22A

3.3V S5 PW 0.01A

USB CORE I/O 0.2A

3.3V I/O 0.45A

1.8V USB

RTCVCC

ATX P/S WITH 1A STBY CURRENT

VBAT

D D

5VSB

+/-5%

5V

+/-5%

3.3V

+/-5%

12V

+/-5%

-12V

+/-5%

CPU

PW

12V

+/-5%

VCC 2.5V

REGULATOR

1.8V_S3

REGULATOR

2.5V VDDR

REGULATOR

+1.8V_S3

1.25V VTT_DDR

REGULATOR

VRM SW

REGULATOR

VDD 1.2V SW

REGULATOR

1.8V

REGULATOR

VTT_DDR_SUS (S0,S1,S3)

VCC_DDR(S0,S1,S3)

+3.3VSB REGULAT OR

C C

ACPI CONTROLLER

+5VSB REGULATOR

ACPI CONTROLLER

+3V_Dual (S0, S1, S3, S4, S5)

+5V_Dual (S0, S 1, S3)

CPU_VCORE (S0, S1)

VDDA_1V2 (S0, S1)

+1.8V_S0 (S0, S1)

DDR400 DIMMs

VTT_DDR 2A

VDD MEM 8.52A

1.8V STB LDO

REGULATOR

VTT_DDR_SUS (S0,S1,S3)

VCC_DDR(S0,S1,S3)

VDDQ 1.8V

REGULATOR

+1.8VSB (S0, S1, S3, S4, S5)

+3.3V (S0, S1)

AC97 CODEC

5VAA LDO

REGULATOR

+5VR (S0, S1)

3.3V CORE 0.3A

5V ANALOG 0.1A

ENTHERNET

B B

3.3V 0.5A (S0, S1)

3.3V 0.1A (S0,S1,S3)

SUPER I/O

+3V SD 0.01A

+3V 0.1A

VBAT

PCI Slot (per slot)

5V

3.3V

A A

12V

3.3Vaux

-12V

5.0A

7.6A

0.5A

0.375A

0.1A

X16 PCIE

3.3V

12V

3.0A

5.5A

USB X4 FR USB X4 RL

VDD

5VDual

VDD

5VDual

2.0A 2.0A

+3.3VDUAL (S0, S1, S3)

5

4

3

2XPS/2

5VDual

1.0A

Title

POWER DELIVERY CHART

Size Document Number Re v

Custom

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7093 200

1

of

434Thursday, November 11, 2004

5

4

3

2

1

D D

CLOCK DISTRIBUTION

PCI CLKFB

DIMM1,3 DIMM2,4

3 PAIR MEM CLK

3 PAIR MEM CLK

C C

ATHLON 64 FX

LGA939 PACKAGE

3 PAIR MEM CLK

3 PAIR MEM CLK

1 PAIR CPU_CLK

14.318MHZ OSC INPUT

200MHZ

EXTERNAL

CLK GEN.

ICS 951412

B B

SB400

AC97 CODEC

SB_OSC_14M

14.318MHZ

AC97_CLK

14.318MHZ

HTREFCLK

66MHZ

NB_OSC_14M

14.318MHZ

1 PAIR NBSRCCLK

100MHZ

1 PAIR SBLINKCLK

100MHZ

1 PAIR GFXCLK

100MHZ

ATI RS480

PCIE GFX SLOT - 16 LANES

BIOS

ATI SB

SB400

SB_OSC_14M

14.318MHZ

PCI CLK5

33MHZ

1 PAIR SBSRCCLK

100MHZ

USBCLK_EXT

48MHZ

PCI CLK9

33MHZ

PCI CLK0

33MHZ

PCI CLK1

33MHZ

PCI CLK2

33MHZ

PCI CLK3

33MHZ

RTC_CLK

32.768KHZ

PCI CLK6

33MHZ

SIO_CLK

48MHZ

AC_BITCLK

12.288MHZ

32.768KHZ OSC INPUT

25MHZ OSC INPUT FOR SATA

PCI SLOT1

PCI SLOT2

PCI SLOT3

LAN 8100C/ 8110SB

PCI Gbit/100/10

SUPER IO

W83627 THE

AC97 CODEC

25MHZ OSC INPUT

KBCLK

MSCLK

AC97_CLK

14.318MHZ

KEYBOARD

MOUSE

A A

Title

CLOCK DISTRIBUTION

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7093 200

1

of

534Thursday, November 11, 2004

5

4

3

2

1

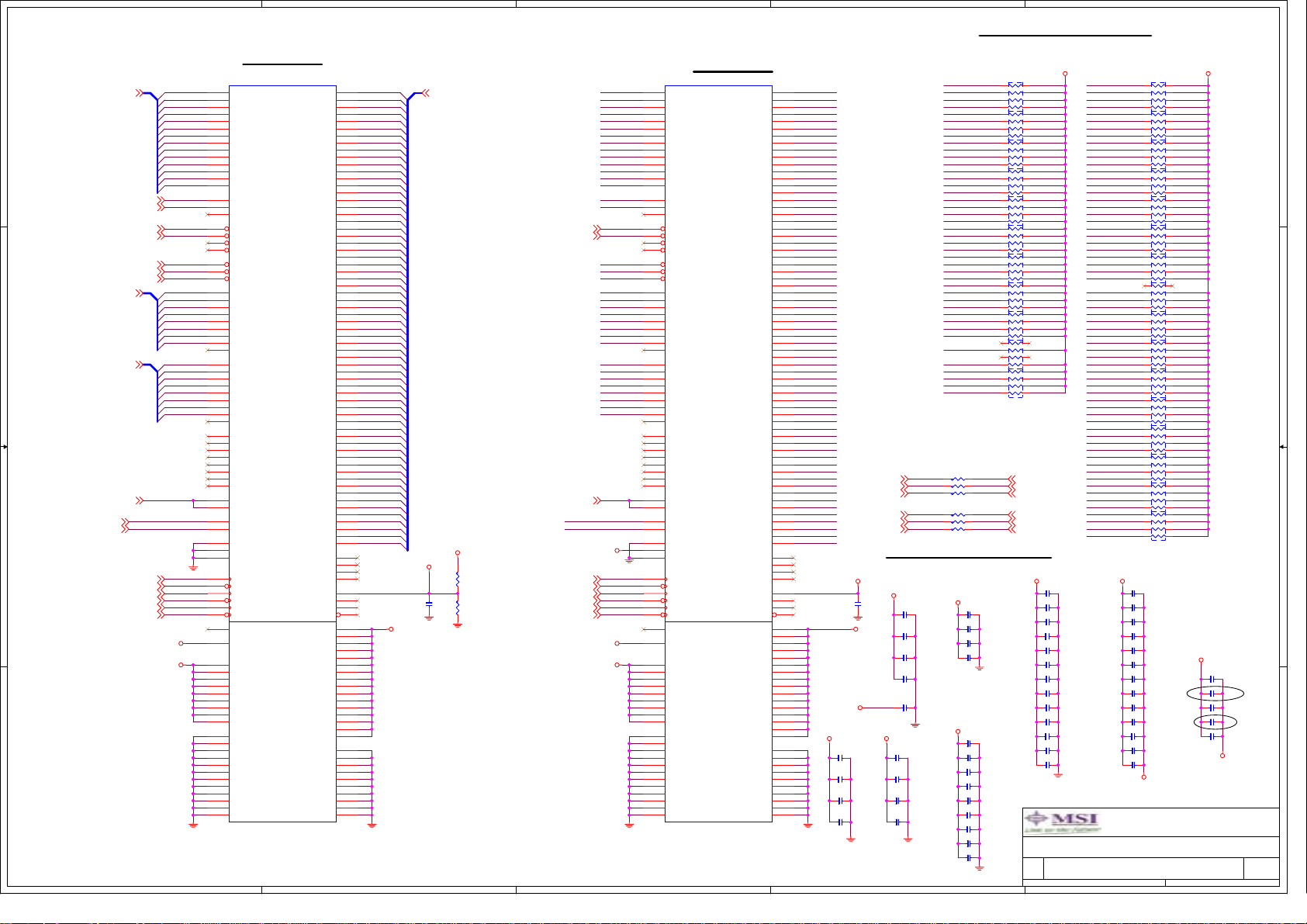

CPU1D

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

FBCLKOUT_L

DBREQ_L

SCANCLK2

SCANCLK1

SCANEN

TDO

SCANOUT_H

SCANOUT_L

PROGEN1_L

PROGEN0_L

FREE22

FREE23

FREE24

FREE25

FREE26

FREE27

FREE28

FREE29

FREE30

FREE31

FREE32

FREE33

FREE34

FREE35

FREE36

FREE37

FREE38

FREE39

FREE40

FREE41

VCC2_5

R813 680R

R814 680R

R815 680R

Thermal Sensor Trip output, asserted

at nominal temperature of 125oC.

CPU_THRIP#

BP3

BP2

BP1

BP0

AG10

THERMDA_CPU

AJ2

THERMDC_CPU

AJ1

VID4

A13

A12

VID2

C12

VID1

A11

VID0

A10

CPU_NC_C13

C13

CPU_NC_E9

E9

CPU_STRAP_LO_B13

B13

CPU_STRAP_LO_C10

C10

CPU_FBCLKOUT_H

F13

E13

CPU_THRIP# 30

THERMDA_CPU 23

THERMDC_CPU 23

TP1

TP2

R7

80.6R1%

CPU_FBCLKOUT_L

DBREQ_L

A6

CPU_STRAP_LO_AG9

AG9

CPU_STRAP_LO_AH6

AH6

CPU_STRAP_LO_AF10

AF10

CPU_STRAP_LO_AH10

AH10

CPU_STRAP_LO_AJ10

AJ10

TDO

AG8

CPU_NC_V5

V5

CPU_NC_U5

U5

TP34

TP39

TP9

TP10

VTT_DDR

AL14

A14

AL9

AL10

AL11

AL12

C22

C28

D8

D11

D12

D29

E21

E22

G15

N27

T25

T29

U28

C11

AG15

AH12

LDT_RST#

LDT_PG

LDTSTOP#

R3 680R

R4 680R

VID[0..4] 15

RN2

8P4R-680R

D D

HT_CADIN_H[15..0]11

HT_CADIN_L[15..0]11

HT_CADOUT_H[15..0]11

HT_CADO U T _L[15..0]11

HT_CADIN_H [15..0]

HT_CADIN_L[15..0]

HT_CADO UT_H[15..0]

HT_CADOUT_L[15..0]

VCCA_1V2

L1

2 1

X_80L2_50_0805

1 2

VCC1_2HT

CPU_STRAP_HI_AF12

CPU_STRAP_HI_AJ12

CPU_STRAP_LO_AH10

CPU_STRAP_LO_AJ10

CPU_STRAP_LO_AF10

CPU_STRAP_LO_AH6

CPU_STRAP_LO_AG9

CP45

Internal regulator driver from VCC1_2HT

AG4

AG3

AG1

AG2

V4

V3

Y5

W5

Y4

Y3

AB5

AA5

AD5

AC5

AD4

AD3

AF5

AE5

AF4

AF3

V1

U1

W2

W3

Y1

W1

AA2

AA3

AC2

AC3

AD1

AC1

AE2

AE3

AF1

AE1

AB4

AB3

AB1

AA1

U2

U3

VCC1_2HT

C9

C0.22U16X

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

HT_CLKOUT_H1 11

HT_CLKOUT_L1 11

HT_CLKOUT_H0 11HT_CLKIN_H011

HT_CLKOUT_L0 11

HT_CTLOUT_L0 11

C10

C0.22U16X

20:5:5:20

20:5:5:20

C11

C0.22U16X

VCC_DDR

R6

820R1%

R8

820R1%

C12

C0.22U16X

CPU_CLK14

CPU_CLK#14

VCC1_2HT_OUT

E2

VLDT_06

E1

C4

X_C0.22U16X

C C

C5

X_C0.22U16X

20:5:5:20

B B

20:5:5:20

C6

X_C0.22U16X

HT_CADIN_H15

HT_CAD IN_L15

HT_CADIN_H14

HT_CAD IN_L14

HT_CADIN_H13

HT_CAD IN_L13

HT_CADIN_H12

HT_CAD IN_L12

HT_CADIN_H11

HT_CAD IN_L11

HT_CADIN_H10

HT_CAD IN_L10

HT_CADIN_H9

HT_CAD IN_L9

HT_CADIN_H8

HT_CAD IN_L8

HT_CADIN_H7

HT_CAD IN_L7

HT_CADIN_H6

HT_CAD IN_L6

HT_CADIN_H5

HT_CAD IN_L5

HT_CADIN_H4

HT_CAD IN_L4

HT_CADIN_H3

HT_CAD IN_L3

HT_CADIN_H2

HT_CAD IN_L2

HT_CADIN_H1

HT_CAD IN_L1

HT_CADIN_H0

HT_CAD IN_L0

HT_CLKIN_H111

HT_CLKIN_L111

C7

X_C0.22U16X

HT_CLKIN_L011

HT_CTLIN_H011 HT_CTLOUT_H0 11

HT_CTLIN_L011

VLDT_05

F1

VLDT_02

F2

VLDT_01

R5

L0_CADIN_H15

T5

L0_CADIN_L15

P3

L0_CADIN_H14

P4

L0_CADIN_L14

N5

L0_CADIN_H13

P5

L0_CADIN_L13

M3

L0_CADIN_H12

M4

L0_CADIN_L12

K3

L0_CADIN_H11

K4

L0_CADIN_L11

J5

L0_CADIN_H10

K5

L0_CADIN_L10

H3

L0_CADIN_H9

H4

L0_CADIN_L9

G5

L0_CADIN_H8

H5

L0_CADIN_L8

R3

L0_CADIN_H7

R2

L0_CADIN_L7

N1

L0_CADIN_H6

P1

L0_CADIN_L6

N3

L0_CADIN_H5

N2

L0_CADIN_L5

L1

L0_CADIN_H4

M1

L0_CADIN_L4

J1

L0_CADIN_H3

K1

L0_CADIN_L3

J3

L0_CADIN_H2

J2

L0_CADIN_L2

G1

L0_CADIN_H1

H1

L0_CADIN_L1

G3

L0_CADIN_H0

G2

L0_CADIN_L0

L5

L0_CLKIN_H1

M5

L0_CLKIN_L1

L3

L0_CLKIN_H0

L2

L0_CLKIN_L0

R1

L0_CTLIN_H0

T1

L0_CTLIN_L0

CPU1A

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H0

L0_CTLOUT_L0

VLDT 0

VLDT_08

VLDT_07

VLDT_04

VLDT_03

LM90 DIGITAL TEMPERATURE SENSOR

+3.3V

THERMDA_CPU

THERMDC_CPU SMB_DATA

CPU_THRIP#

+3.3V

A A

Already have pull high to 2.5V in MS6 side (R405)

X_C2200P10XC971

R635 0R

R636 X_10KR

U35

1

VDD

2

D+

3

DT_CRIT_A#4SMC

SNSR-LM90CIMM

GND

ALERT#

SMD

5

6

7

8

R633 10KR

SMB_CLK

Since THERM_ALERT# is S5 power plant in SB400.

ATI's recommend to pull-up to 3V-dual.

+3V_Dual

R634 0R

THERM_ALERT# 17,23

SMB_DATA 9,10,14,17,25,28,30

SMB_CLK 9,10,14,17,25,28,30

VCC2_5 VDDA25VDDA_25

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN3

8P4R-680R

C1

C4.7U16Y1206

VCC1_2HT_OUT

R1 44.2R1%

R2 44.2R1%

C14

C13

C15

C3900P50X

C16

C3900P50X

C1000P50X

R5

169R1%

CPUCLKIN#

C1000P50X

CPUCLKIN

VDDIOSENSE

C934

X_C0.22U10X

VCC1_2HT_OUT

R9 49.9R1%

R10 49.9R1%

C2

C0.22U16X

LDT_RST#16

LDT_PG16

LDTSTOP#12,16

COREFB+15

COREFB-15

TP3

TP4

TP5

TP6

VDDIOSENSE30

CPU_STRAP_HI_E11

CPU_STRAP_LO_F11

TP7

TP8

TP33

TP35

TP36

TP37

TP38

CPU_STRAP_HI_AJ12

CPU_STRAP_HI_AF12

CPU_STRAP_LO_T4

TP11

TP12

TP13

TP14

TP15

TP16

X_80L2_50_0805

L41

2 1

1 2

CP44

VDDA25

C3

C0.01U50X

LDT_RST#

LDT_PG

LDTSTOP# VID3

CPU_L0_REF1

CPU_L0_REF0

CPU_CORESENSE

CPU_VDDIOFB_H

CPU_VDDIOFB_L

VDDIOSENSE

CPU_NC_C5

CPU_NC_A5

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST_L

CPU_TDI

CPU_STRAP_HI_T3

CPU_NC_A4

CPU_NC_D4

CPU_NC_B4

CPU_NC_C4

CPU_NC_C7

CPU_NC_C6

COREFB+

COREFB-

AA24

AE13

AG6

AG7

AJ12

AF12

AE22

AG22

AH8

AH29

AJ22

AJ28

AK3

AK4

AK6

AK8

AK10

AK12

C3

B3

A3

F8

E8

B6

D1

C1

E5

E6

E7

Y24

A8

B8

E11

F11

C5

A5

B11

AF8

AJ9

T3

T4

A4

D4

B4

C4

C7

C6

AL8

AL7

AJ4

AJ5

AJ6

AJ7

AJ8

AL3

AL4

AL5

AL6

VDDA3

VDDA2

VDDA1

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORESENSE

VDDIOFB_H

VDDIOFB_L

VDDIOSENSE

CLKIN_H

CLKIN_L

BYPASSCLK_H

BYPASSCLK_L

PLLCHRZ_H

PLLCHRZ_L

DBRDY

TMS

TCK

TRST_L

TDI

SINGLECHAIN

BURNIN_L

SCANIN_H

SCANIN_L

ANALOG3

ANALOG2

ANALOG1

ANALOG0

DIG_T

ANALOG_T

RSVD_SMBUSC

RSVD_SMBUSD

FREE1

FREE2

FREE3

FREE4

MISC

FREE5

FREE6

FREE7

FREE8

FREE9

FREE10

FREE11

FREE12

FREE13

FREE14

FREE15

FREE16

FREE17

FREE18

FREE19

FREE20

FREE21

THERMTRIP_L

FBCLKOUT_H

SCANSHIFTENB

SCANSHIFTEN

Title

ATHLON64 HT I /F,CT RL&DEBUG

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7093 200

1

of

634Monday, November 15, 2004

5

4

3

2

1

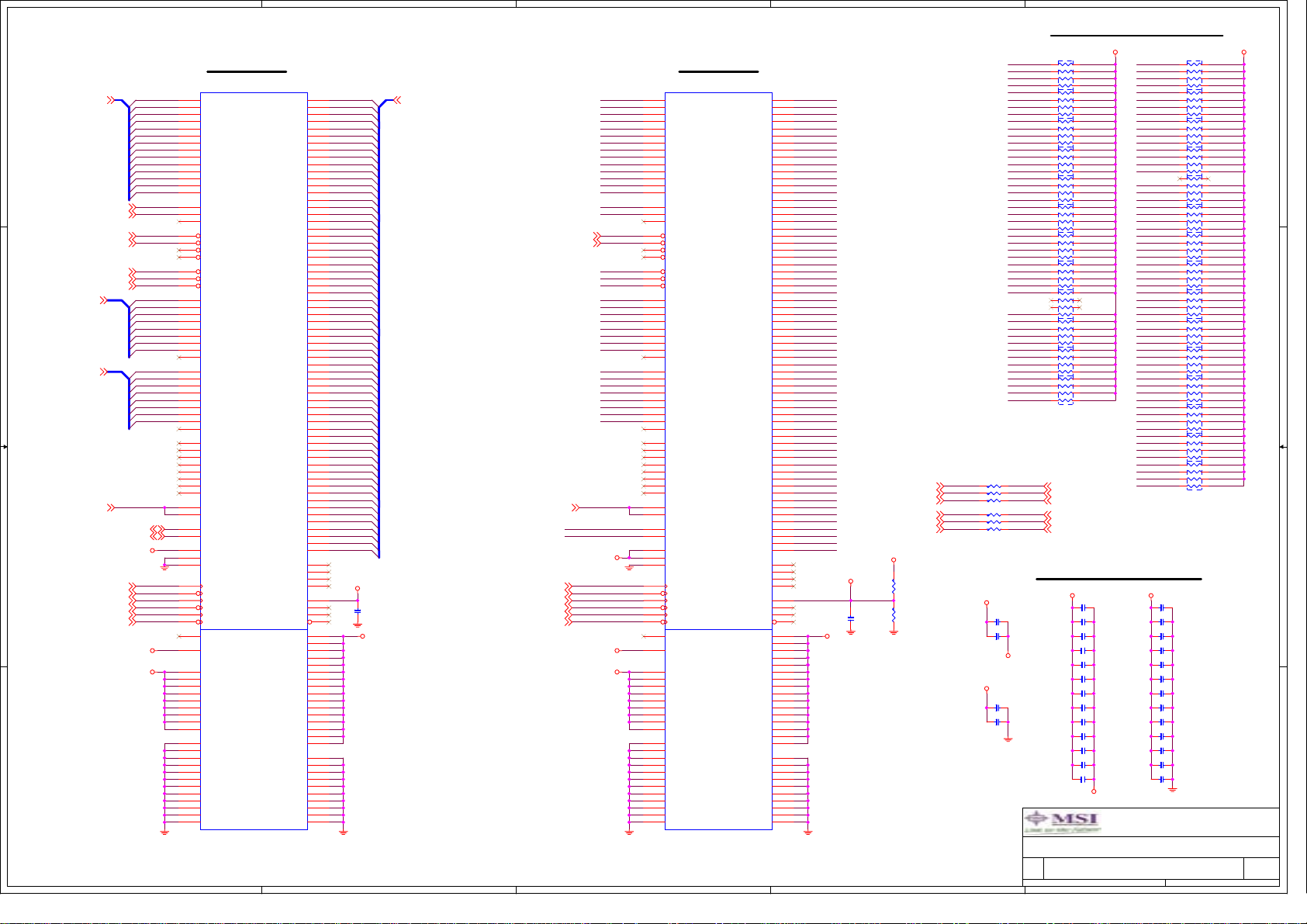

VDD_VTT_SUS_CPU is connected to the VDD_VTT_SUS power

supply through the package or on the die. It is only connected

on the board to decoupling near the CPU package.

VDDR_VREF

MBA_A19

MBA_A09

MRAS_A#9

MCAS_A#9

MWE_A#9

VTT_DDR

CPU_VTT_SENSE

MEM_ZN

MEM_ZP

MCS_1H#1

MCS_1H#0

MCS_1L#1

MCS_1L#0

MCS_2H#1

MCS_2H#0

MCS_2L#1

MCS_2L#0

MEM_CKED

MEM_CKEC

MEM_CKEB

MEM_CKEA

MA_A13

MA_A12

MA_A11

MA_A10

MA_A9

MA_A8

MA_A7

MA_A6

MA_A5

MA_A4

MA_A3

MA_A2

MA_A1

MA_A0

MRAS_A#

MCAS_A#

MWE_A#

AG14

AK14

AJ14

AH14

AF13

AF15

AE15

AL29

AJ29

AG28

AF29

AL28

AJ30

AG27

AE26

AF23

W25

AC27

AD27

AF27

AE28

B14

C14

D14

E14

F15

C25

B25

E25

G24

C26

E28

V27

F29

H25

G28

J26

J25

L27

L28

N26

P25

U25

MA_A13

MA_A12

MA_A11

MA_A10

MA_A9

MA_A8

MA_A7

MA_A6

MA_A5

MA_A4

MA_A3

MA_A2

MA_A1

MA_A0

MA_B13

MA_B12

MA_B11

MA_B10

MA_B9

MA_B8

MA_B7

MA_B6

MA_B5

MA_B4

MA_B3

MA_B2

MA_B1

MA_B0

VTT6

VTT7

VTT8

VTT1

VTT5

VTT4

VTT3

VTT2

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MEMCS_1H_L1

MEMCS_1H_L0

MEMCS_1L_L1

MEMCS_1L_L0

MEMCS_2H_L1

MEMCS_2H_L0

MEMCS_2L_L1

MEMCS_2L_L0

MEMCKED

MEMCKEC

MEMCKEB

MEMCKEA

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMBANKA1

MEMBANKA0

MEMRASA_L

MEMCASA_L

MEMWEA_L

DDR: CMD/CTRL/CLK

Athlon 64 939 Processor

CPU1B

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMWEB_L

AL22

AL23

A22

A23

R31

R30

AH23

AG23

D23

E23

R27

R26

AJ21

AH21

C21

D21

T31

U31

AF21

AE21

G21

G22

T27

U27

AK23

A26

A29

W30

C29

E29

D31

G29

F31

J31

K31

N28

N30

U29

Y31

AE30

AG30

AK29

AH31

D19

MEMCLK_1H_H2

MEMCLK_1H_L2

MEMCLK_1H_H1

MEMCLK_1H_L1

MEMCLK_1H_H0

MEMCLK_1H_L0

MEMCLK_1L_H2

MEMCLK_1L_L2

MEMCLK_1L_H1

MEMCLK_1L_L1

MEMCLK_1L_H0

MEMCLK_1L_L0

MEMCLK_2H_H2

MEMCLK_2H_L2

MEMCLK_2H_H1

MEMCLK_2H_L1

MEMCLK_2H_H0

MEMCLK_2H_L0

MEMCLK_2L_H2

MEMCLK_2L_L2

MEMCLK_2L_H1

MEMCLK_2L_L1

MEMCLK_2L_H0

MEMCLK_2L_L0

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMBANKB1

MEMBANKB0

MEMRASB_L

MEMCASB_L

MEMRESET_L

X_C22P50N0402C19

X_C22P50N0402C20

X_C22P50N0402C21

X_C22P50N0402C22

X_C22P50N0402C23C17

X_C22P50N0402C25

X_C22P50N0402C27

X_C22P50N0402C29

X_C22P50N0402C31

X_C22P50N0402C32

X_C22P50N0402C33

X_C22P50N0402C35

X_C22P50N0402C37

X_C22P50N0402C39 X_C22P50N0402C36

X_C22P50N0402C41

X_C22P50N0402C42

X_C22P50N0402C44

X_C22P50N0402C45

X_C22P50N0402C47

X_C22P50N0402C48

X_C22P50N0402C50

X_C22P50N0402C52

X_C22P50N0402C54

X_C22P50N0402C56

X_C22P50N0402C58

X_C22P50N0402C60

X_C22P50N0402C61

X_C22P50N0402C62

MA_B13

MA_B12

MA_B11

MA_B10

MA_B9

MA_B8

MA_B7

MA_B6

MA_B5

MA_B4

MA_B3

MA_B2

MA_B1

MA_B0

MBA_B1MBA_A1

MBA_B0MBA_A0

MRAS_B#

MCAS_B#

MWE_B#

MCS_2H#1

MCS_2H#0

MCS_2L#1

MCS_2L#0

MCS_1H#1

MCS_1H#0

MCS_1L#1

MCS_1L#0

MBA_A1

MBA_A0

MBA_B1

MBA_B0

MEM_CKED

MEM_CKEC

MEM_CKEB

MEM_CKEA

MRAS_A#

MCAS_A#

MWE_A#

MRAS_B#

MCAS_B#

MWE_B#

MCLK_1H2 10

MCLK_1H#2 10

MCLK_1H1 10

MCLK_1H#1 10

MCLK_1H0 10

MCLK_1H#0 10

MCLK_1L2 9

MCLK_1L#2 9

MCLK_1L1 9

MCLK_1L#1 9

MCLK_1L0 9

MCLK_1L#0 9

MCLK_2H2 10

MCLK_2H#2 10

MCLK_2H1 10

MCLK_2H#1 10

MCLK_2H0 10

MCLK_2H#0 10

MCLK_2L2 9

MCLK_2L#2 9

MCLK_2L1 9

MCLK_2L#1 9

MCLK_2L0 9

MCLK_2L#0 9

MBA_B1 10

MBA_B0 10

MRAS_B# 10

MCAS_B# 10

MWE_B# 10

DIMM2

DIMM1

DIMM4

DIMM3

DIMM2

DIMM4

X_C22P50N0402C576

X_C22P50N0402C577

X_C22P50N0402C578

X_C22P50N0402C579

X_C22P50N0402C24

X_C22P50N0402C26

X_C22P50N0402C28

X_C22P50N0402C30

X_C22P50N0402C34

X_C22P50N0402C38

X_C22P50N0402C40

X_C22P50N0402C580

X_C22P50N0402C43

X_C22P50N0402C581

X_C22P50N0402C46

X_C22P50N0402C49

X_C22P50N0402C51

X_C22P50N0402C53

X_C22P50N0402C55

X_C22P50N0402C57

X_C22P50N0402C59

MDQ_B[0..63]10 MDQ_A[0..63] 9

D D

C C

B B

MDQM_B[0..7]10

MDQS_B[0..7]10

A A

MDQ_B63

MDQ_B62

MDQ_B61

MDQ_B60

MDQ_B59

MDQ_B58

MDQ_B57

MDQ_B56

MDQ_B55

MDQ_B54

MDQ_B53

MDQ_B52

MDQ_B51

MDQ_B50

MDQ_B49

MDQ_B48

MDQ_B47

MDQ_B46

MDQ_B45

MDQ_B44

MDQ_B43

MDQ_B42

MDQ_B41

MDQ_B40

MDQ_B39

MDQ_B38

MDQ_B37

MDQ_B36

MDQ_B35

MDQ_B34

MDQ_B33

MDQ_B32

MDQ_B31

MDQ_B30

MDQ_B29

MDQ_B28

MDQ_B27

MDQ_B26

MDQ_B25

MDQ_B24

MDQ_B23

MDQ_B22

MDQ_B21

MDQ_B20

MDQ_B19

MDQ_B18

MDQ_B17

MDQ_B16

MDQ_B15

MDQ_B14

MDQ_B13

MDQ_B12

MDQ_B11

MDQ_B10

MDQ_B9

MDQ_B8

MDQ_B7

MDQ_B6

MDQ_B5

MDQ_B4

MDQ_B3

MDQ_B2

MDQ_B1

MDQ_B0

MDQM_B7

MDQM_B6

MDQM_B5

MDQM_B4

MDQM_B3

MDQM_B2

MDQM_B1

MDQM_B0

MDQS_B7

MDQS_B6

MDQS_B5

MDQS_B4

MDQS_B3

MDQS_B2

MDQS_B1

MDQS_B0

AJ15

AL16

AL18

AL19

AL15

AK15

AK17

AJ17

AH19

AL21

AJ23

AL25

AK19

AJ19

AL24

AK25

AJ25

AL26

AG29

AF31

AH25

AL27

AJ31

AG31

AE31

AD31

AB31

AA29

AE29

AC28

AC31

AA30

M31

H31

G31

G30

E30

C31

C27

D25

E31

C30

B27

A27

C23

B23

A20

B19

A25

A24

C19

A19

D17

B17

C15

A15

A18

C17

D15

B15

AA31

W29

N31

N29

W28

W31

R29

P31

V31

AL17

AK21

AK27

AC29

B29

B21

A16

U30

AH15

AL20

AJ27

AC30

A28

A21

A17

L30

L31

L29

J28

J30

J29

MEMDATA127

MEMDATA126

MEMDATA125

MEMDATA124

MEMDATA123

MEMDATA122

MEMDATA121

MEMDATA120

MEMDATA119

MEMDATA118

MEMDATA117

MEMDATA116

MEMDATA115

MEMDATA114

MEMDATA113

MEMDATA112

MEMDATA111

MEMDATA110

MEMDATA109

MEMDATA108

MEMDATA107

MEMDATA106

MEMDATA105

MEMDATA104

MEMDATA103

MEMDATA102

MEMDATA101

MEMDATA100

MEMDATA99

MEMDATA98

MEMDATA97

MEMDATA96

MEMDATA95

MEMDATA94

MEMDATA93

MEMDATA92

MEMDATA91

MEMDATA90

MEMDATA89

MEMDATA88

MEMDATA87

MEMDATA86

MEMDATA85

MEMDATA84

MEMDATA83

MEMDATA82

MEMDATA81

MEMDATA80

MEMDATA79

MEMDATA78

MEMDATA77

MEMDATA76

MEMDATA75

MEMDATA74

MEMDATA73

MEMDATA72

MEMDATA71

MEMDATA70

MEMDATA69

MEMDATA68

MEMDATA67

MEMDATA66

MEMDATA65

MEMDATA64

MEMCHECK15

MEMCHECK14

MEMCHECK13

MEMCHECK12

MEMCHECK11

MEMCHECK10

MEMCHECK9

MEMCHECK8

MEMDM_UP8

MEMDM_UP7

MEMDM_UP6

MEMDM_UP5

MEMDM_UP4

MEMDM_UP3

MEMDM_UP2

MEMDM_UP1

MEMDM_UP0

MEMDQS_UP8

MEMDQS_UP7

MEMDQS_UP6

MEMDQS_UP5

MEMDQS_UP4

MEMDQS_UP3

MEMDQS_UP2

MEMDQS_UP1

MEMDQS_UP0

CPU1C

DDR: DATA

MEMDQS_LO8

MEMDQS_LO7

MEMDQS_LO6

MEMDQS_LO5

MEMDQS_LO4

MEMDQS_LO3

MEMDQS_LO2

MEMDQS_LO1

MEMDQS_LO0

Athlon 64 939 Processor

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

MEMDM_LO8

MEMDM_LO7

MEMDM_LO6

MEMDM_LO5

MEMDM_LO4

MEMDM_LO3

MEMDM_LO2

MEMDM_LO1

MEMDM_LO0

AE16

AG17

AG18

AE18

AJ16

AG16

AE17

AJ18

AJ20

AE20

AE23

AG24

AG19

AE19

AJ24

AE24

AG25

AE25

AD25

AC25

AF25

AJ26

AE27

AD29

AB25

AB27

AA28

Y25

AC26

AB29

AA27

Y27

N25

M25

K27

K25

M29

M27

K29

J27

H27

G27

D27

F25

H29

G26

E26

G25

G23

F23

C20

F19

E24

C24

G19

E19

E18

G17

E16

E15

G18

C18

G16

C16

Y29

W27

P27

R25

W26

V25

R28

P29

V29

AF17

AG21

AH27

AA25

L26

F27

G20

E17

U26

AH17

AG20

AG26

AA26

L25

E27

E20

F17

MDQ_A63

MDQ_A62

MDQ_A61

MDQ_A60

MDQ_A59

MDQ_A58

MDQ_A57

MDQ_A56

MDQ_A55

MDQ_A54

MDQ_A53

MDQ_A52

MDQ_A51

MDQ_A50

MDQ_A49

MDQ_A48

MDQ_A47

MDQ_A46

MDQ_A45

MDQ_A44

MDQ_A43

MDQ_A42

MDQ_A41

MDQ_A40

MDQ_A39

MDQ_A38

MDQ_A37

MDQ_A36

MDQ_A35

MDQ_A34

MDQ_A33

MDQ_A32

MDQ_A31

MDQ_A30

MDQ_A29

MDQ_A28

MDQ_A27

MDQ_A26

MDQ_A25

MDQ_A24

MDQ_A23

MDQ_A22

MDQ_A21

MDQ_A20

MDQ_A19

MDQ_A18

MDQ_A17

MDQ_A16

MDQ_A15

MDQ_A14

MDQ_A13

MDQ_A12

MDQ_A11

MDQ_A10

MDQ_A9

MDQ_A8

MDQ_A7

MDQ_A6

MDQ_A5

MDQ_A4

MDQ_A3

MDQ_A2

MDQ_A1

MDQ_A0

MDQM_A7

MDQM_A6

MDQM_A5

MDQM_A4

MDQM_A3

MDQM_A2

MDQM_A1

MDQM_A0

MDQS_A7

MDQS_A6

MDQS_A5

MDQS_A4

MDQS_A3

MDQS_A2

MDQS_A1

MDQS_A0

MDQM_A[0..7] 9

MDQS_A[0..7] 9

R16

15R1%1206

R17

15R1%1206

VCC_DDR

R14

34.8R1%

CPU_VTT_SENSE30

R15

34.8R1%

MA_A[13..0]9 MA_B[13..0] 10

MCS_1H#110

MCS_1H#010

MCS_1L#19

MCS_1L#09

MCS_2H#110

MCS_2H#010

MCS_2L#19

MCS_2L#09

MEM_CKED10

MEM_CKEC10

MEM_CKEB9

MEM_CKEA9

DIMM1

DIMM3

VTT_DDR

VDDR_VREF

C64

C1000P50X

C18

C0.22U16X

C63

C0.1U25Y

C4.7U10Y0805

VCC_DDR

Title

ATHLON64 DDR MEMORY I/F

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7093 200

1

of

734Monday, November 15, 2004

5

VCORE VCC_DDR

R11

R13

R15

R17

R19

R21

T10

T12

T14

T16

T18

T20

U11

U13

U15

D D

VCORE

C C

H23

H26

H28

VSS136

VSS137

VSS1A7VSS2A9VSS3

AA6

VDD109

VDD1

AA4

VSS138

VSS139J6VSS140J8VSS141

VSS4

VSS5

AA8

AA10

VDD110

VDD2

AA7

AA9

J10

J12

VSS6

AA12

AA14

VDD111

VDD112

VDD3

VDD4

AA11

AA13

J14

J16

VSS142

VSS143

VSS7

VSS8

AA16

AA18

VDD113

VDD114

VDD115T2VDD116T6VDD117T8VDD118

VDD5

VDD6

VDD7

AA15

AA17

AA19

J18

J20

J22

VSS144

VSS145

VSS146

VSS9

VSS10

VSS11

AB2

AA20

AA22

VDD8

VDD9

VDD10

AB6

AB8

AA21

J24

VSS147

VSS148

VSS149K2VSS150K7VSS151K9VSS152

VSS12

VSS13

VSS14

AB7

AB9

AB11

VDD119

VDD120

VDD11

VDD12

AB10

VSS15

VSS16

AB13

VDD121

VDD13

AB12

AB14

K11

K13

VSS17

AB15

AB17

VDD122

VDD123

VDD124U4VDD125U7VDD126U9VDD127

VDD14

VDD15

VDD16

AB16

AB18

K15

K17

VSS153

VSS154

VSS155

VSS18

VSS19

VSS20

AB19

AB21

VDD17

AC9

AB20

K19

K21

VSS156

VSS21

AB23

AB26

VDD18

VDD19

AC11

K23

VSS157

VSS158

VSS22

VSS23

AB28

VDD128

VDD20

AC13

AC15

K26

K28

VSS159

VSS24

AC4

AC6

VDD129

VDD21

VSS160

VSS25

U17

U19

U21

VDD130

VDD131

VDD132

VDD133V6VDD134V8VDD135

VDD22

VDD23

VDD24

VDD25

AD2

AD6

AC17

AC19

L10

VSS161L4VSS162L6VSS163L8VSS164

VSS26

VSS27

VSS28

VSS29

AC10

AC12

AC14

AC16

V10

VDD26

AD8

AD10

L12

L14

VSS165

VSS30

AC18

AC20

4

V12

VDD136

VDD27

VDD28

AD12

L16

VSS166

VSS167

VSS31

VSS32

AC22

V14

V16

VDD137

VDD29

AD14

AD16

L18

L20

VSS168

VSS33

AD7

AC24

V18

V20

VDD138

VDD139

VDD30

VDD31

AE4

AD18

L22

L24

VSS169

VSS170

VSS34

VSS35

AD9

AD11

W11

VDD140

VDD141W7VDD142W9VDD143

VDD32

VDD33

VDD34

AE7

AE9

AE11

M11

VSS171

VSS172M7VSS173M9VSS174

VSS36

VSS37

VSS38

AD13

AD15

AD17

W13

VDD144

VDD35

VDD36

AJ11

M13

VSS175

VSS39

VSS40

AD19

W15

W17

VDD145

VDD37

AK5

AK7

M15

M17

VSS176

VSS41

AD21

AD23

W19

W21

VDD146

VDD147

VDD38

VDD39

AK9

AK11

M19

M21

VSS177

VSS178

VSS42

VSS43

AD26

AD28

Y10

VDD148

VDD149Y2VDD150Y6VDD151Y8VDD152

VDD40

VDD41B5VDD42

VDD43

B10

B12

D10

M23

M26

M28

VSS179

VSS180

VSS181

VSS182

VSS44

VSS45

VSS46

VSS47

AE6

AE8

AE10

AE12

Y12

Y14

Y16

VDD153

VDD154

VDD155

VDD44

VDD45G7VDD46G9VDD47

G11

N10

N12

VSS183N6VSS184N8VSS185

VSS186

VSS48

VSS49

VSS50

VSS51

AF2

AF6

AE14

Y18

Y20

VDD156

VDD157

VDD48

VDD49H2VDD50H6VDD51H8VDD52

G13

N14

N16

N18

VSS187

VSS188

VSS189

VSS52

VSS53

VSS54

AF7

AF9

AF11

AA23

AB22

VDDIO1

H10

N20

N22

VSS190

VSS55

AF14

AF16

AB24

AB30

AC21

VDDIO2

VDDIO3

VDDIO4

VDD53

VDD54

H12

H14

H16

N24

VSS191

VSS192

VSS193P2VSS194P7VSS195P9VSS196

VSS56

VSS57

VSS58

AF20

AF22

AF24

AC23

AD20

VDDIO5

VDDIO6

VDDIO7

VDD55

VDD56

VDD57J4VDD58J7VDD59J9VDD60

H18

P11

VSS59

VSS60

VSS61

AF26

AF28

AD22

AD24

VDDIO8

P13

P15

VSS197

VSS62

AG5

AG11

AD30

AF30

VDDIO9

VDDIO10

J11

J13

P17

P19

VSS198

VSS199

VSS63

VSS64

AG13

AG12

AH30

AK16

VDDIO11

VDDIO12

VDDIO13

VDD61

VDD62

VDD63

J15

J17

P21

P23

VSS200

VSS201

VSS202

VSS65

VSS66

VSS67

AH1

AH2

3

AK18

AK20

VDDIO14

VDDIO15

VDD64

VDD65K6VDD66K8VDD67

J19

P26

P28

VSS203

VSS204

VSS68

VSS69

AH3

AH4

AK22

AH5

AK24

AK26

AK28

AK30

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDD68

VDD69

VDD70

K10

K12

K14

K16

R10

R12

VSS205R4VSS206R6VSS207R8VSS208

VSS209

VSS70

VSS71

VSS72

VSS73

VSS74

AH7

AH9

AH11

AH13

B16

B18

VDDIO21

VDDIO22

VDD71

VDD72

K18

K20

R14

R16

VSS210

VSS211

VSS75

VSS76

AH16

AH18

B20

B22

B24

VDDIO23

VDDIO24

VDDIO25

VDD73L7VDD74L9VDD75

L11

R18

R20

R22

VSS212

VSS213

VSS214

VSS77

VSS78

VSS79

AH20

AH22

AH24

B26

B28

B30

VDDIO26

VDDIO27

VDD76

VDD77

L13

L15

L17

R24

VSS215

VSS216T7VSS217T9VSS218

VSS80

VSS81

AJ3

AH26

AH28

D30

F30

VDDIO28

VDDIO29

VDDIO30

VDD78

VDD79

VDD80

L19

L21

T11

T13

VSS219

VSS82

VSS83

VSS84

AJ13

AK13

H20

VDDIO31

VDD81M2VDD82M6VDD83M8VDD84

T15

VSS220

VSS85

AL13

H22

H24

H30

J21

J23

K22

K24

K30

L23

M22

M24

M30

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90N4VDD91N7VDD92N9VDD93

M16

M18

M20

T28

VSS226

VSS227U6VSS228U8VSS229

U10

U12

U14

VSS230

N11

U16

VSS231

VSS232

D13

M10

M12

M14

T17

T19

T21

T23

T26

VSS221

VSS222

VSS223

VSS224

VSS225

VSS86B7VSS87B9VSS88C2VSS89C8VSS90C9VSS91D2VSS92D3VSS93D5VSS94D6VSS95D7VSS96D9VSS97

N23

P22

VDDIO44

VDDIO45

VDD94

VDD95

N13

N15

U18

U20

VSS233

VSS234

VSS98

VSS99

D16

D18

P24

P30

VDDIO46

VDDIO47

VDD96

VDD97

N17

N19

U22

U24

VSS235

VSS236

VSS100

VSS101

D20

D22

R23

N21

D24

2

T22

T24

T30

U23

VDDIO48

VDDIO49

VDDIO50

VDDIO51

VDDIO52

VDD98

VDD99P6VDD100P8VDD101

VDD102

P10

P12

V11

V13

VSS237V2VSS238V7VSS239V9VSS240

VSS241

VSS102

VSS103

VSS104

VSS105E3VSS106E4VSS107

D26

D28

V22

V24

VDDIO53

VDDIO54

VDD103

VDD104

P14

P16

V15

V17

VSS242

VSS243

VSS108

E10

E12

V30

P18

V19

G12

W23

Y22

Y30

CPU1E

VDDIO55

VDDIO56

VDDIO57

VDDIO58

VDD105

VDD106

VDD107R7VDD108

POWER

R9

P20

V21

V23

V26

V28

VSS244

VSS245

VSS246

VSS247

VSS248

VSS109

VSS110F5VSS111F6VSS112F7VSS113F9VSS114

F10

W10

W12

W14

VSS249W4VSS250W6VSS251W8VSS252

VSS253

VSS115

VSS116

VSS117

VSS118

F12

F14

F16

F18

F22

W16

VSS254

VSS255

VSS119

VSS120

F24

W18

W20

VSS256

VSS121

F26

F28

W22

VSS257

VSS122

W24

Y11

VSS258

VSS259

VSS260Y7VSS261Y9VSS262

VSS123G4VSS124G6VSS125G8VSS126

VSS127

G10

G14

Y13

Y15

Y17

Y19

VSS263

VSS264

VSS265

VSS128H7VSS129H9VSS130

H11

H13

Y21

VSS266

VSS267

VSS131

VSS132

H15

Y23

Y26

VSS268

VSS133

H17

H19

Y28

VSS269

VSS270

VSS134

VSS135

H21

1

CPU1F

GROUND

B B

VCORE

VCC_DDR

VCC_DDR VTT_DDR

A A

5

Bottomside Decoupling

C83

C0.22U16X

C84

C0.22U16X

C72

C10U10Y1206

C86

C0.22U16X

C85

C0.22U16X

4

C73

C10U10Y1206

C89

C4.7U10Y0805

C69

C10U10Y1206

C81

C4.7U10Y0805

C87

C0.22U16X

C70

C10U10Y1206

C82

C4.7U10Y0805

C88

C0.22U16X

C71

C10U10Y1206

C74

C10U10Y1206

C90

C4.7U10Y0805

C93

C4.7U10Y0805

C75

C0.22U16X

C91

C4.7U10Y0805

C94

C0.22U16X

C76

C0.22U16X

C95

C0.22U16X

C77

C0.22U16X

C92

C4.7U10Y0805

C78

C0.22U16X

3

C79

C0.22U16X

C80

C0.22U16X

Title

ATHLON64 PWR & GND

Size Document Number Re v

Custom

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7093 200

1

of

834Monday, November 15, 2004

5

4

3

2

1

DDR Terminational Resisitors

DDR DIMM1

DIMM1

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

157

158

71

163

154

65

63

5

14

25

36

56

67

78

86

47

97

107

119

129

149

159

169

177

140

44

45

49

51

134

135

142

144

21

111

92

91

181

182

183

16

17

137

138

76

75

82

184

7

38

46

70

85

108

120

148

168

81

89

93

100

116

124

132

139

145

152

160

176

DIMM-184_blue

SIGNALS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/NC

A13/NC

BA0

BA1

NC/BA2

CS0#

CS1#

NC/CS2#

NC/CS3#

RAS#

CAS#

WE#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQM0/DQS9

DQM1/DQS10

DQM2/DQS11

DQM3/DQS12

DQM4/DQS13

DQM5/DQS14

DQM6/DQS15

DQM7/DQS16

DQM8/DQS17

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

CKE0

CKE1

SCL

SDA

SA0

SA1

SA2

CK0/NC

CK0#/NC

CK1/CK0

CK1#/CK0#

CK2/NC

CK2#/NC

ID_VDD

SPD_VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

POWER

FETEN/NC

NC/RESET#

MBA_A07

MBA_A17

MWE_A#7

MEM_CKEA

SMB_CLK

SMB_DATA

VCC_DDR

VCC_DDR

MA_A0

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

MA_A13

MBA_A0

MBA_A1

MCS_1L#0

MCS_1L#1

MRAS_A#

MCAS_A#

MWE_A#

MDQS_A0

MDQS_A1

MDQS_A2

MDQS_A3

MDQS_A4

MDQS_A5

MDQS_A6

MDQS_A7

MDQM_A0

MDQM_A1

MDQM_A2

MDQM_A3

MDQM_A4

MDQM_A5

MDQM_A6

MDQM_A7

MA_A[13..0]7

D D

MCS_1L#07

MCS_1L#17

MRAS_A#7

MCAS_A#7

MDQS_A[0..7]7

C C

MDQM_A[0..7]7

MEM_CKEA7

SMB_CLK6,10,14,17,25,28,30

SMB_DATA6,10,14,17,25,28,30

B B

MCLK_1L17

MCLK_1L#17

MCLK_1L07

MCLK_1L#07

MCLK_1L27

MCLK_1L#27

A A

ADDR.=1010000B

5

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

MDQ_A0

2

MDQ_A1

4

MDQ_A2

6

MDQ_A3

8

MDQ_A4

94

MDQ_A5

95

MDQ_A6

98

MDQ_A7

99

MDQ_A8

12

MDQ_A9

13

MDQ_A10

19

MDQ_A11

20

MDQ_A12

105

MDQ_A13

106

MDQ_A14

109

MDQ_A15

110

MDQ_A16

23

MDQ_A17

24

MDQ_A18

28

MDQ_A19

31

MDQ_A20

114

MDQ_A21

117

MDQ_A22

121

MDQ_A23

123

MDQ_A24

33

MDQ_A25

35

MDQ_A26

39

MDQ_A27

40

MDQ_A28

126

MDQ_A29

127

MDQ_A30

131

MDQ_A31

133

MDQ_A32

53

MDQ_A33

55

MDQ_A34

57

MDQ_A35

60

MDQ_A36

146

MDQ_A37

147

MDQ_A38

150

MDQ_A39

151

MDQ_A40

61

MDQ_A41

64

MDQ_A42

68

MDQ_A43

69

MDQ_A44

153

MDQ_A45

155

MDQ_A46

161

MDQ_A47

162

MDQ_A48

72

MDQ_A49

73

MDQ_A50

79

MDQ_A51

80

MDQ_A52

165

MDQ_A53

166

MDQ_A54

170

MDQ_A55

171

MDQ_A56

83

MDQ_A57

84

MDQ_A58

87

MDQ_A59

88

MDQ_A60

174

MDQ_A61

175

MDQ_A62

178

MDQ_A63

179

9

NC

101

NC

102

NC

173

NC

1

90

WP

103

10

15

22

30

54

62

77

96

104

112

128

136

143

156

164

172

180

3

11

18

26

34

42

50

58

66

74

C0.1U25Y

VCC_DDR

4

MDQ_A[0..63] 7

DDR_VREF1

C67

VCC_DDR

R21

75R1%

R23

75R1%

MCS_2L#07

MCS_2L#17

MEM_CKEB7

MCLK_2L17

MCLK_2L#17

MCLK_2L07

MCLK_2L#07

MCLK_2L27

MCLK_2L#27

SMB_CLK

SMB_DATA

VCC_DDR

VCC_DDR

VCC_DDR

MA_A0

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

MA_A13

MBA_A0

MBA_A1

MCS_2L#0

MCS_2L#1

MRAS_A#

MCAS_A#

MWE_A#

MDQS_A0

MDQS_A1

MDQS_A2

MDQS_A3

MDQS_A4

MDQS_A5

MDQS_A6

MDQS_A7

MDQM_A0

MDQM_A1

MDQM_A2

MDQM_A3

MDQM_A4

MDQM_A5

MDQM_A6

MDQM_A7

130

125

122

141

118

115

167

113

157

158

163

154

107

119

129

149

159

169

177

140

134

135

142

144

111

181

182

183

137

138

184

108

120

148

168

100

116

124

132

139

145

152

160

176

3

DDR DIMM3

DIMM3

48

SIGNALS

A0

43

A1

41

A2

A3

37

A4

32

A5

A6

29

A7

A8

27

A9

A10/AP

A11

A12/NC

A13/NC

59

BA0

52

BA1

NC/BA2

CS0#

CS1#

71

NC/CS2#

NC/CS3#

RAS#

65

CAS#

63

WE#

5

DQS0

14

DQS1

25

DQS2

36

DQS3

56

DQS4

67

DQS5

78

DQS6

86

DQS7

47

DQS8

97

DQM0/DQS9

DQM1/DQS10

DQM2/DQS11

DQM3/DQS12

DQM4/DQS13

DQM5/DQS14

DQM6/DQS15

DQM7/DQS16

DQM8/DQS17

44

MECC0

45

MECC1

49

MECC2

51

MECC3

MECC4

MECC5

MECC6

MECC7

21

CKE0

CKE1

92

SCL

91

SDA

SA0

SA1

SA2

16

CK0/NC

17

CK0#/NC

CK1/CK0

CK1#/CK0#

76

CK2/NC

75

CK2#/NC

82

POWER

ID_VDD

SPD_VDD

7

VDD

38

VDD

46

VDD

70

VDD

85

VDD

VDD

VDD

VDD

VDD

81

GND

89

GND

93

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

DIMM-184_green

ADDR.=1010010B

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

FETEN/NC

NC/RESET#

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VTT_DDR

MDQ_A40

1 2

MDQ_A0

2

MDQ_A1

4

MDQ_A2

6

MDQ_A3

8

MDQ_A4

94

MDQ_A5

95

MDQ_A6

98

MDQ_A7

99

MDQ_A8

12

MDQ_A9

13

MDQ_A10

19

MDQ_A11

20

MDQ_A12

105

MDQ_A13

106

MDQ_A14

109

MDQ_A15

110

MDQ_A16

23

MDQ_A17

24

MDQ_A18

28

MDQ_A19

31

MDQ_A20

114

MDQ_A21

117

MDQ_A22

121

MDQ_A23

123

MDQ_A24

33

MDQ_A25

35

MDQ_A26

39

MDQ_A27

40

MDQ_A28

126

MDQ_A29

127

MDQ_A30

131

MDQ_A31

133

MDQ_A32

53

MDQ_A33

55

MDQ_A34

57

MDQ_A35

60

MDQ_A36

146

MDQ_A37

147

MDQ_A38

150

MDQ_A39

151

MDQ_A40

61

MDQ_A41

64

MDQ_A42

68

MDQ_A43

69

MDQ_A44

153

MDQ_A45

155

MDQ_A46

161

MDQ_A47

162

MDQ_A48

72

MDQ_A49

73

MDQ_A50

79

MDQ_A51

80

MDQ_A52

165

MDQ_A53

166

MDQ_A54

170

MDQ_A55

171

MDQ_A56

83

MDQ_A57

84

MDQ_A58

87

MDQ_A59

88

MDQ_A60

174

MDQ_A61

175

MDQ_A62

178

MDQ_A63

179

9

NC

101

NC

102

NC

173

NC

DDR_VREF2

1

90

WP

103

10

15

22

30

54

62

77

96

104

112

128

136

143

156

164

172

VCC_DDR

180

3

11

18

26

34

42

50

58

66

74

MCLK_1L27

MCLK_1L17

MCLK_1L07 MCLK_1L#0 7

MCLK_2L27

MCLK_2L17

MCLK_2L07

DECOUPLING CAPACITORS

DDR_VREF2

VCC_DDR

C582

C1000P50X

VCC_DDR

VTT_DDR

VCC_DDR

C959

X_C4.7U10X1206

C960

X_C4.7U10X1206

C961

X_C4.7U10X1206

C962

X_C4.7U10X1206

2

MDQ_A44

3 4

MDQ_A35

5 6

MBA_A0

7 8

MDQ_A41

1 2

MWE_A#

3 4

MDQ_A45

5 6

MRAS_A#

7 8

MDQ_A42

1 2

MDQS_A5

3 4

MDQM_A5

5 6

MCS_2L#1

7 8

MDQ_A48

1 2

MDQ_A47

3 4

MDQ_A43

5 6

MDQ_A46

7 8

MA_A13

1 2

MDQ_A53

3 4

MDQ_A49

5 6

MDQ_A52

7 8

MDQ_A55

1 2

MDQ_A54

3 4

MDQS_A6

5 6

MDQM_A6

7 8

MDQ_A61

1 2

MDQ_A60

3 4

MDQ_A51

5 6

MDQ_A50

7 8

MDQ_A62

1 2

MDQM_A7

3 4

MDQ_A57

5 6

MDQ_A56

7 8

MDQ_A59

1 2

MDQ_A58

3 4

MDQ_A63 MDQ_A19

5 6

MDQS_A7

7 8

1 2

MA_A1

3 4

5 6

MA_A2

7 8

MCS_1L#1

1 2

MCAS_A#

3 4

MCS_1L#0

5 6

MCS_2L#0

7 8

CB29

C0.1U25Y

CB35

X_C0.1U25Y

CB44

C0.1U25Y

CB49

C0.1U25Y

C964

X_C0.1U25Y

CB28

C0.22U16X

CB34

C0.22U16X

CB43

C0.1U25Y

CB48

C0.1U25Y

R18 120R

R19 120R

R20 120R

R570 120R

R571 120R

R572 120R

VTT_DDR

VCC_DDR

MCLK_1L#2 7

MCLK_1L#1 7

MCLK_2L#2 7

MCLK_2L#1 7

MCLK_2L#0 7

VTT_DDR

CB5

C0.1U10X0402

CB8

C0.1U10X0402

CB11

C0.1U10X0402

CB14

C0.1U10X0402

CB23

X_C0.1U10X0402

CB27

X_C0.1U25Y

CB33

C0.22U16X

CB39

C0.22U16X

CB42

C0.1U25Y

CB47

C0.22U16X

CB50

C0.22U16X

Title

CB51

C0.1U25Y

CB52

C0.1U25Y

Size Document Number Re v

Custom

Date: Sheet

RN6

8P4R-47R0402

RN8

8P4R-47R0402

RN10

8P4R-47R0402

RN12

8P4R-47R0402

RN14

8P4R-47R0402

RN16

8P4R-47R0402

RN18

8P4R-47R0402

RN20

8P4R-47R0402

RN22

8P4R-47R0402

RN28

8P4R-47R0402

RN30

8P4R-47R0402

MDQ_A1

1 2

MDQ_A5

3 4

MDQ_A0

5 6

MDQ_A4

7 8

MDQ_A2

1 2

MDQ_A6

3 4

MDQS_A0

5 6

MDQM_A0

7 8

MDQ_A8

1 2

MDQ_A12

3 4

MDQ_A3

5 6

MDQ_A7

7 8

MDQM_A1

1 2

MDQS_A1

3 4

MDQ_A9

5 6

MDQ_A13

7 8

MDQ_A11

1 2

MDQ_A10

3 4

MDQ_A15

5 6

MDQ_A14

7 8

MDQS_A2

1 2

MDQ_A21

3 4

MDQ_A17

5 6

MDQ_A16

7 8

MDQ_A18

1 2

MA_A9

3 4

MDQM_A2

5 6

MA_A11

7 8

1 2

MA_A8

3 4

MA_A7

5 6

MDQ_A22

7 8

MA_A6

1 2

MA_A5

3 4

5 6

MDQ_A23

7 8

MA_A12

1 2

MDQ_A20

3 4

MEM_CKEB

5 6

MEM_CKEA

7 8

MDQ_A25

1 2

MDQ_A29

3 4

MDQ_A28

5 6

MDQ_A24

7 8

MDQ_A31

1 2

MDQ_A27

3 4

MDQ_A26

5 6

MDQ_A30

7 8

MDQ_A32

1 2

MBA_A1

3 4

MA_A10

5 6

MA_A0

7 8

MDQS_A4

1 2

MDQ_A33

3 4

MDQ_A37

5 6

MDQ_A36

7 8

MDQ_A39

1 2

MDQ_A38

3 4

MDQ_A34

5 6

MDQM_A4

7 8

MA_A3

1 2

MA_A4

3 4

MDQM_A3

5 6

MDQS_A3

7 8

VCC_DDR

CB1

C0.1U10X0402

CB3

C0.1U10X0402

CB6

C0.1U10X0402

CB9

X_C1U16Y0805

CB12

C0.1U10X0402

CB15

C0.1U10X0402

CB17

C0.1U10X0402

CB20

C0.1U10X0402

CB24

C0.1U10X0402

CB30

C0.1U10X0402

CB36

X_C1U16Y0805

CB40

C0.1U10X0402

CB45

C0.1U10X0402

VTT_DDR

MICRO-START INT'L CO.,LTD.

FIRST LO GI CAL DDR DIMM

MS-7093 200

RN7

8P4R-47R0402

RN9

8P4R-47R0402

RN11

8P4R-47R0402

RN13

8P4R-47R0402

RN15

8P4R-47R0402

RN17

8P4R-47R0402

RN19

8P4R-47R0402

RN21

8P4R-47R0402

RN23

8P4R-47R0402

RN25

8P4R-47R0402

RN27

8P4R-47R0402

RN29

8P4R-47R0402

RN31

8P4R-47R0402

RN32

8P4R-47R0402

RN33

8P4R-47R0402

RN34

8P4R-47R0402

CB2

C0.1U10X0402

CB4

C0.1U10X0402

CB7

C0.1U10X0402

CB10

C0.1U10X0402

CB13

VCC_DDR

C0.1U10X0402

CB16

C0.1U10X0402

CB18

C1000P50X

CB21

C0.1U10X0402

CB25

C0.1U10X0402

CB31

C0.1U10X0402

CB37

X_C1U16Y0805

CB41

C0.1U10X0402

CB46

C0.1U10X0402

1

VTT_DDR

VTT_DDR

934Monday, November 15, 2004

CB19

C0.1U10X0402

CB22

C0.1U10X0402

CB26

C0.1U10X0402

CB32

C1000P50X

CB38

C0.1U10X0402

of

5

4

3

2

1

SYSTEM MEMORY

DDR DIMM2

DIMM2

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

157

158

71

163

154

65

63

5

14

25

36

56

67

78

86

47

97

107

119

129

149

159

169

177

140

44

45

49

51

134

135

142

144

21

111

92

91

181

182

183

16

17

137

138

76

75

82

184

7

38

46

70

85

108

120

148

168

81

89

93

100

116

124

132

139

145

152

160

176

DIMM-184_blue

SIGNALS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/NC

A13/NC

BA0

BA1

NC/BA2

CS0#

CS1#

NC/CS2#

NC/CS3#

RAS#

CAS#

WE#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQM0/DQS9

DQM1/DQS10

DQM2/DQS11

DQM3/DQS12

DQM4/DQS13

DQM5/DQS14

DQM6/DQS15

DQM7/DQS16

DQM8/DQS17

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

CKE0

CKE1

SCL

SDA

SA0

SA1

SA2

CK0/NC

CK0#/NC

CK1/CK0

CK1#/CK0#

CK2/NC

CK2#/NC

ID_VDD

SPD_VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

POWER

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

FETEN/NC

NC/RESET#

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

MDQ_B0

2

MDQ_B1

4

MDQ_B2

6

MDQ_B3

8

MDQ_B4

94

MDQ_B5

95

MDQ_B6

98

MDQ_B7

99

MDQ_B8

12

MDQ_B9

13

MDQ_B10

19

MDQ_B11

20

MDQ_B12

105

MDQ_B13

106

MDQ_B14

109

MDQ_B15

110

MDQ_B16

23

MDQ_B17

24

MDQ_B18

28

MDQ_B19

31

MDQ_B20

114

MDQ_B21

117

MDQ_B22

121

MDQ_B23

123

MDQ_B24

33

MDQ_B25

35

MDQ_B26

39

MDQ_B27

40

MDQ_B28

126

MDQ_B29

127

MDQ_B30

131

MDQ_B31

133

MDQ_B32

53

MDQ_B33

55

MDQ_B34

57

MDQ_B35

60

MDQ_B36

146

MDQ_B37

147

MDQ_B38

150

MDQ_B39

151

MDQ_B40

61

MDQ_B41

64

MDQ_B42

68

MDQ_B43

69

MDQ_B44

153

MDQ_B45

155

MDQ_B46

161

MDQ_B47

162

MDQ_B48

72

MDQ_B49

73

MDQ_B50

79

MDQ_B51

80

MDQ_B52

165

MDQ_B53

166

MDQ_B54

170

MDQ_B55

171

MDQ_B56

83

MDQ_B57

84

MDQ_B58

87

MDQ_B59

88

MDQ_B60

174

MDQ_B61

175

MDQ_B62

178

MDQ_B63

179

9

NC

101

NC

102

NC

DDR_VREF1

173

NC

1

90

WP

103

10

15

22

30

54

62

77

96

104

112

128

136

143

156

164

172

180

3

11

18

26

34

42

50

58

66

74

C68

C0.1U25Y

VCC_DDR

MDQ_B[0..63] 7

MCS_2H#07

MCS_2H#17

MEM_CKED7

MCLK_2H17

MCLK_2H#17

MCLK_2H07

MCLK_2H#07

MCLK_2H27

MCLK_2H#27

MBA_B07

MBA_B17

MWE_B#7

SMB_CLK6,9,14,17,25,28,30

SMB_DATA6,9,14,17,25,28,30

VCC_DDR

VCC_DDR

VCC_DDR

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MA_B12

MA_B13

MBA_B0

MBA_B1

MCS_1H#0

MCS_1H#1

MRAS_B#

MCAS_B#

MWE_B#

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

MDQM_B0

MDQM_B1

MDQM_B2

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

MEM_CKEC

MA_B[13..0]7

D D

MCS_1H#07

MCS_1H#17

MRAS_B#7

MCAS_B#7

MDQS_B[0..7]7

C C

MDQM_B[0..7]7

MEM_CKEC7

B B

MCLK_1H17

MCLK_1H#17

MCLK_1H07

MCLK_1H#07

MCLK_1H27

MCLK_1H#27

A A

ADDR.=1010001B

5

4

MEM_CKED

SMB_CLK

SMB_DATA

VCC_DDR

VCC_DDR

VCC_DDR

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MA_B12

MA_B13

MBA_B0

MBA_B1

MCS_2H#0

MCS_2H#1

MRAS_B#

MCAS_B#

MWE_B#

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

MDQM_B0

MDQM_B1

MDQM_B2

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

DDR DIMM4

DIMM4

48

A0

43

A1

41

A2

130

A3

37

A4

32

A5

125

A6

29

A7

122

A8

27

A9

141

A10/AP

118

A11

115

A12/NC

167

A13/NC

59

BA0

52

BA1

113

NC/BA2

157

CS0#

158

CS1#

71

NC/CS2#

163

NC/CS3#

154

RAS#

65

CAS#

63

WE#

5

DQS0

14

DQS1

25

DQS2

36

DQS3

56

DQS4

67

DQS5

78

DQS6

86

DQS7

47

DQS8

97

DQM0/DQS9

107

DQM1/DQS10

119

DQM2/DQS11

129

DQM3/DQS12

149

DQM4/DQS13

159

DQM5/DQS14

169

DQM6/DQS15

177

DQM7/DQS16

140

DQM8/DQS17

44

MECC0

45

MECC1

49

MECC2

51

MECC3

134

MECC4

135

MECC5

142

MECC6

144

MECC7

21

CKE0

111

CKE1

92

SCL

91

SDA

181

SA0

182

SA1

183

SA2

16

CK0/NC

17

CK0#/NC

137

CK1/CK0

138

CK1#/CK0#

76

CK2/NC

75

CK2#/NC

82

ID_VDD

184

SPD_VDD

7

VDD

38

VDD

46

VDD

70

VDD

85

VDD

108

VDD

120

VDD

148

VDD

168

VDD

81

GND

89

GND

93

GND

100

GND

116

GND

124

GND

132

GND

139

GND

145

GND

152

GND

160

GND

176

GND

DIMM-184_green

ADDR.=1010011B

3

SIGNALS

POWER

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

FETEN/NC

NC/RESET#

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND