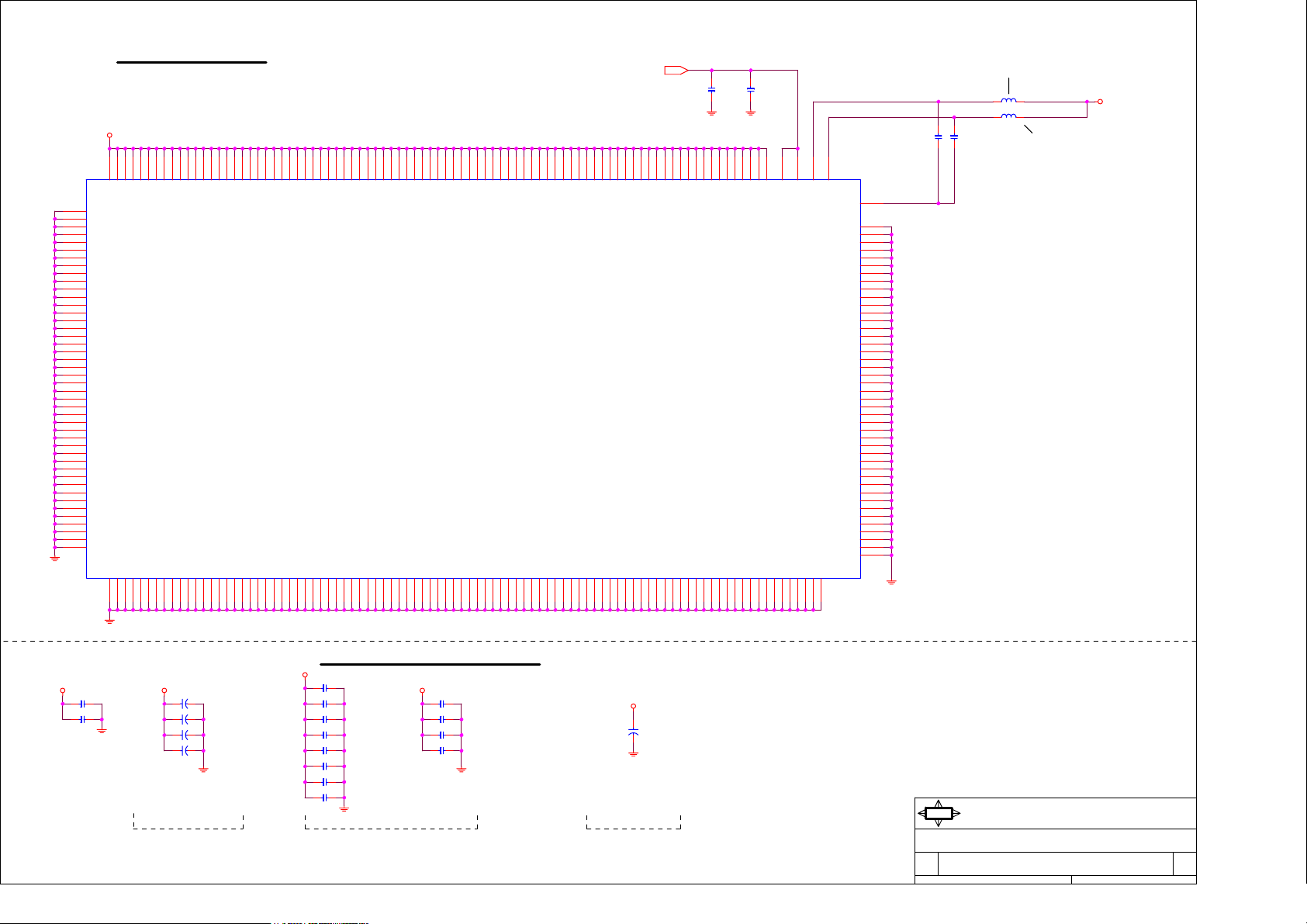

MSI MS-7072 Schematics

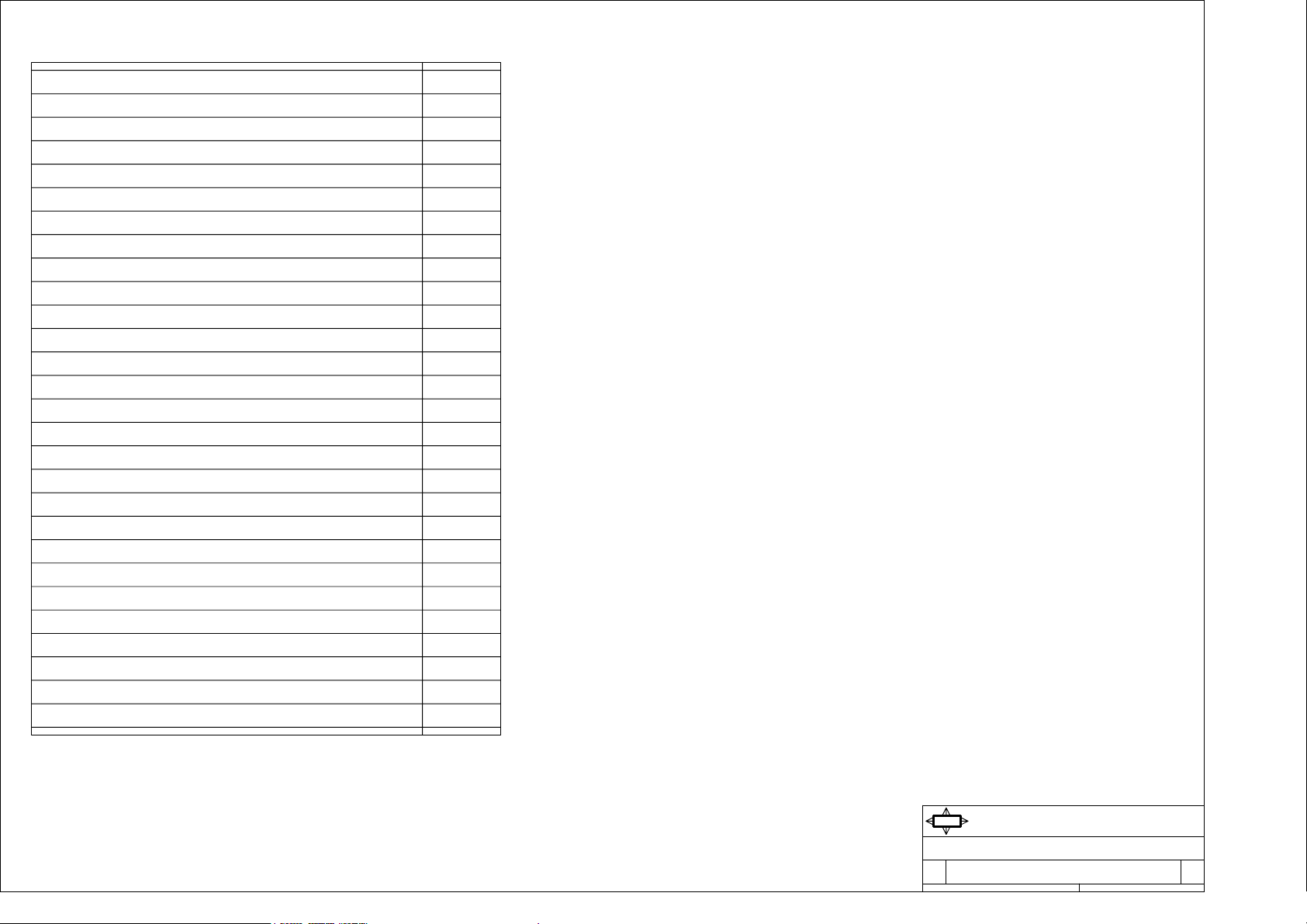

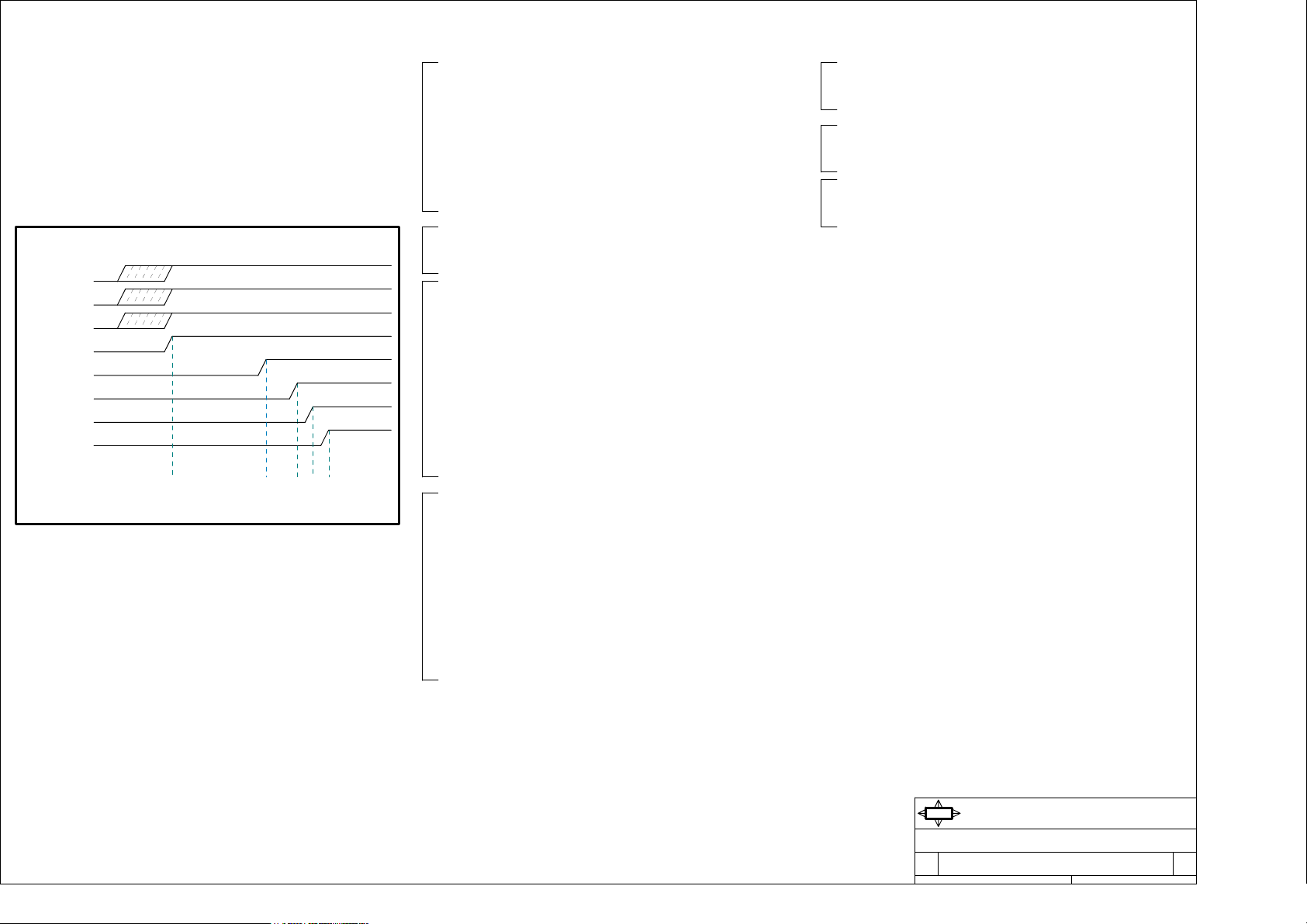

Cover Sheet, Block diagram, History, Power rails

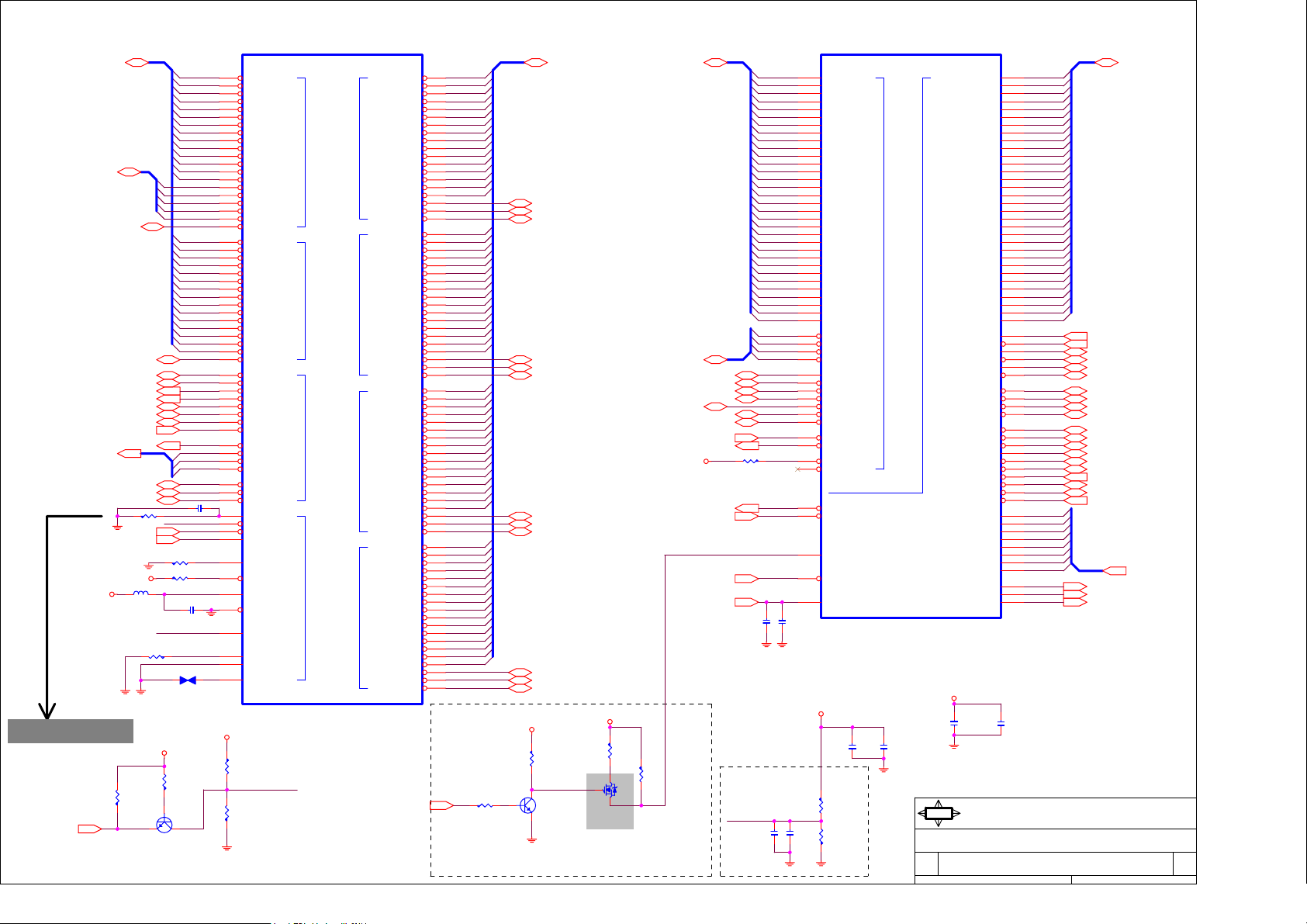

Intel µPGA478B CPU - Signals

Intel µPGA478B CPU - Power

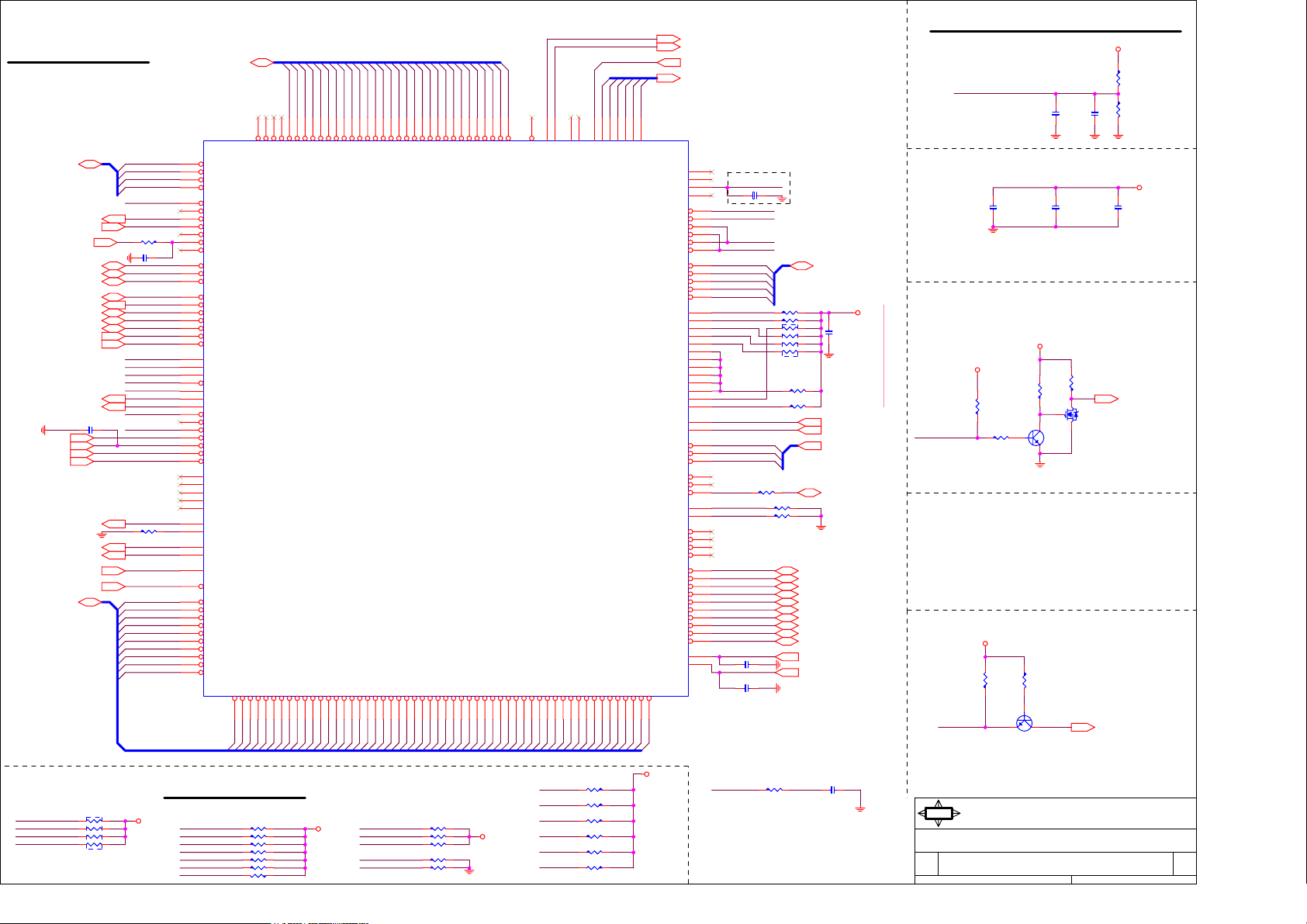

ATi RS300 - CPU & AGP & A-LINK

ATi RS300 - MEMORY A & B signals

ATi RS300 - VIDEO & CLK & PWR & Straps

SB300 - A-LINK & PCI & CPU & LPC & PWR

SB300 - IDE & SATA & GPIO & ACPI

SB300 - USB & MII & AC'97 & Straps

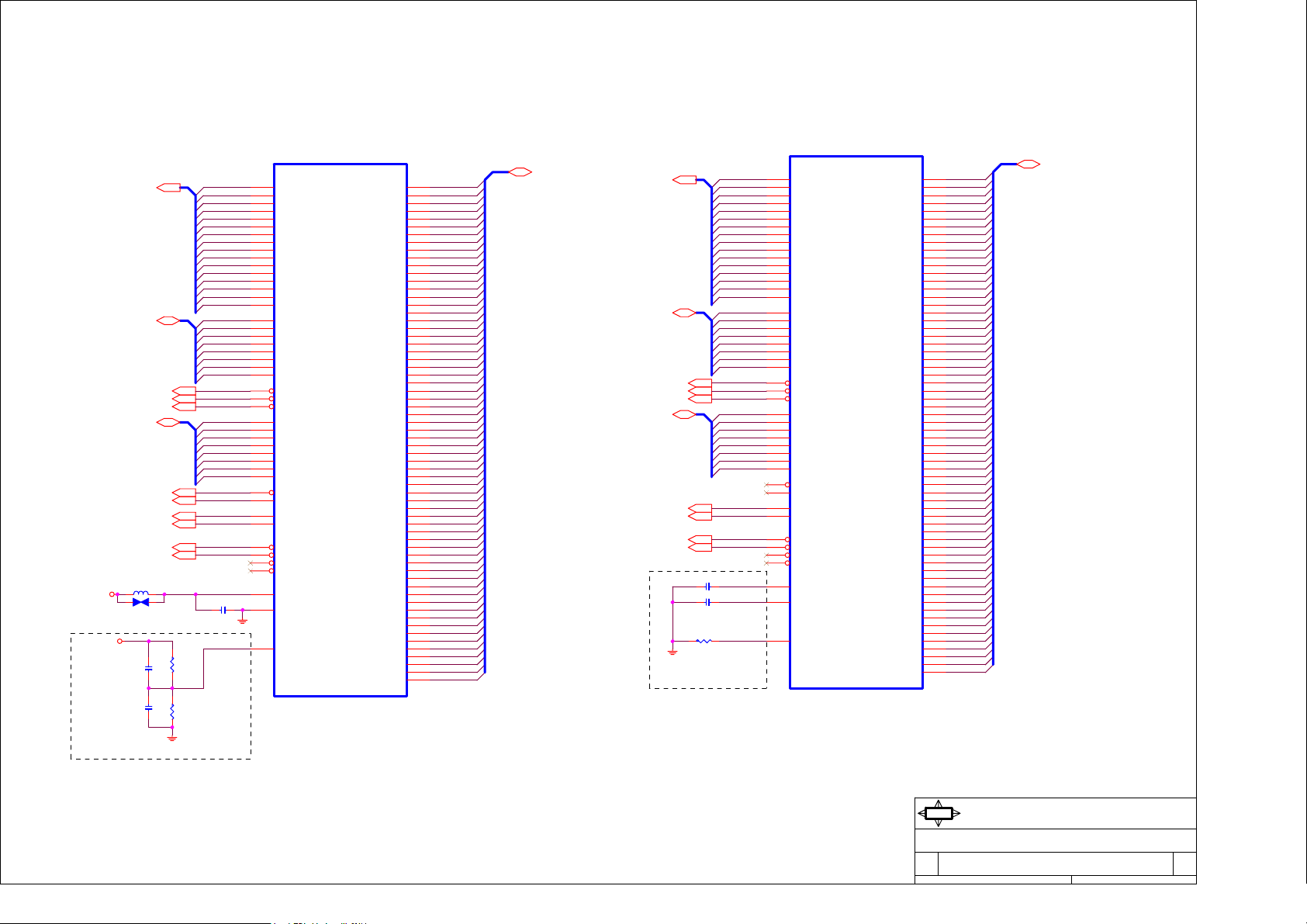

SIO-SMSC 47M997 & KB/MS

COM, LPT, FLOPPY & VGA

AC'97 CODEC & Audio JACK

MAIN CLOCK & DDR CLOCK BUFFER

DDR DIMM I & II

DDR Terminational Resisitors

IDE Connectors 22

Mini PCI & MDC 23

PCI Slot 1 & IR

AGP Slot & FAN Control

USB CONNECTORS

LAN RTL8100C & 8100S

1394 VIA-6307

ATX & F_ PANEL & XBus Rom

ACPI Controller MS7 Ver: C

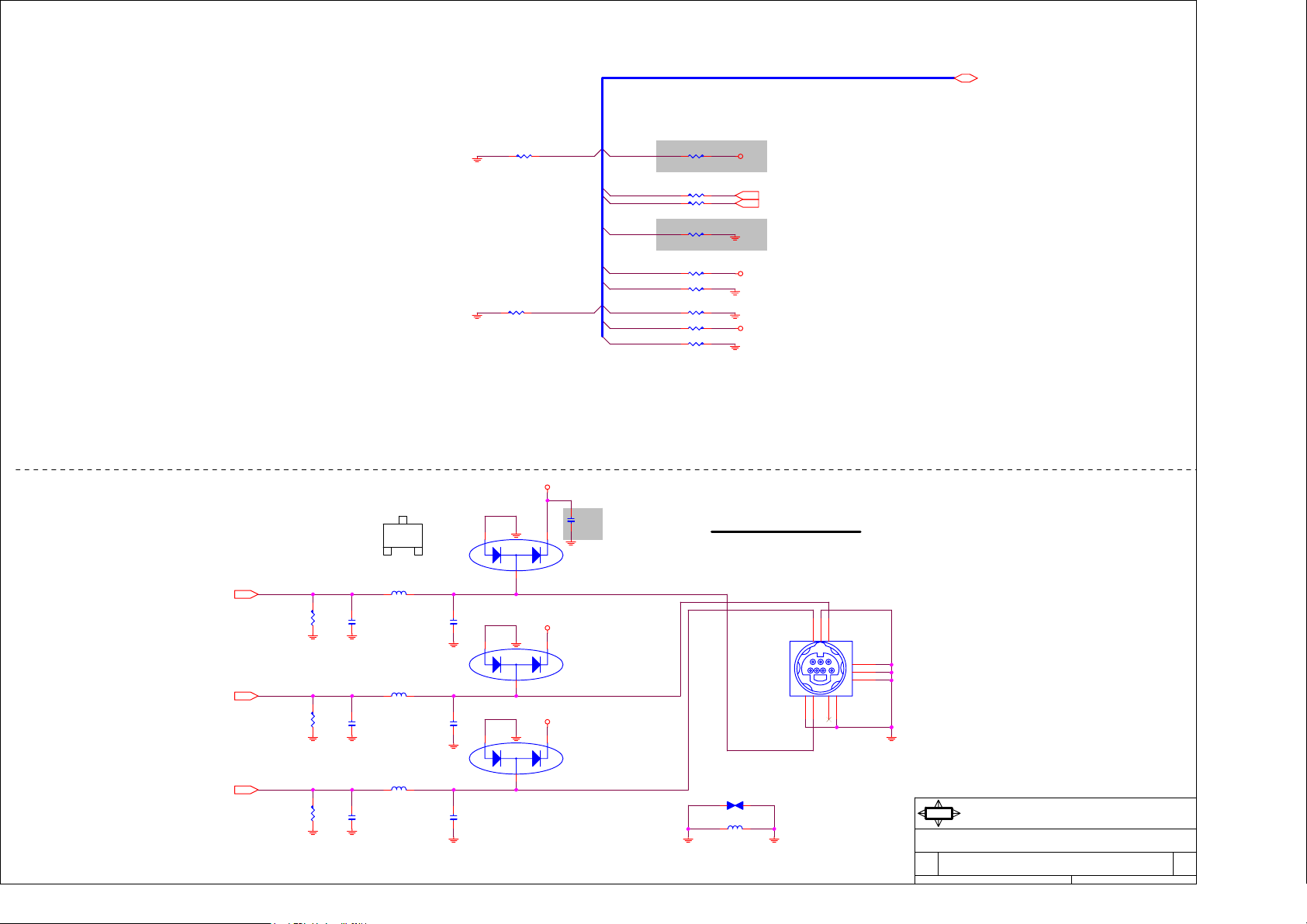

VRM 10 - Intersil HIP 6556B + HIP 6602B

PWR GOOD & Front Audio & CMOS

GPIO & JUMPER SETTING & Manual Parts

Power Delivery

1-4

5

6

7

8

9-10

11

12

13-14

15

16

17

18

19-20

21

24

25

26

27

28

29

30

31

32

33

34

MS-7072 / 6282

ATi RS350 (IGP) + SB300 (IXP) Chipset

Intel Northwood & Prescott mPGA478B Processor

CPU:

Intel Northwood/Prescott - 3.0G & Above

System Chipset:

ATi RS350 - RADEON IGP (North Bridge)

ATi SB300 (South Bridge)

On Board Chipset:

BIOS -- XBus EEPROM 4M

AC'97 Codec -- CMI9761A+

LPC Super I/O -- SMSC 47M997

LAN - Realtek RTL8100C

1394 -- VIA6307

DDR CLOCK BUFFER -- ICS ICS9P750-CF

Main Memory:

DDR X2

Expansion Slots:

PCI2.3 SLOT X1

AGP4X/8X SLOT X1

Intersil PWM:

Controller: HIP6556A

Driver: HIP6602+HIP6601

Version 0A

Regulators

MS-7

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

COVER SHEET

MS-7072

135Monday, April 12, 2004

of

0A

SRSEQ

P.33 P.33

VRM10

Intersil 6556A

3-Phase PWM

P.31

AGP 1.5V

Connector

Analog

Video Out

TV

Out

IDE Primary

IDE Secondary

P.25

P.16

P.10

P.22

P.22

USB2.0

USB Port0~ 7

MDC

P.26

P.23

AC'97 Codec

CMI9761A+

P.17

LAN

Realtek

8100C

P.27

4X/8X w/Fast Wr i t e

R,G,B,DDC

Y,C,COMP

UltraDMA

33/66/100/133

USB2.0

AC'97

PCI Bus

Intel mPAG478B Processor

FSB

RS350

IGP

P.7~9

A- Link

SB300

IXP

P.11~13

LPC Bus

P.5~6

CHANNEL A

CHANNEL B

PCI

SATA

LPC SIO

SMSC 47M997

Block Diagram

1 DDR

DIMM

Modules

1 DDR

DIMM

Modules

SATA1

P.15

P.17

P.18

P.22

Clock

Generator

Clock

Buffer

PCI Slot 1

P.24

P.18

P.18

Mini PCI

P.23

1394

VIA-6307

Flash

P.28

P.29

Serial

Port

P.16

Hardware

Monitor

P.15

LCM

Micro-Processor

P.32

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

BLOCK DIAGRAM

MS-7072

235Monday, April 12, 2004

of

0A

5

4

3

2

1

Revision Initial ver: 0A on

03/23/2004

1. Audio mute pull to gnd..

2. BIOS need set model ID for CMI driver.

Project Member

PM / Kevin #1558

BIOS / Sam #1790

EMI / Owl #1565

D D

ME / Tony #1829

Layout / Minchi #1829

software / Sunny #1951

Thermal / Chung #1891

C C

B B

A A

MSI

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

MICRO-STAR INt'L CO., LTD.

REVISION HISTORY - 1

MS-7072

335Monday, April 12, 2004

1

of

0A

I2C / SMBUS ADDRESSING

DEVICE

DDR DIMM A0

HEX

A0

DDR DIMM B0 1 0 1 0 0 1 0 XA4

D2CLOCK GENERATOR (EXT.)

DDR CLOCK BUFFER D4 1 1 0 1 0 1 0 X

ADDRESS

1 0 1 0 0 0 0 X

1 1 0 1 0 0 1 X

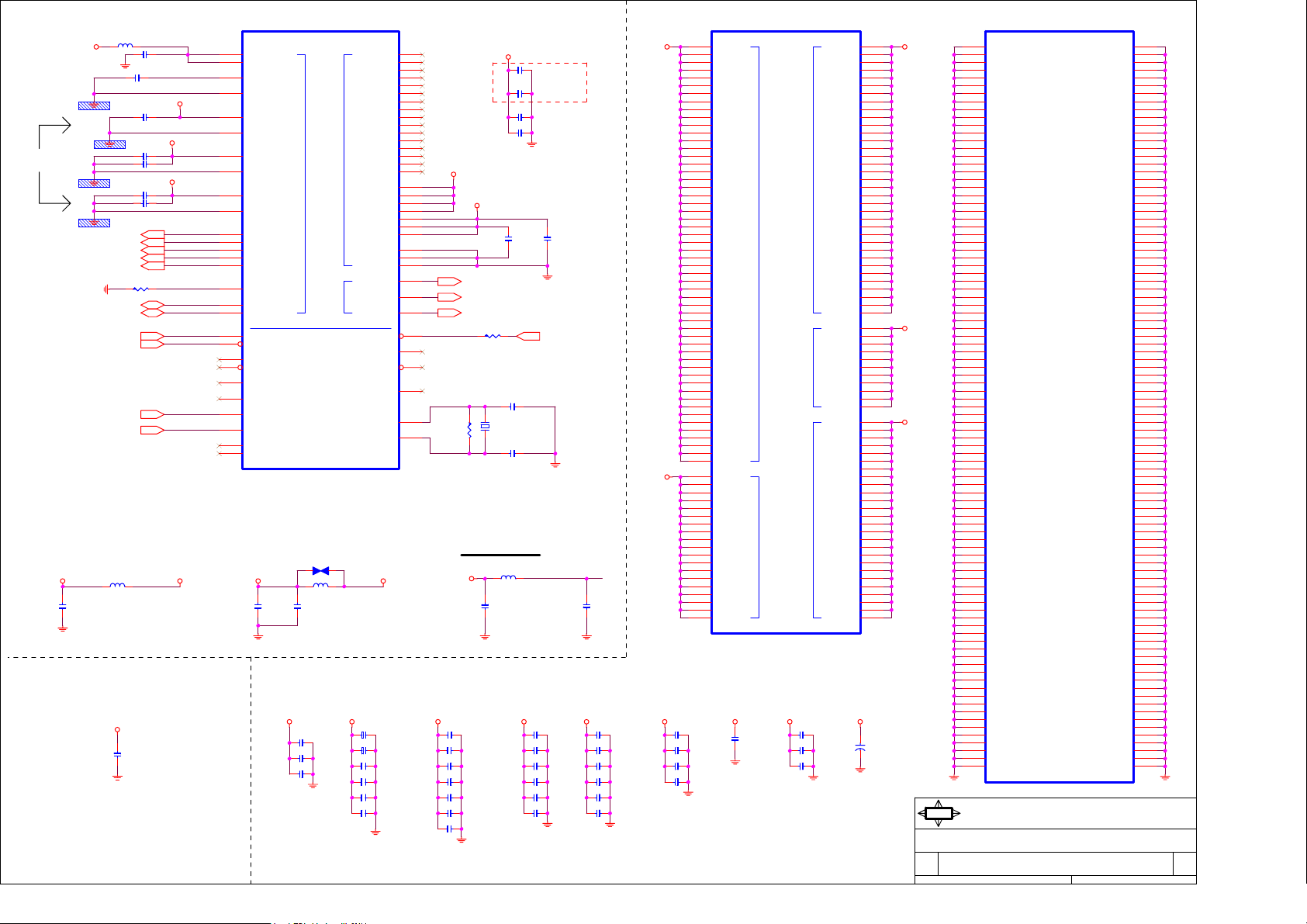

POWER SEQUENCE

POWER RAILS

POWER VOLTAGE ACTIVE SCOPE

+12V

-12V

VCC5

VCC3

VCC5_SB

SYSTEMRS350 NBSB300 SB

VCC3_SB

USB_STR1

USB_STR2

CLK_VDD

+12V

-12V

+5V

+3.3V

+5V

+3.3V

+5V

+5V 80 mils

OFF IN S3-S5

OFF IN S3-S5

OFF IN S3-S5

OFF IN S3-S5

S0-S5(ON)

S0-S5(ON)

S0-S3(ON)

S0-S3(ON)

OFF IN S3-S5+3.3V

ROUTING

80 mils/20 mils

40 mils/20 mils

PLANE

PLANE

80 mils/40 mils

40 mils

80 mils

PLANE/TRACE

POWER VOLTAGE ACTIVE SCOPE ROUTING

P3VA

P3VD

IEEE-1394

BUS_PWR

VDD33

VDD25

10/100

LAN

+5VR

AC97

DVDD

+3.3V

OFF IN S3-S5+3.3V

OFF IN S3-S5 40/40mils+12V

+3.3V PLANE/TRACE

+2.5V

S0-S5(ON)

S0-S5(ON)

+5V OFF IN S3-S5

+3.3V OFF IN S3-S5 10mils

20milsOFF IN S3-S5

20mils

PLANE/TRACE

20mils

VCC_NB_PWRGD

VDRM_PWRGD

VRM_PWRGD

NB_PWRGD

SB_PWRGD

CPU_PWRGD

PCI_RST#

CPU_RST#

T1

T1>= 70 ms

T3

T2

1ms < T2 < 10ms

1ms < T3 < 5ms

VCCP

VCC_VID

Processor

1.VCCP

2.VCC_NB

3.VCC_DDR

4.VCC_AGP

5.VDDL

6.VCC1.8_NB

7.AVDD

8.AVDDI

9.AVDDQ

10.PLLVDD

11.CPVDD

12.MPVDD

13.VTT_DDR

1.VDDQ

2.VCC_18

3.VCC3_SB

4.VCC18_SUS

5.APIC_POWER

6.AVDD_CK

7.5V_REF

8.3.3V_AVDDC

9.USB_AVDD

10.AVDD_SATA

11.PLVDD_SATA

12.XTLVDD_SATA

VID[0..5]

+1.2V

OFF IN S3-S5

OFF IN S3-S5

PLANE

20 mils

OFF IN S3-S5VCCP PLANE(I/O POWER FOR CPU)

+1.6V

+2.5V

+1.5V

OFF IN S3-S5

S0-S3(ON)

OFF IN S3-S5

+3.3V OFF IN S3-S5

+1.8V

+2.5V

OFF IN S3-S5

OFF IN S3-S5

OFF IN S3-S5+1.8V

+1.8V

+1.8V

OFF IN S3-S5

OFF IN S3-S5

PLANE(CORE POWER)

PLANE(I/O POWER FOR DDR)

PLANE(I/O POWER FOR AGP)

PLANE(I/O POWER FOR A-LINK)

40 mils(CORE TRANSFORM)

20 mils(I/O POWER FOR DAC)

20 mils(DIGITAL POWER FOR DAC)

20 mils(POWER FOR DAC BAND GAP REFERANCE)

20 mils(PLL POWER)

+1.8V OFF IN S3-S5 20 mils(CPU PLL POWER)

+1.8V OFF IN S3-S5 20 mils(MEMORY PLL POWER)

+1.25V

OFF IN S3-S5

OFF IN S3-S5+3.3V

60/60 mils(DDR TERMINATION POWER)

PLANE(3.3V I/O POWER)

OFF IN S3-S5 PLANE(CORE_POWER)+1.8V

+3.3V

+1.8V

+1.8V

S0-S5(ON)

S0-S5(ON)

OFF IN S3-S5VCCP

OFF IN S3-S5

20 mils

20 mils

10 mils(CPU I/O)

10 mils(PLL POWER)

OFF IN S3-S5+5V 10 mils(PCI CLAMP VOLTAGE)

S0-S5(ON)

S0-S5(ON)

+1.8V 20 mils(SERIAL PHY POWER)

+1.8V

OFF IN S3-S5

OFF IN S3-S5

10 mils(USB PLL POWER)+3.3V

20 mils(USB PHY POWER)+3.3V

10 mils(SERIAL ATA PLL POWER)

10 mils(SERIAL ATA PLL POWER)+3.3V OFF IN S3-S5

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

TABLE OF CONTENT S

MS-7072

of

435Monday, April 12, 2004

0A

CPU SIGNAL BLOCK

HDBI#[0..3](7)

FERR#(11)

STPCLK#(11)

HINIT#(11)

5:5<17"

HDRDY#(7)

HDEFER#(7)

10:10:10<8"

CPU_TMPA(15)

VTIN_GND(15)

C18 X_100p

IGNNE#(11)

H_SMI#(11)

A20M#(11)

SLP#(11)

CPU_GD(11)

CPURST#(7)

HD#[0..63](7)

HDBSY#(7)

HTRDY#(7)

HLOCK#(7)

28RST

HADS#(7)

HBNR#(7)

HIT#(7)

HITM#(7)

HBPRI#(7)

BOOT(31)

BSEL0(10,18)

BSEL1(10,18)

HDBI#0

HDBI#1

HDBI#2

HDBI#3

IERR#

FERR#

R117

C440

X_100p

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

H_TRMTRIP#

H_PROCHOT#

BOOT

R729 X_0

5:13<12"

CPU_GD

5:13<10"

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

HA#[3..31](7)

CPU1A

E21

DBI0#

G25

DBI1#

P26

DBI2#

V21

DBI3#

AC3

IERR#

V6

MCERR#

B6

FERR#

Y4

STPCLK#

AA3

BINIT#

W5

INIT#

AB2

RSP#

H5

DBSY#

H2

DRDY#

J6

TRDY#

G1

ADS#

G4

LOCK#

G2

BNR#

F3

HIT#

E3

HITM#

D2

BPRI#

E2

DEFER#

C1

TDI

D5

TDO

F7

TMS

E6

TRST#

D4

TCK

B3

THERMDA

C4

THERMDC

A2

THERMTRIP#

AF26

GND/SKTOCC#

C3

PROCHOT#

B2

IGNNE#

B5

SMI#

C6

A20M#

AB26

SLP#

A22

RESERVED0

A7

RESERVED1

AE21

RESERVED2

AF24

RESERVED3

AF25

RESERVED4

AD1

BOOTSELECT

AE26

OPTIMIZED/COMPAT#

AD6

BSEL0

AD5

BSEL1

AB23

PWRGOOD

AB25

RESET#

AA24

D63#

AA22

D62#

AA25

D61#

Y21

D60#

Y24

D59#

Y23

D58#

W25

D57#

Y26

D56#

W26

D55#

V24

D54#

HA#23

HA#20

HA#22

HA#24

HA#27

HA#26

HA#29

HA#28

HA#30

HA#31

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

V22

U21

V25

U23

U24

U26

T23

HD#46

HD#48

HD#47

HD#49

HD#53

HD#50

HD#51

HD#52

T22

A31#

D46#

T25

HD#45

A30#

D45#

T26

HD#44

A29#

D44#

R24

HD#43

A28#

D43#

R25

HD#42

A27#

D42#

P24

HD#41

HA#25

A26#

D41#

R21

HD#40

A25#

D40#

N25

HD#39

A24#

D39#

HD#38

N26

A23#

D38#

M26

HD#37

HA#21

A22#

D37#

N23

HD#36

A21#

D36#

M24

HD#35

HA#19

A20#

D35#

P21

HD#34

HA#18

A19#

D34#

N22

HD#33

HA#17

A18#

D33#

M23

HD#32

HA#16

A17#

D32#

HD#31

H25

HA#15

A16#

D31#

K23

HD#30

HA#14

A15#

D30#

J24

HD#29

HA#13

A14#

D29#

L22

HD#28

HA#12

A13#

D28#

M21

HD#27

HA#11

A12#

D27#

H24

HD#26

HA#10

A11#

D26#

G26

HD#25

HA#9

A10#

D25#

L21

HD#24

HA#8

A9#

D24#

D26

HD#23

HA#7

A8#

D23#

F26

HD#22

HA#6

A7#

D22#

E25

HD#21

HA#5

A6#

D21#

F24

HD#20

HA#4

A5#

D20#

F23

HD#19

HA#3

A4#

D19#

G23

HD#18

A3#

D18#

E24

HD#17

D17#

H22

HD#16

AE25A5A4

DBR#

D16#

D15#

D25

J21

HD#15

HD#14

D14#

D23

HD#13

VCC_SENSE

D13#

C26

HD#12

VSS_SENSE

D12#

H21

HD#11

AD26

D11#

G22

HD#10

AC26

ITP_CLK1

D10#

B25

HD#9

ITP_CLK0

D9#

D8#

C24

HD#8

AD2

VIDPWRGD

D7#

C23

HD#7

VID5

AD3

VID5#

D6#

B24

HD#6

VID4

AE1

VID4#

D5#

D22

HD#5

VID3HD#4

AE2

VID3#

D4#

C21

VID2

AE3

VID2#

D3#

A25

HD#3

VID1HD#2

VID0

AE4

AE5

VID1#

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D2#

D1#

D0#

PGA-S478-GD10-F02

A23

B22

B21

<Priority>

HD#0

HD#1

VCC_SENSE (31)

VSS_SENSE (31)

CPU_VID_GD (31)

VID[0..5] (15,31)

AA21

AA6

F20

F6

BPM#5

AB4

BPM#4

AA5

Y6

AC4

AB5

AC6

HREQ#4

H3

HREQ#3

J3

HREQ#2

J4

HREQ#1

K5

HREQ#0

J1

TESTHI12

AD25

TESTHI11

A6

TESTHI10

Y3

TESTHI9

W4

TESTHI8

U6

AB22

AA20

AC23

AC24

AC20

TESTHI2

AC21

TESTHI1

AA2

TESTHI0

AD24

CPUCLK#_EXT

AF23

CPUCLK_EXT

AF22

HRS#2

F4

HRS#1

G5

HRS#0

F1

V5

AC1

H_BR#0

H6

COMP1

P1

COMP0

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

C439 X_100p

D1

C438 X_100p

GTLREF

C3 220p

BPM#1

BPM#0

R226 X_0

R25 61.9_1%

R26 61.9_1%

PLACE CLOSE TO CPU

12:15<1.5"

R10 62

R11 62

1 2

3 4

5 6

7 8

RN74 8P4R-62

R20 62

R21 62

HADSTB#1 (7)

HADSTB#0 (7)

HDSTBP#3 (7)

HDSTBP#2 (7)

HDSTBP#1 (7)

HDSTBP#0 (7)

HDSTBN#3 (7)

HDSTBN#2 (7)

HDSTBN#1 (7)

HDSTBN#0 (7)

H_NMI (11)

INTR (11)

HREQ#[0..4] (7)

VCCP

C4

0.1u

5:7<1"

CPUCLK#_EXT (18)

CPUCLK_EXT (18)

HRS#[0..2] (7)

HBR#0 (7)

CPU GTL REFERNCE VOLTAGE BLO CK

VCCP

CLOSE TO CPU

R1

49.9R1%

C1

R2

0.1u

100RST

CB283

0.1u

PROCHOT# (12)

TRMTRIP# (12)

H_PROCHOT#

<0.75"

H_TRMTRIP#

GTLREF

CB281

0.1u

ALL COMPONENTS CLOSE TO CPU

VCC3

VCCP

R31

56_1%

R32 470

Q2

2N3904S

VCCP

R16

62

2N3904S

R1184

1K

Q165

R30

470

C2

220p

CB282

0.1u

R29

1K

DS

Q1

G

2N7002S

VCCP

ALL COMPONENTS CLOSE TO CPU

RN75 8P4R-62

BPM#5

1 2

BPM#4

3 4

BPM#1

5 6

BPM#0

7 8

CPU Pull up resistors

VCCP

CPU_GD

H_BR#0

CPURST#

IERR#

HINIT#

IGNNE#

FERR#

R17 301RST R9 1K

R18 62

R748 49.9R1%

R210 62

R222 X_200

R223 X_200

R35 X_56_1%

VCCP

ITP_TDI

ITP_TMS

ITP_TDO

ITP_TCK

ITP_TRST#

R22 1K

R23 X_75

R24 1K

R12 1K

VCCP

STPCLK#

SLP#

H_SMI#

H_NMI

INTR

A20M#

R206

X_200

R209

X_200

R207

X_56

R225

X_200

R224

X_200

R208

X_200

VCCP

CPURST#

R1205 X_0/S

C768 X_100p

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel mPGA478B - Signals

MS-7072

of

535Monday, April 12, 2004

0A

D10

A11

A13

A15

A17

A19

A21

A24

A26

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

A3

A9

CPU1B

CPU VOLTAGE BLOCK

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

AD12

AD14

VCC

VSS

VSS

VSS

VSS

VSS

VSS

AD16

AD18

AD21

AD4

AD23

AD8

AE11

VCC

VSS

VCC_VID(30,31)

C5

10u_0805

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

E12

E14

E16

E18

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE13

AE15

AE17

AE19

AE22

AE24

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B23

B20

B26B4B8

C11

C13

C15

C17C2C19

C22

C25C5C7C9D12

D14

D16

D18

D20

D21D3D24D6D8E1E11

E13

E15

E17

E19

E23

E7E9F10

E4

E26

VSS

F12

F14

F16

F18F2F22

F25F5F8

1.2V 150mA It must close bulk caps.

E20E8F11

VCC

VCC

VSS

VSS

VCC

VSS

F13

VCC

VSS

G21G6G24

F15

F17

VCC

VCC

VCC

VSS

VSS

VSS

G3H1H23

C6

0.1u

F19

VCC

VSS

F9

VCC

VSS

H26H4J2

VSS

AF4

VCC-VID

VSS

VSS

AF3

J22

VCC-VIDPRG

VSS

AD20

VSS

J25J5K21

CPU_IOPLL

AE23

VCCA

VSSA

VCC-IOPLL

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

PGA-S478-GD10-F02

<Priority>

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

EC1

10u/1206

VSSA

It support DC current if 100mA.

L1 10uH_0805_100mA

L2 10uH_0805_100mA

EC2

10u/1206

DC voltage drop should

be less than 70mV.

VCCP

C784

X_10u/1206

C785

X_10u/1206

CPU DECOUPLING CAPACITORS

VCCP

VCCPVCCP

+

EC10

220u_2V

+

EC11

X_220u_2V

+

EC12

220u_2V

+

EC13

X_220u_2V

4pcs

C823

X_10u/1206

EC14

10u/1206

EC15

10u/1206

C824

X_10u/1206

EC16

X_10u/1206

EC17

X_10u/1206

EC18

X_10u/1206

EC19

X_10u/1206

10pcs 1pcs

Place these caps within north side of processor

VCCP

EC20

X_10u/1206

EC21

10u/1206

EC22

X_10u/1206

EC23

10u/1206

VCCP

+

EC24

X_100u_2V

MSI

Place these caps within south side of processorPlace these caps within socket cavity

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel mPGA478B - Power

MS-7072

of

635Monday, April 12, 2004

0A

HA#[3..31](5)

HREQ#[0..4](5)

HADSTB#0(5)

HRS#[0..2](5)

NB_PWRGD(32)

VCC1.8_NB

R38 = 49.9 : Internal clock

R38 = 365 : External clock

SUS_STAT#(12)

HADSTB#1(5)

HADS#(5)

HBNR#(5)

HBPRI#(5)

HDEFER#(5)

HDRDY#(5)

HDBSY#(5)

HBR#0(5)

HLOCK#(5)

CPURST#(5)

HTRDY#(5)

HIT#(5)

HITM#(5)

R38 365RST

NB_RST#(11)

VCCP

L3 26/600mA-0805

R259 X_30K_1%

C111 X_0.1u

SUSSTAT#

R39 49.9R1%

R40 24.9_1%

C7 0.1u

GTLREF1

CP30

1 2

O = Normal mode

VCC_DDR

R1186

R1187

10K

5.6K

Q166

2N3904S

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HRS#2

HRS#1

HRS#0

M31

P29

M29

N34

N33

M30

N32

P32

P30

R34

P33

R33

N30

N31

M34

N29

R30

M33

L32

R31

U33

T33

R32

R29

U29

T31

V32

T30

U32

U30

V30

T29

V29

U31

V33

T34

L31

K29

H30

J31

L30

G31

F29

K30

A21

G29

G30

J29

F30

J30

H29

D10

AE5

AE6

E12

W32

W33

H26

J27

Y33

AA33

Y32

B21

VCC1.8_NB

U1A

AD3#

AD4#

AD5#

AD6#

AD7#

AD8#

AD9#

AD10#

AD11#

AD12#

AD13#

AD14#

AD15#

AD16#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADSTB0#

AD17#

AD18#

AD19#

AD20#

AD21#

AD22#

AD23#

AD24#

AD25#

AD26#

AD27#

AD28#

AD29#

AD30#

AD31#

ADSTB1#

ADS#

BNR#

BPR#

DEFER#

DRDY#

DBSY#

BR0#

LOCK#

CPURST#

RS2#

RS1#

RS0#

TRDY#

HIT#

HITM#

RSET

SUS_STAT#

SYSRST#

POWERGOOD

COMP_P

COMP_N

CPVDD

CPVSS

P4_VREF

THERMA_D_P

THERMAL_D_N

TESTMODE

R45

1K

SUSSTAT#

R47

10K

RS300 IGP

Part 1 of 7

Address Group 0Address Group 1ControlMISC.

P4 AGTL+ Interface

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

DATA Group 0DATA Group 1DATA Group 2DATA Group 3

D11#

D12#

D13#

D14#

D15#

DBI0#

DSTBN0#

DSTBP0#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DBI1#

DSTBN1#

DSTBP1#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3#

CL-ATI-RS350

8X_DET(25)

HD#0

L33

HD#1

K34

HD#2

J34

HD#3

J33

HD#4

K32

HD#5

K33

HD#6

H31

HD#7

J32

HD#8

F32

HD#9

H33

HD#10

E33

HD#11

D32

HD#12

G32

HD#13

E32

HD#14

D33

HD#15

F34

HDBI#0

F33

G33

G34

HD#16

B30

HD#17

C32

HD#18

A31

HD#19

C33

HD#20

B33

HD#21

C34

HD#22

B32

HD#23

D34

HD#24

D30

HD#25

B31

HD#26

C30

HD#27

E29

HD#28

E30

HD#29

A30

HD#30

B29

HD#31

C29

HDBI#1

A32

D31

E31

HD#32

F28

HD#33

D28

HD#34

E27

HD#35

E28

HD#36

F27

HD#37

C28

HD#38

B28

HD#39

A28

HD#40

F25

HD#41

A27

HD#42

B27

HD#43

C26

HD#44

B26

HD#45

C25

HD#46

E25

HD#47

D26

HDBI#2

D27

E26

F26

HD#48

B25

HD#49

F24

HD#50

A25

HD#51

C24

HD#52

E24

HD#53

D24

HD#54

A24

HD#55

D23

HD#56

C22

HD#57

B24

HD#58

E22

HD#59

B23

HD#60

D22

HD#61

B22

HD#62

C21

HD#63

A22

HDBI#3

F23

E23

F22

R1233

4.7K

8X_DET#:L(3.0) = 8X

8X_DET#:H(2.0) = 2/4X

HD#[0..63] (5)

HDBI#0 (5)

HDSTBN#0 (5)

HDSTBP#0 (5)

HDBI#1 (5)

HDSTBN#1 (5)

HDSTBP#1 (5)

HDBI#2 (5)

HDSTBN#2 (5)

HDSTBP#2 (5)

HDBI#3 (5)

HDSTBN#3 (5)

HDSTBP#3 (5)

+12V

R1232

4.7K

8X_DET#

Q15

2N3904S

VCC_AGP

R44

71.5_1%

DS

G

Q5

2N7002S

ATI Recommand

2N7002E for low

RDS

A_CBE#[0..3](11)

R41

169_1%

A_AD[0..31](10,11)

A_PAR(11)

A_FRAME#(11)

A_IRDY#(11)

A_TRDY#(11)

PIRQ#A(11,24,25)

A_DEVSEL#(11)

A_STOP#(11)

A_SBREQ#(11)

A_SBGNT#(11)

VCC3

(012803 Update)

GGNT#(25)

GREQ#(25)

AGP8X_DET#(25)

AGP_REF(25)

Close to RS300

T/S : 10/10

R37 6.8K

AGP_COMP

C8

X_0.1u

GTLREF1

C9

0.1u

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_CBE#0

A_CBE#1

A_CBE#2

A_CBE#3

AE4

AE2

AE3

AD2

AD1

AD3

AD5

AD6

AC1

AC2

AC4

AC5

AC6

AB2

AB4

AB5

AA4

AA2

AA3

W3

W4

W5

W6

AC3

AB6

W2

AA5

AA6

G6

G5

C66

0.1u

2/3*Vccp

C10

X_105P

V2

V1

V5

V6

U1

U2

U3

U4

U5

V4

Y3

Y2

Y6

U6

Y5

T5

T6

R5

R6

F5

J6

F6

U1B

VCCP

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_CBE#0

A_CBE#1

A_CBE#2

A_CBE#3

A_PAR

A_FRAME#

A_IRDY#

A_TRDY#

A_INTA#

A_DEVSEL#

A_STOP#

A_SBREQ#

A_SBGNT#

A_REQ0#

A_GNT0#

AGP_GNT#

AGP_REQ#

AGP_COMP

AGP8X_DET#

AGP_VERF4X

C786

0.1u

R46

49.9R1%

R48

100RST

RS300 IGP

Part 2 of 7

A_LINK Interface

A_LINK/AGP Interface

AGP_PIPE#DBI_HI

C787

0.1u

MSI

Title

Size Document Number Rev

Date: Sheet

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP 8X Interface

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_SBSTB

AGP_SBSTB#

AGP_ADSTB0

AGP_ADSTB0#

AGP_ADSTB1

AGP_ADSTB1#

AGP_CBE#0

AGP_CBE#1

AGP_CBE#2

AGP_CBE#3

AGP_DEVSEL#

AGP_FRAME#

AGP_IRDY#

AGP_PAR

AGP_DBI_LO

AGP_RBF#

AGP_STOP#

AGP_TRDY#

AGP_WBF#

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

AGP_ST0

AGP_ST1

AGP_ST2

CL-ATI-RS350

VCC_AGP

C788

10u_0805

T3

R2

R3

P2

P3

N3

N2

M3

L2

L3

K2

K3

J2

J1

J3

H3

G2

G3

F2

F1

F3

E1

E2

C1

C2

C3

B2

D4

B3

A3

C4

A6

C6

M1

M2

D3

D2

L1

H1

H2

E3

M5

L6

L5

N5

B4

A4

K6

N6

M6

K5

B8

C7

B7

A7

B6

C5

B5

D5

H6

H5

J5

C789

0.1u

GC_BE#0

GC_BE#1

GC_BE#2

GC_BE#3

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

RBF#

GSTOP#

WBF#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

Add vcc_agp

channel

SB_STB (25)

SB_STB# (25)

AD_STB0 (25)

AD_STB#0 (25)

AD_STB1 (25)

AD_STB#1 (25)

GC_BE#0 (25)

GC_BE#1 (25)

GC_BE#2 (25)

GC_BE#3 (25)

GDEVSEL# (25)

GFRAME# (25)

GIRDY# (25)

GPAR (25)

AGP_DBI_HI/PIPE# (25)

AGP_DBI_LO (25)

RBF# (25)

GSTOP# (25)

GTRDY# (25)

WBF# (25)

ST0 (25)

ST1 (25)

ST2 (25)

GAD0

T2

MICRO-STAR INt'L CO., LTD.

ATi RS350 - CPU & AGP & A_LINK Signals

MS-7072

GAD[0..31] (25)

SBA[0..7] (25)

of

735Monday, April 12, 2004

0A

MDQM_A[0..7](19,21)

MDQS_A[0..7](19,21)

VCC1.8_NB

VCC_DDR

PLACE CLOSE

TO RS300

MA_A[0..15](19,21)

MRAS_A#(19,21)

MCAS_A#(19,21)

MWE_A#(19,21)

MA_CLKOUT#(18)

MA_CLKOUT(18)

MCKE_A0(19,21)

MCKE_A1(19,21)

MCS_A#0(19,21)

MCS_A#1(19,21)

L4 X_26/600mA-0805/S

1 2

CP54

X_CP

C14

0.1u

C15

0.1u

R50

1K_1%

R51

866_1%

MA_A0

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

MA_A13

MA_A14

MA_A15

MDQM_A0

MDQM_A1

MDQM_A2

MDQM_A3

MDQM_A4

MDQM_A5

MDQM_A6

MDQM_A7

MDQS_A0

MDQS_A1

MDQS_A2

MDQS_A3

MDQS_A4

MDQS_A5

MDQS_A6

MDQS_A7

MA_CLKOUT#

MA_CLKOUT

MCKE_A0

MCKE_A1

MPVDD

1uC13

MEM_VREF

AN21

AM21

AN20

AM18

AN17

AN14

AM15

AN12

AM13

AM11

AM22

AP10

AM9

AM27

AN22

AK33

AP4

AP11

AP17

AN25

AM34

AG32

AC32

AN29

AP31

AM30

AK1

AN4

AN10

AM17

AM25

AM33

AG33

AC33

AM23

AP22

AM7

AN7

AN32

AN33

AN31

AP32

AG19

AH19

AP26

AJ3

U1C

MEMA_A0

MEMA_A1

MEMA_A2

MEMA_A3

MEMA_A4

MEMA_A5

MEMA_A6

MEMA_A7

MEMA_A8

MEMA_A9

MEMA_A10

MEMA_A11

MEMA_A12

MEMA_A13

MEMA_A14

MEMA_A15

MEMA_DM0

MEMA_DM1

MEMA_DM2

MEMA_DM3

MEMA_DM4

MEMA_DM5

MEMA_DM6

MEMA_DM7

MEMA_RAS#

MEMA_CAS#

MEMA_WE#

MEMA_DQS0

MEMA_DQS1

MEMA_DQS2

MEMA_DQS3

MEMA_DQS4

MEMA_DQS5

MEMA_DQS6

MEMA_DQS7

MEMA_CK#

MEMA_CK

MEMA_CKE0

MEMA_CKE1

MEMA_CS0#

MEMA_CS1#

MEMA_CS2#

MEMA_CS3#

MPVDD

MPVSS

MEM_VREF

RS300 IGP

Part 3 of 7

MEMA_DQ10

MEMA_DQ11

MEMA_DQ12

MEMA_DQ13

MEMA_DQ14

MEMA_DQ15

MEMA_DQ16

MEMA_DQ17

MEMA_DQ18

MEMA_DQ19

MEMA_DQ20

MEMA_DQ21

MEMA_DQ22

MEMA_DQ23

MEMA_DQ24

MEMA_DQ25

MEMA_DQ26

MEMA_DQ27

MEMA_DQ28

MEMA_DQ29

MEMA_DQ30

MEMA_DQ31

MEMA_DQ32

MEMA_DQ33

MEMA_DQ34

MEMA_DQ35

MEM_A_ Interface

MEMA_DQ36

MEMA_DQ37

MEMA_DQ38

MEMA_DQ39

MEMA_DQ40

MEMA_DQ41

MEMA_DQ42

MEMA_DQ43

MEMA_DQ44

MEMA_DQ45

MEMA_DQ46

MEMA_DQ47

MEMA_DQ48

MEMA_DQ49

MEMA_DQ50

MEMA_DQ51

MEMA_DQ52

MEMA_DQ53

MEMA_DQ54

MEMA_DQ55

MEMA_DQ56

MEMA_DQ57

MEMA_DQ58

MEMA_DQ59

MEMA_DQ60

MEMA_DQ61

MEMA_DQ62

MEMA_DQ63

MEMA_DQ0

MEMA_DQ1

MEMA_DQ2

MEMA_DQ3

MEMA_DQ4

MEMA_DQ5

MEMA_DQ6

MEMA_DQ7

MEMA_DQ8

MEMA_DQ9

CL-ATI-RS350

AH2

AJ1

AL1

AM1

AH3

AJ2

AK2

AL2

AM2

AN3

AM6

AN6

AN2

AP3

AN5

AP5

AN8

AN9

AN11

AN13

AM8

AM10

AM12

AM14

AN15

AN16

AN18

AN19

AM16

AP16

AM19

AM20

AP23

AM24

AM26

AM28

AN23

AN24

AN26

AN27

AM29

AM31

AL33

AK32

AN28

AN30

AL34

AK34

AJ32

AH32

AF33

AE33

AJ33

AH33

AF32

AE32

AD34

AD33

AB33

AA32

AE34

AD32

AB32

AB34

MDQ_A0

MDQ_A1

MDQ_A2

MDQ_A3

MDQ_A4

MDQ_A5

MDQ_A6

MDQ_A7

MDQ_A8

MDQ_A9

MDQ_A10

MDQ_A11

MDQ_A12

MDQ_A13

MDQ_A14

MDQ_A15

MDQ_A16

MDQ_A17

MDQ_A18

MDQ_A19

MDQ_A20

MDQ_A21

MDQ_A22

MDQ_A23

MDQ_A24

MDQ_A25

MDQ_A26

MDQ_A27

MDQ_A28

MDQ_A29

MDQ_A30

MDQ_A31

MDQ_A32

MDQ_A33

MDQ_A34

MDQ_A35

MDQ_A36

MDQ_A37

MDQ_A38

MDQ_A39

MDQ_A40

MDQ_A41

MDQ_A42

MDQ_A43

MDQ_A44

MDQ_A45

MDQ_A46

MDQ_A47

MDQ_A48

MDQ_A49

MDQ_A50

MDQ_A51

MDQ_A52

MDQ_A53

MDQ_A54

MDQ_A55

MDQ_A56

MDQ_A57

MDQ_A58

MDQ_A59

MDQ_A60

MDQ_A61

MDQ_A62

MDQ_A63

MDQ_A[0..63] (19,21)

MA_B[0..15](20,21)

MDQM_B[0..7](20,21)

MRAS_B#(20,21)

MCAS_B#(20,21)

MWE_B#(20,21)

MDQS_B[0..7](20,21)

MCKE_B0(20,21)

MCKE_B1(20,21)

MCS_B#0(20,21)

MCS_B#1(20,21)

PLACE CLOSE TO

RS350

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MA_B12

MA_B13

MA_B14

MA_B15

MDQM_B0

MDQM_B1

MDQM_B2 MDQ_B19

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

MRAS_B#

MCAS_B#

MWE_B#

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

MCKE_B0

MCKE_B1

C11 0.47u

C12 0.47u

R49 49.9R1%

AK21

AJ21

AL20

AJ19

AJ18

AK15

AL15

AL13

AJ14

AK12

AJ22

AJ12

AK10

AL26

AK22

AG28

AH5

AL12

AK18

AK25

AJ31

AE30

AA30

AK28

AK31

AJ29

AK6

AK11

AL17

AJ25

AH30

AE31

AA31

AJ23

AL22

AL8

AL30

AL31

AJ30

AL32

AG3

AA34

AP25

AL6

AJ6

AJ9

U1D

MEMB_A0

MEMB_A1

MEMB_A2

MEMB_A3

MEMB_A4

MEMB_A5

MEMB_A6

MEMB_A7

MEMB_A8

MEMB_A9

MEMB_A10

MEMB_A11

MEMB_A12

MEMB_A13

MEMB_A14

MEMB_A15

MEMB_DM0

MEMB_DM1

MEMB_DM2

MEMB_DM3

MEMB_DM4

MEMB_DM5

MEMB_DM6

MEMB_DM7

MEMB_RAS#

MEMB_CAS#

MEMB_WE#

MEMB_DQS0

MEMB_DQS1

MEMB_DQS2

MEMB_DQS3

MEMB_DQS4

MEMB_DQS5

MEMB_DQS6

MEMB_DQS7

MEMB_CK#

MEMB_CK

MEMB_CKE0

MEMB_CKE1

MEMB_CS0#

MEMB_CS1#

MEMB_CS2#

MEMB_CS3#

MEM_CAP1

MEM_CAP2

MEM_COMP

RS300 IGP

Part 4 of 7

MEMB_DQ10

MEMB_DQ11

MEMB_DQ12

MEMB_DQ13

MEMB_DQ14

MEMB_DQ15

MEMB_DQ16

MEMB_DQ17

MEMB_DQ18

MEMB_DQ19

MEMB_DQ20

MEMB_DQ21

MEMB_DQ22

MEMB_DQ23

MEMB_DQ24

MEMB_DQ25

MEMB_DQ26

MEMB_DQ27

MEMB_DQ28

MEMB_DQ29

MEMB_DQ30

MEMB_DQ31

MEMB_DQ32

MEMB_DQ33

MEMB_DQ34

MEMB_DQ35

MEM_B_ Interface

MEMB_DQ36

MEMB_DQ37

MEMB_DQ38

MEMB_DQ39

MEMB_DQ40

MEMB_DQ41

MEMB_DQ42

MEMB_DQ43

MEMB_DQ44

MEMB_DQ45

MEMB_DQ46

MEMB_DQ47

MEMB_DQ48

MEMB_DQ49

MEMB_DQ50

MEMB_DQ51

MEMB_DQ52

MEMB_DQ53

MEMB_DQ54

MEMB_DQ55

MEMB_DQ56

MEMB_DQ57

MEMB_DQ58

MEMB_DQ59

MEMB_DQ60

MEMB_DQ61

MEMB_DQ62

MEMB_DQ63

CL-ATI-RS350

MEMB_DQ0

MEMB_DQ1

MEMB_DQ2

MEMB_DQ3

MEMB_DQ4

MEMB_DQ5

MEMB_DQ6

MEMB_DQ7

MEMB_DQ8

MEMB_DQ9

AG6

AH6

AJ4

AL3

AG5

AG4

AJ5

AK3

AK4

AM4

AJ8

AK8

AL4

AL5

AJ7

AK7

AJ10

AL10

AJ13

AK14

AK9

AJ11

AK13

AJ15

AJ16

AJ17

AK19

AJ20

AK16

AK17

AL19

AK20

AK23

AK24

AJ26

AK27

AJ24

AL24

AK26

AJ27

AJ28

AL29

AH28

AG29

AL27

AK29

AH29

AG30

AG31

AF29

AD30

AC30

AF30

AF31

AD29

AC29

AB31

AA29

Y30

W30

AB29

AB30

Y29

W29

MDQ_B0

MDQ_B1

MDQ_B2

MDQ_B3

MDQ_B4

MDQ_B5

MDQ_B6

MDQ_B7

MDQ_B8

MDQ_B9

MDQ_B10

MDQ_B11

MDQ_B12

MDQ_B13

MDQ_B14

MDQ_B15

MDQ_B16

MDQ_B17

MDQ_B18

MDQ_B20

MDQ_B21

MDQ_B22

MDQ_B23

MDQ_B24

MDQ_B25

MDQ_B26

MDQ_B27

MDQ_B28

MDQ_B29

MDQ_B30

MDQ_B31

MDQ_B32

MDQ_B33

MDQ_B34

MDQ_B35

MDQ_B36

MDQ_B37

MDQ_B38

MDQ_B39

MDQ_B40

MDQ_B41

MDQ_B42

MDQ_B43

MDQ_B44

MDQ_B45

MDQ_B46

MDQ_B47

MDQ_B48

MDQ_B49

MDQ_B50

MDQ_B51

MDQ_B52

MDQ_B53

MDQ_B54

MDQ_B55

MDQ_B56

MDQ_B57

MDQ_B58

MDQ_B59

MDQ_B60

MDQ_B61

MDQ_B62

MDQ_B63

MDQ_B[0..63] (20,21)

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

ATi IGP - Memory Signals

MS-7072

of

835Monday, April 12, 2004

0A

U1E

L5 200Ohm_200mA/S

VCC3

NB_DDRCLK_EXT(18)

AVDDQ VCC1.8_NB

C398

1u_0805

C16 1u_0805

C17 10u_0805

C23 0.1u

C25 0.1u

C26 0.1u

C27 1u_0805

C28 0.1u

CRT_R(16)

CRT_G(16)

CRT_B(16)

CRT_VSYNC(16)

CRT_HSYNC(16)

R52 715_1%

Trace Width 10 mils

3VDDCDA(16)

3VDDCCL(16)

NB_CLK_EXT(18)

NB_CLK#_EXT(18)

AGPCLK0_EXT(18)

L21

26/600mA-0805

0.15mA

H9

VDDR3_1

G9

AVDD_NB

VCC1.8_NB

AVDDQ

(1.8V)1.8V/0.22A

PLVDD

(1.8V)

VGA_RSET

3VDDCDA

3VDDCCL

VCC1.8_NB PLVDD

VDDR3_2

A18

AVDD

B18

AVSS

B17

AVDDDI

C17

AVSSDI

A19

AVDDQ

B19

AVSSQ

H14

PLLVDD

H15

PLLVSS

D18

RED

E18

GREEN

F18

BLUE

E13

DACVSYNC

D13

DACHSYNC

C18

RSET

E11

DACSDA

A10

HCLKIN

B10

HCLKIN#

B11

SYS_FBCLKOUT

C11

SYS_FBCLKOUT#

F9

ALINK_CLK

C8

AGPCLKOUT

D9

AGPCLKIN

C9

EXT_MEM_CLK

F10

USBCLK

D11

REF27

EMI reserve

VCC1.8_NB

C796

0.1u

RS300 IGP

Part 5 of 7

CRT

Clock

CP11

X_CP

1 2

L20

C449

X_1000p

VCC_NB VCC_NB

X_26/600mA-0805

C395

X_10u_0805

C37

0.1u

C44

0.1u

C71

0.1u

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

VDD18

VDD18

VDD18

VDD18

VDD18

VDD18

VDD18

GND

GND

GND

C_R

Y_G

COMP_BDACSCL

SVID

CPUSTOP#

SYSCLK

SYSCLK#

OSC

XTLOUT

XTLIN

CL-ATI-RS350

C38

10u/1206

C52

10u/1206

C58

10u_0805

C59

10u_0805

C72

10u_0805

C78

10u_0805

1.8V/0.18A

VCC1.8_NB

C/R (10)

Y/G (10)

COMP/B (10)

R543

R60

100K

VCC1.8_NB

X1

14M-32pf-HC49S-D

D15

E15

F15

D16

F16

E16

F17

E17

F14

E14

C13

B13

C12

A13

C14

B14

J26

J9

AF26

AF9

A16

B16

C16

A15

B15

C15

F19

D19

E19F12

E9

A12

B12

E10

B9

A9

VCC1.8_NB

CPU_STP#_R

P_XO

P_XI

1.8V

DAC POWER

L22 120_600mA

AVDD

C200

X_102P

VCC_DDR VCC_DDR

C447

10u_0805

C74

10u_0805

C54

0.1u

C61

0.1u

C53

0.1u

C39

0.1u

C68

10u_0805

C30

10u_0805

0

22pC32

22pC33

2.5V/0.08A

C19

10u_0805

C24

10u_0805

C20

1u

C22

1u

C31

1u

CPU_STOP# (11,18)

AVDD_NB

VCC_AGP

C40

1u

C46

1u

C60

1u

C67

1u

C73

1u

C538

1u

U1F

VCC_NB VCC_DDR

1.5V/2A

VCC_AGP

1.5V/0.23A

C778

0.1u

C35

0.1u

C42

X_0.1u

C49

0.1u

C56

0.1u

C63

0.1u

CB258

0.1u

AA13

AA14

AA15

AA16

AA19

AA20

AA21

AA22

AB13

AB14

AB15

AB16

AB19

AB20

AB21

AB22

G10

G12

G16

H10

H12

H16

N13

N14

N15

N16

N19

N20

N21

N22

P13

P14

P15

P16

P19

P20

P21

P22

R13

R14

R15

R16

R19

R20

R21

R22

Y13

Y14

Y15

Y16

Y19

Y20

Y21

Y22

D7

E7

H8

A2

E4

G4

J4

K8

L4

L7

L8

N4

N8

P1

P5

P6

R4

R7

R8

C76

0.1u

C82

0.1u

C94

0.1u

C100

X_0.1u

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDP33

VDDP33

VDDP33

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

RS300 IGP

Part 6 of 7

CORE PWR

AGP PWR

VCC3VCCP VCCP VCC3

EC48

X_10u_0805

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

MEM I/F PWR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

POWER

VDDL

VDDL

VDDL

VDDL

VDDL

VDDL

VDDL

VDDL

VDDL

VDDL

A_LINK PWRCPU I/F PWR

VDDL

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

CL-ATI-RS350

C41

0.1u

C48

1u

C55

1u

AB27

AB28

AC31

AD27

AD28

AF27

AG1

AG7

AG8

AG10

AG12

AG14

AG16

AG18

AG22

AG24

AG26

AG27

AG34

AH10

AH14

AH16

AH22

AH26

AL9

AL16

AL23

AP2

AP7

AP13

AP19

AP28

AP33

W31

Y27

AA7

AA8

AD7

AD8

AF4

AF5

AF6

U7

U8

W8

Y1

C20

D20

D21

E20

E21

F20

F21

H20

H21

H23

H25

H27

G21

G25

G27

G28

K27

K28

M27

M28

N27

N28

T27

T28

U27

W34

+

EC46

470u/10V

2.5mm

U1G

A33

2.5V/0.4A

VCC3

3.3V/0.15A

VCCP

VCCP/0.5A

Title

Size Document Number Rev

Date: Sheet

AA1

AA18

AA27

AA28

AB3

AB8

AC7

AC8

AC27

AD4

AD31

AE8

AE27

AE28

AE29

AF1

AF2

AF3

AF7

AF8

AG2

AG9

AG11

AG13

AG15

AG17

AG20

AG21

AG23

AG25

AH4

AH8

AH11

AH13

AH17

AH20

AH23

AH25

AH31

AH34

AK5

AK30

AL7

AL11

AL14

AL18

AL21

AL25

AL28

AM3

AM5

AM32

AN1

AN34

AP8

AP14

AP20

AP29

B1

B20

B34

C10

C19

C23

C27

C31

D6

D8

D12

D14

D17

D25

D29

E5

E6

E8

F4

F7

F8

F11

F13

F31

G8

G13

G15

G18

G19

G22

G24

H4

H7

AA17

MSI

MICRO-STAR INt'L CO., LTD.

ATi IGP - Video & Clock & Power Signals

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RS300 IGP

Part 7 of 7

MS-7072

GND

CL-ATI-RS350

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

935Monday, April 12, 2004

H11

H13

H17

H18

H19

H22

H24

H32

J7

J8

J28

K4

K31

L27

L29

M4

M7

M8

M32

N17

N18

P4

P7

P8

P17

P18

P27

P31

R1

R17

R18

R27

R28

T4

T8

T13

T14

T15

T16

T17

T18

T19

T20

T21

T22

T32

U13

U14

U15

U16

U17

U18

U19

U20

U21

U22

V3

V7

V8

V13

V14

V15

V16

V17

V18

V19

V20

V21

V22

V27

V28

V31

V34

W13

W14

W15

W16

W17

W18

W19

W20

W21

W22

W27

W28

Y4

Y7

Y8

Y17

Y18

Y31

AB17

AB18

0A

of

A_AD[0..31] (7,11)

* AD29 : STRAP CONFIGURATION

0 : REDUCEDE SET

Enable SS

R1212

X_4.7K

Auto calibration CPU

R1213

X_4.7K

3

BAT54

1

2

COMP/B(9)

R1120

75_1%

Y/G(9)

R1121

75_1%

C/R(9)

R1122

75_1%

L26 1.8uH

C693

82p

L27 1.8uH

C695

82p

L28 1.8uH

C697

82p

C694

82p

C696

82p

C698

82p

2

3

2

3

2

3

A_AD21

VCC5

1

7/4 Remove

VCC5

1

D44

7/4 Remove

VCC5

1

D45

7/4 Remove

A_AD28

New add

C783

0.1u

D43

BAT54S-S-SOT23

BAT54S-S-SOT23

BAT54S-S-SOT23

A_AD29

A_AD31

A_AD30

A_AD20

A_AD24

A_AD18

A_AD22

A_AD25

A_AD17

COMP_AV

Y_S

C_S

R79 4.7K

R67 10K

R73 10K

R86 4.7K

R68 4.7K

R97 4.7K

R637 X_4.7K

R95 4.7K

R100 4.7K

FB45

VCC3

BSEL1 (5,18)

BSEL0 (5,18)

Close Internal

Clock

VCC3

VCC3

TV_OUT CONNECTOR

3

4

7

J3

2

5

6

1 2

CP57

X_80L

8

9

10

CONN-MiniDIN7P

1

1 : FULL SET

* AD[31:30] : FSB CLK SPEED

00 : 100 MHZ

01 : 133 MHZ

10 : 200 MHZ

11 : 166 MHZ

AD20 : INTERNAL CLK GEN. ENABLE

0 : EXTERNAL CLK GEN.

1 : INTERNAL CLK GEN.

* AD24 : NORTHWOOD CPU

* AD18 : Disabled PHASE CALIBRATION

* AD22 : OSD CLOCK SELECT

* AD[25:17] : CPU = 1.45V

MSI

Title

Size Document Number Rev

Date: Sheet

(DEFAULT)

(DEFAULT)

(DEFAULT)

MICRO-STAR INt'L CO., LTD.

ATi RS350 - Straps Signals

MS-7072

of

10 35Monday, April 12, 2004

0A

R113 20M

20mil

BAT1

ALINK_CLK(18)

NB_RST#(7)

A_AD[0..31](7,10)

A_CBE#[0..3](7)

A_FRAME#(7)

A_DEVSEL#(7)

A_IRDY#(7)

A_TRDY#(7)

A_STOP#(7)

A_SBREQ#(7)

A_SBGNT#(7)

A_PAR(7)

CPU_STOP#(9,18)

Pull double side ?

PIRQ#A(7,24,25)

PIRQ#B(24,25,27)

PIRQ#C(23,24)

PIRQ#D(23,24,28)

12pC151

12pC152

VCCP

CPU_GD(5)

INTR(5)

H_NMI(5)

HINIT#(5)

H_SMI#(5)

SLP#(5)

IGNNE#(5)

A20M#(5)

FERR#(5)

STPCLK#(5)

JCMOS

YJ103

123

Pull down for S3

R101 8.2K

R106 33

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_CBE#0

A_CBE#1

A_CBE#2

A_CBE#3

A_SERR#

PCI_ACT_REQ#

R546 X_10K

VCC3

32K_X1

32.768KHz-12.5pF-20PPM

R114

X3

20M

32K_X2

R502 1K

RN86

R126

1K

10K_8P4R

1 2

VBAT

CPU_GD

GPIO0

3 4

5 6

7 8

AB28

AD27

AC30

AC29

AB30

AB29

AA30

AC27

AC28

AA29

AA28

AB27

AA27

W30

W29

U27

R28

R30

R29

T27

R27

P29

N30

N29

M30

M29

Y29

W28

T30

P30

U29

U28

U30

V27

W27

P27

N28

V28

K27

K28

N27

M27

M28

B29

C29

D30

C28

B27

E29

C30

E30

D28

D27

E28

F27

E27

F30

F28

F29

L27

Y30

Y28

Y27

V30

V29

T29

T28

L30

L29

L28

B2

B1

U7A

218S3LAQA11

PCICLKF

A_RST#

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_CBE0#

A_CBE1#

A_CBE2#

A_CBE3#

A_STROBE#

A_DEVSEL#

A_ACAT#

A_END#

A_OFF#

A_SERR#

A_SBREQ#

A_SBGNT#

A_PAR

PCI_ACT_REQ#

CPU_STP#/DPSLP#

PCI_STP#

A_INTA#

INTB#

INTC#

INTD#

X1

X2

CPURSTIN#

CPU_PWRGD

INTR/LINT0

NMI/LINT1

INIT#

SMI#

SLP#

IGNNE#

A20M#

FERR#

STPCLK#

SSMUXSEL/GPIO0

DPRSLPVR

APIC_D0

APIC_D1

APIC_CLK

SB300 SB

A-LINK INTERFACE

XTAL

CLEAR CMOS JUMPER

CMOS

CLEAR

JBAT1 (2-3)

NORMAL

(1-2)

CLEAR

Part 1 of 4

PCI CLKS

CBE0#/ROMA10

CBE2#/ROMWE#

DEVSEL#/ROMA0

TRDY#/ROMOE#

PCI INTERFACE

REQ3#/PDMA_REQ0#

REQ4#/PLL_BP33/PDMA_REQ1#

GNT3#/PLL_BP66/PDMA_GNT0#

GNT4#/PLL_BP50/PDMA_GNT1#

CPU

LPCRTC

RTC_IRQ#/ACPWR_STRAP

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

PCICLK7

PCICLK8

PCICLK9

PCICLK_FB

PCIRST#

AD0/ROMA18

AD1/ROMA17

AD2/ROMA16

AD3/ROMA15

AD4/ROMA14

AD5/ROMA13

AD6/ROMA12

AD7/ROMA11

AD8/ROMA9

AD9/ROMA8

AD10/ROMA7

AD11/ROMA6

AD12/ROMA5

AD13/ROMA4

AD14/ROMA3

AD15/ROMA2

AD16/ROMD0

AD17/ROMD1

AD18/ROMD2

AD19/ROMD3

AD20/ROMD4

AD21/ROMD5

AD22/ROMD6

AD23/ROMD7

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

CBE1#/ROMA1

CBE3#

FRAME#

IRDY#

PAR/ROMA19

STOP#

PERR#

SERR#

REQ0#

REQ1#

REQ2#

REQ5#/GPIO13

GNT0#

GNT1#

GNT2#

GNT5#/GPIO14

CLKRUN#

LAD0

LAD1

LAD2

LAD3

LFRAME#

LDRQ0#

LDRQ1#

SERIRQ

RTCCLK

VBAT

RTC_GND

Close to

VBAT pin.

PCLK0

M1

PCLK1

N1

PCLK2

M2

PCLK3

P1

PCLK4

P2

PCLK5

R1

PCLK6

T2

PCLK7

T1

PCLK8

V2

PCLK9

U1

PCLK9_FB

V1

PCI_RST#

AG4

AD0

AF3

AD1

AF4

AD2

AE4

AD3

AD4

AD4

AD2

AD5

AD1

AD6

AE3

AD7

AB2

AD8

AC1

AD9

AC2

AD10

AD3

AD11

AC4

AD12

AC3

AD13

AB4

AD14

AB3

AD15

AA4

AD16

Y3

AD17

W4

AD18

W3

AD19

Y2

AD20

Y1

AD21

W2

AD22

W1

AD23

AA1

AD24

AE2

AD25

AF1

AD26

AF2

AD27

AG1

AD28

AG2

AD29

AH1

AD30

AH2

AD31

AJ2

C_BE#0

AA2

C_BE#1

AA3

C_BE#2

AE1

C_BE#3

AK3

AG3

Y4

AH4

AB1

AH5

AH6

AJ4

AH7

PREQ#0

AJ5

PREQ#1

AJ3

PREQ#2

AG6

PREQ#3

AK4

PREQ#4

AK5

PREQ#5

AG5

PGNT#0

AJ6

PGNT#1

AK6

PGNT#2

AH8

PGNT#3

AK7

PGNT#4

AJ7

PGNT#5

AG8

PCI_CLKRUN#

P28

LPC_AD0

AJ18

LPC_AD1

AK18

LPC_AD2

AJ17

LPC_AD3

AK17

LPC_FRAME#

AH17

LPC_DRQ#0

AH18

LPC_DRQ#1

AG16

SERIRQ

AG18

C7

C6

A2

A1

C161

473P

Common ground

PCLK0 (14)

PCLK6 (14)

PCLK7 (14)

PCLK8 (14)

Routed to PCLK9_FB to average

length of PCI clock

CN10 10p

2

4

6

8

10pC462

PCICLK0/5/6/7/8

also be strap pin.

PCLK9 PCLK9_FB

C_BE#[0..3] (23,24,27..29)

FRAME# (23,24,27,28)

DEVSEL# (23,24,27..29)

IRDY# (23,24,27,28)

TRDY# (23,24,27..29)

PAR (23,24,27,28)

STOP# (23,24,27,28)

PERR# (23,24,27,28)

SERR# (23,24,27)

PREQ#0 (24)

PREQ#1 (24)

PREQ#2 (23,24)

PREQ#3 (24,27)

PREQ#4 (24,28)

PREQ#5 (24)

PGNT#0 (24)

PGNT#1 (24)

PGNT#2 (23,24)

PGNT#3 (24,27)

PGNT#4 (24,28)

PGNT#5 (24)

LPC_AD0 (15)

LPC_AD1 (15)

LPC_AD2 (15)

LPC_AD3 (15)

LPC_FRAME# (15)

LPC_DRQ#0 (15)

SERIRQ (15)

SB_RTCCLK (14)

RTC_IRQ# (14)

VBAT

C162

X_0.01u

PCLK5

PCLK3

PCLK4

PCLK2

PCI_RST# (30)

AD[0..31] (23,24,27..29)

For EMI

1

3

5

7

33

R1231

1394_PCLK (28)

LPC_DRQ#0

LPC_DRQ#1

A_SERR#

PCI_ACT_REQ#

PCI_CLKRUN#

SERIRQ

R811 33

1 2

3 4

5 6

7 8

SIO_PCLK (15)

PCI_CLK1 (23)

PCI_CLK2 (24)

LAN_PCLK (14,27)

R125 4.7K

R127 4.7K

RN3 10K_8P4R

1 2

3 4

5 6

7 8

R539 10K

LAN_PCLK

1394_PCLK

SIO_PCLK

PCI_CLK1PCLK1

PCI_CLK2

RN69

8P4R-33

VCC3

VCC3

C112

0.1u

C116

X_0.1u

C122

1u

C124

1u

C128

1u

C131

X_105P

C134

1u

C140

X_0.1u

C142

0.1u

C523

0.1u

C524

X_0.1u

C525

X_0.1u

C526

0.1u

C527

0.1u

C769

X_0.1u

C133

0.1u

C143

0.1u

5V_REF

VCC_18

3

VCC3

VCC18_SUS

VCC3_SB

R685 1K

Add a diode to meet power up sequence

for SB300 5V_REF with respect to VDDQ

APIC_PWR

Enable / VCCP

Disable / 2.5V

VCC_18

L9

26/600mA-0805

C173

0.1u

C174

5V_REF

0.1u

C113

0.1u

C115

X_0.1u

C117

X_0.1u

C119

X_0.1u

C121

X_0.1u

C123

0.1u

C125

0.1u

C135

0.1u

2

VCC18_SUS

D30

S-BAT54C_SOT23

1

C534

0.1u

C159 1u_0805

AVDD_CK

U7C

VCC3

AK1

AH3

AC5

AD5

AF6

AF7

AF17

AF18

AF21

AF22

AF25

G26

K26

P26

R26

V26

W26

AB26

AC26

AF26

AK30

N3

R3

U3

P4

T4

V4

R5

U5

W5

F26

L26

VDDQ

VDDQ#N3

VDDQ#R3

VDDQ#U3

VDDQ#AH3

VDDQ#P4

VDDQ#T4

VDDQ#V4

VDDQ#R5

VDDQ#U5

VDDQ#W5

VDDQ#AC5

VDDQ#AD5

VDDQ#AF6

VDDQ#AF7

VDDQ#AF17

VDDQ#AF18

VDDQ#AF21

VDDQ#AF22

VDDQ#AF25

VDDQ#F26

VDDQ#G26

VDDQ#K26

VDDQ#L26

VDDQ#P26

VDDQ#R26

VDDQ#V26

VDDQ#W26

VDDQ#AB26

VDDQ#AC26

VDDQ#AF26

VDDQ#AK30

SB300 SB

Part 3 of 4

POWER

VCC_18

VCC3_SB

VCC3VCC5

VCCP

AVDD_CK

I=10mA

C175

1u_0805

M12

VDD_CORE#M12

N12

VDD_CORE#N12

V12

VDD_CORE#V12

W12

VDD_CORE#W12

M13

VDD_CORE

N13

VDD_CORE#N13

V13

VDD_CORE#V13

W13

VDD_CORE#W13

M18

VDD_CORE#M18

N18

VDD_CORE#N18

V18

VDD_CORE#V18

W18

VDD_CORE#W18

M19

VDD_CORE#M19

N19

VDD_CORE#N19

V19

VDD_CORE#V19

W19

VDD_CORE#W19

E5

S5_3.3V

G5

S5_3.3V#G5

H5

S5_3.3V#H5

L5

S5_3.3V#L5

M5

S5_3.3V#M5

D6

S5_3.3V#D6

H4

S5_3.3V#H4

B6

S5_3.3V#B6

E7

S5_3.3V#E7

D8

S5_3.3V#D8

E9

S5_3.3V#E9

D10

S5_3.3V#D10

E12

S5_1.8V#E12

E13

S5_1.8V

E16

S5_1.8V#E16

E17

S5_1.8V#E17

E19

S5_1.8V#E19

E20

S5_1.8V#E20

E23

S5_1.8V#E23

E24

S5_1.8V#E24

A28

S5_1.8V#A28

A29

S5_1.8V#A29

D29

APIC_PWR

AG7

V5_VREF

AD30

AVDDCK

AD29

AVSSCK

218S3LAQA11

MSI

Title

Size Document Number Rev

Date: Sheet

SB300 - ALINK,PCI,CPU,LPC,PWR

MICRO-STAR

MS-7072

VSS#AJ1

VSS#N2

VSS#R2

VSS#U2

VSS#AK2

VSS#B3

VSS#C3

VSS#G3

VSS#P3

VSS#T3

VSS#V3

VSS#C4

VSS#D4

VSS#N4

VSS#R4

VSS#U4

VSS#F5

VSS#J5

VSS#K5

VSS#N5

VSS#P5

VSS#T5

VSS#V5

VSS#Y5

VSS#AA5

VSS#AB5

VSS#AE5

VSS#AF5

VSS#E6

VSS#A7

VSS#D7

VSS#C8

VSS#E8

VSS#C9

VSS#D9

VSS#E10

VSS#E11

VSS#P12

VSS

VSS#T12

VSS#U12

VSS#P13

VSS#R13

VSS#T13

VSS#U13

VSS#E14

VSS#M14

VSS#N14

VSS#P14

VSS#R14

VSS#T14

VSS#U14

VSS#V14

VSS#W14

VSS#E15

VSS#M15

VSS#N15

VSS#P15

VSS#R15

VSS#T15

VSS#U15

VSS#V15

VSS#W15

VSS#AF15

VSS#M16

VSS#N16

VSS#P16

VSS#R16

VSS#T16

VSS#U16

VSS#V16

VSS#W16

VSS#AF16

VSS#M17

VSS#N17

VSS#P17

VSS#R17

VSS#T17

VSS#U17

VSS#V17

VSS#W17

VSS#E18

VSS#P18

VSS#R18

VSS#T18

VSS#U18

VSS#P19

AJ1

N2

R2

U2

AK2

B3

C3

G3

P3

T3

V3

C4

D4

N4

R4

U4

F5

J5

K5

N5

P5

T5

V5

Y5

AA5

AB5

AE5

AF5

E6

A7

D7

C8

E8

C9

D9

E10

E11

P12

R12

T12

U12

P13

R13

T13

U13

E14

M14

N14

P14

R14

T14

U14

V14

W14

E15

M15

N15

P15

R15

T15

U15

V15

W15

AF15

M16

N16

P16

R16

T16

U16

V16

W16

AF16

M17

N17

P17

R17

T17

U17

V17

W17

E18

P18

R18

T18

U18

P19

11 35Monday, April 12, 2004

0A

of

Loading...

Loading...