1

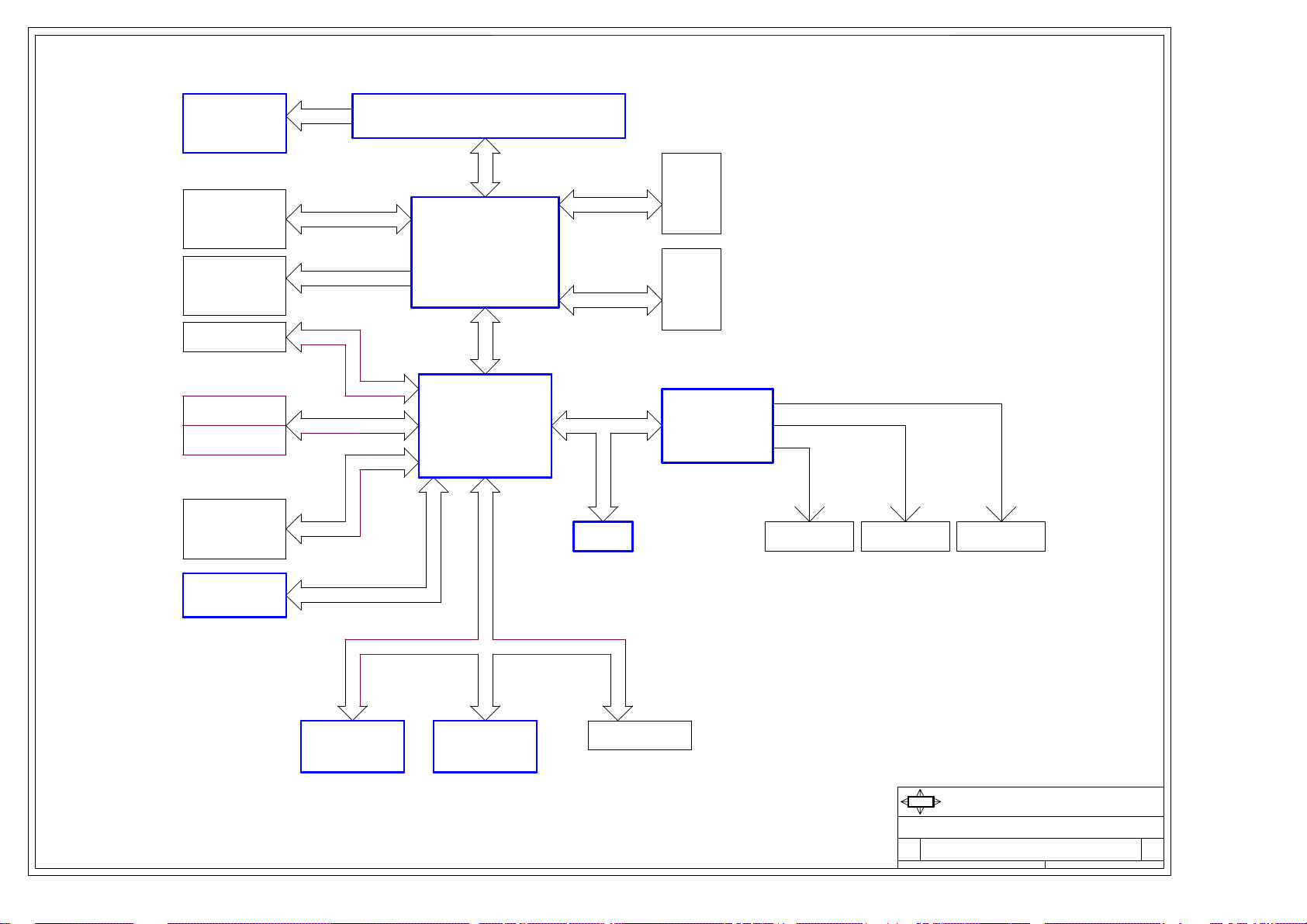

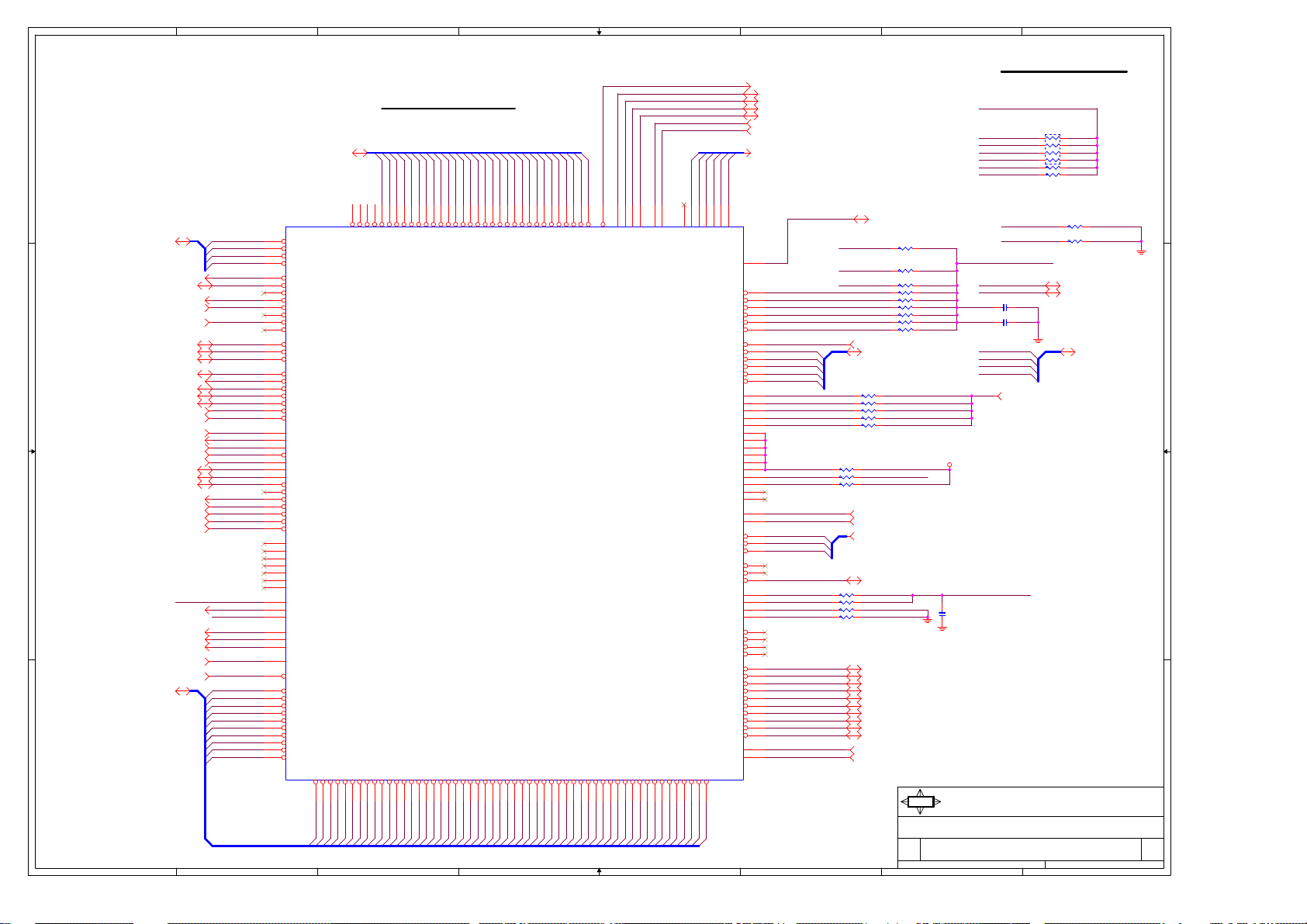

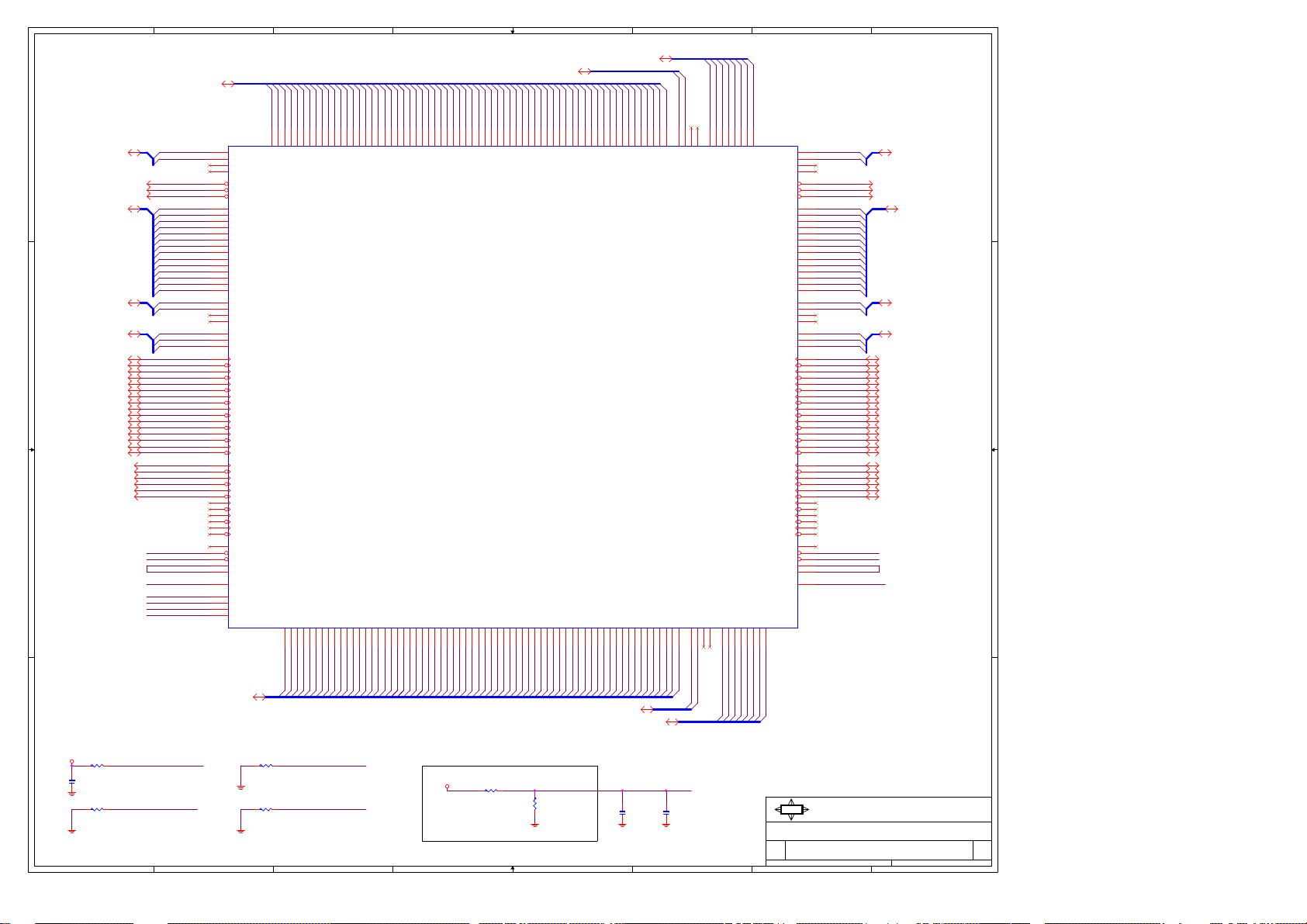

Cover Sheet, Block diagram, Reset/PWRGD Map

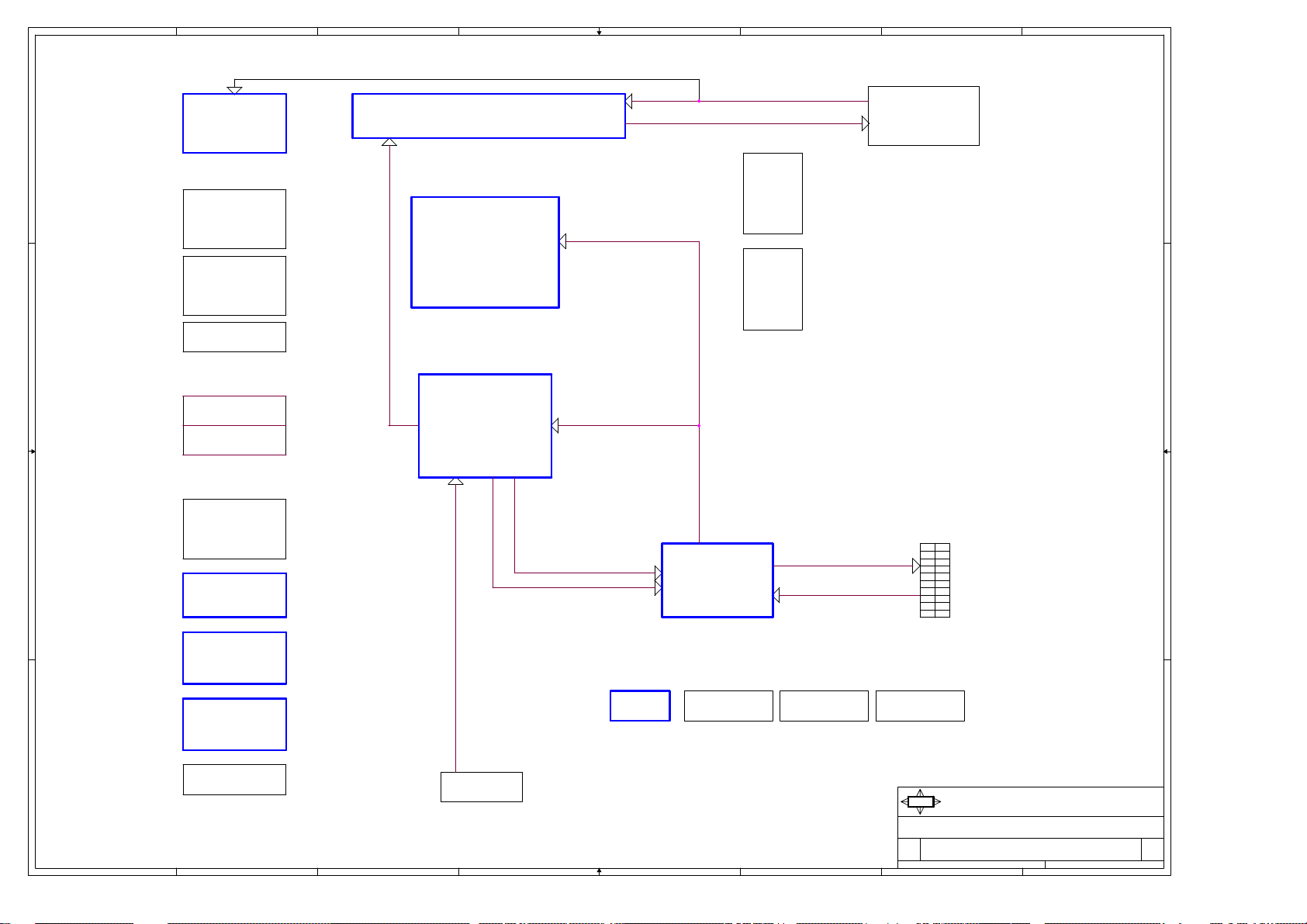

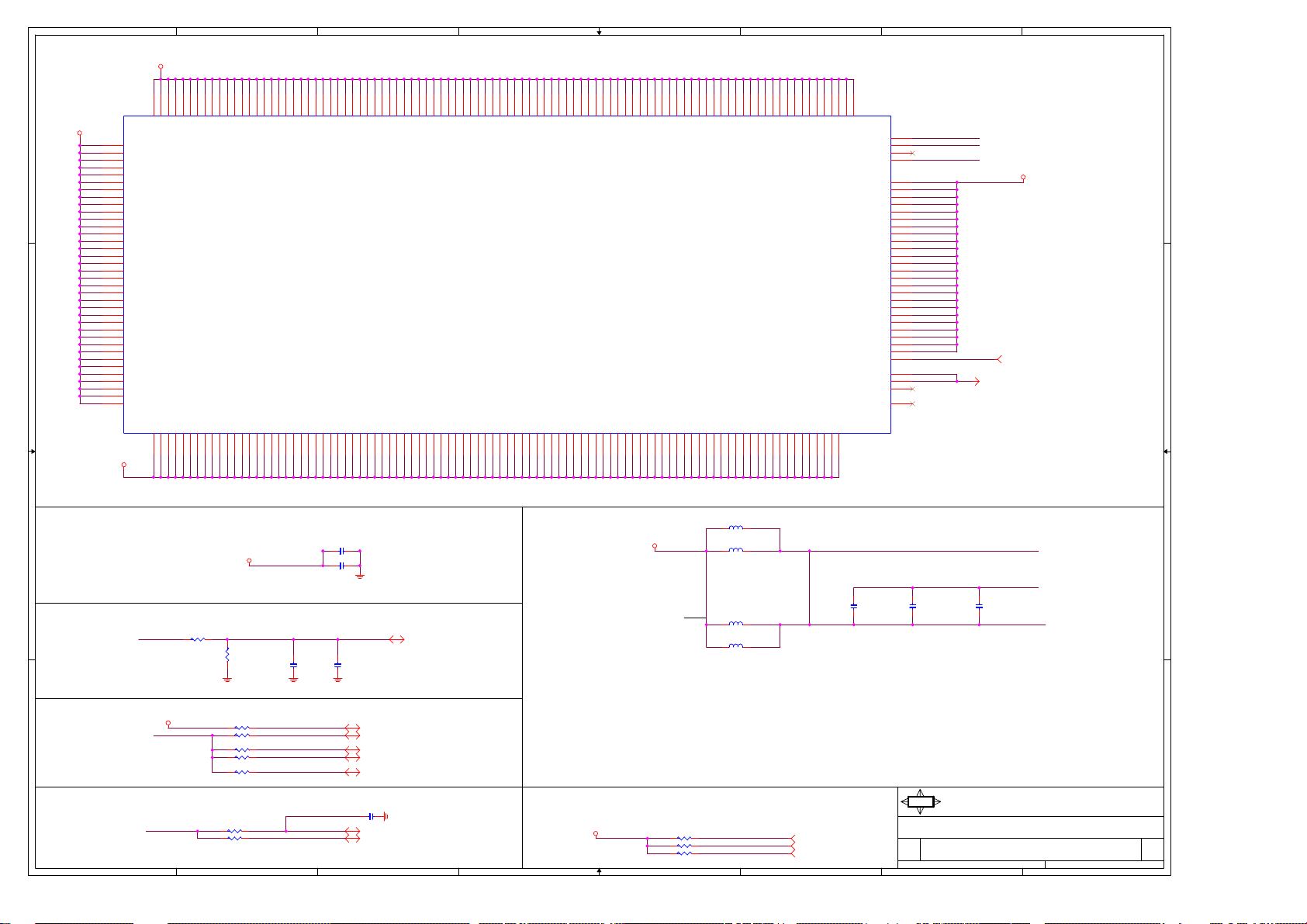

Intel LGA775 CPU - Signals/Power/GND

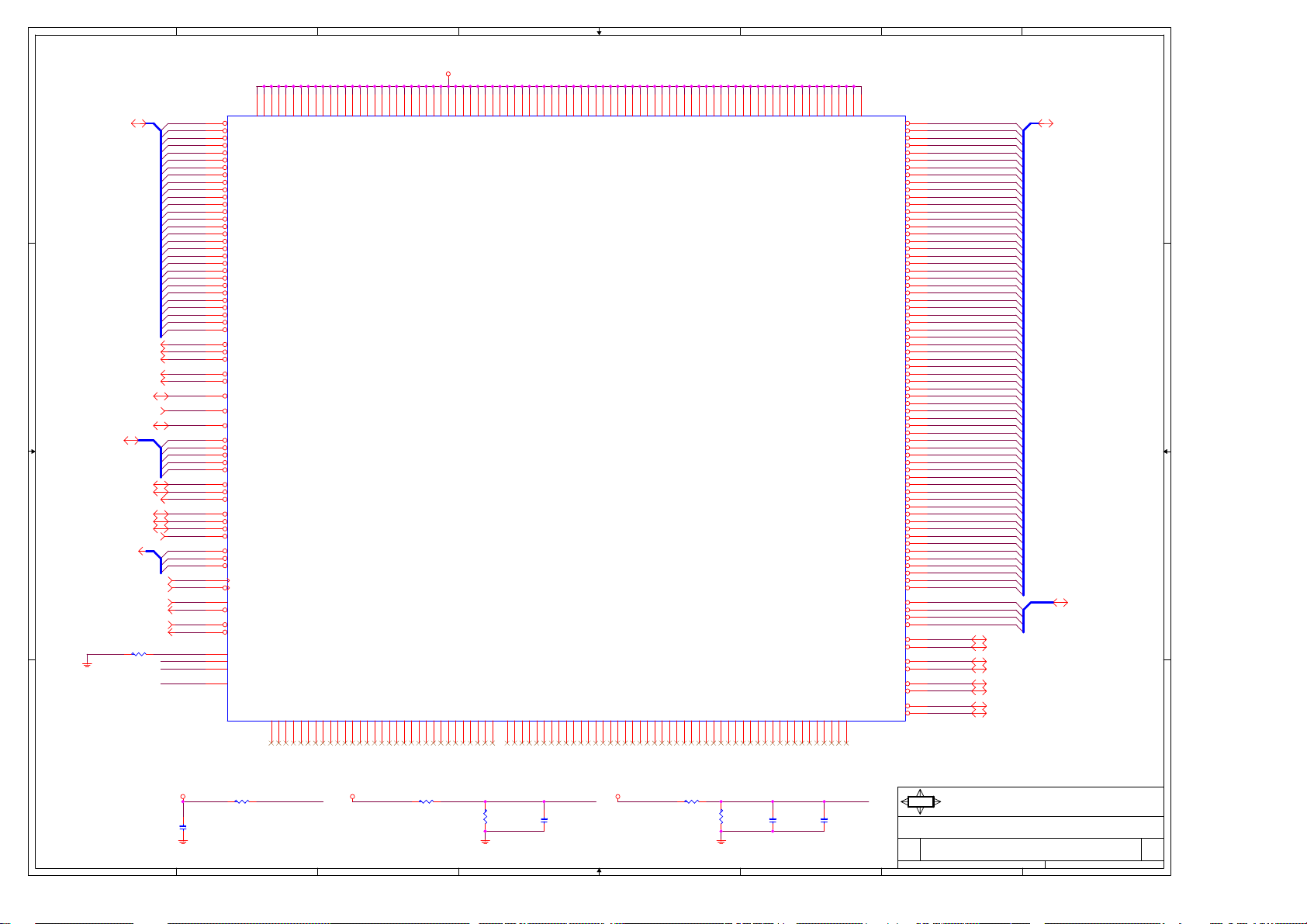

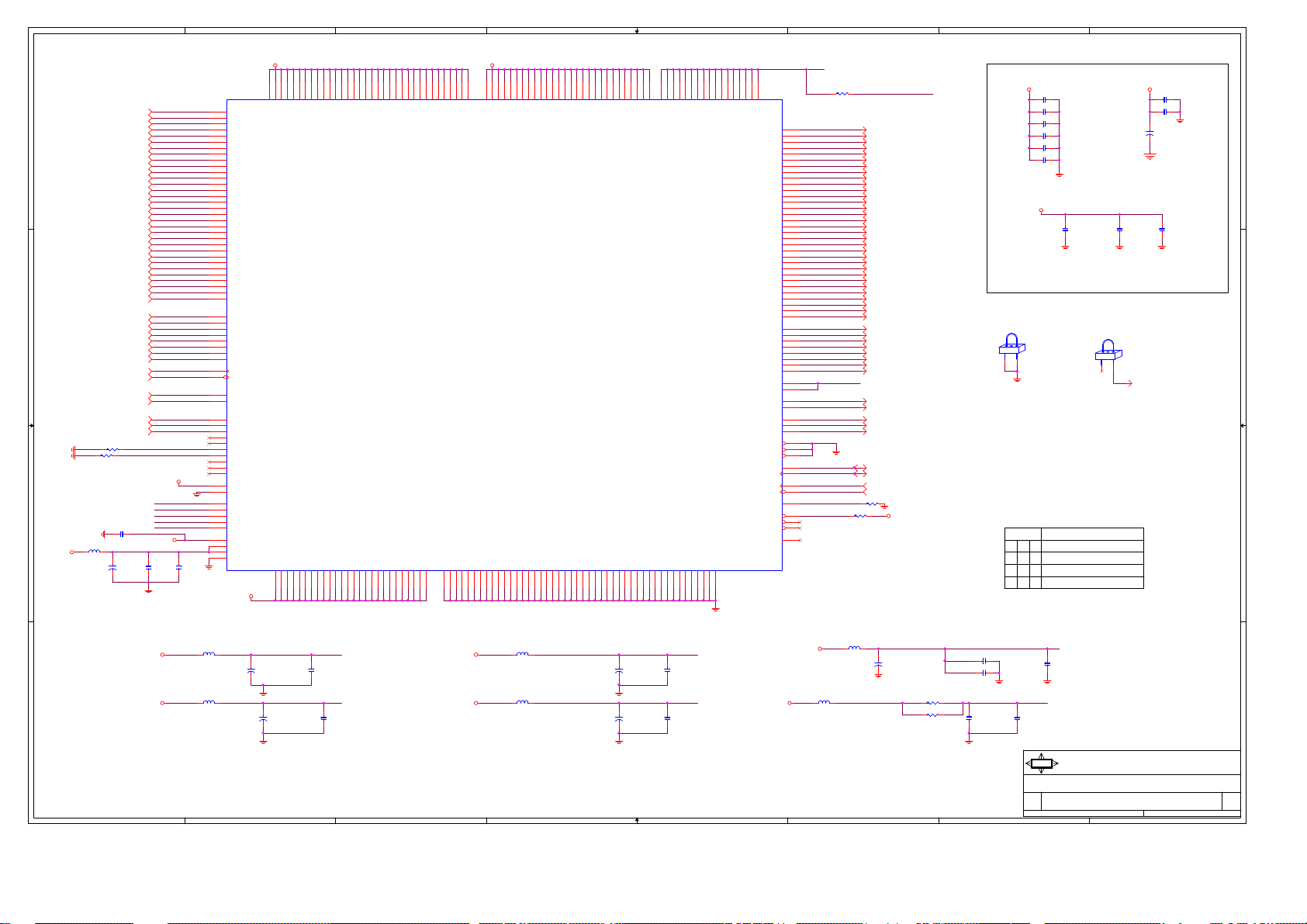

Intel Grantsdale - CPU/Memory/PCI_E/GND

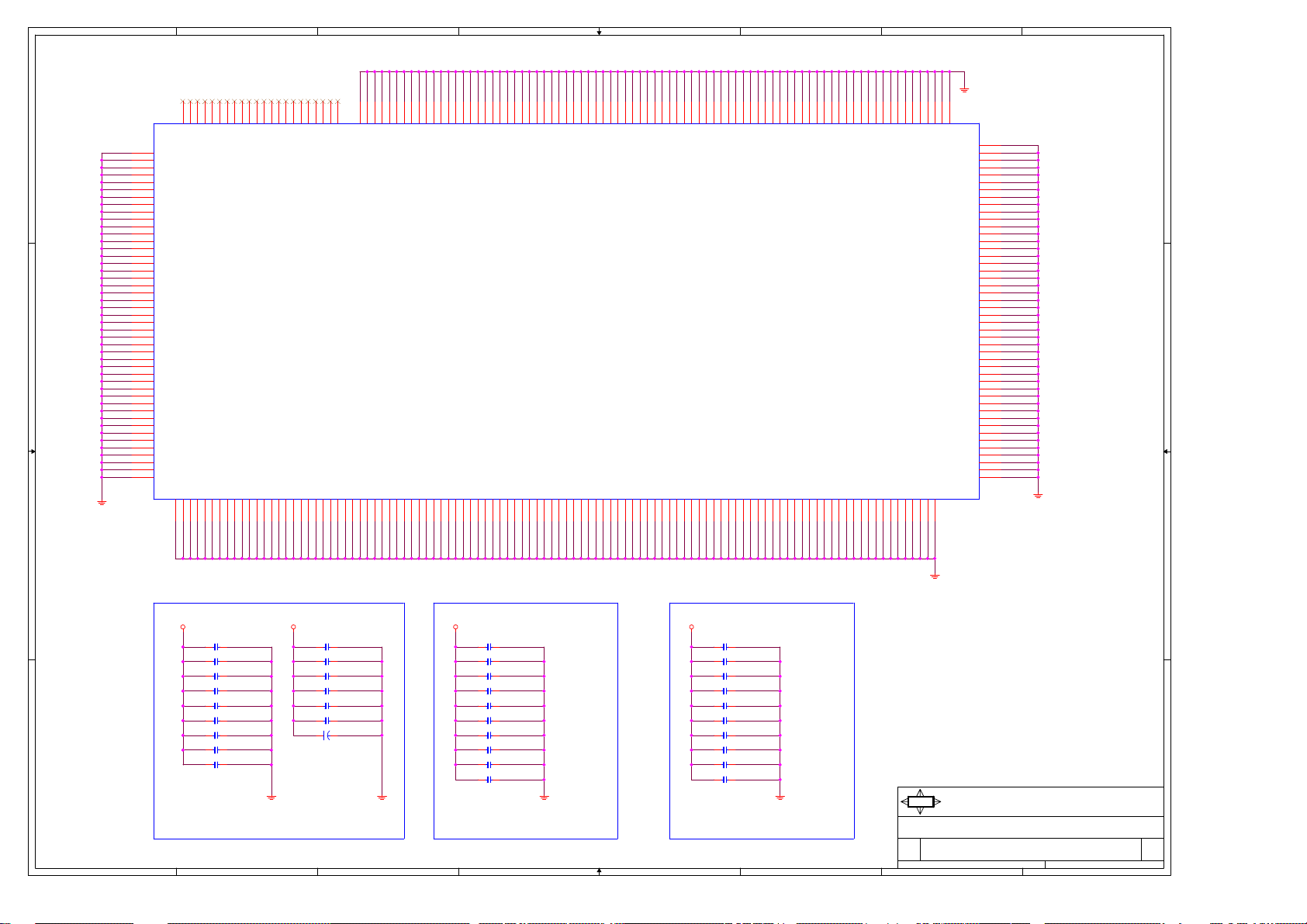

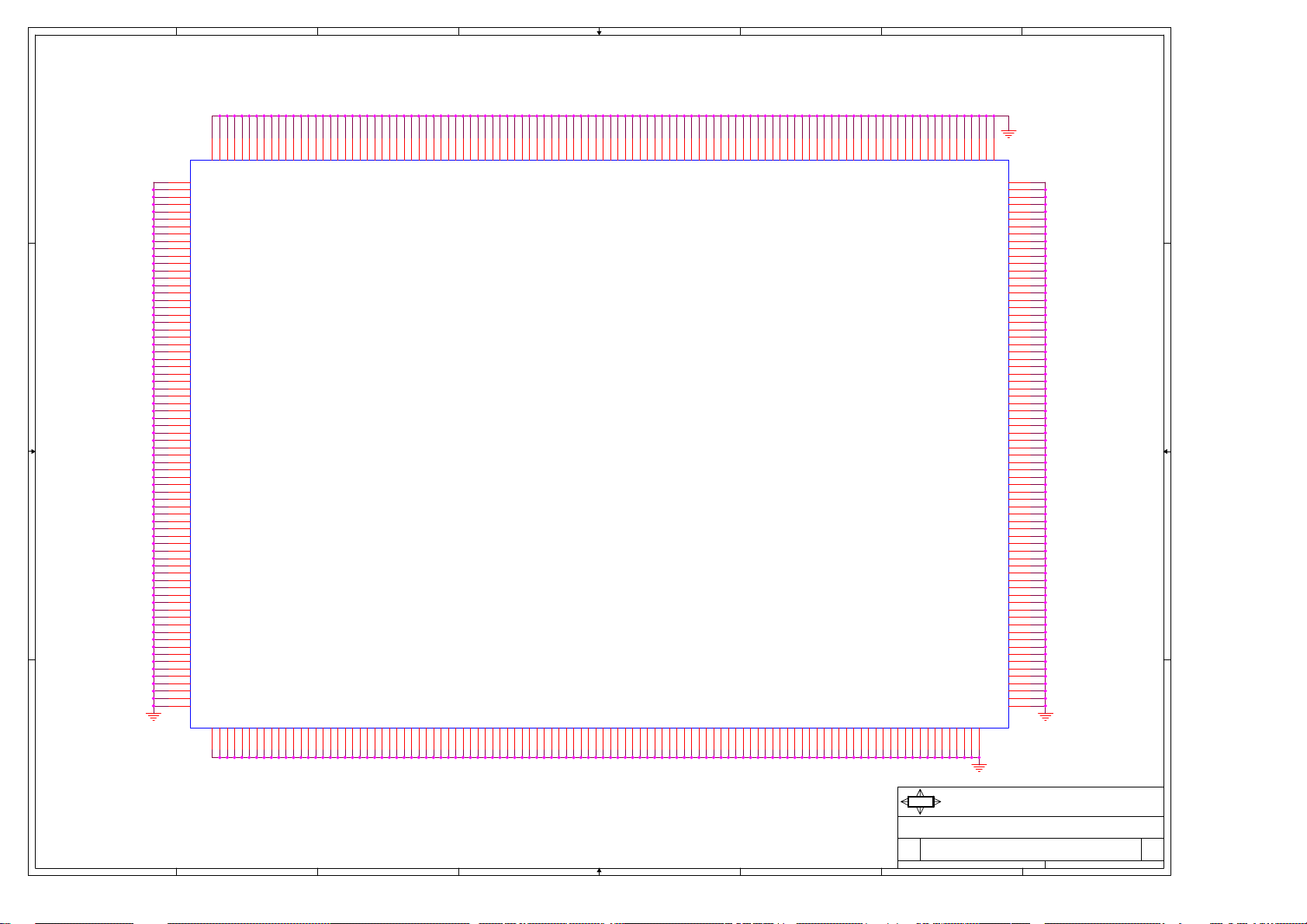

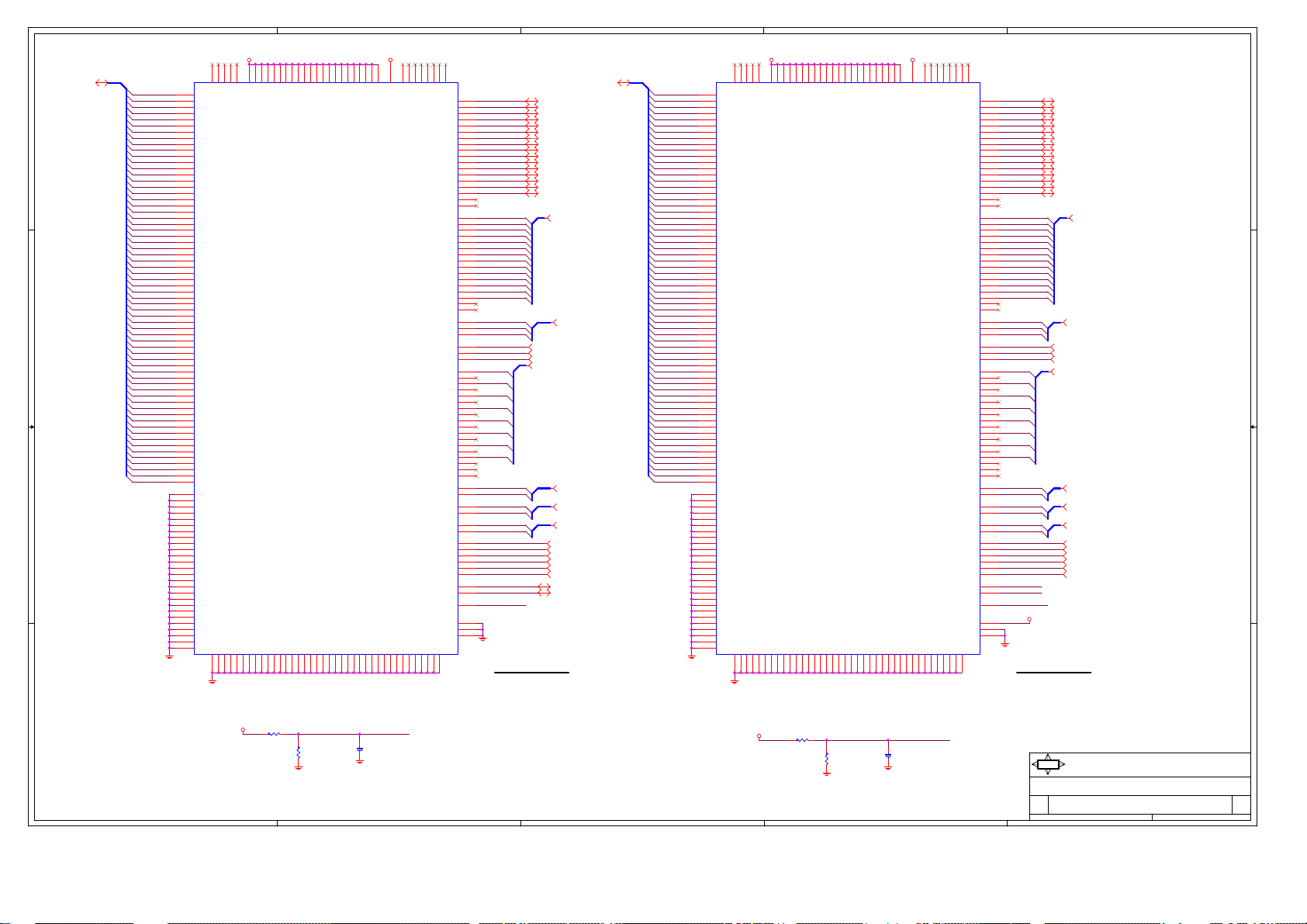

DDR II DIMM 1 , 2

1-4

5-7

8-11

12-13

MS-7059D2

Intel (R) Grantsdale (GMCH) + ICH6 Chipset

Version: X00

Intel Tejas & Prescott LGA775 Processor

PCI Express X16 SLOT 14

CLOCK - ICS954101

ICH6

PCI SLOT & FWH & LPC DEBUG PORT

LAN - BCM4401KQL

1394 TSB43AB23

LPC I/O - SMSC 47M584 & Serial Port

Audio - AC'97/Azalia AD1980/86

MDC 1.0 Interface & Internal 1394a/USB

A A

IDE & SATA & ITP

USB Connectors

VGA Connector

ATX & Front Panel & FAN & Daig LED

DC POWER

VRM 10.1 - ADP3168 + ADP3418 4 PHASES

GPIO & JUMPER SETTING

Manual Parts & Power Delivery

Clock Distribution

SMBUS/I2C Distribution Map

15

16-18

19

20

21

22

23

24

25

26

27

28

29-31

32

33

34

35

36Power Map

37

CPU:

Intel Tejas/Prescott - 3.0G & Above

System Chipset:

Intel Grantsdale - GMCH (North Bridge)

Intel ICH6 (South Bridge)

On Board Chipset:

BIOS -- FWH FLASH 4Mb

Audio - AC'97/Azalia AD1980/86

LPC Super I/O -- SMSC47M584

LAN - Broadcom 4401KQL

1394 -- TSB43AB23

CLOCK -- ICS954101

Main Memory:

2 CHANNEL DDR II * 2 (Max 2GB)

Expansion Slots:

PCI Express X16 SLOT * 1

PCI 2.2 SLOT * 1

ADI PWM:

Controller: ADP3168/3188

Driver: ADP3418

Revision History

Population Option Parts. 40

38-39

MSI

Title

Size Document Number Rev

1

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

COVER SHEET

Rickles

1 40Tuesday, February 24, 2004

X00

1

P.30

P.14

P.27

P.25

P.25

P.25

P.26

P.23

VID

PCI Express X16

RGB

UltraDMA

33/66/100

SATA

USB2.0

AC Link

Intel LGA775 Processor

FSB

Grantsdale-G

P.8~11

DMI

ICH6

P.16~18

PCI

P.5~7

CHANNEL A

CHANNEL B

LPC Bus

P.19

Block Diagram

DDR2

DIMM 1

Module

P.12

DDR2

DIMM 2

Module

P.12

LPC SIO

47M584

P.22

Floopy

P.22

ParallelFWH

P.25

Serial

P.25

VRM 10.1

ADP 3168

4-Phases PWM

PCI

EXPRESS

X16

Connector

Analog

Video

Out

IDE Primary

SERIAL ATA1

A A

SERIAL ATA2

USB2.0

USB Port0~ 7

AD1980

AC'97 Codec

LAN

BCM4401KQL

P.20

1394

TSB43AB23

P.21

PCI Slot

1

P.19

MICRO-STAR INt'L CO., LTD.

MSI

Title

Size Document Number Rev

Date: Sheet of

BLOCK DIAGRAM

Rickles

2 40Tuesday, February 24, 2004

X00

8

7

6

5

4

3

2

1

VRM 10.1

ADP 3168

D D

4-Phases PWM

P.30

Intel LGA775 Processor

P.5~7

~H_RESET

ITP PORT

~H_RESET_R

P.25

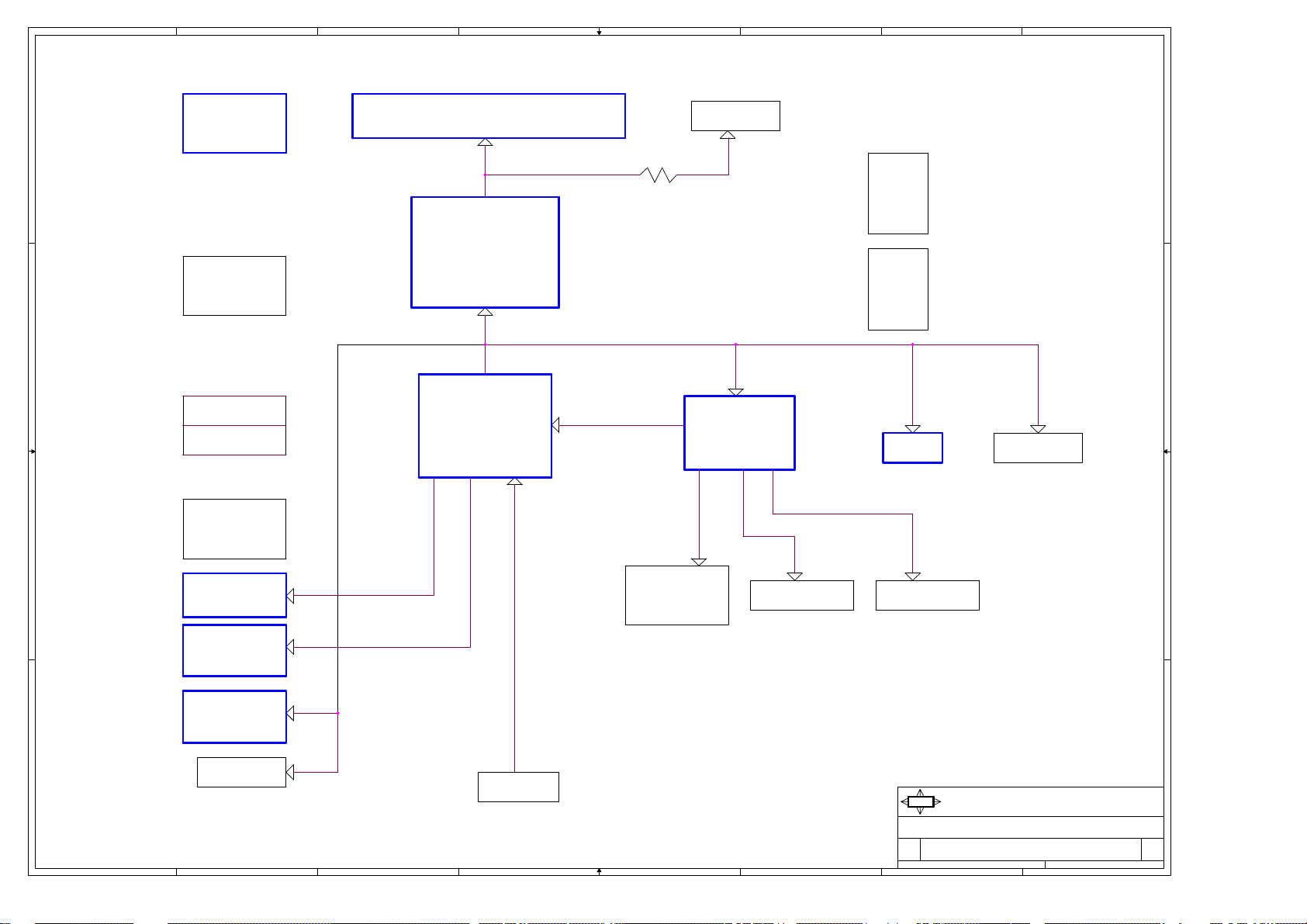

RESET MAP

DDR2

DIMM 1

Module

P.12

Grantsdale-G

Analog

Video

Out

C C

SERIAL ATA1

SERIAL ATA2

P.27

P.25

P.25

ICH6

USB2.0

USB Port0~ 7

B B

AD1980

AC'97 Codec

LAN

P.26

~AC97_RESET

P.23

~PCI_RST

BCM4401KQL

P.20

P.8~11

~PLT_RST

P.16~18

~PB_RESET

~ICH_RSMRST

~EXP_RST_SLOTS

PCI

EXPRESS

X16

Connector

LPC SIO

47M584

P.22

~IDE_PRST

IDE Primary

P.14

DDR2

DIMM 2

Module

FWH

PCI_RST_SLOTS

PCI Slot

P.25

P.12

P.19

P.19

LPC DEBUG

PORT

P.19

1394

TSB43AB23

P.21

A A

8

Diag LED

P.22

7

6

RESET SW

5

MICRO-STAR INt'L CO., LTD.

MSI

Title

Size Document Number Rev

4

3

Date: Sheet of

2

Reset Map

Rickles

3 40Tuesday, February 24, 2004

1

X00

8

7

6

5

4

3

2

1

H_VTT_PWRGOOD

VRM 10.1

ADP 3168

D D

4-Phases PWM

P.30

Intel LGA775 Processor

P.5~7

H_PWRGOOD

PCI

EXPRESS

X16

Connector

P.14

Grantsdale-G

3P3V_PWRGOOD

Analog

Video

Out

C C

IDE Primary

P.27

P.25

P.8~11

VTT_OUT

DDR2

DIMM 1

Module

P.12

DDR2

DIMM 2

Module

P.12

VTT PWRGOOD

DELAY

CIRCUIT

VTT_PWRGOOD signal must be delayed 1-10ms

after VTT_FSB for proper clock/cpu function

P.12

PWROK MAP

SERIAL ATA1

SERIAL ATA2

P.25

P.25

ICH6

P.16~18

3P3V_PWRGOOD

USB2.0

USB Port0~ 7

B B

AD1980

AC'97 Codec

P.26

P.23

~ICH_SLP_S4

~ICH_SLP_S3

LPC SIO

47M584

~PWR_PS_ON

PS_PWRGOOD

P.22

POWER CONN

LAN

BCM4401KQL

P.20

1394

TSB43AB23

P.21

A A

8

PCI Slot

P.19

7

6

~ICH_PWRBTN

FP

5

FWH

P.19

Floopy Parallel Serial

4

P.22 P.25 P.25

3

MICRO-STAR INt'L CO., LTD.

MSI

Title

Size Document Number Rev

Date: Sheet of

2

PWROK MAP

Rickles

4 40Tuesday, February 24, 2004

1

X00

8

7

6

5

4

3

2

1

VID Pull-Up Resistor

H_VID2

H_VID1

AM3

AL5

VID3#

VID2#

VID1#

GTLREF

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

RSVD

RSVD

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

D0#

LGA775

H_VID0

AM2

~H_PB_RESET 17,25

H_VCCSENSE 32

H_VSSSENSE 32

H_AN5 32

H_AN6 32

~CK_100M_ITP 15,25

CK_100M_ITP 15,25

H_VID[0..5] 32

VID0#

H1

~H_BPM5/PREQ

AG3

~H_BPM4/PRDY

AF2

~H_BPM3

AG2

~H_BPM2

AD2

~H_BPM1

AJ1

~H_BPM0

AJ2

~H_PCREQ

G5

~H_REQ4

J6

~H_REQ3

K6

~H_REQ2

M6

~H_REQ1

J5

~H_REQ0

K4

TESTHI_PU_12

W2

TESTHI_PU_11

P1

TESTHI_PU_10

H5

TESTHI_PU_9

G4

TESTHI_PU_8

G3

F24

G24

G26

G27

G25

TESTHI_PU_2

F25

TESTHI_PU_1

W3

TESTHI_PU_0

F26

AK6

G6

G28

F28

~H_RS2

A3

~H_RS1

F5

~H_RS0

B3

U3

U2

F3

H_COMP3

R1

H_COMP2

G2

H_COMP1

T1

H_COMP0

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

H_GTLREF_CPU

R161 62/4

R262 62/4

R162 62/4

R260 100/4/1

R254 100/4/1

R261 60.4/4/1

R206 60.4/4/1

3

H_GTLREF_CPU 6

H_TMS

R264 39/4

H_TDO

R267 75/4/1

H_TDI

R265 150/4/1

R291 62/4

R289 62/4

R286 62/4

R285 62/4

R284 62/4

R282 62/4

~H_PCREQ 8

~H_REQ[0..4] 8

R263 62/4

R259 62/4

R257 62/4

R255 62/4

R256 62/4

~CK_100M_CPU 15

CK_100M_CPU 15

~H_RS[0..2] 8

~H_BREQ0 6,8

PLACE RESISTORS OUTSIDE SOCKET

CAVITY IF NO ROOM FOR VARIABLE

RESISTOR DON'T PLACE

~H_ADSTB1 8

~H_ADSTB0 8

~H_DSTBP3 8

~H_DSTBP2 8

~H_DSTBP1 8

~H_DSTBP0 8

~H_DSTBN3 8

~H_DSTBN2 8

~H_DSTBN1 8

~H_DSTBN0 8

H_NMI 16

H_INTR 16

VTT_OUT

VTT_OUT

MSI

Title

Size Document Number Rev

Date: Sheet of

VTT_OUT

C334 0.1u/16V/4

C328 0.1u/16V/4

V_CPU_VTT

VTT_OUT

C1517

X_0.1u/16V/4

MICRO-STAR INt'L CO., LTD.

2

VTT_OUT

RN14

1K/4/8P4R

H_VID1

1

H_VID2

H_VID4

H_VID3

H_VID0

H_VID5

~H_TRST

H_TCK

~H_BPM5/PREQ

~H_BPM4/PRDY

~H_BPM3

~H_BPM2

~H_BPM1

~H_BPM0

VTT_OUT 6,18,22,25,29,32

2

3

4

5

6

7

8

R243 1K/4

R244 1K/4

R268 680/4

R266 27/4

~H_BPM5/PREQ 25

~H_BPM4/PRDY 25

~H_BPM[0..3] 25

Intel LGA775 CPU - Signals

Rickles

5 40Tuesday, February 24, 2004

X00

1

H_VCCSENSE

CPU SIGNAL BLOCK

D D

~H_INIT16

~H_BPRI8

H_TDI25

H_TDO25

H_TMS25

~H_TRST25

H_TCK25

~H_SMI16

~H_A20M16

NC_H_BOOTSELECT

H_BSEL06,10,15

H_BSEL16,10,15

H_BSEL26,10,15

~H_DBI0

~H_DBI1

~H_DBI2

~H_DBI3

H_TDI

H_TDO

H_TMS

~H_TRST

H_TCK

H_LL_ID0

NC_H__LL_ID1

~H_D63

~H_D62

~H_D61

~H_D60

~H_D59

~H_D58

~H_D57

~H_D56

~H_D55

~H_D54

7

~H_DBI[0..3]8

~H_EDRDY8

~H_IERR6

~H_FERR6,16

~H_STPCLK16

C C

B B

A A

8

~H_DBSY8

~H_DRDY8

~H_TRDY8

~H_ADS8

~H_LOCK8

~H_BNR8

~H_HIT8

~H_HITM8

~H_DEFER8

H_THRM_ANODE22

H_THRM_CATHODE22

~H_THRMTRP6,16

~H_PROCHOT6,22

~H_IGNNE16

~H_CPUSLP16

H_LL_ID032

H_PWRGOOD6,16

~H_RESET6,8,25

~H_D[0..63]8

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

~H_A[3..31]8

CPUA

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

~H_D53

D53#

D52#

C14

~H_D52

D51#

D50#

C15

A14

~H_D50

~H_D51

AJ6

A35#

D49#

D48#

D17

D20

~H_D48

~H_D49

AJ5

AH5

A34#

A33#

D47#

D46#

G22

D22

~H_D47

~H_D46

~H_A31

AH4

AG5

A32#

A31#

D45#

D44#

E22

G21

~H_D45

~H_D44

~H_A30

~H_A29

AG4

AG6

A30#

A29#

D43#

D42#

F21

E21

~H_D43

~H_D42

6

~H_A27

~H_A28

AF4

AF5

A28#

A27#

D41#

D40#

F20

E19

~H_D40

~H_D41

~H_A26

AB4

A26#

D39#

E18

~H_D39

~H_A19

~H_A24

~H_A25

AC5

AB5

A25#

A24#

D38#

D37#

F18

F17

~H_D37

~H_D38

~H_A23

AA5

AD6

A23#

A22#

D36#

D35#

G17

G18

~H_D36

~H_D35

~H_A15

~H_A18

~H_A20

~H_A16

AA4Y4Y6W6AB6W5V4V5U4U5T4U6T5R4M4L4M5P6L5

A21#

A20#

A19#

A18#

A17#

A16#

A15#

D34#

D33#

D32#

D31#

D30#

D29#

D28#

E16

E15

G16

G15

F15

G14

F14

~H_D30

~H_D28

~H_D33

~H_D31

~H_D34

~H_D29

~H_D32

~H_A17

~H_A21

~H_A22

~H_A13

~H_A14

A14#

A13#

D27#

D26#

G13

E13

~H_D26

~H_D27

~H_A12

~H_A11

A12#

A11#

D25#

D24#

D13

F12

~H_D25

~H_D24

5

~H_A7

~H_A8

~H_A9

~H_A10

A9#

A8#

A7#

A10#

D23#

D22#

D21#

D20#

F11

D10

E10D7E9F9F8G9D11

~H_D22

~H_D23

~H_D21

~H_D20

~H_A5

~H_A6

A6#

A5#

D19#

D18#

~H_D19

~H_D18

~H_A4

~H_A3

A4#

A3#

D17#

D16#

~H_D17

~H_D16

~H_PB_RESET

AC2

DBR#

D15#

D14#

C12

~H_D14

~H_D15

AN3

RSVD

D13#

D12#

B12D8C11

~H_D12

~H_D13

AN4

AN5

RSVD

VCC_SENSE

D11#

D10#

B10

~H_D10

~H_D11

H_VSSSENSE

AN6

AJ3

AK3

AM5

RSVD

ITP_CLK1

ITP_CLK0

VSS_SENSE

D9#

D8#

D7#

D6#

D5#

D4#

D3#

A11

A10A7B7B6A5C6A4C5B4

~H_D8

~H_D6

~H_D5

~H_D7

~H_D9

~H_D4

~H_D3

4

H_AN5

H_AN6

H_VID5

H_VID4

AL4

AK4

VID5#

VID4#

D2#

D1#

~H_D1

~H_D2

H_VID3

AL6

LINT0/INTR

~H_D0

8

7

6

5

4

3

2

1

+CPUCORE

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

CPUB

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

U26

U27

U28

U29

U30U8V8

W23

W24

W25

W26

W27

W28

W29

W30W8Y23

Y24

Y25

Y26

Y27

Y28

Y29

Y30

Y8

+CPUCORE

D D

C C

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCA

VSSA

RSVD

VCC-IOPLL

VTTPWRGD

VTT_OUT

VTT_OUT

VTT_SEL

RSVD/VTT_PKGSENSE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AN8

AN9

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30J8J9

K23

K24

K25

K26

K27

K28

K29

K30K8L8

M23

M24

M25

M26

M27

M28

M29

M30M8N23

N24

N25

N26

N27

N28

N29

N30N8P8R8T23

T24

T25

T26

T27

T28

T29

T30T8U23

U24

U25

AN30

AN29

AN26

AN25

LGA775

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

A23

B23

D23

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

F29

VTT_OUT

VTT_OUT

VCC_IO_PLL_A_H

VSS_A_H

VCC_IO_PLL_A_H

H_VTT_PWRGOOD

V_CPU_VTT

H_VTT_PWRGOOD 29,32

VTT_OUT 5,18,22,25,29,32

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

+CPUCORE

B B

V_CPU_VTT

C1518 10u/10V/8

C1519 10u/10V/8

V_CPU_VTT

L30 X_10uH/8

VCC_IO_PLL_A_H

VSS_A_H

L58 FB600/6

C186

22u/6.3V/1206

V_CPU_VTT

DC voltage drop should

be less than 70mV.

R174 470/4

R175 470/4

R154 470/4

4

L31 X_10uH/8

L59 FB600/6

H_BSEL0

H_BSEL1

H_BSEL2

H_BSEL0 5,10,15

H_BSEL1 5,10,15

H_BSEL2 5,10,15

3

49.9 OHM OVER 100 OHM RESISTORS

V_CPU_VTT

VTT_OUT

R277

49.9/4/1

R278

100/4/1

PLACE AT CPU END OF ROUTE

R163 62/4

R246 X_120/4

R258 100/4

R253 62/4

R1334 62/4

PLACE AT ICH END OF ROUTE

R455 62/4

R456 62/4

7

C338

1u/10V/6

~H_RESET

~H_PROCHOTVTT_OUT

H_PWRGOOD

~H_BREQ0

~H_IERR

~H_THRMTRP

~H_FERR

H_GTLREF_CPU

C333

220p/25V/4

~H_RESET 5,8,25

~H_PROCHOT 5,22

H_PWRGOOD 5,16

~H_BREQ0 5,8

~H_IERR 5

C1680 X_0.1u/16V/4

~H_THRMTRP 5,16

~H_FERR 5,16

H_GTLREF_CPU 5

6

5

VTT_OUT

GTLREF VOLTAGE SHOULD BE

0.67*VTT = 0.8V

A A

8

C190

X_10u/10V/8

MSI

Title

Size Document Number Rev

Date: Sheet of

C189

X_1u/10V/6

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - Power

Rickles

2

6 40Tuesday, February 24, 2004

X00

1

8

AC4

AE3

AE4D1D14

CPUC

D D

C C

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

A12

A15

A18

A21

A24

AA3

AA6

AA7

AB1

AB7

AC3

AC6

AC7

AD4

AD7

AE2

RSVD

RSVD

VSS

VSS

VSS

A2

VSS

VSS

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

AE30

AE5

AE7

7

E23

E24E5E6E7F23F6B13H2J2J3N4P5T2V1W1Y3Y7Y5Y2W7W4V7V6

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF3

AF30

AF6

AF7

AG10

AG13

AG16

AG17

VSS

VSS

AG20

VSS

VSS

AG23

VSS

VSS

AG24

AG7

VSS

VSS

AH1

VSS

VSS

6

AH10

VSS

VSS

VSS

VSS

AH13

VSS

VSS

AH16

V30V3V29

VSS

VSS

VSS

VSS

AH17

AH20

AH23

VSS

VSS

V28

VSS

VSS

AH24

V27

AH3

V26

V25

V24

V23U7U1T7T6T3R7R5R30

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH6

AH7

AJ10

AJ13

AJ16

VSS

VSS

AJ17

VSS

VSS

AJ20

VSS

VSS

AJ23

VSS

VSS

AJ24

VSS

VSS

AJ27

VSS

VSS

AJ28

VSS

VSS

5

AJ29

VSS

VSS

R29

AJ30

VSS

VSS

4

R28

R27

R26

R25

R24

R23R2P7P4P30

P29

P28

P27

P26

P25

P24

P23N7N6N3M7M1L7L6L30L3L29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

AL17

AL20

AL23

VSS

VSS

AL24

VSS

VSS

AL27

VSS

VSS

AL28

VSS

VSS

L28

L27

L26

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL3

AL7

AM1

AM10

AM13

L25

VSS

VSS

AM16

L24

VSS

VSS

AM17

L23K7K5

VSS

VSS

VSS

VSS

AM20

AM23

VSS

VSS

AM24

VSS

VSS

AM27

3

VSS

VSS

AM28

AM4

VSS

VSS

AM7

VSS

VSS

AN1

VSS

VSS

VSS

VSS

AN10

VSS

VSS

AN13

VSS

VSS

AN16

H29H3H6H7H8H9J4J7K2

VSS

VSS

AN17

H28

AN2

VSS

VSS

H27

AN20

VSS

VSS

H26

VSS

VSS

AN23

H25

VSS

VSS

AN24

H24

VSS

VSS

AN27

H23

VSS

VSS

AN28

H21

H22

VSS

VSS

VSS

VSS

AN7B1B11

2

H17

H18

H19

H20

VSS

VSS

VSS

VSS

VSS

B14

VSS

LGA775

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

1

B B

+CPUCORE+CPUCORE +CPUCORE +CPUCORE

C261 10u/10V/8

C266 10u/10V/8

C278 10u/10V/8

C235 10u/10V/8

C236 10u/10V/8

C275 10u/10V/8

C274 10u/10V/8

C254 10u/10V/8

A A

C255 10u/10V/8

PLACE CAPS WITHIN CPU CAVITY PLACE CAPS AT NORTH OF CPU PLACE CAPS AT EAST OF CPU

8

7

C253 10u/10V/8

C260 10u/10V/8

C247 10u/10V/8

C238 10u/10V/8

C232 10u/10V/8

C239 10u/10V/8

C227 10u/10V/8

C225 10u/10V/8

C234 10u/10V/8

C245 10u/10V/8

C249 10u/10V/8

C267 10u/10V/8

C259 10u/10V/8

C279 10u/10V/8

C286 10u/10V/8

C282 10u/10V/8

6

5

C1717 10u/10V/8

C1718 10u/10V/8

C1719 10u/10V/8

C1720 10u/10V/8

C1721 10u/10V/8

C1722 10u/10V/8

C1723 10u/10V/8C180 220u/2V/SP

C1724 10u/10V/8

C1725 10u/10V/8

C1726 10u/10V/8

4

MSI

Title

Size Document Number Rev

3

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - GND

Rickles

2

7 40Tuesday, February 24, 2004

X00

1

8

7

6

5

4

3

2

1

+1_5V

AC11

AB11

Y20

Y19

Y17

Y16

W20

W16

U20

U16

T20

T19

T17

T16

AA13

AA14

AA16

AA18

AA20

AA21

AA22

AA23

AA24

AB13

AB14

AB15

AB16

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AB24

N13

N14

N15

N16

N18

N20

N21

P13

P14

P15

P17

P19

P21

P22

R13

R14

R15

R16

R18

R20

R22

R23

T13

T14

T15

T21

T23

T24

U13

U14

U22

U24

V13

V14

V15

V21

V23

V24

W13

W14

W22

W24

Y13

Y14

Y15

Y21

Y23

VCCNCTF

VCCNCTF

AP1

B35B1A34

VCCNCTF

VCCNCTF

VCCNCTF

Grantsdale-G

A2

Y24

VCCNCTF

VCCNCTF

DINV_0#

DINV_1#

DINV_2#

DINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

J33

H33

J34

G35

H35

G34

F34

G33

D34

C33

D33

B34

C34

B33

C32

B32

E28

C30

D29

H28

G29

J27

F28

F27

E27

E25

G25

J25

K25

L25

L23

K23

J22

J24

K22

J21

M21

H23

M19

K21

H20

H19

M18

K18

K17

G18

H18

F17

A25

C27

C31

B30

B31

A31

B27

A29

C28

A28

C25

C26

D27

A27

E24

B25

E34

J26

K19

B26

E33

E35

H26

F26

J19

F19

B29

C29

~H_D0

~H_D1

~H_D2

~H_D3

~H_D4

~H_D5

~H_D6

~H_D7

~H_D8

~H_D9

~H_D10

~H_D11

~H_D12

~H_D13

~H_D14

~H_D15

~H_D16

~H_D17

~H_D18

~H_D19

~H_D20

~H_D21

~H_D22

~H_D23

~H_D24

~H_D25

~H_D26

~H_D27

~H_D28

~H_D29

~H_D30

~H_D31

~H_D32

~H_D33

~H_D34

~H_D35

~H_D36

~H_D37

~H_D38

~H_D39

~H_D40

~H_D41

~H_D42

~H_D43

~H_D44

~H_D45

~H_D46

~H_D47

~H_D48

~H_D49

~H_D50

~H_D51

~H_D52

~H_D53

~H_D54

~H_D55

~H_D56

~H_D57

~H_D58

~H_D59

~H_D60

~H_D61

~H_D62

~H_D63

~H_DBI0

~H_DBI1

~H_DBI2

~H_DBI3

~H_DSTBP0 5

~H_DSTBN0 5

~H_DSTBP1 5

~H_DSTBN1 5

~H_DSTBP2 5

~H_DSTBN2 5

~H_DSTBP3 5

~H_DSTBN3 5

~H_D[0..63] 5

~H_DBI[0..3] 5

U17A

~H_A3

~H_A[3..31]5

D D

C C

~H_ADSTB05

~H_ADSTB15

~H_PCREQ5

~H_BREQ05,6

~H_BPRI5

~H_BNR5

~H_LOCK5

~H_ADS5

~H_REQ[0..4]5

~H_HIT5

~H_HITM5

~H_DEFER5

~H_TRDY5

~H_DBSY5

~H_DRDY5

~H_EDRDY5

B B

~H_RS[0..2]5

20/4/1

R213

CK_100M_MCH15

~CK_100M_MCH15

3P3V_PWRGOOD17,22

~H_RESET5,6,25

~PLT_RST16,19,21,22,28

~ICH_SYNC17

HXRCOMP

HXSCOMP

HXSWING

MCH_GTLREF

~H_A4

~H_A5

~H_A6

~H_A7

~H_A8

~H_A9

~H_A10

~H_A11

~H_A12

~H_A13

~H_A14

~H_A15

~H_A16

~H_A17

~H_A18

~H_A19

~H_A20

~H_A21

~H_A22

~H_A23

~H_A24

~H_A25

~H_A26

~H_A27

~H_A28

~H_A29

~H_A30

~H_A31

~H_REQ0

~H_REQ1

~H_REQ2

~H_REQ3

~H_REQ4

~H_RS0

~H_RS1

~H_RS2

M30

M28

M26

M35

M31

M32

M23

M22

AG7

M14

H29

K29

G30

G32

K30

K27

K33

R29

N26

N31

P26

N29

P28

R28

N33

T27

T31

U28

T26

T29

N27

E31

R33

E30

F33

E32

H31

G31

F31

N35

N34

P33

K34

P34

G24

AF7

B23

D24

A23

A24

J29

L29

L31

L28

J28

L26

J31

L33

L34

J35

L35

J32

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

HPCREQ#

BREQ0#

BPRI#

BNR#

HLOCK#

ADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HIT#

HITM#

DEFER#

HTRDY#

DBSY#

DRDY#

HEDRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

CPURST#

RSTIN#

ICH_SYNC#

HDRCOMP

HDSCOMP

HDSWING

HDVREF

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

AK21

AJ21

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

AK24

AL21

AL20

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

AK18

AJ24

AJ23

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

AJ18

AJ20

V31

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

V30

U30

V32

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

Y30

AB29

R31

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

R30

AA31

AA30

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

AC12

AC13

AC14

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

AC15

AC16

AC17

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

RSVRD

AC18

AC19

AC20

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

NCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNC

RSVRD

RSVRD

RSVRD

N12

N22

N23

N24

P12

P23

P24

R12

R24

T12

U12

V12

W12

Y12

AA12

AB12

AC23

AC24

AN19

AL28

AJ14

AH24

AG6

AD30

P30

L19

L12

K12

J12

H17

H15

H12

G12

F24

F12

E16

C16

AR35

AC21

AC22

AR34

VCCNCTF

VCCNCTF

VCCNCTF

AR2

AR1

AP35

VCCNCTF

A A

V_CPU_VTT V_CPU_VTT V_CPU_VTT

8

R219

60.4/4/1 R195

C257

X_2.2p/25V/4

HXSCOMP MCH_GTLREF

7

HSWING S/B 1/4*VTT +/- 2%

PLACE DIVIDER RESISTOR NEAR VTT

R218 301/4/1

R217

102/4/1

6

5

HXSWING

C264

0.01u/16V/4

MCH_GTLREF VOLTAGE SHOULD BE 0.67*VTT=0.8V

49.9 OHM OVER 100 RESISTORS

R207 49.9/4/1

3

C244

220p/25V/4

100/4/1

4

C231

1u/10V/6

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

Intel Grantsdale - CPU Signals

Rickles

2

8 40Tuesday, February 24, 2004

1

X00

8

7

6

5

4

3

2

1

M_CHA_CKE[0..1]12,13

M_CHA_DM[0..7]12

M_CHA_DQ[0..63]12

M_CHA_DM6

M_CHA_DM2

M_CHA_DM7

M_CHA_DM3

M_CHA_DM5

M_CHA_DM4

M_CHA_DQ37

M_CHA_DQ17

M_CHA_DQ16

M_CHA_DQ15

M_CHA_DQ18

AP3

AR5

AP6

AP9

SADQ14

SADQ15

SADQ16

SADQ17

SBDQ12

SBDQ13

SBDQ14

SBDQ15

AL7

AG10

AG11

AF13

M_CHA_DQ22

M_CHA_DQ21

M_CHA_DQ20

M_CHA_DQ19

AN9

AN5

AP5

AN8

SADQ18

SADQ19

SADQ20

SADQ21

SBDQ16

SBDQ17

SBDQ18

SBDQ19

AH12

AD14

AD15

AD12

M_CHA_DQ25

M_CHA_DQ23

M_CHA_DQ26

M_CHA_DQ24

AR8

AL17

AJ17

AF19

SADQ22

SADQ23

SADQ24

SADQ25

SBDQ20

SBDQ21

SBDQ22

SBDQ23

AE13

AG14

AF14

AK19

M_CHA_DQ29

M_CHA_DQ28

M_CHA_DQ27

AH18

AK16

AF16

SADQ26

SADQ27

SADQ28

SADQ29

SBDQ24

SBDQ25

SBDQ26

SBDQ27

AH19

AH21

AD21

M_CHA_DQ30

M_CHA_DQ32

M_CHA_DQ31

M_CHA_DQ33

AD17

AE19

AK27

AJ28

SADQ30

SADQ31

SADQ32

SADQ33

SBDQ28

SBDQ29

SBDQ30

SBDQ31

AD18

AL18

AE22

AF22

M_CHA_DQ34

AL31

AF24

AH3

SADQ1

SADQ2

SBDQ0

AH4

AJ2

AJ6

AE2

SADQ3

SADQ4

SBDQ1

SBDQ2

AL6

AE1

AN6

AG3

SADQ5

SADQ6

SBDQ3

SBDQ4

AG9

AH2

SADQ7

SBDQ5

AH7

AK2

SADQ8

SBDQ6

AL5

M_CHA_DQ9

AK3

AN4

AP4

AJ1

SADQ9

SADQ10

SADQ11

SBDQ7

SBDQ8

SBDQ9

AM5

AJ8

AL8

AF11

AJ3

AP2

SADQ12

SADQ13

SBDQ10

SBDQ11

AE11

AJ7

D D

~M_CHA_CS[0..1]12,13

~M_CHA_RAS12,13

~M_CHA_CAS12,13

~M_CHA_WE12,13

M_CHA_MA[0..13]12,13

M_CHA_ODT[0..1]12,13

M_CHA_BA[0..2]12,13

C C

B B

M_CHA_DQS012

~M_CHA_DQS012

M_CHA_DQS112

~M_CHA_DQS112

M_CHA_DQS212

~M_CHA_DQS212

M_CHA_DQS312

~M_CHA_DQS312

M_CHA_DQS412

~M_CHA_DQS412

M_CHA_DQS512

~M_CHA_DQS512

M_CHA_DQS612

~M_CHA_DQS612

M_CHA_DQS712

~M_CHA_DQS712

M_CHA_SCK012

~M_CHA_SCK012

M_CHA_SCK112

~M_CHA_SCK112

M_CHA_SCK212

~M_CHA_SCK212

~M_CHA_CS0

~M_CHA_CS1

~M_CHA_RAS

~M_CHA_CAS

~M_CHA_WE

M_CHA_MA0

M_CHA_MA1

M_CHA_MA2

M_CHA_MA3

M_CHA_MA4

M_CHA_MA5

M_CHA_MA6

M_CHA_MA7

M_CHA_MA8

M_CHA_MA9

M_CHA_MA10

M_CHA_MA11

M_CHA_MA12

M_CHA_MA13

M_CHA_ODT0

M_CHA_ODT1

M_CHA_BA0

M_CHA_BA1

M_CHA_BA2

M_CHA_DQS0

~M_CHA_DQS0

M_CHA_DQS1

~M_CHA_DQS1

M_CHA_DQS2

~M_CHA_DQS2

M_CHA_DQS3

~M_CHA_DQS3

M_CHA_DQS4

~M_CHA_DQS4

M_CHA_DQS5

~M_CHA_DQS5

M_CHA_DQS6

~M_CHA_DQS6

M_CHA_DQS7

~M_CHA_DQS7

M_CHA_SCK0

~M_CHA_SCK0

M_CHA_SCK1

~M_CHA_SCK1

M_CHA_SCK2

~M_CHA_SCK2

TP_SA_RCVENOUT

TP_SA_RCVENIN

BUFFER_SLEW_A

SM_VREF

SM_RCOMP_1

SM_RCOMP_0

SM_OCDCOMP_1

SM_OCDCOMP_0

AR29

AP32

AR28

AN31

AP27

AN29

AN28

AP26

AR24

AL24

AP23

AR23

AP22

AN23

AP21

AN22

AN21

AM27

AM21

AR20

AP31

AP30

AN32

AP29

AP33

AR27

AN27

AN20

AF17

AG17

AM30

AL29

AG35

AG33

AA34

AA35

AN26

AP25

AC34

AC35

AN25

AM24

AC33

AB34

AB33

AH15

AE16

AJ12

AK12

AG1

AG2

AL3

AL2

AP7

AR7

U34

U35

AM2

AM3

AN3

AN2

AE7

AG8

AG4

AE5

AF5

U17B

SACS0#

SACS1#

SACS2#

SACS3#

SARAS#

SACAS#

SAWE#

SAMA0

SAMA1

SAMA2

SAMA3

SAMA4

SAMA5

SAMA6

SAMA7

SAMA8

SAMA9

SAMA10

SAMA11

SAMA12

SAMA13

SAODT0

SAODT1

SAODT2

SAODT3

SABA0

SABA1

SABA2

SADQS0

SADQS0#

SADQS1

SADQS1#

SADQS2

SADQS2#

SADQS3

SADQS3#

SADQS4

SADQS4#

SADQS5

SADQS5#

SADQS6

SADQS6#

SADQS7

SADQS7#

SACK0

SACK0#

SACK1

SACK1#

SACK2

SACK2#

SACK3

SACK3#

SACK4

SACK4#

SACK5

SACK5#

SADDR1MA13

SARCVENOUT#

SARCVENIN#

SMXSLEWIN

SMXSLEWOUT

SMVREF0

SMRCOMPP

SMRCOMPN

SMOCDCOMP1

SMOCDCOMP0

AE3

SADQ0

AF3

Grantsdale-G

M_CHA_DQ0

M_CHA_DQ10

M_CHA_DQ13

M_CHA_DQ12

M_CHA_DQ14

M_CHA_DQ11

M_CHA_DQ8

M_CHA_DQ4

M_CHA_DQ2

M_CHA_DQ1

M_CHA_DQ3

M_CHA_DQ6

M_CHA_DQ5

M_CHA_DQ7

M_CHA_DQ36

M_CHA_DQ38

M_CHA_DQ35

AK31

AH27

AL27

AN30

SADQ34

SADQ35

SADQ36

SADQ37

SBDQ32

SBDQ33

SBDQ34

SBDQ35

AF25

AL26

AJ26

AF23

M_CHA_DQ42

M_CHA_DQ40

M_CHA_DQ39

M_CHA_DQ41

AL30

AH33

AH35

AF33

SADQ38

SADQ39

SADQ40

SADQ41

SBDQ36

SBDQ37

SBDQ38

SBDQ39

AD23

AL25

AJ25

AK32

M_CHA_DQ44

M_CHA_DQ46

M_CHA_DQ43

M_CHA_DQ45

AE33

AJ33

AJ34

SADQ42

SADQ43

SADQ44

SADQ45

SBDQ40

SBDQ41

SBDQ42

SBDQ43

AJ31

AG31

AF28

M_CHA_DQ47

M_CHA_DQ48

M_CHA_DQ49

AG32

AF34

AD31

SADQ46

SADQ47

SADQ48

SBDQ44

SBDQ45

SBDQ46

AJ29

AK33

AG30

M_CHA_DQ51

M_CHA_DQ50

M_CHA_DQ52

AD35

Y33

W34

SADQ49

SADQ50

SADQ51

SBDQ47

SBDQ48

SBDQ49

AG27

AF27

AE27

AE35

SADQ52

SBDQ50

AC26

M_CHA_DQ54

M_CHA_DQ57

M_CHA_DQ55

M_CHA_DQ56

M_CHA_DQ53

AE34

AA32

Y35

V34

V33

SADQ53

SADQ54

SADQ55

SADQ56

SBDQ51

SBDQ52

SBDQ53

SBDQ54

AB26

AE31

AE29

AC28

AB27

M_CHA_DQ60

M_CHA_DQ58

M_CHA_DQ61

M_CHA_DQ59

R32

R34

W35

W33

SADQ57

SADQ58

SADQ59

SADQ60

SBDQ55

SBDQ56

SBDQ57

SBDQ58

AA28

W29

V28

V29

M_CHA_DQ62

M_CHA_DQ63

T33

T35

SADQ61

SADQ62

SADQ63

SBDQ59

SBDQ60

SBDQ61

Y26

AA29

M_CHA_CKE0

M_CHA_CKE1

AP19

AM18

AN18

SACKE0

SACKE1

SBDQ62

SBDQ63

W26

U26

AP10

AR19

SACKE2

SACKE3

SBCKE0

SBCKE1

AN10

AR9

M_CHA_DM1

M_CHA_DM0

AF2

AL1

AN7

SADM0

SADM1

SADM2

SBDM7

SBCKE2

SBCKE3

W31

AM9

AH16

SADM3

SBDM6

AD24

AK29

AH31

AG34

AA33

SADM4

SADM5

SADM6

SBRCVENOUT#

SBDM3

SBDM4

SBDM5

AG20

AG24

U33

SBCS0#

SBCS1#

SBCS2#

SADM7

SBCS3#

SBRAS#

SBCAS#

SBWE#

SBMA0

SBMA1

SBMA2

SBMA3

SBMA4

SBMA5

SBMA6

SBMA7

SBMA8

SBMA9

SBMA10

SBMA11

SBMA12

SBMA13

SBODT0

SBODT1

SBODT2

SBODT3

SBBA0

SBBA1

SBBA2

SBDQS0

SBDQS0#

SBDQS1

SBDQS1#

SBDQS2

SBDQS2#

SBDQS3

SBDQS3#

SBDQS4

SBDQS4#

SBDQS5

SBDQS5#

SBDQS6

SBDQS6#

SBDQS7

SBDQS7#

SBCK0

SBCK0#

SBCK1

SBCK1#

SBCK2

SBCK2#

SBCK3

SBCK3#

SBCK4

SBCK4#

SBCK5

SBCK5#

SBDDR1MA13

SBRCVENIN#

SMYSLEWIN

SMYSLEWOUT

SMVREF1

SBDM0

SBDM1

SBDM2

AJ5

AH9

AH13

~M_CHB_CS0

AN33

~M_CHB_CS1

AM34

AP34

AN34

~M_CHB_RAS

AN17

~M_CHB_CAS

AP18

~M_CHB_WE

AP17

M_CHB_MA0

AM15

M_CHB_MA1

AR15

M_CHB_MA2

AN15

M_CHB_MA3

AL15

M_CHB_MA4

AP14

M_CHB_MA5

AM12

M_CHB_MA6

AP13

M_CHB_MA7

AL12

M_CHB_MA8

AN13

M_CHB_MA9

AR12

M_CHB_MA10

AP15

M_CHB_MA11

AP11

M_CHB_MA12

AR11

M_CHB_MA13

AL33

M_CHB_ODT0

AM33

M_CHB_ODT1

AL34

AL35

AK34

M_CHB_BA0

AR16

M_CHB_BA1

AN16

M_CHB_BA2

AN11

M_CHB_DQS0

AK5

~M_CHB_DQS0

AL4

M_CHB_DQS1

AK10

~M_CHB_DQS1

AH10

M_CHB_DQS2

AK13

~M_CHB_DQS2

AL14

M_CHB_DQS3

AD20

~M_CHB_DQS3

AF20

M_CHB_DQS4

AH25

~M_CHB_DQS4

AG26

M_CHB_DQS5

AH28

~M_CHB_DQS5

AH30

M_CHB_DQS6

AB31

~M_CHB_DQS6

AC30

M_CHB_DQS7

W27

~M_CHB_DQS7

Y28

M_CHB_SCK0

AH22

~M_CHB_SCK0

AG23

M_CHB_SCK1

AK9

~M_CHB_SCK1

AL9

M_CHB_SCK2

AE26

~M_CHB_SCK2

AE25

AL23

AK22

AJ11

AL11

AD28

AD29

AD32

TP_SB_RCVENOUT

AK15

TP_SB_RCVENIN

AN14

BUFFER_SLEW_B

AF9

AE10

SM_VREF

AE8

~M_CHB_CS[0..1] 12,13

~M_CHB_RAS 12,13

~M_CHB_CAS 12,13

~M_CHB_WE 12,13

M_CHB_MA[0..13] 12,13

M_CHB_ODT[0..1] 12,13

M_CHB_BA[0..2] 12,13

M_CHB_DQS0 12

~M_CHB_DQS0 12

M_CHB_DQS1 12

~M_CHB_DQS1 12

M_CHB_DQS2 12

~M_CHB_DQS2 12

M_CHB_DQS3 12

~M_CHB_DQS3 12

M_CHB_DQS4 12

~M_CHB_DQS4 12

M_CHB_DQS5 12

~M_CHB_DQS5 12

M_CHB_DQS6 12

~M_CHB_DQS6 12

M_CHB_DQS7 12

~M_CHB_DQS7 12

M_CHB_SCK0 12

~M_CHB_SCK0 12

M_CHB_SCK1 12

~M_CHB_SCK1 12

M_CHB_SCK2 12

~M_CHB_SCK2 12

M_CHB_DQ14

M_CHB_DQ15

M_CHB_DQ21

M_CHB_DQ23

M_CHB_DQ27

M_CHB_DQ11

M_CHB_DQ17

M_CHB_DQ16

M_CHB_DQ13

M_CHB_DQ20

M_CHB_DQ18

M_CHB_DQ19

M_CHB_DQ24

M_CHB_DQ22

M_CHB_DQ25

M_CHB_DQ26

M_CHB_DQ10

M_CHB_DQ5

M_CHB_DQ7

M_CHB_DQ8

M_CHB_DQ6

M_CHB_DQ12

M_CHB_DQ9

M_CHB_DQ4

M_CHB_DQ3

M_CHB_DQ0

M_CHB_DQ2

M_CHB_DQ[0..63]12

M_CHB_DQ1

M_CHB_DQ31

M_CHB_DQ30

M_CHB_DQ28

M_CHB_DQ29

M_CHB_DQ34

M_CHB_DQ32

M_CHB_DQ35

M_CHB_DQ33

M_CHB_DQ36

M_CHB_DQ39

M_CHB_DQ37

M_CHB_DQ38

M_CHB_DQ40

M_CHB_DQ44

M_CHB_DQ43

M_CHB_DQ42

M_CHB_DQ41

M_CHB_DQ45

M_CHB_DQ46

M_CHB_DQ48

M_CHB_DQ47

M_CHB_DQ51

M_CHB_DQ52

M_CHB_DQ50

M_CHB_DQ49

M_CHB_DQ55

M_CHB_DQ56

M_CHB_DQ54

M_CHB_DQ53

M_CHB_DQ57

M_CHB_DQ59

M_CHB_DQ58

M_CHB_DQ60

M_CHB_DQ61

M_CHB_CKE0

M_CHB_DQ63

M_CHB_DQ62

M_CHB_CKE1

M_CHB_DM7

M_CHB_DM6

M_CHB_DM5

M_CHB_DM4

M_CHB_DM2

M_CHB_DM3

M_CHB_DM1

M_CHB_DM0

M_CHB_CKE[0..1]12,13

M_CHB_DM[0..7]12

P1V8STBY

R276

C331

0.1u/16V/4

80.6/4/1

A A

R271 80.6/4/1

SM_RCOMP_0

SM_RCOMP_1

R269 40.2/4/1

R272 40.2/4/1

SM_OCDCOMP_1

SM_OCDCOMP_0

P1V8STBY

R275 1K/4/1

R270

1K/4/1

PLACE CLOSE TO MCH

8

7

6

5

4

PLACE 0.1UF CAP CLOSE TO MCH

SM_VREF

C332

0.1u/16V/4

C329

0.1u/16V/4

MSI

Title

Size Document Number Rev

3

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

Intel Grantsdale - Memory Signals

Rickles

2

9 40Tuesday, February 24, 2004

X00

1

8

7

6

5

4

3

2

1

AB1

W18

VCC

VCC

VSSNCTF

VSSNCTF

AC25

AB25

V19

V17

VCC

VSSNCTF

AA25

AA11

U18

VCC

VCC

VSSNCTF

VSSNCTF

VSSNCTF

Y25

Y18

P1V8STBY

AR33

AR31

VCCSM

VSSNCTF

VSSNCTF

Y11

W25

W11

AR26

AR22

VCCSM

VCCSM

VCCSM

VSSNCTF

VSSNCTF

VSSNCTF

V25

V20

AR18

AR14

VCCSM

VCCSM

VSSNCTF

VSSNCTF

V16

V11

AP28

AR10

VCCSM

VCCSM

VSSNCTF

VSSNCTF

U25

U11

AP24

AP20

VCCSM

VSSNCTF

T25

T18

AP16

AP12

VCCSM

VCCSM

VCCSM

VSSNCTF

VSSNCTF

VSSNCTF

T11

R25

AN35

AM32

VCCSM

VSSNCTF

R11

P25

AM28

AM26

VCCSM

VCCSM

VCCSM

VSSNCTF

VSSNCTF

VSSNCTF

P11

N25

AM25

AM23

VCCSM

VCCSM

VSSNCTF

VSSNCTF

AD25

N11

AM22

AM20

VCCSM

VCCSM

VSSNCTF

VSSNCTF

M11

AA15

AM19

AM17

VCCSM

VCCSM

VSSNCTF

VSSNCTF

AA17

AA19

AM16

AM14

VCCSM

VCCSM

VSSNCTF

VSSNCTF

N17

N19

AM11

AM13

VCCSM

VCCSM

VSSNCTF

VSSNCTF

P16

P18

AM10

AK35

VCCSM

VCCSM

VSSNCTF

VSSNCTF

P20

R17

VCC3G

VSSNCTF

VSSNCTF

R19

R21

VCC3G

VCC3G

VSSNCTF

VSSNCTF

T22

U15

VCC3G

VCC3G

VSSNCTF

VSSNCTF

U21

U23

VCC3G

VCC3G

VSSNCTF

VSSNCTF

V22

W15

VCC3G

VCC3G

VSSNCTF

VSSNCTF

W21

W23

VCC3G

VCC3G

VSSNCTF

Y22

VCC3G

VCC3G

VCC3G

CRTDDCDATA

V_1P5_EXP

Y9Y8Y7Y6Y5Y4Y3Y2Y1W9W8W7W6W4W3W2W1

VCC3G

VCC3G

VCC3G

EXPATXP0

EXPATXN0

EXPATXP1

EXPATXN1

EXPATXP2

EXPATXN2

EXPATXP3

EXPATXN3

EXPATXP4

EXPATXN4

EXPATXP5

EXPATXN5

EXPATXP6

EXPATXN6

EXPATXP7

EXPATXN7

EXPATXP8

EXPATXN8

EXPATXP9

EXPATXN9

EXPATXP10

EXPATXN10

EXPATXP11

EXPATXN11

EXPATXP12

EXPATXN12

EXPATXP13

EXPATXN13

EXPATXP14

EXPATXN14

EXPATXP15

EXPATXN15

DMI TXP0

DMI TXN0

DMI TXP1

DMI TXN1

DMI TXP2

DMI TXN2

DMI TXP3

DMI TXN3

EXPACOMPO

EXPACOMPI

CRTHSYNC

CRTVSYNC

CRTRED

CRTGREEN

CRTBLUE

CRTREDB

CRTGREENB

CTRBLUEB

CRTDDCCLK

DREFCLKINP

DREFCLKINN

CRTIREF

PMEXTTS

PMBMBUSY#

TESTIN#

MCHDETECT

EXP_MCH_G_P0

C10

~EXP_MCH_G_P0

C9

EXP_MCH_G_P1

A9

~EXP_MCH_G_P1

A8

EXP_MCH_G_P2

C8

~EXP_MCH_G_P2

C7

EXP_MCH_G_P3

A7

~EXP_MCH_G_P3

A6

EXP_MCH_G_P4

C6

~EXP_MCH_G_P4

C5

EXP_MCH_G_P5

C2

~EXP_MCH_G_P5EXP_G_MCH_P7_C

D2

EXP_MCH_G_P6

E3

~EXP_MCH_G_P6EXP_G_MCH_P8_C

F3

EXP_MCH_G_P7

F1

~EXP_MCH_G_P7

G1

EXP_MCH_G_P8

G3

~EXP_MCH_G_P8

H3

EXP_MCH_G_P9

H1

~EXP_MCH_G_P9

J1

EXP_MCH_G_P10~EXP_G_MCH_P11_C

J3

~EXP_MCH_G_P10

K3

EXP_MCH_G_P11

K1

~EXP_MCH_G_P11

L1

EXP_MCH_G_P12

L3

~EXP_MCH_G_P12

M3

EXP_MCH_G_P13

M1

~EXP_MCH_G_P13

N1

EXP_MCH_G_P14

N3

~EXP_MCH_G_P14

P3

EXP_MCH_G_P15

P1

~EXP_MCH_G_P15

R1

DMI_MCH_ICH_P0

R3

~DMI_MCH_ICH_P0

T3

DMI_MCH_ICH_P1

T1

~DMI_MCH_ICH_P1

U1

DMI_MCH_ICH_P2

U3

~DMI_MCH_ICH_P2

V3

DMI_MCH_ICH_P3

V5

~DMI_MCH_ICH_P3

W5

Y10

W10

GRP_HSYNC_3V_R

E12

GRP_VSYNC_3V_R

D12

GRP_RED

F14

GRP_GREEN

D14

GRP_BLUE

H14

G14

E14

J14

GRP_DDC_DATA_3V

L14

GRP_DDC_CLK_3V

M15

CK_96M_DOT

M13

~CK_96M_DOT

M12

MCH_REFSET

A15

~EXTTS

K16

G16

R35

A35

R248 24.9/4/1

EXP_RCOMP

R215 255/6/1

R216 8.2K/4

EXP_RCOMP

EXP_MCH_G_P0 14

~EXP_MCH_G_P0 14

EXP_MCH_G_P1 14

~EXP_MCH_G_P1 14

EXP_MCH_G_P2 14

~EXP_MCH_G_P2 14

EXP_MCH_G_P3 14

~EXP_MCH_G_P3 14

EXP_MCH_G_P4 14

~EXP_MCH_G_P4 14

EXP_MCH_G_P5 14

~EXP_MCH_G_P5 14

EXP_MCH_G_P6 14

~EXP_MCH_G_P6 14

EXP_MCH_G_P7 14

~EXP_MCH_G_P7 14

EXP_MCH_G_P8 14

~EXP_MCH_G_P8 14

EXP_MCH_G_P9 14

~EXP_MCH_G_P9 14

EXP_MCH_G_P10 14

~EXP_MCH_G_P10 14

EXP_MCH_G_P11 14

~EXP_MCH_G_P11 14

EXP_MCH_G_P12 14

~EXP_MCH_G_P12 14

EXP_MCH_G_P13 14

~EXP_MCH_G_P13 14

EXP_MCH_G_P14 14

~EXP_MCH_G_P14 14

EXP_MCH_G_P15 14

~EXP_MCH_G_P15 14

DMI_MCH_ICH_P0 16

~DMI_MCH_ICH_P0 16

DMI_MCH_ICH_P1 16

~DMI_MCH_ICH_P1 16

DMI_MCH_ICH_P2 16

~DMI_MCH_ICH_P2 16

DMI_MCH_ICH_P3 16

~DMI_MCH_ICH_P3 16

GRP_HSYNC_3V_R 27

GRP_VSYNC_3V_R 27

GRP_RED 27

GRP_GREEN 27

GRP_BLUE 27

GRP_DDC_DATA_3V 27

GRP_DDC_CLK_3V 27

CK_96M_DOT 15

~CK_96M_DOT 15

V_2P5_DAC

P1V8STBY

C339 2.2u/16V/8

C346 2.2u/16V/8

C347 2.2u/16V/8

C348 2.2u/16V/8

C349 2.2u/16V/8

C350 2.2u/16V/8

V_CPU_VTT

HS1

HK1*3(-2)

1

2

BSEL

2

0

1

0

0

0

0

0

1

0

1

0

+1_5V

C325

C324

C262

10u/10V/8

C271

10u/10V/8

Place close to GMCH

HS2

HK1*3(-2)

1

2

~GPI_HS_DET 16

TABLE

PSB FREQUENCY

RESERVED

133 MHZ (533)

200 MHZ (800)

12

+

C321

470u/10V/8*11.5

C280

10u/10V/8

10u/10V/8

10u/10V/8

+1_5V

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AC10

AC9

AC8

AC7

AC2

AC6

AC5

AC4

AD10

C241

U17C

E11

F11

J11

H11

F9

E9

F7

E7

B3

B4

D5

E5

G6

G5

H8

H7

J6

J5

K8

K7

L6

L5

P10

R10

M8

M7

N6

N5

P7

P8

R6

R5

U5

U6

T9

T8

V7

V8

V10

U10

A11

B11

K13

J13

H16

E15

D17

M16

F15

C15

A16

B15

C14

K15

L10

M10

A17

B17

A12

B13

A14

A13

E13

D13

F13

Grantsdale-G

EXPARXP0

EXPARXN0

EXPARXP1

EXPARXN1

EXPARXP2

EXPARXN2

EXPARXP3

EXPARXN3

EXPARXP4

EXPARXN4

EXPARXP5

EXPARXN5

EXPARXP6

EXPARXN6

EXPARXP7

EXPARXN7

EXPARXP8

EXPARXN8

EXPARXP9

EXPARXN9

EXPARXP10

EXPARXN10

EXPARXP11

EXPARXN11

EXPARXP12

EXPARXN12

EXPARXP13

EXPARXN13

EXPARXP14

EXPARXN14

EXPARXP15

EXPARXN15

DMI RXP0

DMI RXN0

DMI RXP1

DMI RXN1

DMI RXP2

DMI RXN2

DMI RXP3

DMI RXN3

GCLKINP

GCLKINN

SDVOCTRLDATA

SDVOCTRLCLK

BSEL0

BSEL1

BSEL2

RSV

RSV

MTYPE

EXP_SLR

RSV

RSV

RSV

VCC

VSS

VCCAHPLL

VCCAMPLL

VCCADPLLA

VCCADPLLB

VCCA3GPLL

VCCHV

VCCACRTDAC

VCCACRTDAC

VSSACRTDAC

V_CPU_VTT

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

G22

H22

G21

F22

F21

F20

E22

E21

E20

SDVO_DATA14

SDVO_CLK14

+

H_BSEL05,6,15

H_BSEL15,6,15

H_BSEL25,6,15

C242

0.1u/16V/4

EXP_G_MCH_P0_C

~EXP_G_MCH_P0_C

EXP_G_MCH_P1_C

~EXP_G_MCH_P1_C

EXP_G_MCH_P2_C

~EXP_G_MCH_P2_C

EXP_G_MCH_P3_C

~EXP_G_MCH_P3_C

EXP_G_MCH_P4_C

~EXP_G_MCH_P4_C

EXP_G_MCH_P5_C

~EXP_G_MCH_P5_C

EXP_G_MCH_P6_C

~EXP_G_MCH_P6_C

~EXP_G_MCH_P7_C

~EXP_G_MCH_P8_C

EXP_G_MCH_P9_C

~EXP_G_MCH_P9_C

EXP_G_MCH_P10_C

~EXP_G_MCH_P10_C

EXP_G_MCH_P11_C

EXP_G_MCH_P12_C

~EXP_G_MCH_P12_C

EXP_G_MCH_P13_C

~EXP_G_MCH_P13_C

EXP_G_MCH_P14_C

~EXP_G_MCH_P14_C

EXP_G_MCH_P15_C

~EXP_G_MCH_P15_C

DMI_ICH_MCH_P0

~DMI_ICH_MCH_P0

DMI_ICH_MCH_P1

~DMI_ICH_MCH_P1

DMI_ICH_MCH_P2

~DMI_ICH_MCH_P2

DMI_ICH_MCH_P3

~DMI_ICH_MCH_P3

EXP_CK_100M_MCH

~EXP_CK_100M_MCH

V_2P5_DAC

SDVO_DATA

SDVO_CLK

MTYPE

EXP_SLR

+1_5V

V_1P5_HPLL

V_1P5_MPLL

V_1P5_DPLL_A

V_1P5_DPLL_B

V_1P5_EXPPLL

V_2P5_DAC_F

0.01u/16V/4

EXP_G_MCH_P0_C14

~EXP_G_MCH_P0_C14

EXP_G_MCH_P1_C14

D D

C C

B B

V_2P5_DAC

~EXP_G_MCH_P1_C14

~EXP_G_MCH_P2_C14

~EXP_G_MCH_P3_C14

~EXP_G_MCH_P4_C14

~EXP_G_MCH_P5_C14

~EXP_G_MCH_P6_C14

~EXP_G_MCH_P7_C14

~EXP_G_MCH_P8_C14

~EXP_G_MCH_P9_C14

~EXP_G_MCH_P10_C14

~EXP_G_MCH_P11_C14

~EXP_G_MCH_P12_C14

~EXP_G_MCH_P13_C14

~EXP_G_MCH_P14_C14

~EXP_G_MCH_P15_C14

~DMI_ICH_MCH_P016

~DMI_ICH_MCH_P116

~DMI_ICH_MCH_P216

~DMI_ICH_MCH_P316

~EXP_CK_100M_MCH15

R1354 X_1K/4

I=70mA

FB180/6/1.5A

220u/10V/6.3*7

EXP_G_MCH_P2_C14

EXP_G_MCH_P3_C14

EXP_G_MCH_P4_C14

EXP_G_MCH_P5_C14

EXP_G_MCH_P6_C14

EXP_G_MCH_P7_C14

EXP_G_MCH_P8_C14

EXP_G_MCH_P9_C14

EXP_G_MCH_P10_C14

EXP_G_MCH_P11_C14

EXP_G_MCH_P12_C14

EXP_G_MCH_P13_C14

EXP_G_MCH_P14_C14

EXP_G_MCH_P15_C14

DMI_ICH_MCH_P016

DMI_ICH_MCH_P116

DMI_ICH_MCH_P216

DMI_ICH_MCH_P316

EXP_CK_100M_MCH15

R212 2K/4

C1520 X_0.1u/16V/4

L39

C222

AC3

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

C22

E19

D22

D21

D20

D19

C21

C20

C19

AB4

AB9

AB8

AB7

AB6

AB5

AB3

AC1

AB10

VCC

VCC

VTT

VTT

B21

B22

AB2

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VCC

VTT

VTT

VTT

VTT

VTT

VTT

B20

B19

A22

A21

A20

A19

+1_5V

+1_5V

A A

8

L34 10uH/8

L35 10uH/8

V_1P5_HPLL

+

C223

470u/10V/6.3*11

+

C224

470u/10V/6.3*11

7

I=45mA

0.1u/16V/4

I=60mA

C252

0.1u/16V/4

+1_5V

+1_5V

6

L36 10uH/8

L37 10uH/8

5

V_1P5_DPLL_A

+

C220

220u/10V/6.3*7

V_1P5_DPLL_B

+

C221

220u/10V/6.3*7

I=55mA

C272

0.1u/16V/4

I=55mA

C273

0.1u/16V/4

+1_5V

4

+1_5V

L38 1uH/8/0.5A

L40 0.15uH/1210/1.45A

+

V_1P5_EXPPLL V_1P5_EXPPLLV_1P5_MPLL

ANALOG FILTERS

3

C308

220u/10V/6.3*7

V_1P5_EXP

R211 1/4/1

R1355 1/4/1

C315

C316 10u/10V/8C251

C240

10u/10V/8

10u/10V/8

C1681

0.1u/16V/4

I=45mA

C270

0.1u/16V/4

MICRO-STAR INt'L CO., LTD.

MSI

Title

Intel Grantsdale PCI-Express & RBG Signals

Size Document Number Rev

Date: Sheet of

2

Rickles

10 40Tuesday, February 24, 2004

1

X00

8

7

6

5

4

3

2

1

D D

A10

A18

A26

A30

A33

B10

B12

B14

B16

B18

B24

B28

C C

B B

C11

C13

C17

C18

C23

C35

D10

D11

D15

D16

D18

D23

D25

D26

D28

D30

D31

D32

E10

E17

E18

E23

E26

E29

F10

F16

F18

F23

F25

F29

F30

F32

F35

AR25

AR30

U17D

VSS

VSS

A3

VSS

A5

VSS

VSS

VSS

VSS

VSS

VSS

B2

VSS

B5

VSS

B6

VSS

B7

VSS

B8

VSS

B9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C1

VSS

C3

VSS

C4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D3

VSS

D4

VSS

D6

VSS

D7

VSS

D8

VSS

D9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E1

VSS

E2

VSS

E4

VSS

E6

VSS

E8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F2

VSS

F4

VSS

F5

VSS

F6

VSS

F8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

G2G4G7

AR21

VSS

VSS

AR17

VSS

VSS

AR13

VSS

VSS

AR6

G10G9G8

VSS

VSS

AR3

G11

VSS

VSS

AP8

G13

VSS

VSS

AN1

VSS

VSS

G15

AM31

VSS

VSS

G17

AM29

VSS

VSS

G19

AM8

G20

VSS

VSS

AM7

G23

VSS

VSS

AM6

G26

VSS

VSS

AM4

G27

VSS

VSS

AL32

VSS

VSS

AL22

VSS

VSS

AL19

VSS

VSS

AL16

VSS

VSS

AL13

VSS

VSS

AL10

VSS

VSS

AK30

H10H9H6H5H4H2G28

VSS

VSS

AK28

VSS

VSS

H13

AK26

H21

VSS

VSS

AK25

VSS

VSS

H24

AK23

H25

VSS

VSS

AK20

H27

VSS

VSS

AK17

H30

VSS

VSS

AK14

H32

VSS

VSS

AK11

VSS

VSS

AK8

VSS

VSS

AK7

VSS

VSS

AK6

VSS

VSS

AK4

VSS

VSS

AK1

VSS

VSS

AJ35

J10J9J8J7J4J2H34

VSS

VSS

AJ32

VSS

VSS

J15

AJ30

J16

VSS

VSS

AJ27

J17

VSS

VSS

AJ22

J18

VSS

VSS

AJ19

J20

VSS

VSS

AJ16

J23

VSS

VSS

AJ15

VSS

VSS

AJ13

VSS

VSS

AJ10

VSS

VSS

AH26

AH29

AH32

AH34

AJ4

AJ9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K11

K10K9K6K5K4K2J30

K14

AH23

K20

VSS

VSS

AH20

K24

VSS

VSS

AH17

VSS

VSS

K26

AH14

K28

VSS

VSS

AH11

VSS

VSS

K31

AH8

K32

VSS

VSS

AH6

VSS

VSS

AH5

VSS

VSS

AH1

VSS

VSS

AG29

VSS

VSS

AG28

VSS

VSS

L8L7L4L2K35

AG25

VSS

VSS

L9

AG22

VSS

VSS

L11

AG21

VSS

VSS

L13

AG19

VSS

VSS

L15

AG18

VSS

VSS

L16

AG16

VSS

VSS

L17

AG15

VSS

VSS

L18

AG13

VSS

VSS

L20

AG12

VSS

VSS

L21

AG5

VSS

VSS

L22

AF30

AF31

AF32

AF35

VSS

VSS

VSS

VSS

VSS

VSS

L24

L27

L30

L32M2M4M5M6M9M17

VSS

VSS

AF29

VSS

VSS

AF26

VSS

VSS

AF21

VSS

VSS

AF18

VSS

VSS

AF15

VSS

VSS

AF12

VSS

VSS

AF10

VSS

VSS

M20

AF8

M24

VSS

VSS

AF6

M25

VSS

VSS

AF4

VSS

VSS

M27

AE24

AE28

AE30

AE32

AF1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

M29

M34N2N4N7N8N9N10

AE23

VSS

VSS

AE21

VSS

VSS

AE20

VSS

VSS

AE18

VSS

VSS

N28

AE17

VSS

VSS

N30

AE9

AE12

AE14

AE15

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N32P2P4P5P6P9P27

AE6

VSS

VSS

AE4

VSS

VSS

AD34

VSS

VSS

AD27

P29

VSS

VSS

AD26

VSS

VSS

P31

AD19

AD22

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Grantsdale-G

AD16

AD13

AD11

AC32

AC31

AC29

AC27

AB35

AB32

AB30

AB28

AA27

AA26

AA10

AA9

AA8

AA7

AA6

AA5

AA4

AA3

AA2

AA1

Y34

Y32

Y31

Y29

Y27

W32

W30

W28

W19

W17

V35

V27

V26

V18

V9

V6

V4

V2

V1

U32

U31

U29

U27

U19

U17

U9

U8

U7

U4

U2

T34

T32

T30

T28

T10

T7

T6

T5

T4

T2

R27

R26

R9

R8

R7

R4

R2

P35

P32

A A

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet of

MICRO-STAR INt'L CO., LTD.

Intel Grantsdale - GND

Rickles

2

11 40Tuesday, February 24, 2004

X00

1

5

M_CHA_DQ[0..63]9

D D

C C

B B

M_CHA_DQ0

M_CHA_DQ1

M_CHA_DQ2

M_CHA_DQ3

M_CHA_DQ4

M_CHA_DQ5

M_CHA_DQ6

M_CHA_DQ7

M_CHA_DQ8

M_CHA_DQ9

M_CHA_DQ10

M_CHA_DQ11

M_CHA_DQ12

M_CHA_DQ13

M_CHA_DQ14

M_CHA_DQ15

M_CHA_DQ16

M_CHA_DQ17

M_CHA_DQ18

M_CHA_DQ19

M_CHA_DQ20

M_CHA_DQ21

M_CHA_DQ22

M_CHA_DQ23

M_CHA_DQ24

M_CHA_DQ25

M_CHA_DQ26

M_CHA_DQ27

M_CHA_DQ28

M_CHA_DQ29

M_CHA_DQ30

M_CHA_DQ31

M_CHA_DQ32

M_CHA_DQ33

M_CHA_DQ34

M_CHA_DQ35

M_CHA_DQ36

M_CHA_DQ37

M_CHA_DQ38

M_CHA_DQ39

M_CHA_DQ40

M_CHA_DQ41

M_CHA_DQ42

M_CHA_DQ43

M_CHA_DQ44

M_CHA_DQ45

M_CHA_DQ46

M_CHA_DQ47

M_CHA_DQ48

M_CHA_DQ49

M_CHA_DQ50

M_CHA_DQ51

M_CHA_DQ52

M_CHA_DQ53

M_CHA_DQ54

M_CHA_DQ55

M_CHA_DQ56

M_CHA_DQ57

M_CHA_DQ58

M_CHA_DQ59

M_CHA_DQ60

M_CHA_DQ61

M_CHA_DQ62

M_CHA_DQ63

DIMM_1

3

4

9

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

102195156627278

18

55

NC

RC1

RC0

NC/TEST

VSS

VSS

VSS

VSS

100

103

106

109

68

112

191

194

181

175

170535964197

VDD7

VSS

172

69

VDD8

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

145

148

151

154

157

160

163

166

75

NC

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

115

VSS

118

121

124

127

130

133

136

139

142