5

4

3

2

1

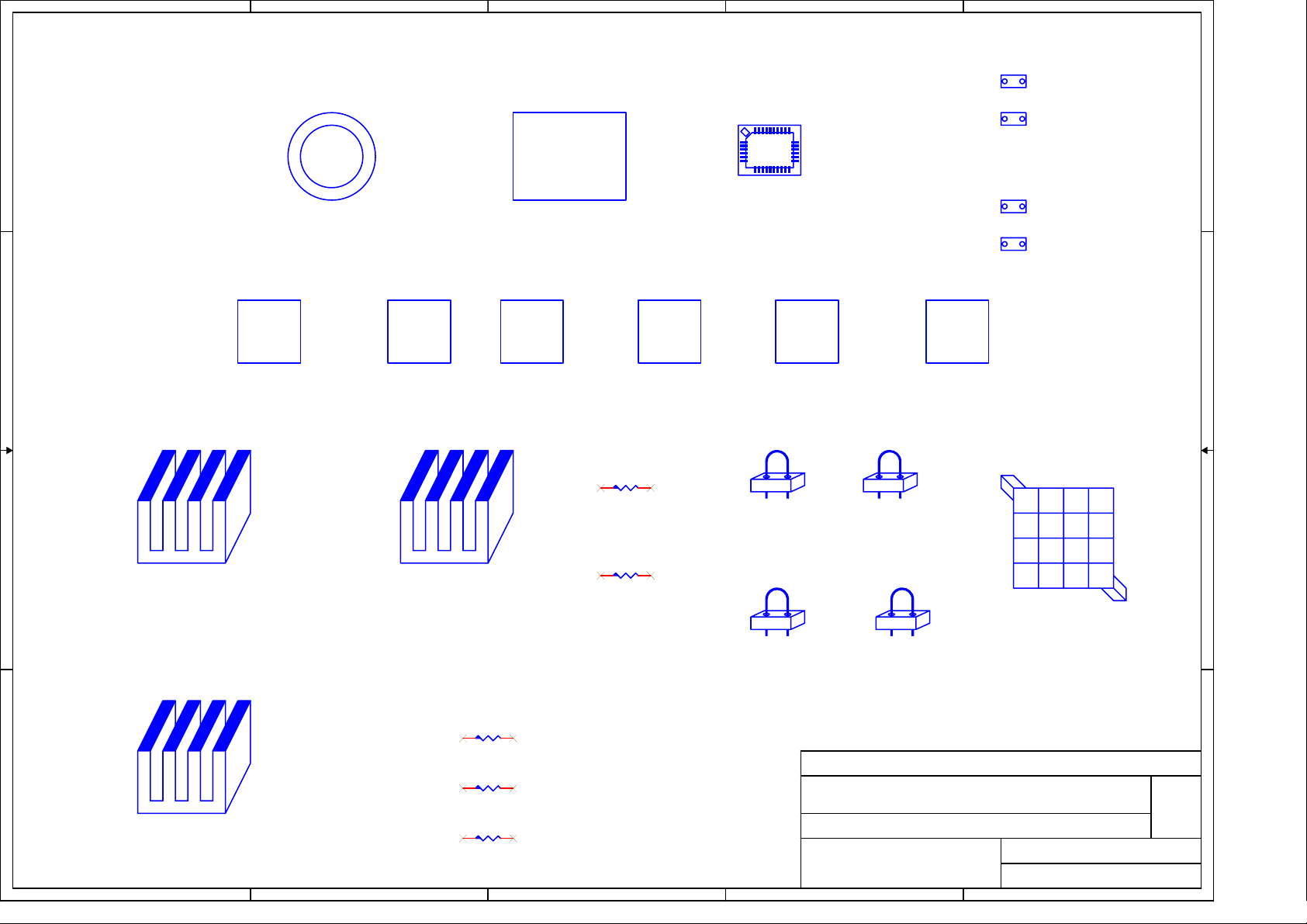

Title

Cover Sheet

D D

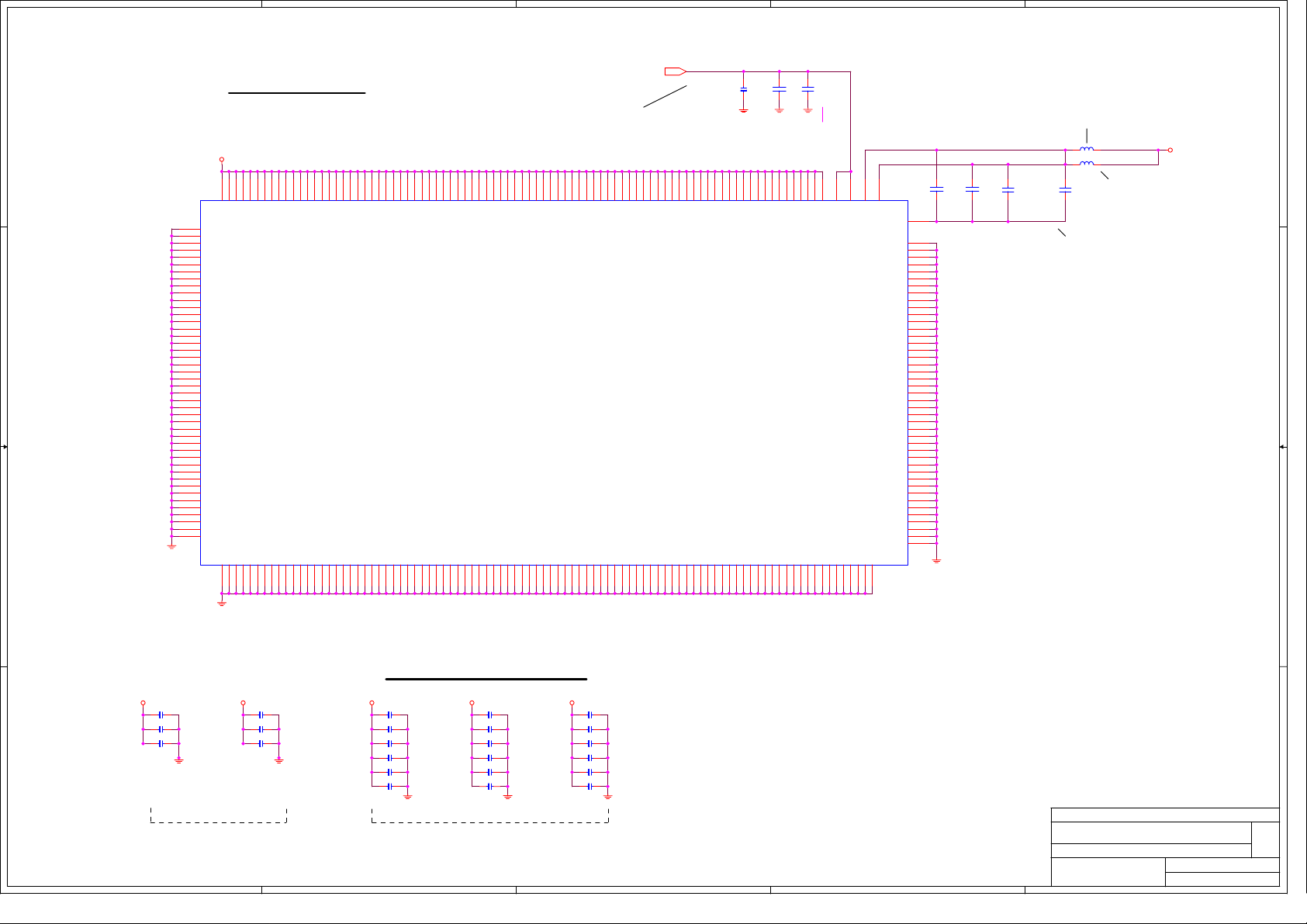

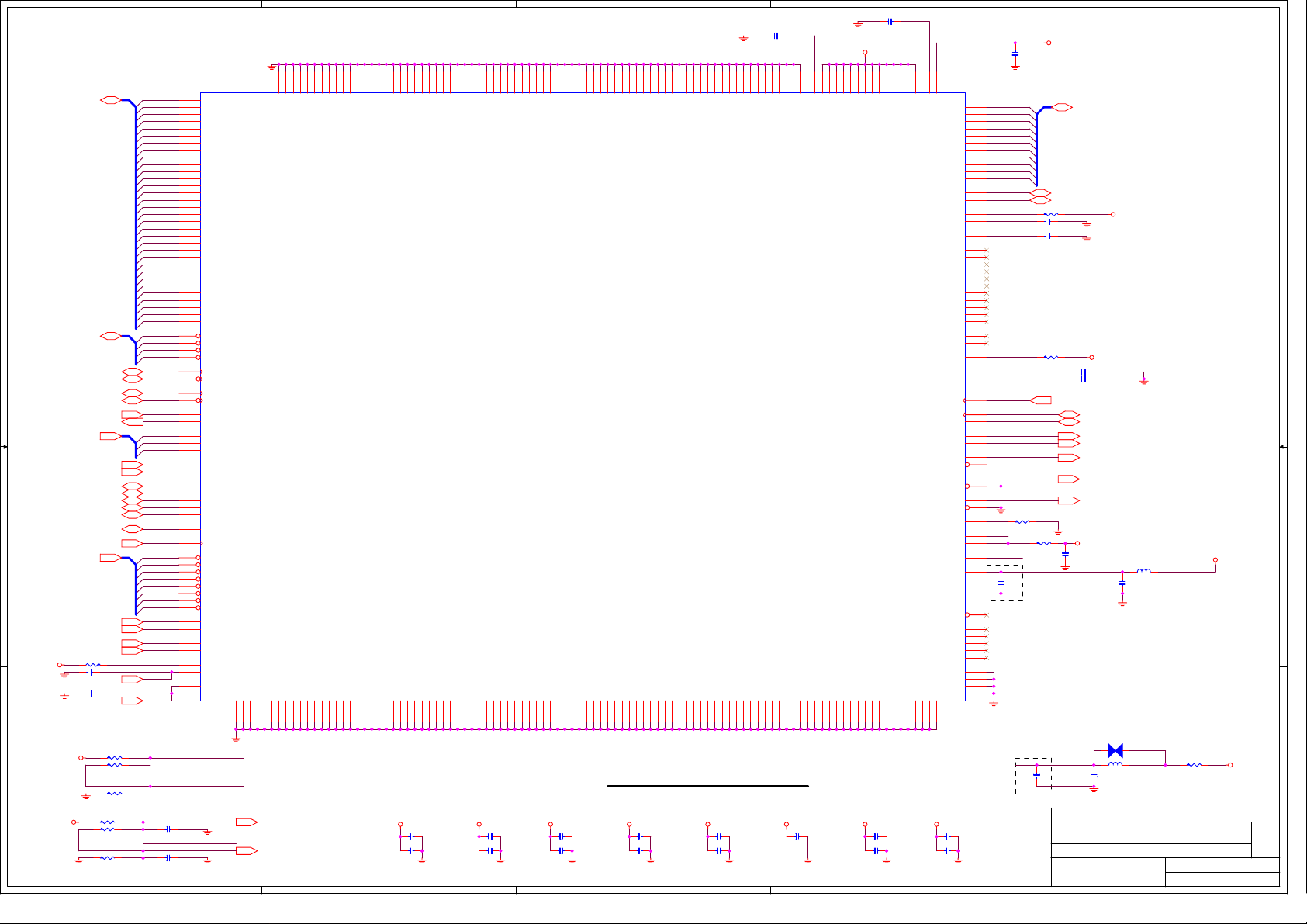

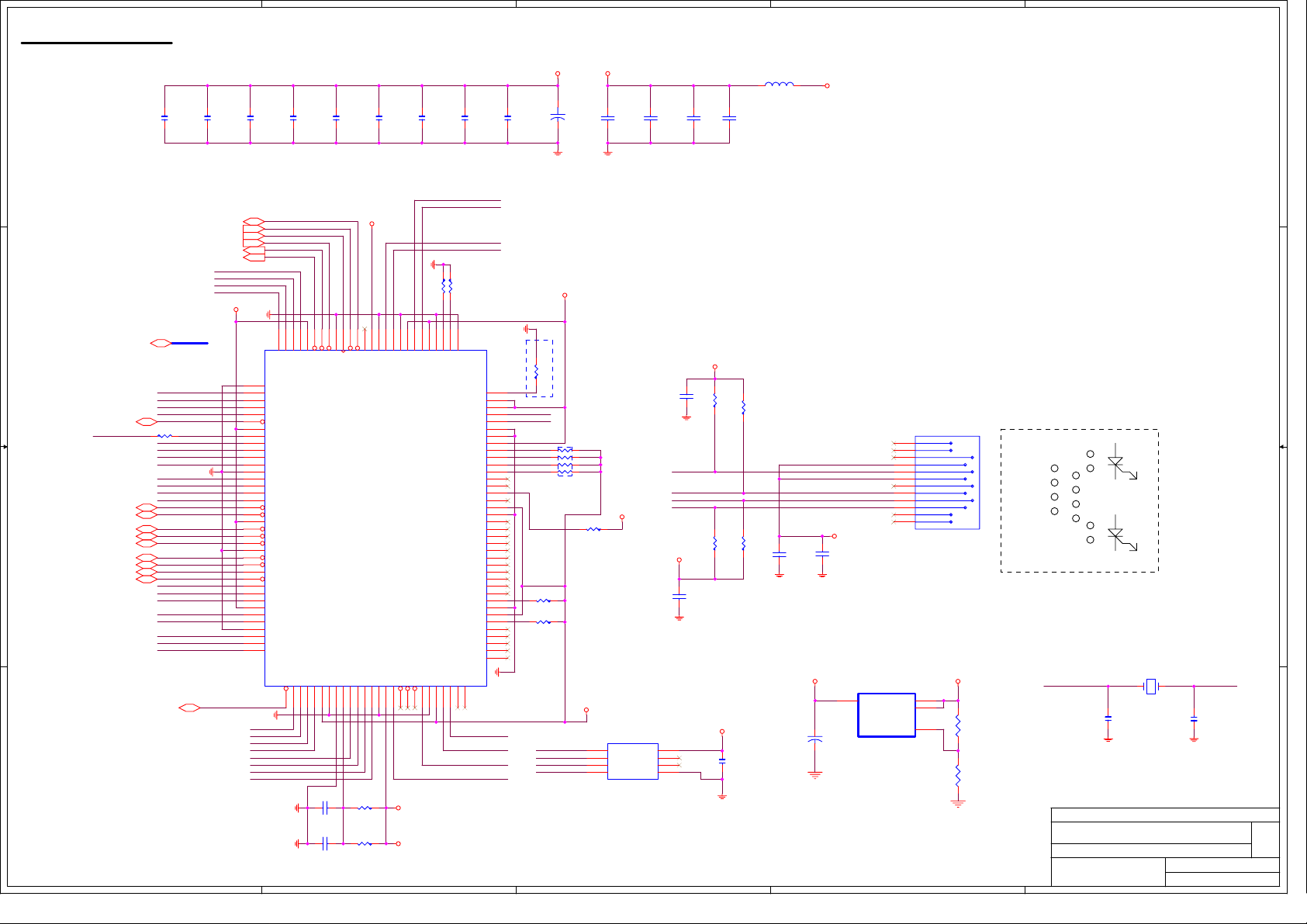

MS-7041 uATX

Block Diagram

GPIO SPEC

*INTEL mPGA 478B Processor

*INTEL Springdale GMCH / ICH5 Chipset

(DDR 400 / AGP 8X) / (integrated serial ATA)

*VIA/6105L

*VIA/6306,IEEE1394 3port

*Winbond 83627HF LPC I/O

*Audio codec 6 channel support

*USB 2.0 support x6 (integrated into ICH5)

C C

Intel mPGA478B

Clock Synthesizer

Intel Springdale

System Memory

/ DDR Terminations

AGP SLOT

ICH5

Mini PCI Audio conn.

PCI Slot / MS-1

VIA 1394(6306)

Lan VIA 6105L

Audio Codec / 6 Channel connector

Intel IDE connector

MS-5 ACPI Controller

VRM 10.0

Page

1

2

3

4,5

6

7,8,9

10,11

12

13,14

15

16

17

18

19

20

21

22

23VGA CONNECTOR

USB CONNECTOR

W627THF LPC I/O / FWH

B B

KB/MS/LPT/COM Port/FAN

ATX connector / Front Panel

Manual Part

HISTORY

24

25

26

27

28

29

A A

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

Cover Sheet

MS-7041

1

Last Revision Date:

Thursday, December 04, 2003

Sheet

Rev

100

129

of

5

4

3

2

1

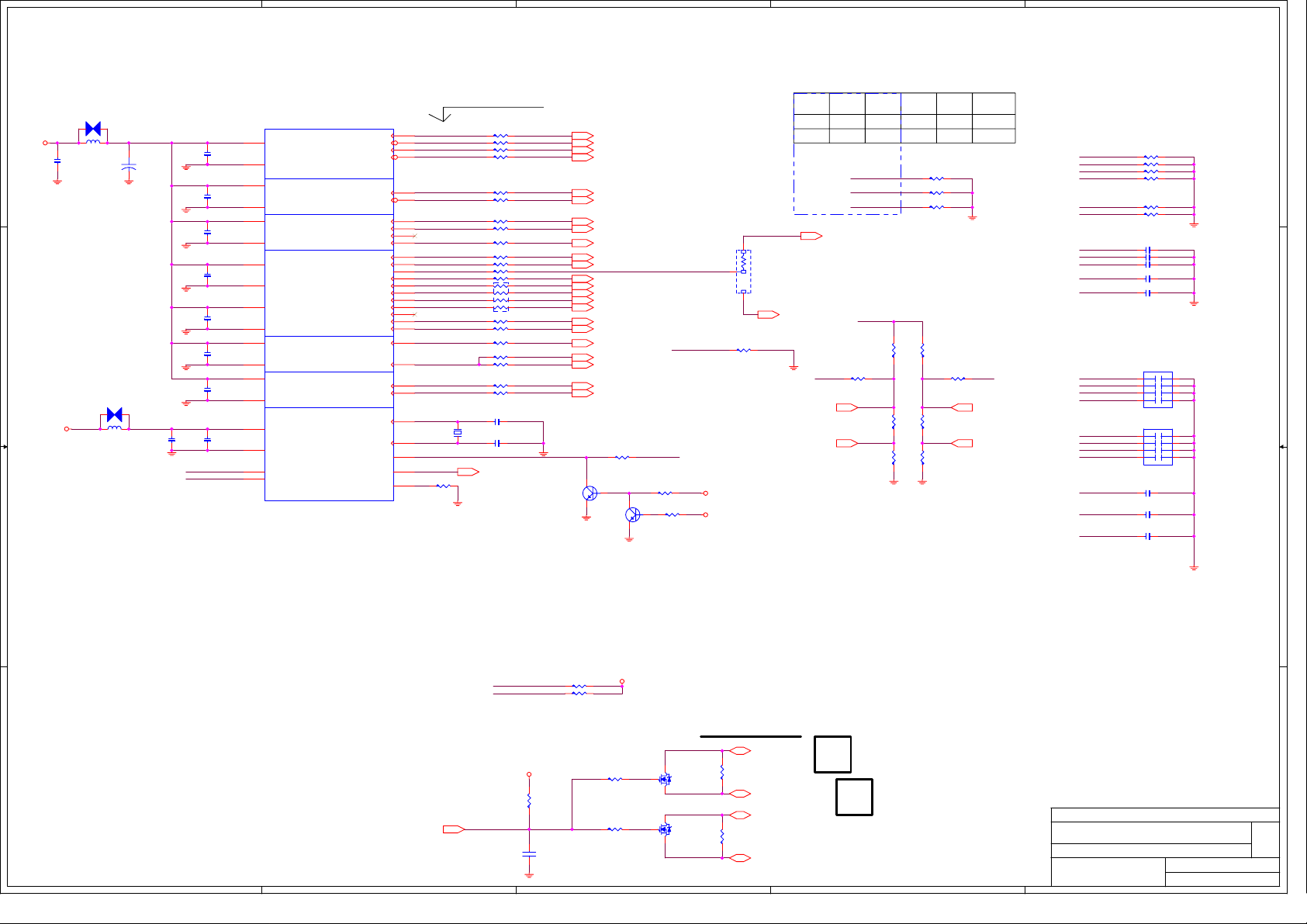

Block Diagram

+5V : VCC5

+3.3V : VCC3

+12V : +12V

5VSB : VCC5_SB

D D

-12V : -12V

+2.55V for DDR : VCC_DDR

1.275V for DDR VTT : VTT_DDR

POWER DELIVERY MAP

Dual 3.3V : 3VDUAL

1.2V for CPU VID : VCC_VID

1.5V for AGP VI/O : VCC_AGP

Dual 5V : 5VDUAL

CPU Vcore : VCCP

+5V for analog CODEC : AVDD5

2.5V for LAN : 2_5VSB

+12V for 1394 bus power : CPWR

C C

A

G

P

AGP 8X/4X

(1.5V)

VGA CONN

B B

1394

Controller

VIA

1394

6306

USB 2.0

Rear x4

Front X4

A A

IDE CONN 1&2

USB Port 0:1

USB Front Panel

USB Port 6:7

USB Front Panel

USB Port 2:3

USB Front Panel

USB Port 4:5

USB Front Panel

AGP 8X /Fast Write

VIA

Lan

6105L

ATA33/ATA66/ATA100

Dual USB 1.1 OHCI

/2.0 EHCI 6 Ports

PS2 Mouse &

Keyboard

5 PCI Slots

Intel mPGA478B

FSB 400/533/800

Springdale

PCI-33

Winbond

LPC I/O

83627THF

Parallel (1)

Serial (1)

LPC Bus

SUPER I/O

Controller HUB

Floppy Disk

Drive

HUB Interface

ICH5

(33MHz)

(200/266/333/400 MHz)

(200/266/333/400 MHz)

LPC BUS

FWH: Firmware HUB

DDR DIMM1,2

2 channel DDR 333

DDR DIMM3,4

Serial ATA

Dual ATA 33/66/100

AC Link

AC97 Codec

6 CHANNEL

+ SPDIF

SATA Con x2

3.3V 5V 5VSB 12V

1.2V VREG

1.5V VREG

3VSB VREG

DDR 2.5V

VREG

VRM

2.5V VREG

Lan 2.5VSB

VREG

AC97 VDD5

VREG

VTT 1.25V

VREG

PROCESSOR VCCP

PROCESSOR 1.2V

AGP SLOT 1.5V

NORTH BRIDGE VCCP

NORTH BRIDGE VCC_AGP

NORTH BRIDGE SYSEM MEMORY

VCC_DDR

DDR DIMM1 / DIMM2 2.5V

DDR VTT 1.25V

SORTH BRIDGE +1.5V

SORTH BRIDGE VCC3

SORTH BRIDGE RESUME VCC5_SB

SORTH BRIDGE RESUME VCC3_SB

SORTH BRIDGE RTC 3.3V

LAN

VT6150 VCC3_SB

VT6150 2.5VSB

FWH 3.3V

LPC SUPER I/O 3.3V

LPC SUPER I/O VCC5

CK-409 3.3V

AC97 VDD5

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

Block Diagram

MS-7041

1

Last Revision Date:

Sheet

Rev

100

Thursday, December 04, 2003

29

2

of

5

4

3

2

1

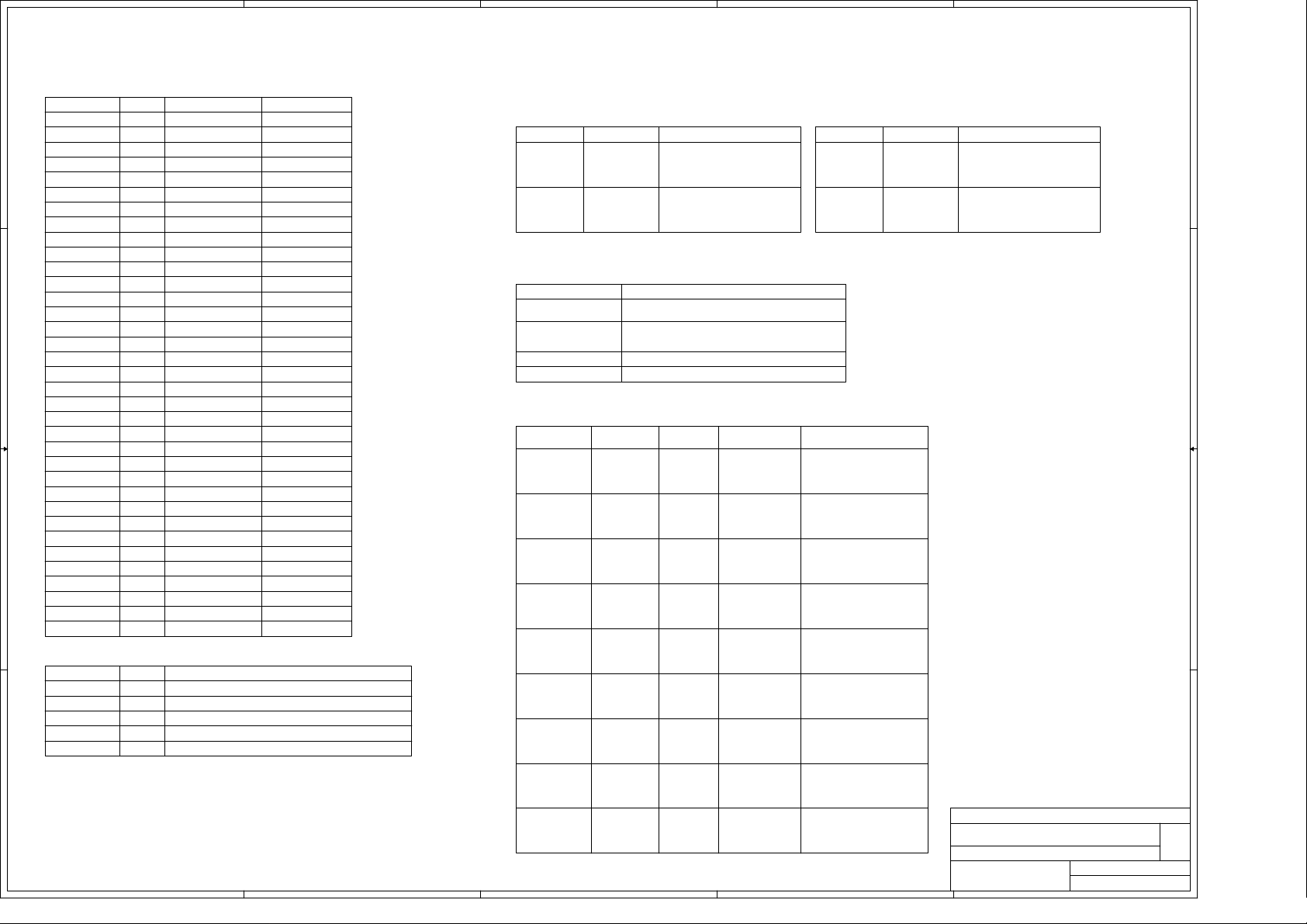

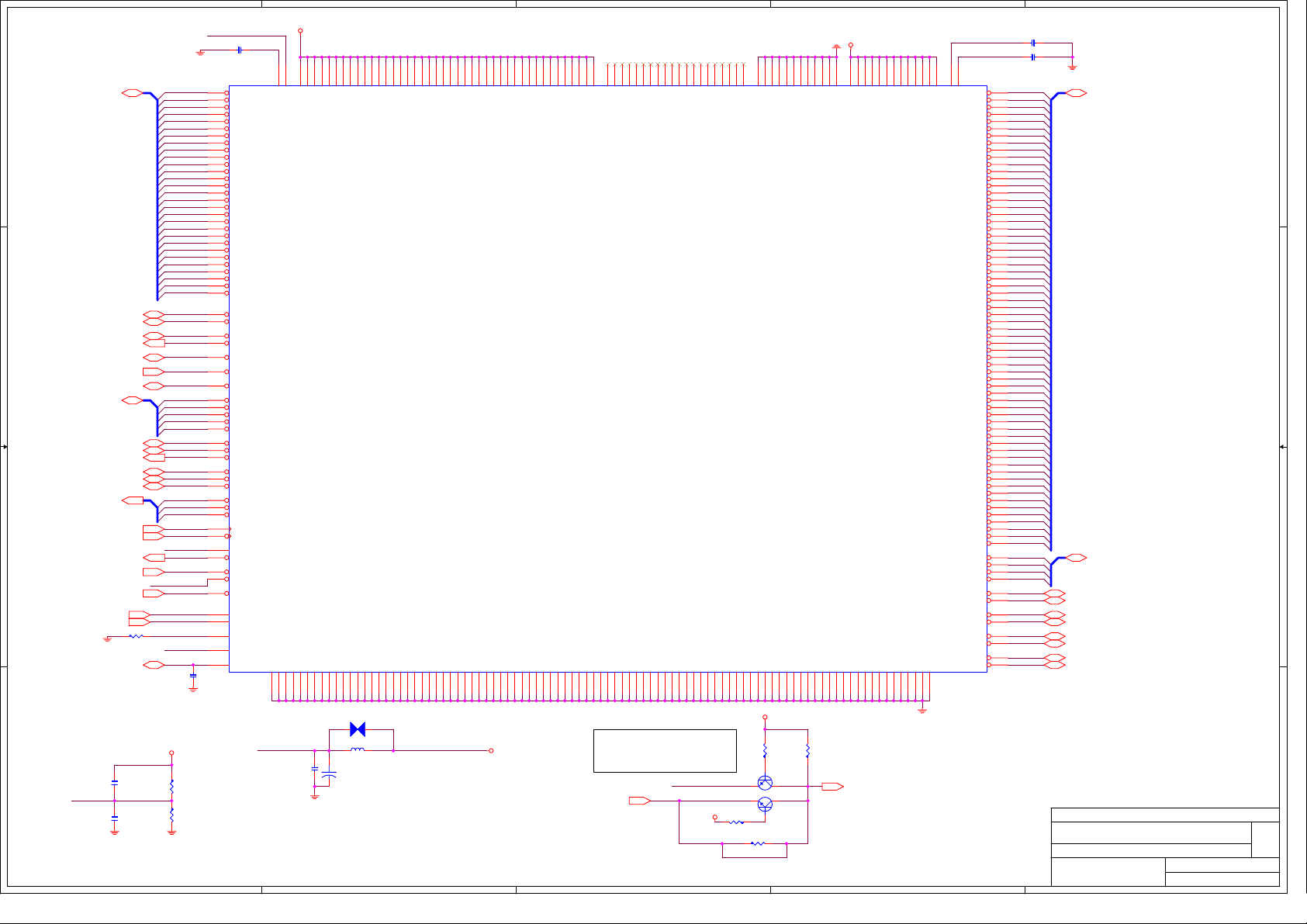

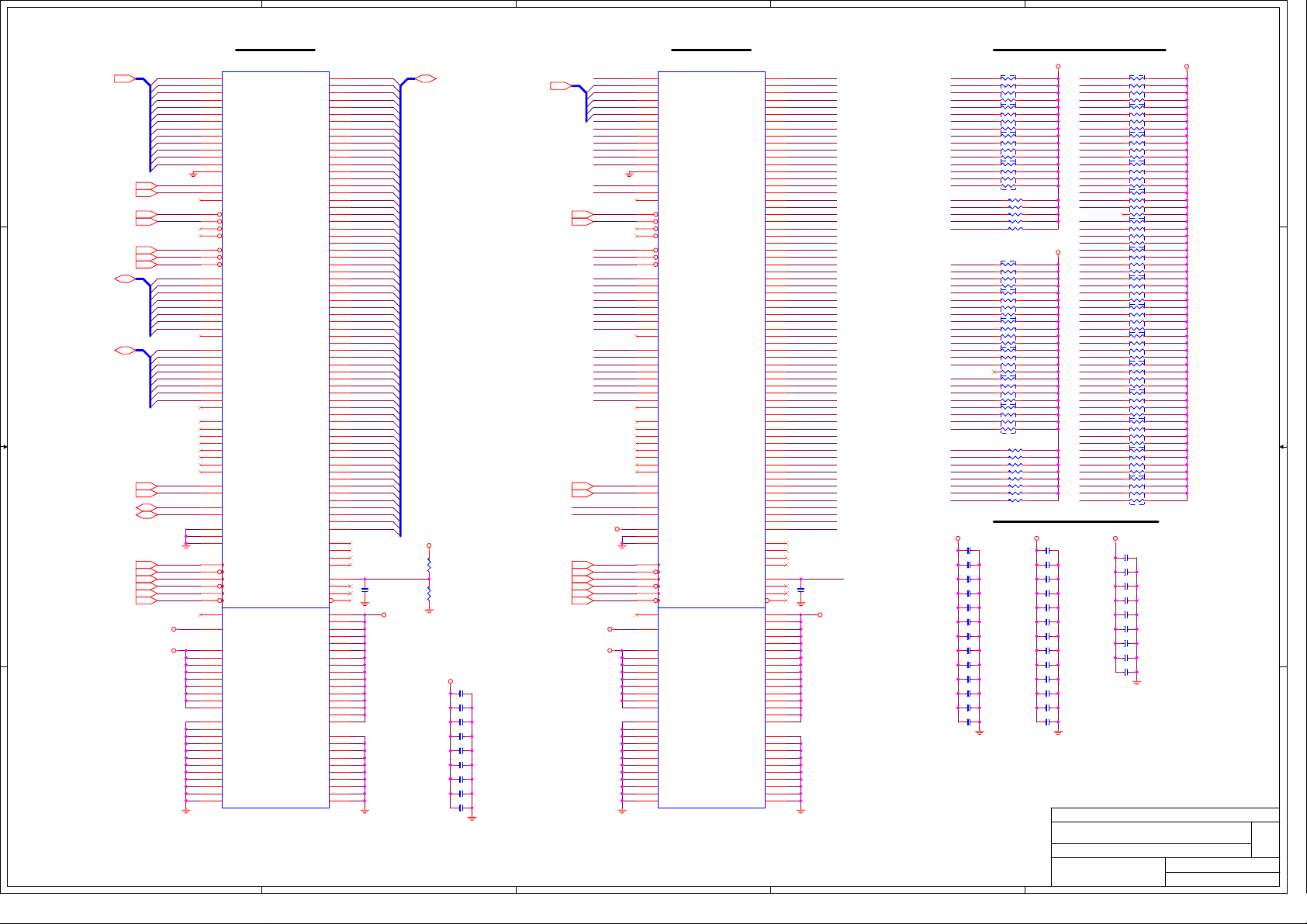

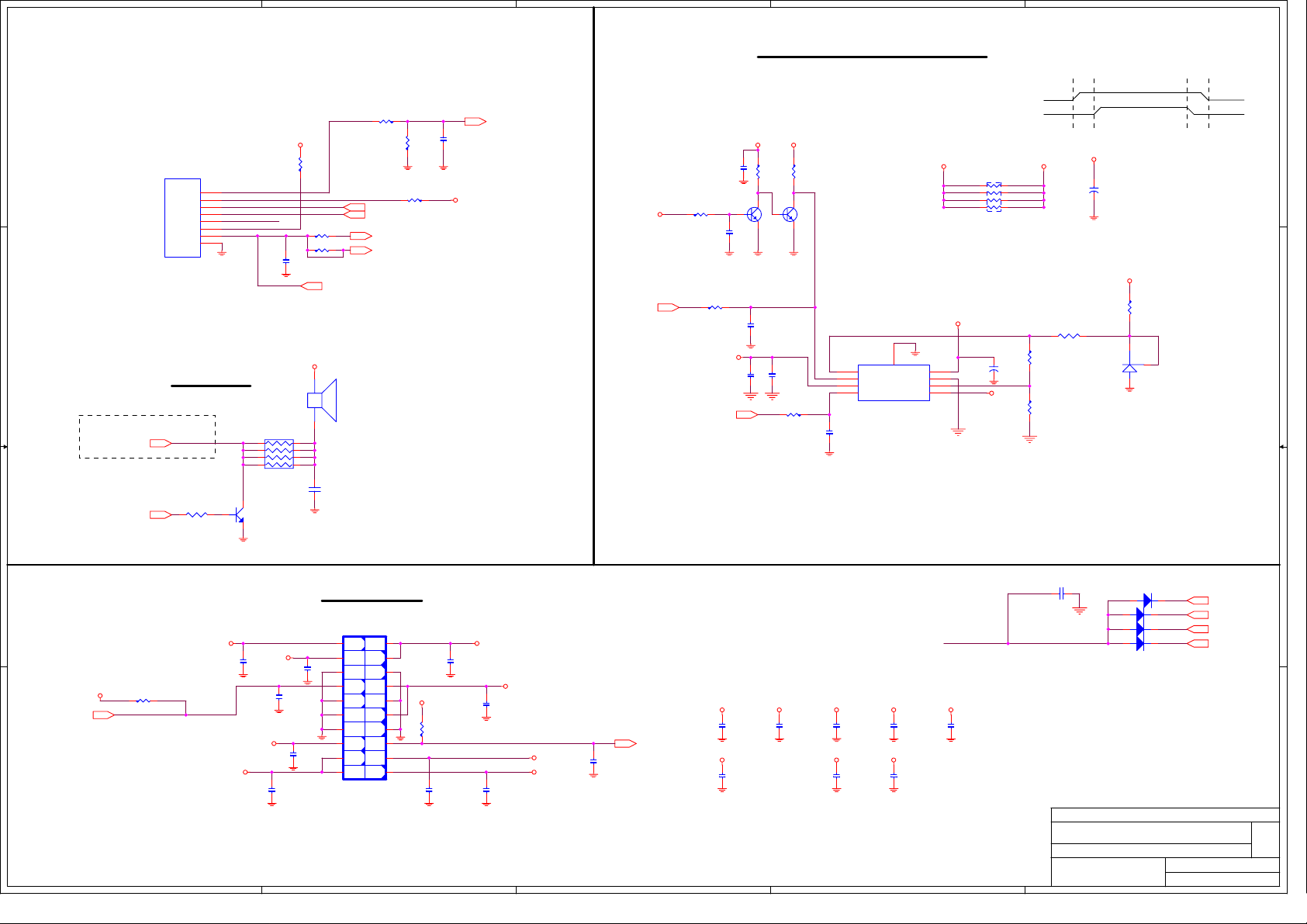

GPIO FUNCTION

ICH5

D D

C C

GPIO 0

GPIO 1

GPIO 2

GPIO 3

GPIO 4

GPIO 5

GPIO 6

GPIO 7

GPIO 8

GPIO 9

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16

GPIO 17

GPIO 18

GPIO 19

GPIO 20

GPIO 21

GPIO 22 GPO22

GPIO 23

PREQ#B

I

PREQ#B

I

PIRQ#E

I

I

PIRQ#F

I

PIRQ#G

I

PIRQ#H

GPI6

I

GPI7

I

GPI8

I

OC4#

I

OC5#

I

SIO_SMI#

I

EXTSMI#

I

SIO_PME#

I

I OC#6

OC#7

I

PGNT#A

O

O

PGNT#B

O GPO18

BIOS_WP#

O

O

GPO20

O GPO21

OD

O

GPO23

GPIO 24 I/O GPIO24

FunctionTypeGPIO Pin

GPIO 25 I/O

GPIO 27

GPIO 28

*

GPIO 32

B B

GPIO 33

GPIO 34

GPIO 40 PREQ#4

GPIO 41

GPIO 48

GPIO 49

GPIO25

I/O

GPIO27

I/O GPIO28

I/O

GPIO32

I/O

GPIO33

I/O

GPIO34

I

GPI41

I

O PGNT#4

CPUPWRGD

OD

FWH

Function

GPI 0 PD_DET

GPI 1

*

GPI 3

GPI 4

*

TypeGPIO Pin

I

SD_DET

I

I

BOM strapping for Bit 0GPI 2

Pull down through 1K ohms (unused)

I

I

BOM strapping for Bit 1

Power well

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

default output

default output

default output

default output

default output

default output

default output

DDR DIMM Config.

DEVICE

DIMM 1 MCLK_A0/MCLK_A0#

1010000B

CLOCKADDRESS

DDR DIMM Config.

DEVICE

DIMM 3 MCLK_B0/MCLK_B0#

MCLK_A1/MCLK_A1#

MCLK_A2/MCLK_A2#

DIMM 2

1010001B

MCLK_A3/MCLK_A3#

DIMM 4

MCLK_A4/MCLK_A4#

MCLK_A5/MCLK_A5#

PCI RESET DEVICE

Signals

PCIRST#_ICH5 AGP,FWH,MS-5

PCIRST#1

HD_RST#

PCI

Clock NC pin : PCI 33MHz(Pin 19 ,20) , 66MHz(Pin 27)

DEVICES

Mini PCI 1

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

Lan 6105L INT#E AD25 Lan_PCLK-Pin-16

Target

Springdale,LAN,

Super I/O,1394,MS-1

PCI slot 1-3 & Mini PCIPCIRST#2

Primary, Scondary IDE

INT#

INT#A

INT#B

INT#B

INT#C

INT#D

INT#A

INT#C

INT#D

INT#A

INT#B

INT#D

INT#A

INT#B

INT#C

INT#G

IDSEL

AD16

AD17

AD18

AD19

AD20

REQ#/GNT#

PREQ#1

PGNT#1

PCI1PREQ#1

PCI1PGNT#1

PREQ#3

PGNT#3

PCI3PREQ#3

PCI3PGNT#3

PREQ#5

PGNT#5

PREQ#4

PGNT#4

CLOCK

PCICLK1-Pin-14

PCICLK2-Pin-15

PCICLK3-Pin-20

MS1

(MS1PCLK-Pin-8)

PCICLK5-Pin-21

1010010B

1010011B

CLOCKADDRESS

MCLK_B1/MCLK_B1#

MCLK_B2/MCLK_B2#

MCLK_B3/MCLK_B3#

MCLK_B4/MCLK_B4#

MCLK_B5/MCLK_B5#

A A

5

4

1394 INT#F AD26 1394_PCLK-Pin-12

MS-1

3

PREQ#2

PGNT#2

PREQ#0

PGNT#0

MS1PCLK-Pin-8

2

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

GPIO Spec.

MS-7041

Last Revision Date:

Thursday, December 04, 2003

Sheet

329

1

Rev

100

of

5

4

3

2

1

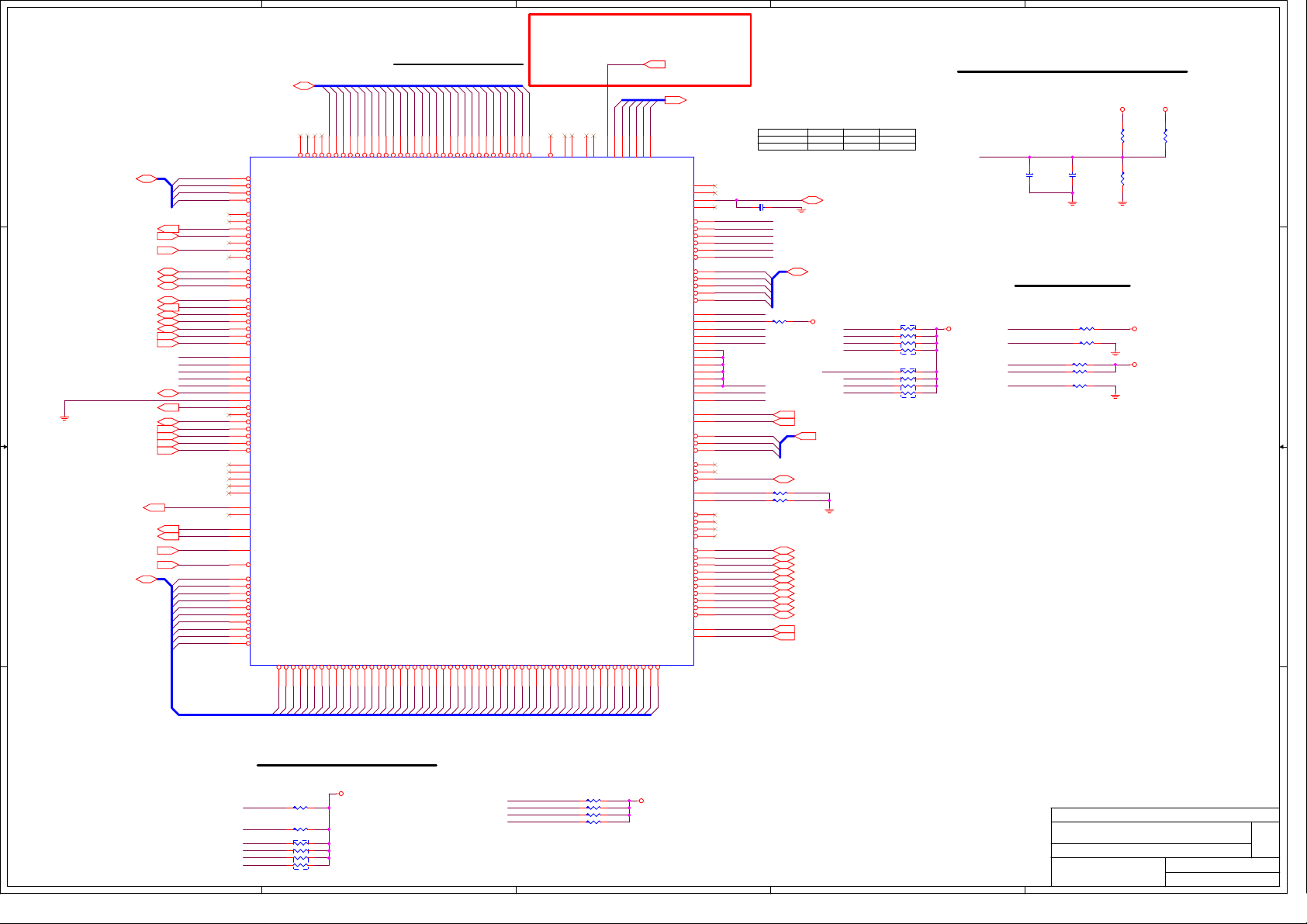

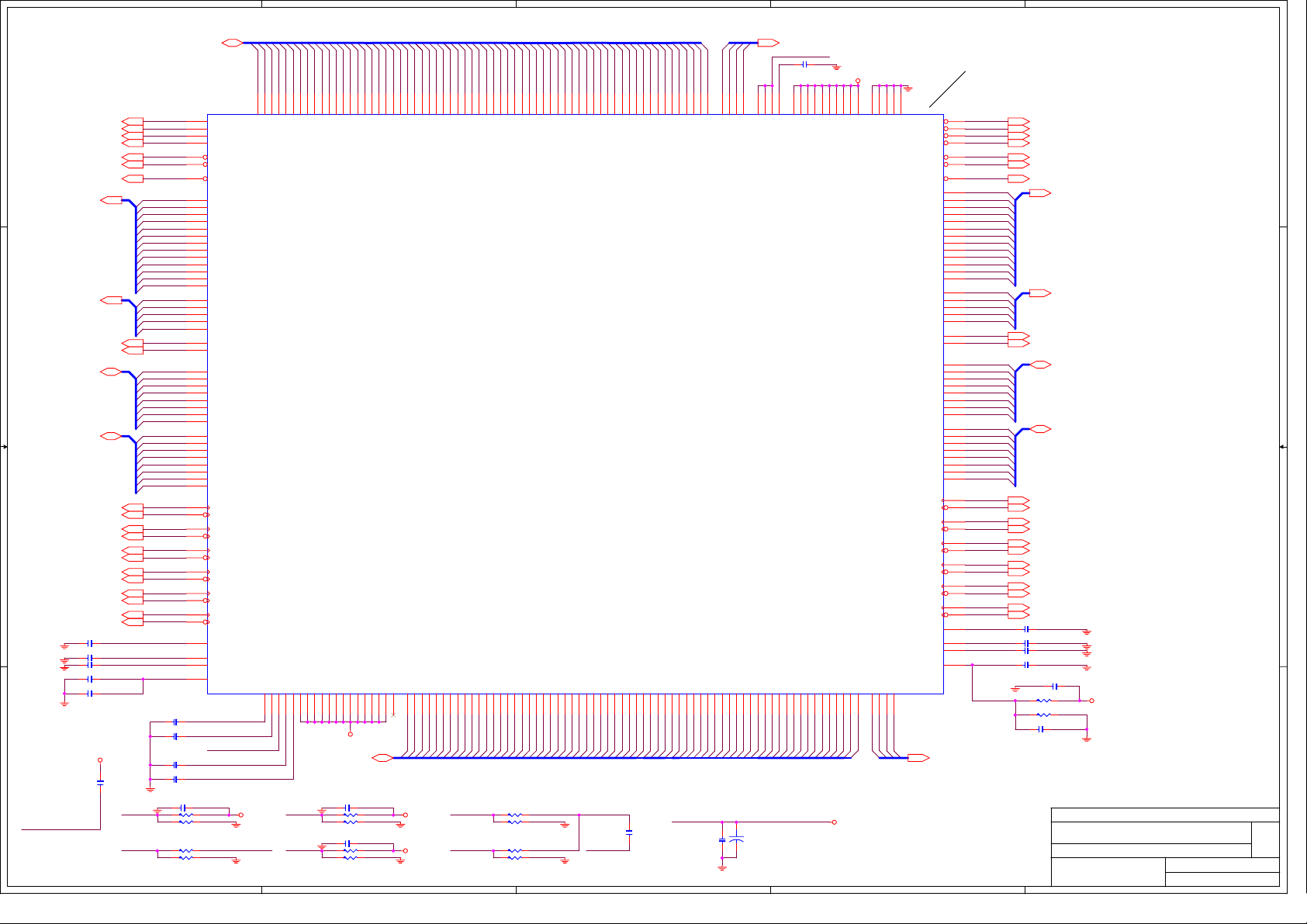

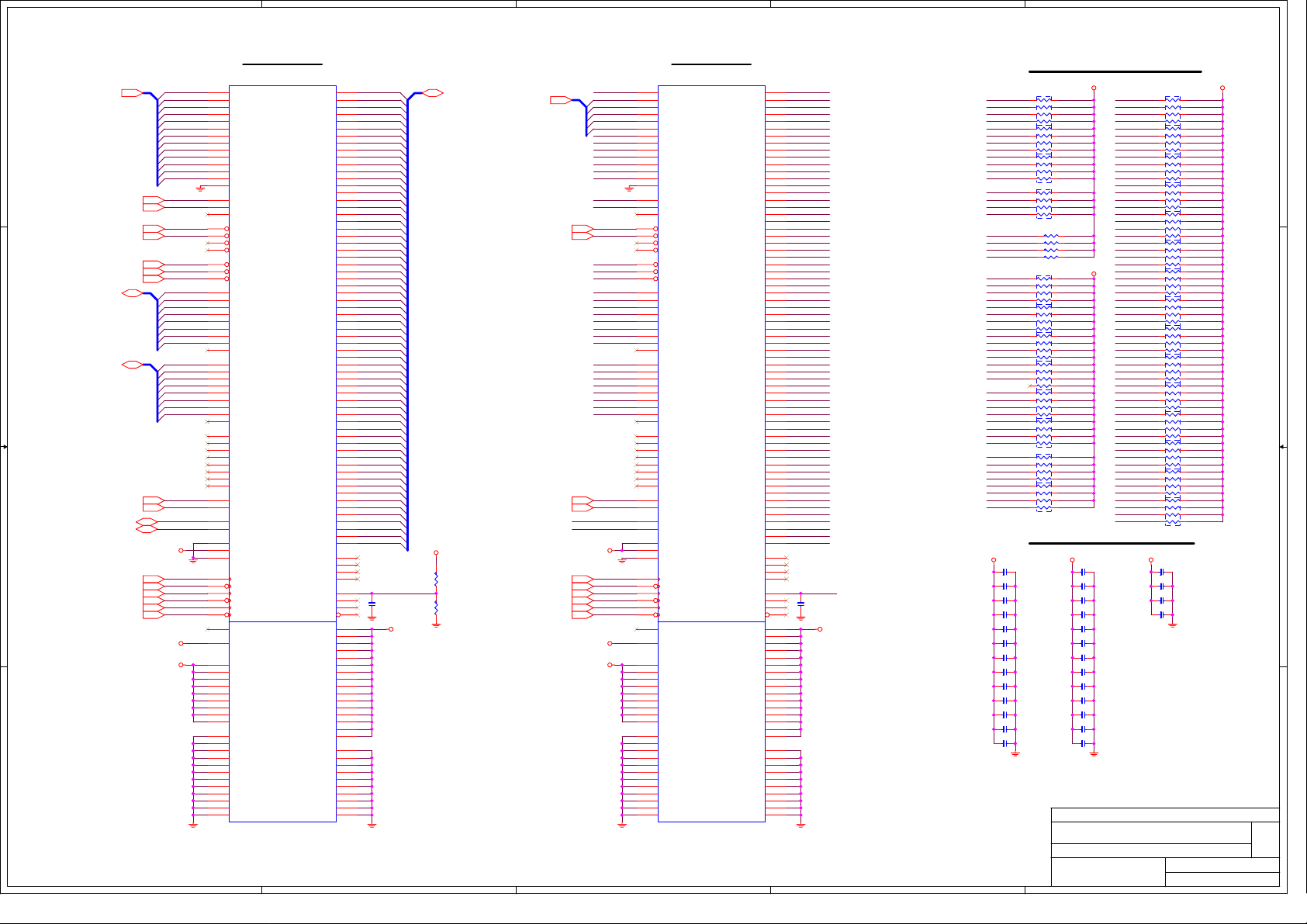

CPU SIGNAL BLOCK

HA#[3..31]7

D D

CPU1A

HDBI#[0..3]7

FERR#14

STPCLK#14

HINIT#14,25

HDBSY#7

HDRDY#7

HTRDY#7

HADS#7

HLOCK#7

HBNR#7

HITM#7

C C

B B

HBPRI#7

HDEFER#7

CPU_TMPA25

TRMTRIP#14

PROCHOT#7

IGNNE#14

A20M#14

BOOT22,27

BSEL06

BSEL16

CPU_GD14

CPURST#7

HD#[0..63]7

HDBI#0

HDBI#1

HDBI#2

HDBI#3

HIT#7

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

PROCHOT#

SMI#14

SLP#14

BOOT

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

G25

AC3

AA3

AB2

AF26

AB26

AE21

AF24

AF25

AD1

AE26

AD6

AD5

AB23

AB25

AA24

AA22

AA25

W25

W26

E21

P26

V21

V6

B6

Y4

W5

H5

H2

J6

G1

G4

G2

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

C3

B2

B5

C6

A22

A7

Y21

Y24

Y23

Y26

V24

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

BOOTSELECT

OPTIMIZED/COMPAT#

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

A33#

D53#

D52#

D51#

D50#

D49#

D48#

V22

U21

V25

U23

U24

U26

T23

A32#

D47#

HA#30

HA#31

A31#

D46#

T22

T25

HA#29

A30#

D45#

T26

HA#28

A29#

D44#

R24

HA#27

A28#

D43#

R25

HA#26

A27#

D42#

P24

HA#25

A26#

D41#

R21

HA#24

A25#

D40#

N25

HA#23

A24#

D39#

N26

HA#22

A23#

D38#

M26

HA#21

A22#

D37#

N23

HA#20

A21#

D36#

M24

HA#19

A20#

D35#

P21

HA#18

A19#

D34#

N22

HA#17

A18#

D33#

M23

HA#16

A17#

D32#

H25

HA#15

A16#

D31#

K23

HA#14

A15#

D30#

J24

HA#13

A14#

D29#

L22

HA#12

A13#

D28#

M21

HA#11

A12#

D27#

H24

HA#10

A11#

D26#

G26

A10#

D25#

HA#9

L21

A9#

D24#

HA#8

D26

A8#

D23#

HA#7

F26

HA#6

A7#

D22#

HA#4

HA#5

HA#3

AE25A5A4

A6#

A5#

A4#

A3#

DBR#

D21#

D20#

D19#

D18#

D17#

D16#

D15#

D14#

E25

F24

F23

G23

E24

H22

D25

J21

D23

AD26

AC26

ITP_CLK1

VSS_SENSE

VCC_SENSE

D13#

D12#

D11#

D10#

C26

H21

G22

B25

VID5

AD2

ITP_CLK0

VIDPWRGD

D9#

D8#

D7#

C24

C23

AD3

VID5#

D6#

B24

VID4

AE1

D22

VID3

VID4#

D5#

AE2

C21

VID2

AE3

VID3#

D4#

A25

VID1

AE4

VID2#

D3#

A23

VID_GD 21,22

VID0

AE5

VID1#

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D2#

D1#

D0#

PGA-S478-GD10-F02

B22

B21

{Priority}

VID[0..5] 22

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

VIDPWRGD DC Specifications

VIL

VIH

It must rout to the enable pin of PWM and CK-409.

VIDGD to Vccp delay time is from 1ms to 10ms.

VIDGD rising time is 150ns.

C63 220p_X7R

{VOLTAGE}

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

TESTHI12

TESTHI11

R57 62

TESTHI10

TESTHI9

TESTHI8

TESTHI2

TESTHI1

TESTHI0

HRS#2

HRS#1

HRS#0

HBR#0

COMP1

R38 61.9RST

R89 61.9RST

COMP0

0.9

HREQ#[0..4] 7

VCCP

CPU_CLK# 6

CPU_CLK 6

HRS#[0..2] 7

HBR#0 7

HADSTB#1 7

HADSTB#0 7

HDSTBP#3 7

HDSTBP#2 7

HDSTBP#1 7

HDSTBP#0 7

HDSTBN#3 7

HDSTBN#2 7

HDSTBN#1 7

HDSTBN#0 7

NMI 14

INTR 14

Min

GTLREF 7

CPURST#

Typ

TESTHI1

TESTHI10

TESTHI9

TESTHI8

TESTHI0

TESTHI12

TESTHI2

Max

0.3

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

CPU GTL REFERNCE VOLTAGE BLOCK

VCCP

{VOLTAGE}

0.63*Vccp

C64

0.1u/25V/Y5V

GTLREF

C66

0.1u_X7R

CPU ITP BLOCK

RN80

VCCP

62

RN81

62

ITP_TDI

ITP_TRST#

ITP_TMS

ITP_TDO

ITP_TCK

R47 150

R16 680

R17 X_39

R15 X_75

R23 27

R74

100RST

R76

169RST

VCCP

VCCP

VTT

R135

X_200RST

HD#1

HD#6

HD#4

HD#3

HD#5

HD#7

HD#8

HD#52

HD#53

HD#50

HD#51

HD#49

HD#48

HD#47

HD#45

HD#46

HD#43

HD#44

HD#41

HD#42

HD#40

HD#39

HD#38

HD#37

HD#36

HD#35

HD#33

HD#34

HD#32

HD#31

HD#29

HD#30

HD#27

HD#28

HD#26

HD#25

HD#23

HD#24

HD#22

HD#21

HD#20

HD#19

HD#17

HD#18

HD#16

HD#15

HD#14

HD#13

HD#12

HD#11

HD#9

HD#10

HD#2

HD#0

CPU STRAPPING RESISTORS

A A

BPM#2 CPU_GD

R31 62

BPM#0

R11 62

BPM#1

1 2

BPM#5

3 4

BPM#4

5 6

BPM#3

7 8

5

VCCP

RN82

62

4

ALL COMPONENTS CLOSE TO CPU

PROCHOT#

HBR#0

CPURST#

R49 62

R113 300

R45 220

R111 X_62

VCCP

3

Micro Star Restricted Secret

Title

Intel mPGA478B - Signals

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

MS-7041

1

Last Revision Date:

Sheet

Tuesday, December 09, 2003

429

Rev

100

of

5

4

3

2

1

C16

X_105P

E20E8F11

VCC

VCC

VSS

VSS

Near processor

F13

F15

VCC

VCC

VSS

VSS

G21G6G24

G3H1H23

1.2V 150mA

C12

X_0.1u/25V/Y5V

F17

F19

F9

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

H26H4J2

AF4

VCC-VID

VSS

AF3

VSS

J22

AD20

VCC-VIDPRG

VSS

VSS

J25J5K21

AE23

VCCA

VSSA

VCC-IOPLL

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

PGA-S478-GD10-F02

{Priority}

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

C74

105P

It support DC current if 100mA.

CPU_IOPLL

C80

C76

X_22u/1206

105P

VSSA

The ESL is less than 5nH, and the ESR is less than 0.3ohm.

L3 4.7uH-1206-100mA

L2 4.7uH-1206-100mA

C79

10U/1206

DC voltage drop should

be less than 70mV.

VCCP

D15

D17

VCC

VCC

VSS

VSS

E7E9F10

D19D7D9

VCC

VCC

VSS

VSS

F12

F14

E10

VCC

VSS

F16

VCC_VID

E12

VCC

VCC

VSS

VSS

F18F2F22

C15

10U/1206

E14

E16

E18

VCC

VCC

VSS

VSS

F25F5F8

VCC

VSS

VCC_VID21

CPU VOLTAGE BLOCK

VID Voltage is from 1.14V to 1.32V.

D D

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

C C

B B

AA19

AA23

AA26

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AC22

AC25

AA4

AA7

AA9

AB3

AB6

AB8

AC2

AC5

AC7

AC9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

VSS

AD12

VSS

AD14

VSS

AD16

VSS

AD18

VSS

AD21

VSS

AD23

AD4

VSS

AD8

VSS

VSS

AE11

VSS

AE13

VSS

AE15

VSS

AE17

AE19

VSS

VSS

AE22

AE24

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B23

B20

B26B4B8

C11

C13

AF19

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

C15

C17C2C19

C22

C25C5C7C9D12

It is derived from 3.3V.

It should be able to source 150mA.

It drives the power logic of BSEL[1:0] and VID[5:0].

VID to VIDGD delay time is from 1ms to 10ms.

VID to VIDGD deassertion time is 1ms for max.

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D14

D16

D18

D20

D21D3D24D6D8E1E11

C10

C12

C14

C16

C18

C20C8D11

D13

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E13

E15

E17

E19

E23

E4

E26

CPU DECOUPLING CAPACITORS

C57

10U/1206

C60

10U/1206

C61

X_100U

A A

5

C58

10U/1206

C59

10U/1206

C41

100U

VCCPVCCP VCCP

C73

X_10U/1206

C39

X_10U/1206

C56

X_10U/1206

C48

10U/1206

C35

X_10U/1206

C65

X_10U/1206

4

VCCP VCCP

Place these caps within north side of processorPlace these caps within socket cavity

C38

X_10U/1206

C36

10U/1206

C68

X_10U/1206

C51

10U/1206

C50

X_10U/1206

C69

X_10U/1206

C40

10U/1206

C49

X_10U/1206

C34

10U/1206

C53

10U/1206

C54

X_10U/1206

C71

X_10U/1206

Micro Star Restricted Secret

Title

Intel mPGA478B - Power

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

3

2

http://www.msi.com.tw

MS-7041

1

Last Revision Date:

Sheet

Tuesday, December 09, 2003

529

Rev

100

of

5

4

3

2

1

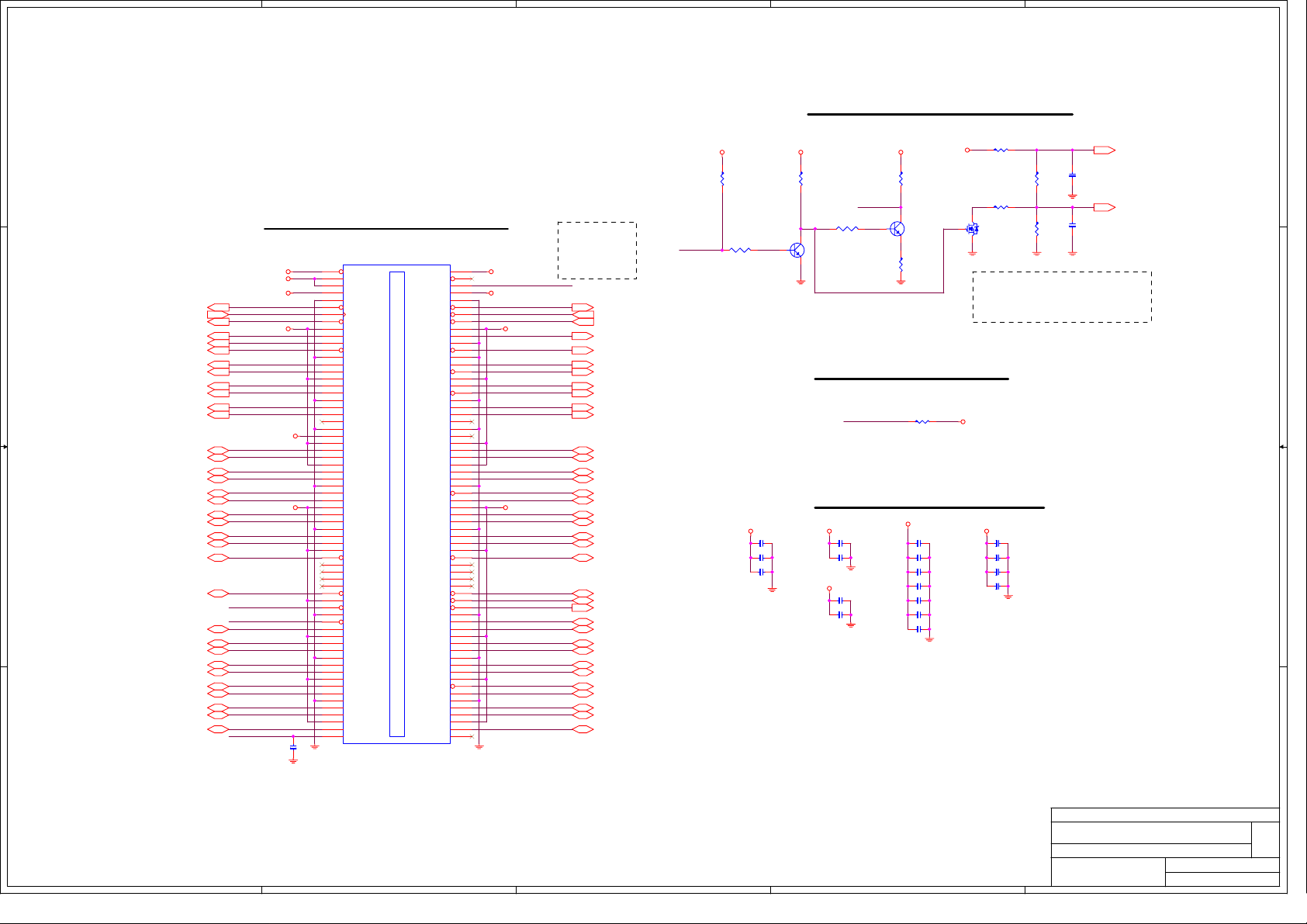

Clock Synthesizer

FS_A

*Trace less 0.5"

D D

C C

CP4 X_COPPER

VCC3

Use 2 VIA hole on BEAD both side

FB7

C130

0.1u/25V/Y5V

CP5 X_COPPER

FB8 X_80-0805-3A

VCC3

Use 2 VIA hole on BEAD both side

X_80-0805-3A

EC19

+

X_10U/16V/S

VCC3V

C132

0.1u/25V/Y5V

SMBDATA_ISO

SMBCLK_ISO

U7

41 39

C135

0.1u/25V/Y5V

C136

0.1u/25V/Y5V

C139

0.1u/25V/Y5V

C133

X_0.1u/25V/Y5V

C176

0.1u/25V/Y5V

C173

0.1u/25V/Y5V

C172

0.1u/25V/Y5V

C140

103P

CPU_VDD CPU0#

44

CPU_GND

35

SRC_VDD

38

SRC_GND

28

3V66_VDD

10

PCI_VDD

11

PCI_GND

17

PCI_VDD

18

PCI_GND

25

48_VDD

24

48_GND

3

REF_VDD

6

REF_GND

48

*120k Pull-up

VDDA

**120k Pull-down

47

GND

33

SDATA

32

SCLK

CPU0

CPU1

CPU1#

SRC

SRC#

3V66_0

3V66_1

3V66_2

3V66_3/VCH3V66_GND

**FS2/PCI_F0

**FS4/PCI_F1

PCI_F2

PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

PCI6

PCI7

**SEL24_48#/24_48

**FS3/48M_0

*FS_A/REF_0

*FS_B/REF_1

XOUT

VTT_PWRGD/PD#

RESET#

IREF

ICS952607

CPUCLK

40

CPUCLK#

MCHCLK

43

MCHCLK#

42

SATA100 SATA_100

37

SATA100#

36

MCH66

31

ICH66

30

27

AGPCLK

2629

7

FWHPCLK

8

RPCISLOT3

9

1394PCLK

12

SIOPCLK

13

PCICLK1

14

PCICLK2

15

16

19

20

PCICLK5

21

SIO48

22

USB48

23

SEL0

1

2

4

XIN

5

34

45

R175 475

46

Iref = 2.32mA

7 8

5 6

3 4

1 2

18PC162

18PC154

CPU_CLK

CPU_CLK#

MCH_CLK

MCH_CLK#

SATA_100#

ICH_PCLKICHPCLK

FWH_PCLK

1394_PCLK

SIO_PCLK

PCI_CLK1

PCI_CLK2

LAN_PCLKLANPCLK

PCI_CLK3

PCI_CLK5

2N3904S

Q18

CPU_CLK 4

CPU_CLK# 4

MCH_CLK 7

MCH_CLK# 7

SATA_100 14

SATA_100# 14

MCH_66 9

ICH_66 14

AGP_CLK 12

ICH_PCLK 13

FWH_PCLK 25

1394_PCLK 17

SIO_PCLK 25

PCI_CLK1 15

PCI_CLK2 16

LAN_PCLK 18

PCI_CLK3 16

PCI_CLK5 16

SIO_48 25

DOT_48 9

USB_48 14

AUDIO_14 19

ICH_14 14

R166 10K

Q17

2N3904S

R162 33

R163 33

R160 33

R161 33

R164 33

R165 33

R157 33

R158 33

R190 33

R215 33

R216 33

R217 33

R203 33

RN67

33

R498 33

R204 33

R199 33

R618 X_33

R198 33

R232 33

R518 33

Y1

14.318M

CG_PWRGD# VCC3V

FP_RST# 14,27

PCISLOT3

R150 10K

R145 10K X_10PC177

1394_PCLK

2

1 3

R505 X_10K

VCC3

VCCP

FS_4 FS_3 FS_2

MS1_PCLK

X_0

Default(2-3)

PCI_CLK4 16

BSEL0_SPG7

00

0

00

0

ICHPCLK

FWHPCLK

USB48

MS1_PCLK 16

VCC3V

R223

1K

SEL0 SEL1

R200 10K

BSEL04

R213

2KST

R112

2.49KST

BSEL0

1

101

R201 1K

R202 1K

R193 1K

FS_B

BSEL1

R224

1K

R214 10K

R235

2KST

R241

2.49KST

CPU

133.3

166.7

BSEL1 4

BSEL1_SPG 7

R151 49.9RST

CPU_CLK

CPU_CLK#

R154 49.9RST

R152 49.9RST

MCH_CLK

MCH_CLK#

R153 49.9RST

SATA_100

R155 49.9RST

SATA_100#

R156 49.9RST

MCH66

ICH66

AGPCLK

USB_48

SIO_48

X_10PC137

X_10PC138R497

X_10PC151

10PC164

10PC168

EMC HF filter capacitors, located close to PLL

ICH_PCLK

FWH_PCLK

SIO_PCLKSEL1

PCISLOT3

1394_PCLK

PCI_CLK1

PCI_CLK2

LAN_PCLK

PCI_CLK3

PCI_CLK5

AUDIO_14

CN10

7 8

5 6

3 4

1 2

8P4C-10P

CN9

7 8

5 6

3 4

1 2

X_8P4C-10P

X_10PC415

10PC426

B B

SMBCLK_ISO

SMBDATA_ISO

R179 2.7K

R169 2.7K

VCC3

SMBus Isolation

SMBCLK

A A

PWROK_SMB21

5

4

+12V

R174

1K

C141

X_0.1u/25V/Y5V

R171 4.7K

R167 4.7K

NDS7002AS

NDS7002AS

3

Q20

SMBCLK_ISO

SMBDATA

Q19

SMBDATA_ISO

SMBCLK 14,16

R529

X_0

SMBCLK_ISO 10,11,21

SMBDATA 14,16

R530

X_0

SMBDATA_ISO 10,11,21

14 ICH5

16 PCI

25 IO

10 DDR

11 DDR

21 MS5

Micro Star Restricted Secret

Title

Clock Synthesizer

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

MS-7041

1

Last Revision Date:

Tuesday, December 09, 2003

Sheet

629

Rev

100

of

5

VCCA_FSB

VCC_AGP

C102 0.1u/25V/Y5V

A31

B4

J6J7J8J9K6K7K8K9L6L7L9

VCC

VCCA_FSB

VCCA_FSB

VSS

VSS

VSS

VSS

VSS

C12

C14

C16

C18

C10

C8

VCC

VSS

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

C20

C22

C24

C26

AE14

D26

D30

L23

E29

B32

K23

C30

C31

J25

B31

E30

B33

J24

F25

D34

C32

F28

C34

J27

G27

F29

E28

H27

K24

E32

F31

G30

J26

G26

B30

D28

B24

B26

B28

E25

F27

B29

J23

L22

C29

J21

K21

E23

L21

D24

E27

G24

G22

C27

B27

B7

C7

E8

AK4

AJ8

L20

L13

L12

E24

C25

F23

U6A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

BREQ0#

BPRI#

BNR#

HLOCK#

ADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HIT#

HITM#

DEFER#

HTRDY#

DBSY#

DRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

CPURST#

RSTIN#

ICH_SYNC#

PROCHOT#

BSEL0

BSEL1

HDRCOMP

HDSWING

HDVREF

HA#[3..31]4

D D

HADSTB#04

HADSTB#14

C C

HBR#04

HBPRI#4

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HBNR#4

HLOCK#4

HADS#4

HREQ#[0..4]4

HITM#4

HDEFER#4

HTRDY#4

HDBSY#4

HDRDY#4

HRS#[0..2]4

MCH_CLK6

MCH_CLK#6

B B

CPURST#4

PCIRST#116,17,18,21,25

PROCHOT#4

BSEL0_SPG6

BSEL1_SPG6

R107 20RST

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HIT#4

HRS#0

HRS#1

HRS#2

MS5_POK

ICH_SYNC#

HRCOMP

HSWING

GTLREF4

220p_X7R

C101

VCC

VCC

VCC

VSS

VSS

VSS

C28D1D11

D9

VCC

VSS

4

N11N9P10

P11

R11

T16

T17

T18

T19

U16

U17

U20

V16

V18

V20

W16

N10

M10

M11M8M9

L10

L11

VCC

VCC

VCC

VSS

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D19

D21

D23

D25

D27

D29

D31

D33

VCC

VCC

VSS

VSS

D13

D15

D17

VCC

VSS

T20

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D35

F3F5F8

E3

F1

E1

F10

W19

W20

Y16

Y17

Y18

Y19

Y20

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F18

F20

F22

F14

F16

F12

VSS

VSS

VSS

VSS

G31

G35

H5

F24

F26

G28

3

A3

A33

A35B2B25

B34C1C23

C35

E26

M31

AF13

AF23

AJ12

AN1

R25

NCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNC

VSS

VSS

VSS

VSS

VSS

VSS

H12

H14

H16H2H20

H18

H8

H9

VSS

NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H22

H24

H26

H30

H33

J10

J12

J14

J16

J18

2

VTT

D5D6D7E6E7

F7

AP2

AR3

AR33

AR35

A7A9A11

A13

A16

A20

A23

A25

A27

A29

A32

C4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J20

J22

J28

J32

J35

K11

K12

K14

K16

K18

K33

K20

K22

K25

K27

K29

L24

L25

A4A5A6B5B6C5C6

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

M3M6M26

VSS

M27

M28

M30

M33N1N4

VSS

VSS

VSS

L26

L35

L31

A15

VTT

VTT

VTT

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

VSS

VSS

Intel Springdale-N

{Priority}

VTT_FSB1

VTT_FSB2

A21

HD0#

HD1#

HD2#

HD3#

VTT_FSB

VTT_FSB

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DINV_0#

DINV_1#

DINV_2#

DINV_3#

B23

E22

B21

D20

B22

D22

B20

C21

E18

E20

B16

D16

B18

B17

E16

D18

G20

F17

E19

F19

J17

L18

G16

G18

F21

F15

E15

E21

J19

G14

E17

K17

J15

L16

J13

F13

F11

E13

K15

G12

G10

L15

E11

K13

J11

H10

G8

E9

B13

E14

B14

B12

B15

D14

C13

B11

D10

C11

E10

B10

C9

B9

D8

B8

C17

L17

L14

C15

B19

C19

L19

K19

G9

F9

D12

E12

C110 0.47u

C107 0.47u

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDBI#0

HDBI#1

HDBI#2

HDBI#3

HD#[0..63] 4

HDBI#[0..3] 4

HDSTBP#0 4

HDSTBN#0 4

HDSTBP#1 4

HDSTBN#1 4

HDSTBP#2 4

HDSTBN#2 4

HDSTBP#3 4

HDSTBN#3 4

1

VCC3

C120

+

CP19 X_COPPER

L11 X_0.82uH-30mA

EC18

10U/16V/S

4

VCC_AGP

0

10

00

1

111

0

0

0

ICH_SYNC#

MS5_POK14,21

MS5_POK

VCC3

3

Q21 X_2N3904S

Q25 X_2N3904S

R227 X_220

R228 X_0

R226

X_220

R225

X_1K

ICH_PWROK 14,21

Micro Star Restricted Secret

Title

Intel Springdale - CPU

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

MS-7041

1

Last Revision Date:

Sheet

Tuesday, December 09, 2003

729

Rev

100

of

VTT

A A

HSWING

C124

X_0.01u_X7R

C125

0.01u_X7R

{VOLTAGE}

1/4*Vccp

5

R144

301RST

R147

100RST

VCCA_FSB

0.1u_X7R

I=30mA ICH_SYNC# MS5_POK ICH_PWROK

5

4

3

2

1

MDQ_A[0..63]10 MCKE_A[0..3] 10

MCKE_A1

MDQ_A4

MDQ_A9

MDQ_A3

MDQ_A6

MDQ_A2

AM12

AN13

AM10

SDQ_A1

SDQ_A2

SDQ_A3

VCC_DDR

VCC_DDR

VCC_DDR

AA35

R35

AR21

MDQ_A7

MDQ_A5

AL10

AL12

AP13

SDQ_A4

SDQ_A5

SDQ_A6

VCC_DDR

VCC_DDR

VCC_DDR

AL7

AR15

AL6

MDQ_A8

MDQ_A10

AP14

AM14

AL18

SDQ_A7

SDQ_A8

SDQ_A9

VCC_DDR

VCC_DDR

VCC_DDR

AM1

AM2

AN8

MDQ_A12

MDQ_A11

MDQ_A13

AP19

AL14

AN15

SDQ_A10

SDQ_A11

SDQ_A12

VCC_DDR

VCC_DDR

VCC_DDR

AP3

AP4

AP5

MDQ_A15

MDQ_A16

MDQ_A14

AP18

AM18

AP22

SDQ_A13

SDQ_A14

SDQ_A15

VCC_DDR

VCC_DDR

VCC_DDR

AR4

AP6

AP7

MDQ_A18

MDQ_A17

MDQ_A19

AM22

AL24

AN27

SDQ_A16

SDQ_A17

SDQ_A18

VCC_DDR

VCC_DDR

VCC_DDR

AR5

AR7

AR31

MDQ_A22

MDQ_A21

MDQ_A20

AP21

AL22

SDQ_A19

SDQ_A20

SDQ_A21

VCC_DDR

SDQ_B0

AJ10

MDQ_A24

MDQ_A23

AP25

AP27

AP28

SDQ_A22

SDQ_A23

SDQ_B1

SDQ_B2

AE15

AL11

AE16

MDQ_A25

MDQ_A26

AP29

AP33

SDQ_A24

SDQ_A25

SDQ_A26

SDQ_B3

SDQ_B4

SDQ_B5

AL8

AF12

MDQ_A28

MDQ_A27

AM33

AM28

SDQ_A27

SDQ_B6

AK11

AG12

MDQ_A30

MDQ_A29

AN29

AM31

SDQ_A28

SDQ_A29

SDQ_A30

SDQ_B7

SDQ_B8

SDQ_B9

AE17

AL13

MDQ_A31

MDQ_A32

AN34

AH32

SDQ_A31

SDQ_A32

SDQ_B10

SDQ_B11

AK17

AL17

MDQ_A33

MDQ_A34

AG34

AF32

SDQ_A33

SDQ_A34

SDQ_B12

SDQ_B13

AK13

AJ14

MDQ_A35

MDQ_A36

AD32

AH31

SDQ_A35

SDQ_A36

SDQ_B14

SDQ_B15

AJ16

AJ18

MDQ_A38

MDQ_A37

AG33

AE34

SDQ_A37

SDQ_A38

SDQ_B16

SDQ_B17

AE19

AE20

MDQ_A40

MDQ_A39

AD34

AC34

SDQ_A39

SDQ_A40

SDQ_B18

SDQ_B19

AG23

AK23

MDQ_A42

MDQ_A41

AB31

V32

SDQ_A41

SDQ_A42

SDQ_B20

SDQ_B21

AL19

AK21

MDQ_A44

MDQ_A43

V31

AD31

SDQ_A43

SDQ_A44

SDQ_B22

SDQ_B23

AJ24

AE22

MDQ_A45

MDQ_A46

AB32

U34

SDQ_A45

SDQ_A46

SDQ_B24

SDQ_B25

AK25

AH26

MDQ_A48

MDQ_A47

U33

T34

SDQ_A47

SDQ_B26

AG27

AF27

MDQ_A50

MDQ_A49

T32

K34

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_B27

SDQ_B28

SDQ_B29

AJ26

AJ27

MDQ_A51

MDQ_A52

K32

T31

SDQ_A51

SDQ_A52

SDQ_B30

SDQ_B31

AD25

AF28

MDQ_A54

MDQ_A53

P34

L34

SDQ_A53

SDQ_A54

SDQ_B32

SDQ_B33

AE30

AC27

MDQ_A56

MDQ_A55

L33

J33

SDQ_A55

SDQ_A56

SDQ_B34

SDQ_B35

AC30

Y29

MDQ_A58

MDQ_A57

H34

E33

SDQ_A57

SDQ_B36

AE31

AB29

MDQ_A59

MDQ_A60

F33

K31

SDQ_A58

SDQ_A59

SDQ_B37

SDQ_B38

AA26

AA27

MDQ_A1

MDQ_A0

AP10

U6B

D D

MCS_A#010

MCS_A#110

MCS_A#210

MCS_A#310

MRAS_A#10

MCAS_A#10

MWE_A#10

MA_A[0..12]10

MAB_A[1..5]10

C C

MBA_A010

MBA_A110

MDQM_A[0..7]10

MDQS_A[0..7]10

MCLK_A010

MCLK_A#010

MCLK_A110

MCLK_A#110

MCLK_A210

B B

MCLK_A#210

MCLK_A310

MCLK_A#310

MCLK_A410

MCLK_A#410

MCLK_A510

MCLK_A#510

103PC189

103PC186

103PC191

0.1u/25V/Y5VC89

C91 105P

AA34

SCS_A0#

Y31

SCS_A1#

Y32

SCS_A2#

W34

SCS_A3#

AC33

SRAS_A#

Y34

SCAS_A#

AB34

SWE_A#

MA_A0

AJ34

AL33

AK29

AN31

AL30

AL26

AL28

AN25

AP26

AP24

AJ33

AN23

AN21

AL34

AM34

AP32

AP31

AM26

AE33

AH34

AP12

AP16

AM24

AP30

AF31

W33

M34

AN11

AP15

AP23

AM30

AF34

M32

AK32

AK31

AP17

AN17

AK33

AK34

AM16

AL16

AK9

AN9

H32

V34

H31

N33

N34

P31

P32

AL9

E34

SMAA_A0

SMAA_A1

SMAA_A2

SMAA_A3

SMAA_A4

SMAA_A5

SMAA_A6

SMAA_A7

SMAA_A8

SMAA_A9

SMAA_A10

SMAA_A11

SMAA_A12

SMAB_A1

SMAB_A2

SMAB_A3

SMAB_A4

SMAB_A5

SBA_A0

SBA_A1

SDM_A0

SDM_A1

SDM_A2

SDM_A3

SDM_A4

SDM_A5

SDM_A6

SDM_A7

SDQS_A0

SDQS_A1

SDQS_A2

SDQS_A3

SDQS_A4

SDQS_A5

SDQS_A6

SDQS_A7

SMDCLK_A0

SMDCLK_A0#

SMDCLK_A1

SMDCLK_A1#

SMDCLK_A2

SMDCLK_A2#

SMDCLK_A3

SMDCLK_A3#

SMDCLK_A4

SMDCLK_A4#

SMDCLK_A5

SMDCLK_A5#

SMXRCOMP

SMXCOMPVOH

SMXCOMPVOL

SMVREF_A

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11 MA_B12

MA_A12

MAB_A1

MAB_A2

MAB_A3

MAB_A4

MAB_A5

MDQM_A0

MDQM_A1

MDQM_A2

MDQM_A3

MDQM_A4

MDQM_A5

MDQM_A6

MDQM_A7

MDQS_A0

MDQS_A1

MDQS_A2

MDQS_A3

MDQS_A4

MDQS_A5

MDQS_A6

MDQS_A7

XRCOMP

XCOMPH

XCOMPL

XVREF

AP11

SDQ_A0

E35

MDQ_A62

MDQ_A63

MDQ_A61

J34

G34

SDQ_A60

SDQ_A61

SDQ_A62

SDQ_B39

SDQ_B40

SDQ_B41

AA30

W30

MCKE_A0

F34

SDQ_A63

SDQ_B42

SDQ_B43

U27

T25

MCKE_A2

AL20

AN19

SCKE_A0

SCKE_A1

SDQ_B44

SDQ_B45

AA31

V29

AM20

SCKE_A2

SDQ_B46

U25

C99 474P

C93 224P

VCC_DDR

A A

C417

XCOMPH

103P

C134 224P

C148 0.1u/25V/Y5V

5

C187 X_105P

R219 42.2RST

R218 42.2RST

R116 42.2RST

R108 42.2RST

VCC_DDR_C2

VCC_DDR_C3

values still need verification

VCC_DDR VCC_DDR

AA35AA33

VCC_DDR

MDQ_B[0..63]11

C192 X_105P

R221 30.1KST

R220 10KST

C190 105P

R209 10KST

R208 30.1KST

MDQ_B0

MDQ_B10

YCOMPLXCOMPLXRCOMP

R33

YCOMPHXCOMPHYRCOMP VCC_DDR_C3

VCC_DDR

4

R34

MDQ_B11

MDQ_B12

MDQ_B14

MDQ_B13

MDQ_B15

R100 30.1KST

R101 10KST

R105 10KST

R103 30.1KST

MDQ_B17

MDQ_B19

MDQ_B22

MDQ_B16

MDQ_B18

MDQ_B21

MDQ_B20

MDQ_B29

MDQ_B27

MDQ_B26

MDQ_B25

MDQ_B23

MDQ_B24

MDQ_B28

VCC_DDR_C2

R35

YCOMPH

MDQ_B36

MDQ_B33

MDQ_B30

MDQ_B32

MDQ_B34

MDQ_B35

MDQ_B31

C416

103P

3

MDQ_B38

MDQ_B39

MDQ_B37

VCCA_DDR

0.1u/25V/Y5V

MDQ_B43

MDQ_B44

MDQ_B42

MDQ_B45

MDQ_B41

MDQ_B40

MDQ_B46

C126

+

MDQ_B9

MDQ_B8

MDQ_B4

MDQ_B5

MDQ_B3

MDQ_B6

MDQ_B7

MDQ_B1

MDQ_B2

MCKE_A3

AP20

AB25

AC25

SCKE_A3

VCCA_DDR

VCCA_DDR

SDQ_B47

SDQ_B48

SDQ_B49

SDQ_B50

R27

P29

R30

K28

MDQ_B49

MDQ_B48

MDQ_B47

MDQ_B50

EC20

X_10U/16V/S

VCCA_DDR

AC26

AL35

VCCA_DDR

VCCA_DDR

SDQ_B51

SDQ_B52

SDQ_B53

L30

R31

R26

MDQ_B53

MDQ_B52

MDQ_B51

AN4

AM3

VCC_DDR

VCC_DDR

SDQ_B54

SDQ_B55

P25

L32

MDQ_B56

MDQ_B55

MDQ_B54

0.1u/25V/Y5VC117

AN5

AM5

AM6

VCC_DDR

VCC_DDR

SDQ_B56

SDQ_B57

K30

H29

F32

MDQ_B58

MDQ_B57

VCC_DDR

AM7

AM8

AN2

VCC_DDR

VCC_DDR

VCC_DDR

SDQ_B58

SDQ_B59

SDQ_B60

G33

N25

M25

MDQ_B59

MDQ_B60

MDQ_B61

VCC_AGP

AN6

AN7

VCC_DDR

VCC_DDR

VCC_DDR

SDQ_B61

SDQ_B62

SDQ_B63

J29

G32

MDQ_B63

MDQ_B62

P3P6P8

N35

N32

VSS

VSS

SCKE_B0

SCKE_B1

AK19

AF19

AG19

MCKE_B0

MCKE_B1

MCKE_B2

SCS_B0#

VSS

VSS

VSS

SCS_B1#

SCS_B2#

SCS_B3#

SRAS_B#

SCAS_B#

SWE_B#

SMAA_B0

SMAA_B1

SMAA_B2

SMAA_B3

SMAA_B4

SMAA_B5

SMAA_B6

SMAA_B7

SMAA_B8

SMAA_B9

SMAA_B10

SMAA_B11

SMAA_B12

SMAB_B1

SMAB_B2

SMAB_B3

SMAB_B4

SMAB_B5

SBA_B0

SBA_B1

SDM_B0

SDM_B1

SDM_B2

SDM_B3

SDM_B4

SDM_B5

SDM_B6

SDM_B7

SDQS_B0

SDQS_B1

SDQS_B2

SDQS_B3

SDQS_B4

SDQS_B5

SDQS_B6

SDQS_B7

SCMDCLK_B0

SCMDCLK_B0#

SCMDCLK_B1

SCMDCLK_B1#

SCMDCLK_B2

SCMDCLK_B2#

SCMDCLK_B3

SCMDCLK_B3#

SCMDCLK_B4

SCMDCLK_B4#

SCMDCLK_B5

SCMDCLK_B5#

SMYRCOMP

SMYCOMPVOH

SMYCOMPVOL

SMVREF_B

SCKE_B2

SCKE_B3

Intel Springdale-N

AE18

{Priority}

MCKE_B3

2

Its current is 5.1A.

U26

T29

V25

W25

W26

W31

W27

AG31

AJ31

AD27

AE24

AK27

AG25

AL25

AF21

AL23

AJ22

AF29

AL21

AJ20

AE27

AD26

AL29

AL27

AE23

Y25

AA25

AG11

AG15

AE21

AJ28

AC31

U31

M29

J31

AF15

AG13

AG21

AH27

AD29

U30

L27

J30

AG29

AG30

AF17

AG17

N27

N26

AJ30

AH29

AK15

AL15

N31

N30

AA33

R34

R33

AP9

MCKE_B[0..3] 11

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MAB_B1

MAB_B2

MAB_B3

MAB_B4

MAB_B5

MDQM_B0

MDQM_B1

MDQM_B2

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

YRCOMP

YCOMPH

YCOMPL

YVREF

MCS_B#0 11

MCS_B#1 11

MCS_B#2 11

MCS_B#3 11

MRAS_B# 11

MCAS_B# 11

MWE_B# 11

MA_B[0..12] 11

MAB_B[1..5] 11

MBA_B0 11

MBA_B1 11

MDQM_B[0..7] 11

MDQS_B[0..7] 11

MCLK_B0 11

MCLK_B#0 11

MCLK_B1 11

MCLK_B#1 11

MCLK_B2 11

MCLK_B#2 11

MCLK_B3 11

MCLK_B#3 11

MCLK_B4 11

MCLK_B#4 11

MCLK_B5 11

MCLK_B#5 11

103PC108

103PC103

103PC100

0.1u/25V/Y5VC161

C197 X_105P

R230 150RST

R229 150RST

C196 105P

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

VCC_DDR

Micro Star Restricted Secret

Intel Springdale - Memory

MS-7041

Last Revision Date:

Tuesday, December 09, 2003

Sheet

1

Rev

100

829

of

5

4

3

2

1

C158 0.1u/25V/Y5V

C147 0.1u/25V/Y5V

VCC_AGP

P26

P27

P28

P30

P33R1R4

R32T1T3

AE32

VSS

VSS

VSS

VSS

AE35

T6T8T9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF3

AF11

AF14

AF6

AF9

VSS

AD30

VSS

AD33

VSS

VSS

VSS

VSS

AE1

AE10

AE4

AD28

800mV

350mV

800mV

HL_SWING 14

350mV

HL_VREF 14

P9

AE11

VSS

VSS

VSS

VSS

AE12

VSS

VSS

AE13

VSS

VSS

AE25

VSS

VSS

AE26

GAD[0..31]12

D D

C C

GC_BE#[0..3]12

AD_STB012

AD_STB#012

AD_STB112

AD_STB#112

GREQ#12

GGNT#12

ST[0..2]12

RBF#12

WBF#12

GFRAME#12

GIRDY#12

GTRDY#12

GDEVSEL#12

GSTOP#12

GAD0

GAD1

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC_BE#0

GC_BE#1

GC_BE#2

GC_BE#3

ST0

ST1

ST2

RBF#

WBF#

GPAR12

MCH_666

VCC_AGP

VCC_AGP

VCC_AGP

SBA[0..7]12

SB_STB12

SB_STB#12

PIPE#12

DBI_LO12

R187 43.2RST

103PC230

GSWING12

103PC169

AGP_REF12

R246 226

R238 147

R245 113

R253 226RST

R237 147RST

B B

A A

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

GRCOMP

GSWING

C234 0.1u/25V/Y5V

U6C

AE6

GAD0/DVOB_HSYNC

AC11

GAD1/DVOB_VSYNC

AD5

GAD2/DVOB_D1

AE5

GAD3/DVOB_D0

AA10

GAD4/DVOB_D3

AC9

GAD5/DVOB_D2

AB11

GAD6/DVOB_D5

AB7

GAD7/DVOB_D4

AA9

GAD8/DVOB_D6

AA6

GAD9/DVOB_D9

AA5

GAD10/DVOB_D8

W10

GAD11/DVOB_D11

AA11

GAD12/DVOB_D10

W6

GAD13/DVOBC_CLKINT

W9

GAD14/DVOB_FLDSTL

V7

GAD15/MDDC_DATA

AA2

GAD16/DVOC_VSYNC

Y4

GAD17/DVOC_HSYNC

Y2

GAD18/DVOC_BLANK#

W2

GAD19/DVOC_D0

Y5

GAD20/DVOC_D1

V2

GAD21/DVOC_D2

W3

GAD22/DVOC_D3

U3

GAD23/DVOC_D4

T2

GAD24/DVOC_D7

T4

GAD25/DVOC_D6

T5

GAD26/DVOC_D9

R2

GAD27/DVOC_D8

P2

GAD28/DVOC_D11

P5

GAD29/DVOC_D10

P4

GAD30/DVOBC_INTR#

M2

GAD31/DVOC_FLDSTL

Y7

GCBE0/DVOB_D7

W5

GCBE1/DVOB_BLANK#

AA3

GCBE2

U2

GCBE3/DVOC_D5

AC6

GADSTBF0/DVOB_CLK

AC5

GADSTBS0/DVOB_CLK#

V4

GADSTBF1/DVOC_CLK

V5

GADSTBS1/DVOC_CLK#

N6

GREQ

M7

GGNT

N3

GST0

N5

GST1

N2

GST2

R10

GRBF

R9

GWBF

U6

GFRAME/MDVI_DATA

V11

GIRDY/MI2CCLK

AB5

GTRDY/MDVI_CLK

AB4

GDEVSEL/MI2CDATA

W11

GSTOP/MDDC_CLK

AB2

GPAR/ADD_DETECT

H4

GCLKIN

R6

GSBA0#/ADD_ID0

P7

GSBA1#/ADD_ID1

R3

GSBA2#/ADD_ID2

R5

GSBA3#/ADD_ID3

U9

GSBA4#/ADD_ID4

U10

GSBA5#/ADD_ID5

U5

GSBA6#/ADD_ID6

T7

GSBA7#/ADD_ID7

U11

GSBSTBF

T11

GSBSTBS

M4

DBI_HI

M5

DBI_LO

AC2

GRCOMP/DVOBC_RCOMP

AC3

GVSWING

AD2

GVREF

CI_SWING

CI_VREF

H_SWING=(0.8*VCC_AGP)+-2%

HL_SWING

HL_VREF

R254 113RST

C235 0.1u/25V/Y5V

VSS

VSS

AF16

VSS

VSS

AF18

VSS

VSS

T10

AF20

VSS

VSS

T26

AF22

VSS

VSS

T27

VSS

VSS

AF24

VCCP

T28

VSS

VSS

AF25

T30

AF30

VSS

VSS

T33

VSS

VSS

AF33

H_SWING=(0.233*VCC_AGP)+-2%

5

4

T35

VSS

VSS

AG4

U4

AG8

VSS

VSS

U18

VSS

VSS

AG14

V6

U19

U32V3V8V9V10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AG16

AG18

AG20

AG22

VSS

VSS

AG24

VSS

VSS

AG26

VSS

VSS

AG28

V17

AG32

VSS

VSS

V19

VSS

VSS

AG35

V26

AH3

V27

VSS

VSS

AH6

V28

V30W4W17

VSS

VSS

VSS

VSS

AH12

AH10

VSS

VSS

V33

VSS

VSS

AH14

W18

W32Y6Y8Y9Y26

VSS

VSS

VSS

VSS

VSS

VSS

AH16

AH18

AH20

AH22

VSS

VSS

Y3

VSS

VSS

AH24

VSS

VSS

AH30

VSS

VSS

AH33

Y28

Y30

Y33

Y35

Y27

AA1

AA4

AA32

AB10

AB26

AC1

AC4

AC32

AB28

VSS

VSS

AL32

AB30

VSS

VSS

AM9

AB33

VSS

VSS

AM11

VSS

VSS

AM13

VSS

VSS

AM15

VSS

VSS

AM17

AC35

VSS

VSS

AM19

AD3

VSS

VSS

AM21

AD6

VSS

VSS

AM23

AD8

VSS

VSS

AM25

AD9

VSS

VSS

AM27

AD10

AM29

AB27

AB3

AB6

AB8

VSS

VSS

AK12

VSS

VSS

AK14

AK16

VSS

VSS

VSS

VSS

AK18

VSS

VSS

AK20

VSS

VSS

AK22

AB9

VSS

VSS

AK24

VSS

VSS

AK26

VSS

VSS

AK28

VSS

VSS

AL1

Y10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK3

AJ9

AJ32

AJ35

AK8

AK10

VSS

VSS

AJ1

AJ4

Springdale Decoupling Capacitors

VCCP

All caps trace length is less than 100mils.

C81

X_0.1u/25V/Y5V

C82

0.1u/25V/Y5V

C85

X_105P/0805

C88

X_105P/0805

C217

0.1u/25V/Y5V

C175

X_0.1u/25V/Y5V

Close CPU side of GMCH Close AG1 and Y1 of GMCH Close E35, R35, AA35, AL35, AR31, AR21 and AR15 of GMCH

3

VCC_DDRVCC_DDR VCC_DDRVCC_AGP

C203

X_0.1u/25V/Y5V

C83

0.1u/25V/Y5V

C165

0.1u/25V/Y5V

C92

0.1u/25V/Y5V

L1L5Y1J1J2J3K2K3K4K5J4J5L4L2L3

VSS

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VSS

VSS

VSS

AN12

VSS

AN14

VSS

AN16

VSS

AN18

AN20

AN22

VSS

AN24

AN26

VSS

VSS

VSS

AM35

AN10

C170

X_0.1u/25V/Y5V

VCC_AGP

VCC_AGP

VCC_AGP

VSS

VSS

VSS

AN28

AN30

AN32

C185

0.1u/25V/Y5V

C131

0.1u/25V/Y5V

VCC_AGP

VCC_AGP

VCC_AGP

VSS

VSS

VSS

AR9

AR11

2

AG1

VCC_AGP

VCCA_AGP

HI_STRF

HI_STRS

HI_RCOMP

HI_SWING

HI_VREF

CI_RCOMP

CI_SWING

CI_VREF

DREFCLK

DDCA_CLK

DDCA_DATA

GREEN#

VCC_DAC

VCC_DAC

VCCA_DPLL

VCCA_DAC

VSSA_DAC

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

VSS

VSS

VSS

AR13

AR16

AR20

VTTVCC_DDR

Y11

HI0

HI1

HI2

HI3

VCCA_AGP

HI4

HI5

HI6

HI7

HI8

HI9

HI10

CI0

CI1

CI2

CI3

CI4

CI5

CI6

CI7

CI8

CI9

CI10

CISTRF

CISTRS

VSYNC

HSYNC

BLUE

BLUE#

GREEN

RED

RED#

REFSET

EXTTS#

VSS

VSS

VSS

VSS

VSS

AR23

Intel Springdale-N

{Priority}

C114

X_0.1u/25V/Y5V

C115

0.1u/25V/Y5V

AF5

AG3

AK2

AG5

AK5

AL3

AL2

AL4

AJ2

AH2

AJ3

AH5

AH4

AD4

AE3

AE2

AK7

AH7

AD11

AF7

AD7

AC10

AF8

AG7

AE9

AH9

AG6

AJ6

AJ5

AG2

AF2

AF4

G4

F2

H3

E2

G3

H7

G6

H6

G5

F4

E4

D2

G1

G2

B3

C2

D3

AP8

AG9

AG10

AN35

AP34

AR1

AR25

AR27

AR29

AR32

CI_RCOMP

VCCA_DPLL

C479

HL0

HL1GAD2

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

HL_COMP

HL_SWING

HL_VREF

MCH_DDC_CLK

MCH_DDC_DATA

VSYNC

HSYNC

VGA_BLUE

R619 0

0

For 865PE

C129

X_0.1u/25V/Y5V

R194 52.3RST

R239 52.3RST

CI_SWING

CI_VREF

VGA_GREEN

VGA_RED

R148 X_0

VCCA_DPLL

For 865PE

VCC_AGP

HL[0..10] 14

HI_RCOMP Calculation

R=[(1.5V-08V)/0.8V]*60ohm=52.5ohm

HL_STRF 14

HL_STRS 14

103PC223

VCC_AGP

103PC224

VCC_AGP

103PC225

103PC167

DOT_48 6

MCH_DDC_CLK 23

MCH_DDC_DATA 23

VSYNC 23

HSYNC 23

VGA_BLUE 23

VGA_GREEN 23

VGA_RED 23

VCC3

C478

X_0.01u

VCCA_DAC

ESR is 0.1mohm to GMCHI=35mA

CP21 X_COPPER

L27 X_100nH

C482 X_10U/1206C481 0

Micro Star Restricted Secret

Title

Intel Springdale - AGP & LAN

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

L26 X_100n

C480

X_10U/1206

DPLL

MS-7041

1

VCC_AGP

R621 X_1

Last Revision Date:

Tuesday, December 09, 2003

Sheet

929

VCC_AGP

Rev

100

of

5

4

3

2

1

DDR DIMM1 DDR DIMM2

MA_A[0..12]8

D D

MBA_A08

MBA_A18

MCS_A#08

MCS_A#18

MRAS_A#8

MCAS_A#8

MWE_A#8

MDQS_A[0..7]8

C C

B B

A A

MDQM_A[0..7]8

MCKE_A08

MCKE_A18

SMBCLK_ISO6,11,21

SMBDATA_ISO6,11,21

MCLK_A18

MCLK_A#18

MCLK_A08

MCLK_A#08

MCLK_A28

MCLK_A#28

MA_A0

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

MBA_A0

MBA_A1

MRAS_A#

MCAS_A#

MWE_A#

MDQS_A0

MDQS_A1

MDQS_A2

MDQS_A3

MDQS_A4

MDQS_A5

MDQS_A6

MDQS_A7

MDQM_A0

MDQM_A1

MDQM_A2

MDQM_A3

MDQM_A4

MDQM_A5

MDQM_A6

MDQM_A7

VCC3 VCC3

VCC_DDR VCC_DDR

DIMM1

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

157

158

71

163

154

65

63

5

14

25

36

56

67

78

86

47

97

107

119

129

149

159

169

177

140

44

45

49

51

134

135

142

144

21

111

92

91

181

182

183

16

17

137

138

76

75

82

184

7

38

46

70

85

108

120

148

168

81

89

93

100

116

124

132

139

145

152

160

176

DIMM-D184-BK

SIGNALS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/NC

A13/NC

BA0

BA1

NC/BA2

CS0#

CS1#

NC/CS2#

NC/CS3#

RAS#

CAS#

WE#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQM0/DQS9

DQM1/DQS10

DQM2/DQS11

DQM3/DQS12

DQM4/DQS13

DQM5/DQS14

DQM6/DQS15

DQM7/DQS16

DQM8/DQS17

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

CKE0

CKE1

SCL

SDA

SA0

SA1

SA2

CK0/NC

CK0#/NC

CK1/CK0

CK1#/CK0#

CK2/NC

CK2#/NC

ID_VDD

SPD_VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

POWER

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

FETEN/NC

NC/RESET#

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

MDQ_A0

2

MDQ_A1

4

MDQ_A2

6

MDQ_A3

8

MDQ_A4

94

MDQ_A5

95

MDQ_A6

98

MDQ_A7

99

MDQ_A8

12

MDQ_A9

13

MDQ_A10

19

MDQ_A11

20

MDQ_A12

105

MDQ_A13

106

MDQ_A14

109

MDQ_A15

110

MDQ_A16

23

MDQ_A17

24

MDQ_A18

28

MDQ_A19

31

MDQ_A20

114

MDQ_A21

117

MDQ_A22

121

MDQ_A23

123

MDQ_A24

33

MDQ_A25

35

MDQ_A26

39

MDQ_A27

40

MDQ_A28

126

MDQ_A29

127

MDQ_A30

131

MDQ_A31

133

MDQ_A32

53

MDQ_A33

55

MDQ_A34

57

MDQ_A35

60

MDQ_A36

146

MDQ_A37

147

MDQ_A38

150

MDQ_A39

151

MDQ_A40

61

MDQ_A41

64

MDQ_A42

68

MDQ_A43

69

MDQ_A44

153

MDQ_A45

155

MDQ_A46

161

MDQ_A47

162

MDQ_A48

72

MDQ_A49

73

MDQ_A50

79

MDQ_A51

80

MDQ_A52

165

MDQ_A53

166

MDQ_A54

170

MDQ_A55

171

MDQ_A56

83

MDQ_A57

84

MDQ_A58

87

MDQ_A59

88

MDQ_A60

174

MDQ_A61

175

MDQ_A62

178

MDQ_A63

179

9

NC

101

NC

102

NC

173

NC

1

90

WP

C178

103

0.1u/25V/Y5V

10

15

22

30

54

62

77

96

104

112

128

136

143

156

164

172

180

3

11

18

26

34

42

50

58

66

74

VCC_DDR

VCC_DDR

MDQ_A[0..63] 8

R211

75RST

R207

75RST

VCC_DDR

MAB_A[1..5]8

CB39

0.1u/25V/Y5V

CB6

X_0.1u/25V/Y5V

CB13

0.1u/25V/Y5V

CB18

X_0.1u/25V/Y5V

CB25

0.1u/25V/Y5V

CB56

0.1u/25V/Y5V

CB61

X_0.1u/25V/Y5V

CB1

0.1u/25V/Y5V

CB66

0.1u/25V/Y5V

MCS_A#28

MCS_A#38

MCKE_A28

MCKE_A38

MCLK_A48

MCLK_A#48

MCLK_A38

MCLK_A#38

MCLK_A58

MCLK_A#58

MA_A0

MAB_A1

MAB_A2

MAB_A3

MAB_A4

MAB_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

MBA_A0

MBA_A1

MRAS_A#

MCAS_A#

MWE_A#

MDQS_A0

MDQS_A1

MDQS_A2

MDQS_A3

MDQS_A4

MDQS_A5

MDQS_A6

MDQS_A7

MDQM_A0

MDQM_A1

MDQM_A2

MDQM_A3

MDQM_A4

MDQM_A5

MDQM_A6

MDQM_A7

SMBCLK_ISO

SMBDATA_ISO

VCC_DDR

ADDR.=1010000B ADDR.=1010001B

5

4

DIMM2

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

157

158

71

163

154

65

63

5

14

25

36

56

67

78

86

47

97

107

119

129

149

159

169

177

140

44

45

49

51

134

135

142

144

21

111

92

91

181

182

183

16

17

137

138

76

75

82

184

7

38

46

70

85

108

120

148

168

81

89

93

100

116

124

132

139

145

152

160

176

DIMM-D184-BK

3

SIGNALS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/NC

A13/NC

BA0

BA1

NC/BA2

CS0#

CS1#

NC/CS2#

NC/CS3#

RAS#

CAS#

WE#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQM0/DQS9

DQM1/DQS10

DQM2/DQS11

DQM3/DQS12

DQM4/DQS13

DQM5/DQS14

DQM6/DQS15

DQM7/DQS16

DQM8/DQS17

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

CKE0

CKE1

SCL

SDA

SA0

SA1

SA2

CK0/NC

CK0#/NC

CK1/CK0

CK1#/CK0#

CK2/NC

CK2#/NC

ID_VDD

SPD_VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

POWER

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

FETEN/NC

NC/RESET#

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

MDQ_A0

2

MDQ_A1

4

MDQ_A2

6

MDQ_A3

8

MDQ_A4

94

MDQ_A5

95

MDQ_A6

98

MDQ_A7

99

MDQ_A8

12

MDQ_A9

13

MDQ_A10

19

MDQ_A11

20

MDQ_A12

105

MDQ_A13

106

MDQ_A14

109

MDQ_A15

110

MDQ_A16

23

MDQ_A17

24

MDQ_A18

28

MDQ_A19

31

MDQ_A20

114

MDQ_A21

117

MDQ_A22

121

MDQ_A23

123

MDQ_A24

33

MDQ_A25

35

MDQ_A26

39

MDQ_A27

40

MDQ_A28

126

MDQ_A29

127

MDQ_A30

131

MDQ_A31

133

MDQ_A32

53

MDQ_A33

55

MDQ_A34

57

MDQ_A35

60

MDQ_A36

146

MDQ_A37

147

MDQ_A38

150

MDQ_A39

151

MDQ_A40

61

MDQ_A41

64

MDQ_A42

68

MDQ_A43

69

MDQ_A44

153

MDQ_A45

155

MDQ_A46

161

MDQ_A47

162

MDQ_A48

72

MDQ_A49

73

MDQ_A50

79

MDQ_A51

80

MDQ_A52

165

MDQ_A53

166

MDQ_A54

170

MDQ_A55

171

MDQ_A56

83

MDQ_A57

84

MDQ_A58

87

MDQ_A59

88

MDQ_A60

174

MDQ_A61

175

MDQ_A62

178

MDQ_A63

179

9

NC

101

NC

102

NC

173

NC

DDR_VREF1DDR_VREF1

1

90

WP

C179

103

0.1u/25V/Y5V

10

15

22

30

54

62

77

96

104

112

128

136

143

156

164

172

180

3

11

18

26

34

42

50

58

66

74

VCC_DDR

VTT_DDR VTT_DDR VCC_DDR

2

DDR Terminational Resisito rs

VTT_DDR

VTT_DDR

MDQ_A9

MDQ_A8

MDQ_A3

MDQ_A7

MDQ_A6

MDQ_A2

MDQM_A0

MDQS_A0

MDQM_A1

MDQ_A13

MDQS_A1

MDQ_A12

MDQS_A2

MDQ_A21

MDQ_A17

MDQ_A16

MDQ_A22

MDQ_A18

MDQM_A2

MDQM_A3

MDQS_A3

MDQ_A29

MDQ_A25

MDQ_A31

MDQ_A27

MDQ_A26

MDQ_A30

MDQ_A38

MDQM_A4

MDQ_A34

MDQS_A4

MDQ_A40

MDQ_A44

MDQ_A35

MDQ_A39

MDQ_A28

MDQ_A24

MDQ_A19

MDQ_A23

MDQ_A1

MDQ_A5

MDQ_A4

MDQ_A0

MDQ_A47

MDQ_A46

MDQ_A43