5

4

3

2

1

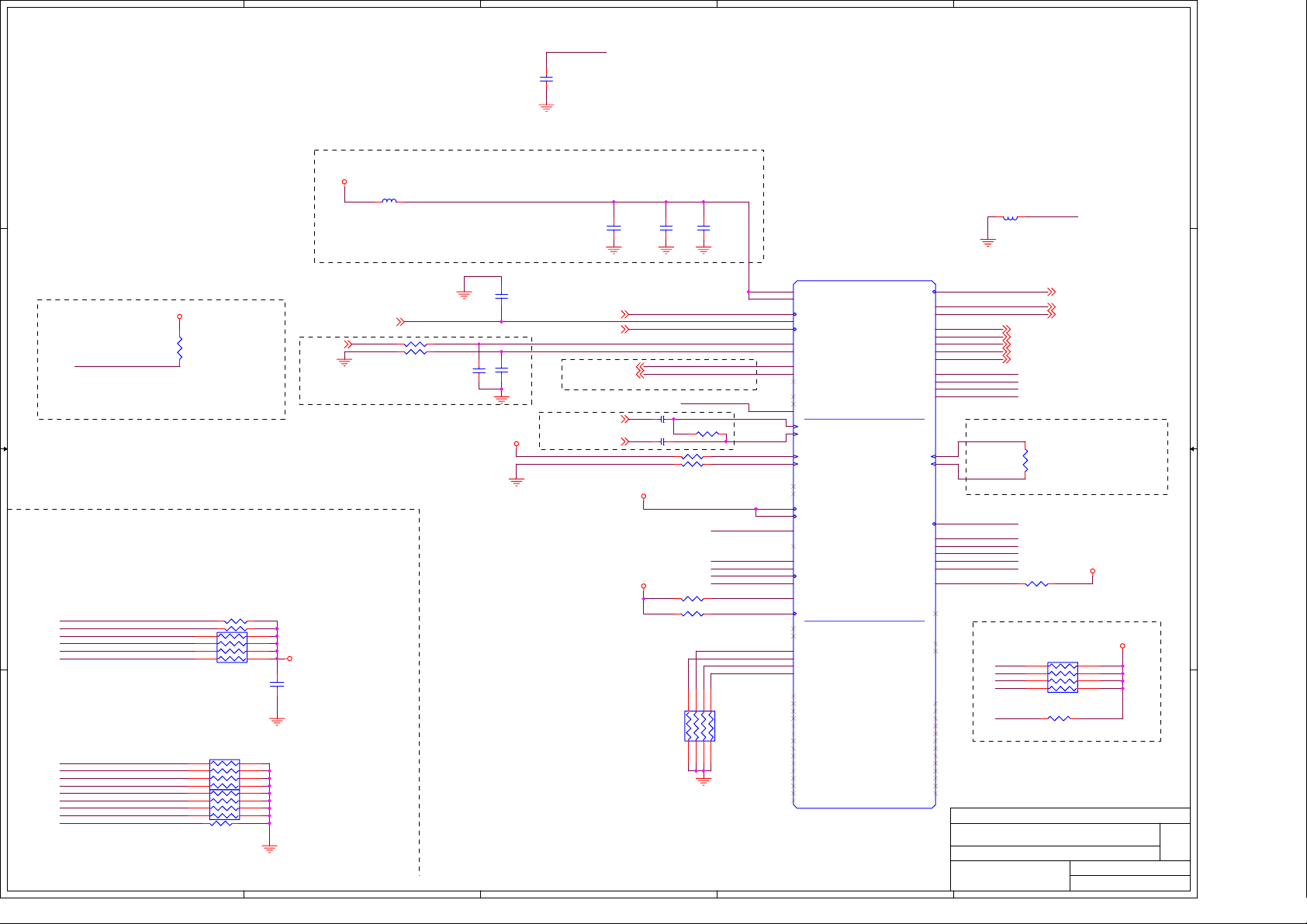

MS-7032 VER:10A ATX

PageTitle

Cover Sheet 1

*AMD PGA 754 K8-Processor (DDR 400)

D D

*VIA K8M800 /K8T800 Pro

*VIA VT8237

(AGP 8X / VLink 8X)

*Winbond 83627THF LPC I/O

*RTL 8110S Giga/8110SB Giga/ 8201BL/

8201CL 100/10 Bit LAN Support

*USB 2.0 support (integrated into VT8237)

*Vcore Jumpless support

*ALC655 6 channel S/W Audio

C C

*DDR DIMM * 2

*AGP SLOT * 1 ( 8X )

*PCI SLOT * 5

B B

A A

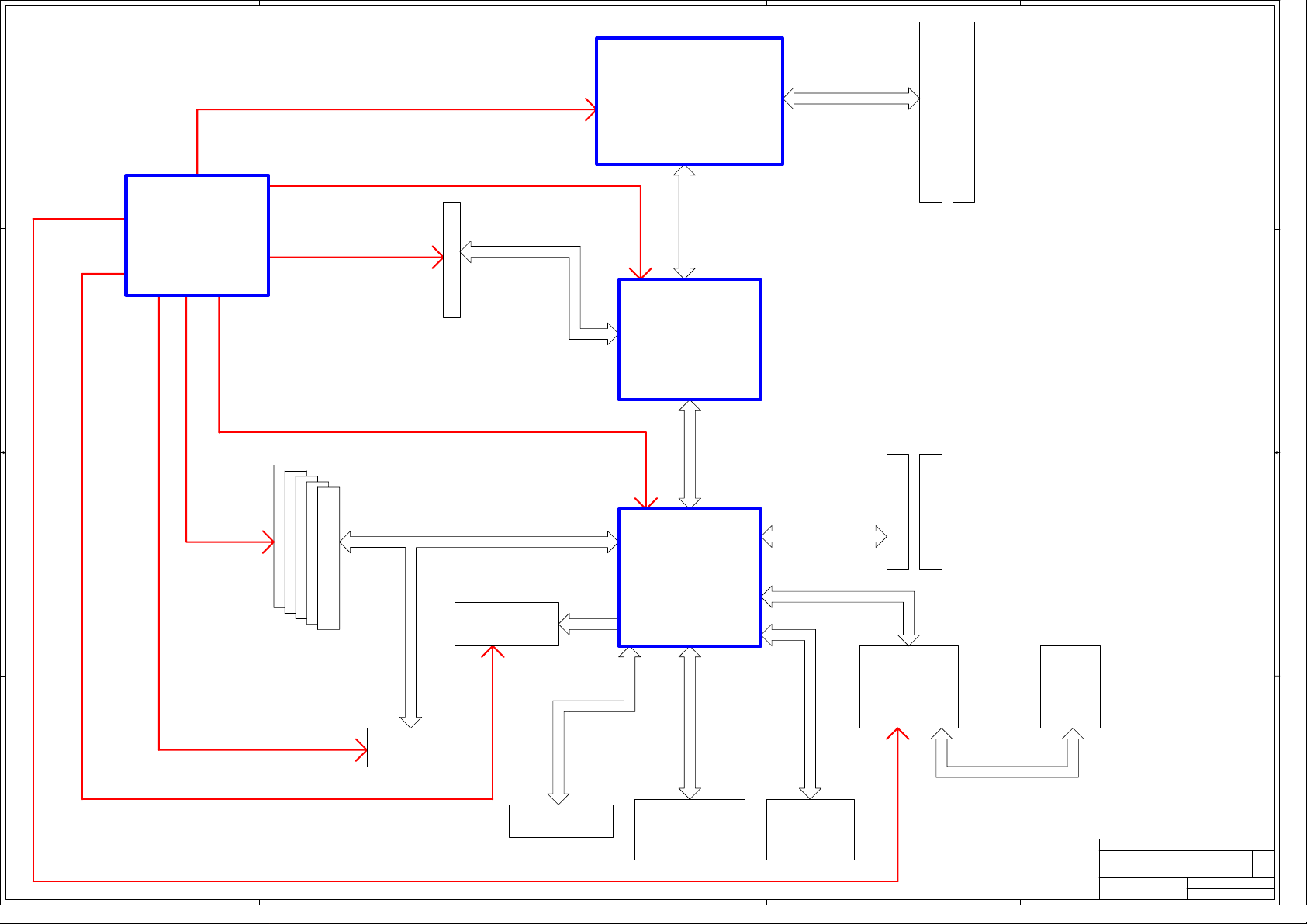

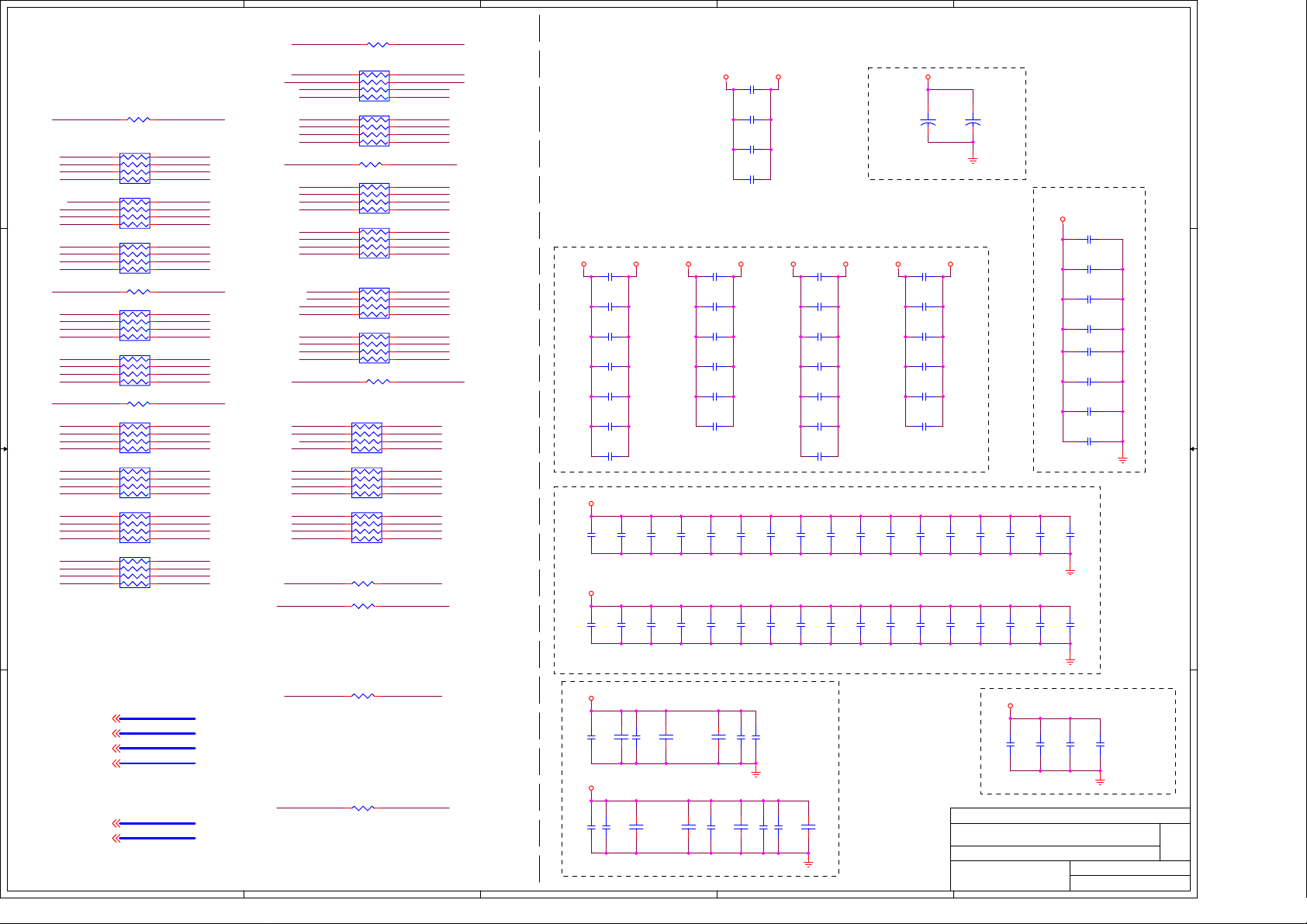

Block Diagram 2

GPIO SPEC

3

AMD K8 -> 754 PGA Socket 4,5,6

Clock Synthesizer

System Memory

DDR DIMM 1 & 2

DDR Terminations R & C

DDR Damping R & Bypass Cap.

NB VIA K8T800A/K8M800 (HT)

K8 Vcore

AGP SLOT 8X

VT8237

PCI Connectors * 5

ALC650/ALC655 6 channel S/ W A udi o

IDE ATA 66/100 Connectors * 2

Front and Rear USB Port

LPC I/O W83697HF & Floppy

Hardware monitor & FAN

Keyboard/Mouse Connectors

LPT/COM Port

10/100 LAN & VGA

Giga-Bit LAN RTL8110S

ACPI Power CONTROLLER (MS-6)

VOLTAGE REGULATOR & ROM

Front Panel & POWER OK CIRCUIT

Decoupling Cap.

Power Sequence

History

OPTION PARTS

7

8

9

10

11,12,13

14

15

16,17,18

19,20,21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

Cover Sheet

MS-7032

1

Last Revision Date:

Monday, June 14, 2004

Sheet

Rev

10A

of

137

5

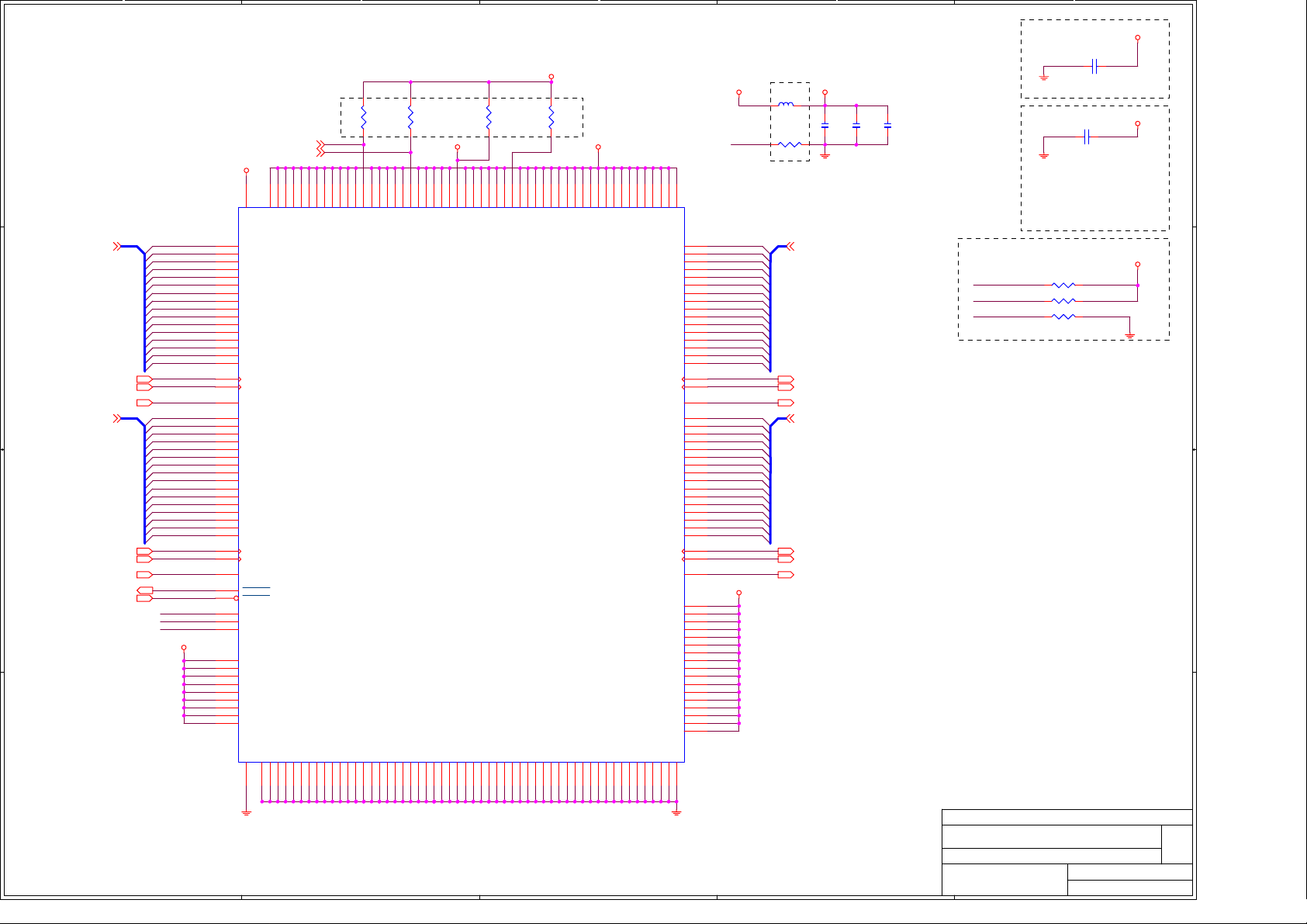

Block Diagram

4

3

2

1

D D

CPUCLK+ & CPUCLK-(100/133/166/200)

AMD K8 Socket 754

HCLK+ & HCLK-(100/133/166/200) / GCLK(66)

DDR400

VIA

HT

VLINK

Dual ATA 100/133

IDE Slot

==>ATA66,100,133 *2

SYSTEM CLOCK

Synthesizer

C C

AGPCLK(66)

A

G

P

AGP 8X /Fast Write

S

L

O

T

K8T800/K8T800A

VCLK(66) / OSC(14) / PCISB(33) / USBCLK(48) / APICCLK(14)

PCICLK[0~5]

PCI-33

DDR * 2

B B

GLANCLK(33)

A A

AC_14(14)

SIOPCLK(33)/SIO48M(48)

5

5 PCI Slots

AC97

Giga Bit LAN

RTL8110S

AC97 => S/W Audio

ALC655 / 6 channel

SERIAL ATA *2

4

VT8237

Dual USB 1.1 OHCI

/2.0 EHCI 8 Ports

==> Front-Port *4 ,

Back-Port *4

3

USB

LPC BUS

MII

10/100 LAN

RTL8201BL

SUPER I/O

W83697HF

2

X BUS

ROM

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

1

Block Diagram

MS-7032

Last Revision Date:

Sheet

Rev

10A

Monday, June 14, 2004

237

of

5

4

3

2

1

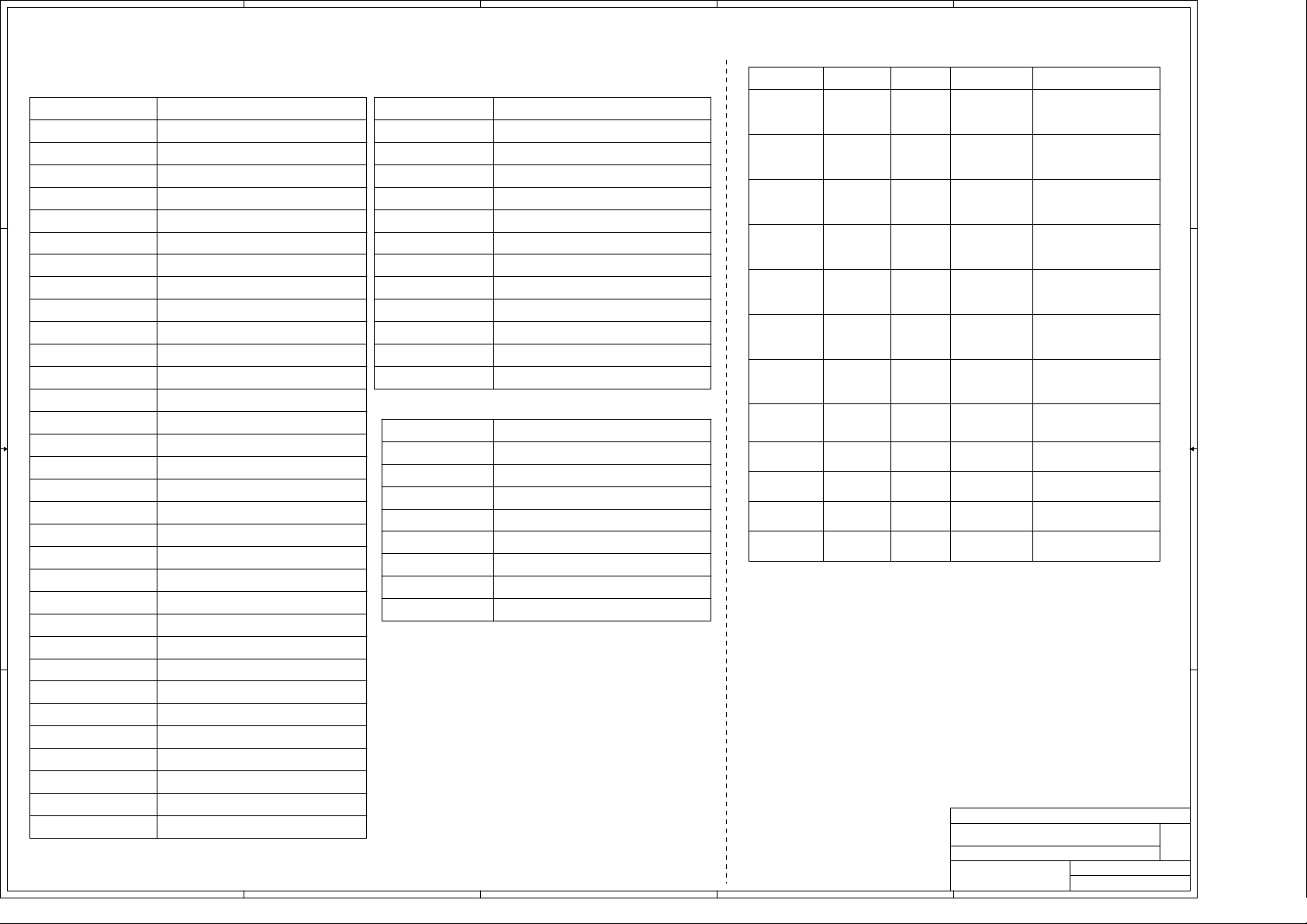

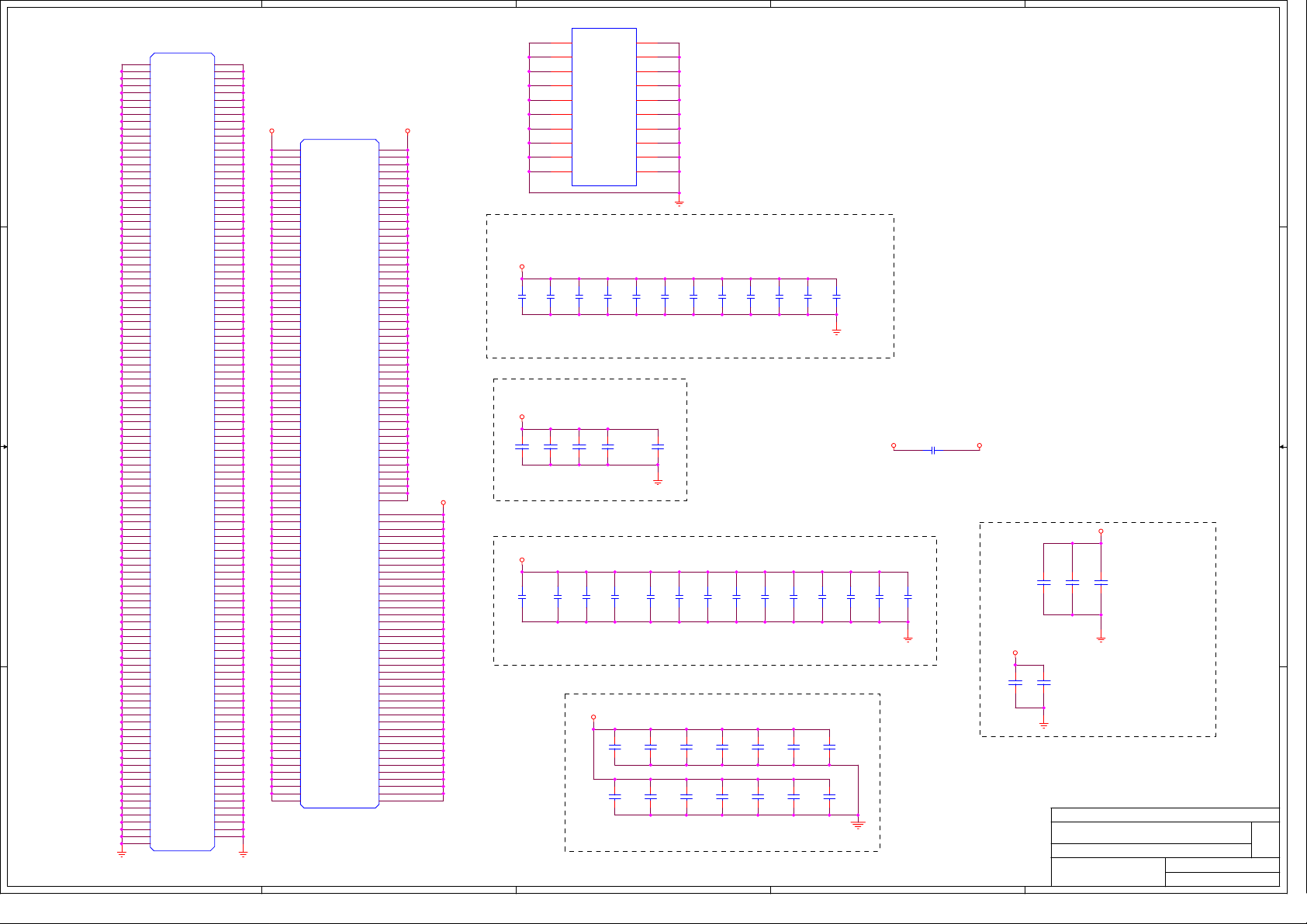

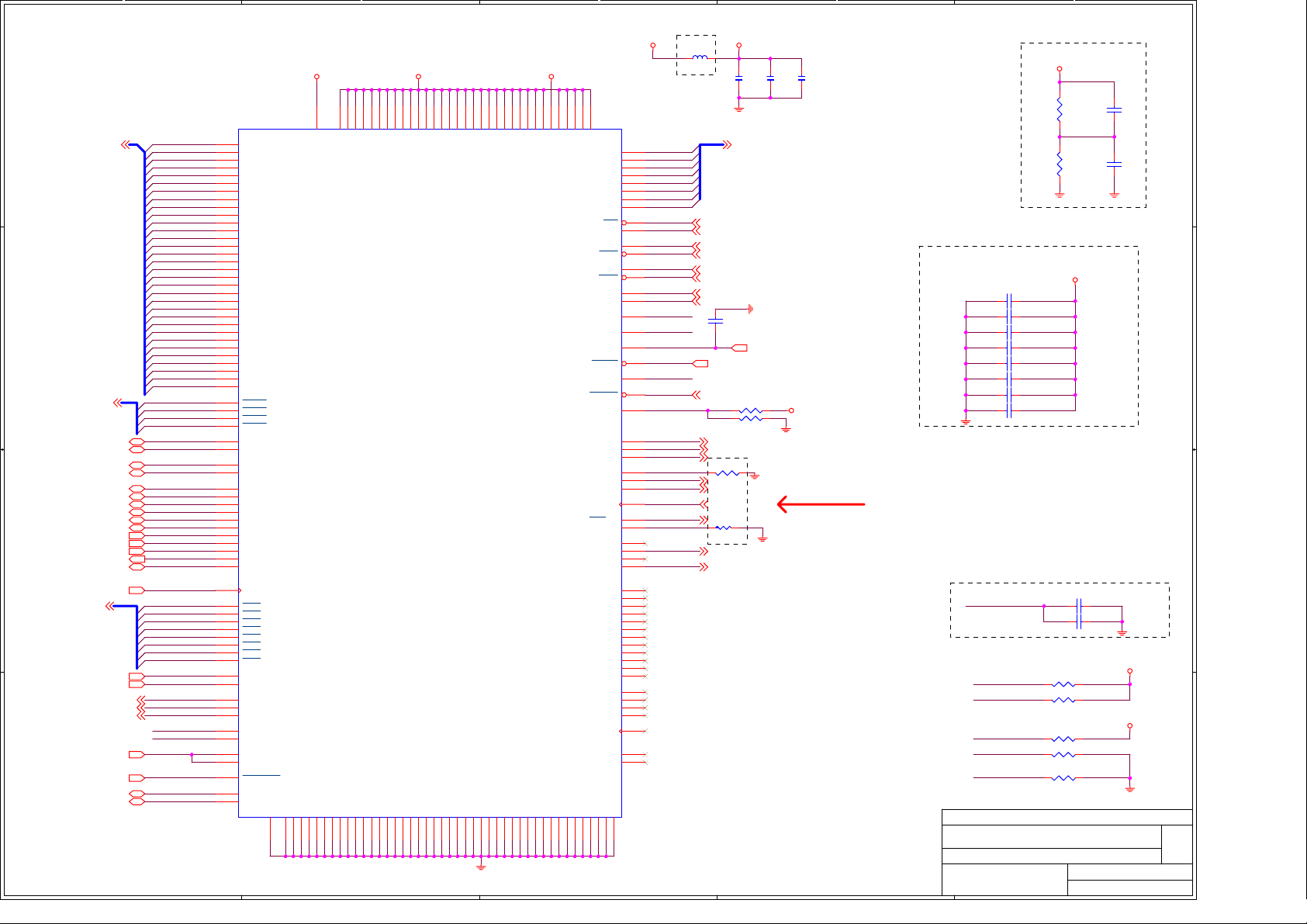

GPIO FUNCTION

VT8237 GPIO Function Define

PIN NAME

D D

GPO0 (VSUS33)

GPO1/SUSA#(VSUS33)

GPO2/SUSB#(VSUS33)

GPO3/SUSST1#(VSUS33)

GPO4/SUSCLK(VSUS33)

GPO5/CPUSTP#

GPO6/PCISTP#

GPO7/SLP#

GPO8/GPI8/IPBIN0

GPO9/GPI9/IPBIN1

C C

GPO10/GPI10/IPBRDFR

GPO11/GPI11/IPBRDCK

GPO12/GPI12/INTE#

GPO13/GPI13/INTF#

GPO14/GPI14/INTG#

GPO15/GPI15/INTH#

GPO16/SA16/STRAP

GPO17/SA17/STRAP

GPO18/SA18/STRAP

GPO19/SA19/STRAP

B B

GPO20/GPI20

/ACSDIN2/PCS0#/EI

GPO21/GPI21/ACSDIN3

/PCS1#/SLPBTN#

GPO22/GPI22/IOR#

GPO23/GPI23/DPSLP

GPO24/GPI24/GPIOA

GPO25/GPI25/GPIOC

GPO26/GPI26/SMBDT2

(VSUS33)

GPO27/GPI27/SMBCK2

(VSUS33)

GPO28/GPI28/

VIDSEL

GPO29/GPI29/

A A

VRDSLP

GPO30/GPI30/GPIOD

GPO31/GPI31/GPIOE

5

NA

NA

SUSB#

SUSST#

NA (Exteranl Pull up to 3VDUAL)

NA (Exteranl Pull up to VCC3)

NA (Exteranl Pull up to VCC3)

LDTSTOP#

NA

NA

NA

NA

VSET0

VSET1

VSET2

NA

LDT Freq Strapping Bit0

LDT Freq Strapping Bit1

LDT Width (Low=8 Bit)

Fast Command (Low=Disable)

POWERF1

POWERF2

NA

ROMLOCK

NA

NA

SMBDATA2/Slave SMBUS

SMBCLK2/Slave SMBUS

NA

NA

NA

NA

PIN NAME Function defineFunction define

GPI0

GPI1

GPI2/EXTSMI#

GPI3/RING#

GPI4/LID#

GPI5/BATLOW#

GPI6/AGPBZ#

GPI7/REQ#5

GPI16/INTRUDER#

GPI17/CPUMISS

GPI18/AOLGP1/THRM#

GPI19/IORDY

(Exteranl Pull up to VBAT)NA

ATADET0=>Detect IDE1 ATA100/66

EXTSMI#

RING#

ATADET1=>Detect IDE2 ATA100/66

(Exteranl Pull up to 3VDUAL)

NA

POWERF3

(Exteranl Pull up to 3VDUAL)

NA

(Exteranl Pull up to VBAT)

NA

(Exteranl Pull up to 3VDUAL)

NA

THRM#

(Exteranl Pull up to VCC3)NA

S/IO GPIO Function Define

PIN NAME Function define

GPBX/GP13

GPAY/GP15

GPAS1/GP10

GPAS2/GP17

GPAX/GP12

GPBY/GP14

GPBS1/GP11

GPBS2/GP16

4

LED#4

LED#2

LED1

LED4

LED#3

LED#1

LED2

LED3

3

PCI Routing

DEVICES

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

PCI SLOT 5

Giga-Bit

LAN

INT#

INT#A

INT#B

INT#C

INT#D

INT#B

INT#C

INT#D

INT#A

INT#C

INT#D

INT#A

INT#B

INT#D

INT#A

INT#B

INT#C

INT#B

INT#C

INT#D

INT#A

INT#A AD22 GLAN_PCLK

2

IDSEL

AD16

AD17

AD18

AD19

AD21

REQ#/GNT#

PREQ#6

PGNT#6

PREQ#3

PGNT#3

PREQ#4

PGNT#4

PREQ#7

PGNT#7

PREQ#8

PGNT#8

PREQ#1

PGNT#1

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

CLOCK

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

GPIO Spec.

MS-7032

Last Revision Date:

Monday, June 14, 2004

Sheet

337

1

Rev

10A

of

5

4

3

2

1

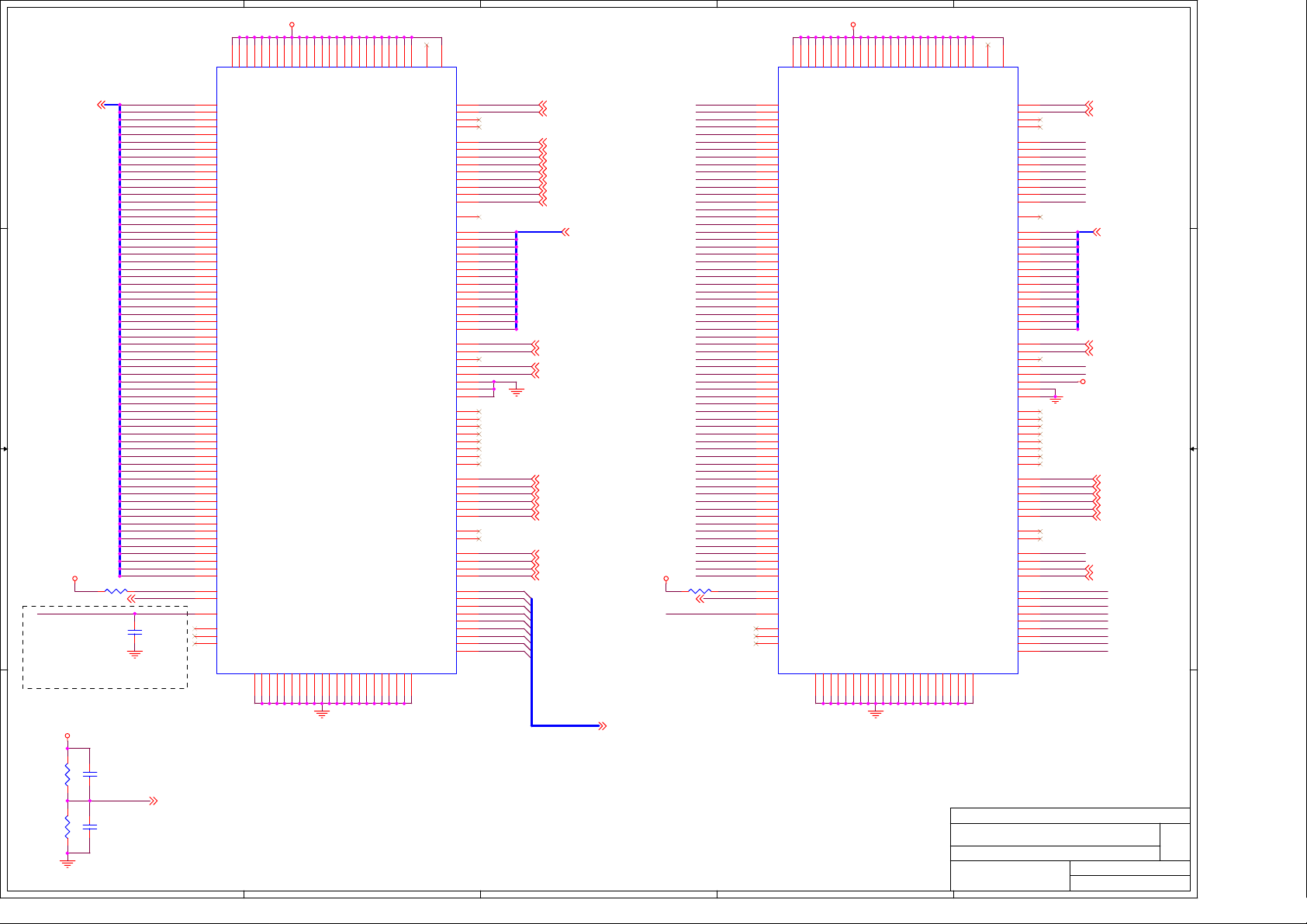

MEMZN

MEMZP

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

DM8

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

-MDQS8

-MDQS7

-MDQS6

-MDQS5

-MDQS4

-MDQS3

-MDQS2

-MDQS1

-MDQS0

C38

X_C1000P50N

AE13

VTT_SENSE

AG12

MEMVREF1

D14

MEMZN

C14

MEMZP

A16

MEMDATA63

B15

MEMDATA62

A12

MEMDATA61

B11

MEMDATA60

A17

MEMDATA59

A15

MEMDATA58

C13

MEMDATA57

A11

MEMDATA56

A10

MEMDATA55

B9

MEMDATA54

C7

MEMDATA53

A6

MEMDATA52

C11

MEMDATA51

A9

MEMDATA50

A5

MEMDATA49

B5

MEMDATA48

C5

MEMDATA47

A4

MEMDATA46

E2

MEMDATA45

E1

MEMDATA44

A3

MEMDATA43

B3

MEMDATA42

E3

MEMDATA41

F1

MEMDATA40

G2

MEMDATA39

G1

MEMDATA38

L3

MEMDATA37

L1

MEMDATA36

G3

MEMDATA35

J2

MEMDATA34

L2

MEMDATA33

M1

MEMDATA32

W1

MEMDATA31

W3

MEMDATA30

AC1

MEMDATA29

AC3

MEMDATA28

W2

MEMDATA27

Y1

MEMDATA26

AC2

MEMDATA25

AD1

MEMDATA24

AE1

MEMDATA23

AE3

MEMDATA22

AG3

MEMDATA21

AJ4

MEMDATA20

AE2

MEMDATA19

AF1

MEMDATA18

AH3

MEMDATA17

AJ3

MEMDATA16

AJ5

MEMDATA15

AJ6

MEMDATA14

AJ7

MEMDATA13

AH9

MEMDATA12

AG5

MEMDATA11

AH5

MEMDATA10

AJ9

MEMDATA9

AJ10

MEMDATA8

AH11

MEMDATA7

AJ11

MEMDATA6

AH15

MEMDATA5

AJ15

MEMDATA4

AG11

MEMDATA3

AJ12

MEMDATA2

AJ14

MEMDATA1

AJ16

MEMDATA0

R1

MEMDQS17

A13

MEMDQS16

A7

MEMDQS15

C2

MEMDQS14

H1

MEMDQS13

AA1

MEMDQS12

AG1

MEMDQS11

AH7

MEMDQS10

AH13

MEMDQS9

T1

MEMDQS8

A14

MEMDQS7

A8

MEMDQS6

D1

MEMDQS5

J1

MEMDQS4

AB1

MEMDQS3

AJ2

MEMDQS2

AJ8

MEMDQS1

AJ13

MEMDQS0

U7B

RSVD_MEMADDA15

RSVD_MEMADDA14

RSVD_MEMADDB15

RSVD_MEMADDB14

MEMORY INTERFACE

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

4

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

VTT_DDR_SUS

MCKE0

MCKE1

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

-MCS3

-MCS2

-MCS1

-MCS0

-MSRASA

-MSCASA

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

MCKE0 8,9

MCKE1 8,9

MEMCLK_H7 8,9

MEMCLK_L7 8,9

MEMCLK_H6 8,9

MEMCLK_L6 8,9

MEMCLK_H5 8,9

MEMCLK_L5 8,9

MEMCLK_H4 8,9

MEMCLK_L4 8,9

MEMCLK_H1 8,9

MEMCLK_L1 8,9

MEMCLK_H0 8,9

MEMCLK_L0 8,9

-MCS3 8,9

-MCS2 8,9

-MCS1 8,9

-MCS0 8,9

-MSRASA 8,9

-MSCASA 8,9

-MSWEA 8,9

MEMBANKA1 8,9

MEMBANKA0 8,9

MAA[13..0] 8,9

-MSRASB 8,9

-MSCASB 8,9

-MSWEB 8,9

MEMBAKB1 8,9

MEMBAKB0 8,9

MAB[13..0] 8,9

CADIP[0..15]11

CLKIP111

CLKIN111

CLKIP011

CLKIN011

CTLIP011

CTLIN011

3

VLDT0

R51 49.9R1%

R56 49.9R1%

VREF routed as 40~50 mils trace wide ,

Space>25 mils

C29

D D

C C

B B

DDR_VREF8

VDD_25_SUS

Place near CPU in 1" ,

Routed => 5:10/Trace:Space ,

Same Length

R95 15R1%

R98 15R1%

C1000P50X

MD[63..0]10

DM[8..0]10

A A

-MDQS[8..0]10

5

VDD_12_A

X_C0.22U16Y

VDD_12_A

CADIN15

CADIN14

CADIN13

CADIN12

CADIN11

CADIN10

CADIN9

CADIN8

CADIN7

CADIN6

CADIN5

CADIN4

CADIN3

CADIN2

CADIN1

CADIN0

C149

CADIP15

CADIP14

CADIP13

CADIP12

CADIP11

CADIP10

CADIP9

CADIP8

CADIP7

CADIP6

CADIP5

CADIP4

CADIP3

CADIP2

CADIP1

CADIP0

CTLIP1

CTLIN1

C0.22U16Y

C134

D29

D27

D25

C28

C26

B29

B27

T25

R25

U27

U26

V25

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

T27

T28

V29

U29

V27

V28

Y29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

Y25

W25

Y27

Y28

R27

R26

T29

R29

C136

C0.22U16Y

U7A

N12-7540020-A10

VLDT0_A6

VLDT0_A5

VLDT0_A4

VLDT0_A3

VLDT0_A2

VLDT0_A1

VLDT0_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

2

X_C0.22U16Y

C147

C0.22U16Y

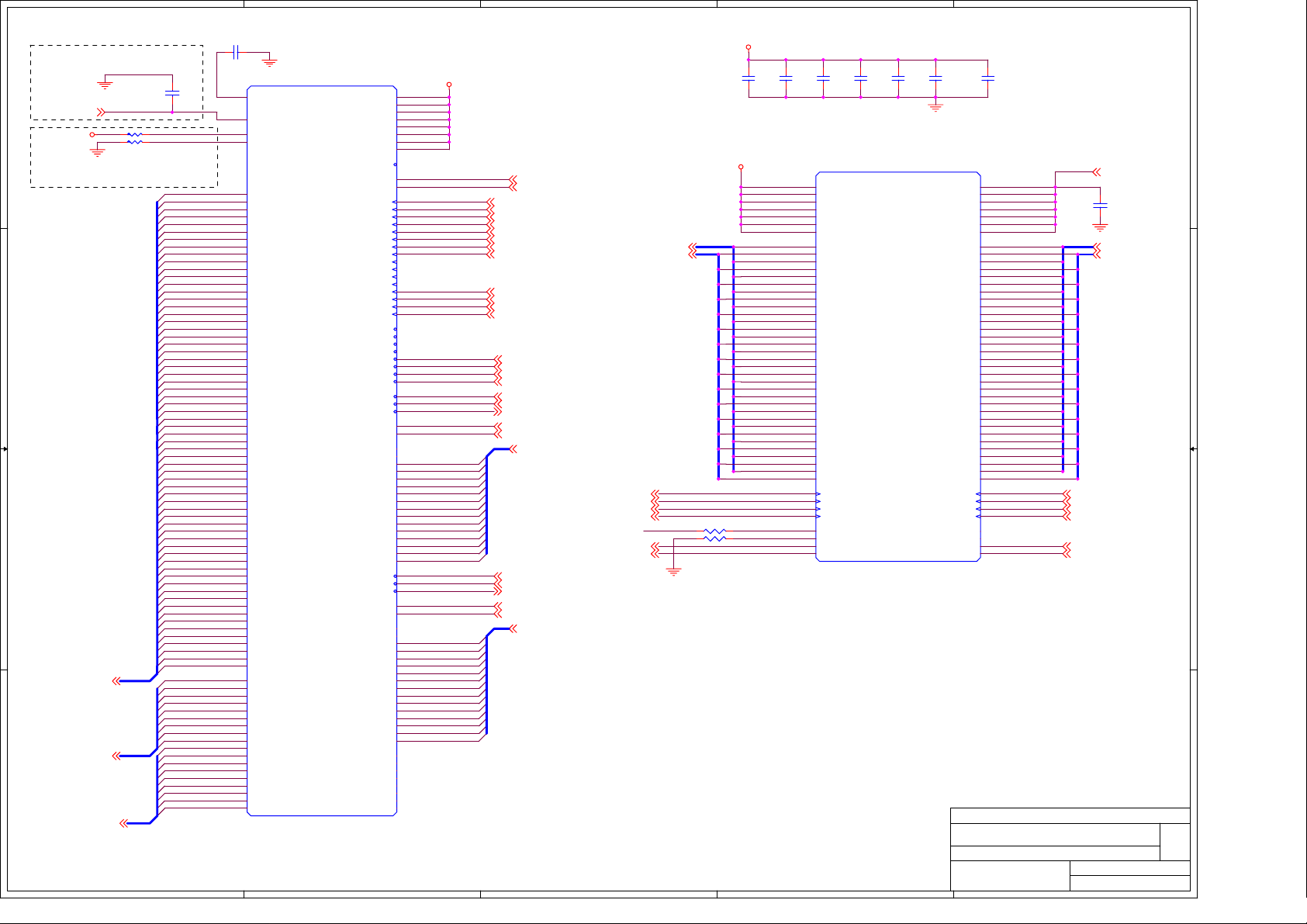

HYPER TRANSPORT - LINK0

C210

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

C227

C0.22U16Y

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

C0.22U16Y

AH29

AH27

AG28

AG26

AF29

AE28

AF25

N26

N27

L25

M25

L26

L27

J25

K25

G25

H25

G26

G27

E25

F25

E26

E27

N29

P29

M28

M27

L29

M29

K28

K27

H28

H27

G29

H29

F28

F27

E29

F29

J26

J27

J29

K29

N25

P25

P28

P27

C135

CADON15

CADON14

CADON13

CADON12

CADON11

CADON10

CADON9

CADON8

CADON7

CADON6

CADON5

CADON4

CADON3

CADON2

CADON1

CADON0

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

CADOP15

CADOP14

CADOP13

CADOP12

CADOP11

CADOP10

CADOP9

CADOP8

CADOP7

CADOP6

CADOP5

CADOP4

CADOP3

CADOP2

CADOP1

CADOP0

CLKOP1

CLKON1

CLKOP0

CLKON0

CTLOP0

CTLON0

VLDT0

CLKOP1 11

CLKON1 11

CLKOP0 11

CLKON0 11

CTLOP0 11

CTLON0 11

K8 DDR & HT

MS-7032

Last Revision Date:

Sheet

1

VLDT0 5

C39

C4.7U10Y0805

CADOP[0..15] 11

CADON[0..15] 11CADIN[0..15]11

Rev

10A

Monday, June 14, 2004

of

437

5

D D

4

C37

X_C1000P50N

VDDIO_SENSE

3

VCCA_PLL trace length from the VR1 to the

PGA must be 0.75".

2

1

Place al filters close to the PGA.

Keep all power and signal trce away from

the VR1.

Place a cut in the GND plane around the

VCCA_PLL regulator circuit.

VDDA_25

VCC2_5

C C

-LDTSTOP

R168

1KR

VLDT04

Place near CPU in 1" ,

Routed => 5:10/Trace:Space ,

Same Length

HDT Test Port Signal .

B B

DBREQ_L

DBRDY

TMS

TCK

TRST_L

TDI

NC_AH18

NC_AJ18

NC_AG18

A A

NC_AG17

NC_C19

NC_D18

NC_D20

NC_B19

NC_C21

5

R50 X_1KR

R49 X_1KR

1 2

3 4

5 6

7 8

RN44 X_8P4R-1KR

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R101 1KR

VCC2_5

C18

C4.7U10Y0805

RN4

8P4R-1KR

8P4R-1KR

RN39

LAYOUT: Route VDDA trace approx. 50 mils wide (use 2x25 mil

traces to exit ball field) and 500 mils long.

FB2 300L700m_250_0805

CPU_GD31

R62 44.2R1%

VLDT0

R63 44.2R1%

4

CPU_VDDA_25

C27

X_C1000P50N

C52

C1000P50X

C53

C1000P50X

VDD_25_SUS

C55

C4.7U10Y0805

-CPURST33

-LDTSTOP11,18

COREFB_H14

COREFB_L14

Differential , "10:10:5:10:10" .

CPUCLK0_H7

Near CPU in 0.5" .

CPUCLK0_L7

VTT_DDR_SUS

3

C34

C0.22U16Y

CPU_GD

L0_REF1

L0_REF0

C47 C0.039U16X

R65

C46 C0.039U16X

R54 820R

R47 820R

VCC2_5

R100 1KR

R99 1KR

C44

C1000P50X

VDDIO_SENSE

169R1%

RN8

1 2

3 4

5 6

7 8

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

DBRDY

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

NC_AE23

NC_AF23

NC_AF22

NC_AF21

X_8P4R-1KR

AH25

AJ25

AF20

AE18

AJ27

AF27

AE26

AE12

AF12

AE11

AJ21

AH21

AJ23

AH23

AE24

AF24

AG15

AH17

AJ28

AE23

AF23

AF22

AF21

AG2

AH1

AE21

AG4

AG6

AE9

AG9

A23

A24

B23

C16

C15

E20

E17

B21

A21

C18

A19

A28

AA2

B18

C20

C1

J3

R3

D3

C6

VDDA1

VDDA2

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

VTT_A5

VTT_B5

DBRDY

NC_C15

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

KEY1

KEY0

NC_AE23

NC_AF23

NC_AF22

NC_AF21

FREE29

FREE31

FREE33

FREE35

FREE1

FREE37

FREE4

FREE38

FREE41

FREE7

FREE11

FREE12

FREE13

FREE14

FREE40

FB1

THERMDC_CPU

X_120S/0603

U7C

THERMTRIP_L

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

G_FBCLKOUT_H

G_FBCLKOUT_L

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

NC_AF18

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

2

THRM#

A20

THERMDA_CPU

A26

THERMDC_CPU

A27

VID4

AG13

VID3

AF14

VID2

AG14

VID1

AF15

VID0

AE15

NC_AG18

AG18

NC_AH18

AH18

NC_AG17

AG17

NC_AJ18

AJ18

FBCLKOUT_H

AH19

AJ19

AE19

D20

C21

D18

C19

B19

A22

AF18

D22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

R64

80.6R1%

FBCLKOUT_L

Zdiff = 80 ohm

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

VID2

VID3

VID1

VID0

VID4

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

THRM# 31

THERMDA_CPU 25,26

THERMDC_CPU 25

VID4 14

VID3 14

VID2 14

VID1 14

VID0 14

LAYOUT: Route

FBCLKOUT_H/L d if fe re n ti al ly

with 20/8/5/8/20 spacing and

trace width. ( In CPU

breakout => routed 5:5:5 )

VDD_25_SUS

R102

1KR

RN5

1 2

3 4

5 6

7 8

X_8P4R-4.7KR

R36 X_4.7KR

K8 HDT & MISC

MS-7032

Last Revision Date:

Monday, June 14, 2004

Sheet

1

VCC2_5

Rev

10A

of

537

5

4

3

2

1

U7F

1

U7E

B2

VSS1

AH20

VSS3

AB21

VSS4

W22

VSS5

M23

VSS6

L24

VSS7

AG25

VSS8

AG27

VSS9

D D

C C

B B

A A

AF2

AA8

AB9

AA10

AE16

G20

R20

U20

W20

AA20

AC20

AE20

AG20

AJ20

D21

H21

M21

AD21

AG21

G22

N22

R22

U22

AG29

AA22

AC22

AG22

AH22

AJ22

D23

H23

AB23

AD23

AG23

G24

N24

R24

U24

W24

AA24

AC24

AG24

AJ24

C25

D26

H26

M26

AD26

AF26

AH26

C27

D28

G28

H15

AB17

AD17

G18

AA18

AC18

D19

H19

AB19

AD19

AF19

N20

D2

VSS10

VSS11

W6

VSS12

Y7

VSS13

VSS14

VSS15

VSS16

J12

VSS17

B14

VSS18

Y15

VSS19

VSS20

J18

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

F21

VSS32

VSS33

K21

VSS34

VSS35

P21

VSS36

T21

VSS37

V21

VSS38

Y21

VSS39

VSS40

VSS41

B22

VSS42

E22

VSS43

VSS44

J22

VSS45

L22

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

F23

VSS57

VSS58

K23

VSS59

P23

VSS60

T23

VSS61

V23

VSS62

Y23

VSS63

VSS64

VSS65

VSS66

E24

VSS67

VSS68

J24

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

B25

VSS78

VSS79

B26

VSS80

VSS81

VSS82

VSS83

T26

VSS84

Y26

VSS85

VSS86

VSS87

VSS88

VSS89

B28

VSS90

VSS91

VSS92

F15

VSS187

VSS188

VSS206

VSS207

B16

VSS208

VSS209

VSS210

VSS211

VSS212

F19

VSS213

VSS214

K19

VSS215

Y19

VSS216

VSS217

VSS218

VSS219

J20

VSS220

L20

VSS221

VSS222

GROUND

5

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

VCORE

AC15

AB14

AA15

AB16

AA17

AC17

AE17

AB18

AD18

AG19

AC19

AA19

AB20

AD20

W21

AA21

AC21

M22

AB22

AD22

G23

W23

AA23

AC23

M24

AB24

AD24

AH24

AE25

GNDGND

H18

B20

E21

H22

H24

F26

V10

G13

K14

Y14

G15

H16

K16

Y16

G17

F18

K18

Y18

E19

G19

F20

H20

K20

M20

P20

T20

V20

Y20

G21

N21

R21

U21

F22

K22

P22

T22

V22

Y22

E23

N23

R23

U23

B24

D24

F24

K24

P24

T24

V24

Y24

K26

P26

V26

U7D

L7

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

J23

VDD7

VDD8

VDD9

N7

VDD10

L9

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

J15

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

J17

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD39

VDD38

J19

VDD37

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

J21

VDD51

L21

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

L23

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

POWER

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD93

VDD94

VDD95

VDD_25_SUS

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

4

VCORE

C488

Place between DIMN1 & 2

VDD_25_SUS

C0.1U25Y

VCORE

VDD_25_SUS

C61

GND

2

GND

3

GND

4

GND

5

GND

6

GND

7

GND

8

GND

9

GND

10

GND

LAYOUT: Place 6 EMI caps along bottom right side of Clawhammer,

2 in middle of HT link, and 12 along bottom left side of

Claw-hammer.

C490

C491

X_C1U16Y

C62

{nopop}

C1U16Y

X_C6.8P50N

C82

C0.1U25Y

C83

X_C1U16Y

C154

C0.1U25Y

C117

C4.7U10Y0805

VCORE

11

GND

12

GND

13

GND

14

GND

15

GND

16

GND

17

GND

18

GND

19

GND

20

GND

GND

C481

C60

C486

X_C6.8P50N

C233

C482

X_C6.8P50N

C484

{nopop}

{nopop}

X_C6.8P50N

C208

C0.1U25Y

X_C1U16Y

C0.1U25Y

GND

LAYOUT: Place beside processor.

C145

C4.7U10Y0805

{nopop}

C1U16Y

C198

C196

C1000P50X

C69

C4.7U10Y0805

X_C0.22U16Y

In CPU.

C95

C180P50N

C104

C180P50N

C99

C8.2P50N

C96

C0.22U16Y

C89

C0.22U16Y

C90

C180P50N

3

C131

{nopop}

X_C6.8P50N

C76

C0.22U16Y

C101

C0.22U16Y

C100

C8.2P50N

C175

X_C6.8P50N

C93

C103

C0.22U16Y

C102

C0.22U16Y

C1U16Y0805

C485

X_C6.8P50N

C119

C1U16Y0805

C108

C0.22U16Y

C105

C0.22U16Y

C483

X_C6.8P50N

GND

C141

X_C1U16Y

VDD_25_SUS VTT_DDR_SUS

C0.22U16Y

C213

C1U16Y

C144

GND

C151

C1U16Y0805

C92

C0.22U16Y

C107

C8.2P50N

2

C228

X_C0.22U16Y

{nopop}

C0.22U16Y

C494

C1U16Y

VTT_DDR_SUS

C495

X_C0.1U25Y

VDD_25_SUS

C478

C489

C1U16Y

BACK

C496

X_C0.1U25Y

GND

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

C1U16Y

GND

Micro Star Restricted Secret

K8 POWER & GND

MS-7032

Last Revision Date:

Sheet

1

Rev

10A

Monday, June 14, 2004

637

of

5

4

3

2

1

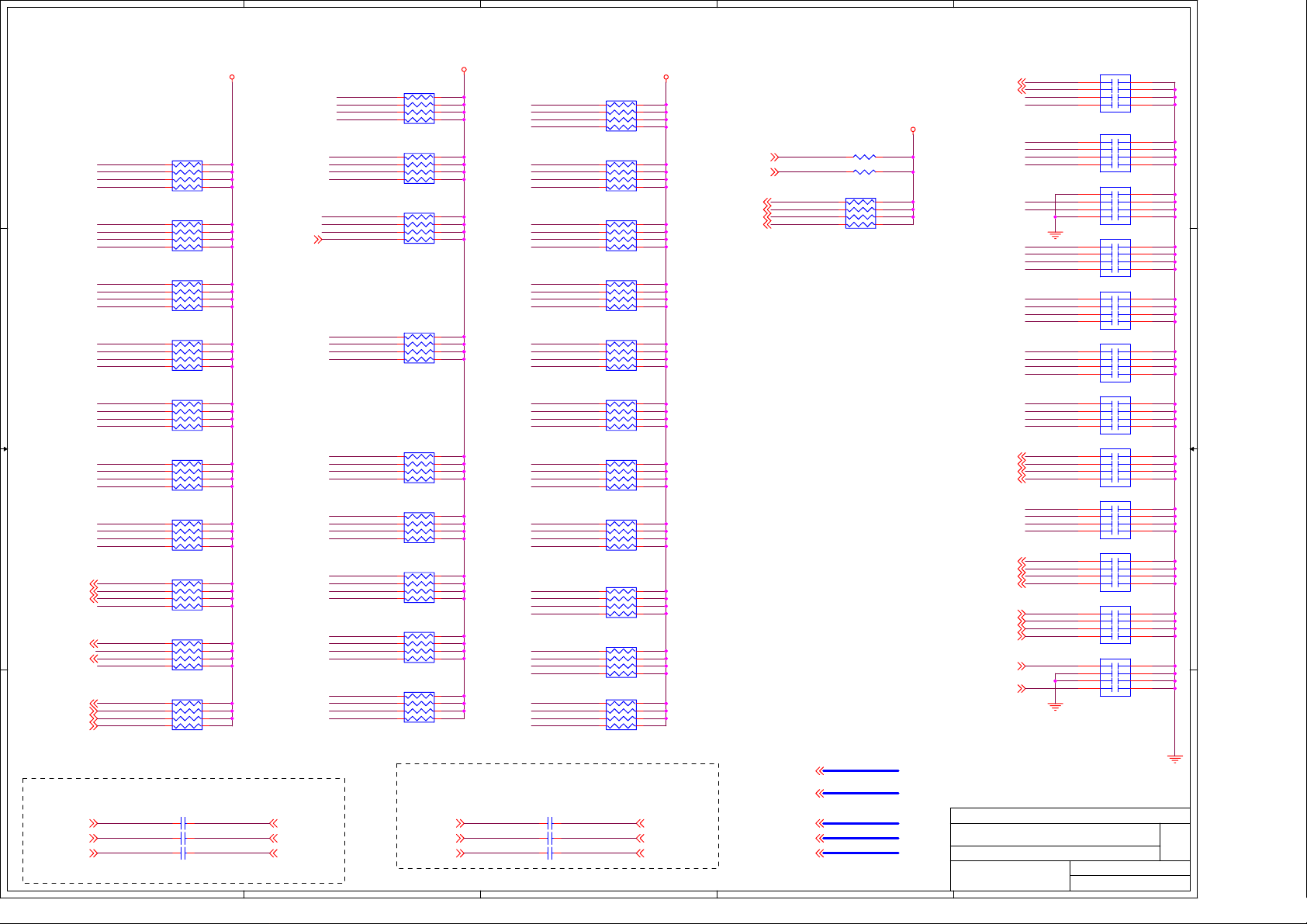

For K8M800

PCICLK5

HCLK+

HCLK-

C590 X_C10P50N

C591 X_C10P50N

C592 C10P50N

C349 C10P50N

C352 C10P50N

C326 X_C10P50N

C310 X_C10P50N

C619 X_C10P50N

C611 M_C10P50N

CN23

7 8

5 6

3 4

1 2

8P4C-10P50N

CN24

7 8

5 6

3 4

1 2

8P4C-10P50N

C348 C10P50N

C594 C10P50N

C595 X_C10P50N

C596 X_C10P50N

C602 C10P50N

ICS950410AF

Strapping CPU

FS1

FS0FS2FS3

0000

000

00 0

00

000

00

00

***

0

1

11

11

111

11

11 1

1

11

1

11

11

111

000

00

00

0

00

0

111

1111

ModeA ModeB

***

00

01

10

11

HTTCLK0

ModeA In

PCICLK7 PCICLK8 PCICLK9 PCICLK10

ModeA In

MHz

100.90

1

133.90

168.00

202.00

100.20

133.50

166.70

200.40

150.00

180.00

210.00

240.00

270.00

233.33

0

266.67

300.00

Pin6 Pin7

HTTCLK1 HTTCLK2 PCICLK10

HTTCLK1 HTTCLK2 HTTCLK3

PCICLK8 PCICLK9 PCICLK10

HTT

MHz

PCI

MHz

67.27 33.63

66.95

33.48

67.20

33.60

67.33

33.67

66.80

33.40

66.75

33.38

66.68

33.34

66.80

33.40

60.00

33.00

60.00

33.00

70.00

35.00

60.00

30.00

67.50

33.75

66.67

33.33

66.67

33.33

75.00

37.50

Pin8 Pin11

VCLK

Clock Synthesizer

D D

U16

CLKVCC3

C324 C0.1U25Y

CLKVCC3

CLKVCC3

C335 C0.1U25Y

CLKVCC3

C347 X_C0.1U25Y

CLKVCC3

C350 C0.1U25Y

CLKVCC3

C321 C0.1U25Y

CLKVCC3

CLKVCC3

CLKVDDA

CLKVCC3

C339 X_C0.1U25Y

CLKVCC3

C357 C0.1U25Y

C332 C0.1U25Y

TURBO#25

R251 10KR

C C

ICS950407AF_SSOP48

46

VDDREF

47

GND

2

VDDHTT

5

GND

9

VDDPCI

10

GND

16

VDDPCI

15

GND

19

VDDPCI

20

GND

28

AVDD48

29

GND

40

VDDCPU

37

GND

36

VDDCPU

33

GND

44

VDDA

43

GND

31

PD#

32

Turbo#

FS0/REF0

FS1/REF1

RESET#

XOUT

ModeA/HTT66_0

ModeB/PCI33_8/HTT66_1

PCI33_9/HT66_2

PCI33_11/HT66_3

FS2/PCI33_10

PCI33_0

PCI33_1

PCI33_2

PCI33_3

PCI33_4

PCI33_5

PCI33_6

PCI33_7

FS3/48M

24_48MHZ/SEL

SDATA

SCLK

CPUCLK8T0

CPUCLK8C0

CPUCLK8T1

CPUCLK8C1

CPUCLK8T2

CPUCLK8C2

FS0 APICCLK

1

FS1

48

45

CLKX1

3

XIN

CLKX2

4

MODEA

6

MODEB

7

8

11

FS2

12

13

14

17

PCI33_3

18

21

22

23

24

30

SEL_24 USBCLK_SB

27

SMBDATA1

26

SMBCLK1

25

42

41

39

38

35

34

R396 33R

R232 33R

R240 M_33R

For K8M800

7 8

5 6

3 4

RN78 8P4R-22R

1 2

7 8

5 6

3 4

1 2

RN81 8P4R-22R

7 8

5 6

3 4

1 2

RN129 8P4R-22R

R261 33R

R263 33R

R255 15R1%

R256 15R1%

R397 T_15R1%

R398 T_15R1%

For K8T800 Pro

PCI33_3 PCICLK5

AC_14

GUICLK

C314 C27P50N

Y5 14.318MHZ32P_D

C315 C27P50N

VCLK

GCLK_NB

GCLK_SLOT

PCICLK1

PCICLK2

PCICLK3

PCICLK4

SIOPCLK

LPC_PCLK

SBPCLK

GLAN_PCLK

SIO48MFS3

CPUCLK0_H

CPUCLK0_L

HCLK+

HCLK-

R420 22R

R443 22R

PCICLK6

AC_14 22

APICCLK 17,18

GUICLK 12

CLK_RESET# 33

VCLK 18

GCLK_NB 12

GCLK_SLOT 15

PCICLK1 19

PCICLK2 19

PCICLK3 20

PCICLK4 20

SIOPCLK 25

LPC_PCLK 32

SBPCLK 18

GLAN_PCLK 30

SIO48M 25

USBCLK_SB 16

SMBDATA1 8,17,21,31

SMBCLK1 8,17,21,31

CPUCLK0_H 5

CPUCLK0_L 5

HCLK+ 11

HCLK- 11

PCICLK5 21

PCICLK6 21

GCLK_NB

GCLK_SLOT

SIO48M

USBCLK_SB

AC_14

APICCLK

GUICLK

FS1

PCICLK1

PCICLK2

PCICLK3

PCICLK4

SIOPCLK

LPC_PCLK

SBPCLK

GLAN_PCLK

PCICLK6

"FS0~FS3" are all internal

pull-up via 100K ohm ..

FS0

FS2

FS1

FS3

ModeA,B=0:0 ( Set Pin 7,8 clock

-> 66 MHz Pin11->33Mhz )

MODEB

MODEA

"24_48MHZ/SEL" Freq.-Out select

pin => Low->48MHz , Hi->24MHz .

( Internal pull-up via 100K ohm )

SEL_24

R230 10KR

R236 10KR

R233 10KR

R258 10KR

R252 10KR

R237 10KR

R262 10KR

CLKVCC3

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

Clock Synthesizer

MS-7032

Last Revision Date:

Sheet

1

Rev

10A

Monday, June 14, 2004

of

737

VCC3

FB3 X_120S/0805

B B

CP15

X_COPPER

For EMI

VCC3 VCC

A A

C398 C0.1U25Y

C446 X_C0.1U25Y

C333

C1U16Y0805

5

CLKVDDA

C293

X_C0.1U25Y

C365

C1U16Y0805

CLKVCC3

C360

C0.1U25Y

VCC3

Decoupling Cap for CPU Clock

VCC3

C371

C0.1U25Y

FB5 X_120S/0805

CP17

X_COPPER

EMI Request(close to Trace Ending)

HCLK+

HCLKGCLK_SLOT

GCLK_NB

VCLK

USBCLK_SB

SBPCLK

PCICLK1

C620 X_C10P50N

C622 X_C10P50N

R460 X_22R

R464 X_22RC628 X_C10P50N

R468 X_22RC632 X_C10P50N

C624 X_C10P50N

C626 X_C10P50N

C630 X_C10P50N

C634 X_C10P50N

4

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

SIOPCLK

SIO48M

GLAN_PCLK

LPC_PCLK

CPUCLK0_H

CPUCLK0_L

C251 C0.1U25Y

R459 X_22R

R461 X_22R

R472 X_22R

Near CK-Gen in 0.5" .

C338 C22P50N

C340 C22P50N

C621 X_C10P50N

C623 X_C10P50N

C625 X_C10P50N

C627 X_C10P50N

C629 X_C10P50N

C631 X_C10P50N

C633 X_C10P50N

C635 X_C10P50NR471 X_22R

C636 X_C10P50N

3

5

C30

C0.1U25Y

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

WP1

-MSWEA

DR_MD[63..0]9,10

D D

C C

B B

VDD_25_SUS

R148 4.7KR

-MSWEA4,9

DDR_VREF

VREF routed as 40~50

mils trace wide ,

Space>25 mils

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

102

NC4

Place 104p and 1000p Cap. near the DIMM

VDD_25_SUS

738467085

108

120

148

168223054627796

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VSS0

VSS1

VSS2

VSS3

VSS4

3111826344250586674818993

VDD8

VSS5

VDDQ0

VDDQ1

VSS6

VSS7

4

SYSTEM MEMORY

104

112

128

136

143

156

164

172

1801582

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

184

PIN

DDR DIMM

SOCKET

NC(RESET#)

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

100

116

124

132

139

145

152

160

176

184

VDDID

VDDQ15

VDDSPD

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10_AP

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC5

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

VSS21

DDR1

DIMM-184_green

N13-1840061-K06

3

DDR_VREF

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

WP2

-MSWEB

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

102

NC4

-MCS0

157

-MCS1

158

71

163

-DR_MDQS0

5

-DR_MDQS1

14

-DR_MDQS2

25

-DR_MDQS3

36

-DR_MDQS4

56

-DR_MDQS5

67

-DR_MDQS6

78

-DR_MDQS7

86

-DR_MDQS8

47

103

MAA0

48

MAA1

43

MAA2

41

MAA3

130

MAA4

37

MAA5

32

MAA6

125

MAA7

29

MAA8

122

MAA9

27

MAA10

141

MAA11

118

MAA12 MAB12

115

MAA13

167

59

52

113

SMBCLK1

92

SMBDATA1

91

181

182

183

44

45

49

51

134

135

142

144

MEMCLK_H5

16

MEMCLK_L5

17

MEMCLK_H0

137

MEMCLK_L0

138

MEMCLK_H7

76

MEMCLK_L7

75

173

10

MCKE0

21

MCKE1

111

-MSCASA

65

-MSRASA

154

DR_DM0

97

DR_DM1

107

DR_DM2

119

DR_DM3

129

DR_DM4

149

DR_DM5

159

DR_DM6

169

DR_DM7

177

DR_DM8

140

-MCS0 4,9

-MCS1 4,9

-DR_MDQS0 9,10

-DR_MDQS1 9,10

-DR_MDQS2 9,10

-DR_MDQS3 9,10

-DR_MDQS4 9,10

-DR_MDQS5 9,10

-DR_MDQS6 9,10

-DR_MDQS7 9,10

-DR_MDQS8 9,10

MAA[13..0]

MEMBANKA0 4,9

MEMBANKA1 4,9

SMBCLK1 7,17,21,31

SMBDATA1 7,17,21,31

MEMCLK_H5 4,9

MEMCLK_L5 4,9

MEMCLK_H0 4,9

MEMCLK_L0 4,9

MEMCLK_H7 4,9

MEMCLK_L7 4,9

MCKE0 4,9

MCKE1 4,9

-MSCASA 4,9

-MSRASA 4,9

MAA[13..0] 4,9

VDD_25_SUS

R147 4.7KR

-MSWEB4,9

2

VDD_25_SUS

738467085

108

120

148

168223054627796

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

3111826344250586674818993

104

112

128

136

143

156

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

184

DDR DIMM

SOCKET

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

100

116

124

132

139

164

172

1801582

VDDQ11

VDDQ12

VDDQ13

PIN

VSS17

VSS18

VSS19

145

152

160

VDDQ14

VDDQ15

A10_AP

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC(RESET#)

VSS20

VSS21

176

VDDID

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC5

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

184

VDDSPD

157

158

71

163

5

14

25

36

56

67

78

86

47

103

48

A0

43

A1

41

A2

130

A3

37

A4

32

A5

125

A6

29

A7

122

A8

27

A9

141

118

115

167

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

DDR2

DIMM-184_green

N13-1840061-K06

-MCS2

-MCS3

-DR_MDQS0

-DR_MDQS1

-DR_MDQS2

-DR_MDQS3

-DR_MDQS4

-DR_MDQS5

-DR_MDQS6

-DR_MDQS7

-DR_MDQS8

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB13

MEMBAKB0

MEMBAKB1

SMBCLK1

SMBDATA1

MCKE0

MCKE1

-MSCASB

-MSRASB

1

-MCS2 4,9

-MCS3 4,9

MEMBAKB0 4,9

MEMBAKB1 4,9

VDD_25_SUS

-MSCASB 4,9

-MSRASB 4,9

DR_DM0

DR_DM1

DR_DM2

DR_DM3

DR_DM4

DR_DM5

DR_DM6

DR_DM7

DR_DM8

MAB[13..0] 4,9

MEMCLK_H4 4,9

MEMCLK_L4 4,9

MEMCLK_H1 4,9

MEMCLK_L1 4,9

MEMCLK_H6 4,9

MEMCLK_L6 4,9

Place near the DIMM

VDD_25_SUS

R53

1KR1%

A A

R52

1KR1%

C477

X_C0.1U25Y

DDR_VREF

C31

C1U10Y

VREF routed as 40~50 mils trace wide ,

Space>25 mils

DDR_VREF 4

5

DIMM1 SLAVE ADDRESS

= (1010000X)B = A0

4

DR_DM[8..0]

DR_DM[8..0] 9,10

3

DIMM2 SLAVE ADDRESS

= (1010001X)B = A2

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

Micro Star Restricted Secret

System Memory : DDR DIMM 1

MS-7032

Last Revision Date:

Monday, June 14, 2004

Sheet

837

1

Rev

10A

of

5

4

3

2

1

DDR Terminations

VTT_DDR_SUS VTT_DDR_SUS

DR_MD40

DR_MD39

DR_MD35

D D

DR_MD59

DR_MD63

DR_MD58

DR_MD62

-DR_MDQS7

DR_DM7

DR_MD57

DR_MD61

DR_MD56

DR_MD60

DR_MD51

DR_MD55

C C

B B

-MSCASA4,8

-MSRASB4,8

-MSRASA4,8

MEMBANKA04,8

MEMBAKB04,8

MEMBANKA14,8

DR_MD50

DR_MD54

-DR_MDQS6

DR_DM6

MAA13

MAB13

DR_MD53

DR_MD52

DR_MD49

DR_MD48

DR_MD47

DR_MD46

DR_MD43

DR_MD42

DR_DM5

-DR_MDQS5

-MCS1

-MCS14,8

-MCS0

-MCS04,8

-MSCASA

DR_MD41

-MSWEB

-MSWEB4,8

DR_MD45

-MSRASB

DR_MD44

-MSRASA

RN68 8P4R-27R0402

7 8

5 6

3 4

1 2

RN67 8P4R-27R0402

7 8

5 6

3 4

1 2

RN66 8P4R-27R0402

7 8

5 6

3 4

1 2

RN64 8P4R-27R0402

7 8

5 6

3 4

1 2

RN62 8P4R-27R0402

7 8

5 6

3 4

1 2

RN60 8P4R-27R0402

7 8

5 6

3 4

1 2

RN58 8P4R-27R0402

7 8

5 6

3 4

1 2

RN57 8P4R-27R0402

7 8

5 6

3 4

1 2

RN53 8P4R-27R0402

7 8

5 6

3 4

1 2

RN52 8P4R-27R0402

7 8

5 6

3 4

1 2

MEMBAKB14,8

DR_MD38

DR_MD34

DR_DM4

-DR_MDQS4

DR_MD37

DR_MD33

DR_MD36

DR_MD32

MAB0

MAB10

DR_DM8

-DR_MDQS8

MAA1

MAB1

MAA2

MAB2

MAA3

MAA4

MAB4

MAA6

DR_MD30

MAB3

DR_MD26

DR_DM3

-DR_MDQS3

DR_MD25

DR_MD29

DR_MD28

MAB6

MAB5

MAA5

MAA8

VTT_DDR_SUS

RN50 8P4R-27R0402

7 8

5 6

3 4

1 2

RN48 8P4R-27R0402

7 8

5 6

3 4

1 2

RN47 8P4R-27R0402

7 8

5 6

3 4

1 2

RN43 8P4R-27R0402

7 8

5 6

3 4

1 2

RN36 8P4R-27R0402

7 8

5 6

3 4

1 2

RN32 8P4R-27R0402

7 8

5 6

3 4

1 2

RN35 8P4R-27R0402

7 8

5 6

3 4

1 2

RN34 8P4R-27R0402

7 8

5 6

3 4

1 2

RN29 8P4R-27R0402

7 8

5 6

3 4

1 2

DR_MD24

DR_MD19

DR_MD23

MAA7

DR_DM2

MAA9

MAA11

MAA12

MAB8

DR_MD22

MAB7

DR_MD18

MAB9

MAB11

DR_MD21

-DR_MDQS2

DR_MD17

MAB12

DR_MD16

DR_MD20

DR_MD11

DR_MD10

DR_MD15

DR_MD14

DR_DM1

DR_MD13

-DR_MDQS1

DR_MD12

DR_MD9

DR_MD8

DR_MD3

DR_MD7

DR_MD6

DR_MD2

DR_DM0

-DR_MDQS0

DR_MD1

DR_MD5

DR_MD4

DR_MD0

MAA10

MAA0

DR_MD31

DR_MD27

RN27 8P4R-27R0402

7 8

5 6

3 4

1 2

RN25 8P4R-27R0402

7 8

5 6

3 4

1 2

RN23 8P4R-27R0402

7 8

5 6

3 4

1 2

RN20 8P4R-27R0402

7 8

5 6

3 4

1 2

RN19 8P4R-27R0402

7 8

5 6

3 4

1 2

RN14 8P4R-27R0402

7 8

5 6

3 4

1 2

RN11 8P4R-27R0402

7 8

5 6

3 4

1 2

RN9 8P4R-27R0402

7 8

5 6

3 4

1 2

RN7 8P4R-27R0402

7 8

5 6

3 4

1 2

RN3 8P4R-27R0402

7 8

5 6

3 4

1 2

RN41 8P4R-27R0402

7 8

5 6

3 4

1 2

-MCS2

-MCS24,8

-MCS3

-MCS34,8

MAB13

MAA13

VTT_DDR_SUS

MCKE04,8

MCKE14,8

-MCS3

-MCS34,8

-MCS2

-MCS24,8

-MSCASB4,8

-MSCASB

-MSWEA

-MSWEA4,8

R72 27R0402

R71 27R0402

RN55 8P4R-27R0402

7 8

5 6

3 4

1 2

-MSCASB4,8

-MSCASA4,8

-MSRASB4,8

-MSRASA4,8

MEMBAKB14,8

MEMBANKA14,8

MEMBAKB04,8

MEMBANKA04,8

MAB12

MAA12

MAB11

MAA11

MAB1

MAA1

MAB3

MAA3

MAB2

MAA2

MAB6

MAA6

MAB4

MAA4

MAB8

MAA8

MAA5

MAB5

MAA0

MAA10

MAB0

MAB10

-MSCASB

-MCS0

-MCS04,8

-MSCASA

-MCS1

-MCS14,8

MAA9

MAB9

MAB7

MAA7

-MSRASB

-MSRASA

-MSWEA

-MSWEA4,8

-MSWEB

-MSWEB4,8

MCKE14,8

MCKE04,8

CN20

12

34

56

78

X_8P4C-10P50N

CN6

12

34

56

78

X_8P4C-10P50N

CN14

12

34

56

78

X_8P4C-10P50N

CN13

12

34

56

78

X_8P4C-10P50N

CN12

12

34

56

78

X_8P4C-10P50N

CN10

12

34

56

78

X_8P4C-10P50N

CN15

12

34

56

78

X_8P4C-10P50N

CN19

12

34

56

78

X_8P4C-10P50N

CN8

12

34

56

78

X_8P4C-10P50N

CN18

12

34

56

78

X_8P4C-10P50N

CN17

12

34

56

78

X_8P4C-10P50N

CN4

12

34

56

78

X_8P4C-10P50N

A A

For DIMM2 Clock

C564 C10P50N

MEMCLK_H44,8 MEMCLK_L5 4,8

MEMCLK_H14,8

MEMCLK_H64,8

MEMCLK_H4

MEMCLK_H1

5

C565 C10P50N

C566 C10P50N

MEMCLK_L4

MEMCLK_L1

MEMCLK_L6MEMCLK_H6

MEMCLK_L4 4,8

MEMCLK_L1 4,8

MEMCLK_L6 4,8

4

For DIMM1 Clock

MEMCLK_H54,8

MEMCLK_H74,8

MEMCLK_H04,8

MEMCLK_H5

MEMCLK_H7

C567 C10P50N

C568 C10P50N

C569 C10P50N

MEMCLK_L5

MEMCLK_L7

MEMCLK_L0MEMCLK_H0

3

MEMCLK_L7 4,8

MEMCLK_L0 4,8

DR_DM[8..0]8,10

-DR_MDQS[8..0]8,10

DR_MD[63..0]8,10

MAB[13..0]4,8

MAA[13..0]4,8

DR_DM[8..0]

-DR_MDQS[8..0]

DR_MD[63..0]

MAB[13..0]

MAA[13..0]

2

Micro Star Restricted Secret

Title

DDR Terminations Bank 0

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-7032

Last Revision Date:

Monday, June 14, 2004

Sheet

937

1

Rev

10A

of

5

DM8 DR_DM8

DDR Terminations

R66 10R

D D

C C

B B

-MDQS0 -DR_MDQS0

RN10 8P4R-10R

MD0

1 2

MD4

3 4

MD5

5 6

MD1

7 8

RN13 8P4R-10R

DM0

1 2

3 4

MD6 DR_MD6

5 6

MD7 DR_MD7

7 8

RN16 8P4R-10R

1 2

MD8 DR_MD8

3 4

MD9 DR_MD9

5 6

7 8

R75 10R

MD15

RN18 8P4R-10R

-MDQS1

1 2

MD13 DR_MD13

3 4

DM1

5 6

MD14 DR_MD14

7 8

RN24 8P4R-10R

1 2

MD17

3 4

MD21 DR_MD21

5 6

DM2

7 8

R78 10R

MD18

RN21 8P4R-10R

MD10

1 2

3 4

MD20 DR_MD20

5 6

MD16 DR_MD16

7 8

RN28 8P4R-10R

1 2

MD23 DR_MD23

3 4

5 6

MD24

7 8

RN30 8P4R-10R

1 2

MD29

3 4

5 6

-MDQS3

7 8

RN37 8P4R-10R

MD26

1 2

3 4

MD27

5 6

MD31 DR_MD31

7 8

DR_MD0

DR_MD4

DR_MD5

DR_MD1

DR_DM0

DR_MD2MD2

DR_MD3MD3

DR_MD12MD12

DR_MD15

-DR_MDQS1

DR_DM1

-DR_MDQS2-MDQS2

DR_MD17

DR_DM2

DR_MD18

DR_MD10

DR_MD11MD11

DR_MD22MD22

DR_MD19MD19

DR_MD24

DR_MD28MD28

DR_MD29

DR_MD25MD25

-DR_MDQS3

DR_MD26

DR_MD30MD30

DR_MD27

-MDQS4 -DR_MDQS4

MD42

MD50

MD55

MD56

MD61 DR_MD61

MD57 DR_MD57

DM7

-MDQS7

MD62 DR_MD62

MD58

MD63

4

R110 10R

MD38

RN45 8P4R-10R

1 2

3 4

5 6

7 8

RN49 8P4R-10R

1 2

3 4

DM4

5 6

MD34 DR_MD34

7 8

R116 10R

RN51 8P4R-10R

MD35 DR_MD35

1 2

MD39 DR_MD39

3 4

5 6

MD44 DR_MD44

7 8

RN54 8P4R-10R

1 2

MD41 DR_MD41

3 4

-MDQS5 -DR_MDQS5

5 6

DM5 DR_DM5

7 8

RN56 8P4R-10R

MD43

1 2

MD46 DR_MD46

3 4

MD47 DR_MD47

5 6

7 8

RN59 8P4R-10R

1 2

3 4

MD53 DR_MD53

5 6

7 8

R135 10R

MD51

RN61 8P4R-10R

1 2

3 4

5 6

7 8

RN63 8P4R-10R

1 2

3 4

5 6

7 8

RN65 8P4R-10R

1 2

3 4

5 6

7 8

R145 10R

R141 10R

DR_MD38

DR_MD32MD32

DR_MD36MD36

DR_MD33MD33

DR_MD37MD37

DR_DM4

DR_MD42

DR_MD40MD40

DR_MD45MD45

DR_MD43

DR_MD48MD48

DR_MD49MD49

DR_MD52MD52

DR_DM6DM6

DR_MD51

-DR_MDQS6-MDQS6

DR_MD54MD54

DR_MD50

DR_MD55

DR_MD60MD60

DR_MD56

DR_DM7

-DR_MDQS7

DR_MD58

DR_MD59MD59

DR_MD63

VDD_25_SUS

VTT_DDR_SUS

C25

VTT_DDR_SUS

3

LAYOUT: Place on backside,

evenly spaced around VTT fill.

VDD_25_SUS

VDD_25_SUS VDD_25_SUS VDD_25_SUS

C19

X_C0.1U25Y

C28

C0.1U25Y

C43

X_C0.1U25Y

C207

X_C0.1U25Y

C211

X_C0.1U25Y

C63

C0.1U25Y

C68

X_C0.1U25Y

C74

X_C0.1U25Y

C79

C0.1U25Y

C230

X_C0.1U25Y

C91

X_C0.1U25Y

C177

X_C0.1U25Y

C111

X_C0.1U25Y

VTT_DDR_SUS

C192

C1000P50X

{nopop}

C242

X_C0.22U16Y

{nopop}

C35

X_C0.22U16Y

{nopop}

X_C0.22U16Y

{nopop}

C240

2

C123

C0.1U25Y

C129

X_C0.1U25Y

C217

X_C0.1U25Y

C223

C0.1U25Y

C153

X_C0.1U25Y

C157

C0.1U25Y

C164

C0.1U25Y

LAYOUT: Locate close

to Clawhammer

socket.

VTT_DDR_SUS

+

EC16

X_.CD1000U6.3EL15

GND

VTT_DDR_SUSVTT_DDR_SUSVTT_DDR_SUSVTT_DDR_SUS

C168

X_C0.1U25Y

C172

C0.1U25Y

C184

X_C0.1U25Y

C188

X_C0.1U25Y

C194

C0.1U25Y

C202

C0.1U25Y

+

EC4

.CD1000U6.3EL15

LAYOUT: Place alternating caps to GND and VDD_2.5_SUS in a single line along VTT island.

C1U10Y

C71

C40

C1U10Y

C48

C57

X_C0.1U25Y

C59

X_C0.1U25Y

C66

X_C0.1U25Y

C1U10Y

C77

C1U10Y

C80

X_C0.1U25Y

C86

X_C0.1U25Y

C97

X_C0.1U25Y

C13

C0.1U25Y

C112

X_C0.1U25Y

C121

X_C0.1U25Y

C1U10Y

C127

1

Ver:10A modify

VDD_25_SUS

C133

C146

C1U10Y

X_C0.1U25Y

GND

C54

X_C0.1U25Y

C58

C0.1U25Y

C84

C0.1U25Y

C113

X_C0.1U25Y

C142

C0.1U25Y

C148

C0.1U25Y

C174

X_C0.1U25Y

C214

C0.1U25Y

X_C0.1U25Y

GND

C176

X_C0.1U25Y

C11

C12

X_C4.7U10Y0805

C1000P50X

C246

C181

C1U10Y

C6

C1000P50X

X_C100P50N

GND

C161

C1U16Y0805

C1000P50X

C143

C150

R445 10R

-MDQS8 -DR_MDQS8

-MDQS[8..0]4

-DR_MDQS[8..0]8,9

DR_MD[63..0]8,9

MD[63..0]4

A A

DR_DM[8..0]8,9

DM[8..0]4

-DR_MDQS[8..0]

DR_MD[63..0]

MD[63..0]

DR_DM[8..0]

DM[8..0]

5

DM3

R80 10R

4

DR_DM3

VTT_DDR_SUS

C0.22U16Y

C56

VTT_DDR_SUS

C1000P50NC250

3

C155

C1U10Y

C1U16Y0805

X_C1000P50X

C248

C41

C160

X_C0.1U25Y

C36

X_C0.22U16Y

C238

X_C4.7U10Y0805

C165

C171

X_C0.1U25Y

X_C0.1U25Y

LAYOUT: Locate close to

Clawhammer socket.

C33

C1U16Y0805

C182

C203

X_C4.7U10Y0805

C1U10Y

C0.22U16Y

C187

X_C0.1U25Y

C166

GND

C190

C0.1U25Y

C1U16Y0805

2

C197

C204

X_C0.1U25Y

C1U10Y

C209

C1U10Y

C212

Title

Document Number

C219

C216

X_C0.1U25Y

X_C0.1U25Y

C1U10Y

C224

VDD_25_SUS

C608

C607

C0.1U25Y

Micro Star Restricted Secret

DDR Terminations Bank 1

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

C231

C0.1U25Y

C0.1U25Y

GND

LAYOUT: Locate close to

Dimm2 socket.

C609

C610

C0.1U25Y

C0.1U25Y

C0.1U25Y

GND

MS-7032

Last Revision Date:

Monday, June 14, 2004

Sheet

1

of

10 37

Rev

10A

A

B

C

D

E

VDD_12_A

VDD_12_A

VCC3

VLDT

VSS

R393

M_0R

HCKGND

E11

E21

E22

E23

E24E9F10

F11

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F17

F18

F26

G25H1H23

R392

4 4

HCLK-7

C22

C21

AVDD2

AGND2

HCLK+7

A10

A24

A25

A26A9B10

B23

B24

B25

B26B9C10

C11

VLDT

VSS

VLDT

VSS

C23

VLDT

VLDT

VLDT

VLDT

VLDT

VSS

VSS

VSS

VSS

VSS

D6

D12

D14

D16

U10A

VLDT

VSS

VSS

A8

A23

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VSS

VSS

VSS

VSS

VSS

VSS

B15

B21

B8

B22C8D8

B13

B17

B19

AVDD2

From Claw Hammer To Claw Hammer

CADOP[0..15]4

3 3

CLKOP04

CLKOP14

CTLOP04

CADON[0..15]4

CLKON04

2 2

CLKON14

CTLON04

-LDTRST33

-LDTSTOP5,18

CADOP0

CADOP1

CADOP2

CADOP3

CADOP4

CADOP5

CADOP6

CADOP7

CADOP8

CADOP9

CADOP10

CADOP11

CADOP12

CADOP13

CADOP14

CADOP15

CLKOP0

CLKOP1

CTLOP0

CADON0

CADON1

CADON2

CADON3

CADON4

CADON5

CADON6

CADON7

CADON8

CADON9

CADON10

CADON11

CADON12

CADON13

CADON14

CADON15

CLKON0

CLKON1

CTLON0

-LDTRST

-LDTSTOP

RPCOMP

PNCOMP

RTCOMP

VDD_12_A

1 1

T26

P24

P26

M24

K24

K26

H24

H26

R24

R22

N24

N22

L22

J24

J22

G24

M26

L24

F24

R26

P25

N26

M25

K25

J26

H25

G26

R23

P22

N23

M22

K22

J23

H22

G23

L26

L23

F25

B11

A12

D25

D26

C26

U24

U25

U26

V21

V22

V23

V24

V25

V26

RCADP0

RCADP1

RCADP2

RCADP3

RCADP4

RCADP5

RCADP6

RCADP7

RCADP8

RCADP9

RCADP10

RCADP11

RCADP12

RCADP13

RCADP14

RCADP15

RCLKP0

RCLKP1

RCTLP

RCADN0

RCADN1

RCADN2

RCADN3

RCADN4

RCADN5

RCADN6

RCADN7

RCADN8

RCADN9

RCADN10

RCADN11

RCADN12

RCADN13

RCADN14

RCADN15

RCLKN0

RCLKN1

RCTLN

LDTRST

LDTSTP

RPCOMP

RNCOMP

RTCOMP

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

M_0R

C24

C25C9D10

VLDT

VSS

D18

D20

D11

VLDT

VLDT

VLDT

VLDT

VSS

VSS

VSS

VSS

E5E6E8F7F8

D22

R391

VLDT

VSS

M_0R

D23

VLDT

VSS

D24D9E10

VLDT

VSS

F12

VLDT

VSS

F13

F14

VLDT

VSS

R394

FOR K8M800

M_0R

FOR K8T800A

VDD_12_AVCC3HCK

F15

F16

F19

F20

F21

F22

F23

G21

G22

H21

J11

J12

J13

J14

J15

J16

J17

K18

K21

VLDT

VSS

K23H2L10

VLDT

VLDT

TCADP0

TCADP1

TCADP2

TCADP3

TCADP4

TCADP5

TCADP6

TCADP7

TCADP8

TCADP9

TCADP10

TCADP11

TCADP12

TCADP13

TCADP14

TCADP15

TCADN0

TCADN1

TCADN2

TCADN3

TCADN4

TCADN5

TCADN6

TCADN7

TCADN8

TCADN9

TCADN10

TCADN11

TCADN12

TCADN13

TCADN14

TCADN15

VSS

VSS

L11

VLDT

VLDT

TCLKP0

TCLKP1

TCTLP

TCLKN0

TCLKN1

TCTLN

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VSS

VSS

L13

L12

L18

VLDT

VLDT

B12

A13

B14

A15

A17

B18

A19

B20

E12

D13

E14

D15

D17

E18

D19

E20

B16

E16

A21

C12

A14

C14

A16

A18

C18

A20

C20

E13

C13

E15

C15

C17

E19

C19

D21

C16

E17

A22

L21

M18

N18

N21

P18

P21

R18

T18

T21

T22

T23

T24

T25

U18

U21

U22

U23

VSS

VSS

L14

L15

(VIA-K8M800-VT8380)

J10

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VSS

VSS

VSS

VSS

VSS

VSS

J21

J25

K4G1K10

VSS

VSS

VSS

VSS

VSS

VSS

K12

K16

K17

K15

K13

K14

K11

VSS

VSS

J2

J3

J18

CADIP0

CADIP1

CADIP2

CADIP3

CADIP4

CADIP5

CADIP6

CADIP7

CADIP8

CADIP9

CADIP10

CADIP11

CADIP12

CADIP13

CADIP14

CADIP15

CLKIP0

CLKIP1

CTLIP0

CADIN0

CADIN1

CADIN2

CADIN3

CADIN4

CADIN5

CADIN6

CADIN7

CADIN8

CADIN9

CADIN10

CADIN11

CADIN12

CADIN13

CADIN14

CADIN15

CLKIN0

CLKIN1

CTLIN0

VDD_12_A

FB37 T_0R

HCKGND

R395 T_0R

VCC3HCK

C560

C1000P50X

CADIP[0..15] 4

CLKIP0 4

CLKIP1 4

CTLIP0 4

CADIN[0..15] 4

CLKIN0 4

CLKIN1 4

CTLIN0 4

C561

C1U10Y

CB38

X_C1000P50X

5020

PNCOMP

RTCOMP

RPCOMP

C201 C0.1U25Y

Around NB

C506

X_C0.1U25Y

Decoupling capacitors

at NB BGA Area (On

Solder Layer)

R127 49.9R1%

R120 100R1%

R126 49.9R1%

VDD_12_A

VDD_12_A

Micro Star Restricted Secret

Title