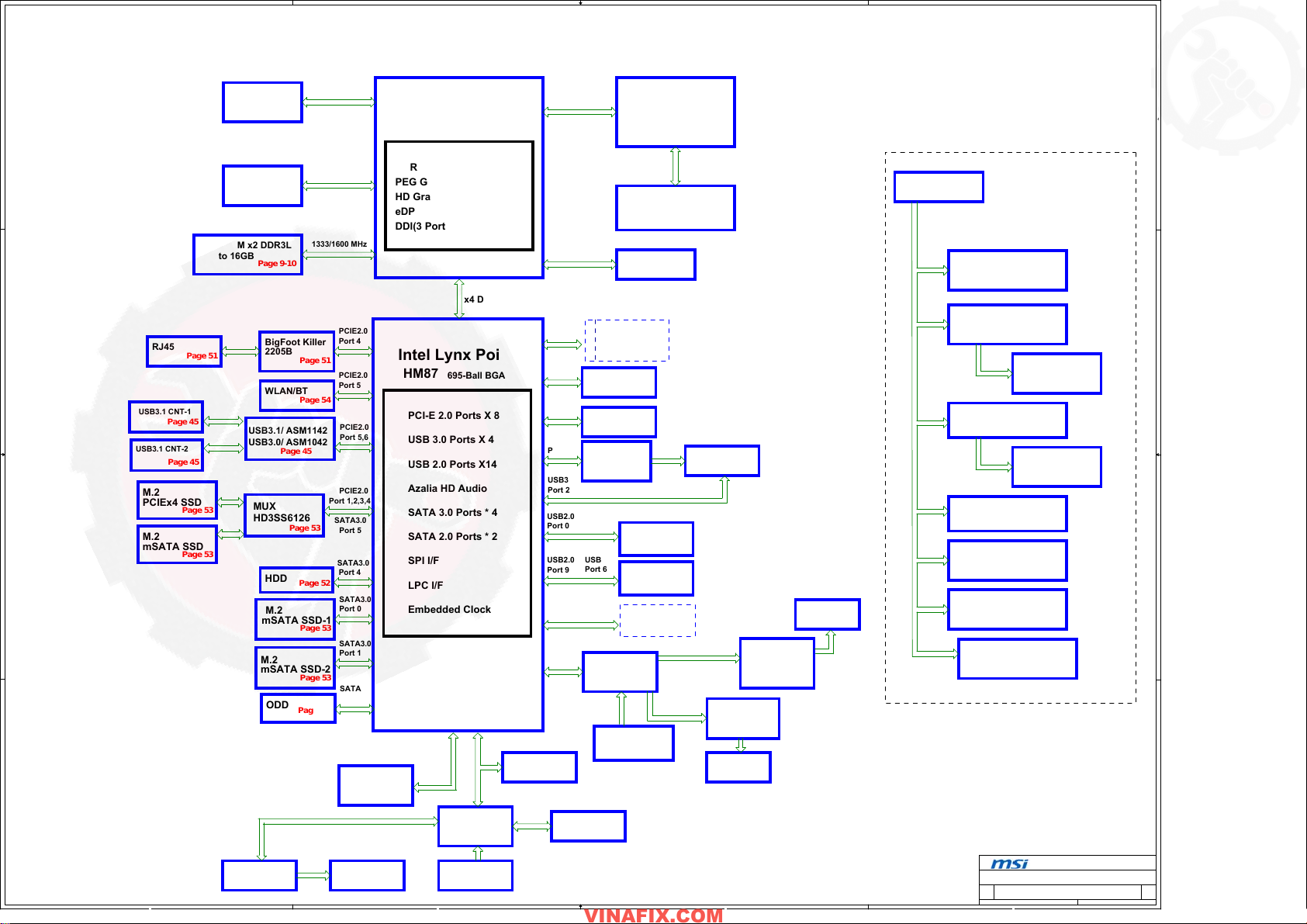

MSI MS-16J11 Schematic 0A

A

VINAFIX.COM

B

C

D

MS-16J1

DisplayPort

4 4

HDMI

DP139

Ver:0A

DDIB

Page 47

DDIC

Page 48

Intel Haswell-M

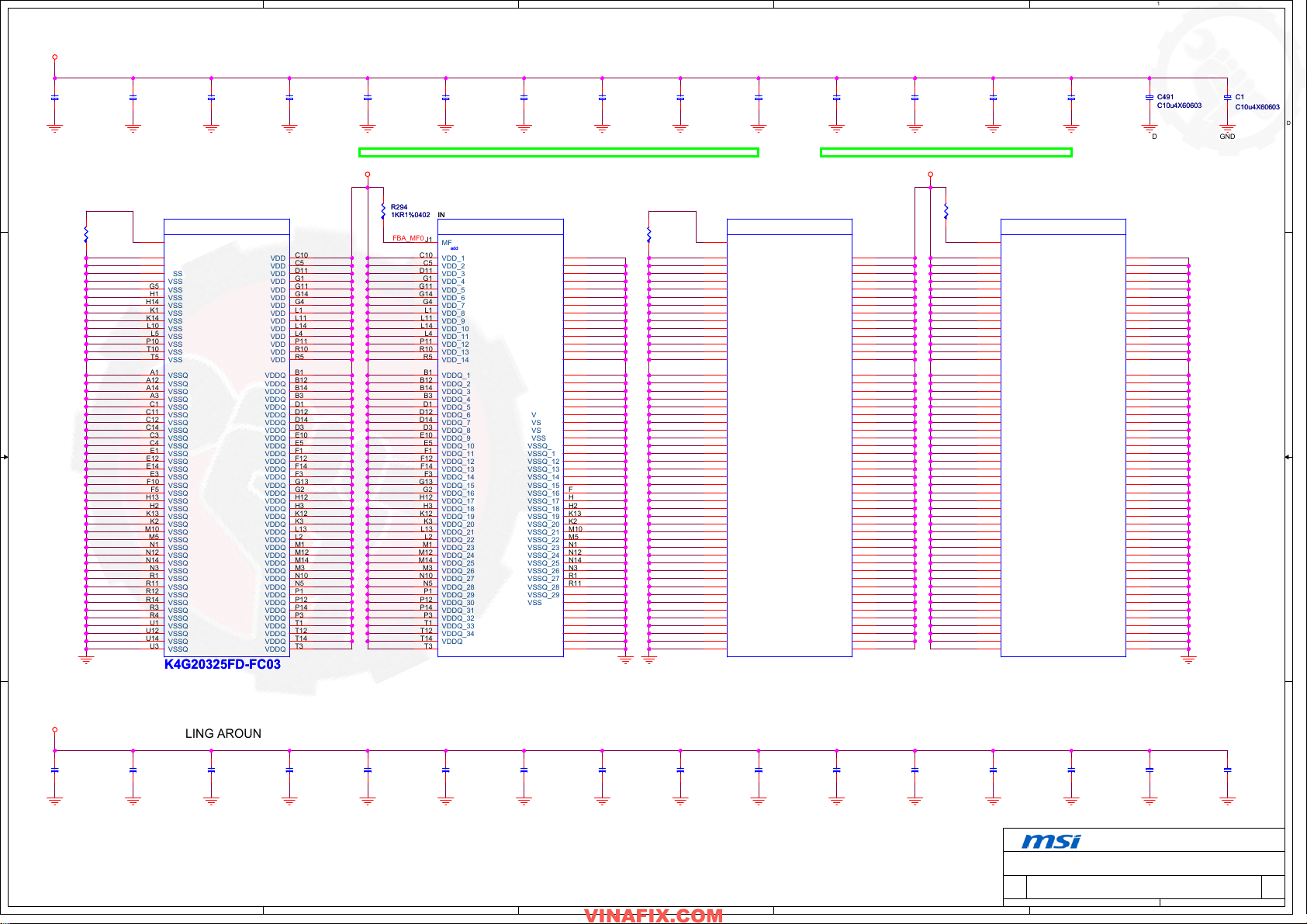

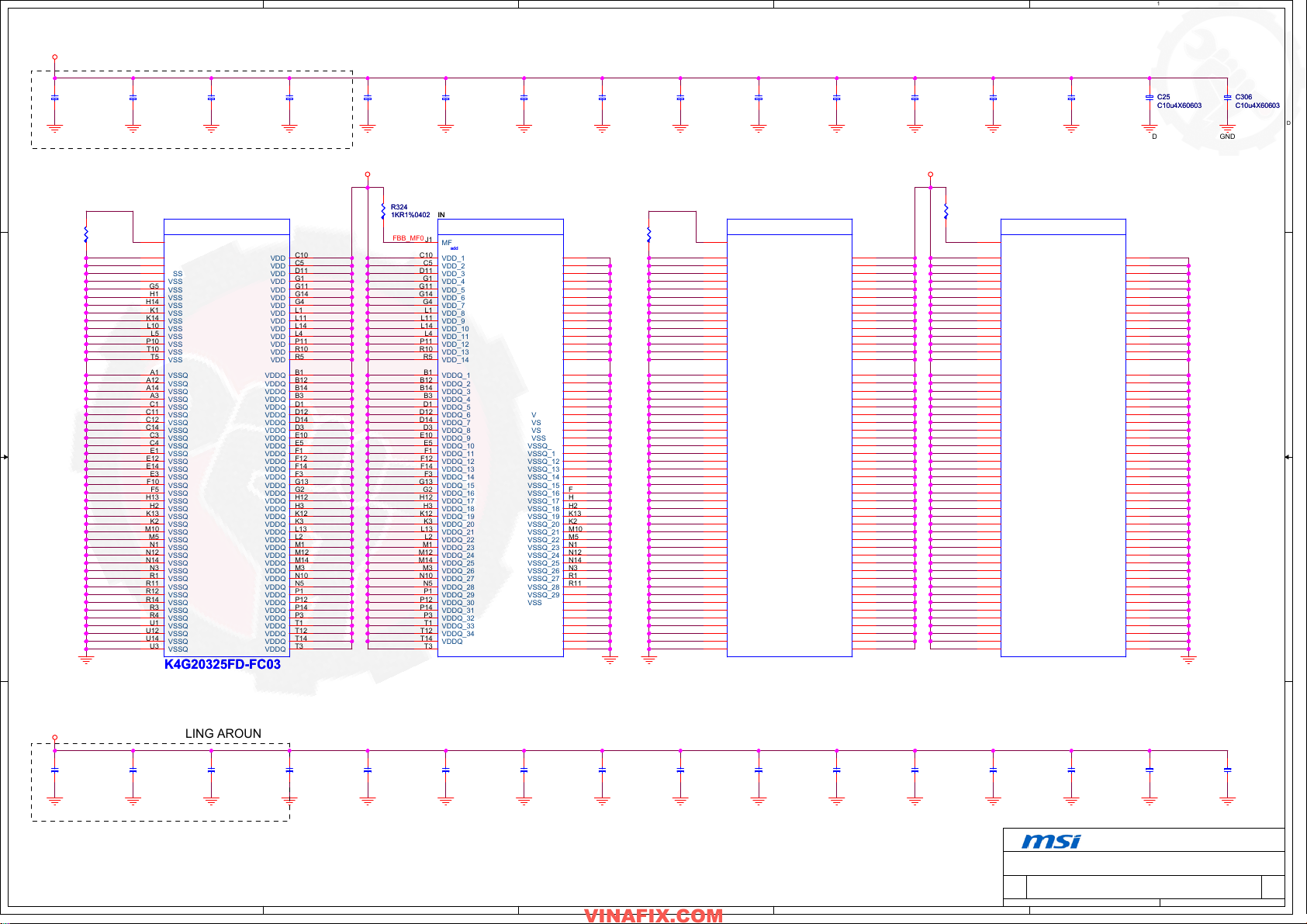

DDR3L

PEG Gen3 PCI-E x16

HD Graphic GT1/GT2/GT3

eDP

DDI(3 Ports)

SO-DIMM x2 DDR3L

Up to 16GB

Page 9-10

1333/1600 MHz

Shark Bay Mobilekp02113

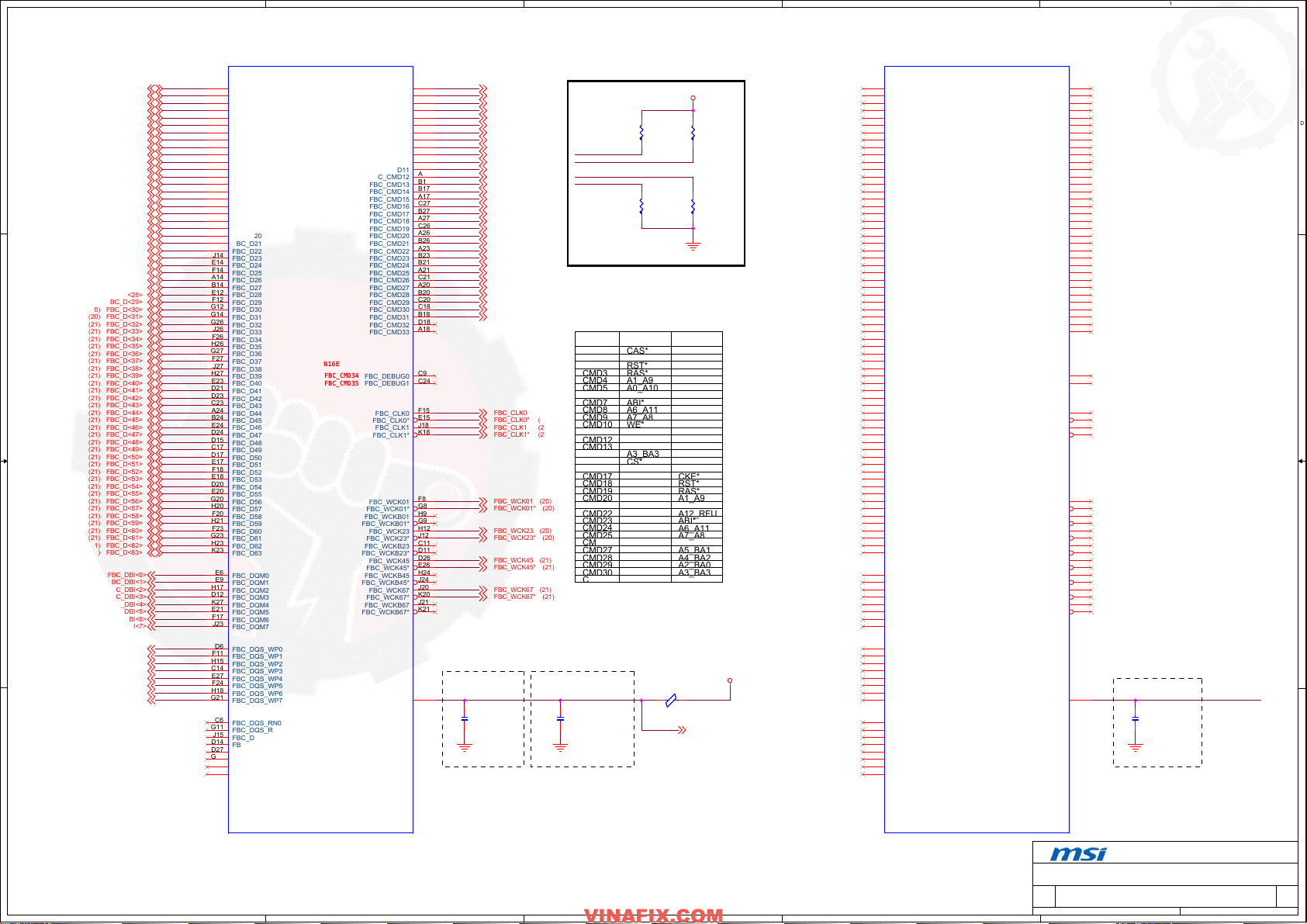

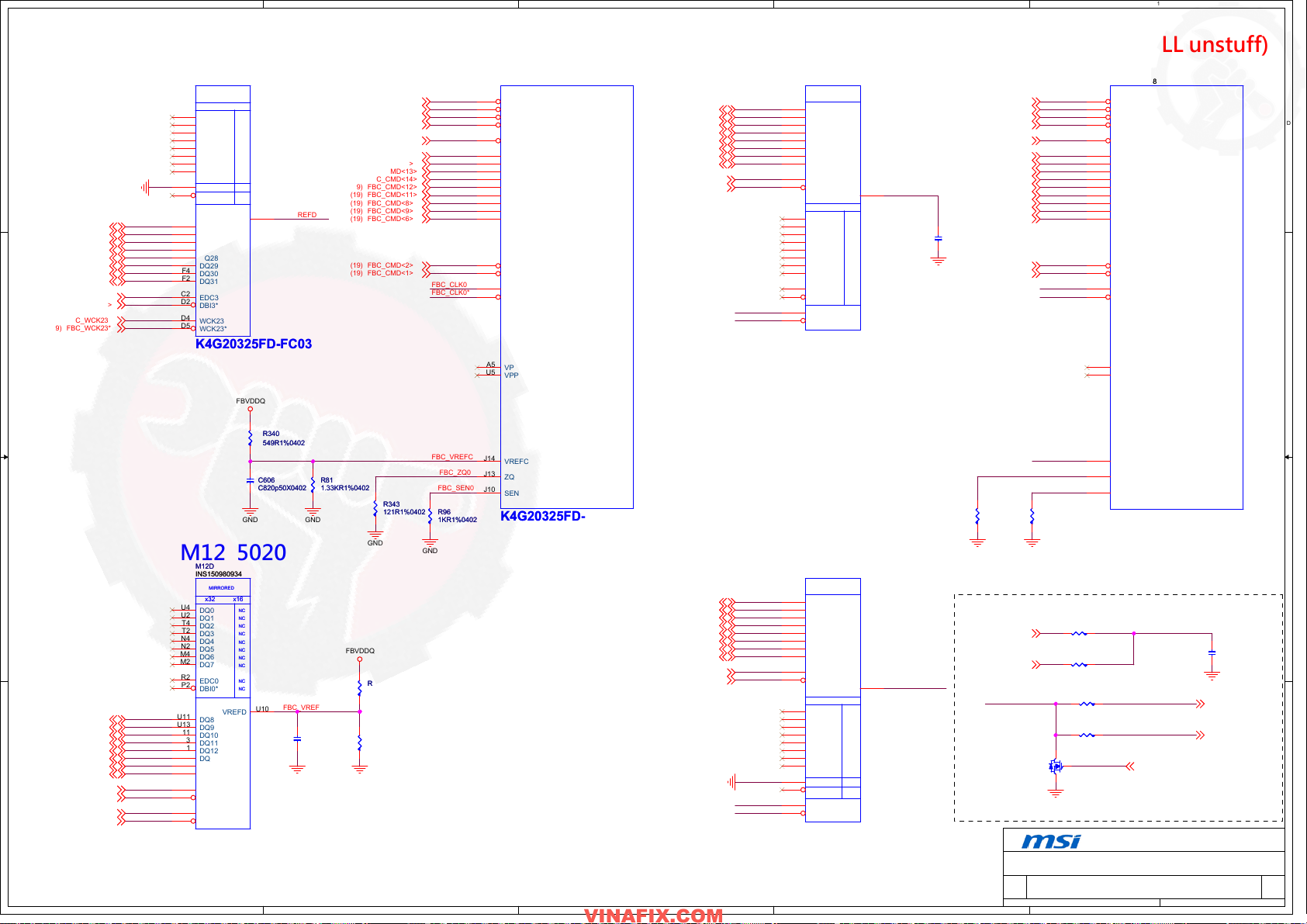

nVIDIA

N16E-GT(GTX 970M)

GB3-256_40*40mm

1745-Ball BGA

GDDR5 /3GB

(64Mx32bit)x12

eDP Panel

Page 11-31

Page 12-22

Page 42

1364-Ball BGA

Page 3-8

PCI-E x16 Gen3

8GT/s

eDP x4

Tuesday, July 29, 2014

Tuesday, July 29, 2014

Tuesday, July 29, 2014

DC JACK

Page 55

BQ24737RGRR

Battery Select/Charger

Page 55

x4 DMI(5GB/s)

TPS51125RGER

16J12

LPC Debug

Page 44

USB2.0

Port 12

USB2.0

Port 10

USB2.0

Port 11

USB2.0

Port 1

USB3.0

Port 2

USB2.0 USB3.0

Port 0

USB2.0

Port 9

USB2.0

Port 8

Azalia

USB3.0

Port 6

EC ROM

Card Reader

RTS5170

WLAN/BT

Camera CONN

iPad Charger

TPS2546RTER

Page 45

Port 1

Audio

ALC892-CG

HeadPhone

MicroPhone

Page 44

Page 54

Page 54

Page 42

USB2.0

USB3.0 CNT-2

USB3.0 CNT-3

USB2.0 CNT-4

(16J12)

Page 49

Page 50

Page 45

Page 46

Page 54

USB3.0 CNT-1

Page 45

Amplifier

APA3010

Woffer

C

Amplifier

APA2051

APA2031

Page 50

Page 50

Page 49

in-Speaker

Page 49

PCIE2.0

Page 51

Page 54

Page 52

Page 53

Page 53

Page 52

Port 4

PCIE2.0

Port 5

PCIE2.0

Port 5,6

PCIE2.0

Port 1,2,3,4

SATA3.0

Port 5

SATA3.0

Port 4

SATA3.0

Port 0

SATA3.0

Port 1

SATA2.0

Port 2

BIOS

8MB/ME

USB2.0

Port 7

LED KeyBoard

Intel Lynx Point

HM87

PCI-E 2.0 Ports X 8

USB 3.0 Ports X 4

USB 2.0 Ports X14

Azalia HD Audio

SATA 3.0 Ports * 4

SATA 2.0 Ports * 2

SPI I/F

LPC I/F

Embedded Clock

Page 34

KBC

KB3930B

Page 43

TouchPadEPF021J

B

695-Ball BGA

Page 32-41

Page 44

Page 46

3 3

RJ45

Page 51

BigFoot Killer

2205B

WLAN/BT

USB3.1 CNT-1

Page 45

USB3.1 CNT-2

Page 45

M.2

PCIEx4 SSD

Page 53

M.2

mSATA SSD

2 2

Page 53

USB3.1/ ASM1142

USB3.0/ ASM1042

Page 45

MUX

HD3SS6126

Page 53

HDD

M.2

mSATA SSD-1

M.2

mSATA SSD-2

ODD

1 1

Page 43

A

+3VSUS / +5VSUS

TPS51125RGER

+1_35VDIMM

TPS51211DSCR

+1_05VRUN

ISL95812HRZ

+VCC_CORE (CPU)

TPS51211DSCR

VRAM(FBVDDQ)

UP1642PQAG

NVVDD (dGPU)

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Page 56

MP2138DQT

+1_5VRUN

Page 57

APL5337KAI

+0.675VRUN

Page 58

Page 61

Page 59

Page 60

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Block Diagram

Block Diagram

Block Diagram

MS-16J1

MS-16J1

MS-16J1

D

Page 58

Page 57

170

170

170

0A

0A

0A

5

VINAFIX.COM

4

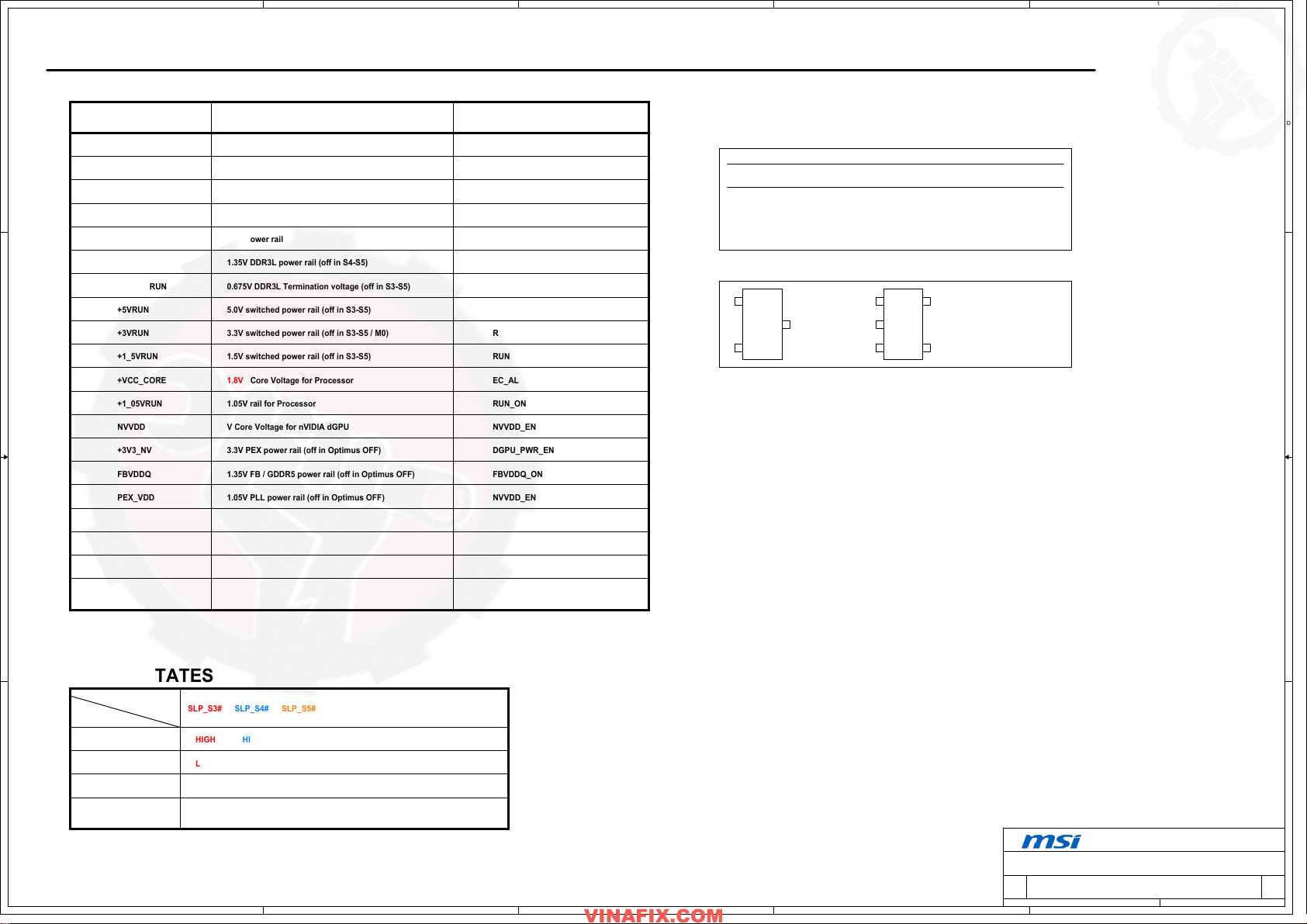

SCHEMATIC ANNOTATIONS AND BOARD INFORMATION

Voltage Rails

3

2

1

D D

C C

Voltage Description Control Signal

PWR_SRC AC ADAPTER OR BATTERY IN

+5VALW 5.0V always on power rail PWR_SRC

+3VALW

+5VSUS

+3VSUS

+0_675VRUN

+5VRUN

+3VRUN

+1_5VRUN 1.5V switched power rail (off in S3-S5)

+VCC_CORE Core Voltage for Processor EC_ALLSYSPG

+1_05VRUN

NVVDD

+3V3_NV

FBVDDQ

PEX_VDD

3.3V always on power rail

5.0V power rail

3.3V power rail

1.35V DDR3L power rail (off in S4-S5)

0.675V DDR3L Termination voltage (off in S3-S5)

5.0V switched power rail (off in S3-S5)

3.3V switched power rail (off in S3-S5 / M0)

1.8V

1.05V rail for Processor RUN_ON

V Core Voltage for nVIDIA dGPU

3.3V PEX power rail (off in Optimus OFF)

1.35V FB / GDDR5 power rail (off in Optimus OFF)

1.05V PLL power rail (off in Optimus OFF)

PWR_SRC

SUS_ON

SUS_ON

DIMM_ON+1_35VDIMM

PM_SLP_S3#

RUN_ON

RUN_ON

RUN_ON

NVVDD_EN

DGPU_PWR_EN#

FBVDDQ_ON

NVVDD_EN

Net Naming Conventions

Suffix

# = Active Low Signal

Prefix

H = Host

M = DDR Memory

TP = Test Point (does not connect anywhere else)

FB = DGPU VRAM

VIAxxx = Like Test Point, but using VIA.

PCB Footprints

SOT-23

1

3

As seen from top

2

1

2

3

5

4

SOT23-5

B B

POWER STATES

STATE

S0( Full ON)

S3( Suspend to RAM) ONHIGH

A A

S4( Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S3# +*VRUNSLP_S4# SLP_S5# +*VSUS

LOW OFF

LOW

LOW

LOW

Note : WHEN AC MODE , System turn on and +V*SUS always keep high

5

HIGHHIGHHIGH

HIGH

HIGH

LOW

+V*ALW

ON

ON

ON

OFF

OFF

4

Clocks

ONONON

OFFLOW

OFFONOFF

OFF

OFF

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Platform

Platform

Platform

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-16J1

MS-16J1

MS-16J1

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

270Tuesday, July 29, 2014

270Tuesday, July 29, 2014

270Tuesday, July 29, 2014

1

0A

0A

0A

5

VINAFIX.COM

4

3

2

1

R338

R338

1.8K1%0402

1.8K1%0402

JNC16 X_0402JNC16 X_0402

1 2

R337

R337

3.3KR1%0402

3.3KR1%0402

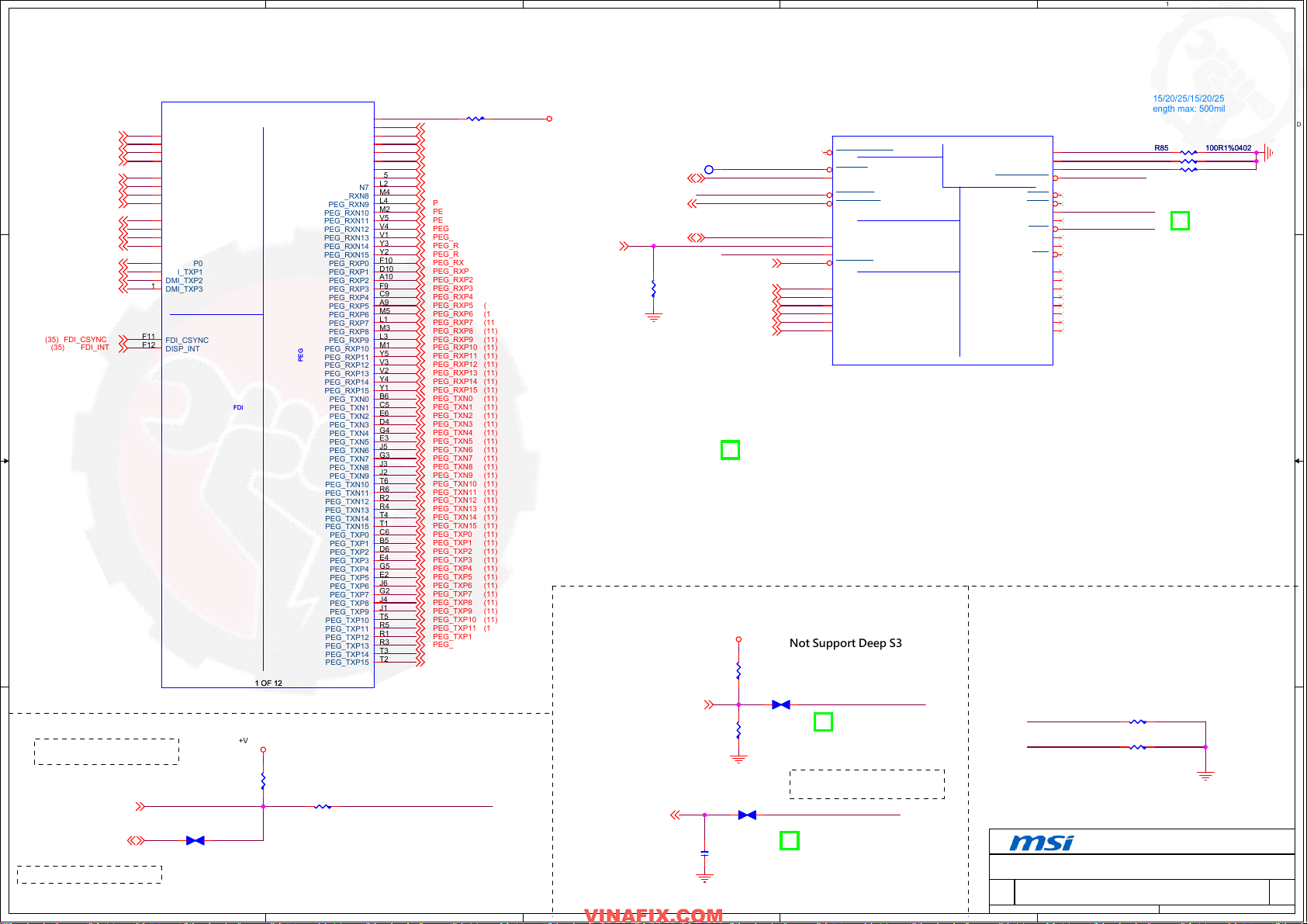

Haswell ( CLK,MISC,JTAG )Haswell ( DMI,PEG,FDI )

U68B

U68B

C51

PROC_DETECT

G50

CATERR

G51

PECI

E50

PROCHOT

D53

THERMTRIP

D52

PM_SYNC

F50

PWRGOOD

AP48

SM_DRAMPWROK

L54

PLTRSTIN

AC6

DPLL_REF_CLKN

AE6

DPLL_REF_CLKP

V6

SSC_DPLL_REF_CLKN

Y6

SSC_DPLL_REF_CLKP

AB6

BCLKN

AA6

BCLKP

Not Support Deep S3

1.35V

PM_DRAM_PWRGD_R

1K on CRB , 0R on DG

CPUDRAMRST#

HASWELL_BGA_E

HASWELL_BGA_E

MISC

MISC

PWRTHERMAL

PWRTHERMAL

CLOCK

CLOCK

2

SM_RCOMP_0/1/2 : 15/20/25/15/20/25

SM_RCOMP_0/1/2 Length max: 500mil

SM_RCOMP0_JNC

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

JTAG DDR3

JTAG DDR3

2 OF 12

2 OF 12

p.11 479493_479493_SharkBay_HSW_ext_rev2.0.pdf

Processor JTAG (TDI, TDO, TMS, TRST#, TCK) signals,

PREQ# and PRDY# signals signals have adequate

internal bias resistances to support the removal of the

external pull up and pull down on the board

when debug is no longer needed.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

BB51

SM_RCOMP1_JNC

BB53

SM_RCOMP2_JNC

BB52

CPUDRAMRST#

BE51

N53

PRDY

N52

PREQ

TCK

TMS

TRST

TDO

DBR

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

CPU-1 ( Host Bus )

CPU-1 ( Host Bus )

CPU-1 ( Host Bus )

MS-16J1

MS-16J1

MS-16J1

TDI

XDP_TCLK

XDP_TRST#

XDP_TCLK

N54

M51

XDP_TRST#

M53

N49

M49

F53

R51

R50

P49

N50

R49

P53

U51

P51

R327 X_51R1%0402R327 X_51R1%0402

R329 X_51R1%0402R329 X_51R1%0402

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

R85 100R1%0402R85 100R1%0402

R83 75R1%0402R83 75R1%0402

R84 100R1%0402R84 100R1%0402

1

GND

370Tuesday, July 29, 2014

370Tuesday, July 29, 2014

370Tuesday, July 29, 2014

0A

0A

of

0A

PEG_RCOMP

Width:12 mils

HASWELL_BGA_E

U68A

U68A

D D

C C

B B

DMI_TXN0(35)

DMI_TXN1(35)

DMI_TXN2(35)

DMI_TXN3(35)

DMI_TXP0(35)

DMI_TXP1(35)

DMI_TXP2(35)

DMI_TXP3(35)

DMI_RXN0(35)

DMI_RXN1(35)

DMI_RXN2(35)

DMI_RXN3(35)

DMI_RXP0(35)

DMI_RXP1(35)

DMI_RXP2(35)

DMI_RXP3(35)

FDI_CSYNC(35)

FDI_INT(35)

AB2

AB3

AC3

AC1

AB1

AB4

AC4

AC2

AF2

AF4

AG4

AG2

AF1

AF3

AG3

AG1

F11

F12

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

FDI_CSYNC

DISP_INT

EC Sink current 2 mA

A A

EC_PROCHOT#(44)

IMVP_PROCHOT#(61)

1 2

JNC5 X_0402JNC5 X_0402

HASWELL_BGA_E

DMI

DMI

FDI

FDI

1 OF 12

1 OF 12

+VCCIO_OUT

PEG

PEG

R56

R56

681R1%0402

681R1%0402

R44 56R0402R44 56R0402

PEG_RCOMP

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

AH6

E10

C10

B10

E9

D9

B9

L5

L2

M4

L4

M2

V5

V4

V1

Y3

Y2

F10

D10

A10

F9

C9

A9

M5

L1

M3

L3

M1

Y5

V3

V2

Y4

Y1

B6

C5

E6

D4

G4

E3

J5

G3

J3

J2

T6

R6

R2

R4

T4

T1

C6

B5

D6

E4

G5

E2

J6

G2

J4

J1

T5

R5

R1

R3

T3

T2

PEG_COMP

PEG_RXN0 (11)

PEG_RXN1 (11)

PEG_RXN2 (11)

PEG_RXN3 (11)

PEG_RXN4 (11)

PEG_RXN5 (11)

PEG_RXN6 (11)

PEG_RXN7 (11)

PEG_RXN8 (11)

PEG_RXN9 (11)

PEG_RXN10 (11)

PEG_RXN11 (11)

PEG_RXN12 (11)

PEG_RXN13 (11)

PEG_RXN14 (11)

PEG_RXN15 (11)

PEG_RXP0 (11)

PEG_RXP1 (11)

PEG_RXP2 (11)

PEG_RXP3 (11)

PEG_RXP4 (11)

PEG_RXP5 (11)

PEG_RXP6 (11)

PEG_RXP7 (11)

PEG_RXP8 (11)

PEG_RXP9 (11)

PEG_RXP10 (11)

PEG_RXP11 (11)

PEG_RXP12 (11)

PEG_RXP13 (11)

PEG_RXP14 (11)

PEG_RXP15 (11)

PEG_TXN0 (11)

PEG_TXN1 (11)

PEG_TXN2 (11)

PEG_TXN3 (11)

PEG_TXN4 (11)

PEG_TXN5 (11)

PEG_TXN6 (11)

PEG_TXN7 (11)

PEG_TXN8 (11)

PEG_TXN9 (11)

PEG_TXN10 (11)

PEG_TXN11 (11)

PEG_TXN12 (11)

PEG_TXN13 (11)

PEG_TXN14 (11)

PEG_TXN15 (11)

PEG_TXP0 (11)

PEG_TXP1 (11)

PEG_TXP2 (11)

PEG_TXP3 (11)

PEG_TXP4 (11)

PEG_TXP5 (11)

PEG_TXP6 (11)

PEG_TXP7 (11)

PEG_TXP8 (11)

PEG_TXP9 (11)

PEG_TXP10 (11)

PEG_TXP11 (11)

PEG_TXP12 (11)

PEG_TXP13 (11)

PEG_TXP14 (11)

PEG_TXP15 (11)

H_PROCHOT#_R

R74 24.9R1%0402R74 24.9R1%0402

Spacing:15 mils

Length:400 mils

+VCCIOA_OUT

H_CPUPWRGD(37)

10KR0402

10KR0402

DDR3_DRAMRST#(9,10)

47P close PWM

5

4

i7-4710HQ,(SR1PX),2.5GHz

TPJNC2TPJNC2

H_PECI(44)

H_THRMTRIP#(37)

H_PM_SYNC(35)

R50

R50

GND

PM_DRAM_PWRGD(35)

R,C Close SO-DIMM

3

VIA_H_CATERR#

H_PROCHOT#_R

PM_DRAM_PWRGD_R

PCH_PLTRST_CPU(37)

CLK_DPN(33)

CLK_DPP(33)

CLK_DP_SSCN(33)

CLK_DP_SSCP(33)

CLK_EXP#(33)

CLK_EXP(33)

+1_35VDIMM

GND

JNC17 X_0402JNC17 X_0402

1 2

EC50

EC50

X_C0.1u50X70402

X_C0.1u50X70402

GND

5

VINAFIX.COM

4

3

2

1

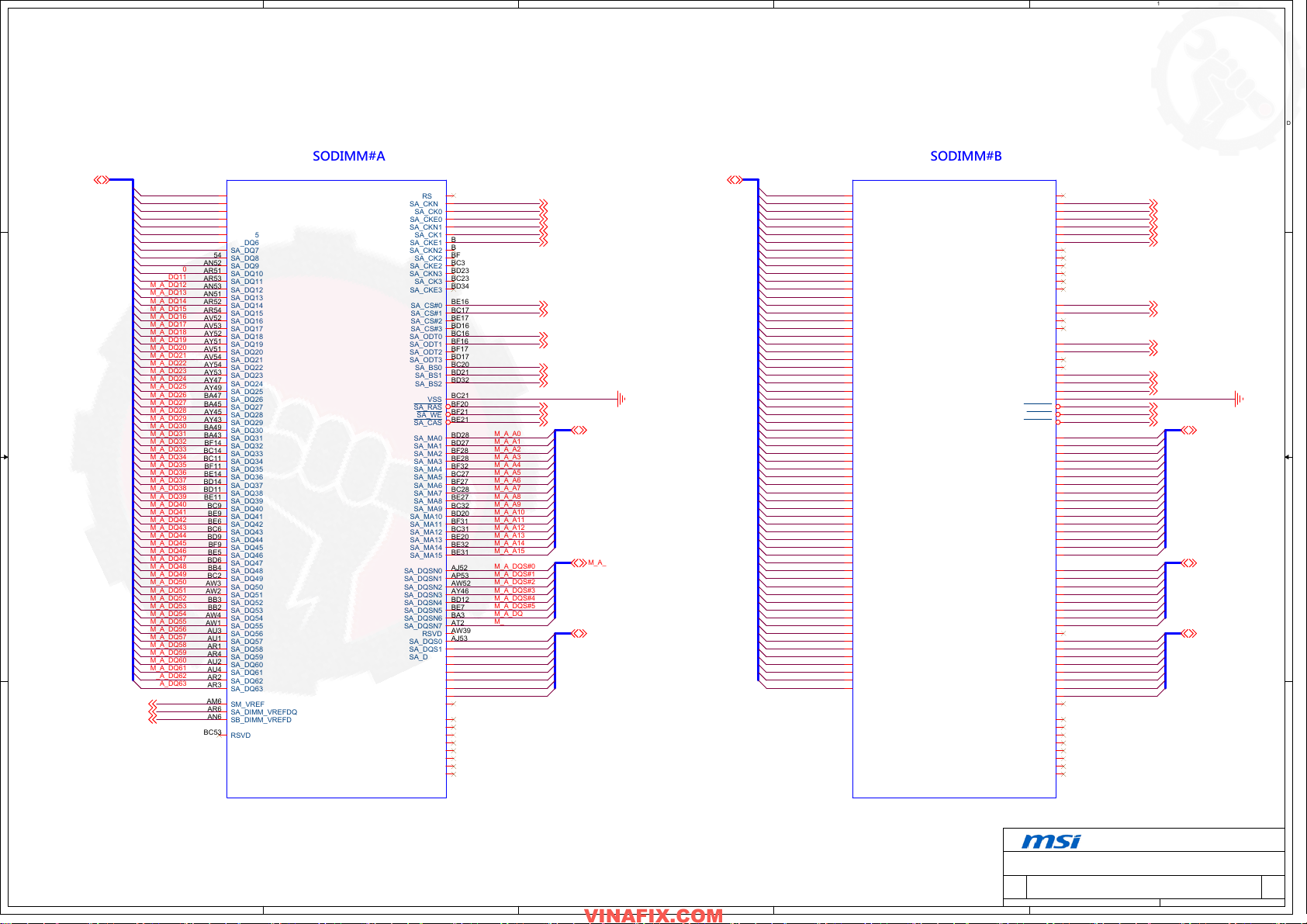

Haswell ( DDR3L )

D D

SODIMM#

HASWELL_BGA_E

U68C

M_A_DQ[63:0](9)

C C

B B

DIMM_SM_VREF(9,10)

M_VREF_DQ_DIMMA(9)

M_VREF_DQ_DIMMB(10)

A A

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AH54

AH52

AK51

AK54

AH53

AH51

AK52

AK53

AN54

AN52

AR51

AR53

AN53

AN51

AR52

AR54

AV52

AV53

AY52

AY51

AV51

AV54

AY54

AY53

AY47

AY49

BA47

BA45

AY45

AY43

BA49

BA43

BF14

BC14

BC11

BF11

BE14

BD14

BD11

BE11

BC9

BE9

BE6

BC6

BD9

BF9

BE5

BD6

BB4

BC2

AW3

AW2

BB3

BB2

AW4

AW1

AU3

AU1

AR1

AR4

AU2

AU4

AR2

AR3

AM6

AR6

AN6

BC53

U68C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

RSVD

HASWELL_BGA_E

3 OF 12

3 OF 12

A

RSVD

SA_CKN0

SA_CK0

SA_CKE0

SA_CKN1

SA_CK1

SA_CKE1

SA_CKN2

SA_CK2

SA_CKE2

SA_CKN3

SA_CK3

SA_CKE3

SA_CS#0

SA_CS#1

SA_CS#2

SA_CS#3

SA_ODT0

SA_ODT1

SA_ODT2

SA_ODT3

SA_BS0

SA_BS1

SA_BS2

VSS

SA_RAS

SA_WE

SA_CAS

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

RSVD

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

BD31

BE25

BF25

BE34

BD25

BC25

BF34

BE23

BF23

BC34

BD23

BC23

BD34

BE16

BC17

BE17

BD16

BC16

BF16

BF17

BD17

BC20

BD21

BD32

BC21

BF20

BF21

BE21

BD28

BD27

BF28

BE28

BF32

BC27

BF27

BC28

BE27

BC32

BD20

BF31

BC31

BE20

BE32

BE31

AJ52

AP53

AW52

AY46

BD12

BE7

BA3

AT2

AW39

AJ53

AP52

AW53

BA46

BE12

BD7

BA2

AT3

AW40

BA40

AY40

BA39

AY39

AV40

AU40

AV39

AU39

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_CLK_DDR#0 (9)

M_A_CLK_DDR0 (9)

M_A_CKE0 (9)

M_A_CLK_DDR#1 (9)

M_A_CLK_DDR1 (9)

M_A_CKE1 (9)

M_A_CS#0 (9)

M_A_CS#1 (9)

M_A_ODT0 (9)

M_A_ODT1 (9)

M_A_BS0 (9)

M_A_BS1 (9)

M_A_BS2 (9)

M_A_RAS# (9)

M_A_WE# (9)

M_A_CAS# (9)

M_A_A[15:0] (9)

M_A_DQS#[7:0] (9)

M_A_DQS[7:0] (9)

SODIMM#

HASWELL_BGA_E

U68D

M_B_DQ[63:0](10)

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AC54

AC52

AE51

AE54

AC53

AC51

AE52

AE53

AU47

AU49

AV43

AV45

AU43

AU45

AV47

AV49

BC49

BE49

BD47

BC47

BD49

BD50

BE47

BF47

BE44

BD44

BC42

BF42

BF44

BC44

BD42

BE42

BA16

AU16

BA15

AV15

AY16

AV16

AY15

AU15

AU12

AY12

BA10

AU10

AV12

BA12

AY10

AV10

AU8

BA8

AV6

BA6

AV8

AY8

AU6

AY6

AM2

AM3

AK1

AK4

AM1

AM4

AK2

AK3

U68D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HASWELL_BGA_E

4 OF 12

4 OF 12

B

RSVD

SB_CKN0

SB_CK0

SB_CKE0

SB_CKN1

SB_CK1

SB_CKE1

SB_CKN2

SB_CK2

SB_CKE2

SB_CKN3

SB_CK3

SB_CKE3

SB_CS#0

SB_CS#1

SB_CS#2

SB_CS#3

SB_ODT0

SB_ODT1

SB_ODT2

SB_ODT3

SB_BS0

SB_BS1

SB_BS2

VSS

SB_RAS

SB_WE

SB_CAS

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

RSVD

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

AY36

AW27

AV27

AU36

AW26

AV26

AU35

BA26

AY26

AV35

BA27

AY27

AV36

BA20

AY19

AU19

AW20

AY20

BA19

AV19

AW19

AY23

BA23

BA36

AU30

AV23

AW23

AV20

BA30

AW30

AY30

AV30

AW32

AY32

AT30

AV32

BA32

AU32

AU23

AY35

AW35

AU20

AW36

BA35

AD52

AU46

BD48

BD43

AW16

AW10

AW8

AL2

BE38

AD53

AV46

BE48

BE43

AW15

AW12

AW6

AL3

BD38

BF39

BE39

BF37

BE37

BD39

BC39

BC37

BD37

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_CLK_DDR#0 (10)

M_B_CLK_DDR0 (10)

M_B_CKE0 (10)

M_B_CLK_DDR#1 (10)

M_B_CLK_DDR1 (10)

M_B_CKE1 (10)

M_B_CS#0 (10)

M_B_CS#1 (10)

M_B_ODT0 (10)

M_B_ODT1 (10)

M_B_BS0 (10)

M_B_BS1 (10)

M_B_BS2 (10)

M_B_RAS# (10)

M_B_WE# (10)

M_B_CAS# (10)

M_B_A[15:0] (10)

M_B_DQS#[7:0] (10)

M_B_DQS[7:0] (10)

GNDGND

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

CPU-2 ( DDR3L )

CPU-2 ( DDR3L )

CPU-2 ( DDR3L )

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-16J1

MS-16J1

MS-16J1

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

470Tuesday, July 29, 2014

470Tuesday, July 29, 2014

470Tuesday, July 29, 2014

1

0A

0A

0A

5

VINAFIX.COM

4

3

2

1

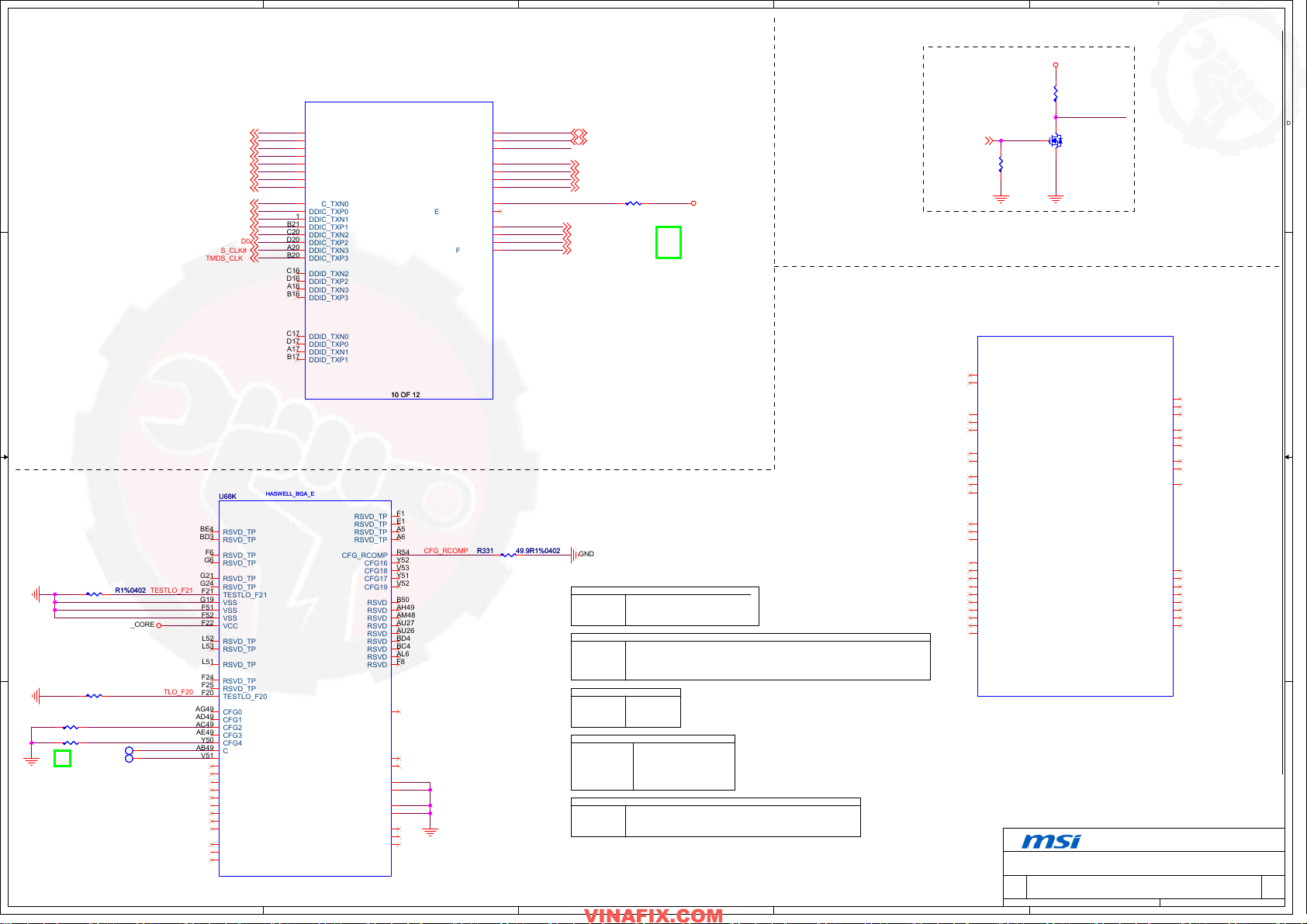

Display/Reserved

HASWELL_BGA_E

U68J

U68J

D D

DP

HDMI

C C

B B

GND

GND

GND

A A

R40 49.9R1%0402R40 49.9R1%0402

R41 49.9R1%0402R41 49.9R1%0402

R69 1KR0402R69 1KR0402

R61 1KR0402R61 1KR0402

TPJNC5TPJNC5

TPJNC4TPJNC4

+VCC_CORE

CFG2

CFG4

5

TESTLO_F21

TESTLO_F20

CFG5

CFG6

DDIB_LANE0_DN(47)

DDIB_LANE0_DP(47)

DDIB_LANE1_DN(47)

DDIB_LANE1_DP(47)

DDIB_LANE2_DN(47)

DDIB_LANE2_DP(47)

DDIB_LANE3_DN(47)

DDIB_LANE3_DP(47)

BE4

BD3

G21

G24

G19

AG49

AD49

AC49

AE49

Y50

AB49

V51

W51

Y49

Y54

Y53

W53

U53

V54

R53

R52

TMDS_CLK#(48)

TMDS_CLK(48)

F6

G6

F21

F51

F52

F22

L52

L53

L51

F24

F25

F20

L50

L49

E5

TMDS_D2#(48)

TMDS_D2(48)

TMDS_D1#(48)

TMDS_D1(48)

TMDS_D0#(48)

TMDS_D0(48)

U68K

U68K

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

TESTLO_F21

VSS

VSS

VSS

VCC

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

TESTLO_F20

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

RSVD

RSVD

RSVD

C25

D25

A25

B25

C24

D24

A24

B24

C21

D21

A21

B21

C20

D20

A20

B20

C16

D16

A16

B16

C17

D17

A17

B17

HASWELL_BGA_E

HASWELL_BGA_E

11 OF 12

11 OF 12

DDIB_TXN0

DDIB_TXP0

DDIB_TXN1

DDIB_TXP1

DDIB_TXN2

DDIB_TXP2

DDIB_TXN3

DDIB_TXP3

DDIC_TXN0

DDIC_TXP0

DDIC_TXN1

DDIC_TXP1

DDIC_TXN2

DDIC_TXP2

DDIC_TXN3

DDIC_TXP3

DDID_TXN2

DDID_TXP2

DDID_TXN3

DDID_TXP3

DDID_TXN0

DDID_TXP0

DDID_TXN1

DDID_TXP1

HASWELL_BGA_E

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

CFG_RCOMP

CFG16

CFG18

CFG17

CFG19

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

VSS

VSS

VSS

VSS

RSVD

RSVD

RSVD

10 OF 12

10 OF 12

F1

E1

A5

A6

R54

Y52

V53

Y51

V52

B50

AH49

AM48

AU27

AU26

BD4

BC4

AL6

F8

F16

G12

G10

H54

H53

H51

H52

N51

G53

H50

4

EDP_AUXN

EDP_AUXP

EDP_TXN0

EDP_TXN1

EDP_RCOMP

EDP_DISP_UTIL

CFG_RCOMP

GND

F15

F14

E14

EDP_HPD

C14

A12

D14

EDP_TXP0

B12

EDP_TXP1

AG6

E12

C12

FDI_TXN0

D12

FDI_TXP0

A14

FDI_TXN1

B14

FDI_TXP1

R331 49.9R1%0402R331 49.9R1%0402

EDP_AUXN (42)

EDP_HPD#

EDP_RCOMP

EDP_RCOMP

Width:20 mils

Spacing:25 mils

Length:100 mils

EDP_AUXP (42)

EDP_TX0_DN (42)

EDP_TX1_DN (42)

EDP_TX0_DP (42)

EDP_TX1_DP (42)

EDP_TX2_DN (42)

EDP_TX2_DP (42)

EDP_TX3_DN (42)

EDP_TX3_DP (42)

GND

PCI Express* Static x16 Lane Numbering Reversal

CFG2

MSR Privacy Bit Feature

CFG3

eDP enable

CFG4

PCI Express* Bifurcation

CFG[5:6]

PEG DEFER TRAINING

CFG7 1: (Default) PEG Train immediately following xxRESETB de assertion

To eDP Panal

R72 24.9R1%0402R72 24.9R1%0402

1 = Normal operation

0 = Lane numbers reversed.

1 = Debug capability is determined by IA32_Debug_Interface_MSR (0xC80) bit[0] setting

0 = IA32_Debug_Interface_MSR (0xC80) bit[0] default setting overridden

1 = Disabled

0 = Enabled

00 = 1 x8, 2 x4 PCI Express

01 = reserved

10 = 2 x8 PCI Express

11 = 1 x16 PCI Express

0: PEG Wait for BIOS for training

3

+VCCIOA_OUT

EDP_HPD(42)

U68L

U68L

A3

DAISY_CHAIN_NCTF_A3

A4

DAISY_CHAIN_NCTF_A4

A51

DAISY_CHAIN_NCTF_A51

A52

DAISY_CHAIN_NCTF_A52

A53

DAISY_CHAIN_NCTF_A53

B2

DAISY_CHAIN_NCTF_B2

B3

DAISY_CHAIN_NCTF_B3

B52

DAISY_CHAIN_NCTF_B52

B53

DAISY_CHAIN_NCTF_B53

B54

DAISY_CHAIN_NCTF_B54

BC1

DAISY_CHAIN_NCTF_BC1

BC54

DAISY_CHAIN_NCTF_BC54

BD1

DAISY_CHAIN_NCTF_BD1

BD54

DAISY_CHAIN_NCTF_BD54

BE1

DAISY_CHAIN_NCTF_BE1

BE2

DAISY_CHAIN_NCTF_BE2

BE3

DAISY_CHAIN_NCTF_BE3

BE52

DAISY_CHAIN_NCTF_BE52

BE53

DAISY_CHAIN_NCTF_BE53

BE54

DAISY_CHAIN_NCTF_BE54

BF2

DAISY_CHAIN_NCTF_BF2

BF3

DAISY_CHAIN_NCTF_BF3

BF4

DAISY_CHAIN_NCTF_BF4

2

+VCCIO_OUT

R37

R37

10KR0402

10KR0402

EDP_HPD#

DS

Q7

Q7

G

N-2N7002_SOT23

N-2N7002_SOT23

R112

R112

100KR0402

100KR0402

GND GND

HASWELL_BGA_E

HASWELL_BGA_E

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

BF51

BF52

BF53

C1

C2

C3

C54

D1

D54

AN35

AN37

AF9

AE9

G14

G17

AD45

AG45

570Tuesday, July 29, 2014

570Tuesday, July 29, 2014

570Tuesday, July 29, 2014

1

DAISY_CHAIN_NCTF_BF51

DAISY_CHAIN_NCTF_BF52

DAISY_CHAIN_NCTF_BF53

DAISY_CHAIN_NCTF_C1

DAISY_CHAIN_NCTF_C2

DAISY_CHAIN_NCTF_C3

DAISY_CHAIN_NCTF_C54

DAISY_CHAIN_NCTF_D1

DAISY_CHAIN_NCTF_D54

12 OF 12

12 OF 12

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

CPU-3 ( Display/Reserved )

CPU-3 ( Display/Reserved )

CPU-3 ( Display/Reserved )

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-16J1

MS-16J1

MS-16J1

Date: Sheet of

Date: Sheet of

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

0A

0A

0A

5

VINAFIX.COM

4

3

2

1

+VCC_CORE

95A

B43

VCC

22uF x 20 /0603

D D

C C

C11-2267313-T04

+VCC_CORE

C44 C22u6.3X0603C44 C22u6.3X0603

C51 C22u6.3X0603C51 C22u6.3X0603

C67 C22u6.3X0603C67 C22u6.3X0603

C528 C22u6.3X0603C528 C22u6.3X0603

C52 C22u6.3X0603C52 C22u6.3X0603

C50 C22u6.3X0603C50 C22u6.3X0603

C527 C22u6.3X0603C527 C22u6.3X0603

C533 C22u6.3X0603C533 C22u6.3X0603

C47 C22u6.3X0603C47 C22u6.3X0603

C534 C22u6.3X0603C534 C22u6.3X0603

C66 C22u6.3X0603C66 C22u6.3X0603

C46 C22u6.3X0603C46 C22u6.3X0603

C526 C22u6.3X0603C526 C22u6.3X0603

C92 C22u6.3X0603C92 C22u6.3X0603

C93 C22u6.3X0603C93 C22u6.3X0603

C49 C22u6.3X0603C49 C22u6.3X0603

C535 C22u6.3X0603C535 C22u6.3X0603

C45 C22u6.3X0603C45 C22u6.3X0603

C43 C22u6.3X0603C43 C22u6.3X0603

C53 C22u6.3X0603C53 C22u6.3X0603

10uF x 4 /060

GND

3

C11-1067333-Y01

B B

A A

+VCC_CORE

CPU_FC_PWR

C82

C82

X_C0.1u50X70402

X_C0.1u50X70402

Resever For BDW H

2-chips

C529 C10u6.3X5-HFC529 C10u6.3X5-HF

C537 C10u6.3X5-HFC537 C10u6.3X5-HF

C530 C10u6.3X5-HFC530 C10u6.3X5-HF

C536 C10u6.3X5-HFC536 C10u6.3X5-HF

+1_05VRUN

R36 X_0R1%0402R36 X_0R1%0402

EC_PCH_PWROK(35,44)

5

GND

C68

C68

X_C4.7u10X50805-HF

X_C4.7u10X50805-HF

GNDGND

R316 X_6.04KR1%0402R316 X_6.04KR1%0402

CPU_FC_PWR

CPU_FC_PWROK

R315

R315

X_2.67KR1%0402

X_2.67KR1%0402

GND

B45

B46

B48

C27

C28

C31

C32

C34

C36

C38

C39

C42

C43

C45

C46

C48

D27

D28

D31

D32

D34

D36

D38

D39

D42

D43

D45

D46

D48

E27

E28

E31

E32

E34

E36

E38

E39

E42

E43

E45

E46

E48

F27

F28

F31

F32

F34

F36

F38

F39

F42

F43

F45

F46

F48

G27

G29

G31

G32

G34

G36

G38

G39

G42

G43

G45

G46

G48

H11

H12

H13

H14

H16

H17

H18

H19

H20

H21

H23

H24

H25

H26

H27

H29

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

D5

FC_D5

D3

FC_D3

4

Haswell ( POWER )

HASWELL_BGA_E

HASWELL_BGA_E

5 OF 12

5 OF 12

U68E

U68E

RSVD

RSVD

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

RSVD

VCC

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

FC_F17

VCOMP_OUT

RSVD

RSVD

RSVD

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VSS

PWR_DEBUG

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J17

J21

J26

J31

AR29

AR31

AR33

AT13

AT19

AT23

AT27

AT32

AT36

AV37

AW22

AW25

AW29

AW33

AY18

BB21

BB22

BB26

BB27

BB30

BB31

BB34

BB36

BD22

BD26

BD30

BD33

BE18

BE22

BE26

BE30

BE33

AN31

L6

M6

AN22

AN18

C50

AH9

D51

F17

AK6

AN33

W9

J12

AR49

J53

J52

J50

B51

F19

E52

V49

U49

AM49

W49

V50

AN49

AJ49

AG50

AK49

AJ50

AP49

AB50

AP50

AD50

AM50

A36

A38

A39

A42

A43

A45

A46

A48

AA46

AA47

AA8

AA9

3

4.2 A

12

+

+

PEC7

PEC7

C330u2SO

C330u2SO

GND GND GND GND GND GND GND

+VCC_CORE

C286

C286

C1u25X0402

C1u25X0402

C396

C396

C1u25X0402

C1u25X0402

C295

C295

C1u25X0402

C1u25X0402

C320

C320

C10u6.3X5-HF

C10u6.3X5-HF

10u*3 / 06031u*3 / 0402

CLK and DATA Misatc

R30

R30

100R1%0402

100R1%0402

VCCSENSE (61)

FC_F17

300 m

R32 X_0R1%0402R32 X_0R1%0402

A

+VCCIOA_OUT

VR_SVID_ALERT#_R

PWR_DEBUG#

VIA_IVR_ERROR

VIA_IST_TRIGGER

If XDP not implemented, then Route Processor

PWR_DEBUG as a test point. This Test point must

be clearly labeled

+VCC_CORE

R317 43R0402R317 43R0402

TPJNC1TPJNC1

300 m

+1_05VRUN

TPJNC6TPJNC6

TPJNC3TPJNC3

+VCCIO_OUT

A

C75

C75

C4.7u10X0603

C4.7u10X0603

GND

+VCCIO_OUT

+VCCIO_OUT +VCCIO_OUT

Close to CP

2

2000mil

R322

R322

75R1%0402

75R1%0402

VR_SVID_ALERT# (61)

R326

R326

130R1%0402

130R1%0402

U

Title

Title

Title

CPU-4 ( Power )

CPU-4 ( Power )

CPU-4 ( Power )

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-16J1

MS-16J1

MS-16J1

Date: Sheet of

Date: Sheet of

Date: Sheet

+1_35VDIMM

C323

C324

C324

C10u6.3X5-HF

C10u6.3X5-HF

C323

C10u6.3X5-HF

C10u6.3X5-HF

h

s

SVID total Length not ove

6

"

+VCCIO_OUT

R23

R23

54.9R1%0402

54.9R1%0402

VR_SVID_CLK (61)

R19

R19

130R1%0402

130R1%0402

Close to IMVP

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

VR_SVID_DATA (61)

1

r

0A

0A

of

670Tuesday, July 29, 2014

670Tuesday, July 29, 2014

670Tuesday, July 29, 2014

0A

5

VINAFIX.COM

4

3

2

1

Haswell ( Power & GND )

VSSSENSE (61)

VSS_NCTFD2VSS_NCTF

VSS

VCC

E54

F54

VSS_NCTFG1VSS_NCTF

VSS_NCTF

VSS

VSS

VSS

F4

F40

F37

B27

A34

A32

VCC

VCC

VCC

R31 100R1%0402R31 100R1%0402

D50

VSS_SENSE

VSS

VSS

VSSF5VSS

VSS

VSS

F49

F44

G16

G13

G11

B42

B39

B36

B38

B34

B32

B31

B28

VCC

VCC

VCC

VCC

VCC

VCC

VCC

U68I

U68I

9 OF 12

9 OF 12

U68F

U68F

6 OF 12

6 OF 12

VCC

D D

C C

GND GND

Y9

W54

W52

Y48

VSS

VSS

VCC

W50

D40

N46

VSS

VSS

D44

N47

VSS

VSS

VCC

D49

Y7

AR22

AB48

G18

VSS

VSSW7VSS

VSS

VSS

VSS

VSS

VSSP9VSS

VSS

VSS

VSS

VSS

VSS

VSSD8VSS

VSS

E11

P45

N9

VCCN8VCC

VCC

VCC

VSS

VSS

E24

E22

E19

E17

E16

E20

E21

E15

T46

T45

R46

R47

P46

VCC

VCCR9VCCR8VCC

VCC

VCCP8VCC

VSS

VCC

A49

E25

U46

VSS_NCTF

VSS

A50

E26

U47

VSS

VCC

VSS_NCTFA8VSS_NCTF

VSS

E30

BA1

VSS_NCTF

VSS_NCTFB4VSS_NCTF

VSS

VSS

E37

E33

V45

VCCU9VCCU8VCC

BA54

BB1

BB54

VSS_NCTF

VSS

VSS

E40

E44

E49

W46

V46

VCC

VCCV8VCC

VSS_NCTF

VSS

VCC

BD2

E51

W47

VSS_NCTF

VSS

BF6

BF5

BF49

BD53

BF50

C53

VSS_NCTF

VSS_NCTF

VSS_NCTF

VSS_NCTF

VSS_NCTF

VSSF3VSS

VSSF2VSSE8VSS

VSS

F33

F30

F26

E53

A31

A28

A27

Y45

Y46

VCC

VCCY8VCC

VCC

VCC

VCCW8VCC

GND

+VCC_CORE

V48

VSS

VCC

U6

D19

N38

VSS

VCC

D22

N39

VSSU7VSS

VSS

VCC

D26

N40

VSS

VCC

D30

N42

VSS

VCC

D33

N43

W48

VSSV9VSSV7VSS

VSS

D37

N44

VCC

U54

U52

U50

VSS

VCC

T48

VSS

C33

M39

VCC

VSSU1VSSR7VSS

VSSC4VSS

VSS

C37

M42

M40

VCC

VCC

C40

M43

VSS

VCC

C44

M44

VSS

VCC

U48

C49

M45

VSS

VSSU5VSSU4VSSU3VSSU2VSS

VSSC8VSS

VSS

C52

M46

VCCM8VCC

D11

VSS

VSS

D15

N37

VCCM9VCC

N48

VSSM7VSS

VSS

VSS

BF30

K48

VCC

P4

VSSP7VSSP6VSS

VSS

VSS

VSS

VSSP5VSS

VSSP2VSSP1VSSN7VSSP3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VSS

VSS

BF7

C30

C26

C22

C19

C11

C15

BF46

BF48

BF43

M37

M38

L47

L46

L43

L44

L42

L39

L40

VCC

VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

BF38

BF36

BF33

BF41

L37

L38

VCC

VCCK9VCCK8VCC

M54

M52

M50

L48

M48

VSSJ7VSS

VSS

BD36

J38

VCC

K6

K1

VSS

VSS

VSS

VSSL7VSS

VSSK7VSSL9VSS

VSSK4VSSK3VSSK2VSSK5VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VSS

VSS

BF22

BF18

BF15

BF26

BF10

BF12

BE46

BE41

BE36

BE15

K45

K46

K44

K43

K40

K38

J46

J48

VCC

VCC

VCC

VCC

VCC

VCCJ9VCCJ8VCC

VCC

VSS

VSS

VSS

VSS

BD5

BE10

BD51

BD46

BD41

J45

J43

J42

J40

J39

VCC

VCC

VCC

VCC

J54

J51

J49

J44

H49

H44

VSS

G7

VSS

VSS

BC46

BC43

VSS

VSSG9VSS

VSSG8VSS

VSS

VSS

VSS

BC5

BC48

J14

J10

VCC

VCC

VCCH9VCCH8VCC

H7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

BC7

BD18

BD15

BD10

BC50

BC52

J37

J36

J29

J33

J24

J19

VCC

VCC

VCC

VCC

VCC

VCC

G54

G52

G49

G44

G37

G33

G26

G30

G40

G25

G23

G20

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

HASWELL_BGA_E

HASWELL_BGA_E

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

BC3

BC41

BC38

BC36

BC33

BC22

BC15

BC30

BC26

BC18

BC12

BC10

H48

H46

H45

H43

H42

H39

H40

H38

H36

H37

H33

H34

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

HASWELL_BGA_E

HASWELL_BGA_E

R48

P52

P50

P48

P54

B B

+VCC_CORE

+VCC_CORE

C79

C79

C1u25X0402

C1u25X0402

A A

GND GND GND GND GND GND GND GND GNDGND GNDGND GNDGND GND GND GNDGNDGND GND

5

C87

C87

C1u25X0402

C1u25X0402

VCC

VCC

AB8

AB45

AB46

C71

C71

C1u25X0402

C1u25X0402

VCC

VCC

AC46

VCC

VCC

VCC

VCC

VCC

VCC

AD8

AC8

AC9

AE47

AE46

AD46

AC47

C74

C74

C1u25X0402

C1u25X0402

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AF8

AE8

AG8

AH47

AH46

AG46

C86

C86

C1u25X0402

C1u25X0402

VCC

VCC

VCC

VCC

VCC

VCC

AK8

AH8

AJ45

AJ46

AK47

AK46

C84

C84

C1u25X0402

C1u25X0402

4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AL9

AL8

AM9

AM8

AL46

AL45

AM47

AM46

C85

C85

C1u25X0402

C1u25X0402

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AN16

AN17

AN15

AN14

AN13

AN12

AN10

C76

C76

C1u25X0402

C1u25X0402

VCC

VCC

VCC

VCC

VCC

VCC

AN25

AN23

AN24

AN21

AN20

AN19

C89

C89

C1u25X0402

C1u25X0402

VCC

VCC

VCC

VCC

VCC

VCC

AN34

AN32

AN29

AN30

AN27

AN26

VCC

VCC

VCC

VCC

AN40

AN38

AN39

AN36

C95

C95

C1u25X0402

C1u25X0402

3

VCC

VCC

AN42

AN41

VCC

VCC

VCC

AN45

AN44

AN43

C72

C72

C1u25X0402

C1u25X0402

VCC

VCC

VCC

AN9

AN8

AN46

VCC

VCC

AP12

AP10

VCC

VCC

VCC

VCC

AP16

AP15

AP14

AP13

C77

C77

C1u25X0402

C1u25X0402

AP17

VCC

VCC

AP18

VCC

VCC

VCC

AP21

AP20

AP19

C69

C69

C1u25X0402

C1u25X0402

VCC

VCC

AP24

AP23

AP22

VCC

VCC

AP25

VCC

VCC

VCC

AP29

AP26

AP27

C81

C81

C1u25X0402

C1u25X0402

VCC

VCC

AP31

AP30

VCC

AP32

VCC

VCC

AP34

AP33

VCC

VCC

VCC

AP37

AP38

AP36

AP35

C94

C94

C1u25X0402

C1u25X0402

2

VCC

VCC

AP39

VCC

VCC

AP41

AP40

VCC

VCC

VCC

VCC

AP44

AP46

AP42

AP43

C88

C88

C1u25X0402

C1u25X0402

AP47

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AP9

AP8

AR41

AR37

AR39

AR35

C80

C80

C1u25X0402

C1u25X0402

Title

Title

Title

CPU-6 ( Power & GND )

CPU-6 ( Power & GND )

CPU-6 ( Power & GND )

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-16J1

MS-16J1

MS-16J1

Date: Sheet of

Date: Sheet of

Date: Sheet of

VCC

AR43

VCC

VCC

AR46

AR45

VCC

VCC

VCC

H32

H31

H30

C70

C70

C1u25X0402

C1u25X0402

C73

C73

C1u25X0402

C1u25X0402

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

1

C78

C78

C1u25X0402

C1u25X0402

0A

0A

770Tuesday, July 29, 2014

770Tuesday, July 29, 2014

770Tuesday, July 29, 2014

0A

5

VINAFIX.COM

HASWELL_BGA_E

HASWELL_BGA_E

U68G

U68G

A11

VSS

A15

VSS

A19

VSS

A22

D D

C C

B B

A26

A30

A33

A37

A40

A44

AA1

AA2

AA3

AA4

AA48

AA5

AA7

AB5

AB51

AB52

AB53

AB54

AB7

AB9

AC48

AC5

AC50

AC7

AD48

AD51

AD54

AD7

AD9

AE1

AE2

AE3

AE4

AE48

AE5

AE50

AE7

AF5

AF6

AF7

AG48

AG5

AG51

AG52

AG53

AG54

AG7

AG9

AH1

AH2

AH3

AH4

AH48

AH5

AH50

AH7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

7 OF 12

7 OF 12

4

Haswell ( GND )

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ48

AJ51

AJ54

AK48

AK5

AK50

AK7

AK9

AL1

AL4

AL48

AL5

AL7

AM5

AM51

AM52

AM53

AM54

AM7

AN1

AN2

AN3

AN4

AN48

AN5

AN50

AN7

AP51

AP54

AP7

AR12

AR14

AR16

AR18

AR20

AR24

AR26

AR48

AR5

AR50

AR7

AR8

AR9

AT1

AT10

AT12

AT15

AT16

AT18

AT20

AT22

AT25

AT26

AT29

AT33

AT35

AT37

AT39

AT4

3

U68H

U68H

AT40

VSS

AT42

VSS

AT43

VSS

AT45

VSS

AT46

VSS

AT47

VSS

AT49

VSS

AT5

VSS

AT50

VSS

AT51

VSS

AT52

VSS

AT53

VSS

AT54

VSS

AT6

VSS

AT8

VSS

AT9

VSS

AU13

VSS

AU18

VSS

AU22

VSS

AU25

VSS

AU29

VSS

AU33

VSS

AU37

VSS

AU42

VSS

AU5

VSS

AU9

VSS

AV1

VSS

AV13

VSS

AV18

VSS

AV2

VSS

AV22

VSS

AV25

VSS

AV29

VSS

AV3

VSS

AV33

VSS

AV4

VSS

AV42

VSS

AV5

VSS

AV50

VSS

AV9

VSS

AW13

VSS

AW18

VSS

AW37

VSS

AW42

VSS

AW43

VSS

AW45

VSS

AW46

VSS

AW47

VSS

AW49

VSS

AW5

VSS

AW50

VSS

AW51

VSS

AW54

VSS

AW9

VSS

AY13

VSS

AY22

VSS

AY25

VSS

AY29

VSS

AY33

VSS

AY37

VSS

AY42

VSS

2

HASWELL_BGA_E

HASWELL_BGA_E

8 OF 12

8 OF 12

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AY50

AY9

B11

B15

B19

B22

B26

B30

B33

B37

B40

B44

B49

B8

BA13

BA18

BA22

BA25

BA29

BA33

BA37

BA4

BA42

BA5

BA50

BA51

BA52

BA53

BA9

BB10

BB11

BB12

BB14

BB15

BB16

BB17

BB18

BB20

BB23

BB25

BB28

BB32

BB33

BB37

BB38

BB39

BB41

BB42

BB43

BB44

BB46

BB47

BB48

BB49

BB5

BB6

BB7

BB9

1

A A

5

4

3

GND GNDGNDGND

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

CPU-5 ( GND )

CPU-5 ( GND )

CPU-5 ( GND )

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

0A

0A

MS-16J1

MS-16J1

MS-16J1

Date: Sheet

Date: Sheet

Date: Sheet

2

of

870Tuesday, July 29, 2014

of

870Tuesday, July 29, 2014

of

870Tuesday, July 29, 2014

1

0A

5

VINAFIX.COM

4

3

2

1

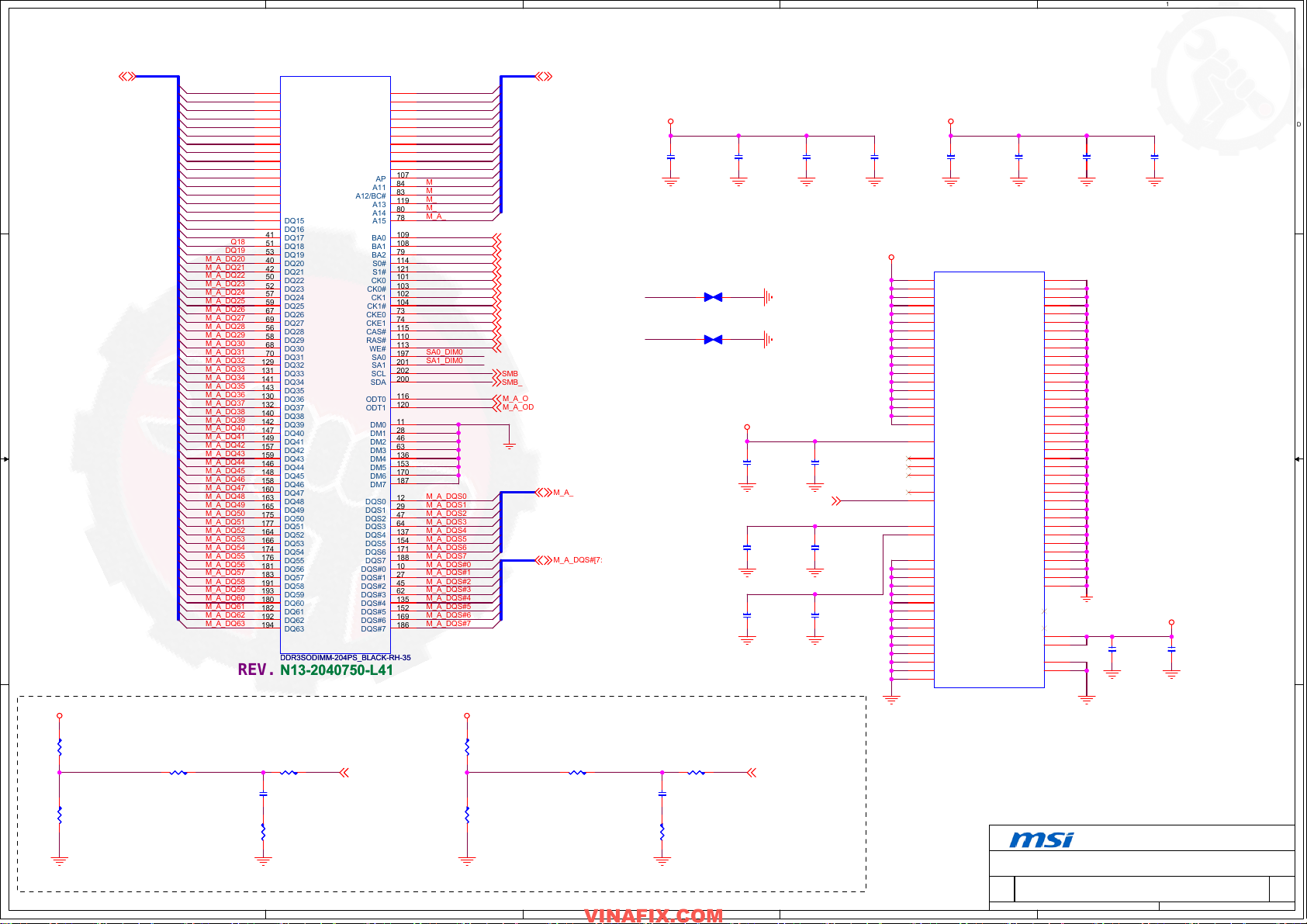

SODIMM#A

SOCKET1A

M_A_DQ[63:0](4)

D D

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

SOCKET1A

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

DDR3SODIMM-204PS_BLACK-RH-35

DDR3SODIMM-204PS_BLACK-RH-35

N13-2040750-L41

N13-2040750-L41

REV.

A10/AP

A11

A12/BC#

A13

A14

A15

BA0

BA1

BA2

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

109

108

79

114

121

101

103

102

104

73

74

115

110

113

197

201

202

200

116

120

11

28

46

63

136

153

170

187

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

SA0_DIM0

SA1_DIM0

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

+1_35VDIMM+1_35VDIMM

M_A_BS0 (4)

M_A_BS1 (4)

M_A_BS2 (4)

M_A_CS#0 (4)

M_A_CS#1 (4)

M_A_CLK_DDR0 (4)

M_A_CLK_DDR#0 (4)

M_A_CLK_DDR1 (4)

M_A_CLK_DDR#1 (4)

M_A_CKE0 (4)

M_A_CKE1 (4)

M_A_CAS# (4)

M_A_RAS# (4)

M_A_WE# (4)

SMB_CLK_DIMM (10,34)

SMB_DATA_DIMM (10,34)

M_A_ODT0 (4)

M_A_ODT1 (4)

M1(used for S3)

M3(used for S0),maybe to over-ride

Active when soft-start

M_A_A0

98

M_A_A[15:0] (4)

M_A_DQS[7:0] (4)

M_A_DQS#[7:0] (4)

+1_35VDIMM +1_35VDIMM

C367

C375

C375

C1u25X0402

C1u25X0402

GND GND GND GND GND GND GNDGND

SA0_DIM0

SA1_DIM0

1 2

JNC8 X_0402JNC8 X_0402

1 2

JNC9 X_0402JNC9 X_0402

C367

C1u25X0402

C1u25X0402

+3VRUN

C372

C372

C0.1u50X70402

C0.1u50X70402

DDR3_DRAMRST#(3,10)

M_VREF_DQ_DIMM0_R

C371

C371

C0.1u50X70402

C0.1u50X70402

M_VREF_CA_DIMM0

C383

C383

C0.1u50X70402

C0.1u50X70402

GND

GND

C373

C373

C1u25X0402

C1u25X0402

C365

C365

C2.2u6.3X0402

C2.2u6.3X0402

C364

C364

C2.2u6.3X0402

C2.2u6.3X0402

C382

C382

C2.2u6.3X0402

C2.2u6.3X0402

C405

C405

C1u25X0402

C1u25X0402

+1_35VDIMM

SOCKET1B

SOCKET1B

75

VDD

76

VDD

81

VDD

82

VDD

87

VDD

88

VDD

93

VDD

94

VDD

99

VDD

100

VDD

105

VDD

106

VDD

111

VDD

112

VDD

117

VDD

118

VDD

123

VDD

124

VDD

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS

3

VSS

8

VSS

9

VSS

13

VSS

14

VSS

19

VSS

20

VSS

25

VSS

26

VSS

31

VSS

32

VSS

37

VSS

38

VSS

43

VSS

DDR3SODIMM-204PS_BLACK-RH-35

DDR3SODIMM-204PS_BLACK-RH-35

N13-2040750-L41

N13-2040750-L41

C392

C392

C10u6.3X5-HF

C10u6.3X5-HF

C393

C393

C10u6.3X5-HF

C10u6.3X5-HF

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MEC1

MEC2

VTT

VTT

205

206

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

MEC1

MEC2

203

204

205

206

C377

C377

C10u6.3X5-HF

C10u6.3X5-HF

C366

C366

C1u25X0603

C1u25X0603

C376

C376

C10u6.3X5-HF

C10u6.3X5-HF

+0_675VRUN

C395

C395

C1u25X0603

C1u25X0603

R149

R149

1KR1%0402

1KR1%0402

M_VREF_DQ_DIMM0_R M_VREF_CA_DIMM0DQ_A

A A

R150

R150

1KR1%0402

1KR1%0402

5

Close to

DIMM

R147 X_0R1%0402R147 X_0R1%0402R148 2R1%0402R148 2R1%0402

C363

C363

C0.022u10X0402

C0.022u10X0402

R146

R146

24.9R1%0402

24.9R1%0402

R153

R153

1KR1%0402

1KR1%0402

M_VREF_DQ_DIMMA (4) DIMM_SM_VREF (4,10)

R157 2R1%0402R157 2R1%0402

GC GC

R156

R156

1KR1%0402

1KR1%0402

GND GNDGND GND

4

Close to

DIMM

CA_A

R155 X_0R1%0402R155 X_0R1%0402

C385

C385

C0.022u10X0402

C0.022u10X0402

R160

R160

24.9R1%0402

24.9R1%0402

3

Vref DQ & CA

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

DDR3L SODIMM 0

DDR3L SODIMM 0

DDR3L SODIMM 0

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-16J1

MS-16J1

MS-16J1

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

970Tuesday, July 29, 2014

970Tuesday, July 29, 2014

970Tuesday, July 29, 2014

1

0A

0A

0A

5

VINAFIX.COM

4

3

2

1

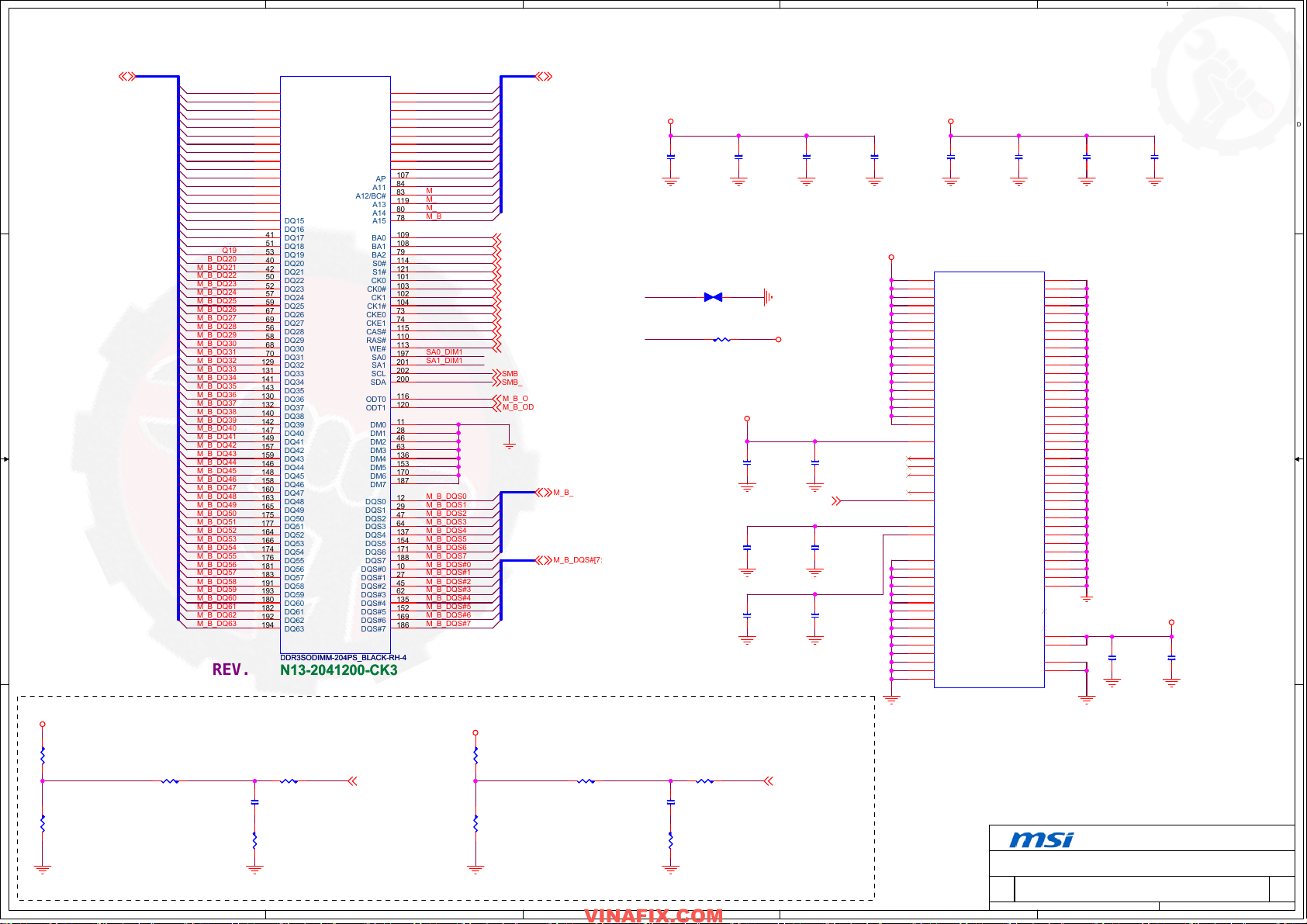

SODIMM#B

SOCKET2A

M_B_DQ[63:0](4)

D D

C C

B B

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

REV.

+1_35VDIMM

R161

R161

1KR1%0402

1KR1%0402

R163 2R1%0402R163 2R1%0402

A A

R164

R164

1KR1%0402

1KR1%0402

5

SOCKET2A

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

DDR3SODIMM-204PS_BLACK-RH-4

DDR3SODIMM-204PS_BLACK-RH-4

N13-2041200-CK3

N13-2041200-CK3

A12/BC#

Close to

DIMM

R158 X_0R1%0402R158 X_0R1%0402

C384

C384

C0.022u10X0402

C0.022u10X0402

R159

R159

24.9R1%0402

24.9R1%0402

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A13

A14

A15

BA0

BA1

BA2

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

M_VREF_DQ_DIMMB (4) DIMM_SM_VREF (4,9)

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

109

108

79

114

121

101

103

102

104

73

74

115

110

113

197

201

202

200

116

120

11

28

46

63

136

153

170

187

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

4

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

SA0_DIM1

SA1_DIM1

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

+1_35VDIMM

M_B_BS0 (4)

M_B_BS1 (4)

M_B_BS2 (4)

M_B_CS#0 (4)

M_B_CS#1 (4)

M_B_CLK_DDR0 (4)

M_B_CLK_DDR#0 (4)

M_B_CLK_DDR1 (4)

M_B_CLK_DDR#1 (4)

M_B_CKE0 (4)

M_B_CKE1 (4)

M_B_CAS# (4)

M_B_RAS# (4)

M_B_WE# (4)

SMB_CLK_DIMM (9,34)

SMB_DATA_DIMM (9,34)

M_B_ODT0 (4)

M_B_ODT1 (4)

R191

R191

1KR1%0402

1KR1%0402

R190

R190

1KR1%0402

1KR1%0402

GND GNDGNDGND

M_B_A0

98

M_B_A[15:0] (4)

M_B_DQS[7:0] (4)

M_B_DQS#[7:0] (4)

R193 2R1%0402R193 2R1%0402

+1_35VDIMM

C370

C404

C404

C10u6.3X5-HF

C10u6.3X5-HF

GND GND GNDGND GND GND GNDGND

SA0_DIM1

JNC10 X_0402JNC10 X_0402

SA1_DIM1

R162 10KR1%0402R162 10KR1%0402

C370

C10u6.3X5-HF

C10u6.3X5-HF

12

+3VRUN

C390

C390

C0.1u50X70402

C0.1u50X70402

DDR3_DRAMRST#(3,9)

M_VREF_DQ_DIMM1_R

C397

C397

C0.1u50X70402

C0.1u50X70402

M_VREF_CA_DIMM1

C408

C408

C0.1u50X70402

C0.1u50X70402

GND

+3VRUN

C403

C403

C10u6.3X5-HF

C10u6.3X5-HF

C398

C398

C2.2u6.3X0402

C2.2u6.3X0402

C391

C391

C2.2u6.3X0402

C2.2u6.3X0402

C407

C407

C2.2u6.3X0402

C2.2u6.3X0402

Close to

DIMM

CA_BM_VREF_DQ_DIMM1_R DQ_B M_VREF_CA_DIMM1

R188 X_0R1%0402R188 X_0R1%0402

C409

C409

C0.022u10X0402

C0.022u10X0402

R192

R192

24.9R1%0402

24.9R1%0402

Vref DQ & CA

3

C369

C369

C10u6.3X5-HF

C10u6.3X5-HF

+1_35VDIMM

+1_35VDIMM

C406

C406

C1u25X0402

C1u25X0402

SOCKET2B

SOCKET2B

75

VDD

76

VDD

81

VDD

82

VDD

87

VDD

88

VDD

93

VDD

94

VDD

99

VDD

100

VDD

105

VDD

106

VDD

111

VDD

112

VDD

117

VDD

118

VDD

123

VDD

124

VDD

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS

3

VSS

8

VSS

9

VSS

13

VSS

14

VSS

19

VSS

20

VSS

25

VSS

26

VSS

31

VSS

32

VSS

37

VSS

38

VSS

43

VSS

DDR3SODIMM-204PS_BLACK-RH-4

DDR3SODIMM-204PS_BLACK-RH-4

N13-2041200-CK3

N13-2041200-CK3

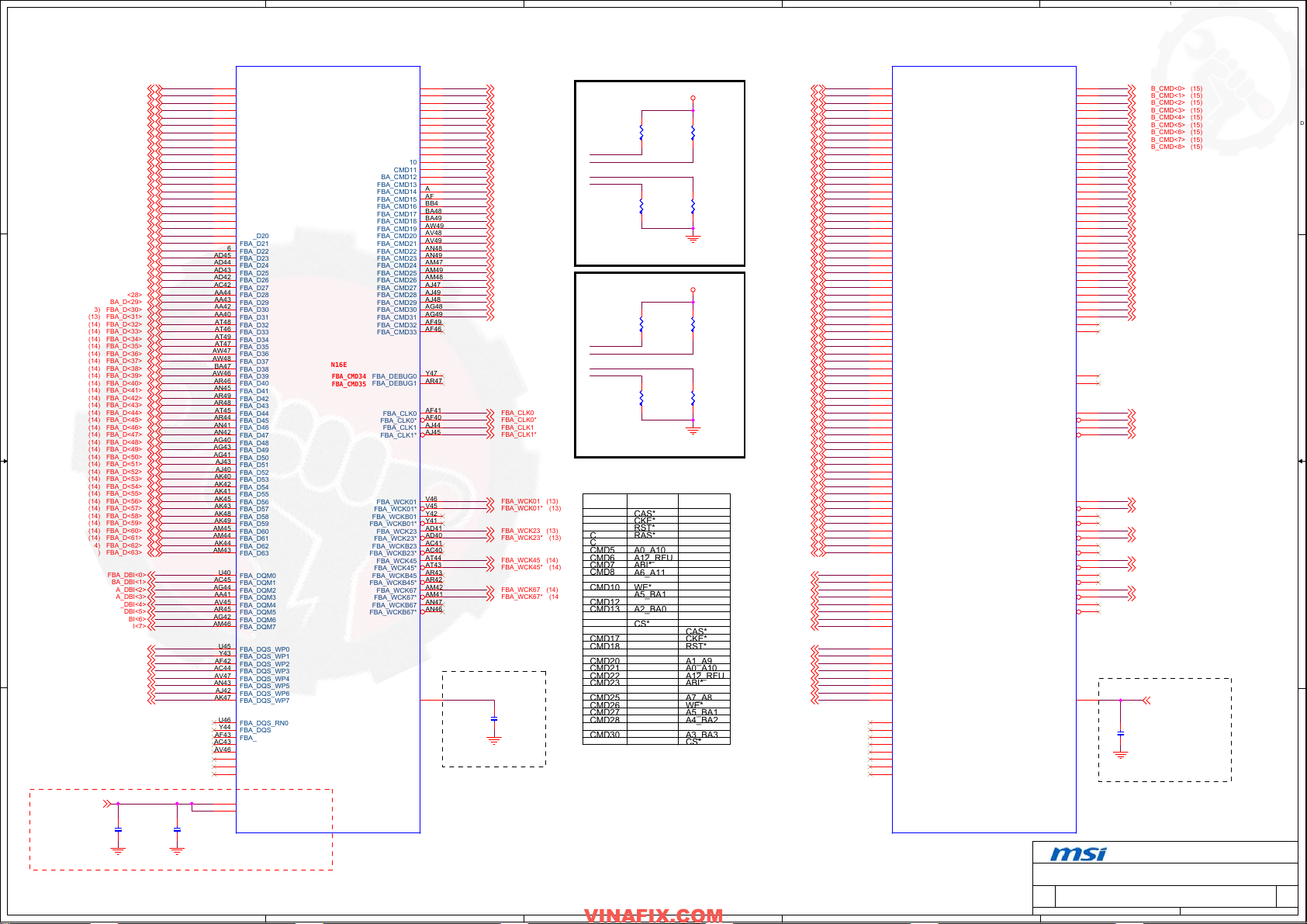

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

C399

C399

C1u25X0402

C1u25X0402

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MEC1

MEC2

VTT

VTT

205

206

DDR3L SODIMM 1

DDR3L SODIMM 1

DDR3L SODIMM 1

MS-16J1

MS-16J1

MS-16J1

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

MEC1

MEC2

203

204

205

206

C368

C368

C1u25X0402

C1u25X0402

C374

C374

C1u25X0603

C1u25X0603

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

C287

C287

C1u25X0402

C1u25X0402

+0_675VRUN

C400

C400

C1u25X0603

C1u25X0603

1

0A

0A

10 70Tuesday, July 29, 2014

10 70Tuesday, July 29, 2014

10 70Tuesday, July 29, 2014

0A

5

VINAFIX.COM

4

3

2

1

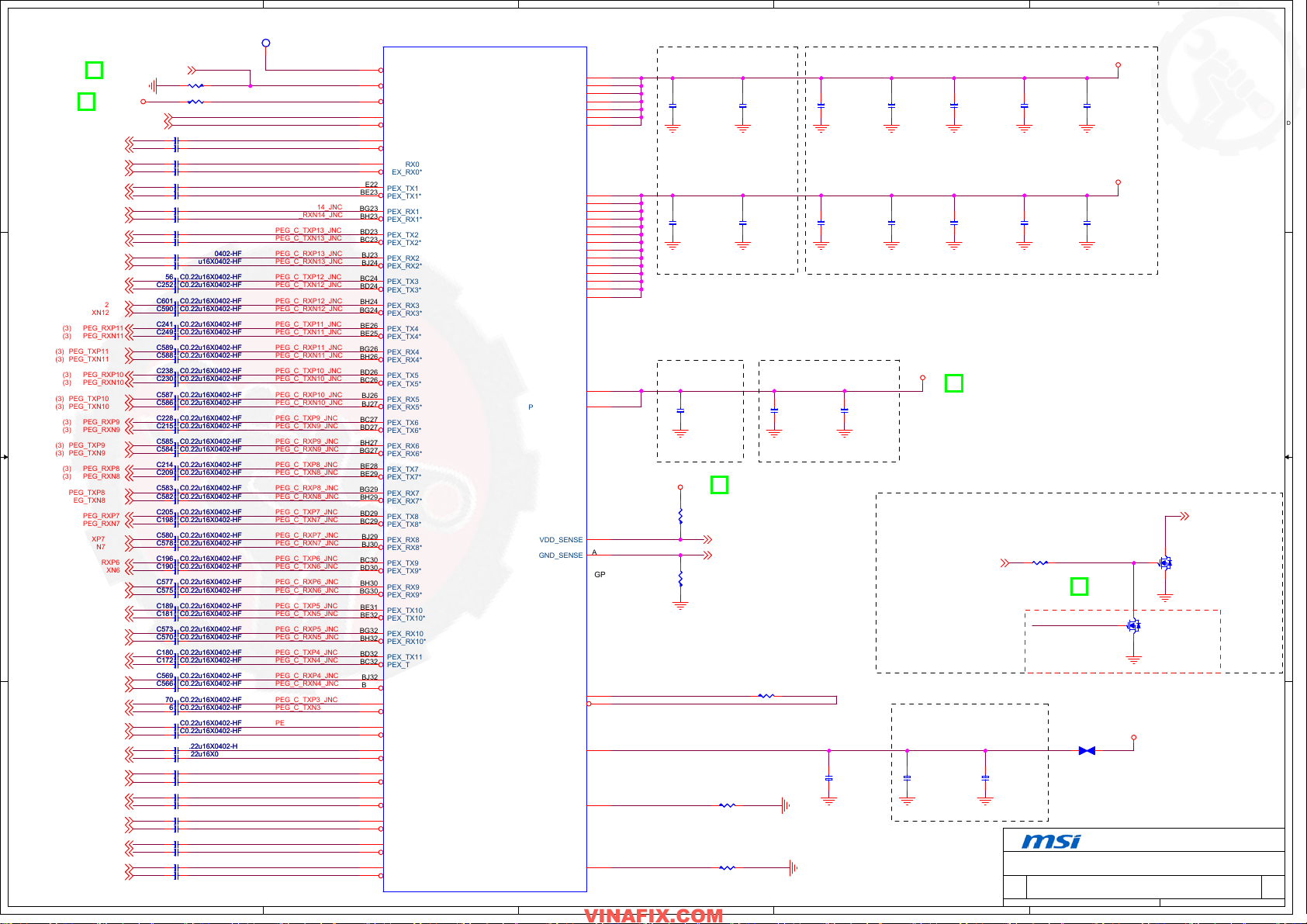

TPJNC21TPJNC21

PEX_RST#(26)

R131 100KR0402R131 100KR0402

GND

3V3_AON

D D

C C

B B

A A

GFX_REFCLK(33)

GFX_REFCLK#(33)

PEG_RXP15(3)

PEG_RXN15(3)

PEG_TXP15(3)

PEG_TXN15(3)

PEG_RXP14(3)

PEG_RXN14(3)

PEG_TXP14(3)

PEG_TXN14(3)

PEG_RXP13(3)

PEG_RXN13(3)

PEG_TXP13(3)

PEG_TXN13(3)

PEG_RXP12(3)

PEG_RXN12(3)

PEG_TXP12(3)

PEG_TXN12(3)

PEG_RXP11(3)

PEG_RXN11(3)

PEG_TXP11(3)

PEG_TXN11(3)

PEG_RXP10(3)

PEG_RXN10(3)

PEG_TXP10(3)

PEG_TXN10(3)

PEG_RXP9(3)

PEG_RXN9(3)

PEG_TXP9(3)

PEG_TXN9(3)

PEG_RXP8(3)

PEG_RXN8(3)

PEG_TXP8(3)

PEG_TXN8(3)

PEG_RXP7(3)

PEG_RXN7(3)

PEG_TXP7(3)

PEG_TXN7(3)

PEG_RXP6(3)

PEG_RXN6(3)

PEG_TXP6(3)

PEG_TXN6(3)

PEG_RXP5(3)

PEG_RXN5(3)

PEG_TXP5(3)

PEG_TXN5(3)

PEG_RXP4(3)

PEG_RXN4(3)

PEG_TXP4(3)

PEG_TXN4(3)

PEG_RXP3(3)

PEG_RXN3(3)

PEG_TXP3(3)

PEG_TXN3(3)

PEG_RXP2(3)

PEG_RXN2(3)

PEG_TXP2(3)

PEG_TXN2(3)

PEG_RXP1(3)

PEG_RXN1(3)

PEG_TXP1(3)

PEG_TXN1(3)

PEG_RXP0(3)

PEG_RXN0(3)

PEG_TXP0(3)

PEG_TXN0(3)

R87 100KR0402R87 100KR0402

C292 C0.22u16X0402-HFC292 C0.22u16X0402-HF

C280 C0.22u16X0402-HFC280 C0.22u16X0402-HF

C615 C0.22u16X0402-HFC615 C0.22u16X0402-HF