Page 1

5

4

3

2

1

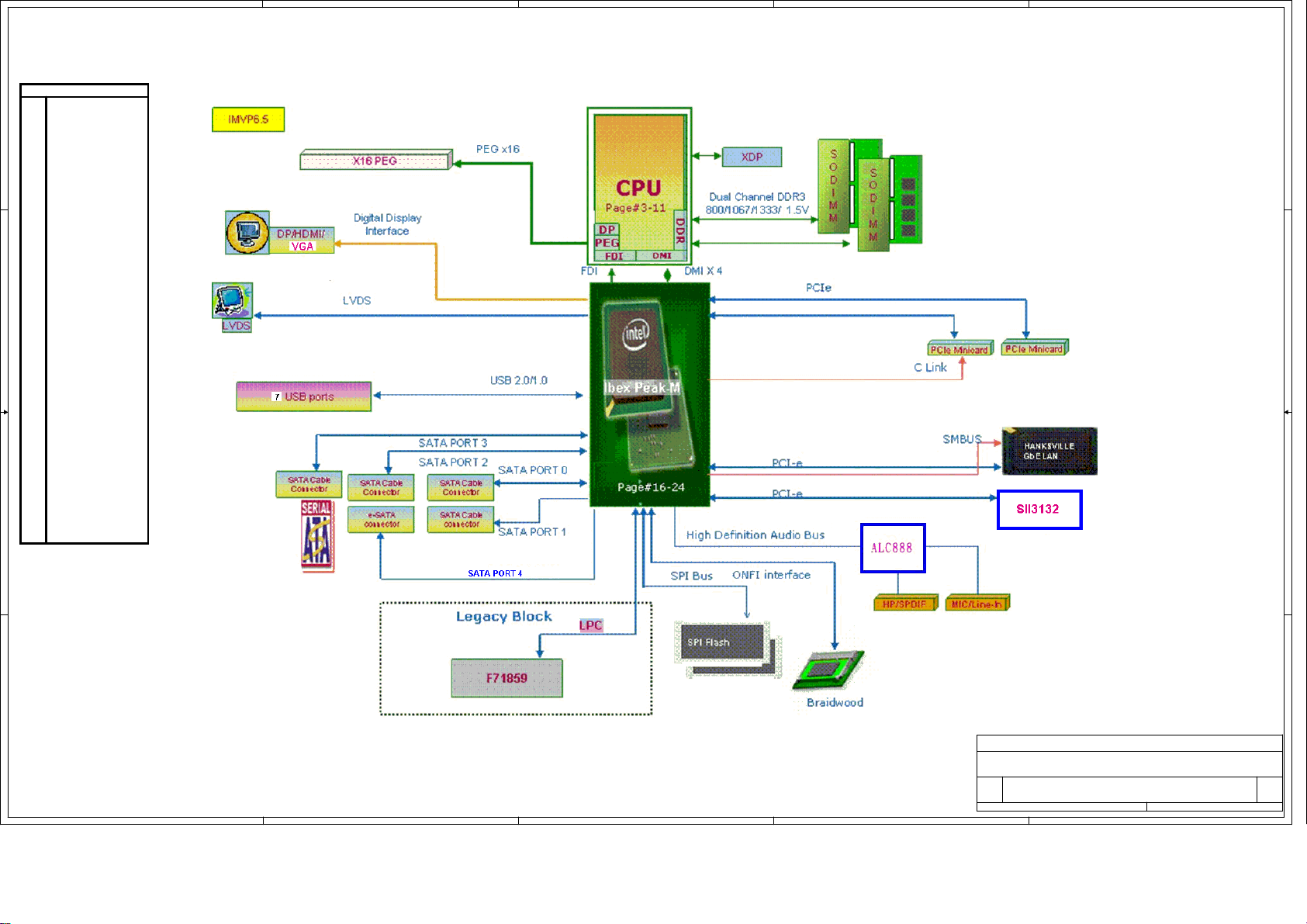

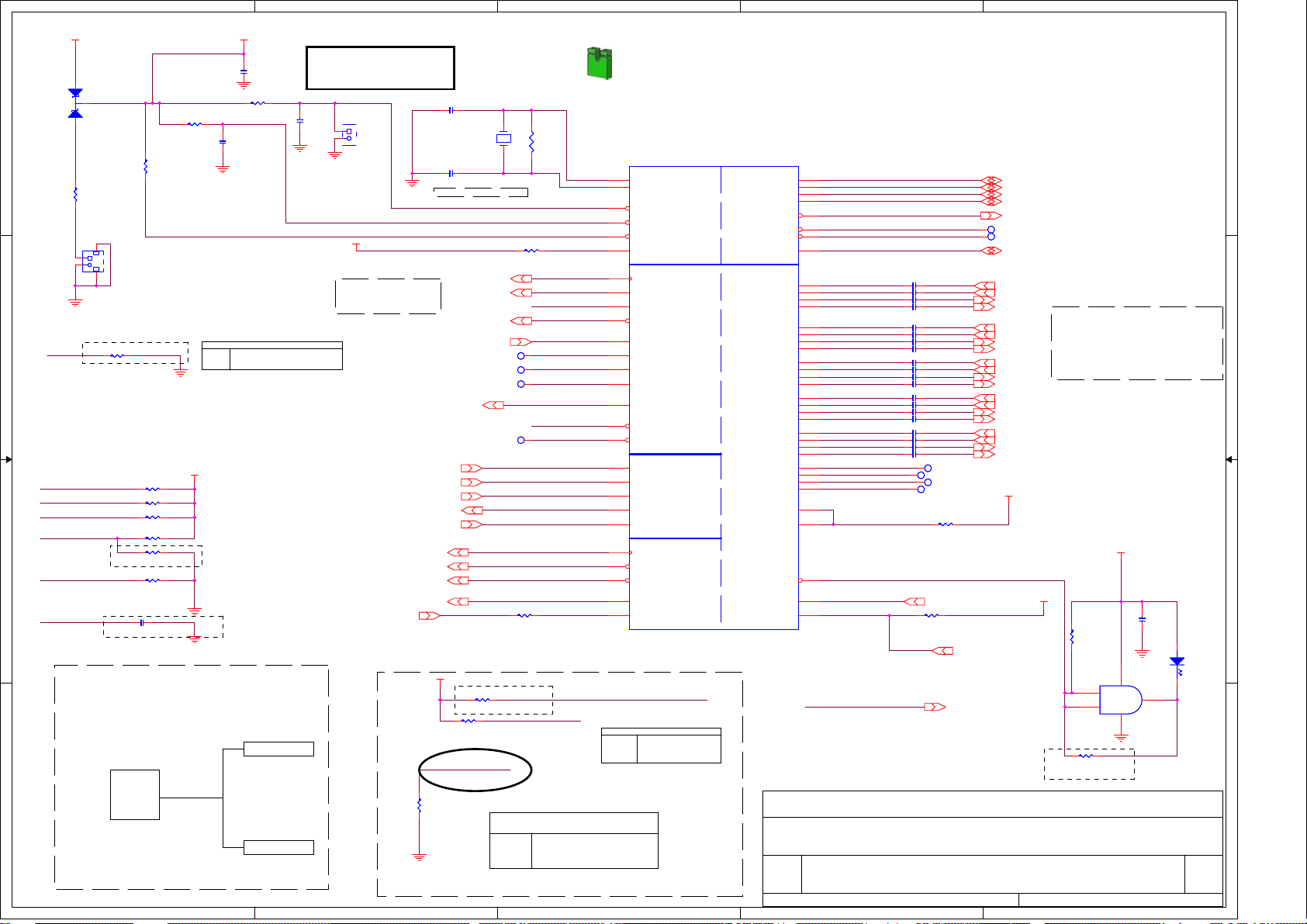

Emerald Bay

Table of Contents

Page Description

D D

1

TITLE PAGE

2

NOTES

3

MCP (1 of 7)

4

MCP (2 of 7)

5

MCP (3 of 7)

6

MCP (4 of 7)

7

MCP (5 of 7)

8

MCP (6 of 7)

9

MCP (7 of 7)

10

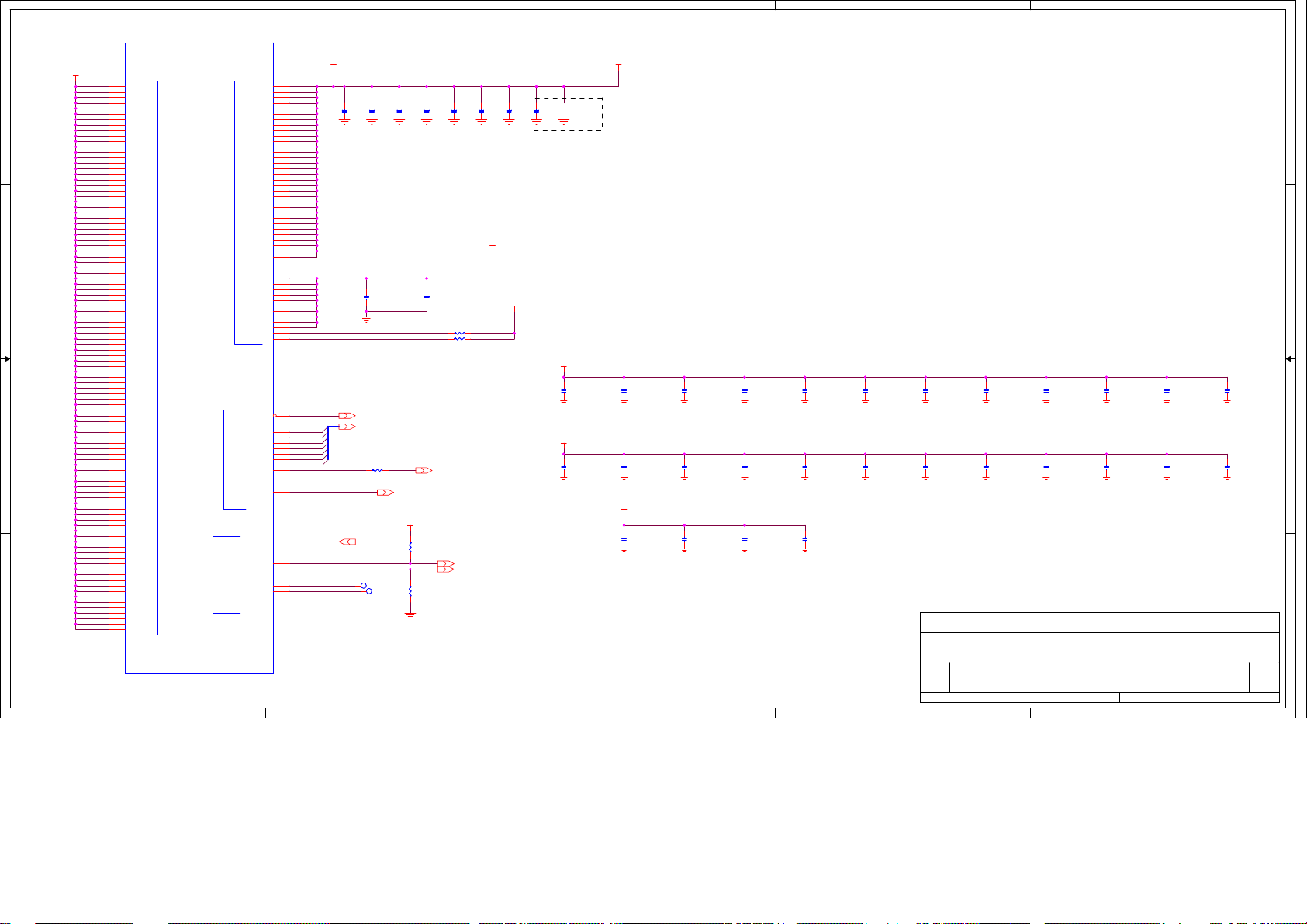

FAN HEADERS

11

XDP (MCP)

12

PROCESSOR STRAPS

13

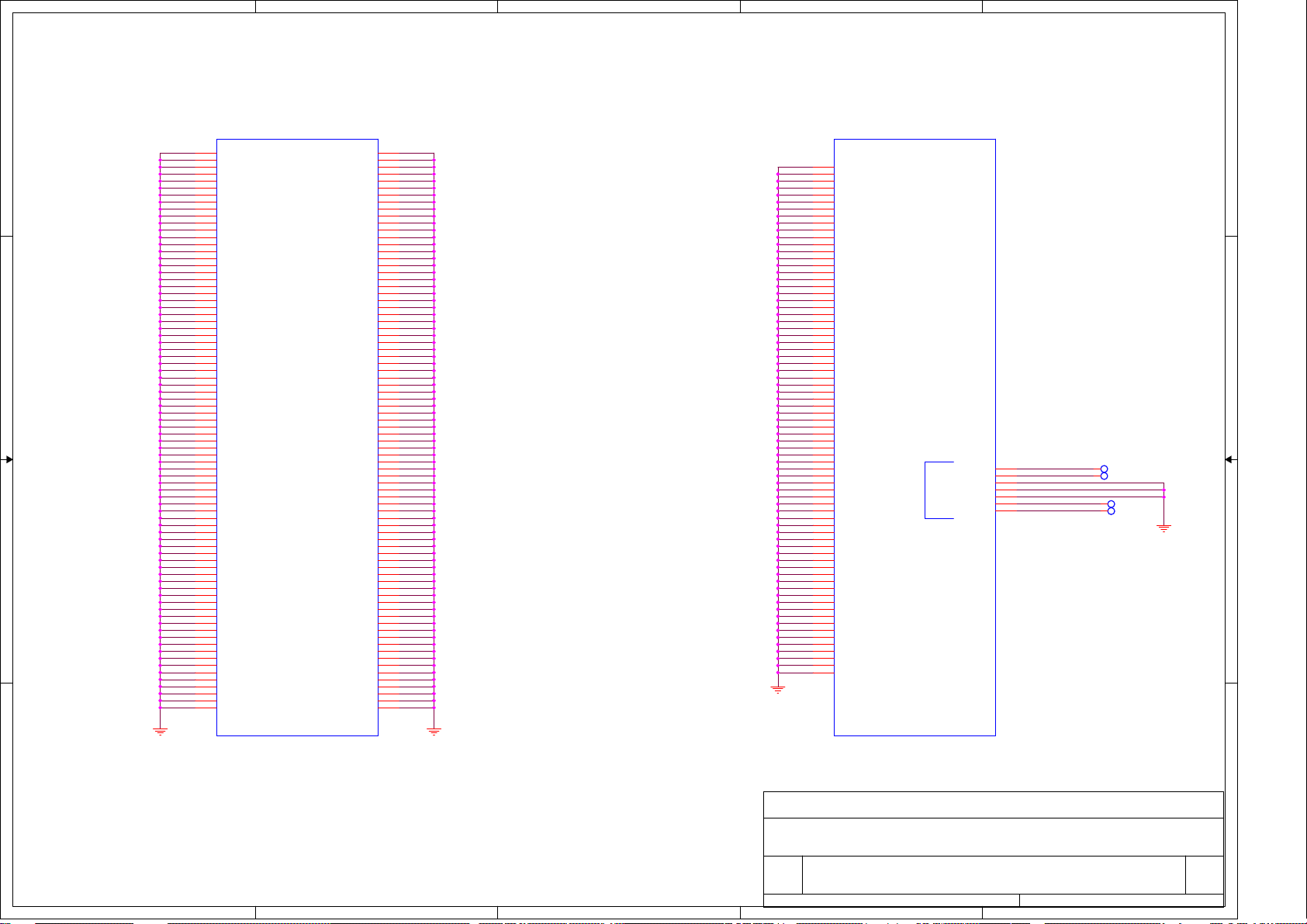

DDR3 SODIMM0

14

DDR3 SODIMM1

15

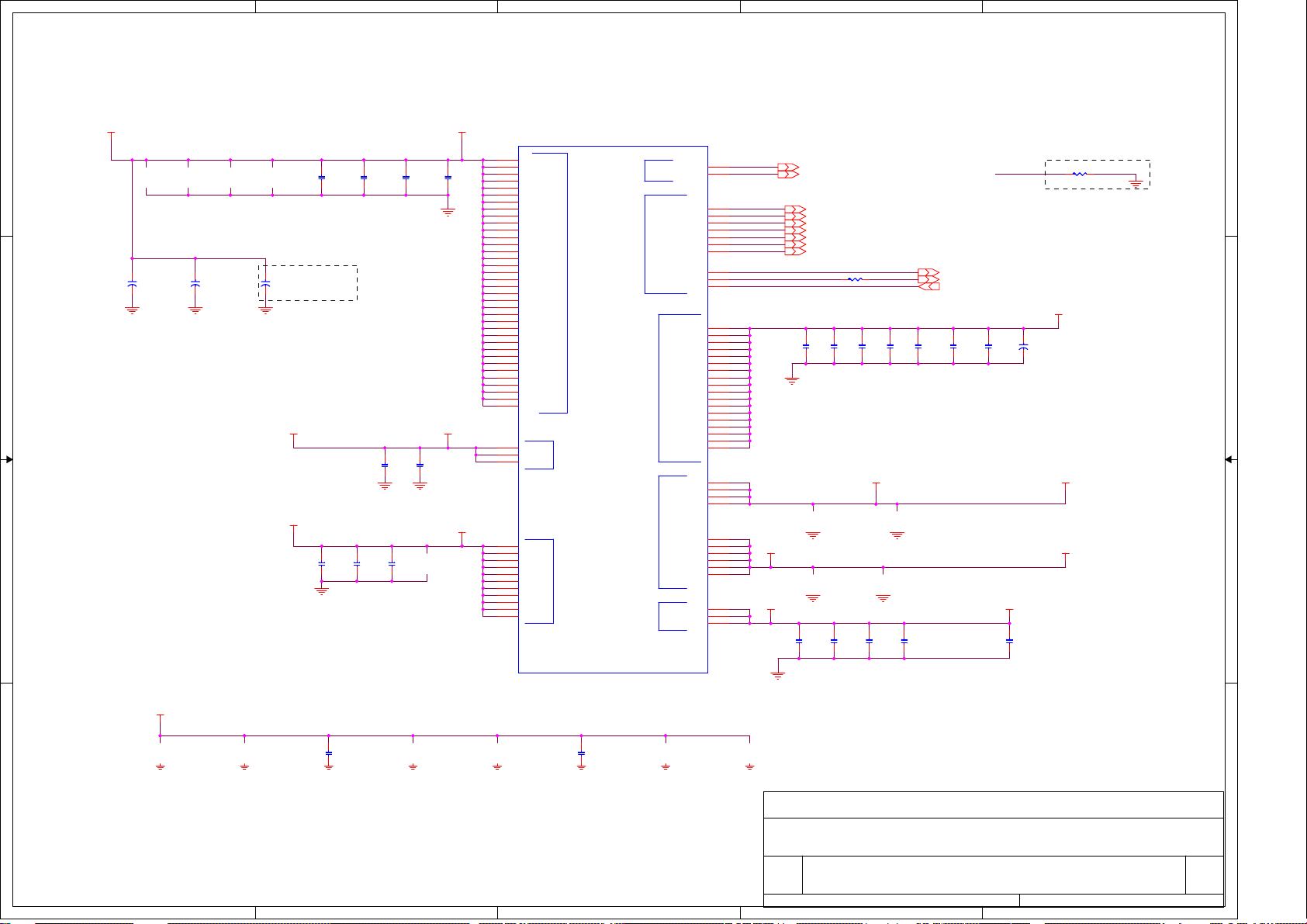

IBEXPEAK (1 of 9)

16

IBEXPEAK (2 of 2)

17

IBEXPEAK (3 of 9)

18

IBEXPEAK (4 of 9)

19

IBEXPEAK (5 of 9)

20

IBEXPEAK (6 of 9)

21

IBEXPEAK (7 of 9)

22

IBEXPEAK (8 of 9)

23

IBEXPEAK (9 of 9)

24

DISPLAYPORT+HDMI

25

LVDS

26

BRAIDWOOD

27

USB 2.0 (1 of 2)

28

USB 2.0 (2 of 2)

29

MINICARD

30

SATA

31

IHDA

32

LAN HANKSVILLE

33

C C

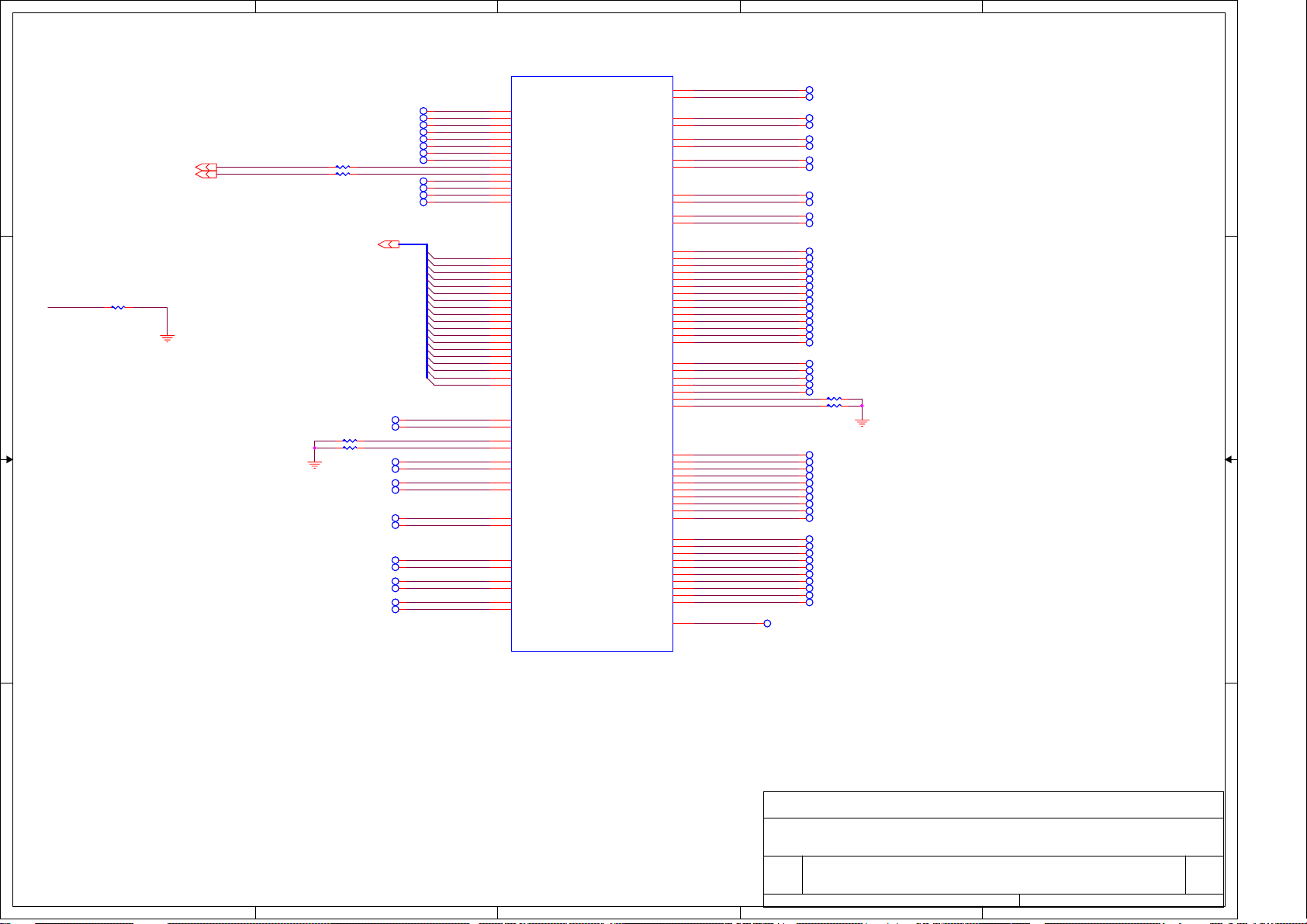

SPI

34

CK505

35

IBEXPEAK-M XDP

36

F71859 SIO

37

PCIE x16

TPS51125 SYSTEM POWER VR

38

+12V &DDR3 VR

39

V1.1 VR

40

GRAPHICS CORE VR

41

IMVP-6.5

42

DISCHARGE CIRCUITS

43

START UP SEQUENCE

44

SLEEP CONTROL

45

POWER SEQUENCE LOGIC

46

POWER UP SEQUENCE

47

PCH STRAPS

48

VGA

49

PCIE TO SATA

50

REVISION HISTORY

51

REVISION HISTORY1

52

REVISION HISTORY2

53

CALPELLA ON DESKTOP ENABLING BOARD

Merom

AUBURNDALE/CLARKSFIELD-IBEXPEAK-M

Fab A

REV 0.5

B B

A A

Intel Confidential

Intel Confidential

153Thursday, September 25, 2008

153Thursday, September 25, 2008

153Thursday, September 25, 2008

Intel Confidential

of

of

of

A

A

A

EMERALD BAY

EMERALD BAY

EMERALD BAY

Title

Title

Title

TITLE PAGE

TITLE PAGE

TITLE PAGE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

B

<Doc>

B

<Doc>

B

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

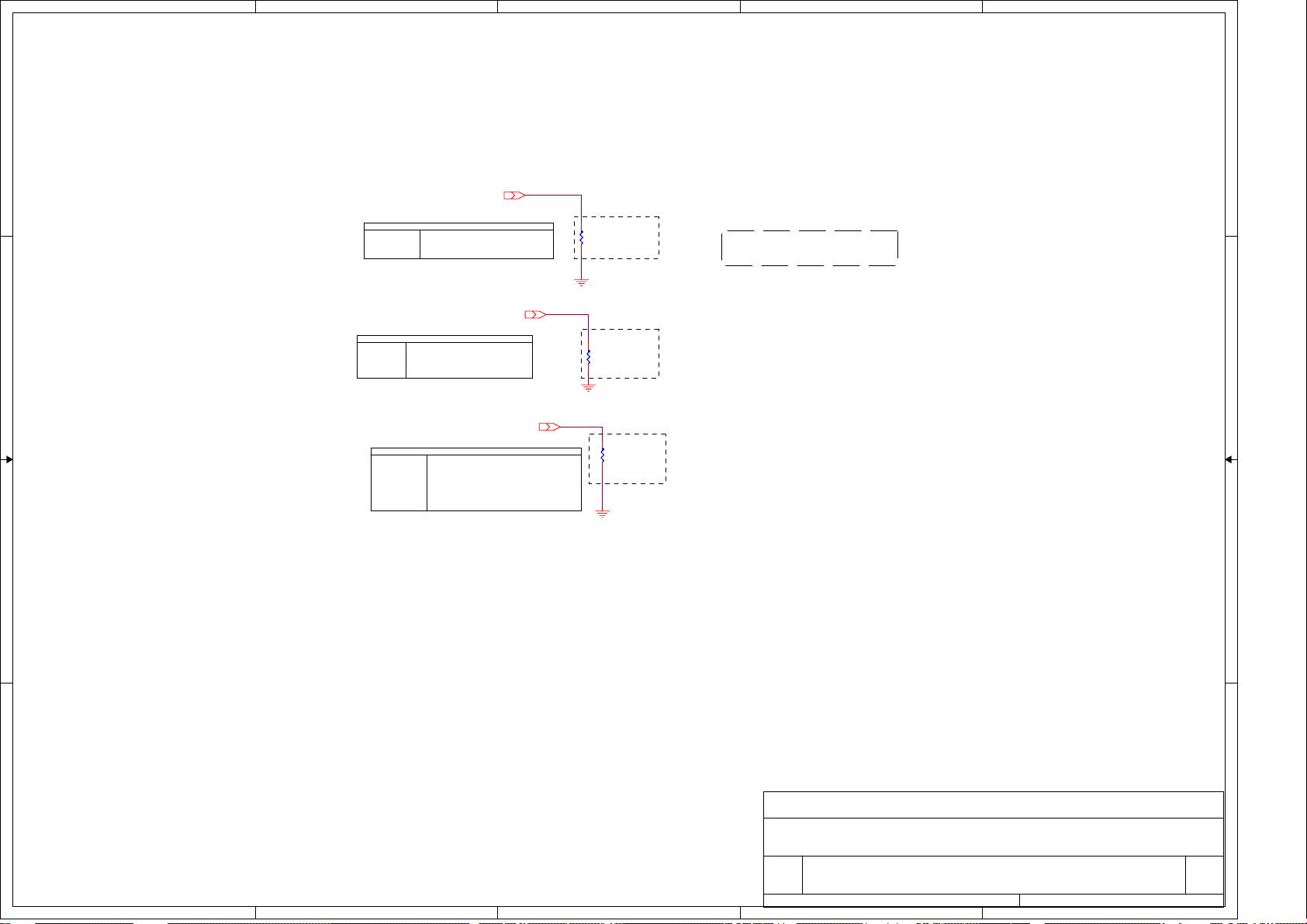

Page 2

5

4

3

2

1

CALPELLA ON DESKTOP ENABLING BOARD

SCHEMATIC ANNOTATIONS AND BOARD INFORMATION

D D

Voltage Rails

+V12A

+V12S

+V5A

+V5

+V5S

+V3.3A

+V3.3M

+V3.3M_CK505

+V3.3

+V3.3S

+V1.5

+V1.5S

+V1.05M

+V1.05S

+V0.75

+VCC_CORE

+VCC_GFXCORE

VOLTAGE DESCRIPTIONACTIVE INPOWER PLANE

12V

12V

5V

5V

5V

3.3V

3.3V

3.3V

3.3V

3.3V

1.8V

1.5V

1.05V

1.05V

0.9V

0.35V-1.5V

0.7V-1.25V

S0/M0, (S3-S5)/M1, (S3-S5)/M-off

S0/M0

S0/M0, (S3-S5)/M1, (S3-S5)/M-off

S0/M0, S3/M1, S3/M-off

S0/M0

S0/M0, (S3-S5)/M1, (S3-S5)/M-off

S0/M0, (S3-S5)/M1, S3/(M-off w/WOL_EN)

S0/M0, (S3-S5)/M1

S0/M0, S3/M1, S3/M-off

S0/M0

S0/M0, (S3-S5)/M1, S3/M-off

S0/M0

S0/M0, (S3-S5)/M1

S0/M0

S0/M0, (S3-S5)/M1, S3/M-off

S0/M0

S0/M0

LAN

Clock, MCH

DDR core

GMCH, ICH core, and FSB rail

DDR command & control pull up.

CPU core rail

GMCH Graphics core rail

C C

Net Naming Conventions

Suffix

# = Active Low Signal

Prefix

H = Host

M = DDR Memory

TP = Test Point (does not connect anywhere else)

PCB Footprints

1

2

SOT-23

3

As seen from top

5

1

2

4

3

SOT23-5

Power States

SLP_S3#

S4_STATE#

SLP_S4#

SLP_S5#

HIGH

HIGH

S0 (Full on)/M0

S3 (Suspend to RAM)/M1

S3 (Suspend to RAM)/Moff

B B

S3 (Suspend to RAM)/Moff w/WOL_EN

S4 (Suspend to Disk)/M1

S5 (Soft Off)/M1

S4 (Suspend to Disk)/Moff

S5 (Soft Off)/Moff

LOW

LOW

LOW

LOW

LOW

LOW

LOW

HIGH

HIGH

HIGH

LOW

LOW

LOW

LOW

HIGH

HIGH

HIGH

HIGH

HIGH

HIGH

LOW

LOW

HIGH

HIGH

HIGH

HIGH

HIGH

LOW

HIGH

LOW

SLP_M#

HIGH

HIGH

LOW

LOW

HIGH

HIGH

LOW

LOW

+V*A

ON

ON

ON

ON

ON

ON

ON

ON

+V3.3M_WOL

ON

ON

OFF

ON

ON

ON

OFF

OFF

A A

5

4

+V1.05M

ON

ON

OFF

OFF

ON

ON

OFF

OFF

+V3.3M

ON

ON

OFF

OFF

ON

ON

OFF

OFF

+V1.5/+V0.75

ON

ON

ON

ON

ON

ON

OFF

OFF

+V5/+V3.3

ON

ON

ON

ON

OFF

OFF

OFF

OFF

+V*S

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

Clocks

ON

only MCH BCLK

OFF

OFF

only MCH BCLK

only MCH BCLK

OFF

OFF

3

Intel Confidential

Intel Confidential

EMERALD BAY

EMERALD BAY

EMERALD BAY

Title

Title

Title

NOTES

NOTES

NOTES

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

2

Intel Confidential

of

of

of

253Thursday, September 25, 2008

253Thursday, September 25, 2008

253Thursday, September 25, 2008

1

A

A

A

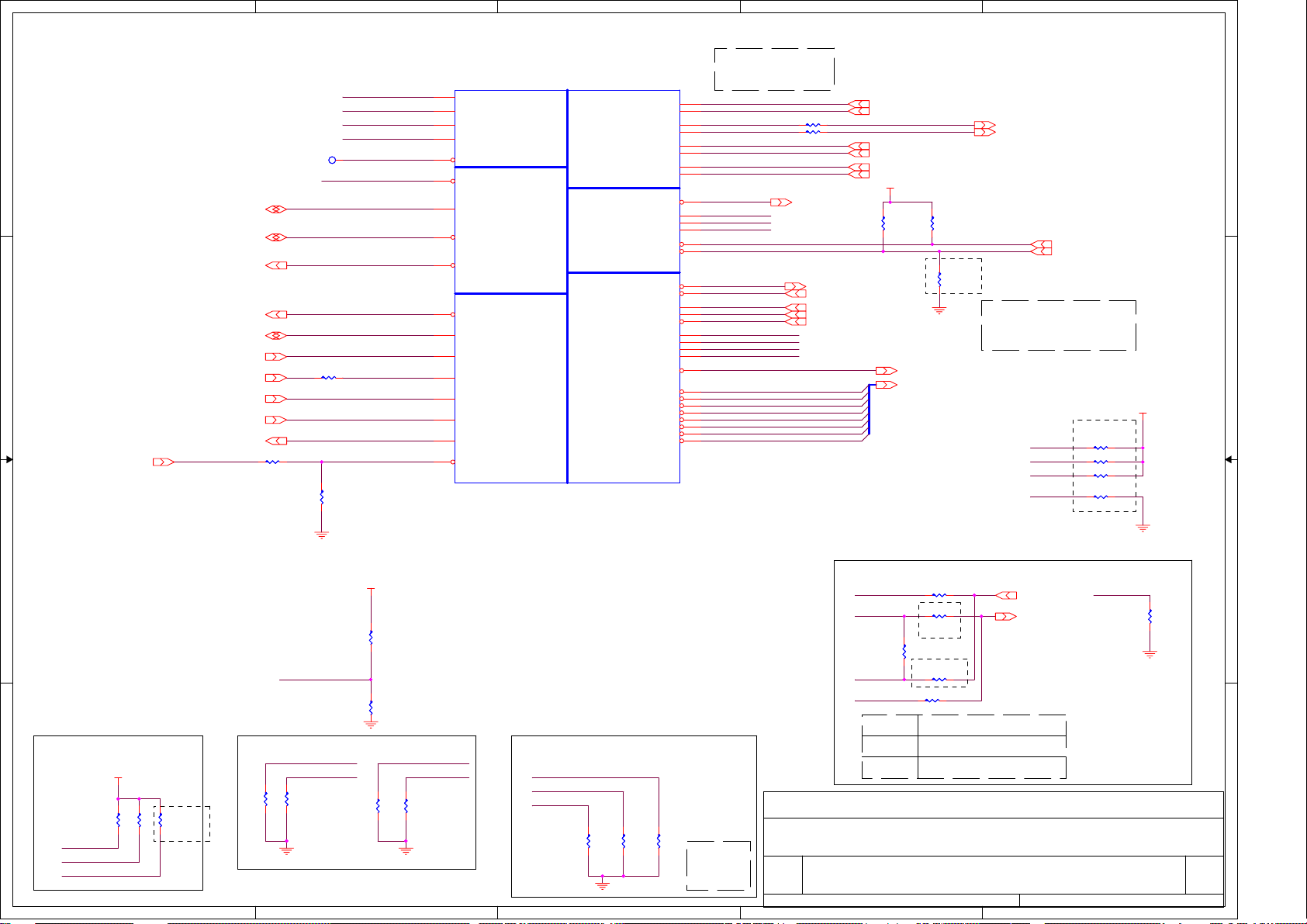

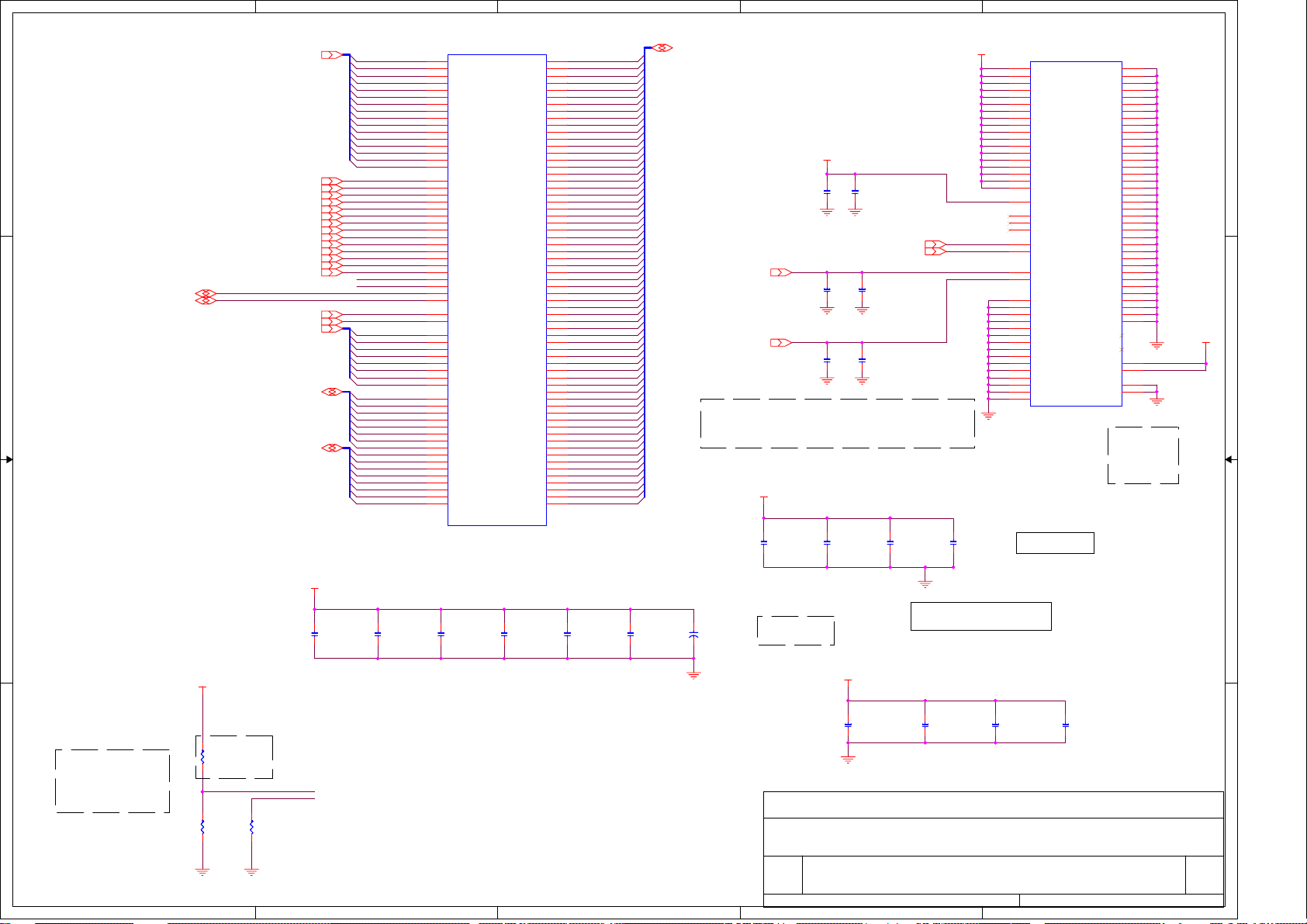

Page 3

5

4

3

2

1

D D

U1A

U1A

DMI_TXN0(17)

DMI_TXN1(17)

DMI_TXN2(17)

DMI_TXN3(17)

DMI_TXP0(17)

DMI_TXP1(17)

DMI_TXP2(17)

DMI_TXP3(17)

DMI_RXN0(17)

DMI_RXN1(17)

DMI_RXN2(17)

DMI_RXN3(17)

DMI_RXP0(17)

DMI_RXP1(17)

DMI_RXP2(17)

DMI_RXP3(17)

FDI_TXN[7:0](17)

C C

FDI_TXP[7:0](17)

FDI_FSYNC0(17)

FDI_FSYNC1(17)

FDI_INT(17)

FDI_LSYNC0(17)

FDI_LSYNC1(17)

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

A24

C23

B22

A21

B24

D23

B23

A22

D24

G24

F23

H23

D25

F24

E23

G23

E22

D21

D19

D18

G21

E19

F21

G18

D22

C21

D20

C18

G22

E20

F20

G19

F17

E17

C17

F18

D17

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI_TX#[0]

FDI_TX#[1]

FDI_TX#[2]

FDI_TX#[3]

FDI_TX#[4]

FDI_TX#[5]

FDI_TX#[6]

FDI_TX#[7]

FDI_TX[0]

FDI_TX[1]

FDI_TX[2]

FDI_TX[3]

FDI_TX[4]

FDI_TX[5]

FDI_TX[6]

FDI_TX[7]

FDI_FSYNC[0]

FDI_FSYNC[1]

FDI_INT

FDI_LSYNC[0]

FDI_LSYNC[1]

B B

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

DMI Intel(R) FDI

DMI Intel(R) FDI

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

PEG_IRCOMP_R

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

EXP_RBIAS

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

R1 49.9R1%0402R1 49.9R1%0402

R2 750R1%0402R2 750R1%0402

PEG_RXN[15:0] (37)

PEG_RXP[15:0] (37)

PEG_TXN[15:0] (37)

PEG_TXP[15:0] (37)

A A

5

4

3

EMERALD BAY

EMERALD BAY

EMERALD BAY

Title

Title

Title

MCP (1 of 7)

MCP (1 of 7)

MCP (1 of 7)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

2

Intel Confidential

Intel Confidential

Intel Confidential

of

of

of

353Thursday, September 25, 2008

353Thursday, September 25, 2008

353Thursday, September 25, 2008

1

A

A

A

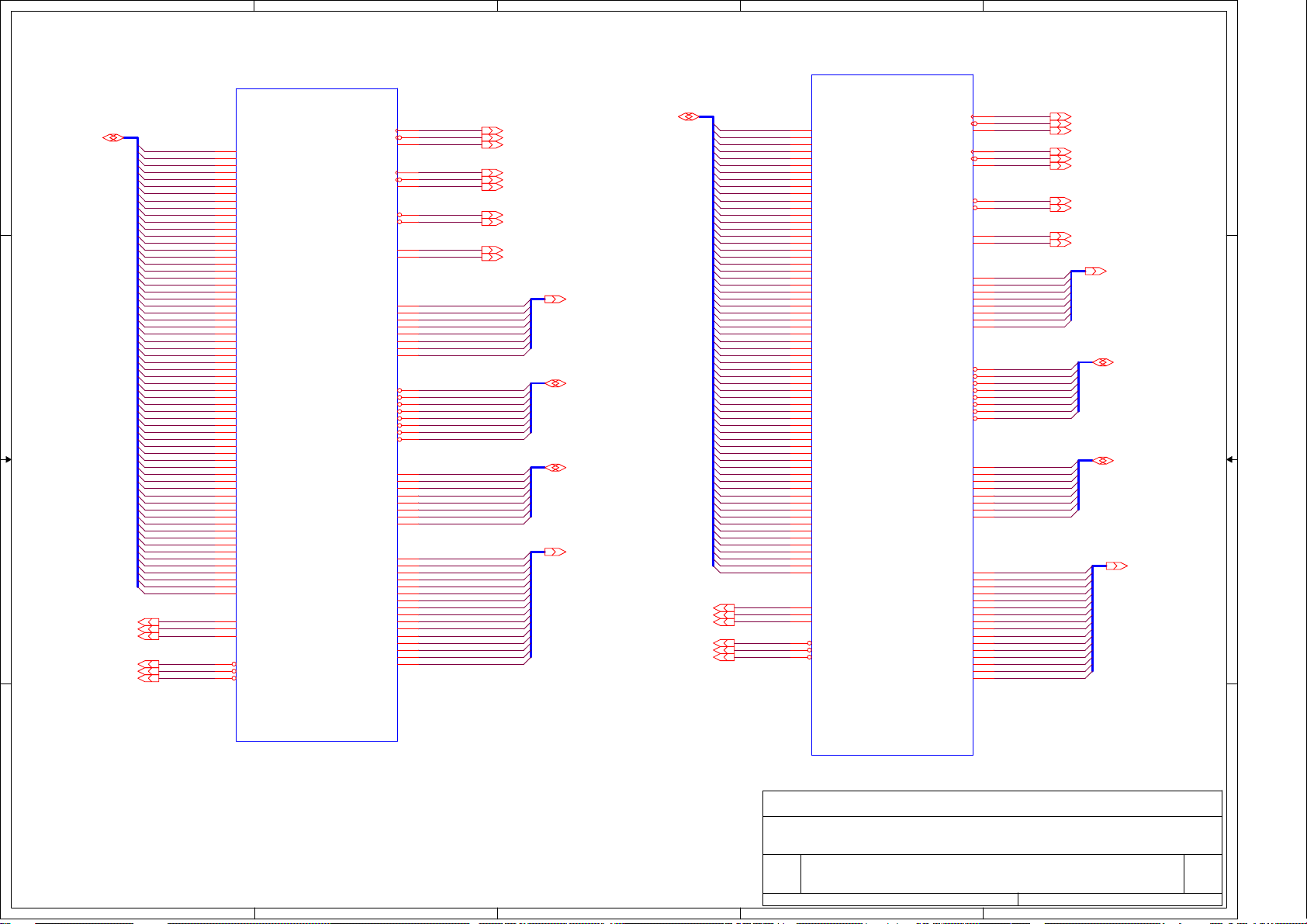

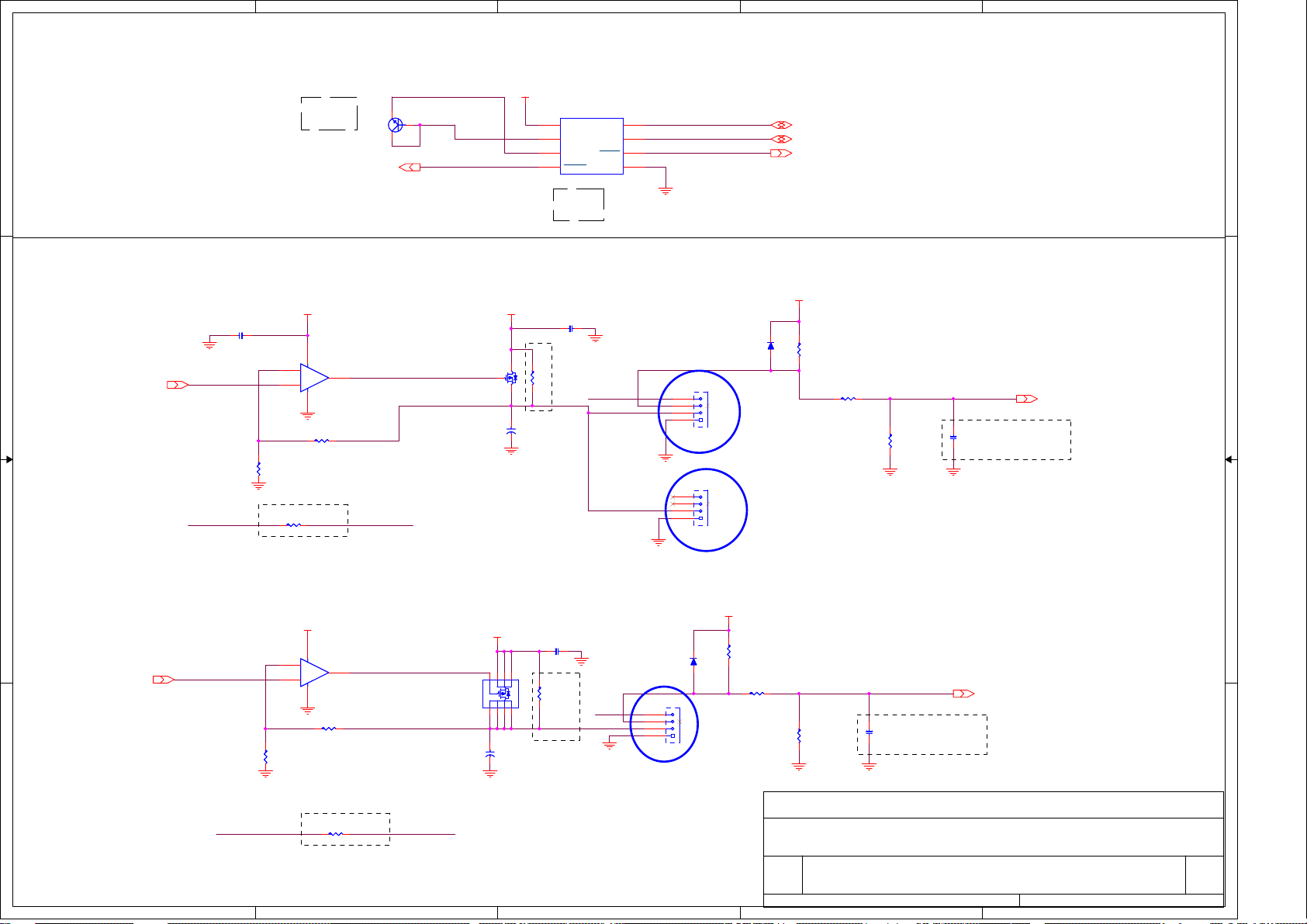

Page 4

5

)

D D

TP9TP9

H_PECI(20)

H_PROCHOT_L(42)

H_THRMTRIP_L(20)

H_CPURST_L(11)

H_PM_SYNC(17)

C C

BUF_PLT_RST_L(19,36)

H_CPUPWRGD(11,20)

H_CPUPWRGD(11,20)

PM_DRAM_PWRGD(17)

H_VTTPWRGD(46)

H_PWRGD_XDP(11)

R603

R603

24.9KR1%0402

24.9KR1%0402

H_PROCHOT_L

H_THRMTRIP_L

R6 0R0402R6 0R0402

H_CPURST_L

PM_DRAM_PWRGD

R10

R10

12.4KR1%0402

12.4KR1%0402

4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TP_SKTOCC_L

H_CATERR_L

VCCPWRGOOD_R

PLT_RST_LBUF_PLT_RST_L

U1B

U1B

AT23

COMP3

AT24

COMP2

G16

COMP1

AT26

COMP0

AH24

SKTOCC#

AK14

CATERR#

AT15

PECI

AN26

PROCHOT#

AK15

THERMTRIP#

AP26

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

AK13

SM_DRAMPWROK

AM15

VTTPWRGOOD

AM26

TAPPWRGOOD

AL14

RSTIN#

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

3

MISC THERMAL

MISC THERMAL

CLOCKS

CLOCKS

DDR3

MISC

DDR3

MISC

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

TDI

A16

B16

AR30

AT30

E16

D16

A18

A17

F6

AL1

AM1

AN1

AN15

AP15

AT28

AP27

AN28

AP28

AT27

AT29

AR27

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

CK_BCK1

CK_BCK1_L

DDR3_DRAMRST_L

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

PM_EXTTS_L0

PM_EXTTS_L1

Layout Note: All

resistors need to be

close to Processor

(AUB/CFD) to avoid stubs

R69 0R0402R69 0R0402

R425 0R0402R425 0R0402

DDR3_DRAMRST_L (13,14)

XDP_TDI_R

XDP_TDO_R

XDP_TDI_M

XDP_TDO_M

XDP_DBRESET_L

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

XDP_PRDY_L (11)

XDP_PREQ_L (11)

XDP_TCLK (11)

XDP_TMS (11)

XDP_TRST_L (11)

2

CLK_MCP_BCLK (20)

CLK_MCP_BCLK_L (20)

BCLK_ITP

BCLK_ITP_L

CLK_MCH_PEG (16)

CLK_MCH_PEG_L (16)

CLK_DP_P (16)

CLK_DP_N (16)

+V1.1S_VTT(6,7,11,20,21,22,34,40,41,42,43)

R3

10KR0402R310KR0402

R4

10KR0402R410KR0402

NO_STUFF

R5

R5

X_12.4KR1%0402

X_12.4KR1%0402

XDP_DBRESET_L (11,35)

XDP_OBS[0:7] (11)

1

BCLK_ITP (11)

BCLK_ITP_L (11)

PM_EXTTS_L0 (10)

PM_EXTTS_L1 (10,13,14)

CAD Note:

TCLK: Provide a scope test point at the

Processor socket breakout via to verify

signal integrity of the first

platforms.

NO_STUFF

R7 X_51R1%0402R7 X_51R1%0402

XDP_TMS

R8 X_51R1%0402R8 X_51R1%0402

XDP_TDI_R

XDP_PREQ_L

R9 X_51R1%0402R9 X_51R1%0402

R11 X_51R1%0402R11 X_51R1%0402

XDP_TCLK

+V1.1S_VTT(6,7,11,20,21,22,34,40,41,42,43)

B B

PM_DRAM_PWRGD

Processor Pullups

+V1.1S_VTT7,11,20,21,22,34,40,41,42,43

A A

R25

R25

R26

5

68R0402

68R0402

R26

X_68R0402

X_68R0402

NO_STUFF

49.9R1%0402

49.9R1%0402

H_CATERR_L

H_PROCHOT_L

H_CPURST_L

R24

R24

20R1%0402

20R1%0402

Processor Compensation Signals

H_COMP3

H_COMP2

R20

R20

R21

R21

20R1%0402

20R1%0402

+V3.3A(15,16,17,19,20,22,27,28,29,32,34,36,37,38,39,45,46)

R22

R22

49.9R1%0402

49.9R1%0402

R15

R15

2KR1%0402-1

2KR1%0402-1

R18

R18

1KR1%0402

1KR1%0402

4

H_COMP1

H_COMP0

R23

R23

49.9R1%0402

49.9R1%0402

DDR3 Compensation Signals

SM_RCOMP_2

SM_RCOMP_1

SM_RCOMP_0

R28

R28

24.9R1%0402

24.9R1%0402

R27

R27

100R1%0402

100R1%0402

3

R29

R29

130R1%0402

130R1%0402

Layout Note:

Place these

resistors near

Processor

XDP_TDI_R

XDP_TDO_M

R12 0R0402R12 0R0402

R13 X_0R0402R13 X_0R0402

XDP_TDI (11)

XDP_TDO (11)

NO_STUFF

R16

R16

0R0402

0R0402

XDP_TDI_M

XDP_TDO_R

Scan Chain

(Default)

CPU Only

GMCH Only

EMERALD BAY

EMERALD BAY

EMERALD BAY

Title

Title

Title

MCP (2 of 7)

MCP (2 of 7)

MCP (2 of 7)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

NO_STUFF

R17 X_0R0402R17 X_0R0402

R19 0R0402R19 0R0402

STUFF -> R2R13, R2D6, R3D13

NO STUFF -> R3D9, R2R9

STUFF -> R2R13, R3D9

NO STUFF -> R2D6, R2R9, R3D13

STUFF -> R2R9, R3D13

NO STUFF -> R2R13, R3D9, R2D6

2

XDP_TRST_L

453Monday, October 06, 2008

453Monday, October 06, 2008

453Monday, October 06, 2008

Intel Confidential

Intel Confidential

Intel Confidential

1

R14

R14

51R1%0402

51R1%0402

of

of

of

A

A

A

Page 5

5

4

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR (DDR3)

U1D

AM6

AN2

AM4

AM3

AN5

AN6

AN4

AN3

AN7

AR10

AT10

AF3

AG1

AJ3

AK1

AG4

AG3

AJ4

AH4

AK3

AK4

AK5

AK2

AP3

AT4

AT5

AT6

AP6

AP8

AT9

AT7

AP9

AB1

AC5

AC6

M1

M4

W5

B5

A5

C3

B3

E4

A6

A4

C4

D1

D2

F2

F1

C2

F5

F3

G4

H6

G2

J6

J3

G1

G5

J2

J1

J5

K2

L3

K5

K4

N5

R7

Y7

U1D

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

W8

SB_CK[0]

W9

SB_CK#[0]

M3

SB_CKE[0]

V7

SB_CK[1]

V6

SB_CK#[1]

M2

SB_CKE[1]

AB8

SB_CS#[0]

AD6

SB_CS#[1]

AC7

SB_ODT[0]

AD1

SB_ODT[1]

M_B_DM0

D4

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS_L0

M_B_DQS_L1

M_B_DQS_L2

M_B_DQS_L3

M_B_DQS_L4

M_B_DQS_L5

M_B_DQS_L6

M_B_DQS_L7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_CLK_DDR2 (14)

M_CLK_DDR2_L (14)

M_CKE2 (14)

M_CLK_DDR3 (14)

M_CLK_DDR3_L (14)

M_CKE3 (14)

M_CS_L2 (14)

M_CS_L3 (14)

M_ODT2 (14)

M_ODT3 (14)

M_B_DM[7:0] (14)

M_B_DQS_L[7:0] (14)

M_B_DQS[7:0] (14)

M_B_A[15:0] (14)

U1C

U1C

M_B_DQ[63:0](14)

D D

C C

B B

M_A_DQ[63:0](13)

M_A_BS0(13)

M_A_BS1(13)

M_A_BS2(13)

M_A_CAS_L(13)

M_A_RAS_L(13)

M_A_WE_L(13)

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_CAS_L

M_A_RAS_L

M_A_WE_L

AJ10

AL10

AK12

AK11

AM10

AR11

AL11

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

A10

C10

B10

D10

E10

H10

G10

AH5

AF5

AK6

AK7

AF6

AG5

AK8

AL7

AL8

AN8

AM9

AN9

AC3

AB2

AE1

AB3

AE9

F10

J10

AJ7

AJ6

AJ9

C7

A7

A8

D8

E6

F7

E9

B7

E7

C6

G8

K7

J8

G7

J7

L7

M6

M8

L9

L6

K8

N8

P9

U7

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA6

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_CKE0

M_CKE1M_A_DQ5

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS_L0

M_A_DQS_L1

M_A_DQS_L2

M_A_DQS_L3

M_A_DQS_L4

M_A_DQS_L5

M_A_DQS_L6

M_A_DQS_L7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_CLK_DDR0 (13)

M_CLK_DDR0_L (13)

M_CKE0 (13)

M_CLK_DDR1 (13)

M_CLK_DDR1_L (13)

M_CKE1 (13)

M_CS_L0 (13)

M_CS_L1 (13)

M_ODT0 (13)

M_ODT1 (13)

M_A_DM[7:0] (13)

M_A_DQS_L[7:0] (13)

M_A_DQS[7:0] (13)

M_A_A[15:0] (13)

M_B_BS0(14)

M_B_BS1(14)

M_B_BS2(14)

M_B_CAS_L(14)

M_B_RAS_L(14)

M_B_WE_L(14)

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_CAS_L

M_B_RAS_L

M_B_WE_L

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

A A

5

4

3

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

Intel Confidential

Intel Confidential

EMERALD BAY

EMERALD BAY

EMERALD BAY

Title

Title

Title

MCP (3 of 7)

MCP (3 of 7)

MCP (3 of 7)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

2

Intel Confidential

of

of

of

553Thursday, September 25, 2008

553Thursday, September 25, 2008

553Thursday, September 25, 2008

1

A

A

A

Page 6

5

4

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR (POWER)

U1F

U1F

+VCC_CORE(42,43)

AG35

VCC1

AG34

VCC2

AG33

VCC3

D D

C C

B B

A A

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

1.1V RAIL POWER

1.1V RAIL POWER

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

VTT_SELECT

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

SENSE LINES

SENSE LINES

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

ISENSE

PSI#

5

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

PM_DPRSLPVR_R

AM34

G15

AN35

AJ34

AJ35

B15

TP_VSS_SENSE_VTT

A15

+V1.1S_VCCTT(4,7,11,20,21,22,34,40,41,42,43)

PSI_L

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

H_VTTVID1

TP_VTT_SENSE

C2

C1

C10u6.3X50805-RH-2C2C10u6.3X50805-RH-2

C10u6.3X50805-RH-2C1C10u6.3X50805-RH-2

C13

C13

C22u6.3X50805-RH

C22u6.3X50805-RH

PSI_L (42)

H_VID[0:6] (42)

R32 0R0402R32 0R0402

IMVP_IMON (42)

TP7TP7

TP8TP8

+VTT_43

+VTT_44

H_VTTVID1 (40)

+VCC_CORE(42,43)

4

C4

C10u6.3X50805-RH-2C4C10u6.3X50805-RH-2

R33

R33

100R0402

100R0402

R34

R34

100R0402

100R0402

C3

C14

C14

C22u6.3X50805-RH

C22u6.3X50805-RH

C6

C10u6.3X50805-RH-2C3C10u6.3X50805-RH-2

C10u6.3X50805-RH-2C6C10u6.3X50805-RH-2

R30 0R0402R30 0R0402

R31 0R0402R31 0R0402

PM_DPRSLPVR (42)

VCCSENSE (42)

VSSSENSE (42)

C7

C5

C10u6.3X50805-RH-2C5C10u6.3X50805-RH-2

+V1.1S_VTT(4,7,11,20,21,22,34,40,41,42,43)

+V1.1S_VTT(4,7,11,20,21,22,34,40,41,42,43)

C8

C10u6.3X50805-RH-2C7C10u6.3X50805-RH-2

X_C10u6.3X50805-RH-2C8X_C10u6.3X50805-RH-2

+VCC_CORE(42,43)

+VCC_CORE(42,43)

+V1.1S_VTT(4,7,11,20,21,22,34,40,41,42,43)

NO_STUFF

C505

C505

C22u6.3X50805-RH

C22u6.3X50805-RH

C521

C521

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

+VCC_CORE(42,43)

C506

C506

C22u6.3X50805-RH

C22u6.3X50805-RH

C522

C522

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C533

C533

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

3

C507

C507

C22u6.3X50805-RH

C22u6.3X50805-RH

C523

C523

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C534

C534

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

22u*12

C508

C508

C22u6.3X50805-RH

C22u6.3X50805-RH

C524

C524

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C535

C535

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C509

C509

C22u6.3X50805-RH

C22u6.3X50805-RH

C525

C525

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C536

C536

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C513

C510

C510

C22u6.3X50805-RH

C22u6.3X50805-RH

C511

C511

C22u6.3X50805-RH

C22u6.3X50805-RH

C512

C512

C22u6.3X50805-RH

C22u6.3X50805-RH

C513

C22u6.3X50805-RH

C22u6.3X50805-RH

C514

C514

C22u6.3X50805-RH

C22u6.3X50805-RH

10u*16

C528

C527

C526

C526

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C527

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

EMERALD BAY

EMERALD BAY

EMERALD BAY

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

2

C528

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

MCP (4 of 7)

MCP (4 of 7)

MCP (4 of 7)

C529

C529

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C530

C530

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C515

C515

C22u6.3X50805-RH

C22u6.3X50805-RH

C531

C531

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

653Thursday, September 25, 2008

653Thursday, September 25, 2008

653Thursday, September 25, 2008

1

Intel Confidential

Intel Confidential

Intel Confidential

of

of

of

C516

C516

C22u6.3X50805-RH

C22u6.3X50805-RH

C532

C532

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

A

A

A

Page 7

5

4

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR (GRAPHICS POWER)

C22u6.3X50805-RH

C22u6.3X50805-RH

C40

C40

C22u6.3X50805-RH

C22u6.3X50805-RH

C22

C22

C10u6.3X50805-RH-2

C10u6.3X50805-RH-2

C35

C35

C22u6.3X50805-RH

C22u6.3X50805-RH

+V1.1S_VCC_PEG_DMI(4,6,11,20,21,22,34,40,41,42,43)

+VGFX_CORE(41,43)

C23

C23

C10u6.3X50805-RH-2

C10u6.3X50805-RH-2

AT21

AT19

AT18

AT16

AR21

AR19

AR18

AR16

AP21

AP19

AP18

AP16

AN21

AN19

AN18

AN16

AM21

AM19

AM18

AM16

AL21

AL19

AL18

AL16

AK21

AK19

AK18

AK16

AJ21

AJ19

AJ18

AJ16

AH21

AH19

AH18

AH16

U1G

U1G

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

GRAPHICS

GRAPHICS

FDI PEG & DMI

FDI PEG & DMI

POWER

POWER

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

GFX_VR_EN

GFX_DPRSLPVR

GRAPHICS VIDs

GRAPHICS VIDs

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

1.1V1.8V

1.1V1.8V

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_IMON

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

GFXVR_DPRSLPVR_R

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

+V1.1S_VCC_SA (4,6,11,20,21,22,34,40,41,42,43) +V1.1S_VTT(4,6,11,20,21,22,34,40,41,42,43)

J18

H21

H20

H19

+V1.8S_VCCSFR (21,26,40,43,46,48) +V1.8S(21,26,40,43,46,48)

L26

L27

M26

VCC_AXG_SENSE (41)

VSS_AXG_SENSE (41)

GFXVR_VID_0 (41)

GFXVR_VID_1 (41)

GFXVR_VID_2 (41)

GFXVR_VID_3 (41)

GFXVR_VID_4 (41)

GFXVR_VID_5 (41)

GFXVR_VID_6 (41)

GFXVR_EN

R35 0R0402R35 0R0402

C26

C26

C27

C27

C1u10X50402-RH

C1u10X50402-RH

C1u10X50402-RH

C1u10X50402-RH

C44

C44

C45

C45

C1u10X50402-RH

C1u10X50402-RH

C1u10X50402-RH

C1u10X50402-RH

C28

C28

C1u10X50402-RH

C1u10X50402-RH

C46

C46

GFXVR_EN (46)

GFXVR_DPRSLPVR (41)

GFXVR_IMON (41)

C29

C29

C30

C30

C31

C1u10X50402-RH

C1u10X50402-RH

C31

C22u6.3X50805-RH

C22u6.3X50805-RH

C1u10X50402-RH

C1u10X50402-RH

C47

C47

C2.2u6.3X5

C2.2u6.3X5

C4.7u6.3X5-1

C4.7u6.3X5-1

GFXVR_EN

C32

C32

C22u6.3X50805-RH

C22u6.3X50805-RH

C48

C48

C22u6.3X50805-RH

C22u6.3X50805-RH

+

+

12

R591 X_4.7KR0402R591 X_4.7KR0402

NO_STUFF

+V1.5(13,14,39,43,45)

EC40

EC40

C330u2.5SO-RH

C330u2.5SO-RH

+V1.1S_VTT(4,6,11,20,21,22,34,40,41,42,43)+V1.1S_VCCTTA_DDR(4,6,11,20,21,22,34,40,41,42,43)

D D

+VCC_GFXCORE (41,43)

+

+

12

EC24

EC24

C330u2.5SO-RH

C330u2.5SO-RH

+

+

12

EC25

EC25

C330u2.5SO-RH

C330u2.5SO-RH

+

+

12

EC26

EC26

X_C330u2.5SO-RH

X_C330u2.5SO-RH

C21

C21

C22u6.3X50805-RH

C22u6.3X50805-RH

NO_STUFF

C15

C15

C22u6.3X50805-RH

C22u6.3X50805-RH

C C

+V1.1S_VTT(4,6,11,20,21,22,34,40,41,42,43) +V1.1S_VCC_FDI(4,6,11,20,21,22,34,40,41,42,43)

C34

C34

+V1.1S_VTT(4,6,11,20,21,22,34,40,41,42,43)

C39

C39

C38

C38

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

B B

C22u6.3X50805-RH

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

+VCC_GFXCORE(41,43)

C470

C467

C467

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

A A

5

4

C470

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

3

Intel Confidential

Intel Confidential

EMERALD BAY

EMERALD BAY

EMERALD BAY

Title

Title

Title

MCP (5 of 7)

MCP (5 of 7)

MCP (5 of 7)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

2

Intel Confidential

of

of

of

753Thursday, September 25, 2008

753Thursday, September 25, 2008

753Thursday, September 25, 2008

1

A

A

A

Page 8

5

4

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR (GND)

D D

C C

B B

AT20

AT17

AR31

AR28

AR26

AR24

AR23

AR20

AR17

AR15

AR12

AR9

AR6

AR3

AP20

AP17

AP13

AP10

AP7

AP4

AP2

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AM8

AM5

AM2

AL34

AL31

AL23

AL20

AL17

AL12

AL9

AL6

AL3

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AH9

AH6

AH3

AG10

AF8

AF4

AF2

AE35

U1H

U1H

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

U1I

U1I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

VSS

VSS

NCTF

NCTF

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

TP_MCP_VSS_NCTF1

AT35

TP_MCP_VSS_NCTF2

AT1

AR34

B34

B2

TP_MCP_VSS_NCTF6

B1

TP_MCP_VSS_NCTF7

A35

TP10TP10

TP11TP11

TP12TP12

TP13TP13

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

A A

5

4

3

EMERALD BAY

EMERALD BAY

EMERALD BAY

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

MCP (6 of 7)

MCP (6 of 7)

MCP (6 of 7)

2

Intel Confidential

Intel Confidential

Intel Confidential

A

A

A

of

of

of

853Thursday, September 25, 2008

853Thursday, September 25, 2008

853Thursday, September 25, 2008

1

Page 9

5

4

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR (RESERVED)

U1E

U1E

RSVD32

TP14TP14

TP_RSVD1

TP_RSVD2

TP15TP15

TP_RSVD3

TP16TP16

TP17TP17

D D

CFG7

M_VREF_DQ_DIMM0(13)

M_VREF_DQ_DIMM1(14)

R663

R663

3KR0402

3KR0402

M_VREF_DQ_DIMM0

M_VREF_DQ_DIMM1

R585 X_0RR585 X_0R

R586 X_0RR586 X_0R

TP_RSVD9

TP_RSVD10

CFG[0:18](11,12)

TP18TP18

TP19TP19

TP20TP20

TP21TP21

TP24TP24

TP25TP25

TP26TP26

TP27TP27

TP_RSVD4

TP_RSVD5

TP_RSVD6

TP_RSVD7

TP_RSVD8

TP_RSVD11

TP_RSVD12

TP_RSVD13

TP_RSVD14

C C

TP28TP28

R39 0R0402R39 0R0402

R38 0R0402R38 0R0402

B B

TP29TP29

TP30TP30

TP31TP31

TP32TP32

TP33TP33

TP34TP34

TP35TP35

TP36TP36

TP37TP37

TP38TP38

TP39TP39

TP40TP40

TP41TP41

TP_RSVD15

TP_RSVD16

H_RSVD17_R

H_RSVD18_R

TP_RSVD19

TP_RSVD20

TP_RSVD21

TP_RSVD22

TP_RSVD24

TP_RSVD26

TP_RSVD27

TP_RSVD28

TP_RSVD29

TP_RSVD30

TP_RSVD31

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

AP25

AL25

AL24

AL22

AJ33

AG9

M27

H17

G25

G17

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

L28

J17

E31

E30

H16

B19

A19

A20

B20

U9

T9

AC9

AB9

C1

A3

J29

J28

A34

A33

C35

B35

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

RSVD_TP_86

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD_NCTF_23

RSVD_NCTF_24

RSVD26

RSVD27

RSVD_NCTF_28

RSVD_NCTF_29

RSVD_NCTF_30

RSVD_NCTF_31

RESERVED

RESERVED

RSVD33

RSVD34

RSVD35

RSVD36

RSVD_NCTF_37

RSVD38

RSVD39

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RSVD58

RSVD_TP_59

RSVD_TP_60

KEY

RSVD62

RSVD63

RSVD64

RSVD65

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

VSS

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

AP1

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

D15

C15

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

TP_RSVD32

TP_RSVD33

TP_RSVD34

TP_RSVD35

TP_RSVD36

TP_RSVD37

TP_RSVD38

TP_RSVD39

TP_RSVD40

TP_RSVD41

TP_RSVD42

TP_RSVD43

TP_RSVD45

TP_RSVD46

TP_RSVD47

TP_RSVD48

TP_RSVD49

TP_RSVD50

TP_RSVD51

TP_RSVD52

TP_RSVD53

TP_RSVD54

TP_RSVD55

TP_RSVD56

TP_RSVD57

TP_RSVD58

TP_RSVD59

TP_RSVD60

TP_RSVD61

TP_RSVD62

TP_RSVD63

RSVD64_R

RSVD65_R

TP_RSVD66

TP_RSVD67

TP_RSVD68

TP_RSVD69

TP_RSVD70

TP_RSVD71

TP_RSVD72

TP_RSVD73

TP_RSVD74

TP_RSVD75TP_RSVD23

TP_RSVD76

TP_RSVD77

TP_RSVD78

TP_RSVD79

TP_RSVD80

TP_RSVD81

TP_RSVD82

TP_RSVD83

TP_RSVD84

TP_RSVD85

TP_RSVD86

TP62TP62

TP82TP82

TP83TP83

TP84TP84

TP85TP85

TP86TP86

TP87TP87

TP88TP88

TP89TP89

TP91TP91

TP90TP90

TP92TP92

TP93TP93

TP72TP72

TP71TP71

TP64TP64

TP63TP63

TP65TP65

TP66TP66

TP69TP69

TP70TP70

TP67TP67

TP68TP68

TP73TP73

TP74TP74

TP75TP75

TP76TP76

TP77TP77

TP78TP78

TP79TP79

TP80TP80

TP81TP81

R37 0R0402R37 0R0402

R36 0R0402R36 0R0402

TP42TP42

TP43TP43

TP45TP45

TP44TP44

TP47TP47

TP46TP46

TP53TP53

TP52TP52

TP49TP49

TP48TP48

TP50TP50

TP51TP51

TP59TP59

TP58TP58

TP55TP55

TP54TP54

TP56TP56

TP57TP57

TP60TP60

TP61TP61

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

A A

5

4

3

EMERALD BAY

EMERALD BAY

EMERALD BAY

Title

Title

Title

MCP (7 of 7)

MCP (7 of 7)

MCP (7 of 7)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

2

Intel Confidential

Intel Confidential

Intel Confidential

A

A

A

of

of

of

953Thursday, September 25, 2008

953Thursday, September 25, 2008

953Thursday, September 25, 2008

1

Page 10

5

4

3

2

1

On Board DDR3 Thermal Sensor

+V3.3S (11,13,14,15,16,17,19,20,21,22,24,25,26,29,30,31,34,35,36,37,40,41,42,43,45,46,49,50)

U2

EC35

EC35

U2

1

VDD

2

D+

3

D-

4

THERM

SNSR-ADM1032ARMZ-REEL7-RH

SNSR-ADM1032ARMZ-REEL7-RH

Layout Note:

Place U3F1

under DIMM 0

+V12S(16,25,30,31,37,39,43)

C627 C4.7u16X0805-RHC627 C4.7u16X0805-RH

NO_STUFF

DS

R647

G

R647

X_0R0805

X_0R0805

+

+

12

SCLK

SDATA

ALERT

GND

CPU_PFAN

8

7

6

5

SMB_CLK_S3

SMB_DATA_S3

PM_EXTTS_L1

D24

1N4148WS-7-F_SOD323-RH

1N4148WS-7-F_SOD323-RH

FAN1

FAN1

4

3

2

1

BH1X4B-FR_WHITE

BH1X4B-FR_WHITE

FAN2

FAN2

4

3

2

1

BH1X4B-FR_WHITE

BH1X4B-FR_WHITE

D24

F_PWM04

MEC1

MEC1

SMB_CLK_S3 (11,13,14,16,34,35,36,37,39)

SMB_DATA_S3 (11,13,14,16,34,35,36,37,39)

PM_EXTTS_L1 (4,13,14)

+V12S(16,25,30,31,37,39,43)

R40

R40

4.7KR0402

4.7KR0402

R41

R41

27KR1%0402-RH

27KR1%0402-RH

R42

R42

10KR1%0402

10KR1%0402

CPU_TACHO_FAN

C50

C50

X_C0.047u16Y0402

X_C0.047u16Y0402

CPU_TACHO_FAN (36)

NO_STUFF

Layout Note:

Place Q1

near minicard

D D

PM_EXTTS_L0(4)

CPU Fan Power Control

C49

C49

C0.1u16Y0402

C C

CPU_PWM_FAN(36)

C0.1u16Y0402

CPU_PWM_FAN

CPU_PWM_FAN

+V12S(16,25,30,31,37,39,43)

U46A

U46A

3

+

+

1

2

-

-

LM358DR2G_SOIC8

LM358DR2G_SOIC8

4 8

R600

R599

R599

3.9KR1%0402

3.9KR1%0402

NO_STUFF

R600

10KR1%0402

10KR1%0402

CPU_PFAN

F_PWM02 F_PWM03

R646 X_100R0402R646 X_100R0402

N-SST3904_SOT23

N-SST3904_SOT23

E

E

B

B

C

C

Q1

Q1

F_PWM01

DDR_THERM1

DDR_THERM2

PM_EXTTS_L0

Q85

Q85

P-P1604EDG_TO252-RH

P-P1604EDG_TO252-RH

CD100u16EL5-RH

CD100u16EL5-RH

PWM FAN : Stuff R646,R647

B B

No Stuff U46,R600,R599,Q85

System Fan Control

+V12S(16,25,30,31,37,39,43)

U46B

U46B

5

+

SYS_PWM_FAN(36)

SYS_PWM_FAN

+

6

-

-

LM358DR2G_SOIC8

LM358DR2G_SOIC8

4 8

R601

R602

R602

3.9KR1%0402

3.9KR1%0402

R601

10KR1%0402

10KR1%0402

F_PWM06 F_PWM07

F_PWM05

7

P-FDS6679_SOIC8

P-FDS6679_SOIC8

CD100u16EL5-RH

CD100u16EL5-RH

A A

NO_STUFF

R648 X_100R0402R648 X_100R0402

SYS_PFANSYS_PWM_FAN

PWM FAN : Stuff R648,R649

No Stuff U46,R601,R602,Q87

5

4

+V12S(16,25,30,31,37,39,43)

C628 C4.7u16X0805-RHC628 C4.7u16X0805-RH

1N4148WS-7-F_SOD323-RH

4

3

1

R649

Q87

Q87

7 2

685

+

+

12

EC36

EC36

R649

X_0R0805

X_0R0805

NO_STUFF

1N4148WS-7-F_SOD323-RH

SYS_PFAN

D25

D25

FAN3

FAN3

4

3

2

1

3

+V12S(16,25,30,31,37,39,43)

MEC1

BH1X4B_BROWN-RH

BH1X4B_BROWN-RH

R43

R43

4.7KR0402

4.7KR0402

R44

R44

27KR1%0402-RH

27KR1%0402-RH

EMERALD BAY

EMERALD BAY

EMERALD BAY

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

SYS_TACHO_FANF_PWM08

R45

R45

10KR1%0402

10KR1%0402

FAN HEADERS

FAN HEADERS

FAN HEADERS

2

C52

C52

X_C0.047u16Y0402

X_C0.047u16Y0402

NO_STUFF

SYS_TACHO_FAN (36)

Intel Confidential

Intel Confidential

Intel Confidential

of

of

of

10 53Thursday, September 25, 2008

10 53Thursday, September 25, 2008

10 53Thursday, September 25, 2008

1

A

A

A

Page 11

5

4

3

2

1

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

XDP

J1

J1

VSS

BPM5#

BPM4#

VSS

BPM3#

BPM2#

VSS

BPM1#

BPM0#

VSS

BPM5#1

BPM4#1

VSS

BPM3#1

BPM2#1

VSS

BPM1#1

BPM0#1

VSS

PWRGD

NC1

VTT

NC2

NC3

VSS

SDA

SCL

TCK1

TCK0

VSS

61

X_BTB60PF-RH

X_BTB60PF-RH

VSS

NC4

NC5

VSS

NC6

NC7

VSS

NC8

NC9

VSS

NC10

NC11

VSS

NC12

NC13

VSS

NC14

NC15

VSS

ITP_CLKP

ITP_CLKN

VTT

RESET_IN#

RESET_OUT#

VSS

TDO

TRST#

TMS

VSS

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

TDI

58

60

62

62

XDP_RST_R

XDP_RST_R

CFG8 (9)

CFG9 (9)

CFG0 (9,12)

CFG1 (9)

CFG2 (9)

CFG3 (9,12)

CFG10 (9)

CFG11 (9)

CFG4 (9,12)

CFG5 (9)

CFG6 (9)

CFG7 (9)

R51 1KR0402R51 1KR0402

XDP_TRST_L (4)

XDP_TDI (4)

XDP_TMS (4)

R53 X_0R0402R53 X_0R0402

T-spec req#100:

Default is CPURST# routed

to XDP. Would like a stuff

option to have PLTRST

routed to XDP instead.

XDP_DBRESET_L(4,35) PM_SYSRST_L (17,44)

NO_STUFF

BCLK_ITP (4)

BCLK_ITP_L (4)

+V1.1S_VTT(4,6,7,20,21,22,34,40,41,42,43)

NO_STUFF

C54

C54

X_C0.1u16Y0402

X_C0.1u16Y0402

H_CPURST_L (4)

PLT_RST_L (19,29,32,35,36,37,45,50)

NO_STUFF

R63 0R0402R63 0R0402

R64 X_0R0402R64 X_0R0402

NO_STUFF

+V3.3S (10,13,14,15,16,17,19,20,21,22,24,25,26,29,30,31,34,35,36,37,40,41,42,43,45,46,49,50)

R48

R62

R62

X_1KR0402

X_1KR0402

R48

1KR0402

1KR0402

R47

R47

51R1%0402

51R1%0402

+V3.3S(10,13,14,15,16,17,19,20,21,22,24,25,26,29,30,31,34,35,36,37,40,41,42,43,45,46,49,50)

XDP_DBRESET_L (4,35)

XDP_TDO (4)

Note: Provision for XDP_DBRESET# to toggle both

PM_SYSRST# & Delay VR Powergood

Default: DBRESET toggles PM_SYSRST#

Stuff - R6D1, R7P3 (page#23), No-Stuff - R6D2, R6D3

DBRESET toggles Delay VR Powergood

Stuff- R6D2, R6D3 , No-Stuff- R6D1, R7P3 (page#23)

Delay_VR_PWRGOOD (42,46)

D D

XDP_PREQ_L(4)

XDP_PRDY_L(4)

+V1.1S_VTT(4,6,7,20,21,22,34,40,41,42,43)

CFG17(9)

C53

C53

X_C0.1u16Y0402

X_C0.1u16Y0402

NO_STUFF

H_CPUPWRGD(4,20)

C C

CFG16(9)

XDP_OBS4(4)

XDP_OBS5(4)

XDP_OBS6(4)

XDP_OBS7(4)

PM_PWRBTN_L(17,35,36,44)

H_PWRGD_XDP(4)

SMB_DATA_S3(10,13,14,16,34,35,36,37,39)

SMB_CLK_S3(10,13,14,16,34,35,36,37,39)

XDP_TCLK(4)

XDP_OBS[3:0](4)

CFG[12:15](9)

B B

CFG18(9)

XDP_OBS0_R

XDP_OBS1_R

XDP_OBS2_R

XDP_OBS3_R

R46 1KR0402R46 1KR0402

R49 0R0402R49 0R0402

R50 0R0402R50 0R0402

XDP_OBS0

1

XDP_OBS1

3

XDP_OBS2

5

XDP_OBS3

7

CFG15

1

CFG13

3

CFG14

5

CFG12

7

NO_STUFF

R61 X_0R0402R61 X_0R0402

NO_STUFF

+V1.1S_VTT(4,6,7,20,21,22,34,40,41,42,43)

R65 X_51R1%0402R65 X_51R1%0402

H_CPUPWRGD_XDP

PM_PWRBTN_XDP

H_PWGD_XDP

RN8

RN8

2

4

6

8

8P4R-0R0402-2

8P4R-0R0402-2

RN9

RN9

2

4

6

8

X_8P4R-0R0402-2

X_8P4R-0R0402-2

XDP_OBS3_R

XDP_OBS1_R

XDP_OBS2_R

XDP_OBS0_R

PM_PWRBTN_XDPCFG18

PM_PWRBTN_XDP

NO_STUFF

A A

5

4

3

EMERALD BAY

EMERALD BAY

EMERALD BAY

Title

Title

Title

XDP (MCP)

XDP (MCP)

XDP (MCP)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

2

Intel Confidential

Intel Confidential

Intel Confidential

A

A

A

of

of

of

11 53Thursday, September 25, 2008

11 53Thursday, September 25, 2008

11 53Thursday, September 25, 2008

1

Page 12

5

4

3

2

1

D D

CFG0(9,11)

PCI-Express Configuration Select

CFG0 1:Single PEG

C C

CFG3 - PCI-Express Static Lane Reversal

CFG3

CFG4 - Display Port Presence

0:Bifurcation enabled

1 :Normal Operation

0 :Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

CFG4

CFG3(9,11)

CFG4(9,11)

1:Disabled; No Physical Display Port

attached to Embedded Display Port

0:Enabled; An external Display Port

device is connected to the Embedded

Display Port

CFG0

CFG3

CFG4

NO_STUFF

R66

R66

X_3.01KR1%0402

X_3.01KR1%0402

NO_STUFF

R67

R67

X_3.01KR1%0402

X_3.01KR1%0402

R68

R68

X_3.01KR1%0402

X_3.01KR1%0402

NO_STUFF

Layout Note:

Location of all CFG strap resistors needs

to be close to trace to minimize stub

B B

A A

5

4

3

EMERALD BAY

EMERALD BAY

EMERALD BAY

Title

Title

Title

PROCESSOR STRAPS

PROCESSOR STRAPS

PROCESSOR STRAPS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

2

Intel Confidential

Intel Confidential

Intel Confidential

A

A

A

of

of

of

12 53Thursday, September 25, 2008

12 53Thursday, September 25, 2008

12 53Thursday, September 25, 2008

1

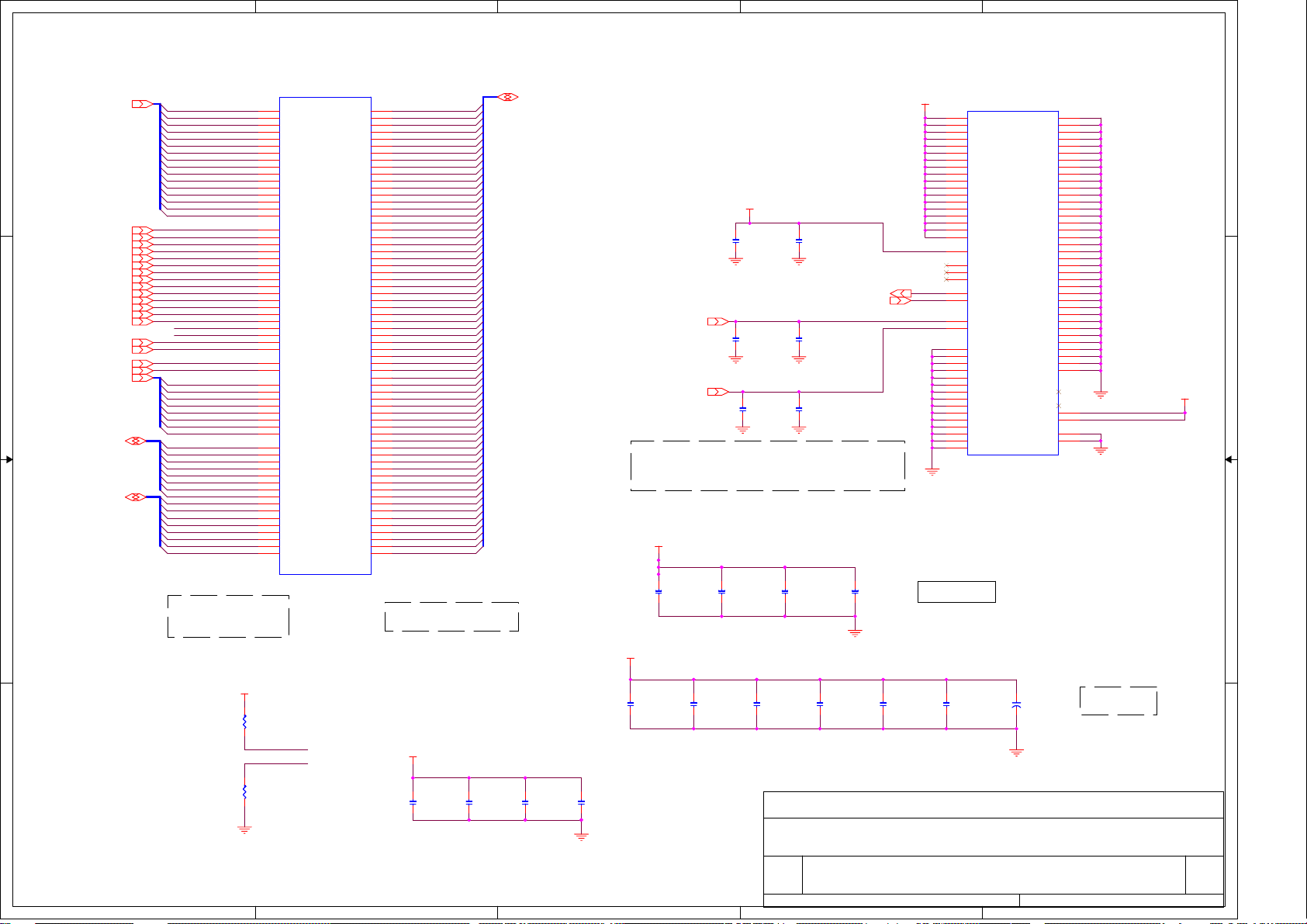

Page 13

5

0

4

3

2

1

Channel A High :9.2mm

DIMM1A

M_A_A[15:0](5)

D D

M_A_BS0(5)

M_A_BS1(5)

M_A_BS2(5)

M_CS_L0(5)

M_CS_L1(5)

M_CLK_DDR0(5)

M_CLK_DDR0_L(5)

M_CLK_DDR1(5)

M_CLK_DDR1_L(5)

M_CKE0(5)

M_CKE1(5)

M_A_CAS_L(5)

M_A_RAS_L(5)

M_A_WE_L(5)

M_ODT0(5)

M_ODT1(5)

SODIMM0_1_SMB_CLK_R

SODIMM0_1_SMB_DATA_R

SMB_CLK_S2(10,11,14,16,34,35,36,37,39)

SMB_DATA_S2(10,11,14,16,34,35,36,37,39)

M_A_DM[7:0](5)

C C

M_A_DQS[7:0](5)

M_A_DQS_L[7:0](5)

M_CS_L0

M_CS_L1

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

SA0_DIM0

SA1_DIM0

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS_L0

M_A_DQS_L1

M_A_DQS_L2

M_A_DQS_L3

M_A_DQS_L4

M_A_DQS_L5

M_A_DQS_L6

M_A_DQS_L7

DIMM1A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDRIIISODIMM-204PS_BLACK-RH-1

DDRIIISODIMM-204PS_BLACK-RH-1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

M_A_DQ0

5

M_A_DQ1

7

M_A_DQ2

15

M_A_DQ3

17

M_A_DQ4

4

M_A_DQ5

6

M_A_DQ6

16

M_A_DQ7

18

M_A_DQ8

21

M_A_DQ9

23

M_A_DQ10

33

M_A_DQ11

35

M_A_DQ12

22

M_A_DQ13

24

M_A_DQ14

34

M_A_DQ15

36

M_A_DQ16

39

M_A_DQ17

41

M_A_DQ18

51

M_A_DQ19

53

M_A_DQ20

40

M_A_DQ21

42

M_A_DQ22

50

M_A_DQ23

52

M_A_DQ24

57

M_A_DQ25

59

M_A_DQ26

67

M_A_DQ27

69

M_A_DQ28

56

M_A_DQ29

58

M_A_DQ30

68

M_A_DQ31

70

M_A_DQ32

129

M_A_DQ33

131

M_A_DQ34

141

M_A_DQ35

143

M_A_DQ36

130

M_A_DQ37

132

M_A_DQ38

140

M_A_DQ39

142

M_A_DQ40

147

M_A_DQ41

149

M_A_DQ42

157

M_A_DQ43

159

M_A_DQ44

146

M_A_DQ45

148

M_A_DQ46

158

M_A_DQ47

160

M_A_DQ48

163

M_A_DQ49

165

M_A_DQ50

175

M_A_DQ51

177

M_A_DQ52

164

M_A_DQ53

166

M_A_DQ54

174

M_A_DQ55

176

M_A_DQ56

181

M_A_DQ57

183

M_A_DQ58

191

M_A_DQ59

193

M_A_DQ60

180

M_A_DQ61

182

M_A_DQ62

192

M_A_DQ63

194

M_A_DQ[63:0] (5)

+V3.3S(10,11,14,15,16,17,19,20,21,22,24,25,26,29,30,31,34,35,36,37,40,41,42,43,45,46,49,50)

C55

C55

C0.1u16Y0402

C0.1u16Y0402

M_VREF_DQ_DIMM0(39)

C57

C57

C0.1u16Y0402

C0.1u16Y0402

M_VREF_DQ_DIMM0(39)

C59

C59

C0.1u16Y0402

C0.1u16Y0402

VRefCA on both SO-DIMMs can be connected by a single M_VREF_MCH trace

VRefDQ on both SO-DIMMs can be shared by a second separate M_VREF_MCH trace

+V0.75S(14,39,43)

C61

C61

C1u10Y0402-RH

C1u10Y0402-RH

C56

C56

C2.2u6.3X5

C2.2u6.3X5

DDR3_DRAMRST_L(4,14)

M_VREF_DQ_DIMM0

C58

C58

M_VREF_DQ_DIMM0

C60

C60

C62

C62

C1u10Y0402-RH

C1u10Y0402-RH

PM_EXTTS_L1(4,10,14)

C2.2u6.3X5

C2.2u6.3X5

C2.2u6.3X5

C2.2u6.3X5

C63

C63

C1u10Y0402-RH

C1u10Y0402-RH

+V1.5(7,14,39,43,45)

C64

C64

C1u10Y0402-RH

C1u10Y0402-RH

DIMM1B

75

VDD

76

VDD

81

VDD

82

VDD

87

VDD

88

VDD

93

VDD

94

VDD

99

VDD

100

VDD

105

VDD

106

VDD

111

VDD

112

VDD

117

VDD

118

VDD

123

VDD

124

VDD

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS

3

VSS

8

VSS

9

VSS

13

VSS

14

VSS

19

VSS

20

VSS

25

VSS

26

VSS

31

VSS

32

VSS

37

VSS

38

VSS

43

VSS

DDRIIISODIMM-204PS_BLACK-RH-1

DDRIIISODIMM-204PS_BLACK-RH-1

Place near Vtt pins

DIMM1B

44

VSS

48

VSS

49

VSS

54

VSS

55

VSS

60

VSS

61

VSS

65

VSS

66

VSS

71

VSS

72

VSS

127

VSS

128

VSS

133

VSS

134

VSS

138

VSS

139

VSS

144

VSS

145

VSS

150

VSS

151

VSS

155

VSS

156

VSS

161

VSS

162

VSS

167

VSS

168

VSS

172

VSS

173

VSS

178

VSS

179

VSS

184

VSS

185

VSS

189

VSS

190

VSS

195

VSS

196

VSS

MEC1

MEC1

MEC2

MEC2

203

VTT

204

VTT

205

205

206

206

Place these caps

close to VTT1 and

VTT2. Place C21

on common path

for both DIMM's

+V0.75S(14,39,43)

B B

,21,22,24,25,26,29,30,31,34,35,36,37,40,41,42,43,45,46,49,5

Note:

If SA0_DIM0 = 0, SA1_DIM0 = 0

SO-DIMM0 SPD Address is 0xA0

SO-DIMM0 TS Address is 0x30

If SA0_DIM0 = 1, SA1_DIM0 = 0

A A

SO-DIMM0 SPD Address is 0xA2

SO-DIMM0 TS Address is 0x32

5

+V3.3S

NO_STUFF

R70

R70

X_10KR0402

X_10KR0402

R71

R71

10KR0402

10KR0402

SA0_DIM0

SA1_DIM0

R72

R72

10KR0402

10KR0402

+V1.5(7,14,39,43,45)

C65

C65

C10u6.3X50805-1

C10u6.3X50805-1

C66

C66

C10u6.3X50805-1

C10u6.3X50805-1

4

C67

C67

C10u6.3X50805-1

C10u6.3X50805-1

C68

C68

C10u6.3X50805-1

C10u6.3X50805-1

C69

C69

C10u6.3X50805-1

C10u6.3X50805-1