MOTOROLA SN74LS175D, SN74LS175DR2, SN74LS175M, SN74LS175MEL, SN74LS175ML1 Datasheet

...

Semiconductor Components Industries, LLC, 1999

December, 1999 – Rev. 6

1 Publication Order Number:

SN74LS175/D

SN74LS175

Quad D Flip-Flop

The LSTTL / MSI SN74LS175 is a high speed Quad D Flip-Flop.

The device is useful for general flip-flop requirements where clock

and clear inputs are common. The information on the D inputs is

stored during the LOW to HIGH clock transition. Both true and

complemented outputs of each flip-flop are provided. A Master Reset

input resets all flip-flops, independent of the Clock or D inputs, when

LOW.

The LS175 is fabricated with the Schottky barrier diode process for

high speed and is completely compatible with all ON Semiconductor

TTL families.

• Edge-Triggered D-Type Inputs

• Buffered-Positive Edge-Triggered Clock

• Clock to Output Delays of 30 ns

• Asynchronous Common Reset

• True and Complement Output

• Input Clamp Diodes Limit High Speed Termination Effects

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

CC

Supply Voltage 4.75 5.0 5.25 V

T

A

Operating Ambient

T emperature Range

0 25 70 °C

I

OH

Output Current – High –0.4 mA

I

OL

Output Current – Low 8.0 mA

LOW

POWER

SCHOTTKY

Device Package Shipping

ORDERING INFORMATION

SN74LS175N 16 Pin DIP 2000 Units/Box

SN74LS175D 16 Pin

SOIC

D SUFFIX

CASE 751B

http://onsemi.com

2500/Tape & Reel

PLASTIC

N SUFFIX

CASE 648

16

1

16

1

SN74LS175

http://onsemi.com

2

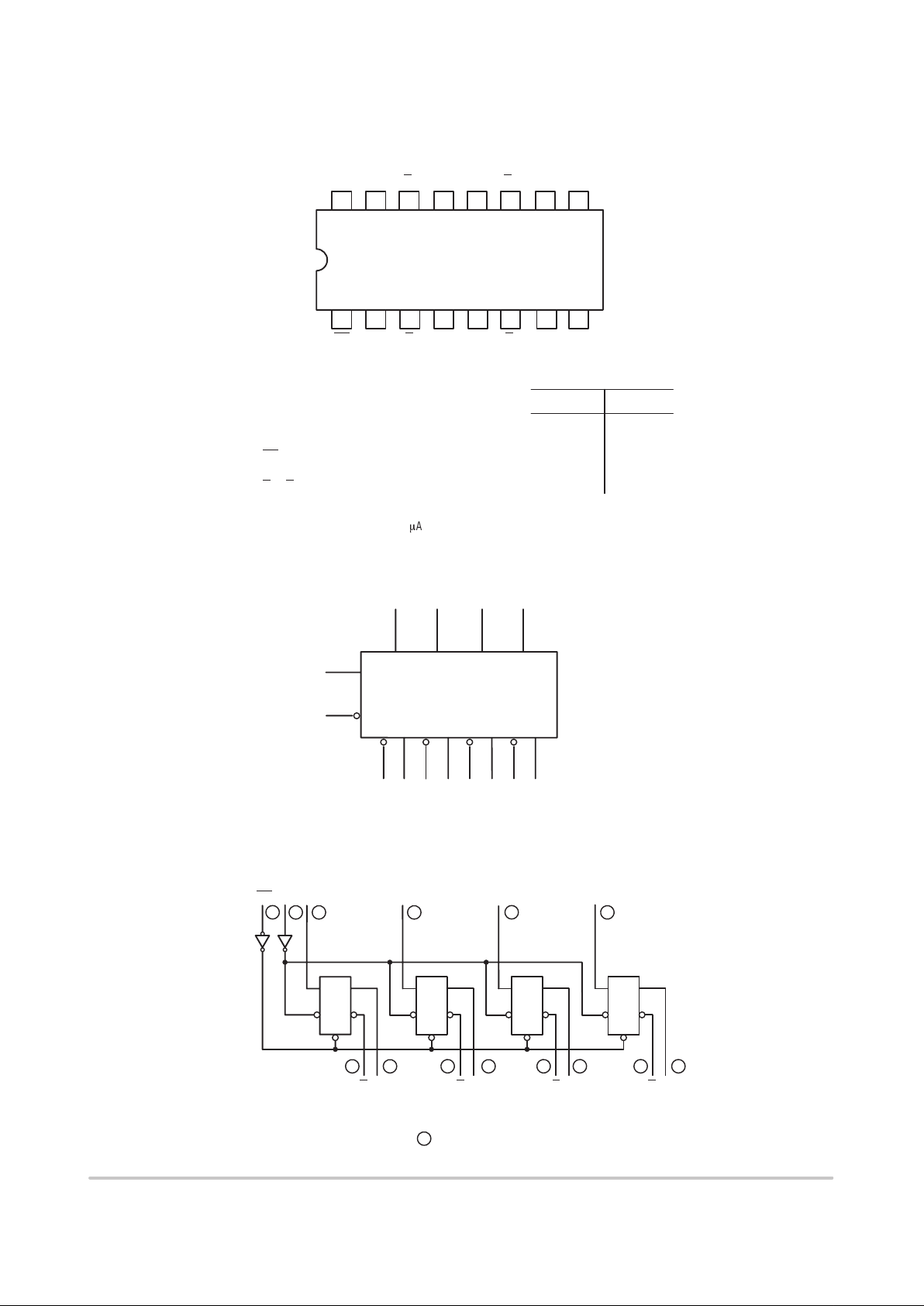

CONNECTION DIAGRAM DIP (TOP VIEW)

Data Inputs

Clock (Active HIGH Going Edge) Input

Master Reset (Active LOW) Input

True Outputs

Complemented Outputs

D

0

– D

3

CP

MR

Q0 – Q

3

Q0 – Q

3

0.5 U.L.

0.5 U.L.

0.5 U.L.

10 U.L.

10 U.L.

0.25 U.L.

0.25 U.L.

0.25 U.L.

5 U.L.

5 U.L.

NOTES:

a) 1 TTL Unit Load (U.L.) = 40 mA HIGH/1.6 mA LOW.

HIGH LOW

(Note a)LOADING

PIN NAMES

LOGIC DIAGRAM

NOTE:

The Flatpak version has the same

pinouts (Connection Diagram) as

the Dual In-Line Package.

VCC = PIN 16

GND = PIN 8

= PIN NUMBERS

LOGIC SYMBOL

VCC = PIN 16

GND = PIN 8

12

1

236711141510

45 13

9CP

D

0

D

1

D

2

D

3

MR

Q

0Q0Q1Q1Q2Q2Q3Q3

DQ

CP

C

D

Q

CP D

3

D

2

D

1

D

0

Q3Q

3

Q2Q

2

Q1Q

1

Q0Q

0

DQ

CP

C

D

Q

MR

14

1

267

3

459

11

12

10

13

15

DQ

CP

C

D

Q

DQ

CP

C

D

Q

14 13 12 11 10 9

123456

7

16 15

8

V

CC

MR

Q3Q3D3D

2

Q

2

Q

2

CP

Q0Q0D0D1Q1Q1GND

SN74LS175

http://onsemi.com

3

FUNCTIONAL DESCRIPTION

The LS175 consists of four edge-triggered D flip-flops

with individual D inputs and Q and Q outputs. The Clock and

Master Reset are common. The four flip-flops will store the

state of their individual D inputs on the LOW to HIGH Clock

(CP) transition, causing individual Q and Q outputs to

follow. A LOW input on the Master Reset (MR

) will force

all Q outputs LOW and Q outputs HIGH independent of

Clock or Data inputs.

The LS175 is useful for general logic applications where

a common Master Reset and Clock are acceptable.

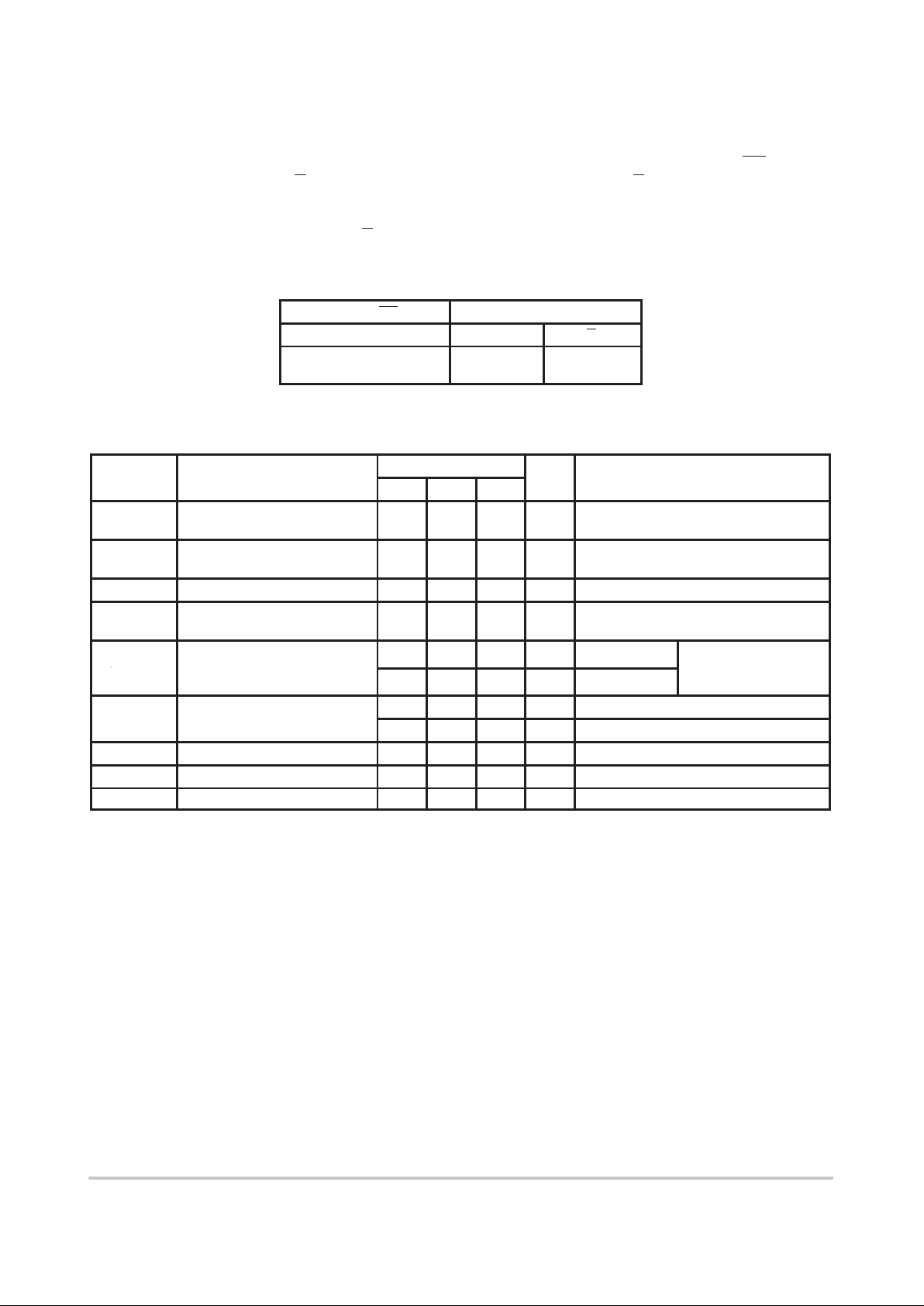

TRUTH TABLE

Inputs (t = n, MR = H) Outputs (t = n+1) Note 1

D Q Q

L L H

H H L

Note 1: t = n + 1 indicates conditions after next clock.

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

Symbol Parameter

Min Typ Max

Unit Test Conditions

V

IH

Input HIGH Voltage 2.0 V

Guaranteed Input HIGH Voltage for

All Inputs

V

IL

Input LOW Voltage

0.8

V

Guaranteed Input LOW Voltage for

All Inputs

V

IK

Input Clamp Diode Voltage –0.65 –1.5 V VCC = MIN, IIN = –18 mA

V

OH

Output HIGH Voltage 2.7 3.5 V VCC = MIN, IOH = MAX, VIN = V

IH

or VIL per Truth Table

p

0.25 0.4 V IOL = 4.0 mA

VCC = VCC MIN,

VOLOutput LOW Voltage

0.35 0.5 V IOL = 8.0 mA

V

IN

=

V

IL

or

V

IH

per Truth Table

p

20 µA VCC = MAX, VIN = 2.7 V

IIHInput HIGH Current

0.1 mA VCC = MAX, VIN = 7.0 V

I

IL

Input LOW Current –0.4 mA VCC = MAX, VIN = 0.4 V

I

OS

Short Circuit Current (Note 1) –20 –100 mA VCC = MAX

I

CC

Power Supply Current 18 mA VCC = MAX

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

Loading...

Loading...