Motorola MC145220EVK Datasheet

SEMICONDUCTOR TECHNICAL DATA

Order this document

by MC145220EVK/D

INTRODUCTION

The MC145220EVK makes it easy to exercise features of the MC145220 and build PLLs which meet

individual performance requirements. The EVK is controlled through menu driven software operating on

an IBM PC or compatible. Other Motorola PLL EVKs (MC145190, MC145191, MC145192, MC145200,

MC145201, MC145202) in up to three–board cascades can use the same program. Frequency defaults

that apply to each are automatically selected. All board functions are controlled through the printer port of

an IBM PC. Up to three different EVKs may be controlled at the same time from one printer port. The

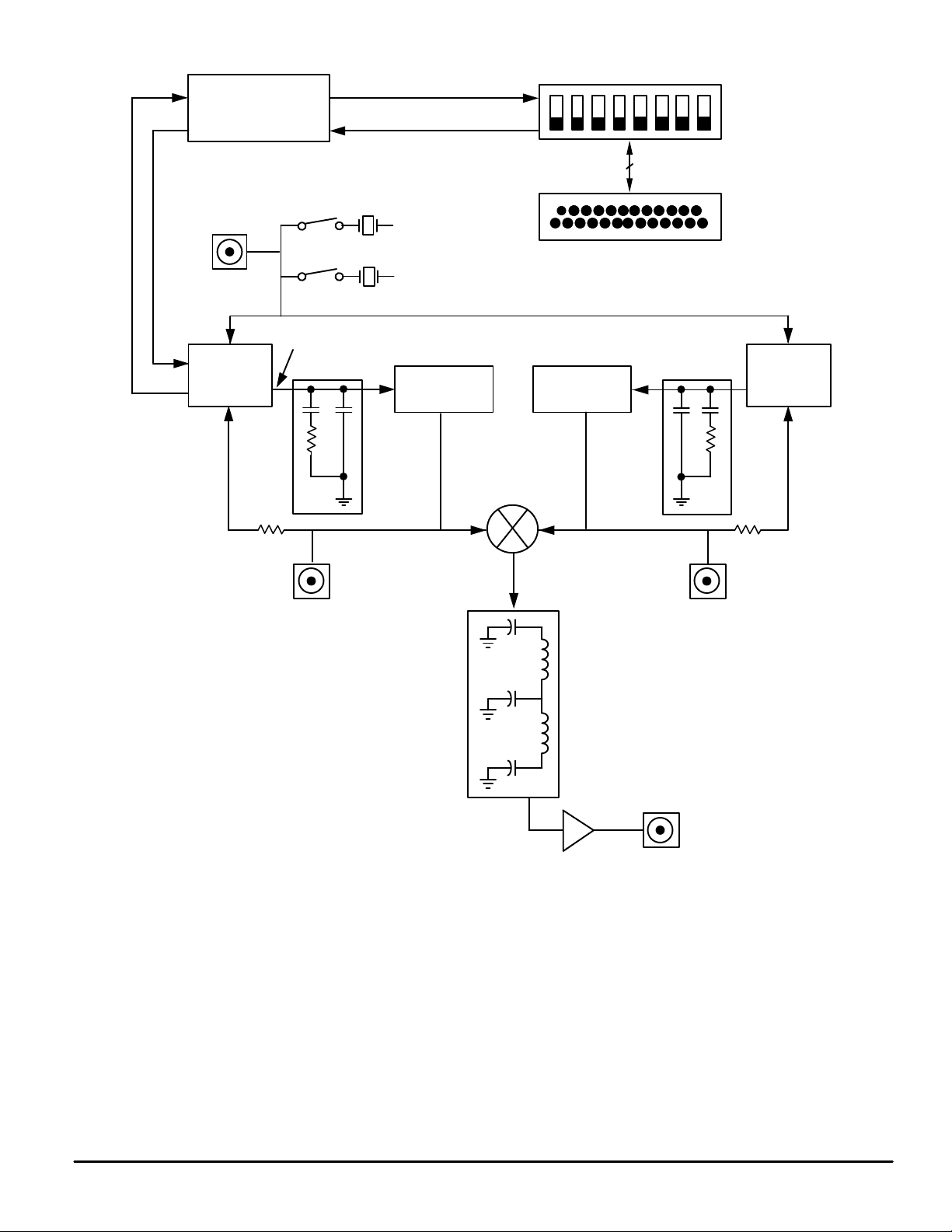

functional block diagram is given in Figure 1.

This manual is divided into three sections. Section 1 describes the hardware, Section 2 describes the

software, and Section 3 is the command summary.

All brand names and product names appearing in this document are registered trademarks or trademarks of their respective holders.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

REV 2

10/96

Motorola, Inc. 1996

MOTOROLA

MC145220EVK

1

MC145220EVK TABLE OF CONTENTS

Section 1 – Hardware 5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Features 5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents of Evaluation Kit 5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Getting Started 5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Modifications 5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Typical Performance 7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Support Material 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Production Test 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Board Operation 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Dual Mode Output 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External Reference Input 11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data Transfer from Computer to EVK 11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Printer Port Configuration 13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Section 2 – Software Descriptions 14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Introduction 14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Purpose 14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Description 14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

User Interface 14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Install 14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Uninstall 15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Conventions 15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Alert and Error Messages 15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Screens 18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

‘Define boards to program’ 18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Help Screen 19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

‘Select from the available options’ 20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

‘Available Boards’ 20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

‘MC145xxx Commands’ 20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

‘Initialization/System Setup Commands’ 20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PLL Output Frequency 22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

REFin Frequency and Channel Spacing 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Set Default Low Frequency 24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Set Function of Output A 25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Change C Register and Prescale 26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Change C Register, PD

Change C Register, Phase Detector Select 28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Change C Register, Polarity 29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Change C Register, Standby 30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Set Output Port Address 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Set Crystal or Reference Mode 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Current 27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

out

Section 3 – Command Summary 33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[A]! Set board A as target 33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[B]! Set board B as target 33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[C]! Set board C as target 33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[L]! Set to low freq. 33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[M]! Set to medium freq. 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[H]! Set to high freq. 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[W] Change default low frequency 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[Y] Change default medium frequency 35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[Z] Change default high frequency 36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[U]! Step frequency up by step size 36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[D]! Step frequency down by step size 36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[O] Set PLL output frequency 37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[F] Set REFin frequency and channel spacing 38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MC145220EVK

2

MOTOROLA

MC145220EVK TABLE OF CONTENTS, continued

[E] Set function of output A 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[0]! Port 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1]! Data Out 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[2]! fv 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[3]! fr 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[N] Change C Register and Prescale 40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[0] Change output A – (Port) 40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[0]! Reset output A to 0 40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1]! Set output A to 1 40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1] Change output B (Out B) (not available on ’220) 40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[0]! Reset output B to 0 40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1]! Set output B to 1 40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[2] Change PD

[0]! 70% 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1]! 80% 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[2]! 90% 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[3]! 100% 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[2] Change PD

[0]! 25% 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1]! 50% 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[2]! 75% 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[3]! 100% 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[2] Change PD

[0]! 5% 42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1]! 50% 42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[2]! 80% 42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[3]! 100% 42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[3] Change phase detector select 42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[0]! phi R & phi V 42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1]! PD

[3] Change phase detector (only available on ’220) 43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[0]! phi R & phi V 43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1]! PD

[4] Change lock detect enable (not available on ’220) 43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[0]! Output low 43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1]! Enable output 43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[5] Change phase detector polarity 43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[0]! Non–invert PD

[1]! Invert PD

[6] Change standby 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[0]! Normal operation 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1]! Standby 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[7] Change prescale (only available on ’220) 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[0]! Prescale 32/33 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1]! Prescale 64/65 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[R] Set crystal/reference mode 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[0]! Crystal mode, shutdown 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[1]! Crystal mode, active 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[2]! Reference mode, REFin enabled, REF

[3]! Reference mode, REF

[4]! Reference mode, REF

[5]! Reference mode, REF

[6]! Reference mode, REF

[7]! Reference mode, REF

[T]! Set target PLL on board 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[P] Set output port address 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

current with Output A defined as port (not available on ’220) 41. . . . . . . . . . . . . . . . . . .

out

current with Output A NOT defined as port (not available on ’220) 41. . . . . . . . . . . . . .

out

current (only available on ’220) 42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

out

out

out

out

out

low 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

= REF

out

= REFin/2 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

out

= REFin/4 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

out

= REFin/8 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

out

= REFin/16 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

out

out

in

42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MOTOROLA

MC145220EVK

3

MC145220EVK TABLE OF CONTENTS, continued

[G] Change board definitions 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[I]! Initialize board(s), write all registers 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[X]! Terminate demonstration program 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[?]! View help screen 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Appendix 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MC145220 PLL Evaluation Board 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MC145220 Power Supply and Reference 48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MC145220EVK Bus Interface 49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MC145220EVK Signal Plot — Dual Loop Mode Output at 70 MHz 50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MC145220EVK Signal Plot — Single Loop Mode PLL on 805 MHz 50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MC145220EVK Signal Plot — Single Loop Mode PLL on 738 MHz 51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bill of Materials: MC145220 PLL Evaluation Board Rev. 4 52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MC145220EVK

4

MOTOROLA

SECTION 1 – HARDWARE

FEATURES

1. The EVK is a complete working synthesizer, including VCOs.

2. Board is controlled by an IBM PC–compatible computer through the printer port.

3. Up to three boards can be operated independently through one printer port.

4. A prototype area and mounting holes are provided for VCOs, mixers, and amplifiers.

5. External reference input can be used.

6. Five element loop filter is included.

7. Frequency range of operation, step size and reference frequency can be changed in the control

program.

8. Lock Detect, Out A, and Out B on any single board are accessible through the printer port.

CONTENTS OF EVALUATION KIT

1. Assembled evaluation board.

2. Nine–foot flat cable with four DB–25 male connectors.

3. MC145220EVK manual.

4. 3.5″ PC–compatible disk containing compiled program.

5. PLL device data sheets.

GETTING STARTED

To perform basic functions, do the following:

1. Plug in 12 volts at J8, observing the polarity marked on the board.

2. Short circuit section 1 of the DIP switch (S1) and open circuit all other sections.

3. Connect the supplied flat cable between the computer printer port and the DB–25 connector on

the board (J9).

4. Type PLL at the DOS prompt. Then press enter.

5. Type the number that corresponds with the type of board given in the on–screen menu. The

MC145220 may operate in single loop or dual loop mode. Then press Q.

You should now see the main menu displayed. There should be a signal present at J5 if single loop, or

J12 if dual loop. The frequency will be the current output frequency given in the main menu. If the signal

is not on the correct frequency , check to see if your printer port address is $278 (hexadecimal 278). If not,

then select the P menu item and enter the correct address. After returning to the main menu, select the

I menu item to send data to the board. You should now be on frequency.

MODIFICATIONS

The user may modify the hardware, such as utilizing a different VCO, by using the prototyping area of the

board. After such modifications are made, the default values in the software may need to be changed.

This is facilitated from the ‘Select from the available options’ screen.

Note that the on–board voltage regulators allow for a maximum VCO control voltage range of 0.5 – 4.5

volts.

MOTOROLA

MC145220EVK

5

Frequency

Control Data

External Reference

Out A, Out B,

Lock Detect

74HCT241, 74LS126

Buffer Logic

PD

out

MC145220

PLL

F

in

Loop Filter

10.01 MHz TCXO

14.4 MHz TCXO

VCO

733 – 743 MHz

REF

in

790 – 820 MHz

LO RF

Logic Control Switches

Parallel Port Connector

Loop Filter

VCO

′

MC145220

′

PLL

F

in

Single Loop Output

733–743 MHz

Figure 1. Evaluation Kit Block Diagram

IF

Single Loop Output

790 – 820 MHz

Fc = 80 MHz

Dual Mode Output

60 – 80 MHz

(f′ – f)

Amplifier

MC145220EVK

6

MOTOROLA

TYPICAL PERFORMANCE

Typical performance applies only to the configuration as shipped. The MC145220EVK is shipped with

V+ = 5 V. For lowest phase noise in single or dual loop mode, a 50 Ω load must be connected to J12.

Single Loop PLL Single Loop PLL′ Dual Loop PLL

Supply Voltage (J8) 11.5 – 12.5 V

Supply Current (J8) (Note 1) 177 mA

Available Current (Note 2)

45 mA

Frequency Range (Note 3) 733 – 743 MHz 790 – 820 MHz 60 – 80 MHz

Reference Frequency (M1) 10.01 MHz

Temperature Stability

< ± 2.5 ppm

(M1, – 30°C to + 70°C)

Reference Frequency (M5) 14.4 MHz

Temperature Stability

< ± 2 ppm

N/A

N/A

(M5, – 30°C to + 85°C)

TCXO Aging (M1, M5) < ± 1 ppm / year

Step Size 10 kHz 10 Hz

Power Output

Frequency Accuracy

Reference Sidebands (Note 4)

Phase Noise (100 Hz)

Phase Noise (10 kHz) (Note 5)

Switching Time (Note 6)

NOTES:

1. Supply current is current the board requires without user modifications.

2. Available current is the sum of currents available to the user (in the prototype area) from the 5 V and 8.5 V supply. The 12 V supply is not

regulated. Current at 12 V is limited by the external power supply . If the on–board VCO and amplifier are disconnected from the power bus,

more current can be drawn in the prototype area. The current flowing into U5 (the 8.5 V regulator) should not exceed 180 mA. This will limit

temperature rise in U5.

3. Frequency ranges require use of the 5 V default charge pump supply voltage.

4. VCO sidebands on PLL at low step sizes (10 kHz) are limited by control line leakage of the VCO. Up to 24 nA of leakage has been seen.

At higher step sizes (100 kHz and above), this effect is much less noticable. This did not affect PLL′ because its VCO leakage was less than

10 pA.

5. 10 kHz phase noise is limited by the PLL device noise. For low noise designs, the loop bandwidth is made narrower and the VCO is relied

upon to provide the 10 kHz phase noise. This can be seen on the EVKs since the VCOs have much lower noise.

6. 10 MHz step, within ± 1 kHz of final frequency (’220).

Due to the software architecture, when the user is measuring the switching time of a single board in dual loop mode, it takes 20 ms to load

the data as compared to single loop mode, which takes 8 ms to load the data. This is a limitation of the software, not the IC.

To find the actual PLL switching time, subtract 8 or 20 ms from the switching time stated in the table.

– 3.0 dBm – 5.0 dBm

± 1.5 kHz ± 1.5 kHz

– 57 dB – 74 dB

– 65 dBc/Hz – 56 dBc/Hz

– 104 dBc/Hz – 90 dBc/Hz

24 ms 40 ms

4.5 – 7.5 dBm

± 50 Hz

– 57 dB

– 50 dBc/Hz

– 89 dBc/Hz

45 ms

MOTOROLA

MC145220EVK

7

SUPPORT MATERIAL

The following documents are included in the appendix:

1. Schematic diagram of MC145220EVK.

2. Bill of materials.

3. Parts layout diagram.

4. Mechanical drawing of board.

5. MC145220 data sheet.

6. Typical signal plots.

PRODUCTION TEST

After assembly is complete, the following alignment and test is performed:

1. The control program is started in ’220 single loop mode.

2. [L]! is selected to set PLL frequency to 733 MHz.

3. Power is applied to the board. DIP switch section 1 is closed circuit with all others being open

circuit.

4. After attaching computer cable, [I]! is selected.

5. Trim resistor VR1 is adjusted to obtain an output frequency at J5 of 733 MHz ± 500 Hz.

6. Voltage at the control voltage test point (TP2) is measured. It must be > 0.5 V.

7. [H]! is selected.

8. Voltage at the control voltage test point (TP2) is measured. It must be < 4.4 V.

9. [T]! is selected to toggle to PLL′.

10. [L]! is selected to set PLL′ frequency to 790 MHz.

11. Voltage at the control voltage test point (TP9) is measured. It must be > 0.5 V.

12. [H]! is selected to set PLL′ frequency to 820 MHz.

13. Voltage at the control voltage test point (TP9) is measured. It must be < 4.4 V.

14. [G] is selected and the board type is changed to ’220 dual loop mode.

15. [Q]!, then [I]!, is selected to initialize the dual mode output (J12) to 70 MHz. The frequency should

be 70 MHz ± 50 Hz.

If in step 5 it isn’t possible to obtain a signal on frequency , the adjustment screw in M1 may be turned for

further frequency adjustment range. If neither adjustment works, [P] should be selected and the correct

printer port address entered. [I]! is then selected to reload the data.

BOARD OPERATION

A computer is connected to the DB–25 connector J9. Data is output from the printer port. The printer card

is in slot 0 using the default address in the control program. Data is sent to the PLL device (U1) through

the DIP switch (S1), and 74HCT241 buffer (U2). D1, D2, D3, R7, R8, and R12 are in the data path between the ’HCT241 and PLL device. This limits the high level output voltage of the buffer . V oltage on PLL

device inputs must be no greater than 0.5 V above V+. A ’220 PLL has three output lines which are

routed through a 74LS126 line driver (U3) back to the computer.

U2, the 74HCT241, provides isolation and logic translation for PLL input lines. Logic translation is needed from the TTL levels on the printer port to the CMOS levels on the ’220 inputs.

A 12 V power supply should be used to power the board at J8 (Augat 2SV–02 connector). The 2SV–02

will accept 18–24 AWG bare copper power leads. No tools are needed for connection. If power is properly connected, LED D4 will be lit.

MC145220EVK

8

MOTOROLA

Power passes from J8 to U5 (LM317 regulator) configured as an 8.5 V regulator. 8.5 V powers the VCOs.

Regulators U6 and U7 use the 8.5 V supply to produce 3 V and 5 V. The ’220 board can use either to

power the logic and charge pump. V+ voltage is selected by J11. U6 and U7 are cascaded with U5 to

equalize their individual voltage drops.

The ’220 operates in both a single loop and dual loop mode. There are no component changes between

the two modes. The differences are in the programming of the counters and the SMA connector that is

used.

The PLL loop is composed of the MC145220 (U1), 733 – 743 MHz VCO (M2), and a passive loop filter

(R4, R5, C6, C7, C8). In single loop mode, output is taken from J5. A passive loop filter was used to keep

the design simple, reduce noise, and reduce the quantity of traces susceptible to stray pickup. The PLL′

loop is composed of the MC145220 (U1), 790 – 820 MHz VCO (M3), and a passive loop filter (R22, R25,

C24, C26, C30). In single loop mode, output is taken from J10.

Dual mode output is the (f′ – f) frequency output from the mixer. It is low pass filtered (L1, L2, C15, C21,

C22) then amplified (U4). The output is available at J12.

Phase detector current is 2 mA. J1 is a removable jumper used for current measurement of V+.

Two TCXOs, a Motorola Saber 14.4 MHz (M5), and Raltron 10.01 MHz (M1) are supplied. As shipped

from the factory, the 10.01 MHz TCXO is in use. This allows both the 10 kHz and 10 Hz step sizes to be

used with one TCXO. 10.01 MHz cannot be divided for larger step sizes such as 100 kHz. For larger step

sizes use the Saber. Jumpers J3, J4, J13, and J14 determine which TCXO or the external reference

input is in use.

DUAL MODE OUTPUT

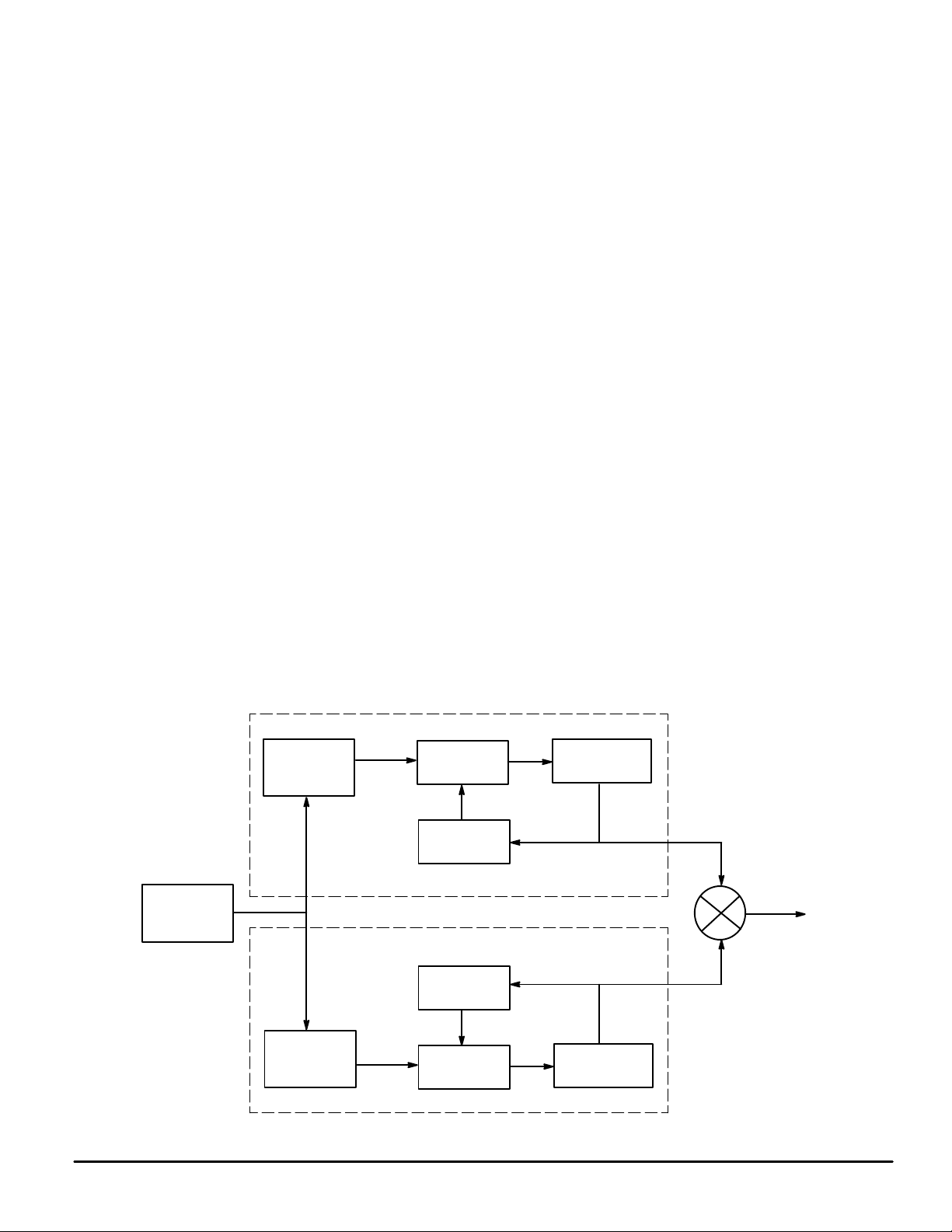

The dual mode output (J12) is the difference frequency from mixing PLL and PLL′. By using a reference

frequency of 10.01 MHz, PLL can be operated with a 10.01 kHz step size and PLL′ with a 10 kHz step

size. If both PLL and PLL′ step down in frequency , the mixed output will step up by 10 Hz. More information on the offset reference technique is in AN1277/D, Offset Reference PLLs for Fine Resolution or

Fast Hopping. The block diagram, formulas, and an example are shown in Figure 2.

REFERENCE

10.01 MHz

R COUNTER

÷

1000

10.01 kHz

PLL

PLL

N = 73,001 – 74,000

N

′

′

PHASE

DETECTOR

÷

N

COUNTER

= 79,075 – 82,074

÷

N

′

COUNTER

VCO

730.7 – 740.7 MHz

MIXER

f

f

′

(f

′ – f)

60 – 80 MHz

(10 Hz STEPS)

MOTOROLA

R′ COUNTER

÷

1001

Figure 2. Dual Mode Block Diagram

10 kHz

PHASE

DETECTOR

VCO

790.7 – 820.7 MHz

MC145220EVK

9

PLL PLL′

f = N (10.01 kHz) f′ = N′ (10 kHz)

f = 10.01 kHz 74,000 –

N = 74,000 –

r(f′ – f)

10 Hz

r(f′ – f)

10 Hz

f′ = 10 kHz

N′ = N + 74 +

w(f′ – f) + 740 kHz

10 kHz

w(f′ – f)

10 kHz

(f′ – f) = w(f′ – f) + r(f′ – f)

(f′ – f) = Desired Output Frequency

w(f′ – f) = Output Frequency Portion that Divides Evenly by 10 kHz

r(f′ – f) = Remainder from Output Frequency Division by 10 kHz

Dual Mode Formulas

Example: Synthesize 76.849 930 MHz

r(f′ – f) = 9.930 kHz, w(f′ – f) = 76.840 MHz

N = 74,000 –

9.930 kHz

= 73,007

f = 73,007 (10.01 kHz) = 730.800 070 MHz

10 Hz

+ N

N ′= 73,007 + 74 +

76.840 MHz

= 80,765

f′ = 80,765 (10 kHz) = 807.650 000 MHz

10 kHz

(f′ – f)= 807.650 000 MHz – 730.800 070 MHz = 76.849 930 MHz

MC145220EVK

10

MOTOROLA

EXTERNAL REFERENCE INPUT

To use an external reference, disconnect J3, J4, J13, and J14. Use a reference signal at J2 which complies with data sheet requirements. Then modify the reference frequency in the program main menu to

reflect the changes made (F menu item).

DATA TRANSFER FROM COMPUTER TO EVK

To control the serial input EVK with the parallel printer port, a conversion is done. Printer cards are designed to output eight bits through eight lines. A bit mask is used to obtain the bit combination for the

three required output lines (Data, Clock, Load). As bytes are sent to the printer card in sequence, it appears to be a serial transfer. The printer port is used because data transfer using the serial port would be

much slower. A standard IBM PC can support a parallel port data rate of 4.77 MHz.

IBM PCs and compatibles can accept up to three printer port configurations. These ports are called

LPT1, LPT2, and LPT3. Each printer port has a unique address. Two sets of addresses are in common

use. One set applies to IBM PC XT, AT, and clones. The other is for the PS 2 line. To load data into the

EVK, the correct address must be selected. The program default is $278. If $278 is not the address in

use, it must be modified by entering the P menu item in the main menu. All allowed addresses given in

hexadecimal are as follows:

Label

IBM PC and Clones PS 2

LPT1 278 3BC

LPT2 378 378

LPT3 3BC 278

Up to three EVK boards can operate independently from one printer port. All lines on the printer port are

connected to every EVK. Even with three boards operating, only three output lines (Clock, Data, and

Load) from the printer card are used. If two boards are controlled together, data for the second board is

received from the Output A of the first. Output A is a configurable output on ’220 devices, which in this

case is used to shift data through chip 1 into chip 2. Output A and Data are connected using a printer port

input line. This was done to avoid connecting extra wires. Fortunately not all port input lines are needed

for computer input. Load and Clock are common to both boards.

A three–board cascade is handled similarly to a two–board cascade. Out A on the first board is fed to

Data on the second. Out A on the second connects to Data on the third. Instructing the program on the

quantity of boards connected together allows it to modify the number of bits sent.

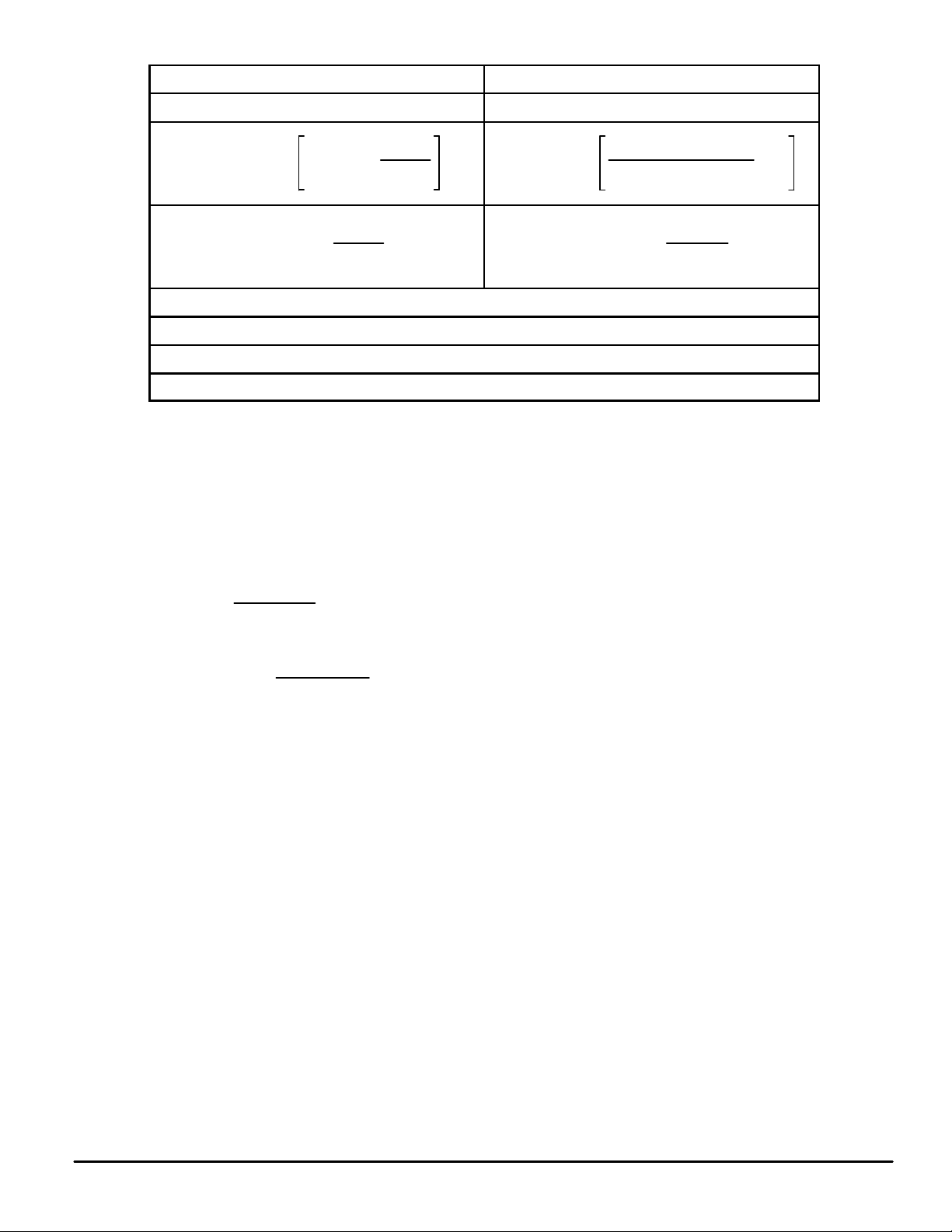

All boards have a DIP switch S1 which gives each a unique address. The configuration menu is used to

tell the program what type of board is connected at a board address. Switch positions for all possible

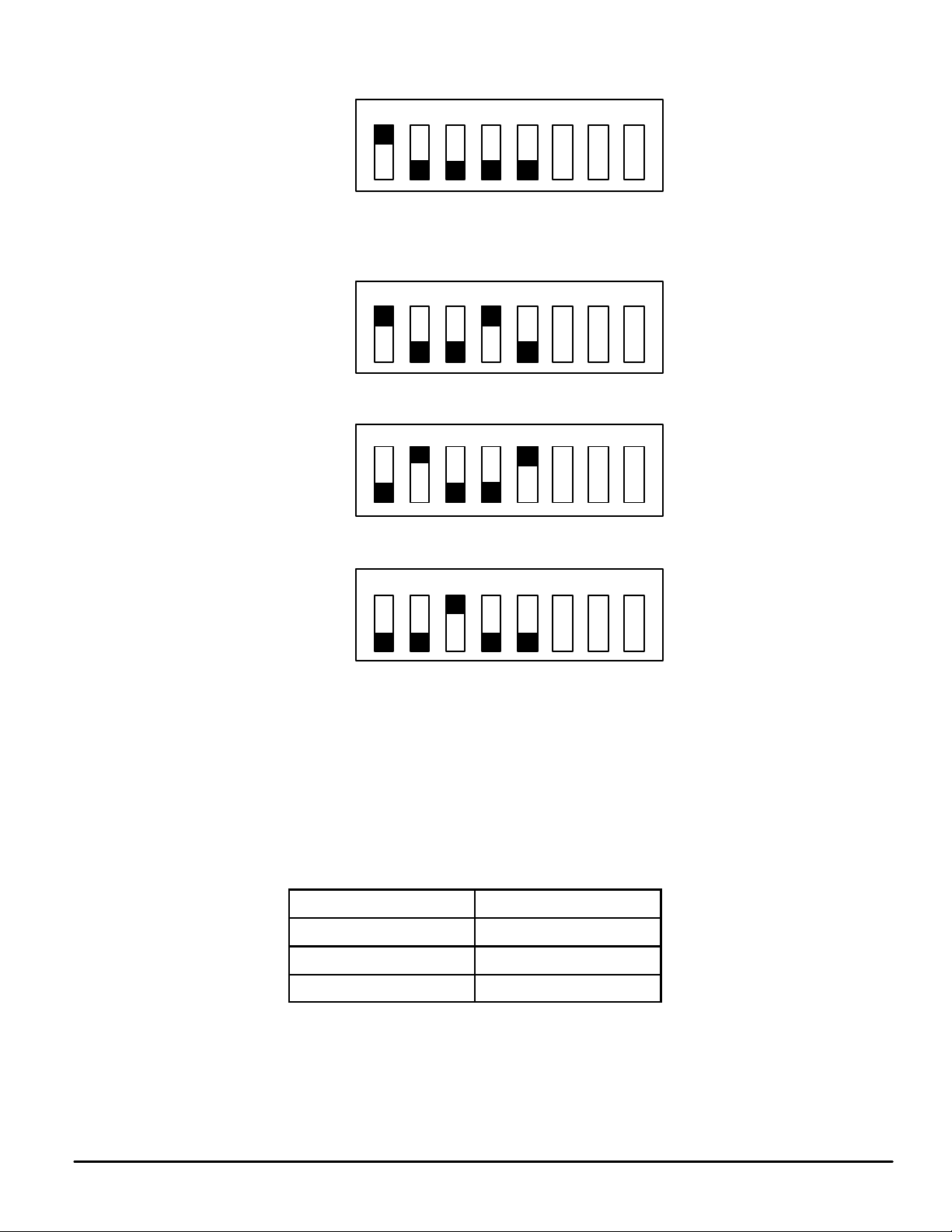

addresses are given in Figure 3.

MOTOROLA

MC145220EVK

11

Single Board Operation

Closed

Open

Closed

Open

Closed

Open

12345678

T wo– or Three–Board Cascade

Board A

12345678

Board B

12345678

Board C

12345678

Closed

Open

Figure 3. Switch Positions

In Figure 3, DIP switch sections 6, 7, and 8 allow the computer to read Out A, Lock Detect′, or Lock

Detect from the PLL device. Each of the inputs can only be read on one board at a time, but each item

could be read on a different board. In a three–board cascade, Out A could be read from the first board,

Out B from the second, and Lock Detect from the third. There is no way to determine the board address

of a particular input with software. The control program does not make use of these inputs; however,

source code could be modified as required. Pin assignment on the printer port connector is:

Label

Pin Number

Out A 12

Out B 13

Lock Detect 15

MC145220EVK

12

MOTOROLA

PRINTER PORT CONFIGURATION

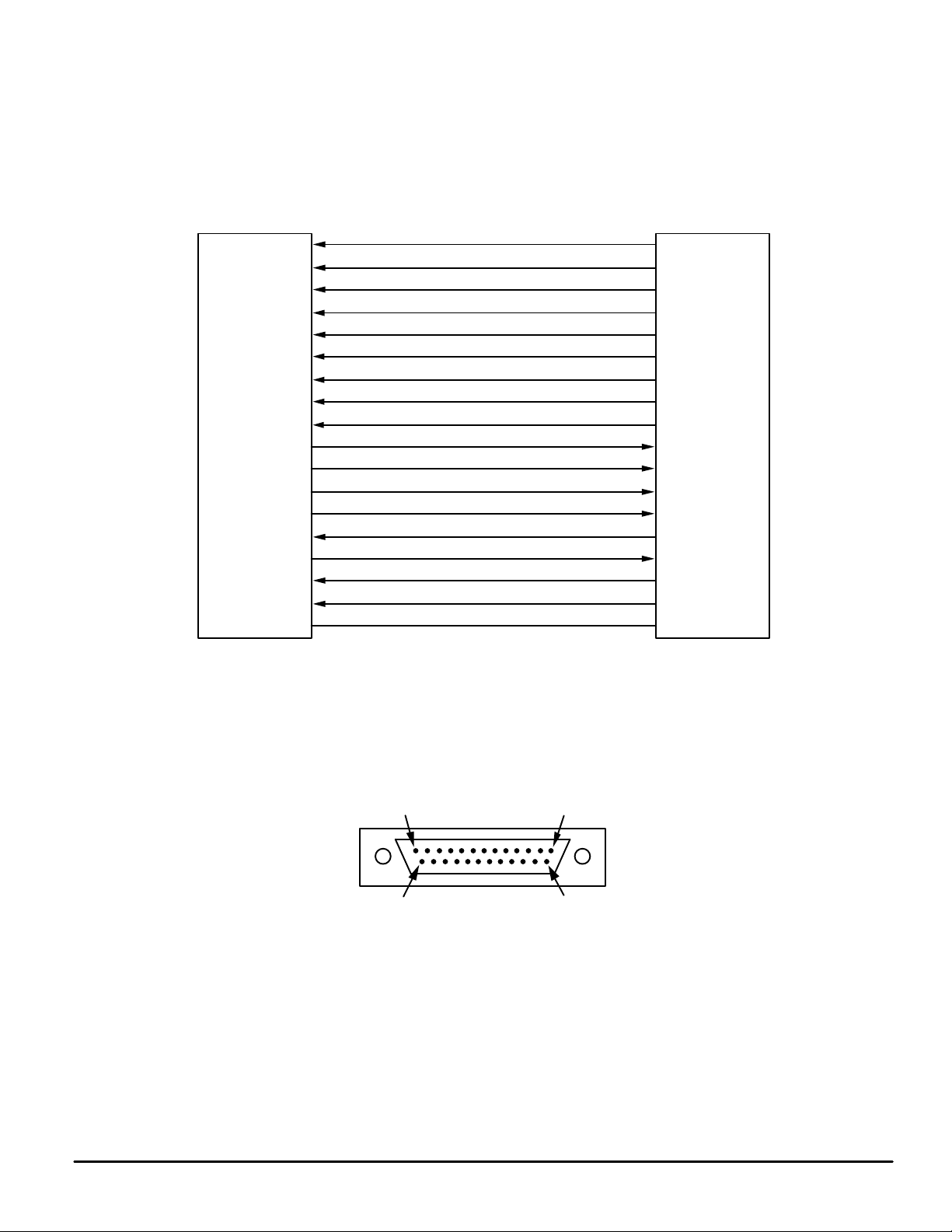

Printer port outputs on an IBM PC or clone use TTL–LS logic levels. Inputs are one TTL–LS load. Signal

lines can be used for any purpose. The standard names, direction of data flow, true and inverted data are

shown in Figure 4.

Printer

Signal Name

– Strobe

+ Data Bit 0

+ Data Bit 1

+ Data Bit 2

+ Data Bit 3

+ Data Bit 4

+ Data Bit 5

+ Data Bit 6

+ Data Bit 7

– Acknowledge

+ Busy

+ P. End (out of paper)

+ Select

– Auto Feed

– Error

– Initialize Printer

– Select Input

Ground

Pin Number

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18 – 25

IBM Printer

Port

Figure 4. Printer Port Data Lines

Pin numbers for the port connector are shown in Figure 5.

13

25

(front view)

Figure 5. DB–25 Male Connector

1

14

MOTOROLA

MC145220EVK

13

SECTION 2 – SOFTWARE DESCRIPTIONS

Á

Á

INTRODUCTION

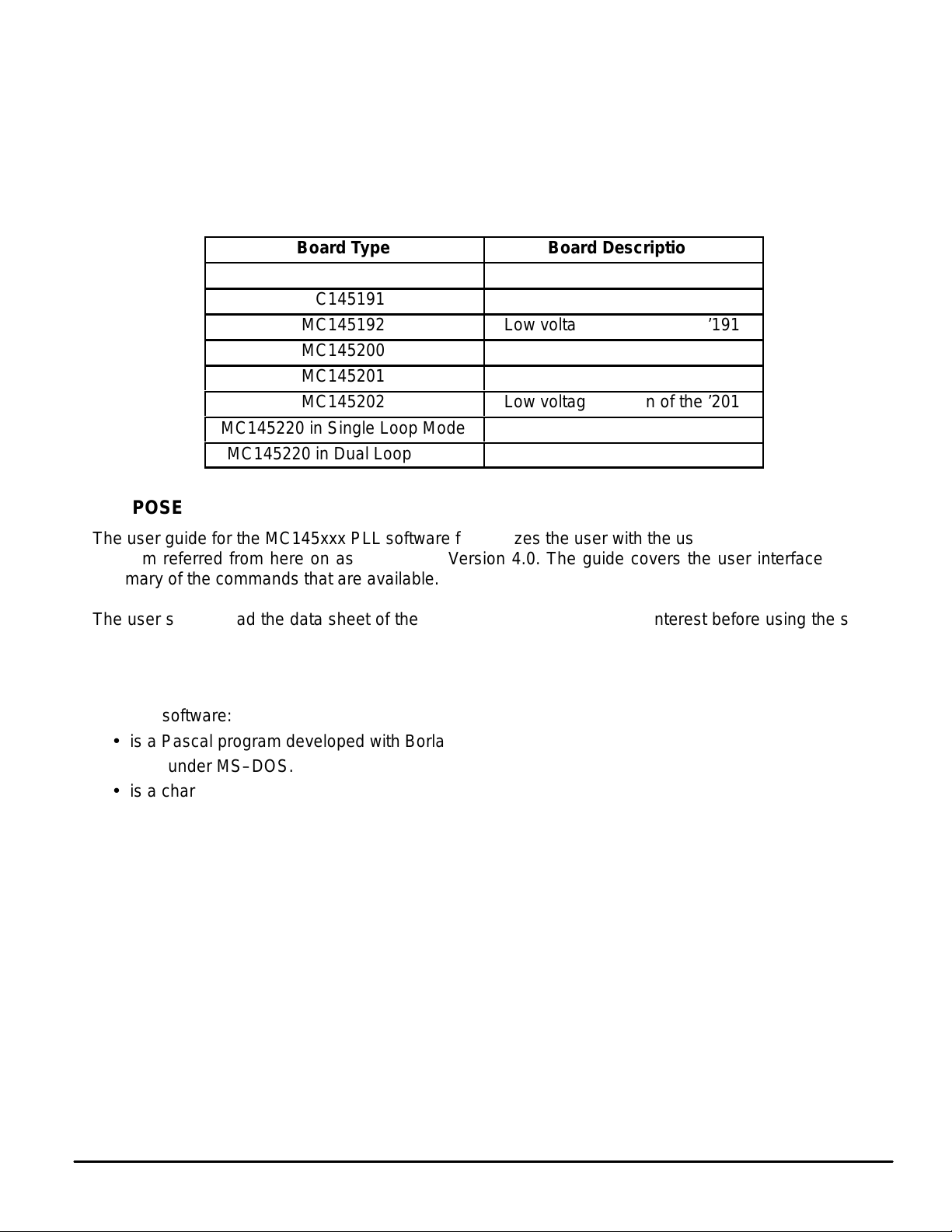

The MC145xxx PLL software is provided to demonstrate the capabilities of the MC145xxx family of PLLs.

The family includes the following devices:

Table 1.

PURPOSE

БББББББББББ

БББББББББББ

Board Type

MC145190

MC145191

MC145192

MC145200

MC145201

MC145202

MC145220 in Single Loop Mode

MC145220 in Dual Loop Mode

Board Description

ББББББББББ

ББББББББББ

Low voltage version of the ’191

Low voltage version of the ’201

The user guide for the MC145xxx PLL software familiarizes the user with the use and capabilities of the

program referred from here on as PLLDEMO Version 4.0. The guide covers the user interface and a

summary of the commands that are available.

The user should read the data sheet of the PLL frequency synthesizer of interest before using the software.

DESCRIPTION

The PLL software:

• is a Pascal program developed with Borland Turbo Pascal v7.0.

• runs under MS–DOS.

• is a character–based, menu–driven program.

USER INTERFACE

The user interface consists of numerous character–based, menu–driven screens which are displayed

below. Each screen is shown, along with a description of its purpose. Note that all screen shots shown

are a representative sample of the program. They are provided to familiarize the end user with the program.

INSTALL

To install this program, create a directory called “PLLEVAL”. Change directories into “PLLEVAL” and

copy PLL.exe into this directory.

MC145220EVK

14

MOTOROLA

UNINSTALL

To uninstall this program, change directories into “PLLEVAL” and type “erase*.*”. After this command,

change out of directory “PLLEVAL” and type “erase PLLEVAL”.

Note: If you are in Windows 3.X or Windows 95, this program adds no entries into .ini or Registry files.

It is recommended that you have the PLL program running while you are reviewing this manual. Due to

the number of screens that may be involved in your evaluation, following the connections, screens, and

commands is easier when the manual and program are used together.

CONVENTIONS

Some of the PLLDEMO screens are necessarily “busy”. Because of this, the program follows several

conventions to help the user quickly absorb the screen information. These conventions are briefly described on a help screen that is available throughout the program. Type the help command, [?], at any

time to view the help screen.

The conventions are as follows:

1. Command keys are surrounded by [ ]s. Type the letter between the [ ]s to execute the command.

[ ]s are followed by a description of the command.

2. [–] indicates a command not available to the user. Commands become available when they are

applicable to the currently targeted board.

3. [ ]s followed by an ! indicate the command will execute immediately. Otherwise a submenu is displayed from which further choices may be made.

4. If no changes are desired to an input field, leave the field blank. The previous value will then be used

for that field. Type the T AB key to move to the next input field, or shift–T AB to move to the prior input

field. Type RETURN to store the new input values while remaining on the same screen. Type Q to

store the new values and return to the prior screen.

5. All numbers are entered as decimal values unless otherwise noted. A $ followed by a value indicates

the value is in hexadecimal format. The output port address is in hexadecimal format.

6. The second line from the top of screen (screen title) states the purpose of the screen.

7. Screen information that can be changed by the user is displayed in bold or reverse video.

8. Commands are case independent. X is the same as x.

9. Frequencies are entered as two numbers, and displayed as one. The two input numbers represent

the desired frequency in MHz, and in kHz. These input values are added together to obtain the final

frequency. Leave either input field blank to retain the prior value for that portion of frequency.

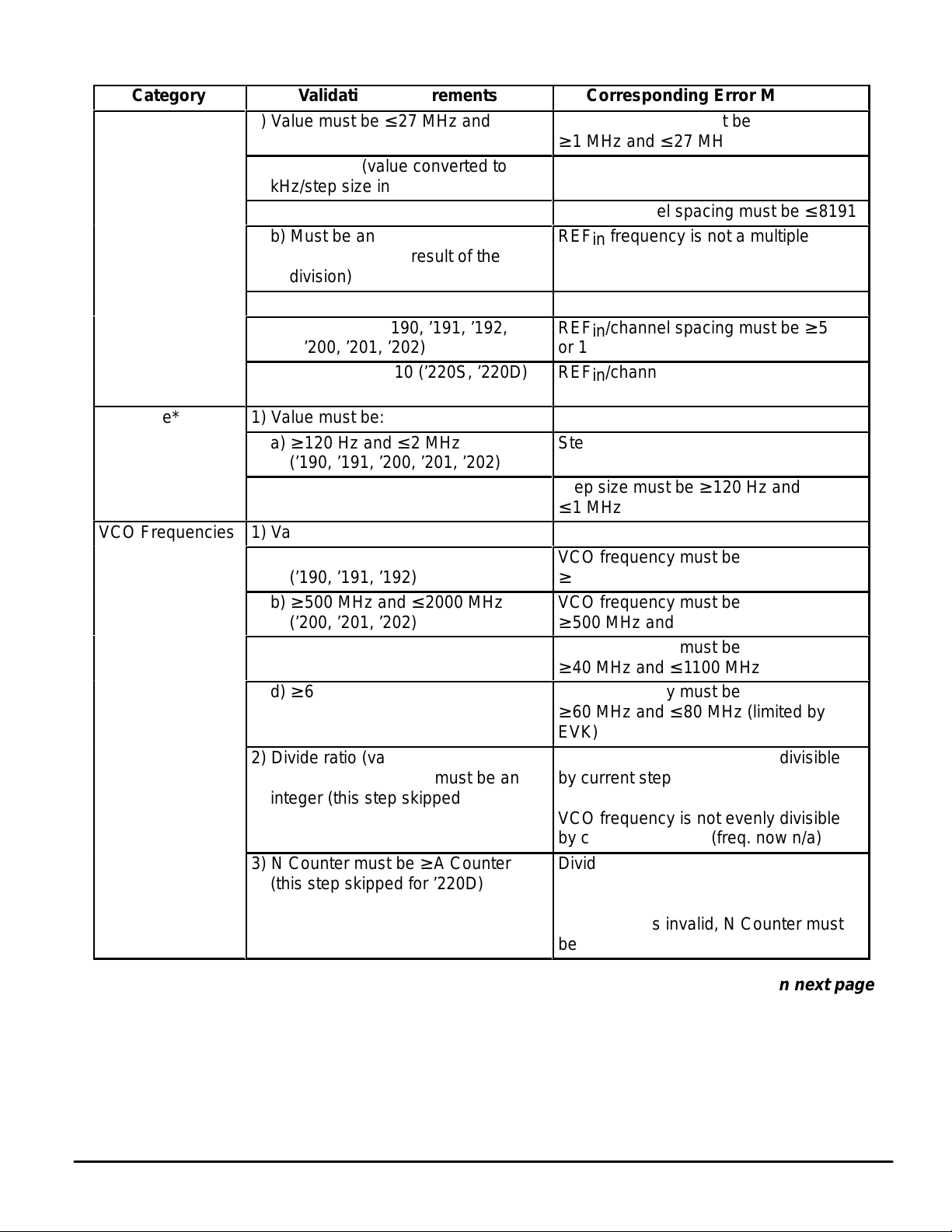

ALERT AND ERROR MESSAGES

This program contains two types of messages that appear when conditions warrant. (See Table 2.)

1. Alert Messages. These messages alert you that though the current values are valid, you are unable

to continuously increment the A and N counters. Hit any key to remove these messages and continue with the program. There are some instances of the alert messages where you may have to hit

any key twice to remove the message.

2. Error Messages. These are messages that indicate you have selected conditions that are outside

of the valid parameters of the IC. After hitting any key to continue, the invalid parameters you selected will change back to the default parameters of the program. Y ou may then enter another value

to continue your evaluation. There are some error messages where you may have to hit any key

twice to remove the message.

MOTOROLA

MC145220EVK

15

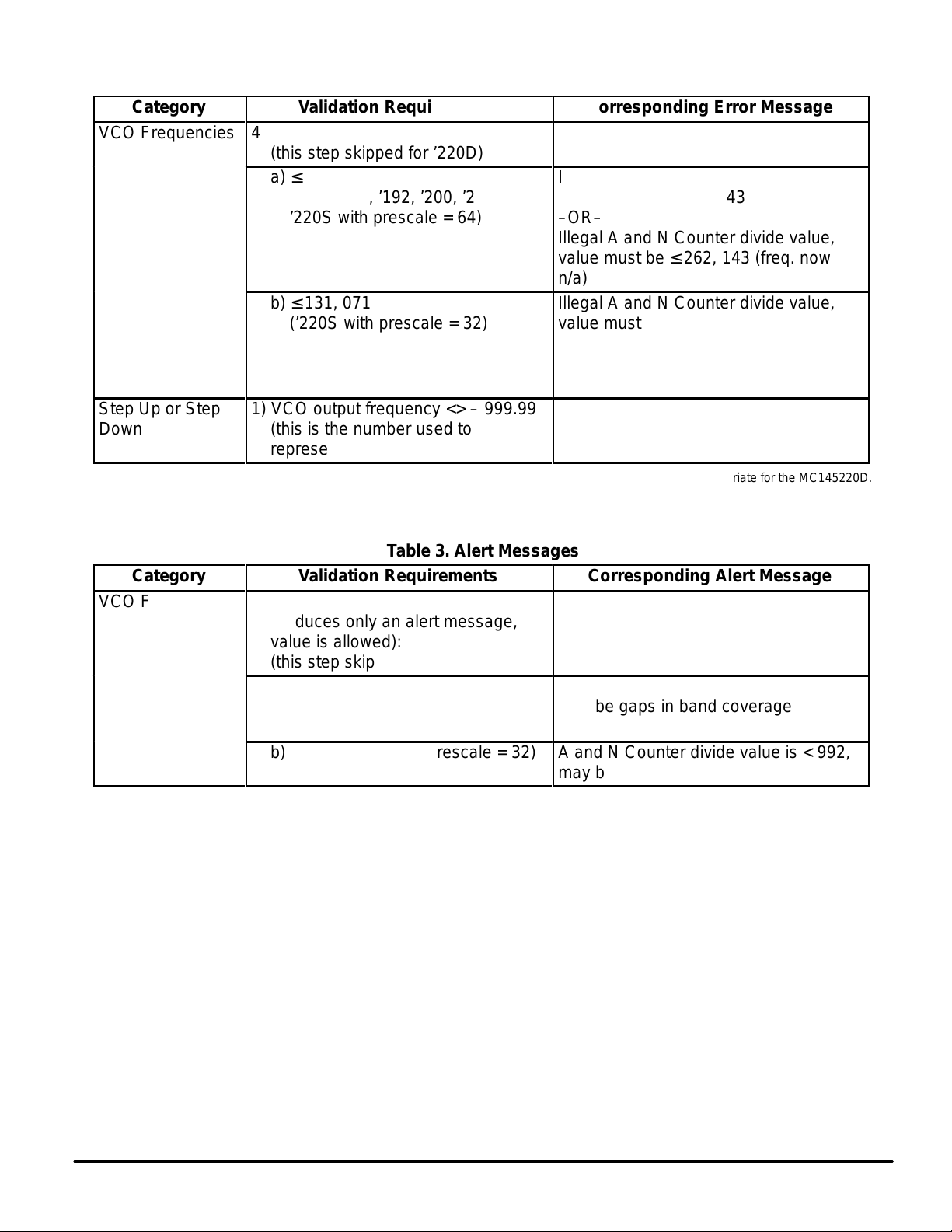

Table 2. Error Messages

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Category

REFin Frequency*

ББББББ

1) Value must be ≤ 27 MHz and

Validation Requirements

ББББББББББББ

≥ 1 MHz

2) Divide ratio (value converted to

ББББББÁББББББББББББ

kHz/step size in kHz):

a) Must be ≤ 8191

b) Must be an integer (there must

ББББББ

ББББББ

ББББББББББББ

be no fractional result of the

division)

ББББББББББББ

c) Must be in range:

i) = 1 or ≥ 5 (’190, ’191, ’192,

ББББББÁББББББББББББ

’200, ’201, ’202)

ii) = 1 or be ≥ 10 (’220S, ’220D)

ББББББÁББББББББББББ

Step Size*

ББББББ

1) Value must be:

ББББББББББББ

a) ≥ 120 Hz and ≤ 2 MHz

ББББББ

ББББББÁББББББББББББ

(’190, ’191, ’200, ’201, ’202)

ББББББББББББ

b) ≥ 120 Hz and ≤ 1 MHz

(’192, ’220S, ’220D)

VCO Frequencies

ББББББÁББББББББББББ

ББББББÁББББББББББББ

1) Value must be:

a) ≥ 100 MHz and ≤ 1100 MHz

(’190, ’191, ’192)

b) ≥ 500 MHz and ≤ 2000 MHz

(’200, ’201, ’202)

c) ≥ 40 MHz and ≤ 1100 MHz

ББББББÁББББББББББББ

(’220S)

d) ≥ 60 MHz and ≤ 80 MHz (’220D)

ББББББ

ББББББ

ББББББББББББ

ББББББББББББ

2) Divide ratio (value converted to

ББББББ

ББББББ

ББББББ

kHz/step size in kHz) must be an

ББББББББББББ

integer (this step skipped for ’220D)

ББББББББББББ

ББББББББББББ

3) N Counter must be ≥ A Counter

ББББББ

ББББББ

ББББББ

ББББББ

ББББББББББББ

(this step skipped for ’220D)

ББББББББББББ

ББББББББББББ

ББББББББББББ

Corresponding Error Message

REFin frequency must be

ББББББББББББ

≥ 1 MHz and ≤ 27 MHz

ББББББББББББ

REFin/channel spacing must be ≤ 8191

REFin frequency is not a multiple of the

ББББББББББББ

step size

ББББББББББББ

REFin/channel spacing must be ≥ 5

or 1

ББББББББББББ

REFin/channel spacing must be ≥ 10

or 1

ББББББББББББ

ББББББББББББ

Step size must be ≥ 120 Hz and

≤ 2 MHz

ББББББББББББ

Step size must be ≥ 120 Hz and

ББББББББББББ

≤ 1 MHz

VCO frequency must be

ББББББББББББ

≥ 100 MHz and ≤ 1100 MHz

VCO frequency must be

ББББББББББББ

≥ 500 MHz and ≤ 2000 MHz

VCO frequency must be

ББББББББББББ

≥ 40 MHz and ≤ 1100 MHz

VCO frequency must be

ББББББББББББ

≥ 60 MHz and ≤ 80 MHz (limited by

EVK)

ББББББББББББ

VCO frequency is not evenly divisible

by current step size

ББББББББББББ

–OR–

ББББББББББББ

VCO frequency is not evenly divisible

ББББББББББББ

by current step size (freq. now n/a)

Divide ratio is invalid, N Counter must

ББББББББББББ

be ≥ A Counter

ББББББББББББ

–OR–

Divide ratio is invalid, N Counter must

ББББББББББББ

be ≥ A Counter (freq. now n/a)

ББББББББББББ

MC145220EVK

16

Continued on next page

MOTOROLA

Continued from previous page

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Category

ББББББ

VCO Frequencies

ББББББ

ББББББ

ББББББ

ББББББ

ББББББ

ББББББ

ББББББ

ББББББ

ББББББ

Step Up or Step

ББББББ

Down

ББББББ

4) Divide ratio must be:

(this step skipped for ’220D)

a) ≤ 262,143

(’190, ’191, ’192, ’200, ’201, ’202,

’220S with prescale = 64)

b) ≤ 131, 071

(’220S with prescale = 32)

1) VCO output frequency <> – 999.99

(this is the number used to

represent n/a)

Validation Requirements

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

Corresponding Error Message

ББББББББББББ

ББББББББББББ

Illegal A and N Counter divide value,

ББББББББББББ

value must be ≤ 262,143

ББББББББББББ

–OR–

ББББББББББББ

Illegal A and N Counter divide value,

ББББББББББББ

value must be ≤ 262, 143 (freq. now

n/a)

ББББББББББББ

Illegal A and N Counter divide value,

value must be ≤ 131,071

ББББББББББББ

–OR–

ББББББББББББ

Illegal A and N Counter divide value,

ББББББББББББ

value must be ≤ 131.071 (freq. now n/a)

VCO frequency is invalid

ББББББББББББ

ББББББББББББ

*NOTE: REFin and step size are NOT validated on the ’220D board. These validation sequences may not be appropriate for the MC145220D.

Table 3. Alert Messages

Category

VCO Frequencies

ББББББ

ББББББ

ББББББ

ББББББ

ББББББ

ББББББ

ББББББ

1) Divide ratio must be (violation

produces only an alert message,

value is allowed):

(this step skipped for ’220D)

a) ≥ 4032

(’190, ’191, ’192, ’200, ’201,

’220S with prescale = 64)

b) ≥ 992 (’220S with prescale = 32)

Validation Requirements

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

ББББББББББББ

Corresponding Alert Message

ББББББББББББ

ББББББББББББ

ББББББББББББ

A and N Counter divide value is < 4032,

may be gaps in band coverage

ББББББББББББ

ББББББББББББ

A and N Counter divide value is < 992,

ББББББББББББ

may be gaps in band coverage

ББББББББББББ

MOTOROLA

MC145220EVK

17

Loading...

Loading...