Motorola MC10H351FN, MC10H351L, MC10H351P Datasheet

SEMICONDUCTOR TECHNICAL DATA

2–77

REV 5

Motorola, Inc. 1996

3/93

The MC10H351 is a quad translator for interfacing data between a

saturated logic section and the PECL section of digital systems when only

a +5.0 Vdc power supply is available. The MC10H351 has TTL/NMOS

compatible inputs and PECL complementary open–emitter outputs that

allow use as an inverting/non–inverting translator or as a differential line

driver. When the common strobe input is at a low logic level, it forces all

true outputs to the PECL low logic state (≈ +3.2 V) and all inverting

outputs to the PECL high logic state (≈ +4.1 V).

The MC10H351 can also be used with the MC10H350 to transmit and

receive TTL/NMOS information differentially via balanced twisted pair

lines.

• Single +5.0 Power Supply

• All VCC Pins Isolated On Chip

• Differentially Drive Balanced Lines

• tpd = 1.3 nsec Typical

MAXIMUM RATINGS

Characteristic Symbol Rating Unit

Power Supply V

CC

0 to +7.0 Vdc

Input Voltage (VCC = 5.0 V) V

I

0 to V

CC

Vdc

Output Current— Continuous

— Surge

I

out

50

100

mA

Operating Temperature Range T

A

0 to +75 °C

Storage Temperature Range— Plastic

— Ceramic

T

stg

–55 to +150

–55 to +165

°C

ELECTRICAL CHARACTERISTICS (VCC = V

CC1

= V

CC2

= 5.0 V ± 5.0%)

0° 25° 75°

Characteristic Symbol Min Max Min Max Min Max Unit

Power Supply

ECL — 50 — 45 — 50 mA

pp y

Current

TTL — 20 — 15 — 20 mA

Reverse Current

Pins 7, 8, 12, 14

Pin 9

I

R

I

INH

——25

100——2080——25100

µA

Forward Current

Pins 7, 8, 12, 14

Pin 9

I

F

I

INL

——–0.8

–3.2——

–0.6

–2.4——

–0.8

–3.2

mA

Input Breakdown

Voltage

V

(BR)in

5.5 — 5.5 — 5.5 — Vdc

Input Clamp Voltage

(Iin = –18 mA)

V

I

— –1.5 — –1.5 — –1.5 Vdc

High Output

Voltage (1)

V

OH

3.98 4.16 4.02 4.19 4.08 4.27 Vdc

Low Output

Voltage (1)

V

OL

3.05 3.37 3.05 3.37 3.05 3.37 Vdc

High Input Voltage V

IH

2.0 — 2.0 — 2.0 — Vdc

Low Input Voltage V

IL

— 0.8 — 0.8 — 0.8 Vdc

(1) With VCC at 5.0 V. VOH/VOL change 1:1 with VCC.

*Positive Emitter Coupled Logic

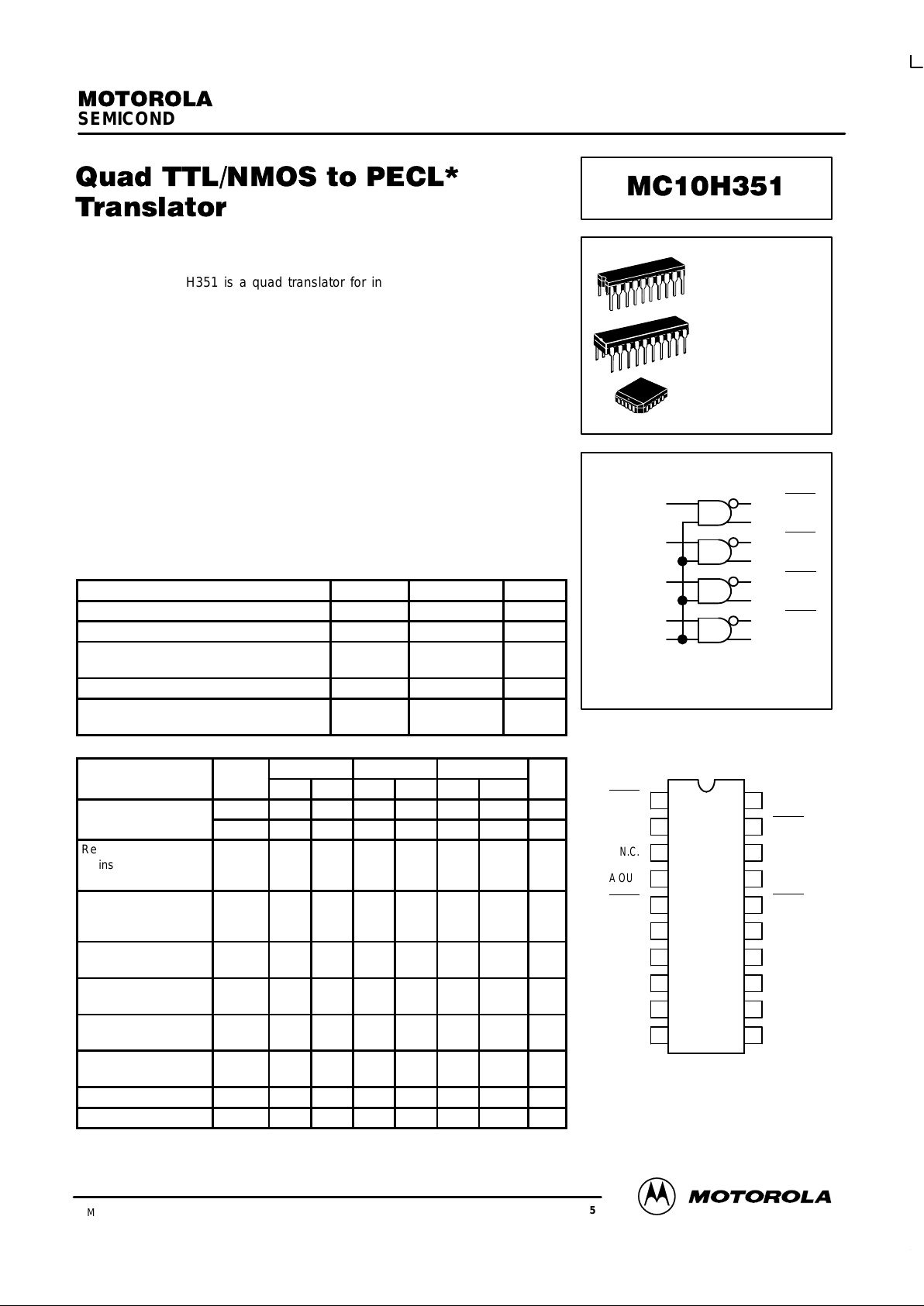

LOGIC DIAGRAM

DIP

PIN ASSIGNMENT

B OUT

B OUT

N.C.

A OUT

A OUT

V

CC

B IN

A IN

ECL V

CC

C OUT

C OUT

D OUT

D OUT

VCC 2

C IN

N.C.

20

19

18

17

16

15

14

13

1

2

3

4

5

6

7

8

COMMON

STROBE

GND

D IN

TTL V

CC

12

11

9

10

14

19

18

12

16

17

8

5

4

71

2

9

B IN

A IN

COMMON

STROBE

D IN

C IN

B OUT

B OUT

A OUT

A OUT

D OUT

D OUT

C OUT

C OUT

VCC (+5.0 VDC) = PINS 6, 11, 15, 20

GND = PIN 10

L SUFFIX

CERAMIC PACKAGE

CASE 732–03

P SUFFIX

PLASTIC PACKAGE

CASE 738–03

FN SUFFIX

PLCC

CASE 775–02

Pin assignment is for Dual–in–Line Package.

For PLCC pin assignment, see the Pin Conversion

T ables on page 6–36 of the Motorola MECL Data

Book (DL122/D).

MC10H351

MOTOROLA MECL Data

DL122 — Rev 6

2–78

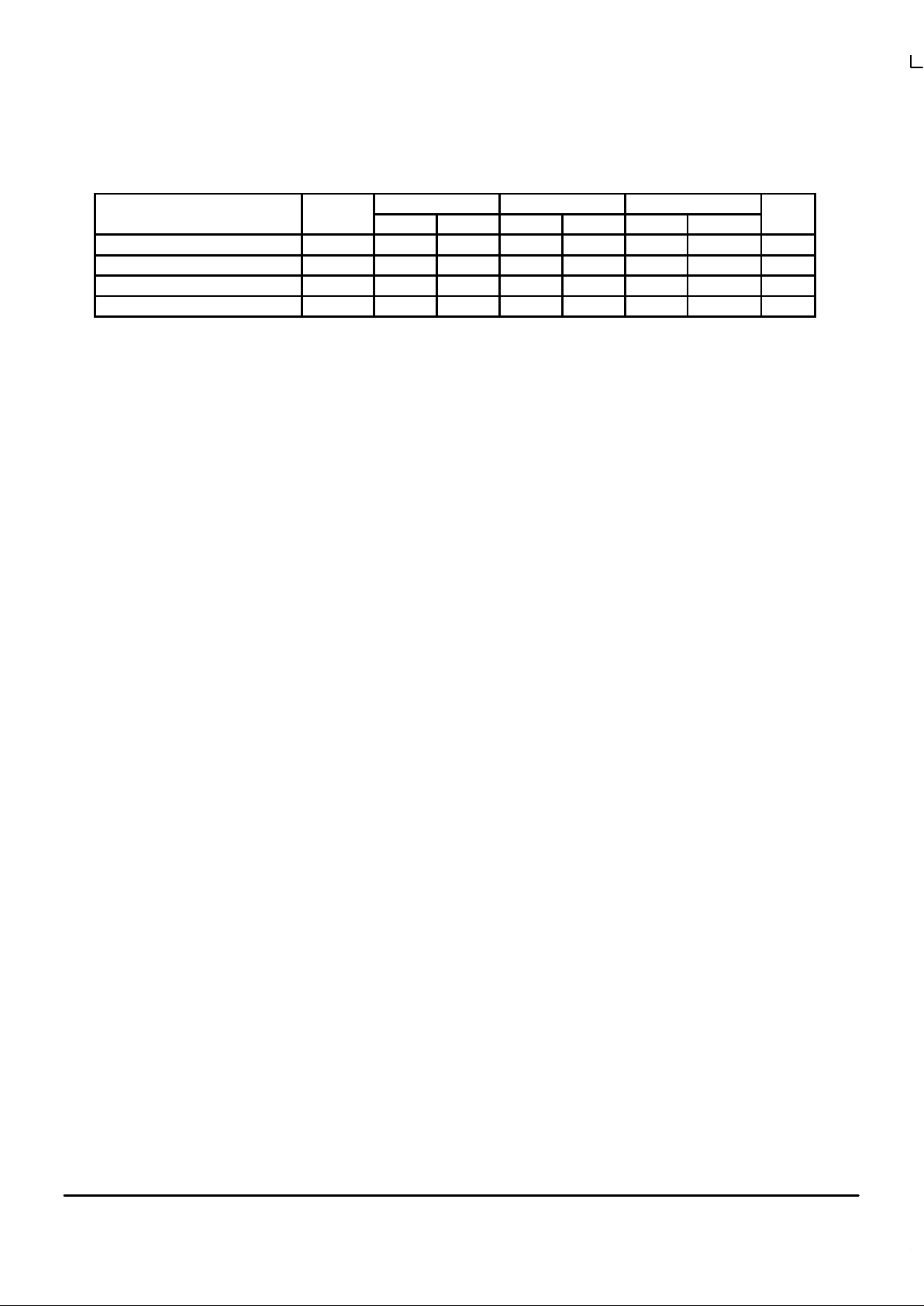

AC PARAMETERS

0° 25° 75°

Characteristic Symbol Min Max Min Max Min Max Unit

Propagation Delay (1) t

pd

0.4 2.2 0.4 2.2 0.4 2.1 ns

Rise Time (20% to 80%) t

r

0.4 1.9 0.4 2.0 0.4 2.1 ns

Fall Time (80% to 20%) t

f

0.4 1.9 0.4 2.0 0.4 2.1 ns

Maximum Operating Frequency f

max

150 — 150 — 150 — MHz

(1) Propagation delay is measured on this circuit from +1.5 volts on the input waveform to the 50% point on the output waveform.

NOTE:

Each MECL 10H series circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The

circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 lfpm is maintained. Outputs are terminated through

a 50–ohm resistor to VCC –2.0 Vdc.

Loading...

Loading...