Page 1

查询M38C80E1-XXXFP供应商查询M38C80E1-XXXFP供应商

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

DESCRIPTION

The 38C8 group is the 8-bit microcomputer based on the 740 family

core technology.

The 38C8 group has a LCD drive control circuit (bias control, time

sharing control), a 10-bit A-D converter, and a Serial I/O as additional

functions.

The various microcomputers in the 38C8 group include variations of

internal memory size and packaging. For details, refer to the section

on part numbering.

FEATURES

●Basic machine-language instructions ....................................... 71

●The minimum instruction execution time ............................ 0.5 µs

(at 8 MHz oscillation frequency)

●Memory size

ROM ............................................................................ 60 K bytes

RAM ............................................................................ 2048 bytes

●Programmable input/output ports ............................................. 35

●Software pull-up resistors

.................................................................. Ports P0–P3, P41–P47

●Interrupts ...................................................15 sources, 15 vectors

(includes key input interrupt)

●Timers ............................................................8-bit ✕ 3, 16-bit ✕ 2

●Serial I/O ........................8-bit ✕ 1 (UART or Clock-synchronized)

●A-D converter (32 kHz operating available) ... 10-bit ✕ 8 channels

●LCD drive control circuit

Bias ................................................................................... 1/5, 1/7

Duty .............................................................................. 1/16, 1/32

Common output ............................................................... 16 or 32

Segment output ............................................................... 52 or 68

●Main clock generating circuit (RC oscillation selectable)

...................... (connect to external ceramic resonator or resistor)

●Sub-clock generating circuit

............................................. (connect to quartz-crystal oscilaltor)

●Power source voltage

In high-speed mode .................................................... 4.0 to 5.5 V

In middle-speed mode ................................................2.2 to 5.5 V

In low-speed mode ..................................................... 2.2 to 5.5 V

●Power dissipation

In high-speed mode ........................................................... 30 mW

(at 8 MHz oscillation frequency, at 5 V power source voltage)

In low-speed mode .............................................................60 µW

(at 32 kHz oscillation frequency, at 3 V power source voltage, at

WIT state, at voltage multiplier operating, LCD drive waveform

generating state)

●Operating temperature range ................................... – 20 to 85°C

APPLICATIONS

Dot-matrix-type displays

Page 2

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to

change.

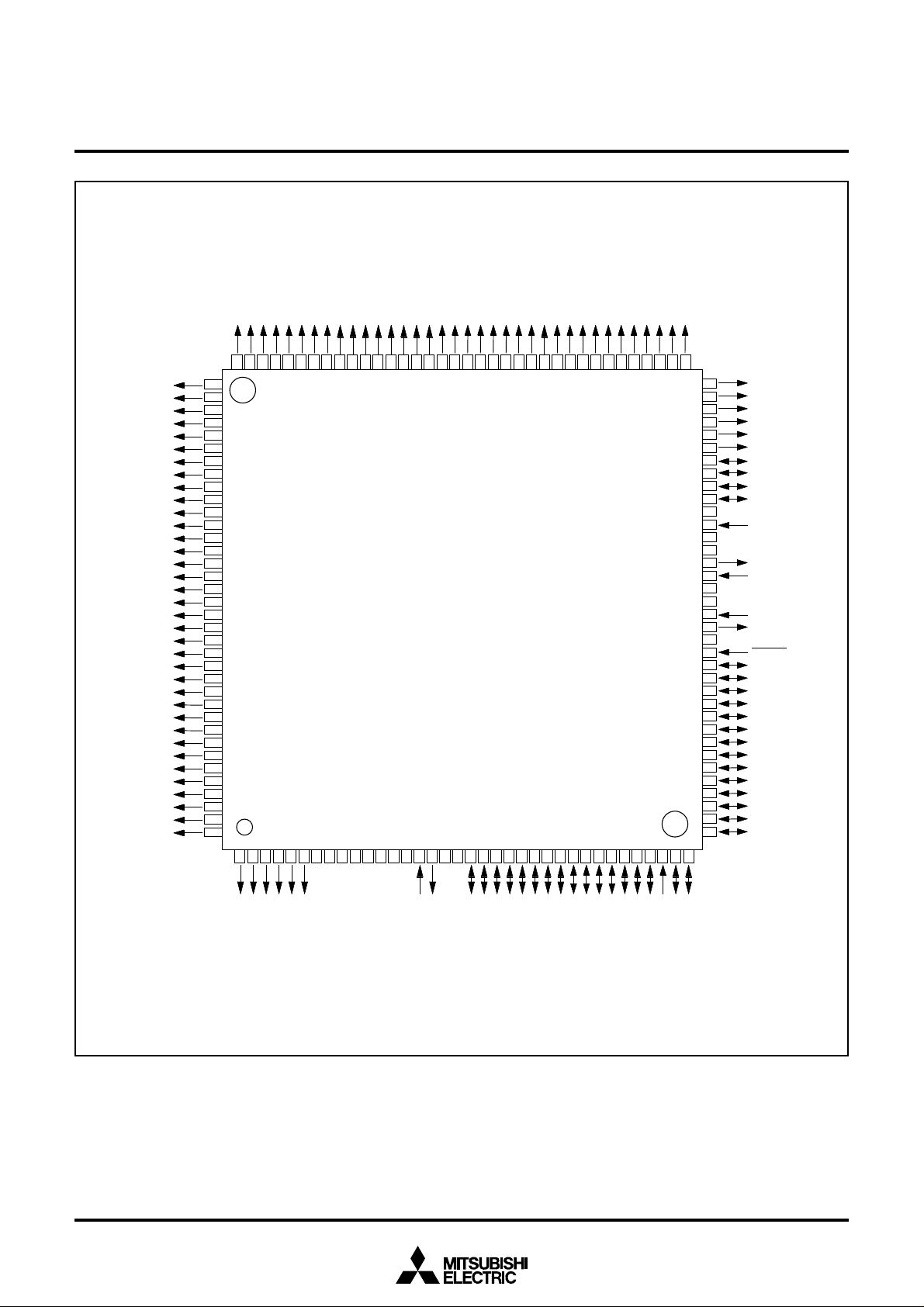

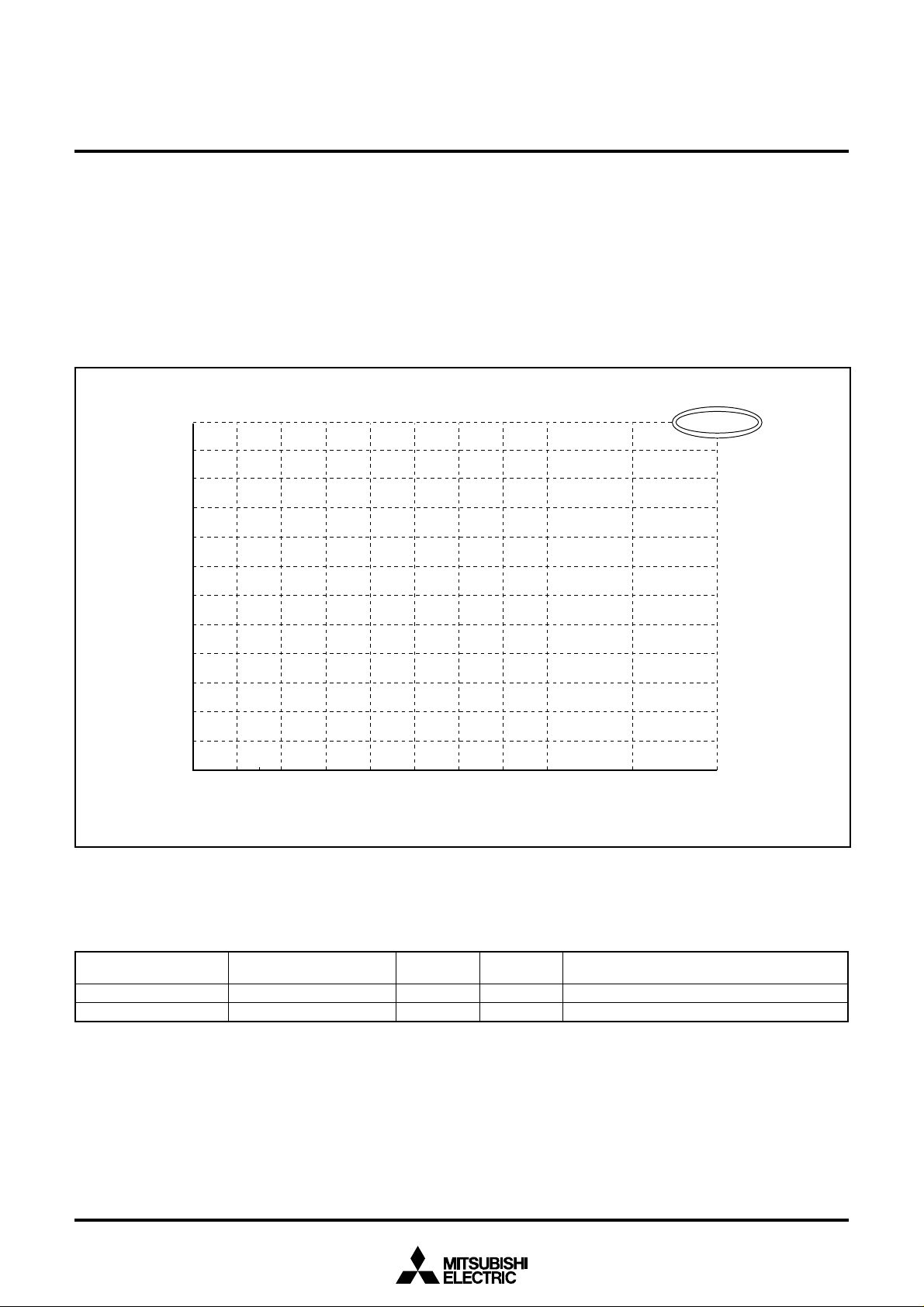

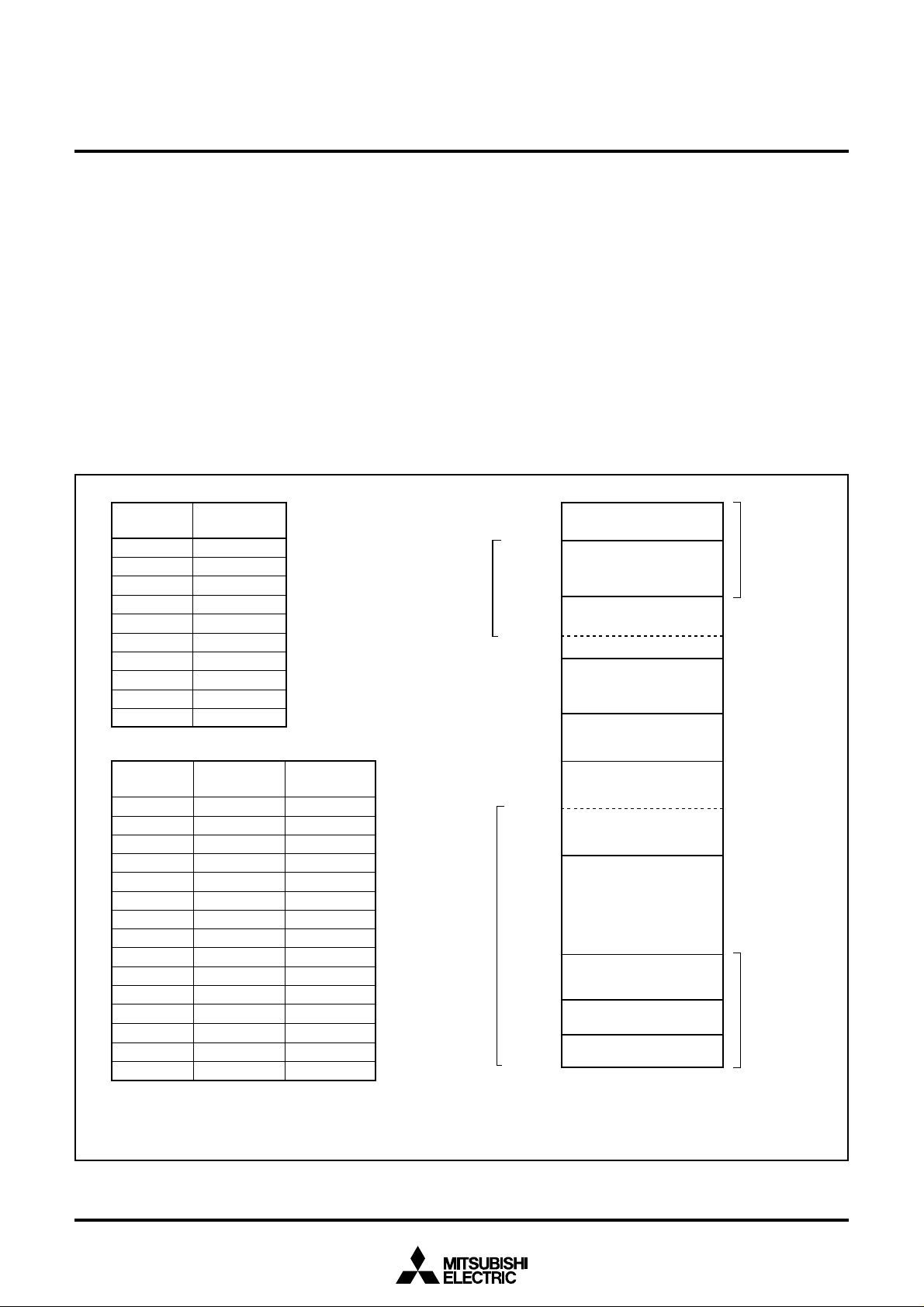

PIN CONFIGURATION (TOP VIEW)

5

6

7

9

0

1

G3

S

E

0 61

G3

S

E

0 51

G3

S

E

0 41

8

G3

E

S

0 31

2

G3

G4

G4

G4

S

S

E

S

E

S

E

1

2

0

1

0

0

1

0

S E G3

S E G3

S E G3

S E G3

S E G2

S E G2

S E G2

S E G2

S E G2

S E G2

S E G2

S E G2

S E G2

S E G2

S E G1

S E G1

S E G1

S E G1

S E G1

S E G1

S E G1

S E G1

S E G1

S E G1

S E G9

S E G8

S E G7/ C O M2

S E G6/ C O M2

S E G5/ C O M2

S E G4/ C O M2

S E G3/ C O M1

S E G2/ C O M1

S E G1/ C O M1

SEG0/COM16

COM7

COM6

4

G3

E

S

E

1

0 81

0 71

1 0 9

3

1 1 0

2

1 1 1

1

1 1 2

0

1 1 3

9

1 1 4

8

1 1 5

7

116

6

117

5

118

4

119

3

120

2

121

1

122

0

123

9

1 2 4

8

1 2 5

7

1 2 6

6

1 2 7

5

128

4

129

3

130

2

131

1

132

0

133

134

135

3

1 3 6

2

1 3 7

1

1 3 8

0

1 3 9

9

1 4 0

8

1 4 1

7

1 4 2

1 4 3

1 4 4

123456789

0

1

2

3

G4

S

E

9

99

4

G4

S

E

89

5

G4

S

E

79

6

G4

S

E

69

7

G4

S

E

59

8

G4

S

E

49

9

G4

S

E

39

E

29

G5

S

E

19

G5

S

E

08

G5

S

E

98

3

G5

E

S

88

M 3 8 C 8 9 M F - X X X F P

1

01

11

21

31

41

51

61

71

81

92

02

12

4

G5

S

E

78

22

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

1

0

8

9

7

6

5

M2

4/

G6

S

E

C O

77

13

23

M2

5/

G6

S

E

C O

67

33

M2

6/

G6

E

S

C O

57

43

4

M2

7/

6

G

S

O

47

53

5

4

M1

M1

C

C

O

3

6

7 2

C O M1

7 1

C O M1

7 0

C O M1

6 9

C O M1

6 8

C O M9

6 7

C O M8

N

6 6

P 30/ AI

6 5

P31/AIN1

6 4

P32/AIN2

N

6 3

P 33/ AI

NC

6 2

XIN

6 1

6 0

5 9

5 8

5 7

5 6

55

54

5 3

5 2

5 1

5 0

4 9

4 8

4 7

4 6

4 5

4 4

4 3

4 2

4 1

4 0

3 9

3 8

3 7

N C

VSS

XOUT

OSCSEL

VC

C

NC

XCIN

O U

XC

NC

R E S E T

P10/AIN4

P11/AIN5

P12/AIN6

N

P 13/ AI

P14

P 15

P 16

P 17

P 00

P01

P 02

P 03

P04

P05

5

G5

S

E

68

32

6

G5

S

E

58

42

7

G5

S

E

48

52

8

G5

E

S

38

62

9

G5

S

E

C O

28

72

M3

0/

G6

S

E

C O

18

82

M3

1/

G6

S

E

C O

07

93

M2

2/

G6

E

S

C O

97

03

M2

3/

G6

S

E

C O

87

3

2

1

0

0

3

T

7

C

O M5C

O

M4

O M3C

C

O

C

O M0C

O

M1

M2

Fig. 1 M38C89MF-XXXFP pin configuration

2

1

VL

L

C3C2C1

VL

VL

VL

V

5

4

3

2

)

N

S

C

N

27P

VS

I

VL

S

( N C

VS

Package type : 144P6Q-A

26

P

25P

24P

23P

22

P

21P

K

Y

20P

SR

47/

L

P

D

-

TXD

RXD

SC

45/

44/

46/

P

P

P

R1/

43/

B E E P

B E E P

C N T

C N T

P

7

+

T

0

06

T0

P

P

40/

T1/

P

I N

R0/

41/

A D

I N

P

42/

P

Page 3

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to

change.

1

0

M

M

C

O

O

C

O

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

7

6

5

1

0

9

0

1

2

6

7

8

1

1

1

M

M

M

/

/

4

5

2

3

M

M

M

M

C

O

C

O

O

C

C

O

1

25436

4 41

/

6

7

0

1

2

M

M

G

G

G

E

S

E

S

E

S

E

C

C

O

C O

C O

C O

C O

0

2

1

4 11

4

1

4 31

4

3

1

2

2

2

2

M

M

M

M

M

/

/

/

/

/

0

1

3

4

5

6

7

G

G

G

G

G

S

S

E

S

E

S

E

S

E

E

C O

C O

C O

C O

9

1

3 81

3 71

3 61

3 51

1

3

3 41

8

G

S

E

3 31

9

G

S

E

3 21

1

G

S

E

3 11

2

1

1

G

G

S

S

E

0

3

7

6

5

5

5

5

G

G

G

E

S

E

S

E

S

E

4

4

4

8

8

8

9

3

3

2

M

M

M

/

/

/

0

1

2

8

9

6

6

6

5

5

G

G

G

G

G

C O

C O

C O

C O

S

E

S

E

S

E

E

S

S

E

4

1

8

28

38

98

08

r

D

L

c

C

o n t r o l l e

4

8

2

2

2

2

2

M

M

M

M

M

/

/

/

/

/

3

6

G

C O

E

S

87

5

4

3

2

1

4

5

6

7

1

6

6

6

6

M

G

G

G

G

C

O

O

C O

C O

C O

S

S

E

S

E

S

E

37

47

57

67

77

0

1

M

C

O

27

9

1

1

1

1

8

M

M

M

M

M

M

C

O

C

C

O

C

O

C

O

C

O

7

6

6

86

97

07

17

5

V

L

4

V

L

3

9 8 7

V

L

2

0

1

V

L

1

1

1

V

L

21

3

1

C

31

2

C

1

41

C

N

5

I

L

V

S

8

1

VS

S

s

9

5

VS

D

a t a b u

C

6

C

V

t

T

15

5

R

E S E

R

e s e t i n p u

t

T

3

5

O U

XC

S

u b - c l o c k o

u t p u

t

N

4

5

I

XC

S

u b - c l o c k i

n p u

T

t

8

5

O

U

X

C

l o c k o

u t p u

t

N

1

6

XI

C

l o c k i

n p u

)

M

R

A

(

L

C D R A M

1 7 6 b y t e

)

T

i m e r X ( 1 6

r

M

T

i m e

)

T

i m e r Y ( 1 6

)

i m e r 2 ( 8 )T

i m e r 3 ( 8

)T

T

i m e r 1 ( 8

1

C N T R0, C N T R

R

O

L

C

A

X

Y

S

S

P

P

U

C

P

t

H

C

P

)

A

- D c o n v e r t e r ( 1 0

φ

)

C

l o c k g e n e r a t i n g c i r c u i

S

e r i a l I / O ( 8

K e y - o n w a k e - u p

6

52

2

2

4

)

P

2 ( 8

)

P

1 ( 8

)

P

0 ( 8

)

P

3 ( 4

)

P

4 ( 7

1

32

26

12

I

/ O p o r t P

02

2

9

1

0

95

1

8

74

64

54

I

/ O p o r t P

44

4

3

4

2

14

4

0

04

94

83

3

7

3

I

/ O p o r t P

6

3

5

3

3

6

6

5

6

4 2

36

I

/ O p o r t P

7

2

8

2

4

9

2

0

13

23

3

I

/ O p o r t P

3

3

4

3

I N T0, I N T

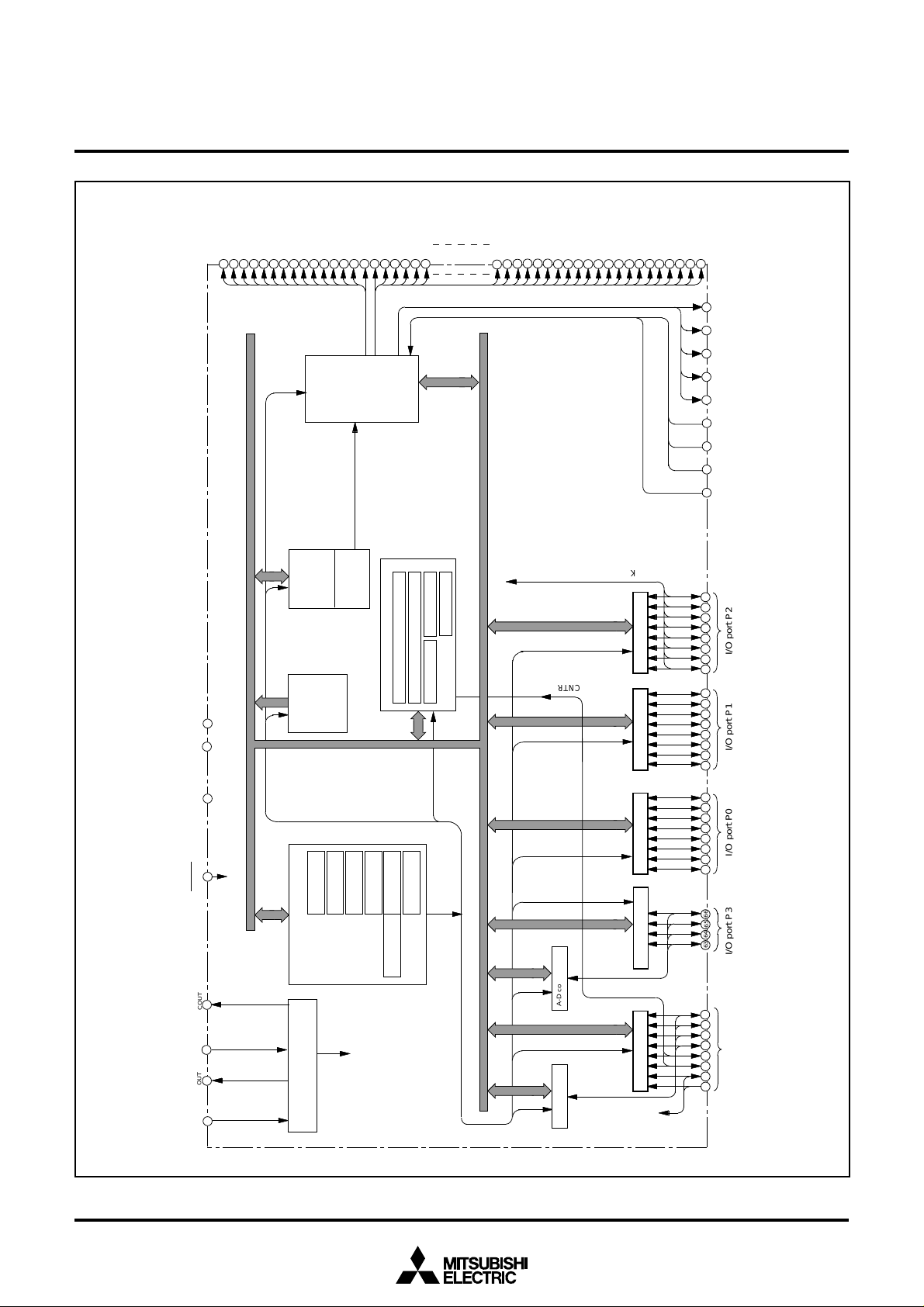

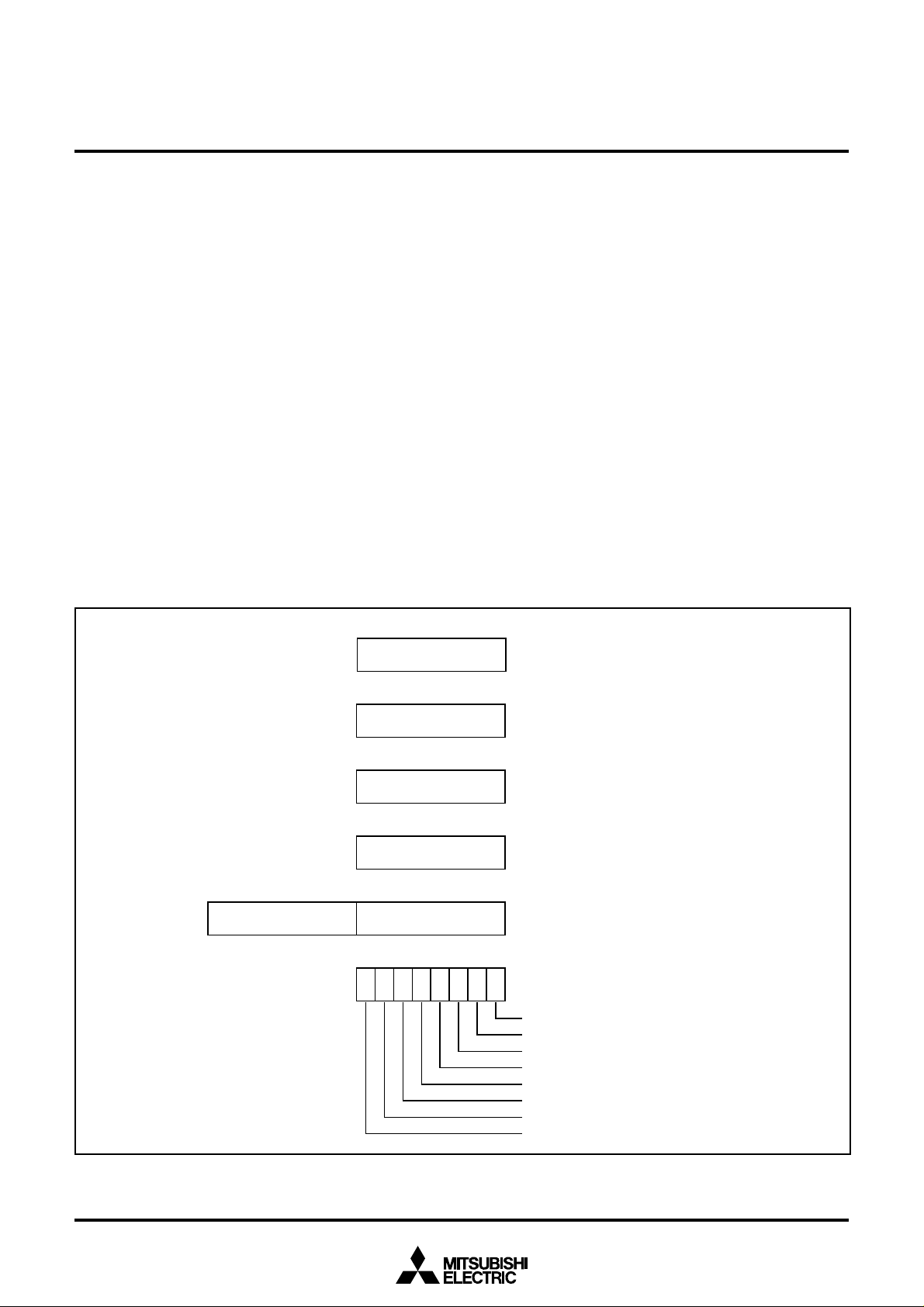

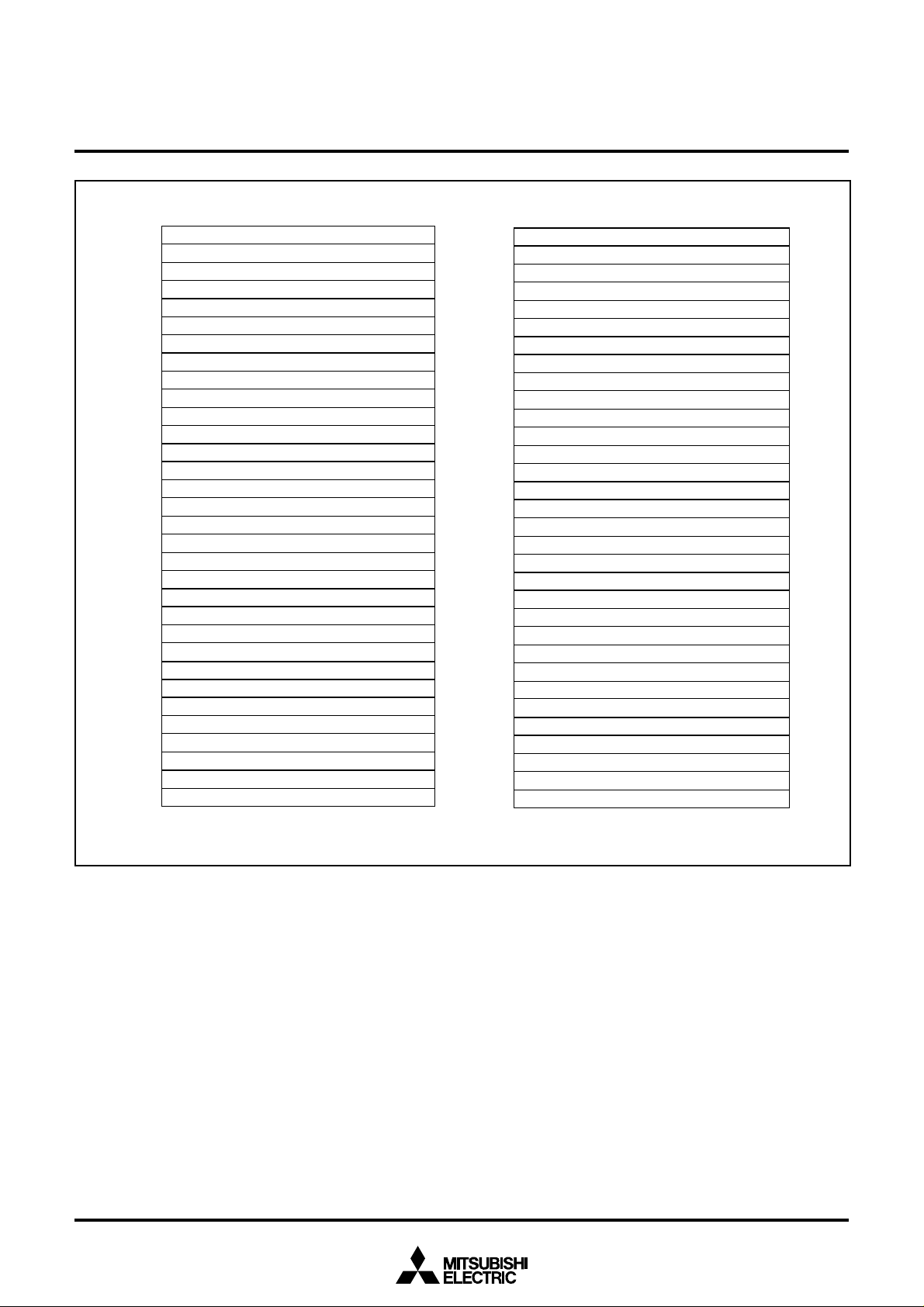

FUNCTIONAL BLOCK DIAGRAM (Package: 144P6Q-A)

Fig. 2 Functional block diagram

3

Page 4

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to

change.

PIN DESCRIPTION

Table 1 Pin description

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Pin

VCC, VSS

RESET

XIN

XOUT

OSCSEL

XCIN

XCOUT

VLIN

VL1 – VL5

COM0 –

COM32

SEG0/COM16–

SEG7/COM23,

SEG60COM31–

SEG67/COM

SEG8–SEG59

P00–P07

P14–P17

P10/AIN4–

P13/AIN7

P20–P27

P30/AIN0 –

P33/AIN3

P40/INT0

P41/INT1/ADT

P42/CNTR0/

BEEP+,

P43/CNTR1/

BEEP-

P44/RxD,

P45/TxD,

P46/SCLK,

P47/SRDY

C1,

C2,

C3

VSS (NC), NC

24

Name

Power source

Reset input

Clock input

Clock output

RC oscillation

select

Sub-clock input

Sub-clock output

Power source

input for LCD

LCD power

source

Common output

Segment output/

Common output

Segment output

I/O port P0

I/O port P1

I/O port P2

I/O port P3

Input port P4

I/O port P4

Voltage multiplier

Function

• Apply voltage of 4.0–5.5 V to VCC, and 0 V to VSS. (at high-speed mode)

• Reset input pin for active “L.”

• Input and output pins for the main clock generating circuit.

• Feedback resistor is built in between XIN pin and XOUT pin.

• Connect a ceramic resonator or a quartz-crystal oscillator between the XIN and XOUT pins to set the

oscillation frequency.

• If an external clock is used, connect the clock source to the XIN pin and leave the XOUT pin open.

• This pin determines the oscillation between XIN and XOUT. The oscillation method can be selected from

either by an oscillator or by a resistor.

• Input and output pins for sub-clock generating circuit. (Connect a quartz-crystal oscillator between the

XCIN and XCOUT pins to set the oscillation frequency . The clock generated the externals cannot be input

directly.)

• Reference voltage input pin for LCD.

• The input voltage to this pin is boosted threefold by voltage multiplier.

• LCD drive power source pins.

• LCD common output pins.

• LCD segment/common output pins.

• LCD segment output pins.

• 8-bit I/O port.

• CMOS compatible input level.

• CMOS 3-state output structure.

• 4-bit I/O port.

• CMOS compatible input level.

• CMOS 3-state output structure.

• 1-bit input port.

• CMOS compatible input level.

• 7-bit I/O port.

• CMOS compatible input level.

• CMOS 3-state output structure.

• I/O direction register allows each pin to be individually

programmed as either input or output.

• External capacitor connect pins for a voltage multiplier of LCD.

• Non-function pins.

• Leave the VSS (NC) pin open.

Function except a port function

• A-D converter analog input pin

• Key-on wake-up interrupt input pin

• A-D converter analog input pin

• External interrupt pin

• External interrupt pin

• A-D trigger input pin

•Timer function I/O pin

• Serial I/O I/O pin

4

Page 5

PRELIMINARY

M

M F

X X X F P

P

R O M / P R O M

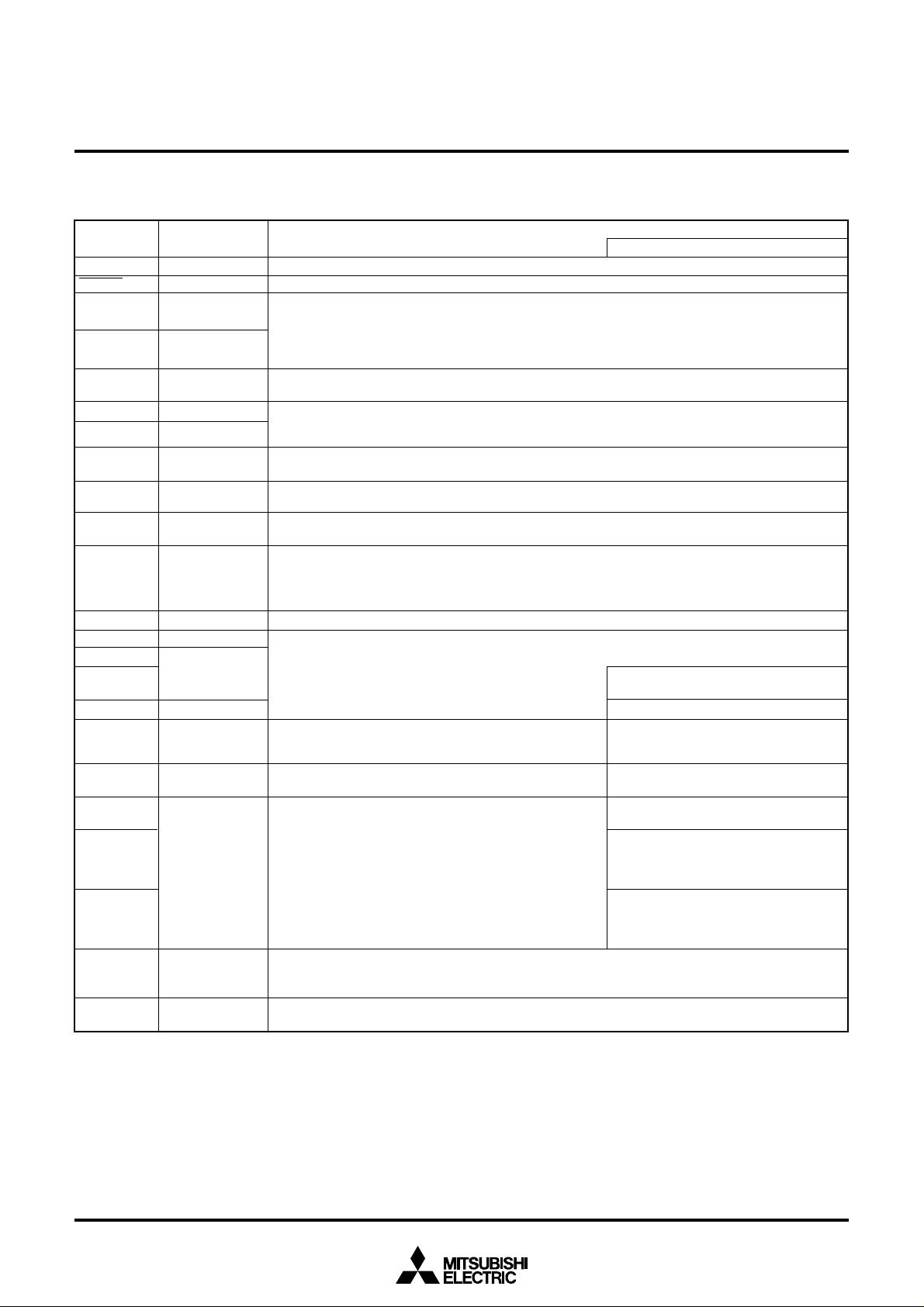

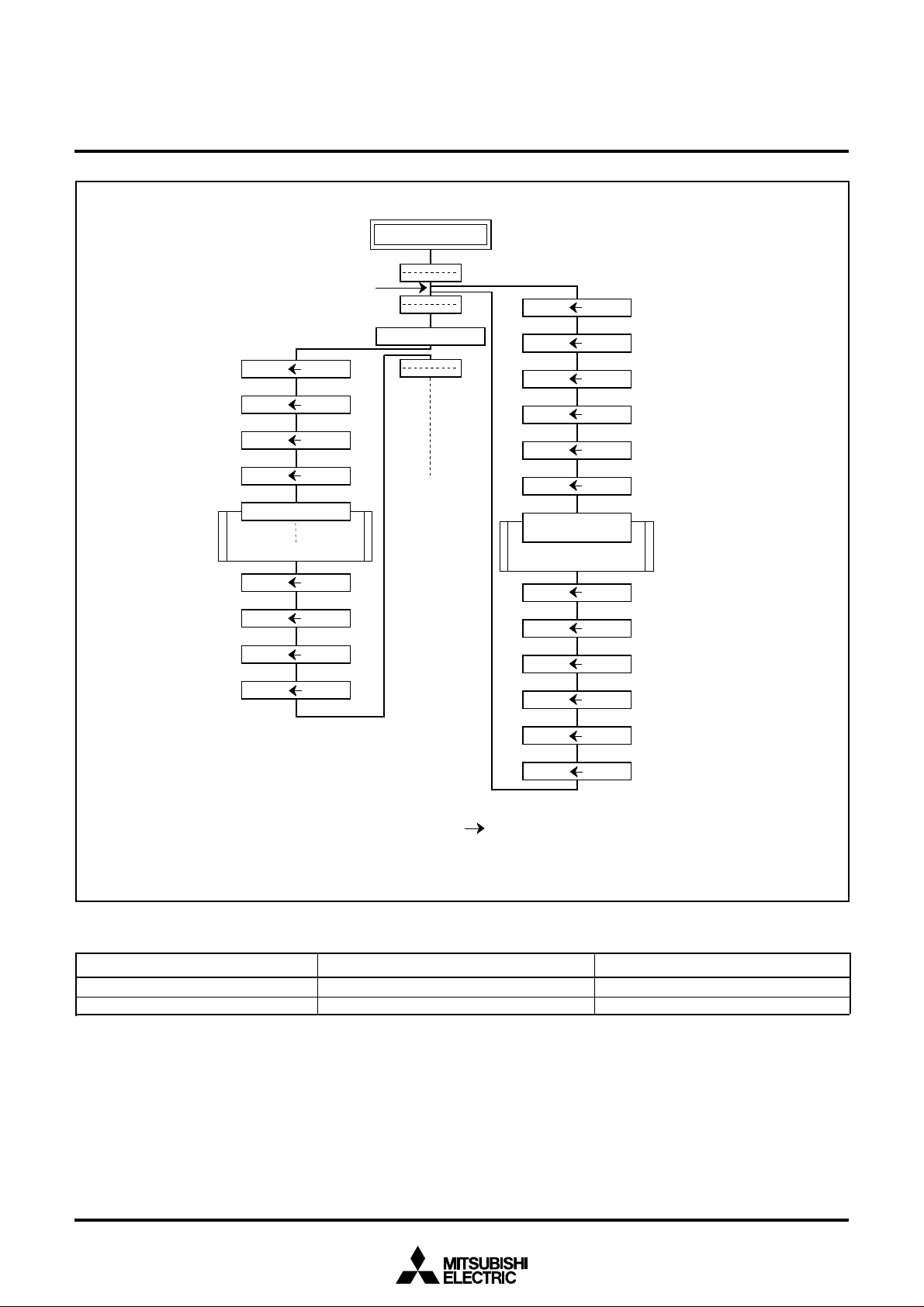

The fi

ROM

M

RAM si

Pack

R O M

b

Notice: This is not a final specification.

Some parametric limits are subject to

change.

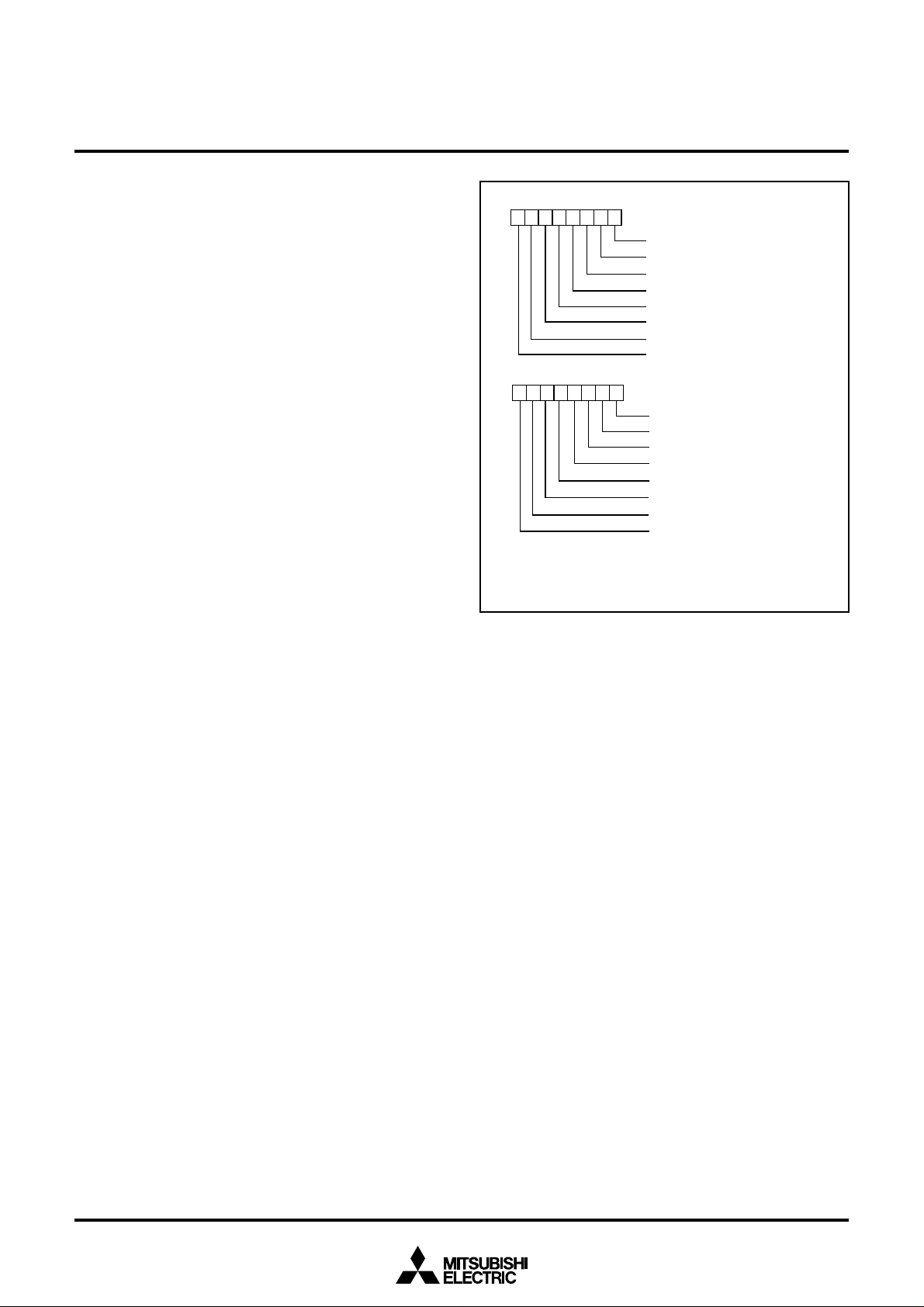

P ART NUMBERING

r o d u c

t

3 8 C

89

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

–

age type

FP: 144P6Q-A package

n u m b e

O m i t t e d i n O n e T i m e P R O M v e r s i o n .

s i z

1 : 4 0 9 6 b y t e s

2 : 8 1 9 2 b y t e s

3 : 1 2 2 8 8 b y t e s

4 : 1 6 3 8 4 b y t e s

5 : 2 0 4 8 0 b y t e s

6 : 2 4 5 7 6 b y t e s

7 : 2 8 6 7 2 b y t e s

8 : 3 2 7 6 8 b y t e s

are reserved areas; they cannot be used.

e m o r y t y p

M : M a s k R O M v e r s i o n

E : O n e T i m e P R O M v e r s i o n

r

e

y t e

9 : 3 6 8 6 4

A : 4 0 9 6 0 b y t e s

B : 4 5 0 5 6 b y t e s

C : 4 9 1 5 2 b y t e s

D : 5 3 2 4 8 b y t e s

E : 5 7 3 4 4 b y t e s

F : 6 1 4 4 0 b y t e s

rst 128 bytes and the last 2 bytes of

e

s

Fig. 3 Part numbering

ze

0: 192 bytes

1: 256 bytes

2: 384 bytes

3: 512 bytes

4: 640 bytes

5: 768 bytes

6: 896 bytes

7: 1024 bytes

8: 1536 bytes

9: 2048 bytes

5

Page 6

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

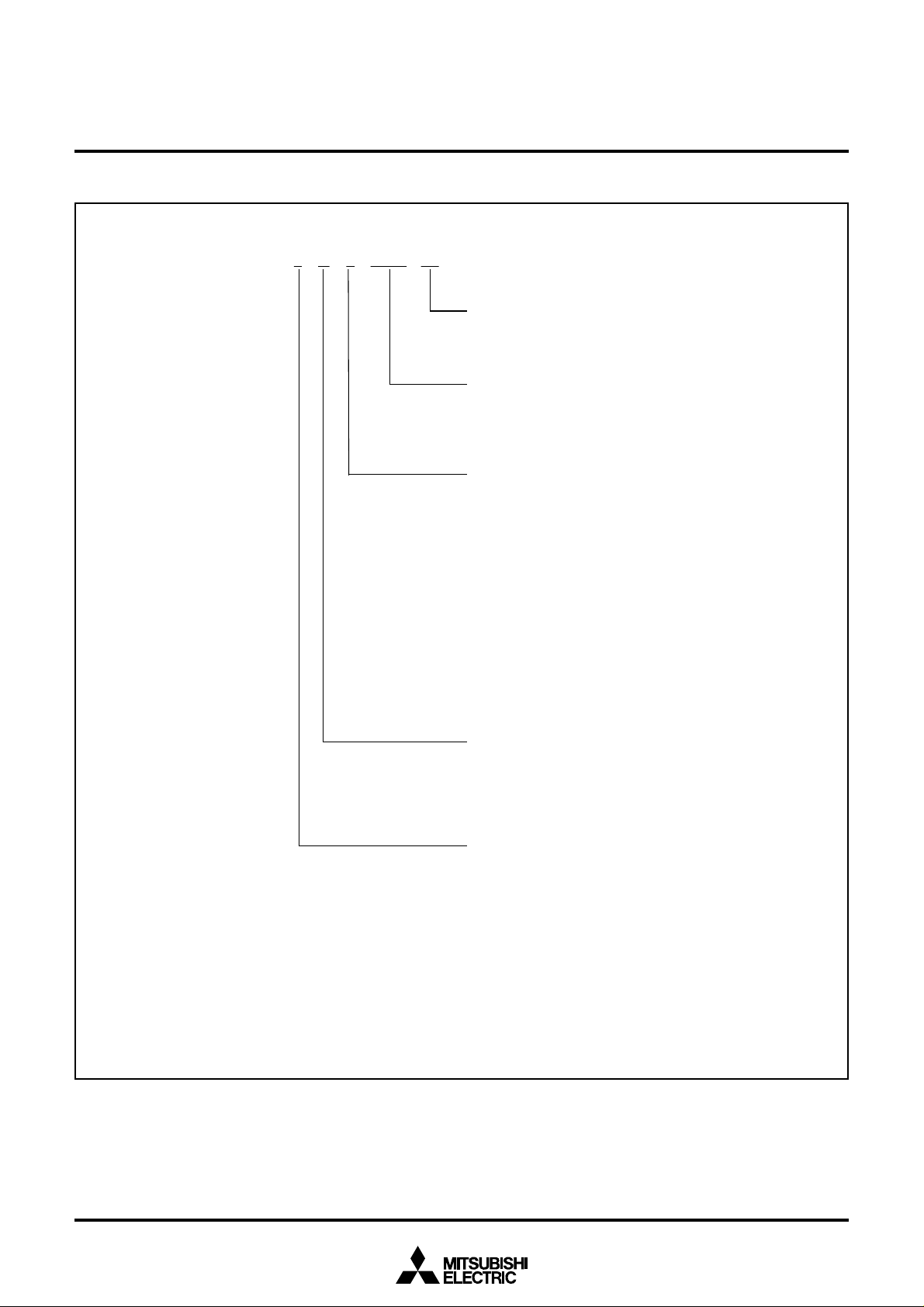

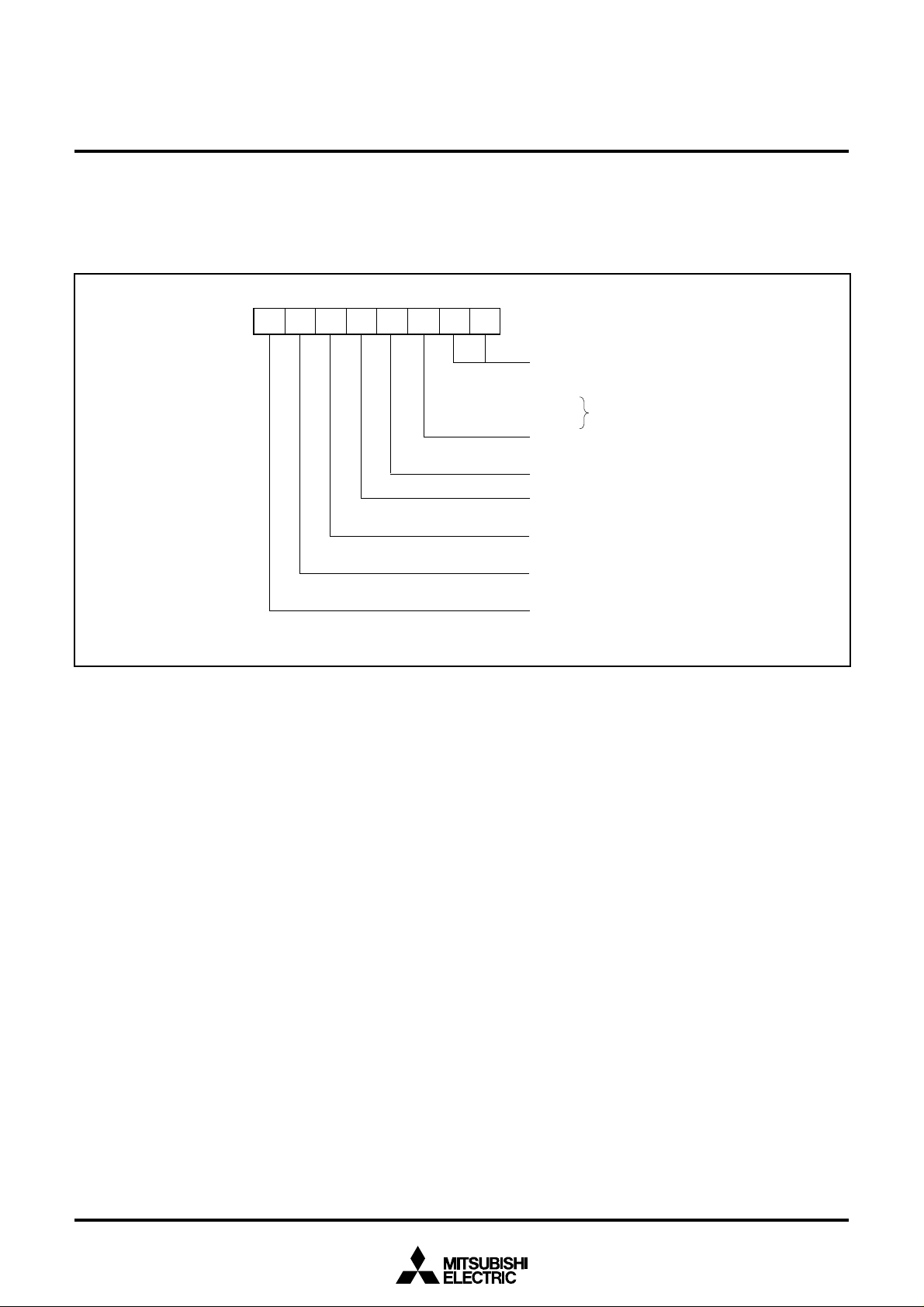

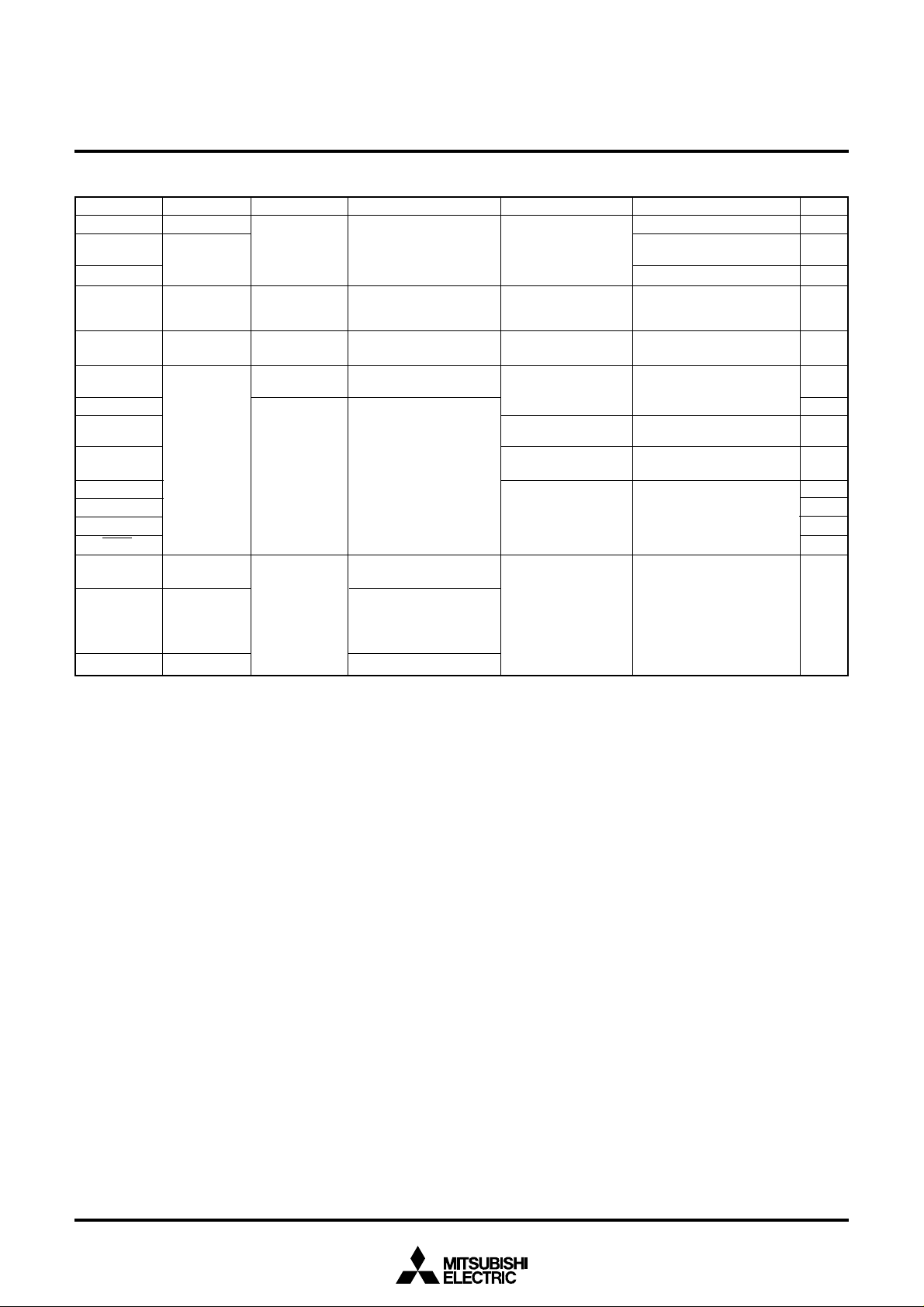

GROUP EXPANSION

Mitsubishi plans to expand the 38C8 group as follows.

Memory Type

Support for mask ROM and One Time PROM versions

Memory Size

ROM/PROM size ............................................................ 60 K bytes

RAM size........................................................................ 2048 bytes

Memory Expansion Plan

R O M s i z e ( b y t e s )

6 0 K

56K

4 8 K

4 0 K

3 2 K

28K

24K

20K

Packages

144P6Q-A ...................................0.5 mm-pitch plastic molded QFP

U n d e r d e v e l o p m e n t

M38C89MF/EF

16K

1 2 K

8K

4K

2 5 63 8 45 1 2 640 7 6 88 9 6

192

P r o d u c t s u n d e r d e v e l o p m e n t o r p l a n n i n g : t h e d e v e l o p m e n t s c h e d u l e a n d s p e c i f i c a t i o n m a y b e r e v i s e d w i t h o u t

n o t i c e . T h e d e v e l o p m e n t o f p l a n n i n g p r o d u c t s m a y b e s t o p p e d .

Fig. 4 Memory expansion plan

Currently planning products are listed below.

Table 2 Support products

Product name

M38C89MF-XXXFP

M38C89EFFP

(P) ROM size (bytes)

ROM size for User in ( )

61440 (61310)

61440 (61310)

R A M s i z e ( b y t e s )

RAM size

(bytes)

2048

2048

1,024

Package

144P6Q-A

144P6Q-A

1 , 5 3 62

Remarks

Mask ROM version

One Time PROM version

, 0 4

8

As of Dec. 2000

6

Page 7

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

FUNCTIONAL DESCRIPTION

CENTRAL PROCESSING UNIT (CPU)

The 38C8 group uses the standard 740 family instruction set. Refer

to the table of 740 family addressing modes and machine instructions or the 740 Family Software Manual for details on the instruction

set.

Machine-resident 740 family instructions are as follows:

The FST and SLW instruction cannot be used.

The STP, WIT, MUL, and DIV instruction can be used.

[Accumulator (A)]

The accumulator is an 8-bit register. Data operations such as data

transfer, etc., are executed mainly through the accumulator.

[Index Register X (X)]

The index register X is an 8-bit register. In the index addressing modes,

the value of the OPERAND is added to the contents of register X and

specifies the real address.

[Index Register Y (Y)]

The index register Y is an 8-bit register. In partial instruction, the

value of the OPERAND is added to the contents of register Y and

specifies the real address.

b7

[Stack Pointer (S)]

The stack pointer is an 8-bit register used during subroutine calls

and interrupts. This register indicates start address of stored area

(stack) for storing registers during subroutine calls and interrupts.

The low-order 8 bits of the stack address are determined by the contents of the stack pointer. The high-order 8 bits of the stack address

are determined by the stack page selection bit. If the stack page

selection bit is “0” , the high-order 8 bits becomes “0016”. If the stack

page selection bit is “1”, the high-order 8 bits becomes “0116”.

The operations of pushing register contents onto the stack and popping them from the stack are shown in Figure 6.

Store registers other than those described in Figure 6 with program

when the user needs them during interrupts or subroutine calls.

[Program Counter (PC)]

The program counter is a 16-bit counter consisting of two 8-bit registers PCH and PCL. It is used to indicate the address of the next instruction to be executed.

b0

A Accumulator

b7

b0

X Index register X

b7

b0

Y Index register Y

b7 b0

S Stack pointer

b7b15 b0

L Program counterPCH

PC

b7 b0

N V T B D I Z C Processor status register (PS)

Carry flag

Zero flag

Interrupt disable flag

Decimal mode flag

Break flag

Index X mode flag

Overflow flag

Negative flag

Fig. 5 740 Family CPU register structure

7

Page 8

PRELIMINARY

e

Notice: This is not a final specification.

Some parametric limits are subject to

change.

O n - g o i n g R o u t i n

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

P u s h r e t u r n a d d r e s s

o n s t a c k

POP return

address from stack

Interrupt request

M ( S )( P CH)

S ) –

( S )

M ( S )( P CL)

(S) (S)– 1

Subroutine

E x e c u t e R T S

S ) +

( S )

( P CL)M ( S )

(S) (S) + 1

( P CH)M ( S )

(Note)

(

(

M (S) (PCH)

E x e c u t e J S R

1

1

S ) –

( S )

(

1

M ( S )( P CL)

S ) –

( S )

(

1

M ( S )( P S )

S ) –

( S )

(

1

Interrupt

Service Routine

Execute RTI

S ) +

( S )

(

1

(PS) M (S)

S ) +

( S )

(

1

(PCL)M (S)

S ) +

( S )

(

1

Push return address

on stack

Push contents of processor

status register on stack

I Flag is set from “0” to “1”

Fetch the jump vector

POP contents of

processor status

register from stack

POP return

address

from stack

Note: Condition for acceptance of an interrupt Interrupt enable flag is “1”

Fig. 6 Register push and pop at interrupt generation and subroutine call

Table 3 Push and pop instructions of accumulator or processor status register

Push instruction to stack

Accumulator

Processor status register

I n t e r r u p t d i s a b l e f l a g i s “ 0 ”

PHA

PHP

(PCH)M (S)

Pop instruction from stack

PLA

PLP

8

Page 9

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

[Processor status register (PS)]

The processor status register is an 8-bit register consisting of 5 flags

which indicate the status of the processor after an arithmetic operation and 3 flags which decide MCU operation. Branch operations can

be performed by testing the Carry (C) flag , Zero (Z) flag, Overflow

(V) flag, or the Negative (N) flag. In decimal mode, the Z, V, N flags

are not valid.

•Bit 0: Carry flag (C)

The C flag contains a carry or borrow generated by the arithmetic

logic unit (ALU) immediately after an arithmetic operation. It can

also be changed by a shift or rotate instruction.

•Bit 1: Zero flag (Z)

The Z flag is set if the result of an immediate arithmetic operation

or a data transfer is “0”, and cleared if the result is anything other

than “0”.

•Bit 2: Interrupt disable flag (I)

The I flag disables all interrupts except for the interrupt

generated by the BRK instruction.

Interrupts are disabled when the I flag is “1”.

•Bit 3: Decimal mode flag (D)

The D flag determines whether additions and subtractions are

executed in binary or decimal. Binary arithmetic is executed when

this flag is “0”; decimal arithmetic is executed when it is “1”.

Decimal correction is automatic in decimal mode. Only the ADC

•Bit 4: Break flag (B)

The B flag is used to indicate that the current interrupt was

generated by the BRK instruction. The BRK flag in the processor

status register is always “0”. When the BRK instruction is used to

generate an interrupt, the processor status register is pushed

onto the stack with the break flag set to “1”.

•Bit 5: Index X mode flag (T)

When the T flag is “0”, arithmetic operations are performed

between accumulator and memory. When the T flag is “1”, direct

arithmetic operations and direct data transfers are enabled

between memory locations.

•Bit 6: Overflow flag (V)

The V flag is used during the addition or subtraction of one byte

of signed data. It is set if the result exceeds +127 to -128. When

the BIT instruction is executed, bit 6 of the memory location

operated on by the BIT instruction is stored in the overflow flag.

•Bit 7: Negative flag (N)

The N flag is set if the result of an arithmetic operation or data

transfer is negative. When the BIT instruction is executed, bit 7 of

the memory location operated on by the BIT instruction is stored

in the negative flag.

Table 4 Set and clear instructions of each bit of processor status register

Set instruction

Clear instruction

C flag

SEC

CLC

Z flag

–

–

I flag

SEI

CLI

D flag

SED

CLD

B flag

–

–

T flag

SET

CLT

V flag

–

CLV

N flag

–

–

9

Page 10

PRELIMINARY

N

P

CPU

( C P U M

B

)

b

b

Notice: This is not a final specification.

Some parametric limits are subject to

change.

[CPU Mode Register (CPUM)] 003B16

The CPU mode register contains the stack page selection bit and the

internal system clock selection bit.

The CPU mode register is allocated at address 003B16.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

7

Fig. 7 Structure of CPU mode register

0

mode register

( C M ) : a d d r e s s 0 0 3

rocessor mode bits

b1 b0

0 0 : Single-chip mode

0 1 :

1 0 :

1 1 :

Stack page selection bit

0 : 0 page

1 : 1 page

Not used (returns “1” when read)

(Do not write “0” to this bit)

Sub-clock (X

0 : Stopped

1 : Oscillating

Main clock (X

0 : Oscillating

1 : Stopped

Main clock division ratio selection bit

0 : f(X

1 : f(XIN)/8 (middle-s peed mode)

Internal system clock selection bit

0 : X

1 : XCIN–XCOUT selected (low-s peed mode)

o t a v a i l a b l

CIN–XCOUT) stop bit

IN–XOUT) stop bit

IN)/2 (high-speed m ode)

IN–XOUT selected (m iddle-/high-speed mode)

1 6

e

10

Page 11

PRELIMINARY

F F

R A M

R A M

A d d

F

F

R O M

R O M

Add

Add

F F

F F D C

F F F E

FFFF16X X X X

YYYY16ZZZZ

RAM

ROM

S F R

N

d

I

a

R

Z

S

R

ROM

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MEMORY

Special Function Register (SFR) Area

The Special Function Register area in the zero page contains control

Zero Page

Access to this area with only 2 bytes is possible in the zero page

addressing mode.

registers such as I/O ports and timers.

Special Page

RAM

RAM is used for data storage and for stack area of subroutine calls

and interrupts.

Access to this area with only 2 bytes is possible in the special page

addressing mode.

ROM

The first 128 bytes and the last 2 bytes of ROM are reserved for

device testing and the rest is user area for storing programs.

Interrupt Vector Area

The interrupt vector area contains reset and interrupt vectors.

a r e

a

s i z

( b y t e s )

192

256

384

512

640

768

896

1024

1536

2048

a r e

s i z

( b y t e s )

4 0 9 6

8 1 9 2

1 2 2 8 8

1 6 3 8 4

2 0 4 8 0

2 4 5 7 6

2 8 6 7 2

3 2 7 6 8

3 6 8 6 4

4 0 9 6 0

4 5 0 5 6

4 9 1 5 2

5 3 2 4 8

5 7 3 4 4

6 1 4 4 0

r e s s

e

X X X X

0 0

0 1 3 F

0 1 B F

0 2 3 F

0 2 B F

0 3 3 F

0 3 B F

0 4 3 F

0 6 3 F

0 8 3 F

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

a

e

YYYY

0 0

E 0 0 0

D 0 0 0

C 0 0 0

B 0 0 0

A 0 0 0

9 0 0 0

8 0 0 0

7 0 0 0

6 0 0 0

5 0 0 0

4 0 0 0

3 0 0 0

20 0 0

10 0 0

ress

0

16

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

ZZZZ

080

E080

D080

C080

B080

A080

9080

8080

7080

6080

5080

4080

3080

2080

1080

ress

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

0000

0040

0130

0 3 4 0

0 4 3 0

0840

0

16

16

LCD display RA M area

16

1 6

1 6

L C D d i s p l a y R A M a r e a

1 6

16

e s e r v e d R O M a r e

16

1 6

0

1 6

nterrupt vector are

1 6

eserved

a r e

ot use

( 1 2 8 b y t e s )

a

e r o p a g

e

✽

✽

a

p e c i a l p a g

e

area

✽ The stard address of the LCD display area can be switched either zero page (addresses 004016–00EF16) or 3 page (addresses

0340

16

Fig. 8 Memory map diagram

–03EF16) by software. Immediately after reset released, 3 page is selected.

11

Page 12

PRELIMINARY

T

(TB/RB)

A

B

C

D

E

F

A

B

C

D

E

F

A

B

C

D

E

F

A

B

C

D

E

F

P

)

P

)

P

)

P

)

P

)

P

)

P

)

P

)

P

D)

S

)

Serial I/O

(SIOCON)

UART

(UARTCON)

I

)

Ti

(TXM)

I

(INTEDGE)

CPU

(CPUM)

I

(IREQ1)

I

(IREQ2)

I

(ICON1)

Ti

(TXL)

P U L L

)

P U L L

)

L C D

)

A

)

A-D

(ADL)

A-D

(high

(ADH)

P

)

B

)

T i

)

T i

)

T i

)

T i

)

T i

)

T i

)

T i

)

T i

)

L C D

)

L C D

)

Notice: This is not a final specification.

Some parametric limits are subject to

change.

0 0 0 0

1 6

ort P0 (P0

o r t P 0 d i r e c t i o n r e g i s t e r ( P 0 D

0 0 0 1

1 6

o r t P 1 ( P 1

0 0 0 2

1 6

o r t P 1 d i r e c t i o n r e g i s t e r ( P 1 D

0 0 0 3

1 6

0 0 0 4

1 6

ort P2 (P2

o r t P 2 d i r e c t i o n r e g i s t e r ( P 2 D

0 0 0 5

1 6

o r t P 3 ( P 3

0 0 0 6

1 6

o r t P 3 d i r e c t i o n r e g i s t e r ( P 3 D

0 0 0 7

1 6

o r t P 4 ( P 4

0 0 0 8

1 6

0009

16

ort P4 direction register (P4

000

16

0 0 0

1 6

0 0 0

1 6

0 0 0

1 6

0 0 0

1 6

0 0 0

1 6

0010

16

0 0 1 1

1 6

0012

16

0013

16

0 0 1 4

1 6

0 0 1 5

1 6

r e g i s t e r A ( P U L L A

0 0 1 6

1 6

r e g i s t e r B ( P U L L B

0 0 1 7

1 6

0 0 1 8

1 6

ransmit/Receive buffer register

e r i a l I / O s t a t u s r e g i s t e r ( S I O S T S

0019

16

001

001

001

001

001

001

16

16

a u d r a t e g e n e r a t o r ( B R G

16

16

16

16

control register

control register

0020

0021

0022

0023

0024

0025

0026

0027

0028

0029

0 0 2

0 0 2

002

002

002

002

0030

0031

0032

0033

0034

0035

0036

0037

0038

0039

0 0 3

0 0 3

0 0 3

0 0 3

0 0 3

003

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

16

mer X (low-order)

m e r X ( h i g h - o r d e r ) ( T X H

16

m e r Y ( l o w - o r d e r ) ( T Y L

16

m e r Y ( h i g h - o r d e r ) ( T Y H

16

m e r 1 ( T 1

16

m e r 2 ( T 2

16

m e r 3 ( T 3

16

16

mer X mode register

m e r Y m o d e r e g i s t e r ( T Y M

16

m e r 1 2 3 m o d e r e g i s t e r ( T 1 2 3 M

16

1 6

1 6

16

16

16

16

16

- D c o n t r o l r e g i s t e r ( A D C O N

16

16

conversion register (low-order)

16

conversion register

16

16

16

c o n t r o l r e g i s t e r 1 ( L C 1

16

c o n t r o l r e g i s t e r 2 ( L C 2

16

m o d e r e g i s t e r ( L M

16

1 6

nterrupt edge selection register

1 6

mode register

1 6

nterrupt request register 1

1 6

nterrupt request register 2

1 6

nterrupt control register 1

n t e r r u p t c o n t r o l r e g i s t e r 2 ( I C O N 2

16

-order)

Fig. 9 Memory map of special function register (SFR)

12

Page 13

PRELIMINARY

P 00– P 03 p u l l - u p

P 04– P 07 p u l l - u p

P 1

0

– P 13 p u l l - u p

P 14– P 17 p u l l - u p

P 20– P 23 p u l l - u p

P 24– P 27 p u l l - u p

P 3

0

– P 33 p u l l - u p

N o t u s e d ( r e t u r n “ 0 ” w h e n r e a d )

N o t e : T h e c o n t e n t s o f P U L L r e g i s t e r A a n d P U L L r e g i s t e r B d o

n o t a f f e c t p o r t s p r o g r a m m e d a s t h e o u t p u t p o r t .

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

I/O PORTS

[Direction Registers]

The I/O ports P0–P3 and P41–P47 have direction registers which

determine the input/output direction of each individual pin. Each bit

in a direction register corresponds to one pin, each pin can be set to

be input port or output port.

When “0” is written to the bit corresponding to a pin, that pin becomes an input pin. When “1” is written to that bit, that pin becomes

an output pin.

If data is read from a pin set to output, the value of the port output

latch is read, not the value of the pin itself. Pins set to input are floating. If a pin set to input is written to, only the port output latch is

written to and the pin remains floating.

Pull-up Control

By setting the PULL register A (address 001616) or the PULL register

B (address 001716), ports P0 to P4 except for port P40 can control

pull-up with a program.

However, the contents of PULL register A and PULL register B do not

affect ports programmed as the output ports.

b7 b0

b 7b0

PULL register A

(PULLA: address 0016

PULL register B

(PULLB: address 0017

N o t u s e d ( r e t u r n “ 0 ” w h e n r e a d )

P 41 p u l l - u p

P 4

2

p u l l - u p

P 43 p u l l - u p

P 4

4

p u l l - u p

P 45 p u l l - u p

P 46 p u l l - u p

P 4

7

p u l l - u p

16

16

0: No pull-up

1: Pull-up

)

)

Fig. 10 Structure of PULL register A and PULL register B

13

Page 14

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to

change.

Table 5 List of I/O port function

Pin

P00–P07

P10/AN4–

P13/AN7

P14–P17

P20–P27

P30/AN0–

P33/AN3

P40/INT0

P41/INT1

P42/CNTR0/

BEEP+

P43/CNTR1/

BEEPP44/RxD

P45/TxD

P46/SCLK

P47/SRDY

COM0–COM7,

COM8–COM

SEG0/COM16–

SEG7/COM23,

SEG60/COM31–

SEG67/COM

SEG8–SEG

24

59

Name

Port P0

Port P1

Port P2

Port P3

Port P4

Common

15

Segment/

Common

Segment

Input/Output

Input/Output,

individual bits

Input/Output,

individual bits

Input/Output,

individual bits

Input

Input/Output,

individual bits

Output

I/O format

CMOS 3-state output

CMOS compatible input

level

CMOS 3-state output

CMOS 3-state output

CMOS compatible input

level

CMOS compatible input

level

CMOS 3-state output

LCD common output

LCD segment output

LCD common ouput

LCD segment output

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Non-port function

Key input (key-on

wake-up) interrupt input

A-D converter input

External interrupt input

Timer X function I/O

Timer Y function input

Serial I/O funtion

I/O

Related SFRs

PULL register A

PULL register A

A-D control register

PULL register A

PULL register A

Interrupt control register 2

PULL register A

A-D control register

PULL register B

Interrupt edge select

register

PULL register B

Timer X mode register

PULL register B

Timer Y mode register

PULL register B

Serial I/O control register

Serial I/O status register

UART control register

LCD mode register

Ref. No.

(1)

(2)

(1)

(1)

(2)

(3)

(1)

(4)

(5)

(6)

(7)

(8)

(9)

14

Page 15

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

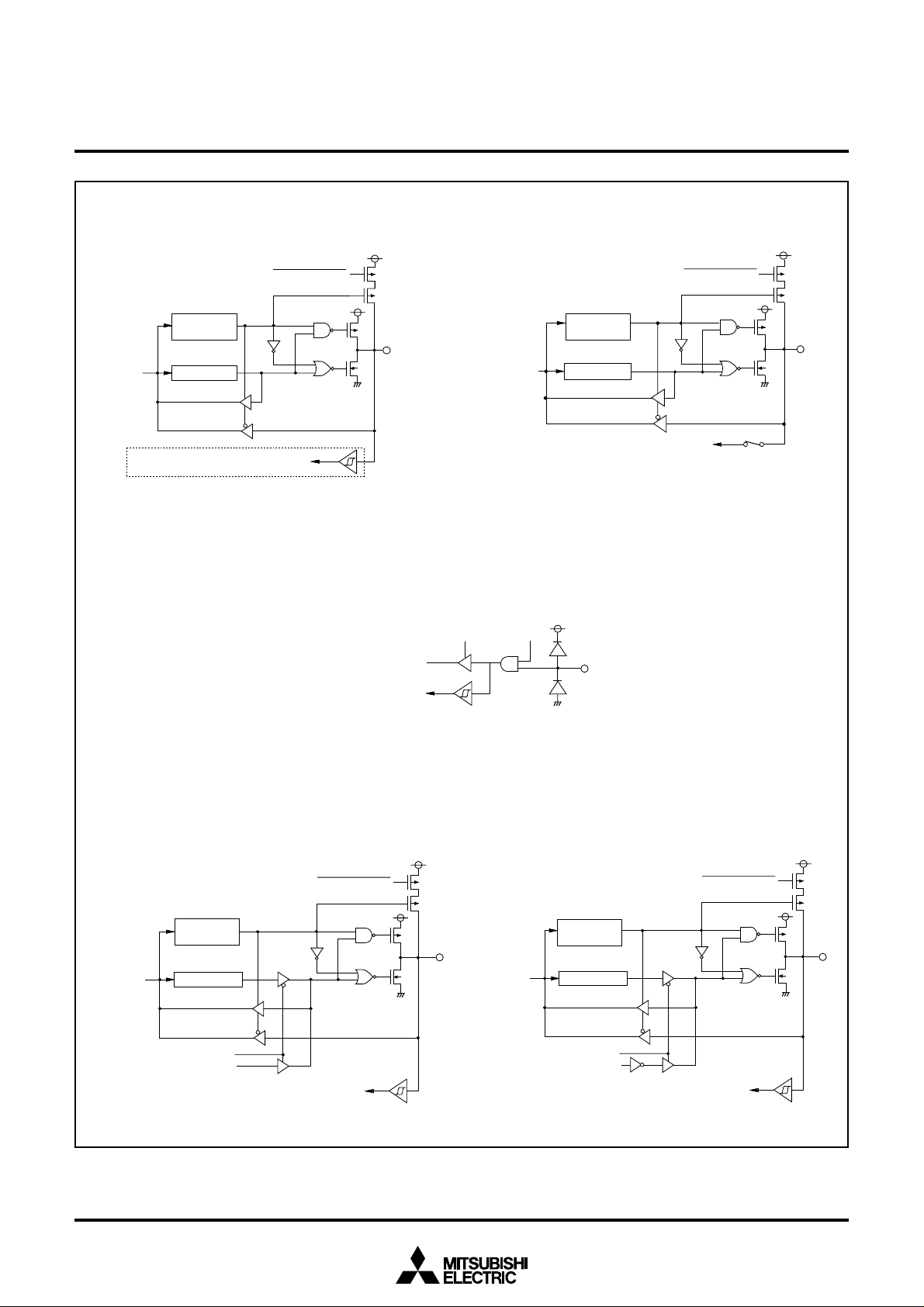

( 1 ) P o r t s P 0 , P 14– P 17, P 2 , P 4

D i r e c t i o n

r e g i s t e r

D a t a b u s

P o r t l a t c h

K e y - o n w a k e - u p i n t e r r u p t i n p u t

1

i n t e r r u p t i n p u t , A D T

I N T

1

P u l l - u p c o n t r o l

E x c e p t P 0 , P 1

(3) Port P4

INT0 interrupt input

0

D a t a b u s

( 2 ) P o r ts P 10– P 13, P 3

D i r e c t i o n

r e g i s t e r

Data bus

Port latch

P u l l - u p c o n t r o l

A-D converter input

A n a l o g i n p u t p i n s e l e c t i o n b i t

( 4 ) P o r t P 4

D a t a b u s

2

D i r e c t i o n

r e g i s t e r

P o r t l a t c h

B u z z e r o u t p u t m o d e

T i m e r o u t p u t

Fig. 11 Port block diagram (1)

P u l l - u p c o n t r o l

C N T R0 i n t e r r u p t i n p u t

( 5 ) P o r t P 4

Data bus

Buzzer output mode

3

Direction

register

P o r t l a t c h

Timer output

CNTR

Pull-up control

1

interrupt input

15

Page 16

PRELIMINARY

t

t

t

s

t

t

t

t

t

t

t

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

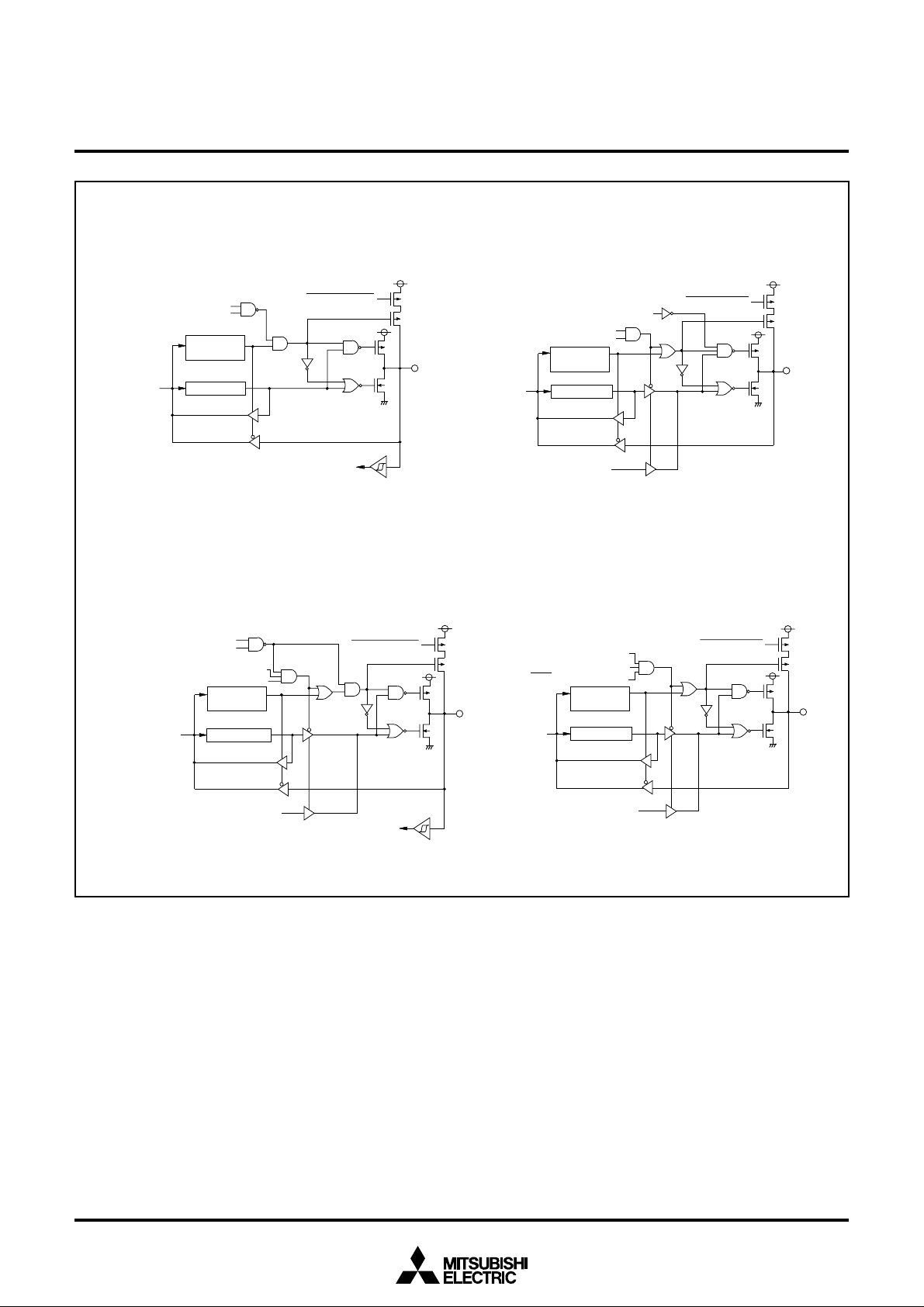

( 6 ) P o r t P 4

D a t a b u s

(8) Port P4

S e r i a l I / O s y n c h r o n o u

4

S e r i a l I / O e n a b l e b i

R e c e i v e e n a l b l e b i

D i r e c t i o n

r e g i s t e r

P o r t l a t c h

6

c l o c k s e l e c t i o n b i

S e r i a l I / O e n a b l e b i t

Serial I/O mode selection bi

Serial I/O enable bi

Direction

register

Pull-up control

S e r i a l I / O i n p u t

Pull-up control

( 7 ) P o r t P 4

P45/TxD P-channel output disable bit

D a t a b u s

(9) Port P4

S e r i a l I / O m o d e s e l e c t i o n b i

5

S e r i a l I / O e n a b l e b i

T r a n s m i t e n a b l e b i

Direction

register

P o r t l a t c h

Serial I/O output

7

S e r i a l I / O e n a b l e b i

S

R D Y

o u t p u t e n a b l e b i

Direction

register

Pull-up control

P u l l - u p c o n t r o l

Port latchData bus

Serial I/O clock output

Fig. 12 Port block diagram (2)

Serial I/O clock input

Data bus

Serial I/O ready output

P o r t l a t c h

16

Page 17

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

INTERRUPTS

Interrupts occur by fifteen sources: six external, eight internal, and

one software.

Interrupt Control

Each interrupt except the BRK instruction interrupt have both an interrupt request bit and an interrupt enable bit, and is controlled by the

interrupt disable flag. An interrupt occurs if the corresponding interrupt request and enable bits are “1” and the interrupt disable flag is

“0”.

Interrupt enable bits can be set or cleared by software. Interrupt request bits can be cleared by software, but cannot be set by software.

The BRK instruction interrupt and reset cannot be disabled with any

flag or bit. The I flag disables all interrupts except the BRK instruction

interrupt and reset. If several interrupts requests occurs at the same

time the interrupt with highest priority is accepted first.

Table 6 Interrupt vector addresses and priority

Interrupt Source

Reset (Note 2)

INT0

INT1

Serial I/O

reception

Serial I/O

transmission

Timer X

Timer Y

Timer 2

Timer 3

CNTR0

CNTR1

Timer 1

Key input (Key-

on wake-up)

A-D conversion

BRK instruction

Notes 1: Vector addresses contain interrupt jump destination addresses.

2: Reset function in the same way as an interrupt with the highest priority.

Priority

Vector Addresses (Note 1)

High

1

FFFD16

2

FFFB16

3

FFF916

4

FFF716

5

FFF516

6

FFF316

7

FFF116

8

FFEF16

9

FFED16

10

11

12

13

14

15

FFEB16

FFE916

FFE716

FFE116

FFDF16

FFDD16

Low

FFFC16

FFFA16

FFF816

FFF616

FFF416

FFF216

FFF016

FFEE16

FFEC16

FFEA16

FFE816

FFE616

FFE016

FFDE16

FFDC16

At reset

At detection of either rising or falling edge of

INT0 intput

At detection of either rising or falling edge of

INT1 input

At completion of serial I/O data reception

At completion of serial I/O transmission shift

or when transmission buffer is empty

At timer X underflow

At timer Y underflow

At timer 2 underflow

At timer 3 underflow

At detection of either rising or falling edge of

CNTR0 input

At detection of either rising or falling edge of

CNTR1 input

At timer 1 underflow

At falling of port P2 (at input) input logical level

AND

At completion of A-D conversion

At BRK instruction execution

Interrupt Operation

By acceptance of an interrupt, the following operations are automatically performed:

1.The processing being executed is stopped.

2.The contents of the program counter and processor status register are automatically pushed onto the stack.

3.The interrupt disable flag is set and the corresponding interrupt

request bit is cleared.

4.The interrupt jump destination address is read from the vector

table into the program counter.

■Notes on interrupts

When setting the followings, the interrupt request bit may be set to

“1”.

•When setting external interrupt active edge

Related register: Interrupt edge selection register (address 3A16)

Timer X mode register (address 2716)

Timer Y mode register (address 2816)

•When switching interrupt sources of an interrupt vector address

where two or more interrupt sources are allocated

Related register: AD control regsiter (address 3116)

When not requiring for the interrupt occurrence synchronized with

these setting, take the following sequence.

➀Set the corresponding interrupt enable bit to “0” (disabled).

➁Set the interrupt edge select bit (active edge switch bit) or the inter-

rupt source select bit to “1”.

➂Set the corresponding interrupt request bit to “0” after 1 or more

instructions have been executed.

➃Set the corresponding interrupt enable bit to “1” (enabled).

Interrupt Request

Generating Conditions

Non-maskable

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

Valid when serial I/O is selected

Valid when serial I/O is selected

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(falling valid)

Valid when A-D conversion interrupt

is selected

Non-maskable software interrupt

Remarks

17

Page 18

PRELIMINARY

t

t

t

I

I N T

i

d

( I R E Q

C

)

I

CNTR0 i

(IREQ

D16)

b7b

I

I N T

i

(INTEDGE

A16)

F

b7b0b

b

I

I N T

i

( I C O N

E

)

I

C N T R

i

d

( I C O N

F

)

b7b0b7b

Notice: This is not a final specification.

Some parametric limits are subject to

change.

I n t e r r u p t r e q u e s t b i

I n t e r r u p t e n a b l e b i

I n t e r r u p t d i s a b l e f l a g ( I )

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Fig. 13 Interrupt control

0

n t e r r u p t e d g e s e l e c t i o n r e g i s t e

: address 003

n t e r r u p t e d g e s e l e c t i o n b i

0

I N T1 i n t e r r u p t e d g e s e l e c t i o n b i t

N o t u s e d ( r e t u r n “ 0 ” w h e n r e a d )

n t e r r u p t r e q u e s t r e g i s t e r

1 : a d d r e s s 0 0 3

n t e r r u p t r e q u e s t b i

0

I N T1 i n t e r r u p t r e q u e s t b i t

S e r i a l I / O r e c e i v e i n t e r r u p t r e q u e s t b i t

S e r i a l I / O t r a n s m i t i n t e r r u p t r e q u e s t b i t

T i m e r X i n t e r r u p t r e q u e s t b i t

T i m e r Y i n t e r r u p t r e q u e s t b i t

T i m e r 2 i n t e r r u p t r e q u e s t b i t

T i m e r 3 i n t e r r u p t r e q u e s t b i t

nterrupt control register 1

1 : a d d r e s s 0 0 3

n t e r r u p t e n a b l e b i

0

I N T1 i n t e r r u p t e n a b l e b i t

S e r i a l I / O r e c e i v e i n t e r r u p t e n a b l e b i t

S e r i a l I / O t r a n s m i t i n t e r r u p t e n a b l e b i t

T i m e r X i n t e r r u p t e n a b l e b i t

T i m e r Y i n t e r r u p t e n a b l e b i t

T i m e r 2 i n t e r r u p t e n a b l e b i t

T i m e r 3 i n t e r r u p t e n a b l e b i t

B R K i n s t r u c t i o n

r

1

1 6

t

1 6

t

R e s e

t

a l l i n g e d g e a c t i v

0 :

1 : R i s i n g e d g e a c t i v e

I n t e r r u p t r e q u e s t

e

7

n t e r r u p t r e q u e s t r e g i s t e r

0

2 : address 003

nterrupt request bit

CNTR

1 interrupt request bit

Timer 1 interrupt request bit

Not used (returns “0” when read)

Key input interrupt request bit

AD conversion interrupt request bit

Not used (returns “0” when read)

0 : No interrupt re quest issue

1 : Interrupt request issued

0

nterrupt control register 2

2 : a d d r e s s 0 0 3

n t e r r u p t e n a b l e b i

0

C N T R1 i n t e r r u p t e n a b l e b i t

T i m e r 1 i n t e r r u p t e n a b l e b i t

N o t u s e d ( r e t u r n s “ 0 ” w h e n r e a d )

( D o n o t w r i t e “ 1 ” t o t h i s b i t )

K e y i n p u t i n t e r r u p t e n a b l e b i t

A D c o n v e r s i o n i n t e r r u p t e n a b l e b i t

N o t u s e d ( r e t u r n s “ 0 ” w h e n r e a d )

( D o n o t w r i t e “ 1 ” t o t h i s b i t )

0 : Interrupts disable

1 : Interrupts enabled

2

1 6

t

Fig. 14 Structure of interrupt-related registers

18

Page 19

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Key Input Interrupt (Key-on Wake-Up)

A key input interrupt request is generated by applying “L” level to any

pin of port P2 that have been set to input mode. In other words, it is

generated when AND of input level goes from “1” to “0”. An example

P o r t P X x

“ L ” l e v e l o u t p u t

7

o u t p u t

P 2

6

output

P2

5

output

P2

4

output

P2

P U L L r e g i s t e r A

B i t 2 = “ 1 ”

✽

✽

✽

✽

Key input control register = “1”

7

d i r e c t i o n

P o r t P 2

r e g i s t e r = “ 1 ”

✽✽

Port P2

latch

Key input control register = “1”

P o r t P 2

6

d i r e c t i o n

r e g i s t e r = “ 1 ”

✽✽

Port P2

latch

K e y i n p u t c o n t r o l r e g i s t e r = “ 1 ”

P o r t P 2

5

d i r e c t i o n

r e g i s t e r = “ 1 ”

✽✽

Port P2

latch

Key input control register = “1”

Port P2

4

direction

register = “1”

✽✽

Port P2

latch

of using a key input interrupt is shown in Figure 15, where an interrupt request is generated by pressing one of the keys consisted as

an active-low key matrix which inputs to ports P20–P23.

Key input interrupt request

7

6

5

4

P 2

P2

P 2

P 2

3

i n p u t

2

i n p u t

1

input

0

i n p u t

Key input control register = “1”

Port P2

3

direction

✽

✽

✽

✽

register = “0”

✽✽

Port P2

✽✽

Port P2

✽✽

P o r t P 2

✽✽

3

Port P2

latch

K e y i n p u t c o n t r o l r e g i s t e r = “ 1 ”

2

direction

register = “0”

2

Port P2

latch

Key input control register = “1”

1

direction

register = “0”

1

Port P2

latch

K e y i n p u t c o n t r o l r e g i s t e r = “ 1 ”

0

d i r e c t i o n

r e g i s t e r = “ 0 ”

Port P2

0

latch

✽

P-channel transistor for pull-up

✽✽

CMOS output buffer

Port P2

Input reading circ uit

Fig. 15 Connection example when using key input interrupt and port P2 block diagram

19

Page 20

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

TIMERS

The 38C8 group has five timers: timer X, timer Y, timer 1, timer 2, and

timer 3. Timer X and timer Y are 16-bit timers, and timer 1, timer 2,

and timer 3 are 8-bit timers.

All timers are down count timers. When the timer reaches “0016”, an

underflow occurs at the next count pulse and the corresponding timer

latch is reloaded into the timer and the count is continued. When a

timer underflows, the interrupt request bit corresponding to that timer

f ( X

I N

) / 1 6

( f ( X

C I N

) / 1 6 i n l o w - s p e e d m o d e✽)

P 42/ C N T R0/ B E E P +

P 42 d i r e c t i o n r e g i s t e r

P 43/ C N T R1/ B E E P -

f(X

CIN

)

Timer X operating

mode bits

CNTR1 active

edge switch bit

f ( X

“ 0 0 ” , “ 1 1 ”

“01”

C N T R0 a c t i v e

e d g e s w i t c h b i t

“ 0 ”

“ 1 ”

Pulse width

measurement

mode

B u z z e r o u t p u t m o d e

“0”

“ 1 ”

I N

)

T i m e r X c o u n t s o u r c e

s e l e c t i o n b i t

“ 1 ”

“ 0 ”

C N T R0 a c t i v e

e d g e s w i t c h b i t

2

latch

P4

Timer X operating

mode bits

“00”,“01”,“11”

“ 1 0 ”

“0”

“ 1 ”

IN

)/16

f(X

(f(X

CIN

)/16 in low-speed mode✽)

“00”,“01”,“11”

Timer Y operating

“10”

mode bits

Timer X stop con t ro l bit

S

Q

T

Q

Timer Y stop

control bit

is set to “1”.

Read and write operation on 16-bit timer must be performed for both

high and low-order bytes. When reading a 16-bit timer, read the highorder byte first. When writing to a 16-bit timer, write the low-order

byte first. The 16-bit timer cannot perform the correct operation when

reading during the write operation, or when writing during the read

operation.

Data bus

Timer X write control bit

T i m e r X ( l o w ) l a t c h ( 8 )

Timer X (low) (8) T i m e r X ( h i g h ) ( 8 )

P u l s e o u t p u t m o d e

Rising edge detection

Falling edge detection

T i m e r Y ( l o w ) l a t c h ( 8 ) Timer Y (low) high (8)

T i m e r Y ( l o w ) ( 8 ) Timer Y (high) (8)

T i m e r X ( h i g h ) l a t c h ( 8 )

Timer Y operating mode bits

Pulse width HL continuously

measurement mode

Period measu r ement mode

“ 0 0 ” , “ 0 1 ” , “ 1 0 ”

“11”

T i m e r Y i n t e r r u p t

r e q u e s t

T i m e r X i n t e r r u p t

r e q u e s t

C N T R 0 i n t e r r u p t

r e q u e s t

CNTR1 interrupt

request

P 4

3

d i r e c t i o n r e g i s t e r

f(XIN)/16

(f(X

CIN

)/16 in low-speed mode✽)

✽ I n t e r n a l c l o c k φ = X

Fig. 16 Timer block diagram

20

BEEP- valid bit

Timer 1 count source

selection bit

C I N

f ( X

P4

3

latch

“0”

T i m e r 1 l a t c h ( 8 )

) / 3 2

“1”

C I N

d i v i d e d b y 2 i n l o w - s p e e d m o d e

Timer 1 (8)

f ( X

C I N

f ( X

( f ( X

) / 3 2

Timer 3 count source

selection bit

T i m e r 2 c o u n t s o u r c e

s e l e c t i o n b i t

“ 0 ”

“ 1 ”

I N

) / 1 6

C I N

) / 1 6 i n l o w - s p e e d m o d e✽)

Timer 3 latch (8)

“ 0 ”

“1”

T i m e r 3 ( 8 )

T i m e r 2 l a t c h ( 8 )

Timer 2 (8)

Timer 2 write control bit

T i m e r 1 i n t e r r u p t

r e q u e s t

T i m e r 2 i n t e r r u p t

r e q u e s t

T i m e r 3 i n t e r r u p t

r e q u e s t

Page 21

PRELIMINARY

T i

T i

b

b

Notice: This is not a final specification.

Some parametric limits are subject to

change.

Timer X

Timer X is a 16-bit timer that can be selected in one of four modes

and can be controlled the timer X write by setting the timer X mode

register.

(1) Timer Mode

When the timer X count source selection bit is “0”, the timer counts

f(XIN)/16 (or f(XCIN)/16 in low-speed mode). When it is “1”, the timer

counts f(XIN).

(2) Buzzer Output Mode

Each time the timer underflows, a signal output from the BEEP+ pin

is inverted. When the BEEP- valid bit is “1”, the opposite phase of

BEEP+ signal is output from the BEEP- pin. When using the BEEP+

pin and the BEEP- pin, set ports shared with these pins to output.

(3) Event Counter Mode

The timer counts signals input through the CNTR0 pin.

Except for this, the operation in event counter mode is the same as

in timer mode. When using a timer in this mode, set the port shared

with the CNTR0 pin to input.

(4) Pulse Width Measurement Mode

When the timer X count source selection bit is “0”, the count source

is f(XIN)/16 (or f(XCIN)/16 in low-speed mode). When it is “1”, the

count source is f(XIN).

If CNTR0 active edge switch bit is “0”, the timer counts while the

input signal of CNTR0 pin is at “H”. If it is “1”, the timer counts while

the input signal of CNTR0 pin is at “L”. When using a timer in this

mode, set the port shared with the CNTR0 pin to input.

MITSUBISHI MICROCOMPUTERS

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

7

Fig. 17 Structure of timer X mode register

0

m e r X m o d e r e g i s t e

( T X M : a d d r e s s 0 0 2 7

m e r X w r i t e c o n t r o l b i

a c t i v e e d g e s w i t c h b i

0 : W r i t e v a l u e i n l a t c h a n d c o u n t e r

1 : W r i t e v a l u e i n l a t c h o n l y

B E E P - v a l i d b i t

0 : I n v a l i d

1 : V a l i d

N o t u s e d

T i m e r X o p e r a t i n g m o d e b i t s

b 5 b 4

0 0 : T i m e r m o d e

0 1 : B u z z e r o u t p u t m o d e

1 0 : E v e n t c o u n t e r m o d e

1 1 : P u l s e w i d t h m e a s u r e m e n t m o d e

0

C N T R

0 : C o u n t a t r i s i n g e d g e i n e v e n t c o u n t e r m o d e

S t a r t f r o m “ H ” o u t p u t i n p u l s e o u t p u t m o d e

M e a s u r e “ H ” p u l s e w i d t h i n p u l s e w i d t h

m e a s u r e m e n t m o d e

F a l l i n g e d g e a c t i v e f o r i n t e r r u p t

1 : C o u n t a t f a l l i n g e d g e i n e v e n t c o u n t e r m o d e

S t a r t f r o m “ L ” o u t p u t i n p u l s e o u t p u t m o d e

M e a s u r e “ L ” p u l s e w i d t h i n p u l s e w i d t h

m e a s u r e m e n t m o d e

R i s i n g e d g e a c t i v e f o r i n t e r r u p t

T i m e r X s t o p c o n t r o l b i t

0 : C o u n t s t a r t

1 : C o u n t s t o p

38C8 Group

r

1 6)

t

t

●Timer X write control

If the timer X write control bit is “0”, when the value is written in the

address of timer X, the value is loaded in the timer X and the latch

at the same time.

If the timer X write control bit is “1”, when the value is written in the

address of timer X, the value is loaded only in the latch. The value

in the latch is loaded in timer X after timer X underflows.

If the value is written in latch only, unexpected value may be set in

the high-order counter when the writing in high-order latch and the

underflow of timer X are performed at the same timing.

■Notes on CNTR0 interrupt active edge selection

CNTR0 interrupt active edge depends on the CNTR0 active edge

switch bit.

21

Page 22

PRELIMINARY

T i

b

b

T i

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Timer Y

Timer Y is a 16-bit timer that can be selected in one of four modes.

(1) Timer Mode

The timer counts f(XIN)/16 (or f(XCIN)/16 in low-speed mode).

(2) Period Measurement Mode

CNTR1 interrupt request is generated at rising/falling edge of CNTR1

pin input signal. Simultaneously, the value in timer Y latch is reloaded

in timer Y and timer Y continues counting down. Except for the abovementioned, the operation in period measurement mode is the same

as in timer mode.

The timer value just before the reloading at rising/falling of CNTR1

pin input signal is retained until the timer Y is read once after the

reload.

The rising/falling timing of CNTR1 pin input signal is found by CNTR1

interrupt. When using a timer in this mode, set the port shared with

the CNTR1 pin to input.

(3) Event Counter Mode

The timer counts signals input through the CNTR1 pin.

Except for this, the operation in event counter mode is the same as

in timer mode. When using a timer in this mode, set the port shared

with the CNTR1 pin to input.

(4) Pulse Width HL Continuously Measurement

Mode

CNTR1 interrupt request is generated at both rising and falling edges

of CNTR1 pin input signal. Except for this, the operation in pulse

width HL continuously measurement mode is the same as in period

measurement mode. When using a timer in this mode, set the port

shared with the CNTR1 pin to input.

7

✽ Internal clock φ in low-speed mode is X

When the timer X operating mode bits are “00” or “11”, the timer X count source is

CIN

)/16. When the timer X operating mode bits are “01”, the timer X count source

f(X

CIN

).

is f(X

0

m e r Y m o d e r e g i s t e

( T Y M : a d d r e s s 0 0 2 8

m e r X c o u n t s o u r c e s e l e c t i o n b i

0 : f ( X

I N

) / 1 6 ( f ( X

1 : f ( X

I N

)

N o t u s e d ( r e t u r n “ 0 ” w h e n r e a d )

T i m e r Y o p e r a t i n g m o d e b i t s

b 5 b 4

0 0 : T i m e r m o d e

0 1 : P e r i o d m e a s u r e m e n t m o d e

1 0 : E v e n t c o u n t e r m o d e

1 1 : P u l s e w i d t h H L c o n t i n u o u s l y

m e a s u r e m e n t m o d e

1

a c t i v e e d g e s w i t c h b i t

C N T R

0 : C o u n t a t r i s i n g e d g e i n e v e n t c o u n t e r m o d e

M e a s u r e t h e f a l l i n g e d g e t o f a l l i n g e d g e

p e r i o d i n p e r i o d m e a s u r e m e n t m o d e

I n t e r r u p t f a l l i n g e d g e a c t i v e

1 : C o u n t a t f a l l i n g e d g e i n e v e n t c o u n t e r m o d e

M e a s u r e t h e r i s i n g e d g e p e r i o d i n p e r i o d

m e a s u r e m e n t m o d e

I n t e r r u p t r i s i n g e d g e a c t i v e

T i m e r Y s t o p c o n t r o l b i t

0 : C o u n t s t a r t

1 : C o u n t s t o p

r

1 6

)

C I N

) / 1 6 i n l o w - s p e e d m o d e✽)

CIN

divide d by 2.

t

Fig. 18 Structure of timer Y mode register

■Notes on CNTR1 interrupt active edge selection

CNTR1 interrupt active edge depends on the CNTR1 active edge

switch bit. However, in the pulse width HL continuously measurement mode, CNTR1 interrupt request is generated at both rising and

falling edges of CNTR1 pin input signal regardless of the setting of

CNTR1 active edge switch bit.

22

Page 23

PRELIMINARY

T i

* I n t e r n a l c l o c k φ i s X

C I N

/ 2 i n t h e l o w - s p e e d m o d e .

b

b

T i

N

d

T i

T i

T i

N

)

Notice: This is not a final specification.

Some parametric limits are subject to

change.

Timer 1, Timer 2, Timer 3

Timer 1, timer 2, and timer 3 are 8-bit timers. The count source for

each timer can be selected by the timer 123 mode register. The timer

latch value is not affected by a change of the count source. However,

because changing the count source may cause an inadvertent count

down of the timer. Therefore, rewrite the value of timer whenever the

count source is changed.

●Timer 2 write control

If the timer 2 write control bit is “0”, when the value is written in the

address of timer 2, the value is loaded in the timer 2 and the latch at

the same time.

If the timer 2 write control bit is “1”, when the value is written in the

address of timer 2, the value is loaded only in the latch. The value in

the latch is loaded in timer 2 after timer 2 underflows.

■Notes on timer 1 to timer 3

When the count source of timer 1 to 3 is changed, the timer counting

value may be changed large because a thin pulse is generated in

count input of timer. If timer 1 output is selected as the count source

of timer 2 or timer 3, when timer 1 is written, the counting value of

timer 2 or timer 3 may be changed large because a thin pulse is

generated in timer 1 output.

Therefore, set the value of timer in the order of timer 1, timer 2 and

timer 3 after the count source selection of timer 1 to 3.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

7

Fig. 19 Structure of timer 123 mode register

0

m e r 1 2 3 m o d e r e g i s t e

( T 1 2 3 M : a d d r e s s 0 0 2 9

o t u s e

m e r 2 w r i t e c o n t r o l b i

0 : W r i t e d a t a i n l a t c h a n d c o u n t e r

1 : W r i t e d a t a i n l a t c h o n l y

m e r 2 c o u n t s o u r c e s e l e c t i o n b i

0 : T i m e r 1 o u t p u t

I N

1 : f ( X

( o r f ( X

m e r 3 c o u n t s o u r c e s e l e c t i o n b i

0 : T i m e r 1 o u t p u t

1 : f ( X

m e r 1 c o u n t s o u r c e s e l e c t i o n b i

0 : f ( X

( o r f ( X

1 : f ( X

o t u s e d ( r e t u r n “ 0 ” w h e n r e a d

) / 1 6

C I N

) / 1 6 i n l o w - s p e e d m o d e * )

CI N

) / 3 2

I N

) / 1 6

C I N

) / 1 6 i n l o w - s p e e d m o d e * )

C I N

) / 3 2

r

1 6

)

t

t

t

t

23

Page 24

PRELIMINARY

P

S

P

S

Y

P

RXD

P

TXD

f ( X

)

F/F

r

A d d

R

)

R

)

S h i f

k

Serial I/O

Add

C

B R G

D

Add

S h i f

k

T

hif

hif

(TSC)

T

(TBE)

T

(TI)

T

Add

D

A d d

A

( f ( X

)

)

R

S

Y

D7D0D1D2D3D4D5D

RBF

T B E

T B E

T

hif

k

S

TXD

S

RXD

W

O

N

(TI)

(TBE=1)

D7D0D

D

D3D4D5D

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

SERIAL I/O

Serial I/O can be used as either clock synchronous or asynchronous

(UART) serial I/O. A dedicated timer (baud rate generator) is also

provided for baud rate generation.

ata bus

r e s s 0 0 1

R e c e i v e b u f f e r r e g i s t e

44/

6/

C L K

4

c o u n t s o u r c e s e l e c t i o n b i

i n l o w - s p e e d m o d e

C I N

I N

1/4

7/

R D

4

Falling - edge detector

45/

R e c e i v e s h i f t r e g i s t e r

t c l o c

clock selection bit

Frequency division ratio 1/(n+1)

t

Baud rate generato r

Transmit shift register

Transmi t buffer regis ter

ata bus

t c l o c

(1) Clock Synchronous Serial I/O Mode

Clock synchronous serial I/O can be selected by setting the mode

selection bit of the serial I/O control register to “1”.

For clock synchronous serial I/O, the transmitter and the receiver

must use the same clock. If an internal clock is used, transfer is started

by a write signal to the transmit/receive buffer registers.

1 6

8

ress 001

ress 001816

S e r i a l I / O c o n t r o l r e g i s t e r

e c e i v e b u f f e r f u l l f l a g ( R B F

Clock control circuit

1/4

16

Clock control circuit

r a n s m i t i n t e r r u p t s o u r c e s e l e c t i o n b i

Serial I/ O status regi s ter

r e s s 0 0 1

e c e i v e i n t e r r u p t r e q u e s t ( R I

ransmit s

ransmit interrupt request

ransmit buffer empty flag

t register s

1 6

t completion flag

t

ress 001916

Fig. 20 Block diagram of clock synchronous serial I/O

ransmit/receive s

(1/2 t o 1/20 48 of internal clock,

or an external clock)

e c e i v e e n a b l e s i g n a l

r i t e s i g n a l t o r e c e i v e / t r a n s m i t

b u f f e r r e g i s t e r ( a d d r e s s 0 0 1 8

otes 1: The transmit interrupt

t cloc

e r i a l o u t p u t

e r i a l i n p u t

R D

1 6)

=

=

0

1

T S C = 0

can be selected to occur either when the transmit buffer register has em ptied

the transmit shift operation has ended (TSC=1), by setting the transmit interrupt source selection bit (TIC) of the serial

I/O control register.

2: If data is written to the transmit buffer register when TSC=0, the transmit clock is generated continuously and serial data

is output continuously from the T

3: The receive interr upt (RI) is set when th e receive buffe r fu ll flag (RBF) bec omes “1” .

XD pin.

Fig. 21 Operation of clock synchronous serial I/O function

6

1

2

6

= 1

TSC = 1

v e r r u n e r r o r ( O E )

d e t e c t i o n

or after

24

Page 25

PRELIMINARY

f ( X

)

O E

P E

F E

D

Add

R

hif

R

)

R

)

B

r

F

)

A d d

C

D

T

hif

A d d

T

hif

hif

(TSC)

T

)

T

(TI)

Add

S T d

S P

UART

A d d

B

C h

A d d

A

BRG

T

bit

S

C l

C h

P

S

Serial I/O

P

RXD

P

TXD

T S C

R B F

T B E

TBE

RBF=1R B F

ST

D0D1S P

D0D

S T

S P

T B E

ST

D0D

S P

D

D

ST

SP

T

l

b i

S

TXD

S

RXD

R

l

T

k

N

E

Notice: This is not a final specification.

Some parametric limits are subject to

change.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

(2) Asynchronous Serial I/O (UART) Mode

Clock asynchronous serial I/O mode (UART) can be selected by clearing the serial I/O mode selection bit of the serial I/O control register

to “0”.

Eight serial data transfer formats can be selected, and the transfer

formats used by a transmitter and receiver must be identical.

The transmit and receive shift registers each have a buffer register,

ata bus

ress 001816

4/

4

46/

CLK

I N

e t e c t o

r

7 b i t s

8 b i t s

count source selection bit

1 / 4

5/

a r a c t e r l e n g t h s e l e c t i o n b i

4

a r a c t e r l e n g t h s e l e c t i o n b i

Receiv e buffer regi s ter

t

eceive s

t register

d e t e c t o

e r i a l I / O c l o c k s e l e c t i o n b i

r e q u e n c y d i v i s i o n r a t i o 1 / ( n + 1

a u d r a t e g e n e r a t o

r e s s 0 0 1

ST/SP/PA generator

ransmit s

t

Transmi t buffer regis ter

a t a b u

s

r

r e s s 0 0 1

but the two buffers have the same address in memory . Since the shift

register cannot be written to or read from directly, transmit data is