Page 1

To all our customers

Regarding the change of names mentioned in the document, such as Mitsubishi

Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas

Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog

and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.)

Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi

Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names

have in fact all been changed to Renesas Technology Corp. Thank you for your understanding.

Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been

made to the contents of the document, and these changes do not constitute any alteration to the

contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices

and power devices.

Renesas Technology Corp.

Customer Support Dept.

April 1, 2003

Page 2

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

GENERAL DESCRIPTION

The 3885 group is the 8-bit microcomputer based on the 740 family core technology.

The 3885 group is designed for Keyboard Controller for the note

book PC.

The multi-master I2C-bus interface can be added by option.

FEATURES

<Microcomputer mode>

●Basic machine-language instructions ...................................... 71

●Minimum instruction execution time .................................. 0.5 µs

(at 8 MHz oscillation frequency)

●Memory size

ROM ................................................................. 32K to 60K bytes

RAM ...............................................................1024 to 2048 bytes

●Programmable input/output ports ............................................ 72

●Software pull-up transistors ....................................................... 8

●Interrupts ................................................. 22 sources, 16 vectors

●Timers............................................................................. 8-bit ✕ 4

●Watchdog timer ............................................................ 16-bit ✕ 1

●PWM output.................................................................. 14-bit ✕ 2

●Serial I/O....................... 8-bit ✕ 1(UART or Clock-synchronized)

●Multi-master I2C bus interface (option) ........................ 1 channel

●LPC interface.............................................................. 2 channels

●Serialized IRQ .................................................................. 3 factor

●A-D converter ............................................... 10-bit ✕ 8 channels

●D-A converter ................................................. 8-bit ✕ 2 channels

●Comparator circuit ...................................................... 8 channels

●Clock generating circuit..................................... Built-in 2 circuits

(connect to external ceramic resonator or quartz-crystal oscillator)

●Power source voltage................................................ 3.0 to 3.6 V

●Power dissipation

In high-speed mode ..........................................................20 mW

(at 8 MHz oscillation frequency, at 3.3 V power source voltage)

In low-speed mode ......................................................... 330 mW

(at 32 kHz oscillation frequency, at 3.3 V power source voltage)

●Operating temperature range....................................–20 to 85°C

<Flash memory mode>

●Supply voltage................................................. VCC = 3.3 ± 0.3V

●Program/Erase voltage .................................VPP = 5.0 V ± 10 %

●Programming method...................... Programming in unit of byte

●Erasing method

Parallel I/O mode

CPU reprogramming mode

●Program/Erase control by software command

●Number of times for programming/erasing ............................100

●Operating temperature range (at programming/erasing)

........................................................................Room temperature

APPLICATION

Note book PC

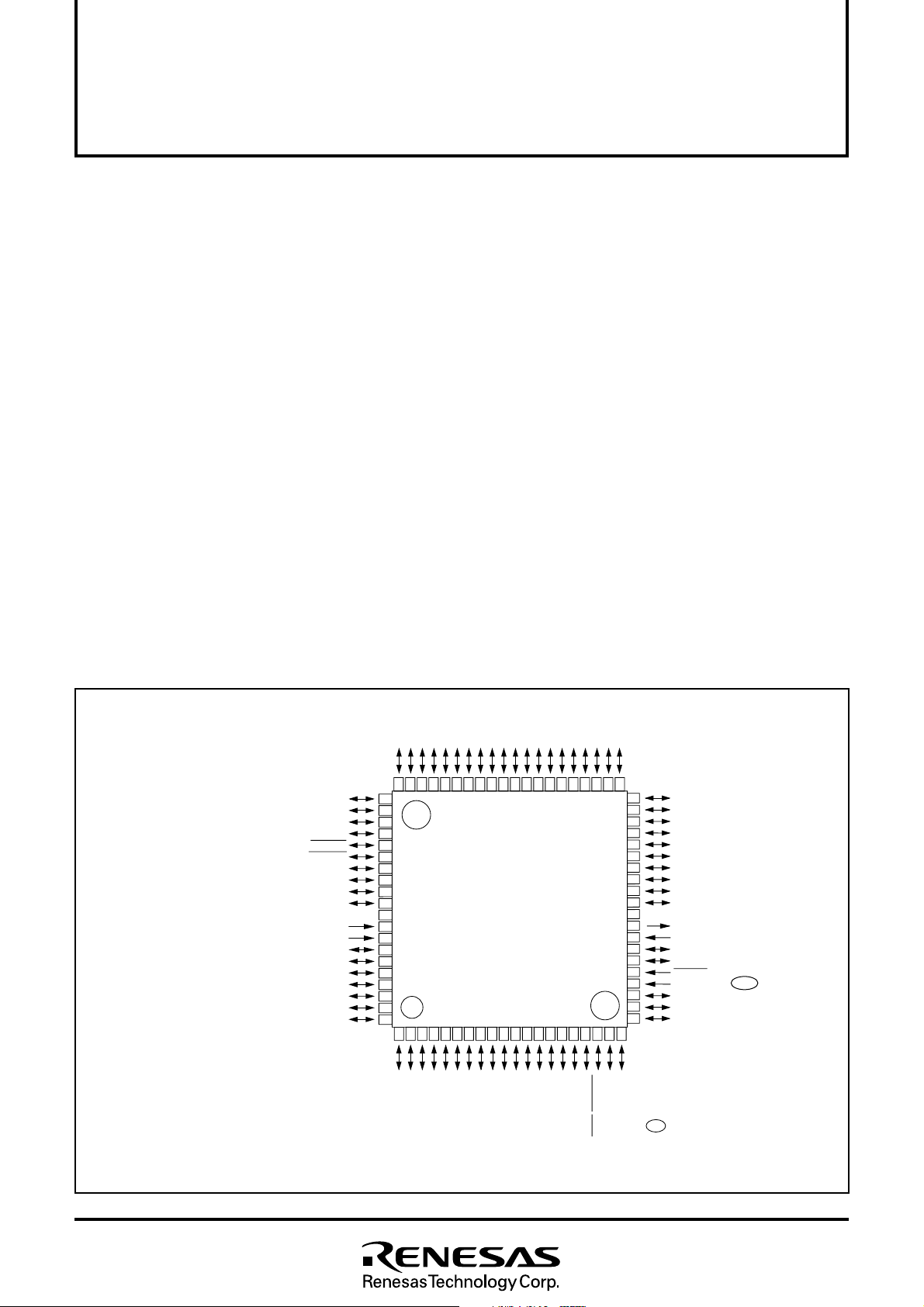

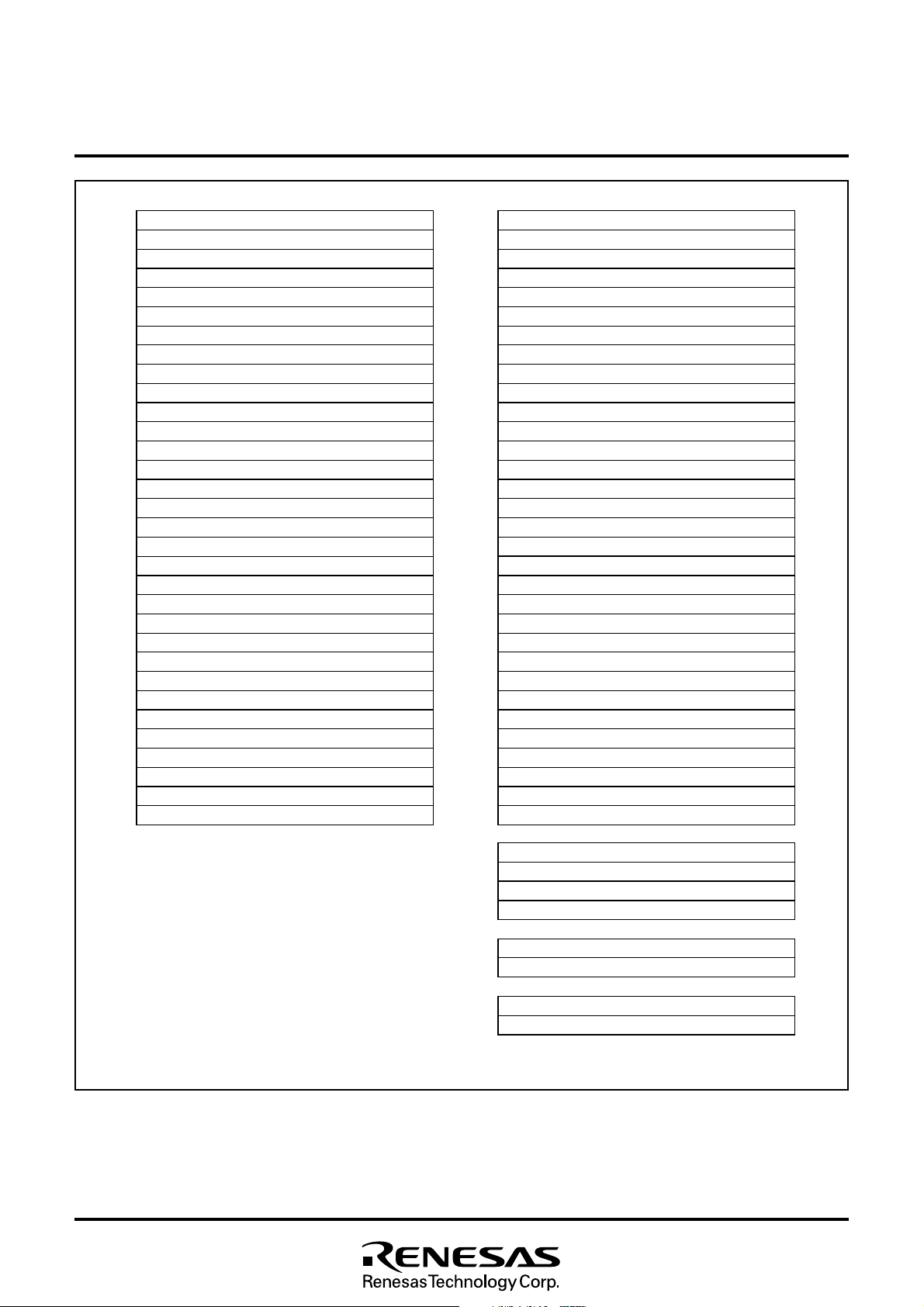

PIN CONFIGURATION (TOP VIEW)

P31/PWM10

P30/PWM00

7/SERIRQ

P8

P86/LCLK

P8

5/LRESET

P84/LFRAME

P83/LAD3

P82/LAD2

P81/LAD1

P80/LAD0

VCC

VREF

SS

AV

P67/AN7

P66/AN6

P65/AN5

P64/AN4

P63/AN3

P62/AN2

P61/AN1

0

6

3

5

2

P3

P34P3

P3

60

59

58

57

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

1

0

/AN

0

P6

56

M38857M8-XXXHP

M38858MC-XXXHP

M38859M8-XXXHP

M38859FFHP

5

3

2

4

31

41

CL

DA

/S

/S

7

6

/INT

/INT

4

5

P7

P7

P7

P7

2

3

1

7

P0

P3

P3

55

54

6

7

2

21

P7

/INT

3

P7

P04P05P06P07P11P12P13P14P1

P0

P0

P0

48

49

51

53

52

50

9

8

0

1

P7

P7

11

10

01

11

/PWM

/PWM

1

2

/DA

/DA

6

7

P5

P5

13

12

0

1

/CNTR

/CNTR

4

5

P5

P5

Package type : 80P6Q-A

47

14

40

/INT

3

P5

0

P1

46

15

30

/INT

2

P5

45

16

20

/INT

1

P5

44

43

17

18

5

/INT

0

P5

/CLKRUN

RDY

/S

7

P4

5

41

42

40

P16

39

P17

38

P20/CMPREF

37

P21

36

P22

35

P2

3

4(LED0)

P2

5(LED1)

P2

P26(LED2)

P27(LED3)

VSS

XOUT

XIN

P40/XCOUT

P41/XCIN

RESET

CNVSS

P42/INT0

P43/INT1

P44/RXD

: Flash memory version

VPP

19

CLK

/S

6

P4

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

XD

/T

5

P4

Fig. 1 Pin configuration

1

Page 3

MITSUBISHI MICROCOMPUTERS

N

T

0

,

C

N T

R

0

C

N T

R

1

R

E

F

V

S

S

R

A

M

R

O

M

C

P

U

A

S

C

C

P

S

V

S

S

3

0

R

E S E

T

5

V

C

C

7

1

2

4

C

N

V

S

S

P

5 ( 8

)

P

7 ( 8

)

2

6

3

7

P

8 ( 8

)

P

6 ( 8

)

7

4

7

6

8

8

0

7

5

7

7

9

1

7

2

3

I

N

2

8

9

S

I / O ( 8

)

D

-

A

c

o n v e r t e r

2

(

8

)

e

s

e

t

i

n

p

u

t

C

l o c k g e n e r a t i n g c i r c u i

t

a

i

n

-

c

l

o

c

k

n

p

u

t

M

a i n - c l o c

k

o

u t p u

t

A

-

D

c

o

n

v

e

r

t

e

r

(

1

0

)

T

i m e r Y ( 8

)

T

i m e r X ( 8

)

P

r e s c a l e r 1 2 ( 8

)

P

r e s c a l e r X ( 8

)

P

r e s c a l e r Y ( 8

)

T

i m e r 1 ( 8

)

T

i m e r 2 ( 8

)

I

/

O

p

o

r

t

P

5

I

/ O p o r t P

7

I

/ O p o r t P

8

I

/

O

p

o

r

t

P

6

S

u b - c l o c

k

i

n p u

t

O

U

T

X

C

I

N

C

O

U

T

S

u b - c l o c

k

o

u t p u

t

W

a t c h d o

g

t

i

m

e

r

R

e s e

t

0

(

8

)

P

1 ( 8

)

P

2 ( 8

)

P

3 ( 8

)

I

/ O p o r t P

0

/

O

p

o

r

t

P

1

I

/ O p o r t P

2

I

/ O p o r t P

3

K

e y - o n

w

a k e - u

p

C

I

N

C

O U

T

P

4 ( 8

)

/

O

p

o

r

t

P

4

C

o m p a r a t o

r

I

N

T

1

W

M

0

(

1

4

)

P

W M 1 ( 1 4

)

W

M

0

0

,

W

M

0

1

P

W

M

1

0

,

P

W

M

1

1

P

C

i

n

t

e

r

f

a

c

e

I

C

S

C

L

S

D

A

N

T

4

1

I

N

T

2

1

,

N

T

3

1

,

6

3

5

6

7

9

4

6

6

8

0

D

-

A

c

o n v e r t e r

1

(

8

)

1

0

2

4

1

6

1

3

1

5

1

7

8

2

0

2

2

6

1

9

2

1

3

2

7

5

5

7

5

9

1

6

5

8

0

2

3

1

3

5

3

7

2

4

3

6

3

8

9

4

1

3

5

0

2

4

4

6

7

8

9

5

0

5

1

2

3

4

N

T

4

0

,

I

N

T

2

0

,

I

N

T

3

0

,

N

T

5

C

L K R U

N

C

M

P

R

E

F

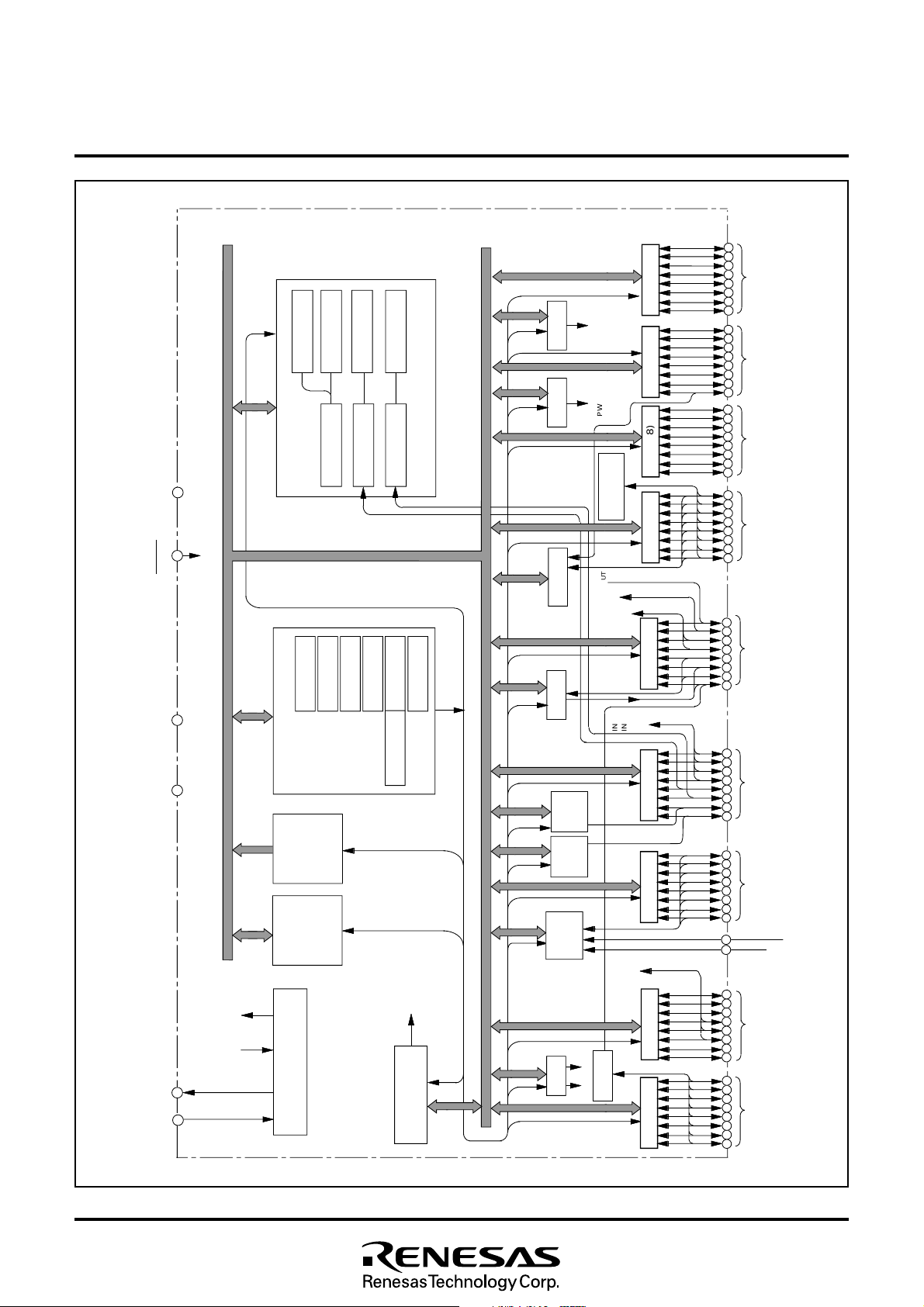

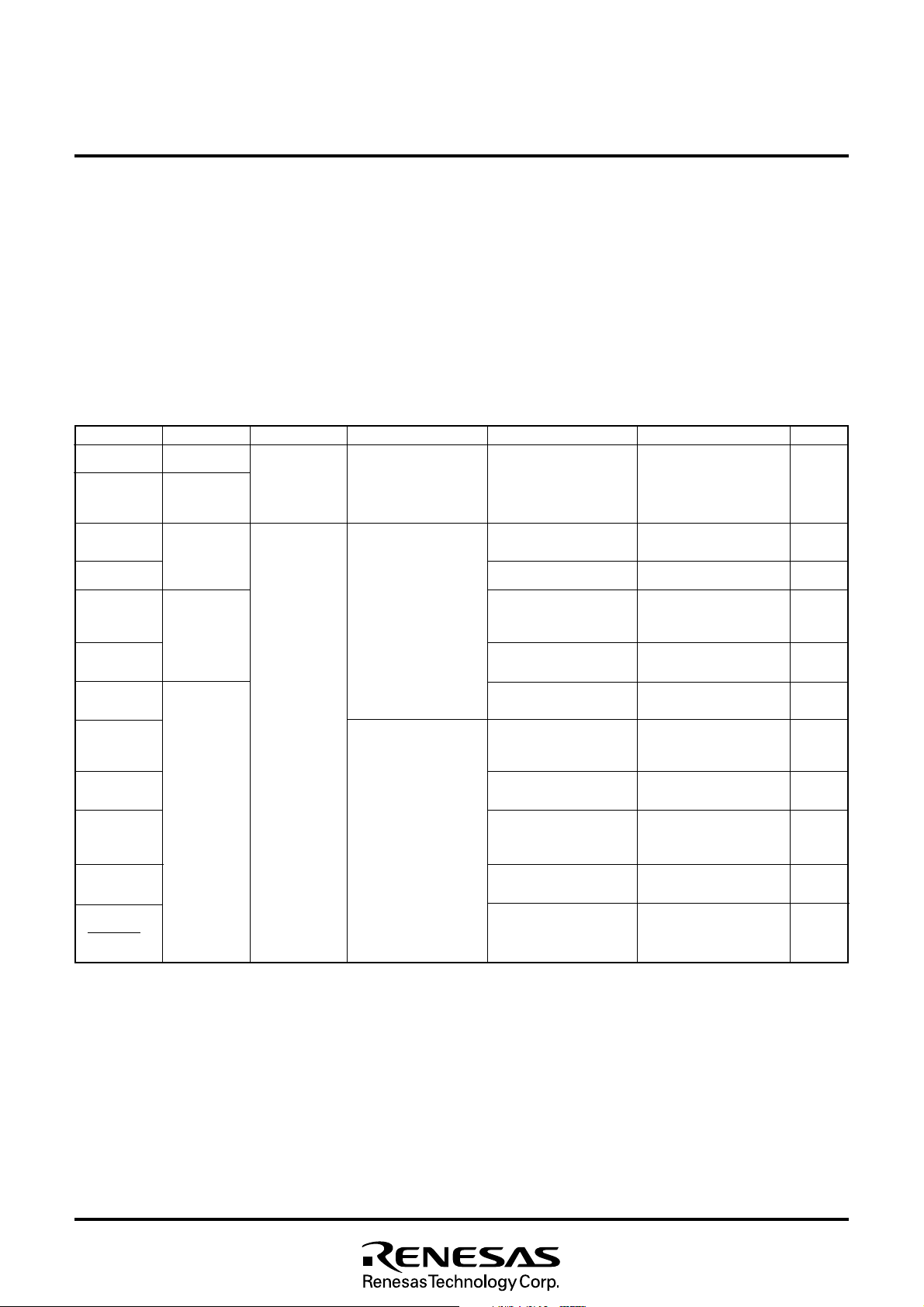

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

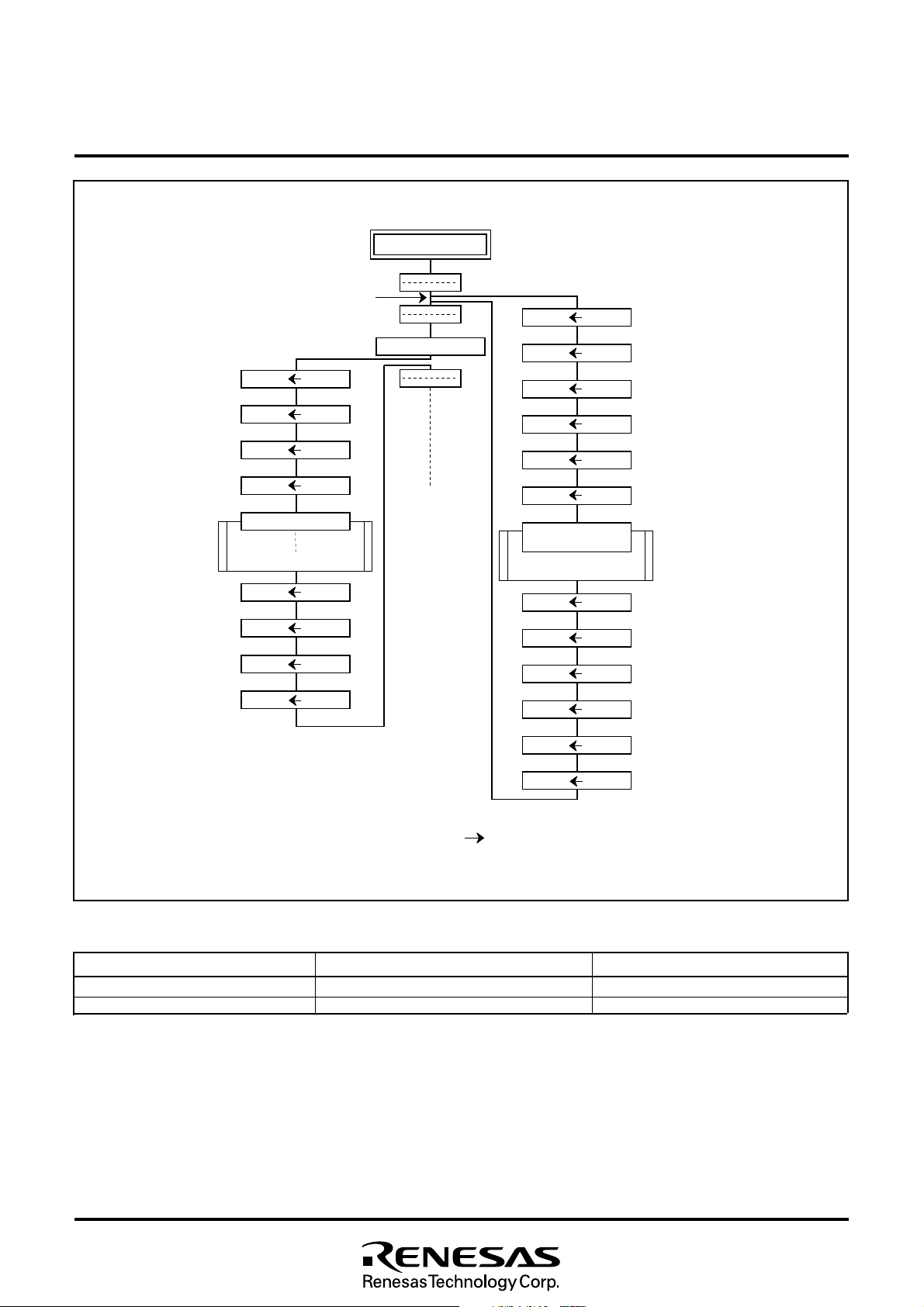

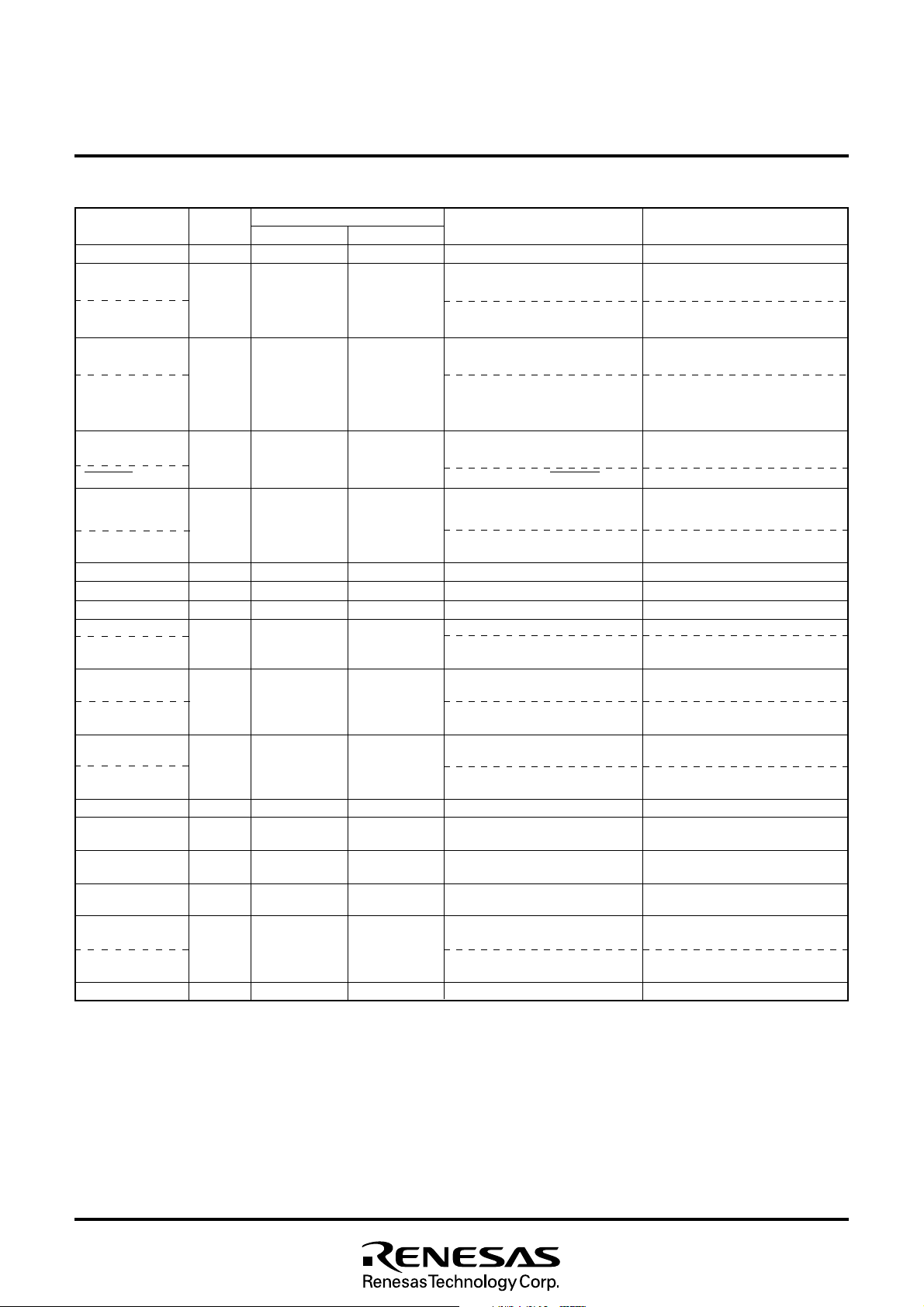

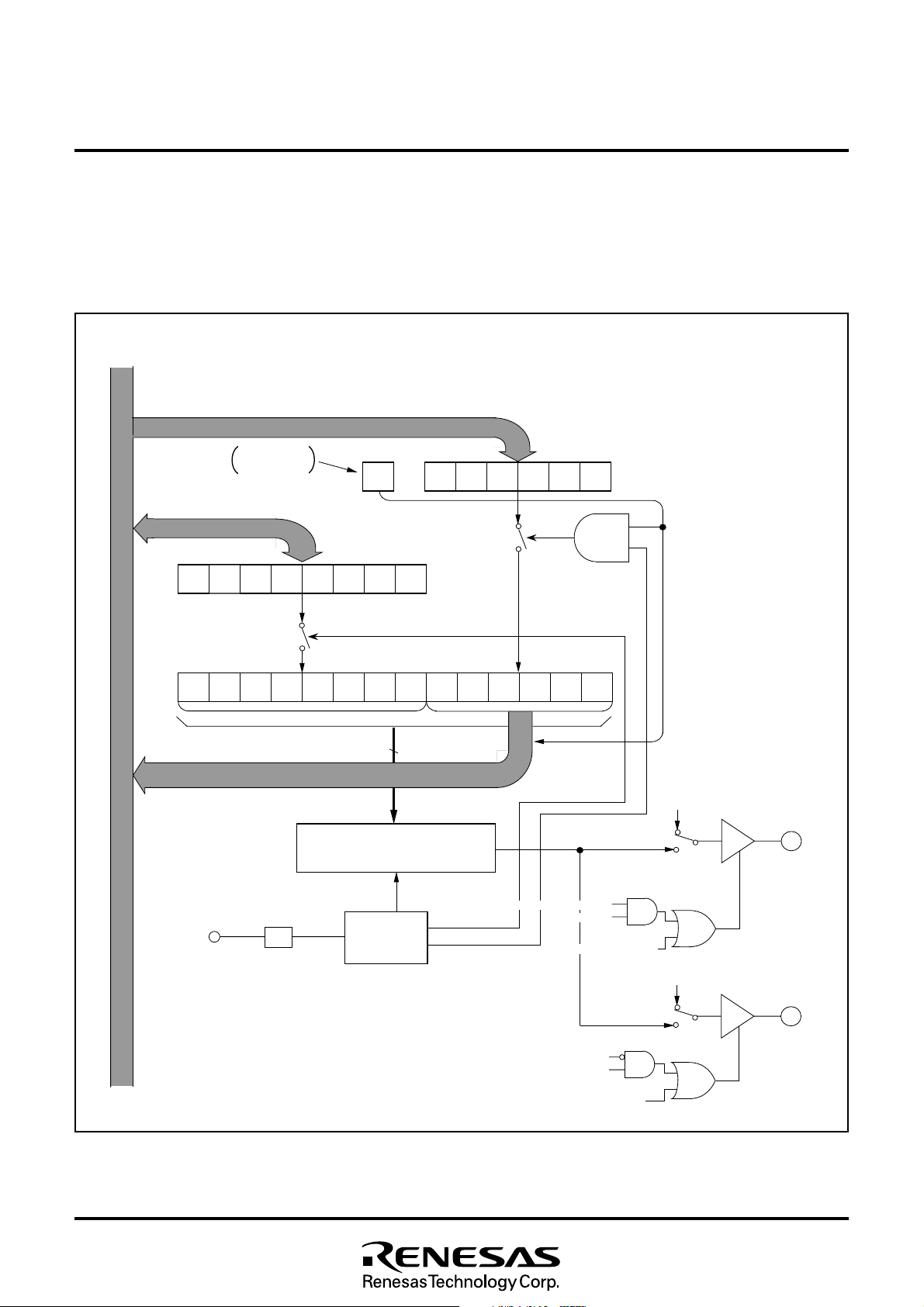

FUNCTIONAL BLOCK DIAGRAM (Package : 80P6Q-A)

Fig. 2 Functional block diagram

2

Page 4

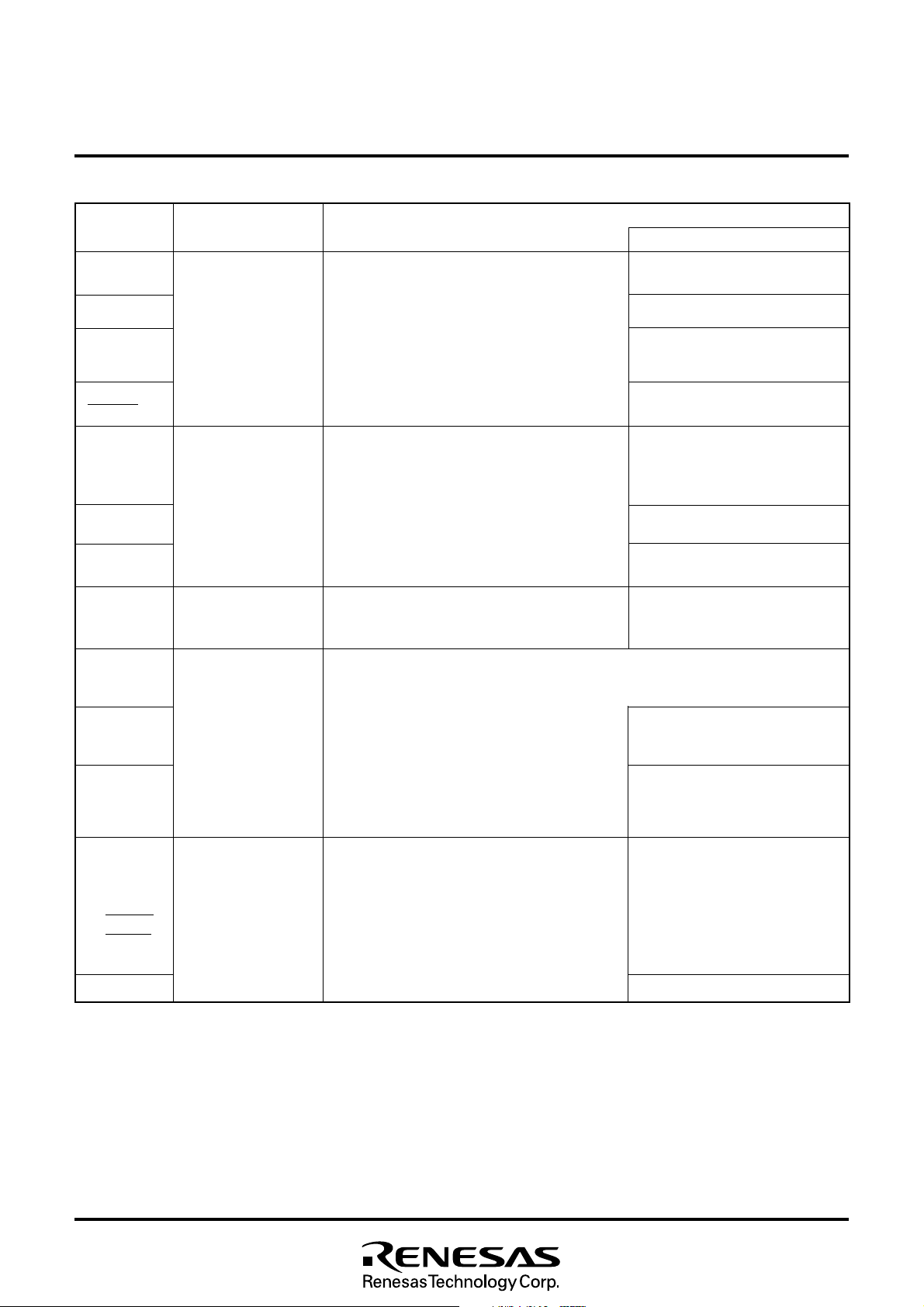

PIN DESCRIPTION

Table 1 Pin description (1)

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

VCC, VSS

CNVSS

VREF

AVSS

RESET

XIN

XOUT

P00–P07

P10–P17

P20/CMPREF

P21–P27

P30/PWM00

P31/PWM10

P32–P37

NamePin

Power source

CNVSS input

Reference voltage

Analog power source

Reset input

Clock input

Clock output

I/O port P0

I/O port P1

I/O port P2

I/O port P3

Functions

•Apply voltage of 3.0 V ±10 % to Vcc, and 0 V to Vss.

•Connected to V

•In the flash memory version, this pin functions as the V

•Reference voltage input pin for A-D and D-A converters.

•Analog power source input pin for A-D and D-A converters.

•Connect to V

•Reset input pin for active “L”.

•Input and output pins for the clock generating circuit.

•Connect a ceramic resonator or quartz-crystal oscillator between the XIN and XOUT pins to set

the oscillation frequency.

•When an external clock is used, connect the clock source to the XIN pin and leave the XOUT

pin open.

•8-bit I/O port.

•I/O direction register allows each pin to be individually programmed as either input or output.

•CMOS compatible input level.

•CMOS 3-state output structure or N-channel open-drain output structure.

•8-bit I/O port.

•I/O direction register allows each pin to be individually programmed as either input or output.

•CMOS compatible input level.

•CMOS 3-state output structure or N-channel open-drain output structure.

•8-bit I/O port.

•I/O direction register allows each pin to be individually

programmed as either input or output.

•CMOS compatible input level.

•CMOS 3-state output structure.

•P24 to P27 (4 bits) are enabled to output large current for LED drive.

•8-bit I/O port.

•I/O direction register allows each pin to be individually

programmed as either input or output.

•CMOS compatible input level.

•CMOS 3-state output structure.

•These pins function as key-on wake-up and compara-

tor input.

•These pins are enabled to control pull-up.

SS.

SS.

Function except a port function

PP power source input pin.

•Comparator reference power source

input pin

•Key-on wake-up input pins

•Comparator input pins

•PWM output pins

•Key-on wake-up input pins

•Comparator input pins

3

Page 5

Table 2 Pin description (2)

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

P4

0/XCOUT

P41/XCIN

P42/INT0

P43/INT1

P44/RxD

P45/TxD

P46/SCLK

P47/SRDY

/CLKRUN

P50/INT5

P51/INT20

P52/INT30

P53/INT40

P54/CNTR0

P55/CNTR1

P56/DA1/PWM01

P57/DA2/PWM11

P60/AN0–P67/AN

P70

P71

P72

P73/INT21

P74/INT31

P75/INT41

P76/SDA

P77/SCL

P80/LAD0

P81/LAD1

P82/LAD2

P83/LAD3

P84/LFRAME

P85/LRESET

P86/LCLK

P87/SERIRQ

I/O port P4

I/O port P5

7

I/O port P6

I/O port P7

I/O port P8

NamePin

•8-bit I/O port with the same function as port P0

<Input level>

CMOS compatible input level

<Output level>

P40, P41 : CMOS 3-state output structure

P42-P47 : CMOS 3-state output structure or N-

channel open-drain output structure

•Each pin level of P42 to P46 can be read even in

output port mode.

•8-bit I/O port with the same function as port P0

•CMOS compatible input level

•CMOS 3-state output structure

•8-bit I/O port with the same function as port P0

•CMOS compatible input level.

•CMOS 3-state output structure.

•8-bit CMOS I/O port with the same function as port P0

<Input level>

P70–P75 : CMOS compatible input level or

TTL compatible input level

P76, P77 : CMOS compatible input level or

SMBUS input level in the I2C-BUS

interface function,

<Output structure>

N-channel open-drain output structure

•Each pin level of P70 to P75 can be read evev in

output port mode.

•8-bit CMOS I/O port with the same function as port

P0

•CMOS compatible input level.

•CMOS 3-state output structure.

Functions

Function except a port function

•Sub-clock generating circuit I/O

pins (Connect a resonator.)

•Interrupt input pins

•Serial I/O function pins

•Serial I/O function pins

•Serialized IRQ function pin

•Interrupt input pins

•Timer X, timer Y function pins

•D-A converter output pins

•PWM output pins

•A-D converter output pins

•Interrupt input pins

•I2C-BUS interface function pins

•LPC interface function pins

•Serialized IRQ function pin

4

Page 6

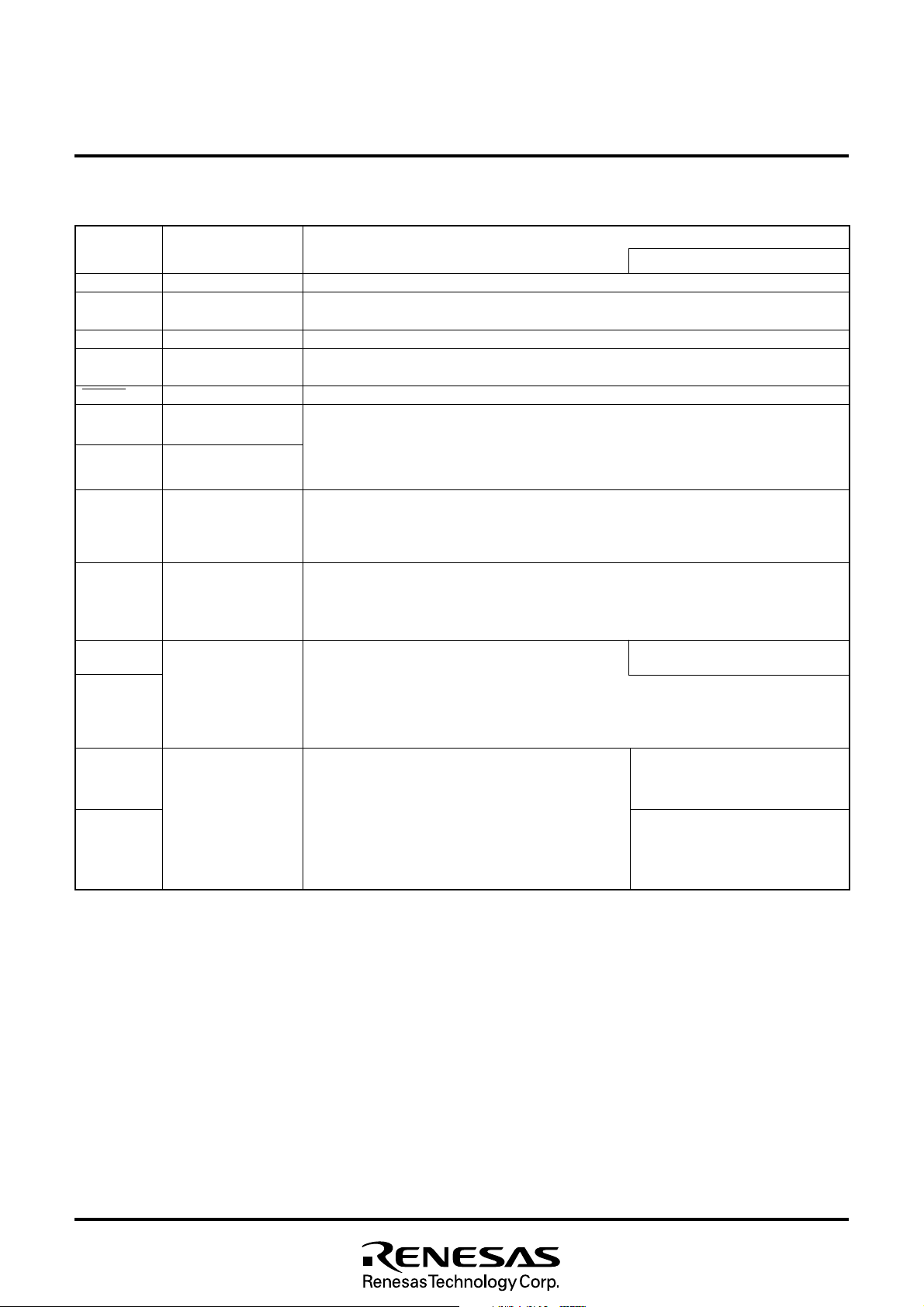

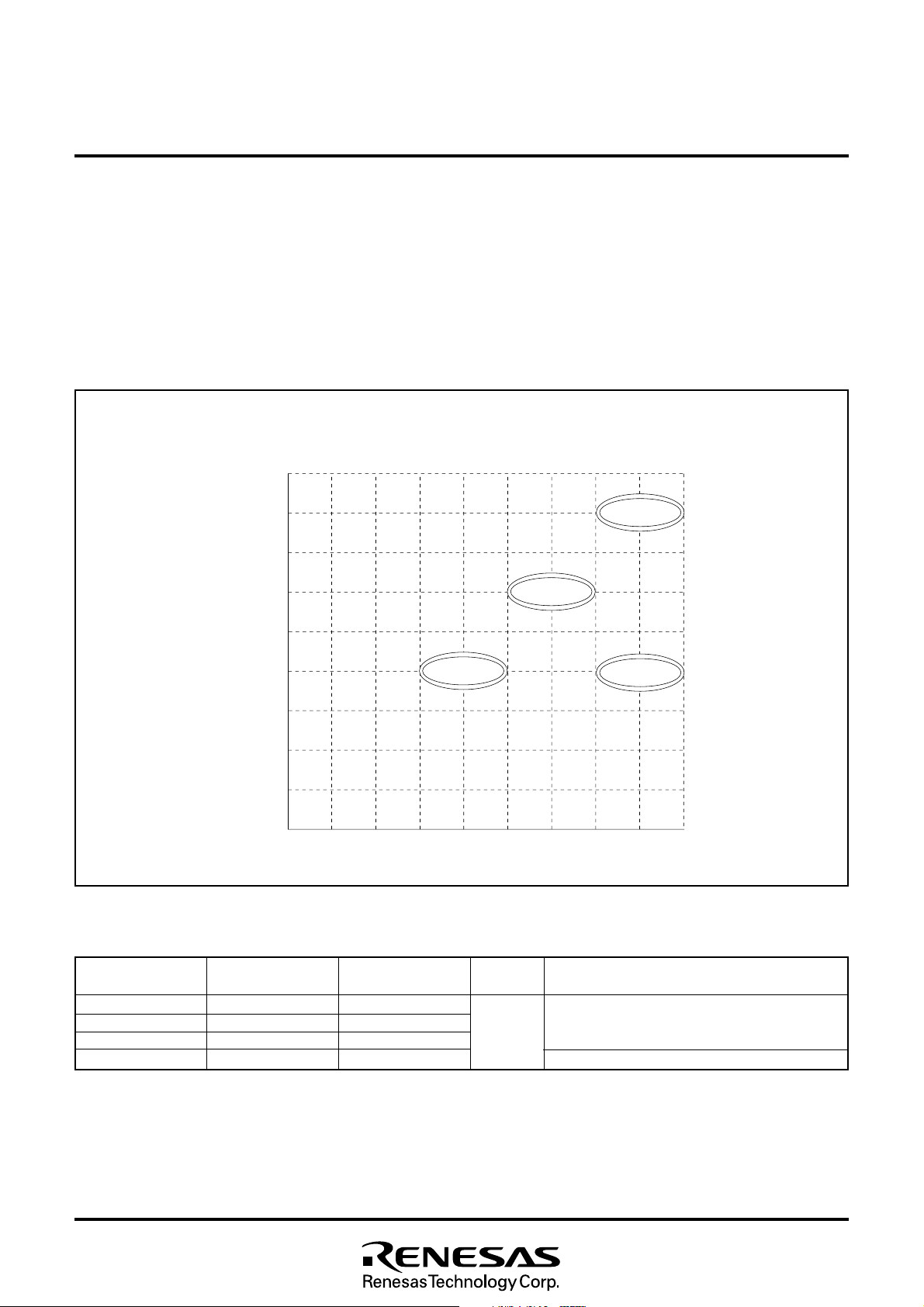

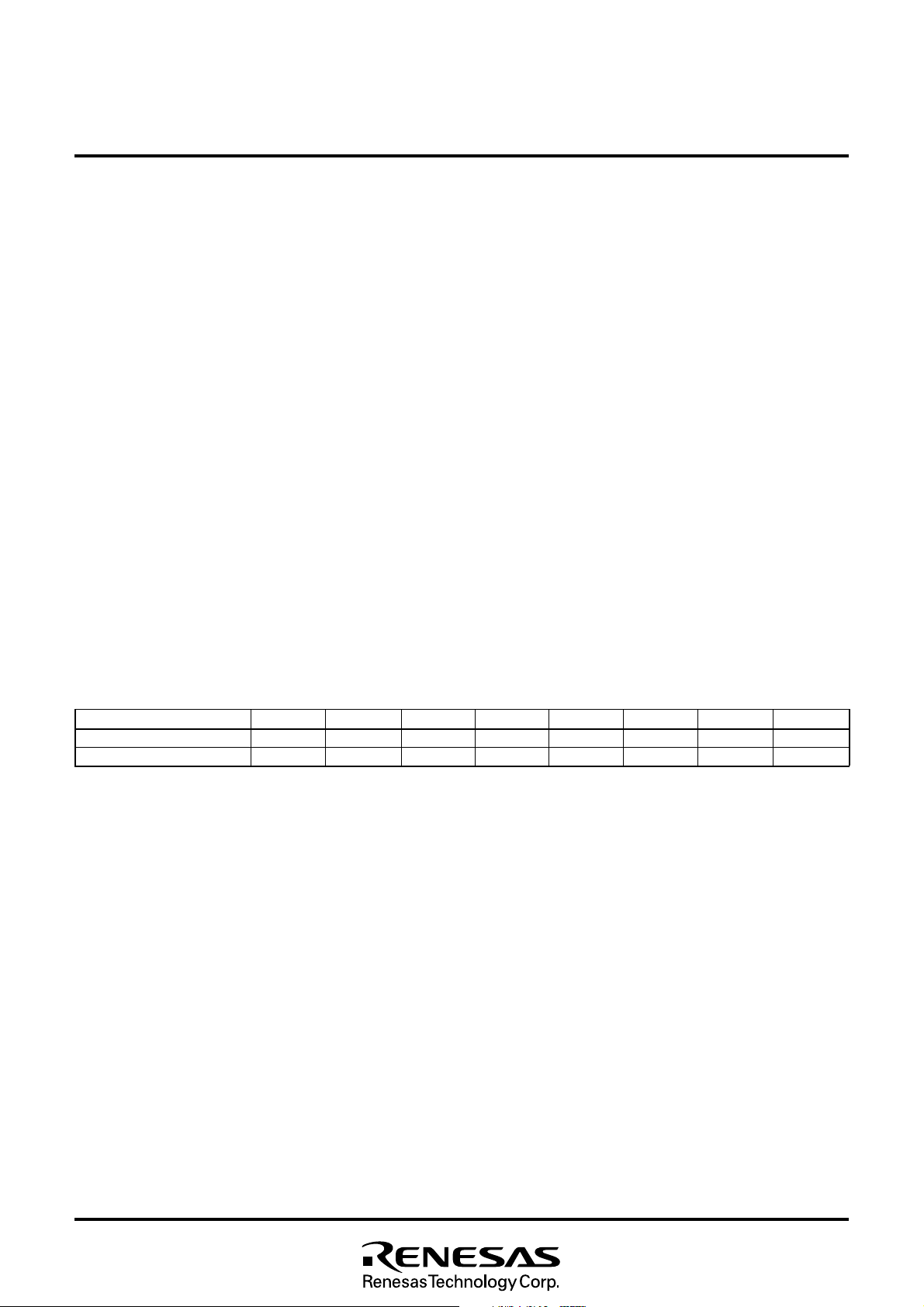

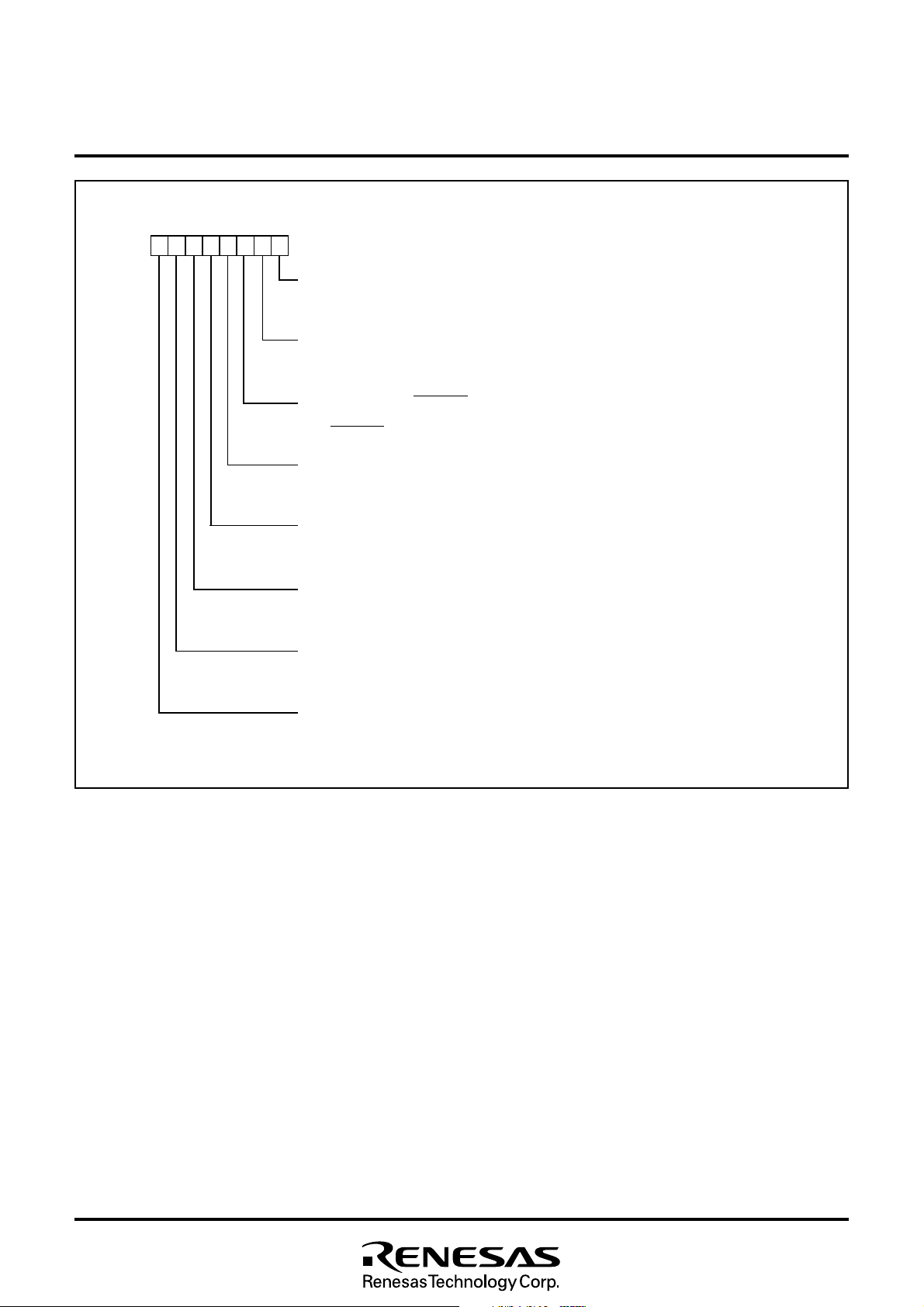

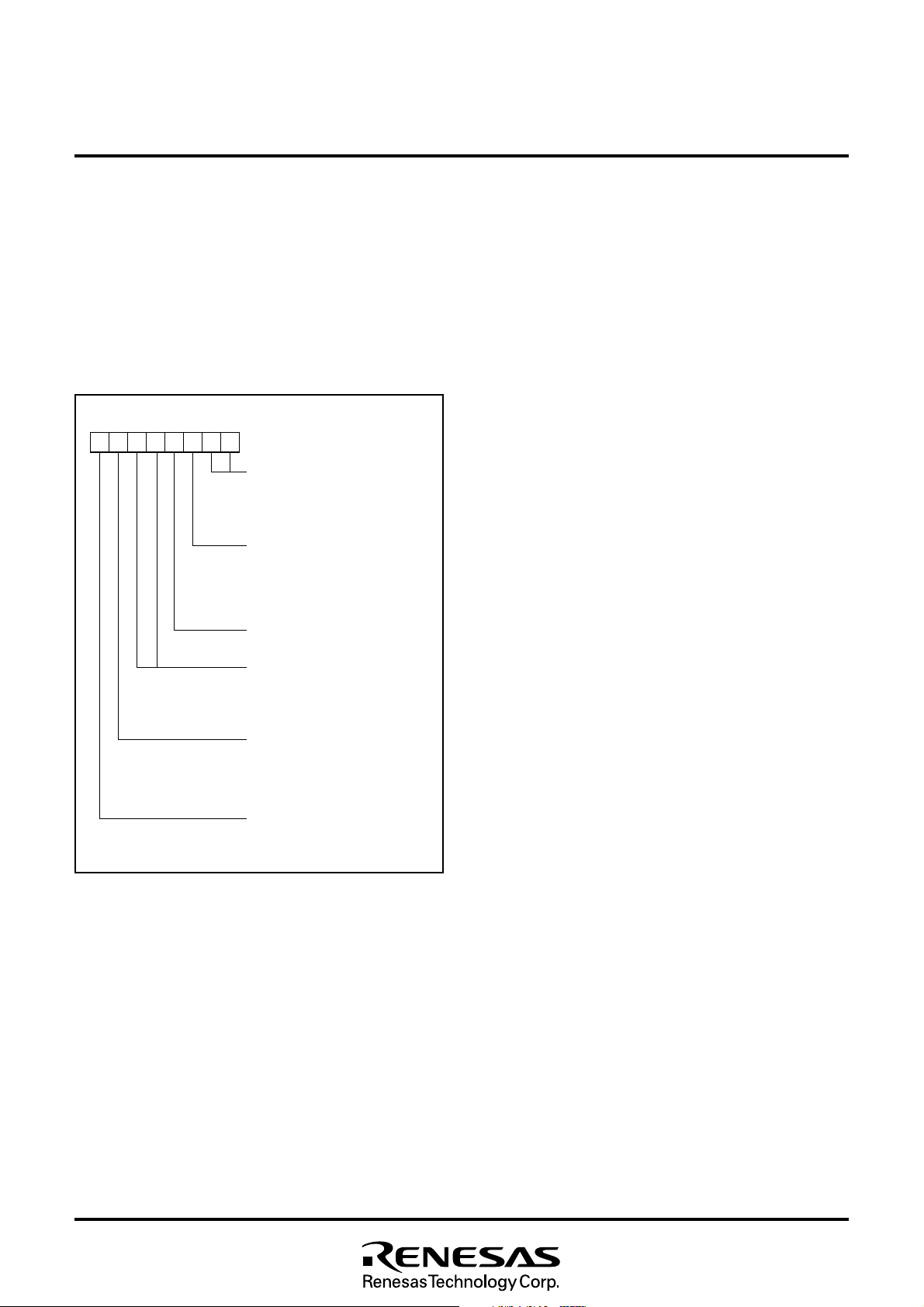

PART NUMBERING

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Product name

M3885 8 M C -XXX HP

Package type

HP : 80P6Q-A

ROM number

Omitted in the flash memory version.

ROM/Flash memory size

1

: 4096 bytes

2

: 8192 bytes

3

: 12288 bytes

4

: 16384 bytes

5

: 20480 bytes

6

: 24576 bytes

7

: 28672 bytes

8

: 32768 bytes

The first 128 bytes and the last 2 bytes of ROM are reserved

areas ; user cannot use those bytes.

However, they can be programmed or erased in the flash

memory version, so that the users can use them.

9: 36864 bytes

A: 40960 bytes

B: 45056 bytes

C: 49152 bytes

D: 53248 bytes

E: 57344 bytes

F: 61440 bytes

Fig. 3 Part numbering

Memory type

M

: Mask ROM version

F

: Flash memory version

RAM size

: 192 bytes

0

: 256 bytes

1

: 384 bytes

2

: 512 bytes

3

: 640 bytes

4

: 768 bytes

5

: 896 bytes

6

: 1024 bytes

7

: 1536 bytes

8

: 2048 bytes

9

5

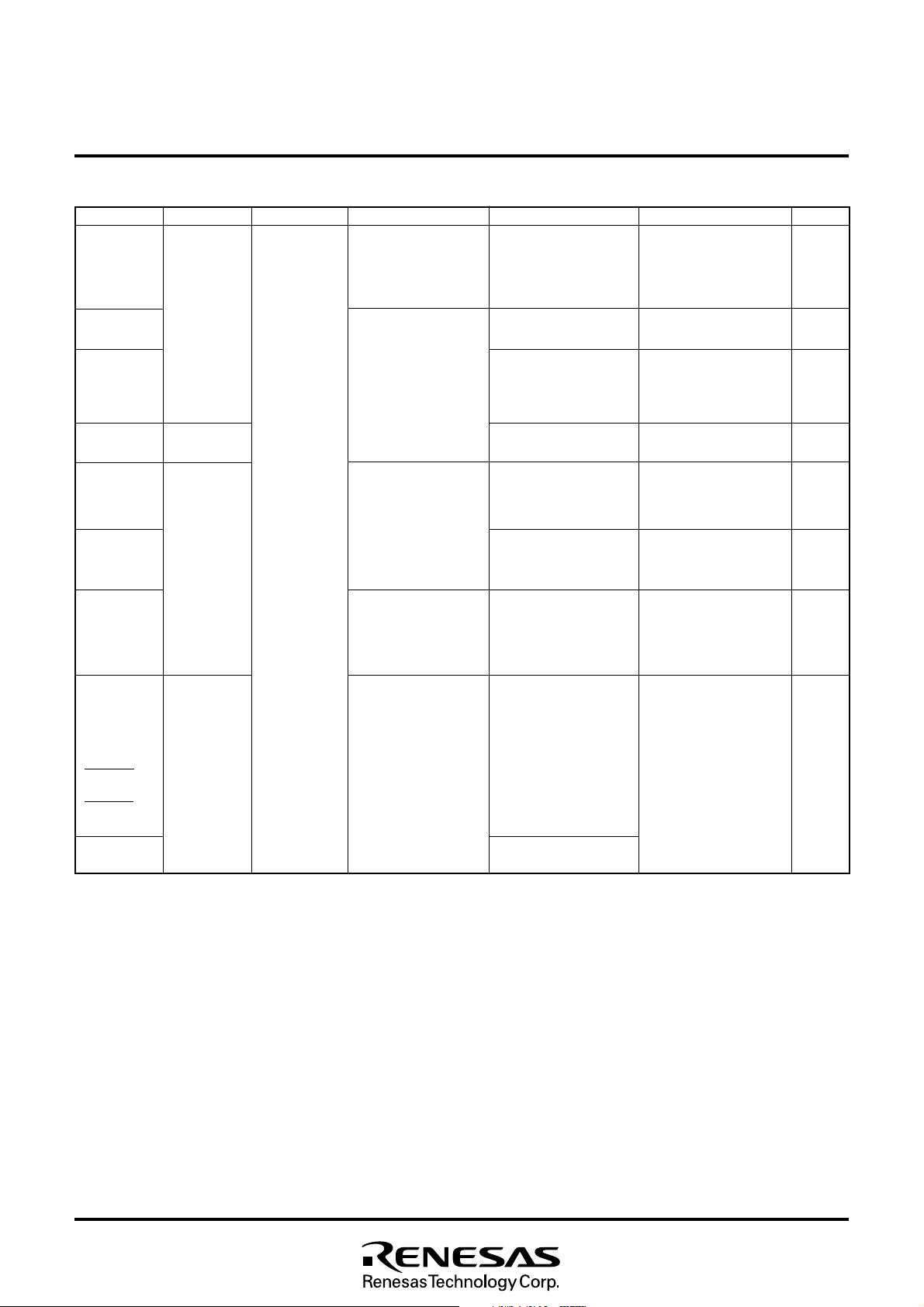

Page 7

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

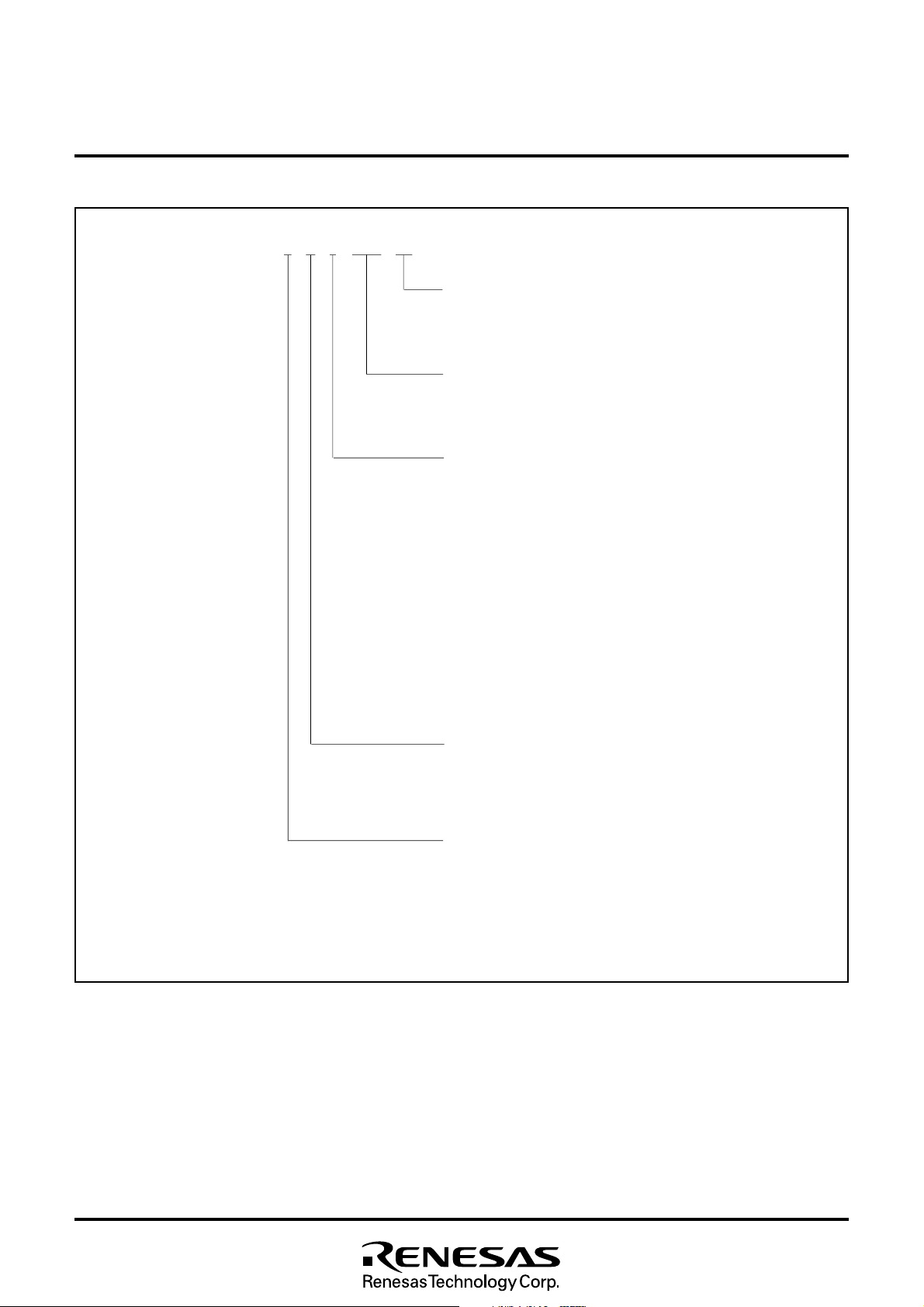

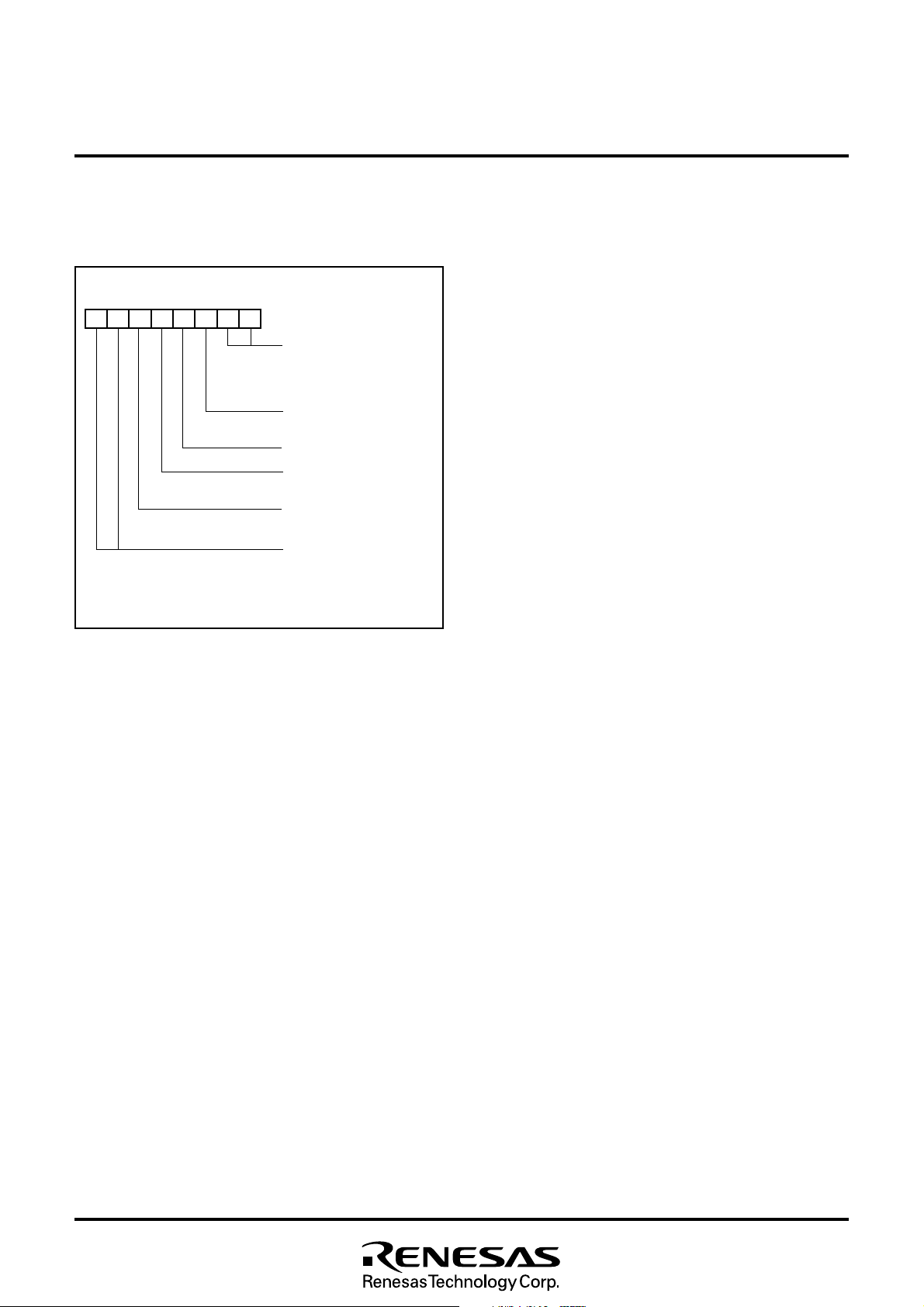

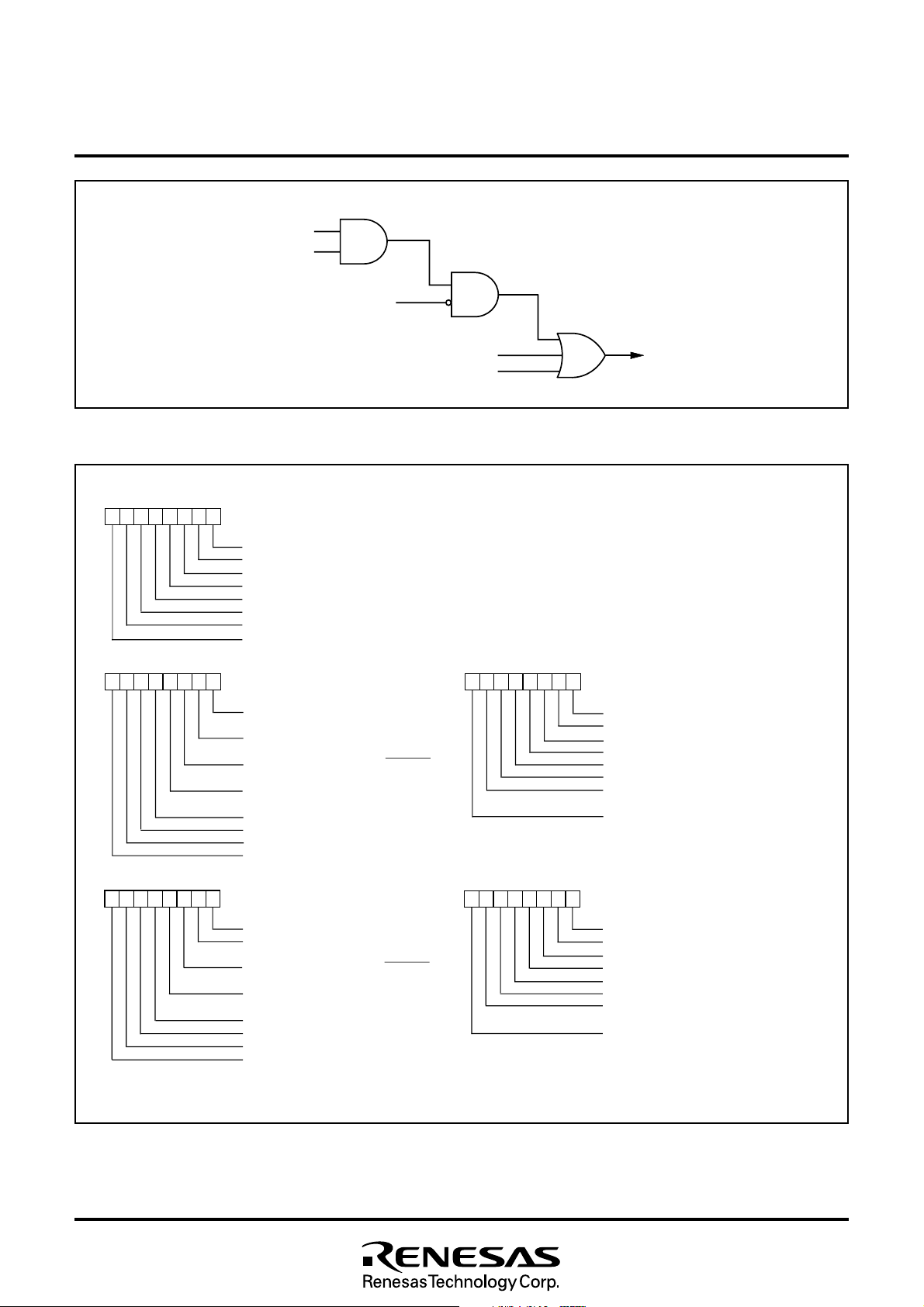

GROUP EXPANSION

Mitsubishi plans to expand the 3885 group as follows.

Memory Type

Support for mask ROM, flash memory version.

Memory Size

ROM size ........................................................... 32 K to 60 K bytes

RAM size ..........................................................1024 to 2048 bytes

Memory Expansion

ROM size (bytes)

ROM

external

60K

56K

48K

40K

Packages

80P6Q-A ..................................0.5 mm-pitch plastic molded LQFP

M38859FF

M38858MC

Fig. 4 Memory expansion plan

Table 3 Products plan list

Product name

M38857M8-XXXHP

M38858MC-XXXHP

M38859M8-XXXHP

M38859FFHP

(P) ROM size (bytes)

ROM size for User in ( )

32768 (32638)

49152 (19022)

32768 (32638)

32K

24K

16K

8K

61440

256 512 768

RAM size (bytes)

1024

1536

2048

2048

M38857M8

1024 1280 1536 1792 2048

RAM size (bytes)

Package

80P6Q-A

Mask ROM version

Flash memory version

M38859M8

As of May 2002

Remarks

6

Page 8

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

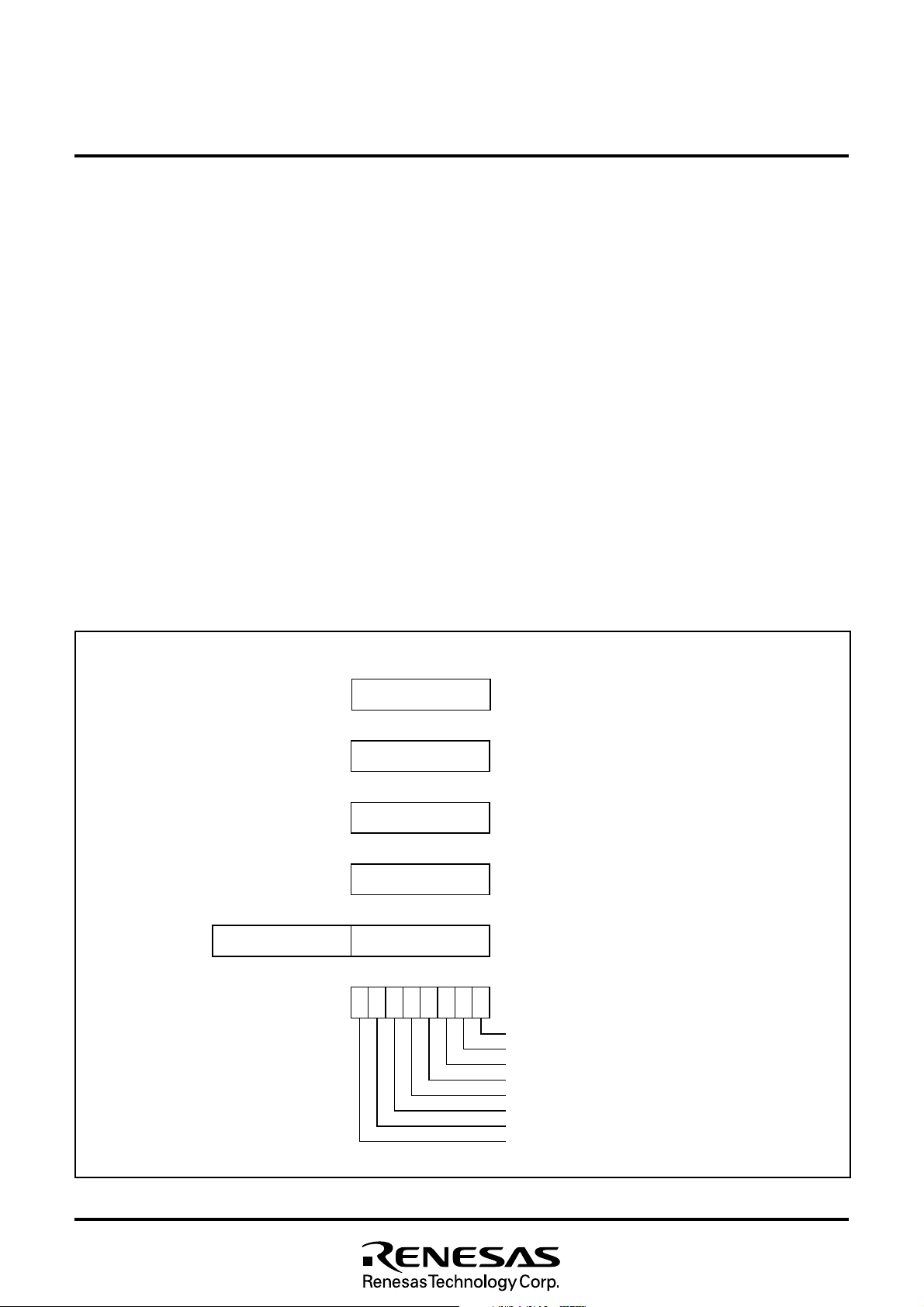

FUNCTIONAL DESCRIPTION

CENTRAL PROCESSING UNIT (CPU)

The 3885 group uses the standard 740 Family instruction set. Refer to the table of 740 Family addressing modes and machine

instructions or the 740 Family Software Manual for details on the

instruction set.

Machine-resident 740 Family instructions are as follows:

The FST and SLW instructions cannot be used.

The STP, WIT, MUL, and DIV instructions can be used.

[Accumulator (A)]

The accumulator is an 8-bit register. Data operations such as data

transfer, etc., are executed mainly through the accumulator.

[Index Register X (X)]

The index register X is an 8-bit register. In the index addressing

modes, the value of the OPERAND is added to the contents of

register X and specifies the real address.

[Index Register Y (Y)]

The index register Y is an 8-bit register. In partial instruction, the

value of the OPERAND is added to the contents of register Y and

specifies the real address.

[Stack Pointer (S)]

The stack pointer is an 8-bit register used during subroutine calls

and interrupts. This register indicates start address of stored area

(stack) for storing registers during subroutine calls and interrupts.

The low-order 8 bits of the stack address are determined by the

contents of the stack pointer. The high-order 8 bits of the stack address are determined by the stack page selection bit. If the stack

page selection bit is “0” , the high-order 8 bits becomes “0016”. If

the stack page selection bit is “1”, the high-order 8 bits becomes

“0116”.

The operations of pushing register contents onto the stack and

popping them from the stack are shown in Figure 7.

Store registers other than those described in Figure 7 with program when the user needs them during interrupts or subroutine

calls.

[Program Counter (PC)]

The program counter is a 16-bit counter consisting of two 8-bit

registers PCH and PCL. It is used to indicate the address of the

next instruction to be executed.

b7

b0

A Accumulator

b7

b0

X Index register X

b7

b0

Y Index register Y

b7 b0

S Stack pointer

b7b15 b0

H

PC

L

Program counterPC

b7 b0

N V T B D I Z C Processor status register (PS)

Carry flag

Zero flag

Interrupt disable flag

Decimal mode flag

Break flag

Index X mode flag

Overflow flag

Negative flag

Fig. 5 740 Family CPU register structure

7

Page 9

On-going Routin

e

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

P u s h r e t u r n a d d r e s s

o n s t a c k

P O P re t u r n

a d d r e s s f r o m s t a c k

I n t e r r u p t r e q u e s t

M (S) (PCH)

( S )

M ( S )( P CL)

(S)

S u b r o u t i n e

E x e c u t e R T S

( S )

( P CL)M ( S )

( S )

( P CH)M ( S )

( S ) – 1

(S)– 1

( S ) + 1

( S ) + 1

( N o t e )

E x e c u t e J S R

M (S) (PCH)

(S)

(S) – 1

M (S) (PCL)

(S)

(S) – 1

M ( S )( P S )

(S)

(S) – 1

I n t e r r u p t

S e r v i c e R o u t i n e

E x e c u t e R T I

(S)

(S) + 1

( P S )M ( S )

(S)

(S) + 1

(PCL)M (S)

(S)

(S) + 1

Push return address

on stack

Push contents of processor

status register on stack

I Flag is set from “0” to “1”

Fetch the jump vector

POP contents of

processor status

register from stack

POP return

address

from stack

(PCH)M (S)

N o t e: C o n d i t i o n f o r a c c e p t a n c e o f a n i n t e r r u p t I n t e r r u p t e n a b l e f l a g i s “ 1 ”

Fig. 6 Register push and pop at interrupt generation and subroutine call

Table 4 Push and pop instructions of accumulator or processor status register

Push instruction to stack

Accumulator

Processor status register

Interrupt disable flag is “0”

PHA

PHP

Pop instruction from stack

PLA

PLP

8

Page 10

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

[Processor status register (PS)]

The processor status register is an 8-bit register consisting of 5

flags which indicate the status of the processor after an arithmetic

operation and 3 flags which decide MCU operation. Branch operations can be performed by testing the Carry (C) flag , Zero (Z) flag,

Overflow (V) flag, or the Negative (N) flag. In decimal mode, the Z,

V, N flags are not valid.

•Bit 0: Carry flag (C)

The C flag contains a carry or borrow generated by the arithmetic

logic unit (ALU) immediately after an arithmetic operation. It can

also be changed by a shift or rotate instruction.

•Bit 1: Zero flag (Z)

The Z flag is set if the result of an immediate arithmetic operation

or a data transfer is “0”, and cleared if the result is anything other

than “0”.

•Bit 2: Interrupt disable flag (I)

The I flag disables all interrupts except for the interrupt

generated by the BRK instruction.

Interrupts are disabled when the I flag is “1”.

•Bit 3: Decimal mode flag (D)

The D flag determines whether additions and subtractions are

executed in binary or decimal. Binary arithmetic is executed when

this flag is “0”; decimal arithmetic is executed when it is “1”.

Decimal correction is automatic in decimal mode. Only the ADC

•Bit 4: Break flag (B)

The B flag is used to indicate that the current interrupt was

generated by the BRK instruction. The BRK flag in the processor

status register is always “0”. When the BRK instruction is used to

generate an interrupt, the processor status register is pushed

onto the stack with the break flag set to “1”.

•Bit 5: Index X mode flag (T)

When the T flag is “0”, arithmetic operations are performed

between accumulator and memory. When the T flag is “1”, direct

arithmetic operations and direct data transfers are enabled

between memory locations.

•Bit 6: Overflow flag (V)

The V flag is used during the addition or subtraction of one byte

of signed data. It is set if the result exceeds +127 to -128. When

the BIT instruction is executed, bit 6 of the memory location

operated on by the BIT instruction is stored in the overflow flag.

•Bit 7: Negative flag (N)

The N flag is set if the result of an arithmetic operation or data

transfer is negative. When the BIT instruction is executed, bit 7 of

the memory location operated on by the BIT instruction is stored

in the negative flag.

Table 5 Set and clear instructions of each bit of processor status register

Set instruction

Clear instruction

C flag

SEC

CLC

Z flag

–

–

I flag

SEI

CLI

D flag

SED

CLD

B flag

–

–

T flag

SET

CLT

V flag

–

CLV

N flag

–

–

9

Page 11

[CPU Mode Register (CPUM)] 003B16

The CPU mode register contains the stack page selection bit, etc.

The CPU mode register is allocated at address 003B16.

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

b 7

1

b 0

C P U m o d e r e g i s t e r

(

C P U M : a d d r e s s

P r o c e s s o r m o d e b i t s

b 1 b 0

0 0 : S i n g l e - c h i p m o d e

0 1 : N o t a v a i l a b l e

1 0 : N o t a v a i l a b l e

1 1 : N o t a v a i l a b l e

S t a c k p a g e s e l e c t i o n b i t

0 : 0 p a g e

1 : 1 p a g e

F i x t h i s b i t t o “ 1 ” .

P o r t P 4

0 : I / O p o r t f u n c t i o n ( s t o p o s c i l l a t i n g )

1 : X

M a i n c l o c k ( X

0 : O s c i l l a t i n g

1 : S t o p p e d

M a i n c l o c k d i v i s i o n r a t i o s e l e c t i o n b i t s

b 7 b 6

0 0 : φ = f ( X

0 1 : φ = f ( X

1 0 : φ = f ( X

1 1 : N o t a v a i l a b l e

Fig. 7 Structure of CPU mode register

0

/ P 41 s w i t c h b i t

C I N

– X

C O U T

0 0 3 B

1 6

)

o s c i l l a t i n g f u n c t i o n

I N

– X

O U T

) s t o p b i t

I N

) / 2 ( h i g h - s p e e d m o d e )

I N

) / 8 ( m i d d l e - s p e e d m o d e )

C I N

) / 2 ( l o w - s p e e d m o d e )

10

Page 12

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

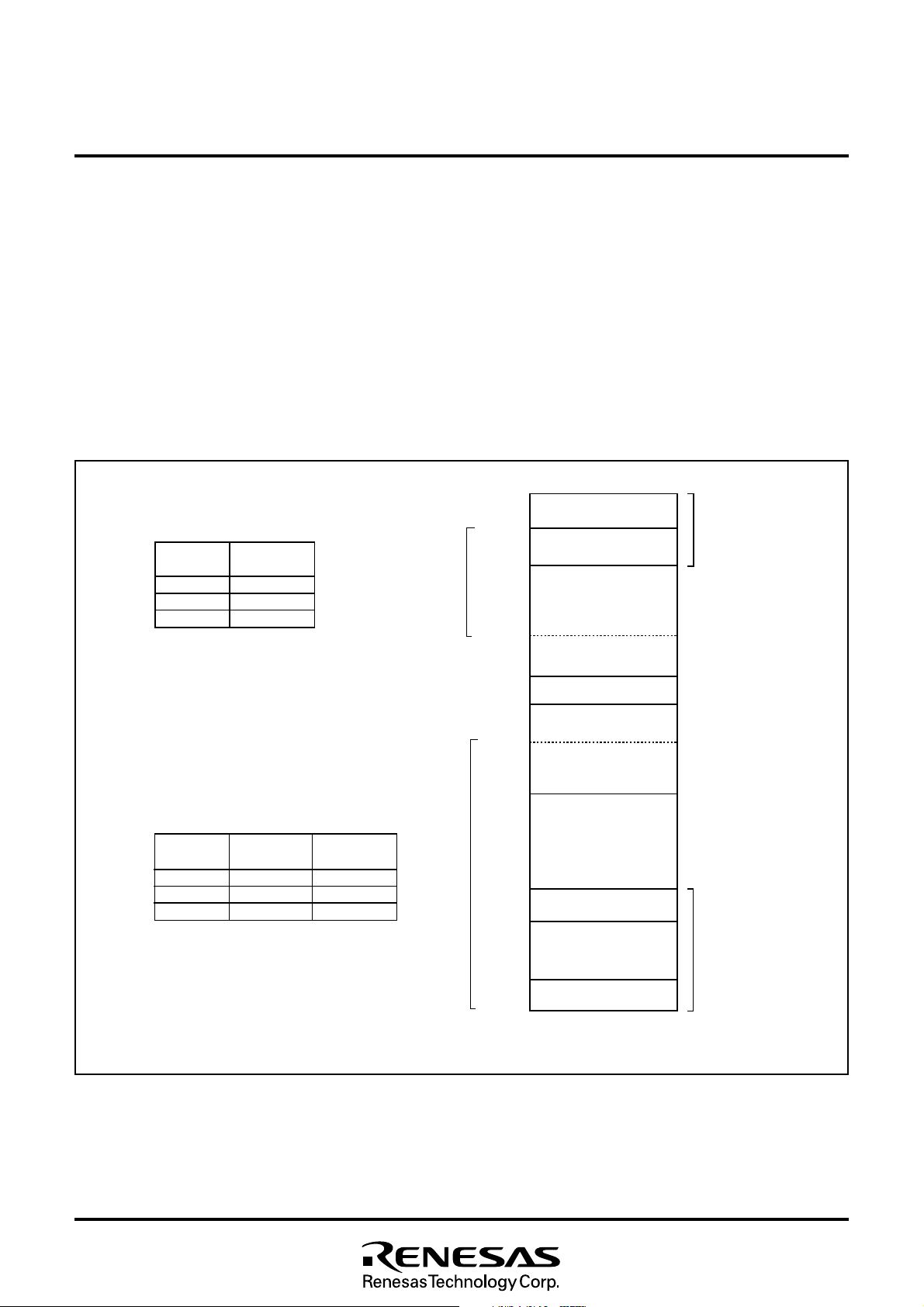

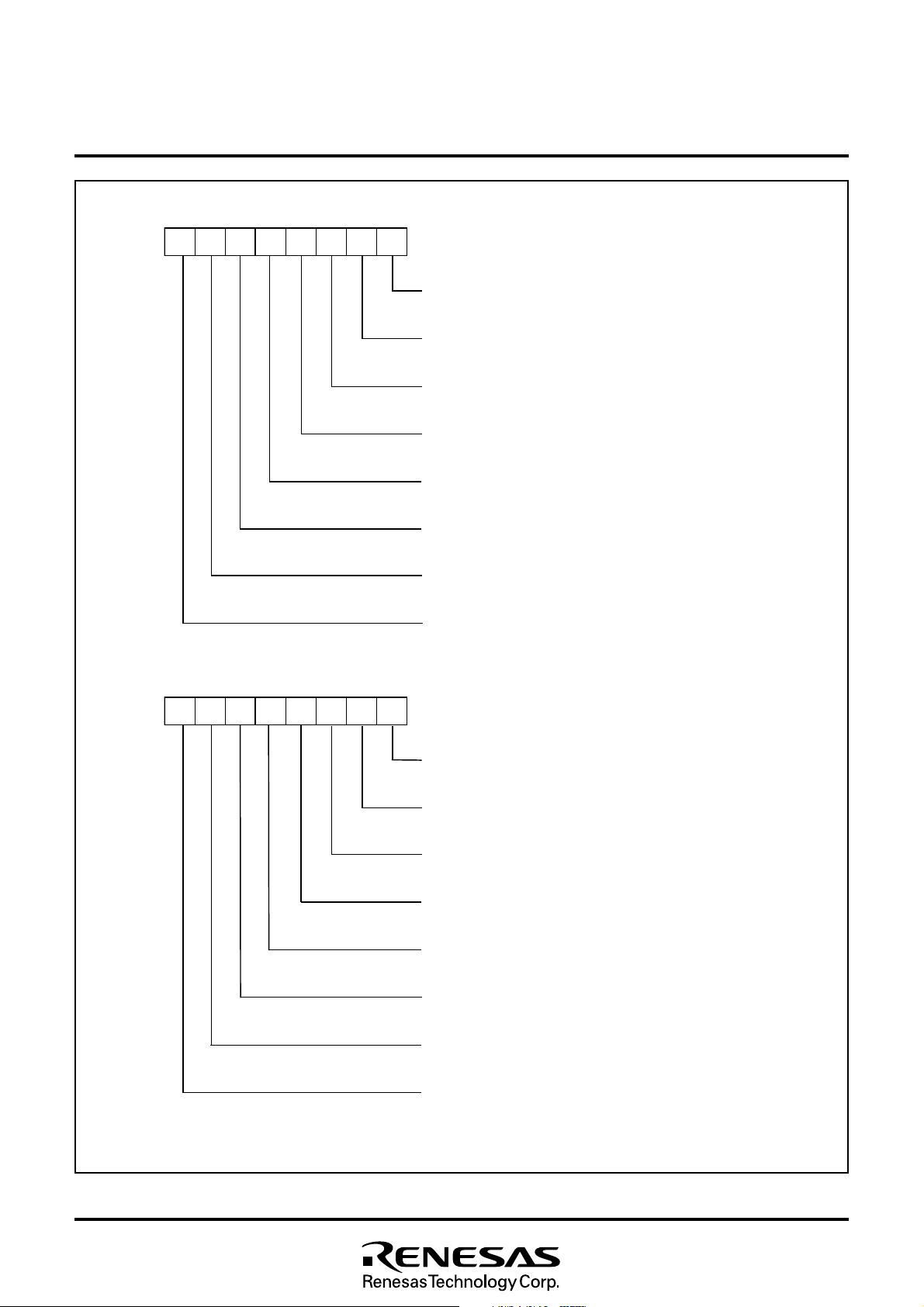

MEMORY

RAM

RAM is used for data storage and for stack area of subroutine

calls and interrupts.

ROM

ROM is used for program code and data table storage.

The first 128 bytes and the last 2 bytes of ROM are reserved for

device testing code and the rest is user area. Programming/Erasing of the reserved ROM area is possible in the flash memory

version.

R A M a r e a

R A M s i z e

( b y t e s )

1 0 2 4

1 5 3 6

2 0 4 8

A d d r e s s

X X X X

0 4 3 F

0 6 3 F

0 8 3 F

1 6

1 6

1 6

1 6

R A M

Zero Page

Access to this area with only 2 bytes is possible in the zero page

addressing mode.

Special Page

Access to this area with only 2 bytes is possible in the special

page addressing mode.

Interrupt Vector Area

The interrupt vector area contains reset and interrupt vectors.

Special Function Register (SFR) Area

The special function register area contains the control registers

such as I/O ports, timers, serial I/O, etc.

0000

0040

0100

XXXX

16

16

16

16

S F R a r e a

Z e r o p a g e

R O M a r e a

R O M s i z e

( b y t e s )

3 2 7 6 8

4 9 1 5 2

6 1 4 4 0

Fig. 8 Memory map diagram

A d d r e s s

Y Y Y Y

8 0 0 0

4 0 0 0

1 0 0 0

Not used

0FF0

0 F F F

Y Y Y Y

16

1 6

1 6

SFR area

R e s e r v e d R O M a r e a

( N o t e )

( 1 2 8 b y t e s )

ZZZZ

16

A d d r e s s

1 6

1 6

1 6

1 6

Z Z Z Z

8 0 8 0

4 0 8 0

1 0 8 0

1 6

1 6

1 6

1 6

ROM

FF00

16

FFDC

16

I n t e r r u p t v e c t o r a r e a

FFFE

16

Reserved ROM area

FFFF

16

Notes: This area is reserv ed in the mask ROM version.

This area is usable in f las h memory version.

(Note)

Special page

11

Page 13

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

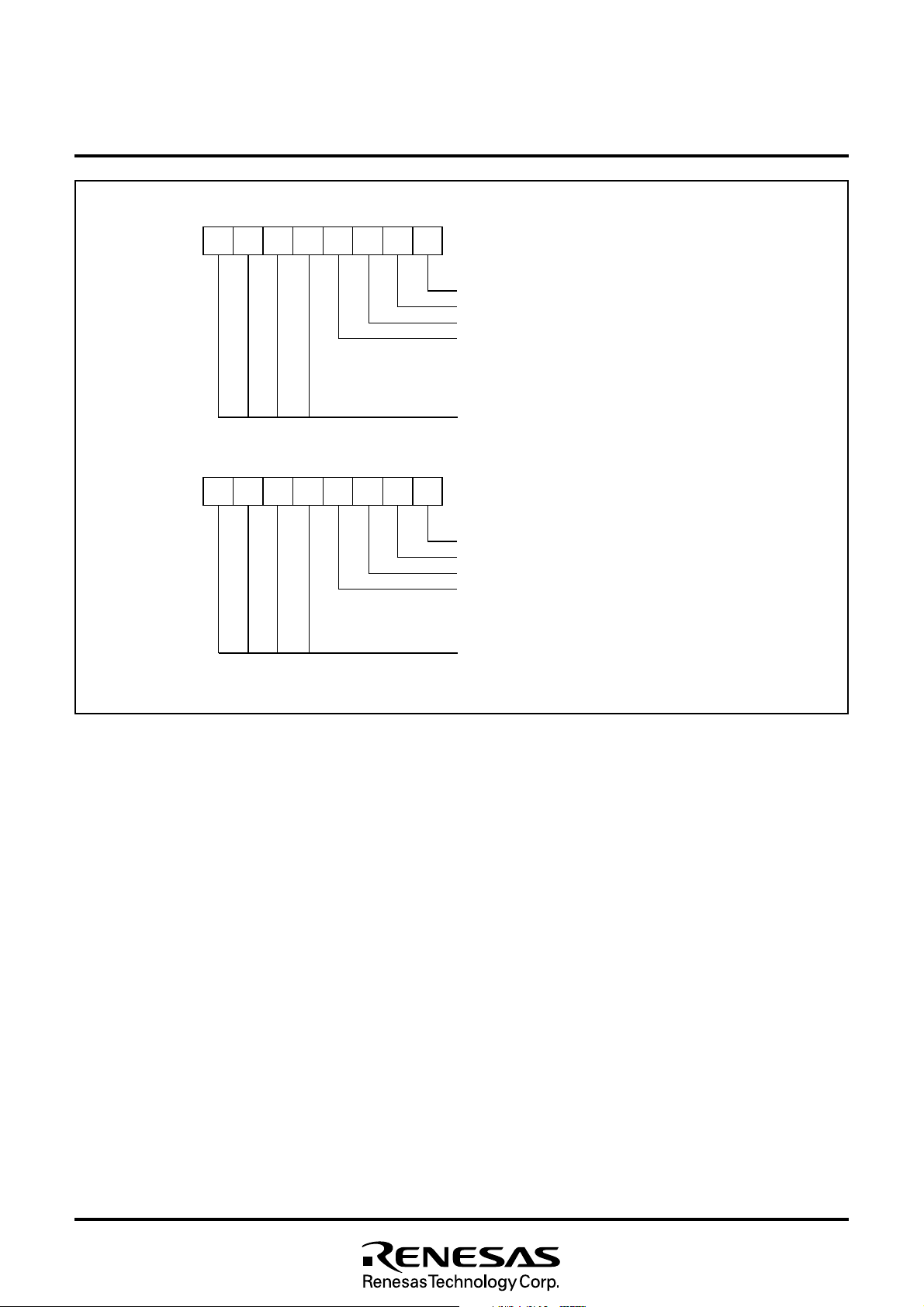

P o r t P 0 ( P 0 )

0000

16

P o r t P 0 d i r e c t i o n r e g i s t e r ( P 0 D )

0 0 0 1

1 6

P o r t P 1 ( P 1 )

0 0 0 2

1 6

P o r t P 1 d i r e c t i o n r e g i s t e r ( P 1 D )

0 0 0 3

1 6

P o r t P 2 ( P 2 )

0 0 0 4

1 6

P o r t P 2 d i r e c t i o n r e g i s t e r ( P 2 D )

0 0 0 5

1 6

P o r t P 3 ( P 3 )

0 0 0 6

1 6

P o r t P 3 d i r e c t i o n r e g i s t e r ( P 3 D )

0 0 0 7

1 6

P o r t P 4 ( P 4 )

0 0 0 8

1 6

P o r t P 4 d i r e c t i o n r e g i s t e r ( P 4 D )

0 0 0 9

1 6

P o r t P 5 ( P 5 )

0 0 0 A

1 6

P o r t P 5 d i r e c t i o n r e g i s t e r ( P 5 D )

0 0 0 B

1 6

P o r t P 6 ( P 6 )

0 0 0 C

1 6

P o r t P 6 d i r e c t i o n r e g i s t e r ( P 6 D )

0 0 0 D

1 6

P o r t P 7 ( P 7 )

0 0 0 E

1 6

P o r t P 7 d i r e c t i o n r e g i s t e r ( P 7 D )

0 0 0 F

1 6

Port P8 (P8)/Port P4 in put register (P4I)

0 0 1 0

1 6

0 0 1 1

1 6

Port P8 direction register (P8D)/Port P7 input register (P7I)

0012

0013

0 0 1 4

0 0 1 5

0016

0017

0 0 1 8

0 0 1 9

001A

001B

0 0 1 C

0 0 1 D

0 0 1 E

001F

2

16

I

C d a t a s h i f t r e g i s t e r ( S 0 )

2

16

I

C a d d r e s s r e g i s t e r ( S 0 D )

2

1 6

I

C status register ( S 1)

2

1 6

I

C control register (S1D)

2

16

I

C c l o c k c o n t r o l r e g i s t e r ( S 2 )

2

16

I

C s t a r t / s t o p c o n d i t i o n c o n t r o l r e g i s t e r ( S 2 D )

Transmit/Receiv e buffer register (TB/RB)

1 6

Serial I/O status re gister (SIOSTS)

1 6

S e r i a l I / O c o n t r o l r e g i s t e r ( S I O C O N )

16

U A R T c o n t r o l r e g i s t e r ( U A R T C O N )

16

Baud rate generator ( B RG)

1 6

S e r i a l i z e d I R Q c o n t r o l r e g i s t e r ( S E R C O N )

1 6

W a t c h d o g t i m e r c o n t r o l r e g i s t e r ( W D T C O N )

1 6

S e r i a l i z e d I R Q r e q u e s t r e g i s t e r ( S E R I R Q )

16

0020

0021

0022

0023

0024

0025

0026

0027

0028

0029

002A

002B

002C

002D

002E

0 0 2 F

0030

0031

0032

0033

0034

0035

0036

0037

0038

0039

003A

003B

003C

003D

003E

003F

P r e s c a l e r 1 2 ( P R E 1 2 )

16

T i m e r 1 ( T 1 )

16

T i m e r 2 ( T 2 )

16

T i m e r X Y m o d e r e g i s t e r ( T M )

16

P r e s c a l e r X ( P R E X )

16

T i m e r X ( T X )

16

P r e s c a l e r Y ( P R E Y )

16

T i m e r Y ( T Y )

16

D a t a b a s b u f f e r r e g i s t e r 0 ( D B B 0 )

16

D a t a b a s b u f f e r s t a t u s r e g i s t e r 0 ( D B B S T S 0 )

16

L P C c o n t r o l r e g i s t e r ( L P C C O N )

16

D a t a b a s b u f f e r r e g i s t e r 1 ( D B B 1 )

16

D a t a b a s b u f f e r s t a t u s r e g i s t e r 1 ( D B B S T S 1 )

16

C o m p a r a t o r d a t a r e g i s t e r ( C M P D )

16

P o r t c o n t r o l r e g i s t e r 1 ( P C T L 1 )

16

P o r t c o n t r o l r e g i s t e r 2 ( P C T L 2 )

1 6

P W M 0 H r e g i s t e r ( P W M 0 H )

16

P W M 0 L r e g i s t e r ( P W M 0 L )

16

PWM1H register (PWM1H)

16

PWM1L register (PWM1L)

16

AD/DA control regi s ter (ADCON)

16

A - D c o n v e r s i o n r e g i s t e r 1 ( A D 1 )

16

D - A 1 c o n v e r s i o n r e g i s t e r ( D A 1 )

16

D-A2 conversion register (DA2)

16

A-D conversion regis ter 2 (AD2)

16

I n t e r r u p t s o u r c e s e l e c t i o n r e g i s t e r ( I N T S E L )

16

I n t e r r u p t e d g e s e l e c t i o n r e g i s t e r ( I N T E D G E )

16

C P U m o d e r e g i s t e r ( C P U M )

16

Interrupt request register 1 (IREQ1)

16

I n t e r r u p t r e q u e s t r e g i s t e r 2 ( I R E Q 2 )

16

I n t e r r u p t c o n t r o l r e g i s t e r 1 ( I C O N 1 )

16

I n t e r r u p t c o n t r o l r e g i s t e r 2 ( I C O N 2 )

16

Fig. 9 Memory map of special function register (SFR)

12

LPC0 address register L ( LP C0ADL)

0 F F 0

1 6

0FF1

0FF2

0FF8

0FFE

L P C 0 a d d r e s s r e g i s t e r H ( L P C 0 A D H )

16

L P C 1 a d d r e s s r e g i s t e r L ( L P C 1 A D L )

16

LPC1 address regist er H ( LP C1ADH)

0FF3

16

16

P o r t P 5 i n p u t r e g i s t e r ( P 5 I )

P o r t c o n t r o l r e g i s t e r 3 ( P C T L 3 )

0FF9

16

F l a s h m e m o r y c o n t r o l r e g i s t e r ( F M C R )

16

0FFF16Reserved

N o t e : T h i s a p p l i e s t o o n l y f l a s h m e m o r y v e r s i o n .

(Note)

(Note)

Page 14

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

I/O PORTS

All I/O pins are programmable as input or output. All I/O ports

have direction registers which specify the data direction of each

pin like input/output. One bit in a direction register corresponds to

one pin. Each pin can be set to be input or output port.

Writing “0” to the bit corresponding to the pin, that pin becomes an

input mode. Writing “1” to the bit, that pin becomes an output

mode.

When the data is read from the bit of the port register corresponding to the pin which is set to output, the value shows the port latch

data, not the input level of the pin. When a pin set to input, the pin

Table 6 I/O port function (1)

Pin

P00-P07

P10–P17

P20/CMPREF

P21–P27

P30/PWM00

P31/PWM10

P32–P37

P40/XCOUT

P41/XCIN

P42/INT0

P43/INT1

P44/RXD

P45/TXD

P46/SCLK (13)

P47/SRDY

/CLKRUN

Name

Port P0

Port P1

Port P2

Port P3

Port P4

Input/Output

Input/output,

individual bits

I/O Structure Non-Port Function

CMOS compatible

input level

CMOS 3-state output

or N-channel opendrain output

CMOS compatible

input level

CMOS 3-state output

CMOS compatible

input level

CMOS 3-state output

or N-channel opendrain output

comes floating. In input port mode, writing the port register

changes only the data of the port latch and the pin remains high

impedance state.

When the P8 function selection bit of the port control register 2 is

set to “1”, reading from address 001016 reads the port P4 register,

and reading from address 001116 reads the port P7 register.

Especially, the input level of P42 to P46 pins and P70 to P75 pins

can be read regardless of the data of the direction registers in this

case.

Related SFRs

Port control register 1 (1)

Analog comparator

power source input pin

PWM output

Key-on wake up input

Comparator input

Key-on wake up input

Comparator input

Sub-clock generating

circuit

External interrupt input

Serial I/O function input

Serial I/O function output

Serial I/O function I/O

Serial I/O function output

Serialized IRQ function

output

Port control register 1

Port control register 2

Port control register 1

AD/DA control register

Port control register 1

CPU mode register

Interrupt edge selection

register

Port control register 2

Serial I/O control register

Port control register 2

Serial I/O control register

UART control register

Port control register 2

Serial I/O control register

Port control register 2

Serial I/O control register

Serialized IRQ control

register

Ref.No.

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(10)

(11)

(12)

(14)

13

Page 15

Table 7 I/O port function (2)

Pin

P50/INT5

P51/INT20

P52/INT30

P53/INT40

P54/CNTR0

P55/CNTR1

Name

Port P5

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Input/Output I/O Format Non-Port Function Ref.No.

CMOS compatible

input level

CMOS 3-state output

or N-channel

opendrain output

External interrupt input

Timer X, timer Y function I/O

Related SFRs

Interrupt edge selection

register

Timer XY mode register

(15)

(16)

(17)

P56/DA1/

PWM01

P57/DA2/

PWM11

P60/AN0–

P67/AN7

P70

P71

P72

P73/INT21

P74/INT31

P75/INT41

P76/SDA

P77/SCL

P80/LAD0

P81/LAD1

P82/LAD2

P83/LAD3

P84/

LFRAME

P85/

LRESET

P86/LCLK

P87/

SERIRQ

Notes1: For details usage of double-function ports as function I/O ports, refer to the applicable sections.

2: Make sure that the input level of each pin should be either 0 V or V

When an input level is at an intermediate voltage level, the I

Port P6

Input/output,

individual bits

Port P7

Port P8

CMOS compatible

input level

CMOS 3-state output

CMOS compatible

input level or

TTL input level

Pure N-channel

open-drain output

CMOS compatible

input level or SMBUS

input level

Pure N-channel

open-drain output

CMOS compatible

input level

CMOS 3-state output

CC in STP mode.

CC current will become large because of the input buffer gate.

D-A converter output

PWM output

A-D converter input AD/DA control register

External interrupt input

I2C-BUS interface function I/O

LPC interface function

I/O

Serialized IRQ function

I/O

AD/DA control register

UART control register

Port control register 2

Interrupt edge selection

register

Port control register 2

I2C control register

Data bus buffer control

register

(18)

(19)

(20)

(21)

(22)

(23)

(24)

(25)

(26)

(27)

(28)

14

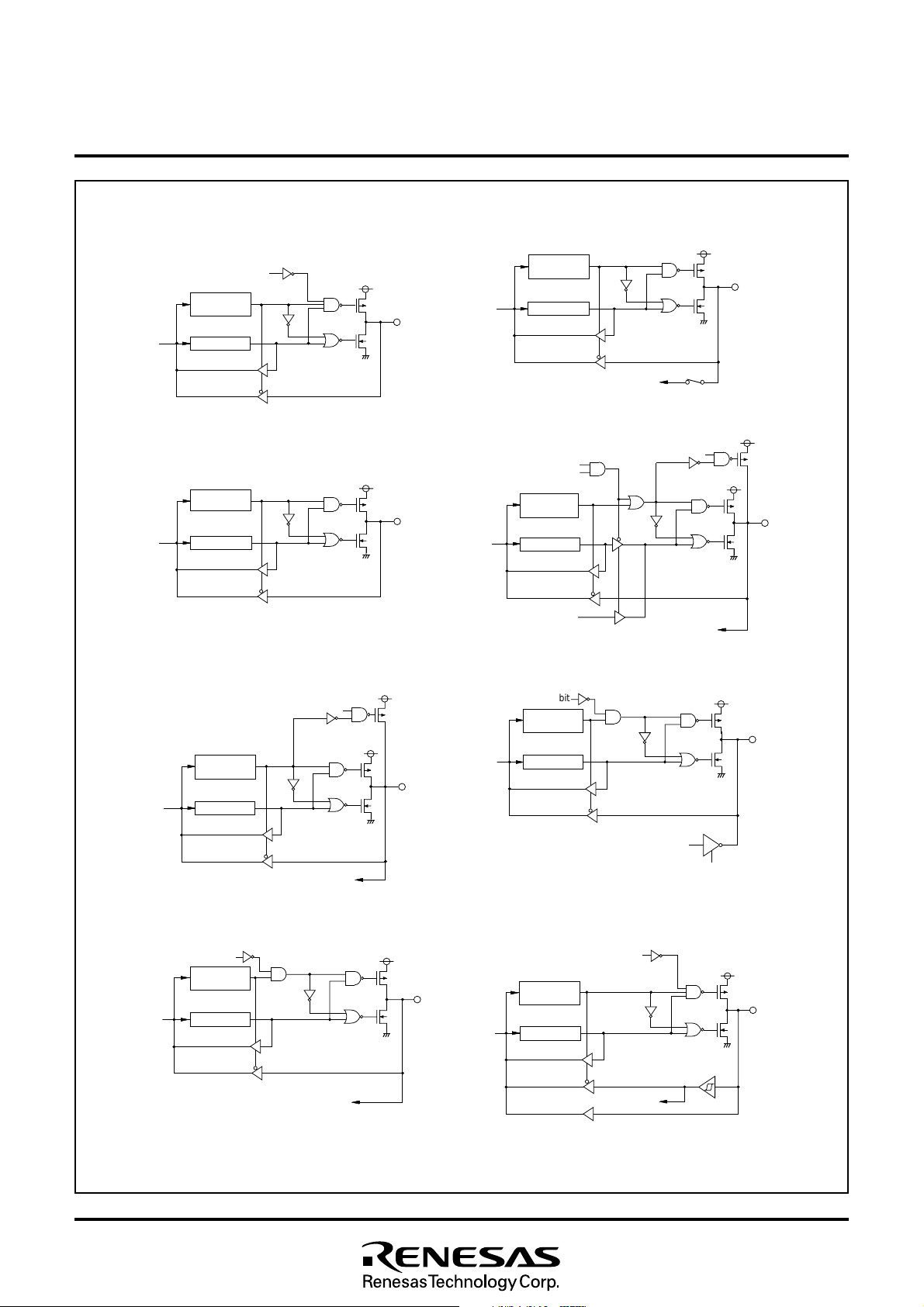

Page 16

MITSUBISHI MICROCOMPUTERS

g

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

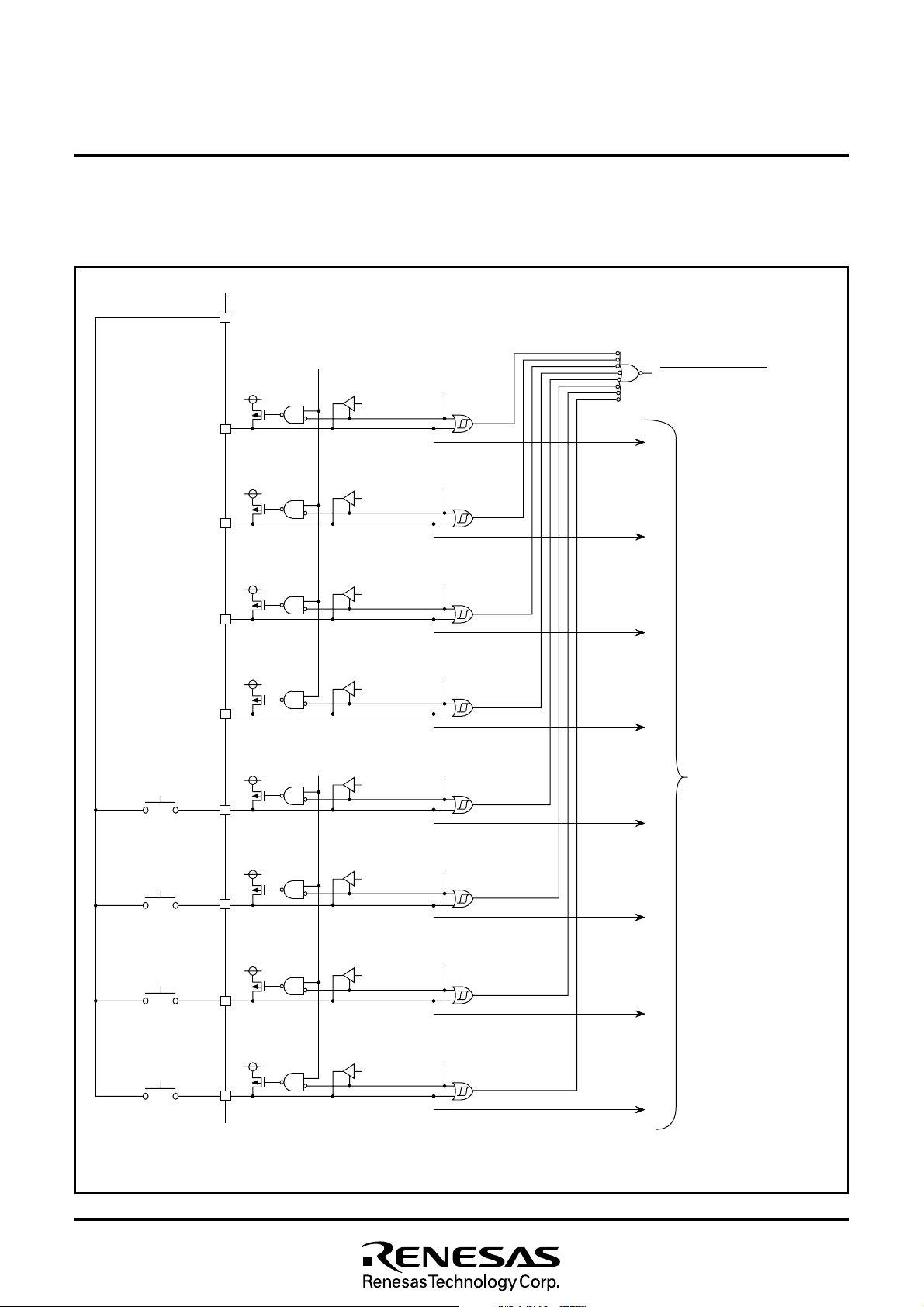

( 1 ) P o r t s P 0 , P 1

P 00– P 03,

P 04– P 07,

P 10– P 13,

P 14– P 1

7

D a t a b u s

( 3 ) P o r t P21– P 2

D a t a b u s

o u t p u t s t r u c t u r e

s e l e c t i o n b i t s

D i r e c t i o n

r e g i s t e r

P o r t l a t c h

7

i s t e

D i r e c t i o n

r

r e

P o r t l a t c h

( 2 ) P o r t P 2

D a t a b u s

( 4 ) P o r t s P 30, P 3

P W M0 ( P W M1) o u t p u t p i n s e l e c t i o n b i t

D a t a b u s

0

D i r e c t i o n

r e g i s t e r

P o r t l a t c h

C o m p a r a t o r r e f e r e n c e p o w e r s o u r c e i n p u t

1

PWM

0

(PWM1) enable bit

Direction

register

P o r t l a t c h

00

(PWM10) output

PWM

C o m p a r a t o r r e f e r e n c e i n p u t

P 3

0

– P 33 p u l l - u p c o n t r o l b i t

Comparator input

Key-on wake-up input

p i n s e l e c t b i t

( 5 ) P o r t s P 32– P 3

D a t a b u s

(7) Port P4

D a t a b u s

1

P o r t XC s w i t c h b i t

7

P30–P33,

P3

4

–P3

7

pull-up control bit

D i r e c t i o n

r e g i s t e r

P o r t l a t c h

Key-on wake-up input

D i r e c t i o n

r e g i s t e r

P o r t l a t c h

S u b - c l o c k o s c i l l a t i o n c i r c u i t

C o m p a r a t o r i n p u t

( 6 ) P o r t P 4

D a t a b u s

0

Port XC switch bit

D i r e c t i o n

r e g i s t e r

P o r t l a t c h

(8) Ports P42 , P4

P 4 o u t p u t s t r u c t u r e s e l e c t i o n b i t

D i r e c t i o n

Data bus

Port latch

3

r e g i s t e r

Sub-clock oscillation circuit

I n t e r r u p t i n p u t

✻1

Port P4

P o r t X

1

C

s w i t c h b i t

✻1 . R e a d i n g t h e p o r t P 8 r e g i s t e r ( a d d r e s s 0 0 1 0

r e g i s t e r 2 ( P C T L 2 ) .

1 6

) i s s w i t c h e d t o p o r t P 4 p i n i n p u t l e v e l b y t h e P 8 f u n c t i o n s e l e c t i o n b i t o f t h e p o r t c o n t r o l

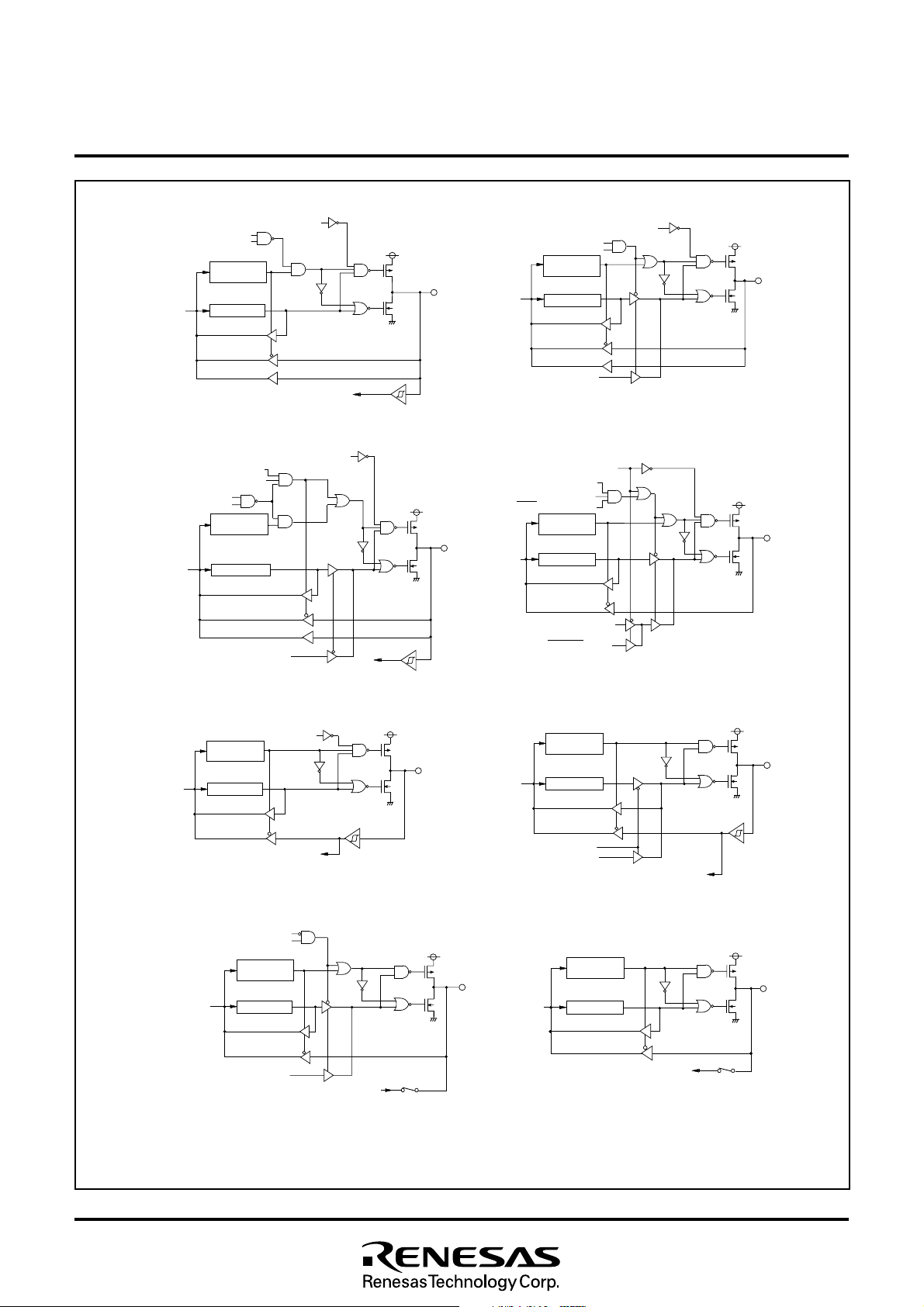

Fig. 10 Port block diagram (1)

15

Page 17

MITSUBISHI MICROCOMPUTERS

s

t

t

t

s

t

t

s

t

t

t

s

s

t

s

s

s

t

t

t

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

( 9 ) P o r t P 44

P 4 o u t p u t s t r u c t u r e s e l e c t i o n b i t

S e r i a l I / O e n a b l e b i

R e c e i v e e n a b l e b i

D a t a b u

( 1 1 ) P o r t P 46

Serial I/O mode selection bi

S e r i a l I / O

s y n c h r o n o u s c l o c k s e l e c t i o n b i t

Serial I/O enable bi

Serial I/O enable bit

Data bu

Serial I/O clock output

D i r e c t i o n

r e g i s t e r

P o r t l a t c h

✻1

S e r i a l I / O i n p u t

P 4 o u t p u t s t r u c t u r e s e l e c t i o n b i

Direction

register

P o r t l a t c h

✻1

Serial I/O external clock input

(10) Port P45

5/

TXD P - c h a n n e l o u t p u t d i s a b l e b i

P 4

D a t a b u

S e r i a l I / O e n a b l e b i

T r a n s m i t e n a b l e b i

(12) Port P47

Serial I/O mode selection bi

Serial I/O enable bi

SRDY

Data bu

Serial I/O ready output

Direction

register

P o r t l a t c h

✻1

S e r i a l I / O o u t p u t

Serialized IRQ enable bit

output enable bi

Direction

register

P o r t l a t c h

CLKRUN output

(13) Ports P50 to P53

P 5 i o p e n d r a i n s e l e c t i o n b i t

D i r e c t i o n

r e g i s t e r

Data bu

Port latch

I n t e r r u p t i n p u t

(15) Ports P56, P57

P W M0 ( P W M1) o u t p u t p i n s e l e c t i o n b i t

i s s w i t c h e d t o p o r t P 4 p i n i n p u t l e v e l b y t h e P 8 f u n c t i o n s e l e c t i o n b i t o f t h e p o r t c o n t r o

✻1 . R e a d i n g t h e p o r t P 8 r e g i s t e r ( a d d r e s s 0 0 1 01

P W

P W M

0 (

M1) e n a b l e b i t

Data bu

P W

o u t p u

P W M

0 1 (

r e g i s t e r 2 ( P C T L 2 ) .

D i r e c t i o n

r e g i s t e r

P o r t l a t c h

M1

1)

t

D - A c o n v e r t e r o u t p u

D-A1 (D-A2) output enable bit

6)

(14) Ports P54, P55

Direction

register

Data bu

Port latch

Pulse output mode

Timer output

(16) Port P6

Data bu

C N T

C N T R

D i r e c t i o n

r e g i s t e r

P o r t l a t c h

0,

R1 i n t e r r u p t i n p u t

A-D converter input

A n a l o g i n p u t p i n s e l e c t i o n b i t

l

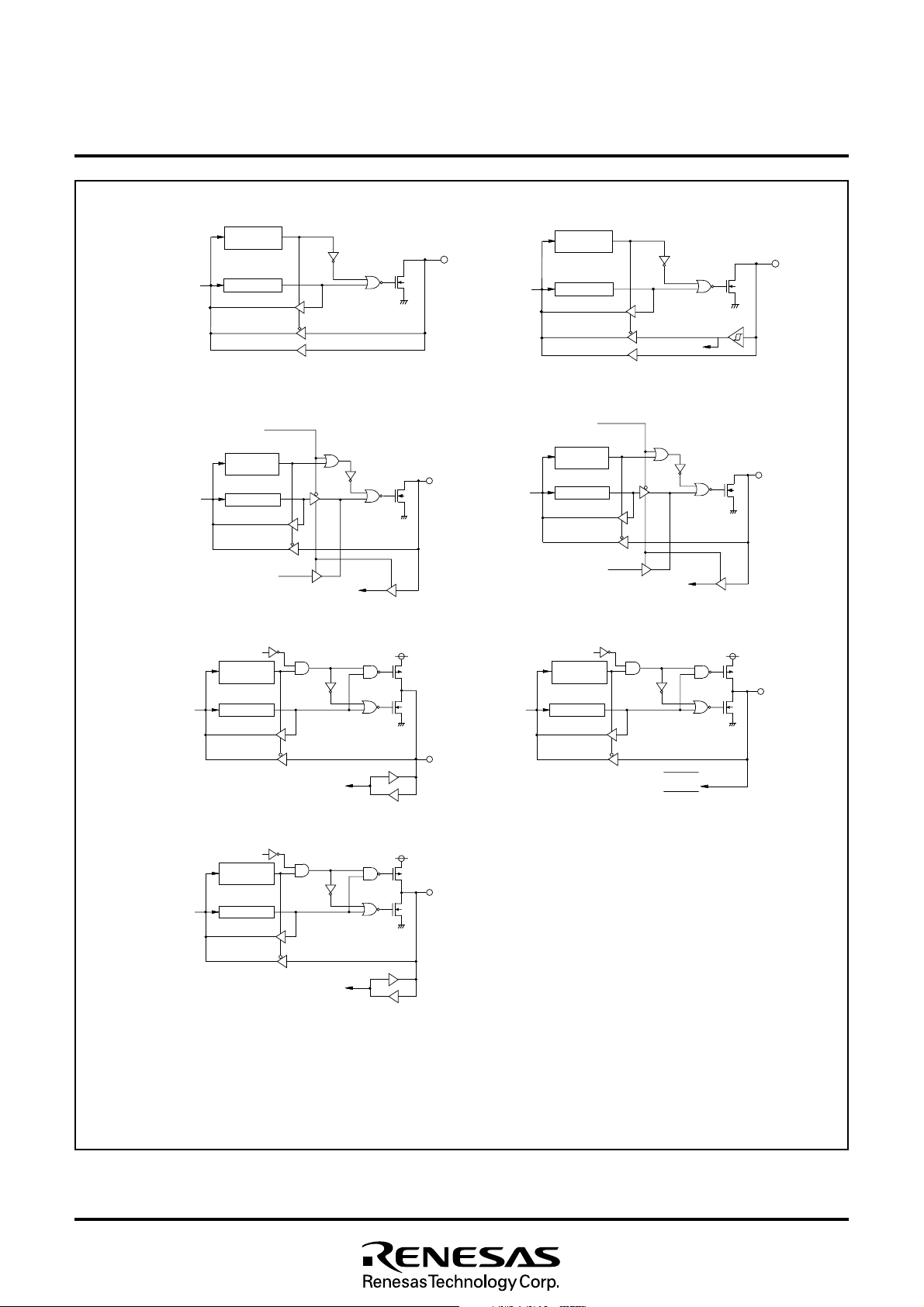

Fig. 11 Port block diagram (2)

16

Page 18

MITSUBISHI MICROCOMPUTERS

s

g

t

e

t

e

t

s

s

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

( 1 7 ) P o r t s P 70 t o P 7

D i r e c t i o n

r e g i s t e r

D a t a b u

( 1 9 ) P o r t P 7

D a t a b u s

P o r t l a t c h

6

I2C - B U S i n t e r f a c

e n a b l e b i

i s t e

D i r e c t i o n

r e

Port latch

S

DA

( 2 1 ) P o r t s P 80 t o P 8

LPC enable bit

Direction

register

2

r

output

3

(18) Ports P73 to P7

Data bu

✻2

(20) Port P7

I2C-BUS interfac

D a t a b u

D A

S

i n p u

✻3

(22) Ports P84 to P8

LPC enable bit

7

enable bi

Direction

register

5

D i r e c t i o n

r e g i s t e r

P o r t l a t c h

D i r e c t i o n

r e g i s t e r

Port latch

S

C L

o u t p u t

6

✻2

I n t e r r u p t i n p u t

CL

input

S

✻3

Data bus

( 2 3 ) P o r t P 8

D a t a b u s

✻2. T h e i n p u t l e v e l c a n b e s w i t c h e d b e t w e e n C M O S c o m p a t i b l e i n p u t l e v e l a n d T T L l e v e l b y t h e P 7 i n p u t l e v e l s e l e c t i o n b i t o f t h e p o r t

c o n t r o l r e g i s t e r 2 ( P C T L 2 ) .

R e a d i n g t h e p o r t P 8 d i r e c t i o n r e g i s t e r i s s w i t c h e d t o p o r t P 7 p i n i n p u t l e v e l b y t h e P 8 f u n c t i o n s e l e c t i o n b i t o f t h e p o r t c o n t r o l r e g i s t e r 2

( P C T L 2 ) .

✻3. T h e i n p u t l e v e l c a n b e s w i t c h e d b e t w e e n C M O S c o m p a t i b l e i n p u t l e v e l a n d S M B U S l e v e l b y t h e I2C - B U S i n t e r f a c e p i n i n p u t s e l e c t i o n

b i t o f t h e I

Port latch

7

S I R Q e n a b l e b i t

D i r e c t i o n

r e g i s t e r

Port latch

2

C c o n t r o l r e g i s t e r ( S I D ) .

L A D [ 3 : 0 ]

I R Q S E R

Data bus

Port latch

L R E S E T

L C L K

L F R A M E

Fig. 12 Port block diagram (3)

17

Page 19

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

b 7b

0

Port control register 1

1 6

( P C T L 1 : a d d r e s s 0 0 2 E

)

P00–P03 output structure selection bit

0: CMOS

1: N-channel open-drain

P0

4

–P07 output structure selection bit

0: CMOS

1: N-channel open-drain

P1

0

–P13 output structure selection bit

0: CMOS

1: N-channel open-drain

P1

4

–P17 output structure selection bit

0: CMOS

1: N-channel open-drain

P3

0

–P33 pull-up control bit

0: No pull-up

1: Pull-up

P3

4

–P37 pull-up control bit

0: No pull-up

1: Pull-up

PWM

0

enable bit

0: PWM

0

output disabled

1: PWM

0

output enabled

PWM

1

enable bit

0: PWM

1

output disabled

1: PWM

1

output enabled

b7 b0

Port control register 2

( P C T L 2 : a d d r e s s 0 0 2 F

1 6

)

N o t u s e d ( r e t u r n s “ 0 ” w h e n r e a d )

P 7 i n p u t l e v e l s e l e c t i o n b i t ( P 7

0

- P 75)

0 : C M O S i n p u t l e v e l

1 : T T L i n p u t l e v e l

P 4 o u t p u t s t r u c t u r e s e l e c t i o n b i t ( P 4

2

, P 43, P 44, P 46)

0 : C M O S

1 : N - c h a n n e l o p e n - d r a i n

P 8 f u n c t i o n s e l e c t i o n b i t

0 : P o r t P 8 / P o r t P 8 d i r e c t i o n r e g i s t e r

1 : P o r t P 4 i n p u t r e g i s t e r / P o r t P 7 i n p u t r e g i s t e r

I N T

2

, I N T3, I N T4 i n t e r r u p t s w i t c h b i t

0 : I N T

2 0

, I N T

3 0

, I N T

4 0

i n t e r r u p t

1 : I N T

2 1

, I N T

3 1

, I N T

4 1

i n t e r r u p t

T i m e r Y c o u n t s o u r c e s e l e c t i o n b i t

0 : f ( X

I N

) / 1 6 ( f ( X

C I N

) / 1 6 i n l o w - s p e e d m o d e )

1 : f ( X

C I N

)

O s c i l l a t i o n s t a b i l i z i n g t i m e s e t a f t e r S T P i n s t r u c t i o n r e l e a s e d b i t

0 : A u t o m a t i c s e t “ 0 1

1 6

” t o t i m e r 1 a n d “ F F

1 6

” t o p r e s c a l e r 1 2

1 : N o a u t o m a t i c s e t

C o m p a r a t o r r e f e r e n c e i n p u t s e l e c t i o n b i t

0 : P 2

0

/ C M P

R E F

i n p u t

1 : R e f e r e n c e i n p u t f i x e d

Fig. 13 Structure of port I/O related registers (1)

18

Page 20

MITSUBISHI MICROCOMPUTERS

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

b 7b0

P o r t P 5 i n p u t r e g i s t e r

( P 5 I : a d d r e s s 0 F F 8

P 50 i n p u t l e v e l b i t

P 5

1

i n p u t l e v e l b i t

P 5

2

i n p u t l e v e l b i t

P 5

3

i n p u t l e v e l b i t

T h e s e b i t s d i r e c t l y s h o w t h e p i n i n p u t l e v e l s .

0 : “ L ” l e v e l i n p u t

1 : “ H ” l e v e l i n p u t

N o t u s e d ( r e t u r n s “ 0 ” w h e n r e a d )

b 7b0

P o r t c o n t r o l r e g i s t e r 3

( P C T L 3 : a d d r e s s 0 F F 9

1 6

)

1 6

)

3885 Group

Fig. 14 Structure of port I/O related registers (2)

P 50 o p e n d r a i n s e l e c t i o n b i t

P 5

1

o p e n d r a i n s e l e c t i o n b i t

P 5

2

o p e n d r a i n s e l e c t i o n b i t

P 5

3

o p e n d r a i n s e l e c t i o n b i t

0 : C M O S

1 : N - c h a n n e l o p e n d r a i n

N o t u s e d ( r e t u r n s “ 0 ” w h e n r e a d )

19

Page 21

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

INTERRUPTS

Interrupts occur by 16 sources among 22 sources: thirteen external, nine internal, and one software.

Interrupt Control

Each interrupt is controlled by an interrupt request bit, an interrupt

enable bit, and the interrupt disable flag except for the software interrupt caused by the BRK instruction. An interrupt occurs when

both the corresponding interrupt request bit and interrupt enable

bit are “1” and the interrupt disable flag is “0”.

Interrupt enable bits can be set or cleared by software.

Interrupt request bits can be cleared by software, but cannot be

set by software.

The BRK instruction interrupt cannot be disabled with any flag or

bit. The I (interrupt disable) flag disables all interrupts except the

BRK instruction interrupt.

When several interrupts occur at the same time, the interrupts are

serviced according to the priority.

Interrupt Operation

By acceptance of an interrupt, the following operations are automatically performed:

1. The contents of the program counter and the processor status

register are automatically pushed onto the stack.

2. The interrupt disable flag is set and the corresponding interrupt

request bit is cleared.

3. The interrupt jump destination address is read from the vector

table and stored into the program counter.

Interrupt Source Selection

Any of the following interrupt sources can be selected by the interrupt source selection register (INTSEL).

1. INT0 or Input buffer full

2. INT1 or Output buffer empty

3. Serial I/O receive or LRESET

4. Serial I/O transmission or SCLSDA

5. Timer 2 or INT5

6. CNTR0 or INT0

7. CNTR1 or INT1

8. A-D conversion or Key-on wake-up

External Interrupt Pin Selection

The external interrupt sources of INT2, INT3, and INT4 can be selected from either input pin from INT20, INT30, INT40 or input pin

from INT21, INT31, INT41 by the INT2, INT3, INT4 interrupt switch

bit (bit 4 of PCTL2).

■ Notes

When setting the followings, the interrupt request bit may be set to

“1”.

•When setting external interrupt active edge

Related register: Interrupt edge selection register (address

003A16); Timer XY mode register (address

002316)

•When switching interrupt sources of an interrupt vector address

where two or more interrupt sources are allocated

Related register: Interrupt source selection register (address

003916)

•When setting input pin of external interrupts INT2, INT3 and INT4

Related register: INT2, INT3, INT4 interrupt switch bit of Port con-

trol register 2 (bit 4 of address 002F16)

When not requiring the interrupt occurrence synchronized with

these setting, take the following sequence.

➀ Set the corresponding interrupt enable bit to “0” (disabled).

➁ Set the active edge selection bit or the interrupt source selec-

tion bit to “1”.

➂ Set the corresponding interrupt request bit to “0” after 1 or more

instructions have been executed.

➃ Set the corresponding interrupt enable bit to “1” (enabled).

20

Page 22

Table 8 Interrupt vector addresses and priority

Interrupt Source

Reset (Note 2)

INT0

Input buffer full

(IBF)

INT1

Output buffer

empty (OBE)

Priority

1

2

3

Vector Addresses (Note 1)

High

16

FFFD

FFFB16

FFF916

Low

FFFC16

FFFA16

FFF816

MITSUBISHI MICROCOMPUTERS

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Interrupt Request

Generating Conditions

At reset

At detection of either rising or

falling edge of INT0 input

At input data bus buffer writing

At detection of either rising or

falling edge of INT1 input

At output data bus buffer reading

3885 Group

Remarks

Non-maskable

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

Serial I/O

reception

LRESET At falling edge of LRESET input External interrupt

Serial I/O

transmission

SCL, SDA

Timer X

Timer Y

Timer 1

Timer 2

INT5

CNTR0

INT0

CNTR1

INT1

I2C

INT2

INT3

INT4

10

11

12

13

14

15

4

5

6

7

8

9

FFF716

FFF516

FFF316

FFF116

FFEF16

FFED16

FFEB16

FFE916

FFE716

FFE516

FFE316

FFE116

FFF616

FFF416

FFF216

FFF016

FFEE16

FFEC16

FFEA16

FFE816

FFE616

FFE416

FFE216

FFE016

At completion of serial I/O data

reception

At completion of serial I/

Otransfer shift or when transmission buffer is empty

At detection of either rising or

falling edge of SCL or SDA

At timer X underflow

At timer Y underflow

At timer 1 underflow

At timer 2 underflow

At detection of either rising or

falling edge of INT5 input

At detection of either rising or

falling edge of CNTR0 input

At detection of either rising or

falling edge of INT0 input

At detection of either rising or

falling edge of CNTR1 input

At detection of either rising or

falling edge of INT1 input

At completion of data transfer

At detection of either rising or

falling edge of INT2 input

At detection of either rising or

falling edge of INT3 input

At detection of either rising or

falling edge of INT4 input

Valid when serial I/O is selected

Valid when serial I/O is selected

External interrupt

(active edge selectable)

STP release timer underflow

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt (falling valid)

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

A-D converter

16

Key-on wake-up

BRK instruction

Notes 1: Vector addresses contain interrupt jump destination addresses.

2: Reset functions in the same way as an interrupt with the highest priority.

17

FFDF16

FFDD16

FFDE16

FFDC16

At completion of A-D conversion

At falling of port P3 (at input) input logical level AND

At BRK instruction execution

External interrupt (falling valid)

Non-maskable software interrupt

21

Page 23

Interrupt request bi

t

t

I n t e r r u p t e n a b l e b i t

I n t e r r u p t d i s a b l e f l a g ( I )

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Fig. 15 Interrupt control

b7

b7

b7

b0

b0

b0

BRK instruction

Interrupt edge selection register

(INTEDGE : address 003A

INT0 active edge selection bit

INT

1

active edge selection bit

Not used (returns “0” when read)

INT

2

active edge selection bit

INT

3

active edge selection bit

INT

4

active edge selection bit

INT

5

active edge selection bit

Not used (returns “0” when read)

Interrupt request register 1

(IREQ1 : address 003C

INT0/input buffer full interrupt request

bit

INT

1

/output buffer empty interrupt

request bit

Serial I/O receive interrupt/LRESET

request bit

Serial I/O transmit/S

request bit

Timer X interrupt request bit

Timer Y interrupt request bit

Timer 1 interrupt request bit

Timer 2/INT

5

interrupt request bit

Interrupt control register 1

(ICON1 : address 003E

INT0/input buffer full interrupt enable bit

INT

1

/output buffer empty interrupt enable

bit

Serial I/O receive interrupt/LRESET

enable bit

Serial I/O transmit/S

enable bit

Timer X interrupt enable bit

Timer Y interrupt enable bit

Timer 1 interrupt enable bit

Timer 2/INT

5

interrupt enable bit

16

)

16

)

CL

, SDA interrupt

16

)

CL

, S

DA

interrupt

Rese

0 : Falling edge active

1 : Rising edge active

b7

b7

0

Interrupt request

b0

Interrupt request register 2

(IREQ2 : address 003D

CNTR0/INT0 interrupt request bit

CNTR

1

/INT1 interrupt request bit

2

I

C interrupt request bit

INT

2

interrupt request bit

INT

3

interrupt request bit

INT

4

interrupt request bit

AD converter/key-on wake-up interrupt

request bit

Not used (returns “0” when read)

0 : No interrupt request issued

1 : Interrupt request issued

b0

Interrupt control register 2

(ICON2 : address 003F

CNTR0/INT0 interrupt enable bit

CNTR

1

/INT1 interrupt enable bit

2

I

C interrupt enable bit

INT

2

interrupt enable bit

INT

3

interrupt enable bit

INT

4

interrupt enable bit

AD converter/key-on wake-up interrupt

enable bit

Not used (returns “0” when read)

(Do not write “1” to this bit)

0 : Interrupts disabled

1 : Interrupts enabled

16

)

16

)

Fig. 16 Structure of interrupt-related registers (1)

22

Page 24

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

b 7

b 0

I n t e r r u p t s o u r c e s e l e c t i o n r e g i s t e r

( I N T S E L : a d d r e s s 0 0 3 9

1 6

)

INT0/input buffer full interrupt source selection bit

0 : INT

0

interrupt

1 : Input buffer full interrupt

INT

1

/output buffer empty interrupt source selection bit

0 : INT

1

interrupt

1 : Output buffer empty interrupt

Serial I/O receive/LRESET interrupt source selection bit

0 : Serial I/O receive

1 : LRESET interrupt

Serial I/O transmit/S

CL

, SDA interrupt source selection bit

0 : Serial I/O transmit interrupt

1 : S

CL

, SDA interrupt

Timer 2/INT

5

interrupt source selection bit

0 : Timer 2 interrupt

1 : INT

CNTR

0 : CNTR

1 : INT

CNTR

0 : CNTR

1 : INT

5

interrupt

0

/INT0 interrupt source selection bit

0

interrupt

0

interrupt

1

/INT1 interrupt source selection bit

1

interrupt

1

interrupt

AD converter/key-on wake-up interrupt source selection bit

0 : A-D

converter interrupt

1 : Key-on wake-up interrupt

Fig. 17 Structure of interrupt-related registers (2)

23

Page 25

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Key Input Interrupt (Key-on Wake Up)

A Key input interrupt request is generated by applying “L” level to

any pin of port P3 that have been set to input mode. In other

words, it is generated when the logical AND of all port P3 input

P o r t P X x

“ L ” l e v e l o u t p u t

P o r t c o n t r o l r e g i s t e r 1

P 3

P 3

P 3

7

o u t p u t

6

o u t p u t

5

o u t p u t

✻

✻

✻

B i t 5 = “ 0 ”

✻✻

✻✻

✻✻

Port P3

direction register = “1”

P o r t P 3

7

l a t c h

Port P3

direction register = “1”

P o r t P 3

6

l a t c h

P o r t P 3

5

l a t c h

Port P3

direction register = “1”

goes from “1” to “0”. An example of using a key input interrupt is

shown in Figure 18, where an interrupt request is generated by

pressing one of the keys consisted as an active-low key matrix

which inputs to ports P30–P33.

7

6

5

K e y i n p u t i n t e r r u p t r e q u e s t

P 3

4

o u t p u t

P3

3

P3

P 3

1

0

P 3

input

2

input

i n p u t

i n p u t

✻

P o r t c o n t r o l r e g i s t e r 1

B i t 4 = “ 1 ”

✻

✻

✻

✻

✻✻

✻✻

✻✻

✻✻

✻✻

P o r t P 3

l a t c h

Port P3

latch

Port P3

latch

Port P3

latch

P o r t P 30

l a t c h

P o r t P 3

d i r e c t i o n r e g i s t e r = “ 1 ”

4

Port P3

direction register = “0”

3

P o r t P 3

d i r e c t i o n r e g i s t e r = “ 0 ”

2

P o r t P 3

d i r e c t i o n r e g i s t e r = “ 0 ”

1

P o r t P 3

d i r e c t i o n r e g i s t e r = “ 0 ”

4

3

Port P3 input circuit

Comparator circuit

2

1

0

✻ P-channel transistor for pull-up

✻✻ CMOS output buffer

Fig. 18 Connection example when using key input interrupt and port P3 block diagram

24

Page 26

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

TIMERS

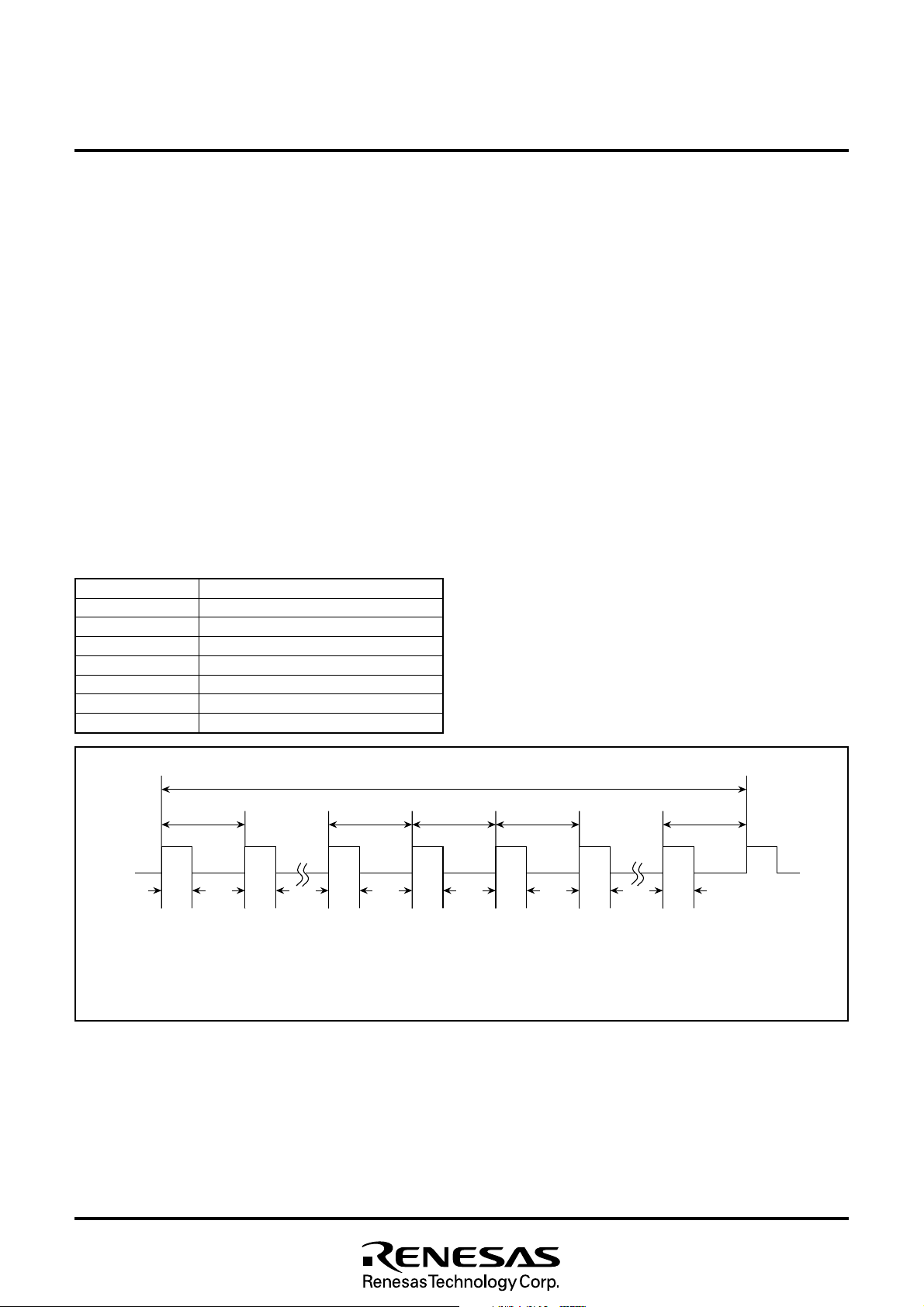

The 3885 group has four timers: timer X, timer Y, timer 1, and

timer 2.

The division ratio of each timer or prescaler is given by 1/(n + 1),

where n is the value in the corresponding timer or prescaler latch.

All timers are count down structure. When the timer reaches

“0016”, an underflow occurs at the next count pulse and the corresponding timer latch is reloaded into the timer and the count is

continued. When a timer underflows, the interrupt request bit corresponding to that timer is set to “1”.

b7

Fig. 19 Structure of timer XY mode register

b 0

Timer XY mode register

(TM : address 0023

T i m e r X o p e r a t i n g m o d e b i t

b 1 b 0

0 0 : T i m e r m o d e

0 1 : P u l s e o u t p u t m o d e

1 0 : E v e n t c o u n t e r m o d e

1 1 : P u l s e w i d t h m e a s u r e m e n t m o d e

C N T R

0

a c t i v e e d g e s e l e c t i o n b i t

0 : I n t e r r u p t a t f a l l i n g e d g e

C o u n t a t r i s i n g e d g e i n e v e n t

c o u n t e r m o d e

1 : I n t e r r u p t a t r i s i n g e d g e

C o u n t a t f a l l i n g e d g e i n e v e n t

c o u n t e r m o d e

T i m e r X c o u n t s t o p b i t

0 : C o u n t s t a r t

1 : C o u n t s t o p

Timer Y operating mode bit

b5b4

0 0 : Timer mode

0 1 : Pulse output mode

1 0 : Event counter mode

1 1 : Pulse width measureme nt mode

CNTR

1

active edge selection bit

0: Interrupt at falling edge

Count at rising edge in event

counter mode

1: Interrupt at rising edge

Count at falling edge in event

counter mode

Timer Y count stop bit

0: Count start

1: Count stop

16

)

Timer 1 and Timer 2

The count source of prescaler 12 is the oscillation frequency divided by 16. The output of prescaler 12 is counted by timer 1 and

timer 2, and a timer underflow sets the interrupt request bit.

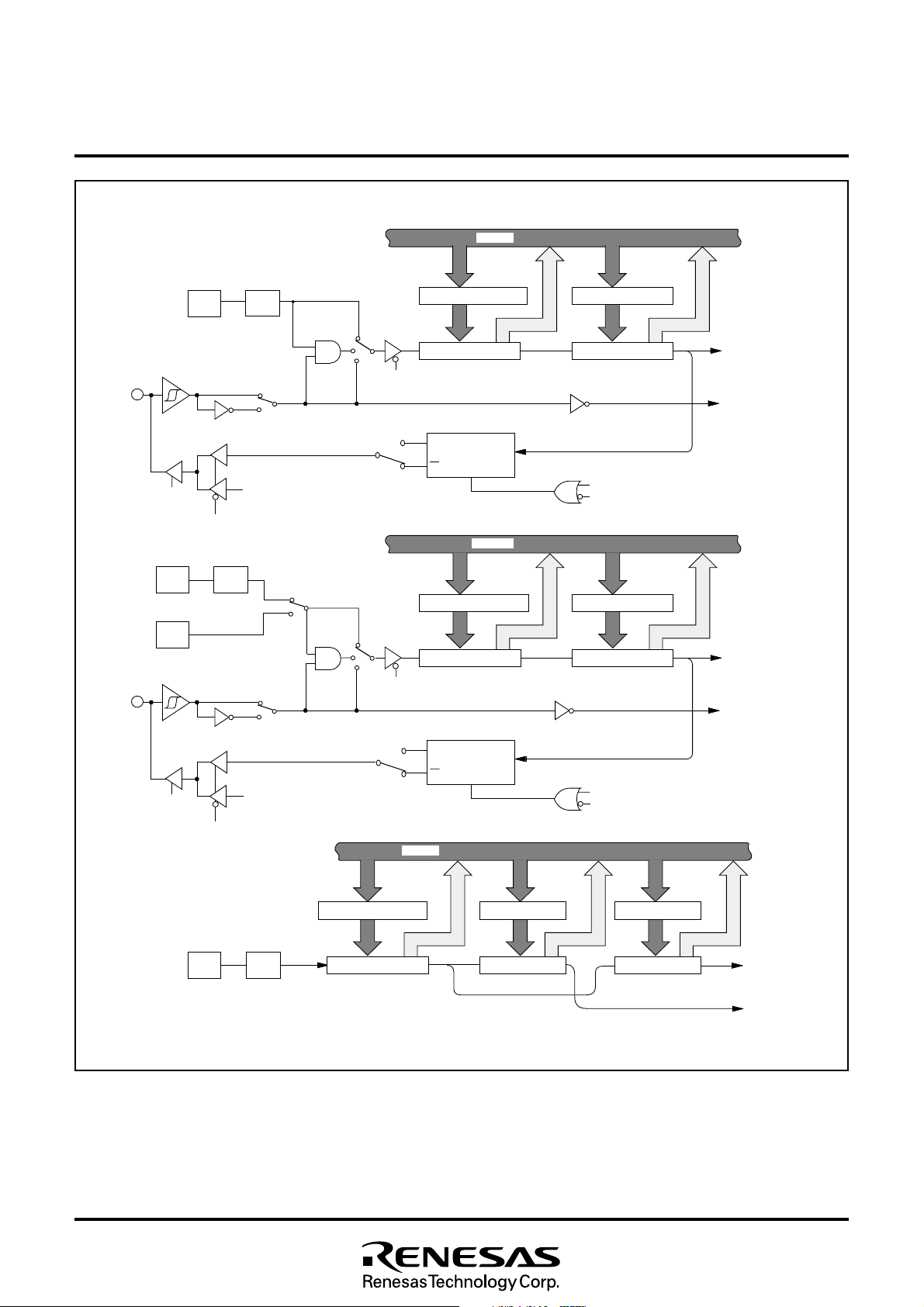

Timer X and Timer Y

Timer X and Timer Y can each select one of four operating modes

by setting the timer XY mode register.

(1) Timer Mode

The timer counts f(XIN)/16.

(2) Pulse Output Mode

Timer X (or timer Y) counts f(XIN)/16. Whenever the contents of

the timer reach “0016”, the signal output from the CNTR0 (or

CNTR1) pin is inverted. If the CNTR0 (or CNTR1) active edge selection bit is “0”, output begins at “ H”.

If it is “1”, output starts at “L”. When using a timer in this mode, set

the corresponding port P54 ( or port P55) direction register to output mode.

(3) Event Counter Mode

Operation in event counter mode is the same as in timer mode,

except that the timer counts signals input through the CNTR0 or

CNTR1 pin.

When the CNTR0 (or CNTR1) active edge selection bit is “0”, the

rising edge of the CNTR0 (or CNTR1) pin is counted.

When the CNTR0 (or CNTR1) active edge selection bit is “1”, the

falling edge of the CNTR0 (or CNTR1) pin is counted.

(4) Pulse Width Measurement Mode

If the CNTR0 (or CNTR1) active edge selection bit is “0”, the timer

counts f(XIN)/16 while the CNTR0 (or CNTR1) pin is at “H”. If the

CNTR0 (or CNTR1) active edge selection bit is “1”, the timer

counts while the CNTR0 (or CNTR1) pin is at “L”.

The count can be stopped by setting “1” to the timer X (or timer Y)

count stop bit in any mode. The corresponding interrupt request

bit is set each time a timer overflows.

The count source for timer Y in the timer mode or the pulse output

mode can be selected from either f(XIN)/16 or f(XCIN) by the timer

Y count source selection bit of the port control register 2 (bit 5 of

PCTL2).

25

Page 27

s

D a t a b u

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

( f ( X

4

/ C N T R

P 5

d i r e c t i o n r e g i s t e r

(f(X

CIN

) in low-speed mode)

P 55/ C N T R

direction register

O s c i l l a t o r

I N

C I N

) i n l o w - s p e e d m o d e )

0

4

P o r t P 5

Pulse output mode

O s c i l l a t o r

I N

)

O s c i l l a t o r

f ( X

C I N

)

1

Port P5

5

Pulse output mode

)

C N T R

e d g e s e l e c t i o n

b i t

Divider

1 / 1 6f ( X

CNTR

edge selection

bit

D i v i d e r

1 / 1 6f ( X

0

a c t i v e

“ 0 ”

“1”

P o r t P 5

4

l a t c h

T i m e r Y c o u n t s o u r c e

s e l e c t i o n b i t

“ 0 ”

“1”

1

active

“ 0 ”

“ 1 ”

P o r t P 5 5

l a t c h

P u l s e w i d t h

m e a s u r e m e n t

m o d e

E v e n t

c o u n t e r

m o d e

C N T R

e d g e s e l e c t i o n

b i t

Pulse width

measurement mode

Event

counter

mode

C N T R

e d g e s e l e c t i o n

b i t

Timer mode

Pulse output mode

T i m e r X c o u n t s t o p b i t

0

a c t i v e

“ 1 ”

“ 0 ”

Timer mode

Pulse output mode

Timer Y count stop bit

1

a c t i v e

“1”

“0”

Data bus

P r e s c a l e r X l a t c h ( 8 )

Prescaler X (8)

Q

T o g g l e f l i p - f l o p

Q

R

Data bus

Prescaler Y latch (8)

Prescaler Y (8)

Q

Toggle flip-flop

Q

R

T i m e r X l a t c h ( 8 )

T i m e r X ( 8 )

T o t i m e r X i n t e r r u p t

r e q u e s t b i t

T o C N T R

0

i n t e r r u p t

r e q u e s t b i t

T

Timer X latch write pulse

Pulse output mode

T i m e r Y l a t c h ( 8 )

Timer Y (8)

To timer Y interrupt

request bit

To CNTR

1

interrupt

request bit

T

T i m e r Y l a t c h w r i t e p u l s e

P u l s e o u t p u t m o d e

Prescaler 12 latch (8)

D i v i d e rO s c i l l a t o r

Prescaler 12 (8)

(f(X

CIN

) in low-speed mode)

1/16f(XIN)

Fig. 20 Block diagram of timer X, timer Y, timer 1, and timer 2

26

Timer 1 latch (8)

Timer 1 (8)

Timer 2 latch (8)

T i m e r 2 ( 8 )

To timer 2 interrupt

request bit

T o t i m e r 1 i n t e r r u p t

r e q u e s t b i t

Page 28

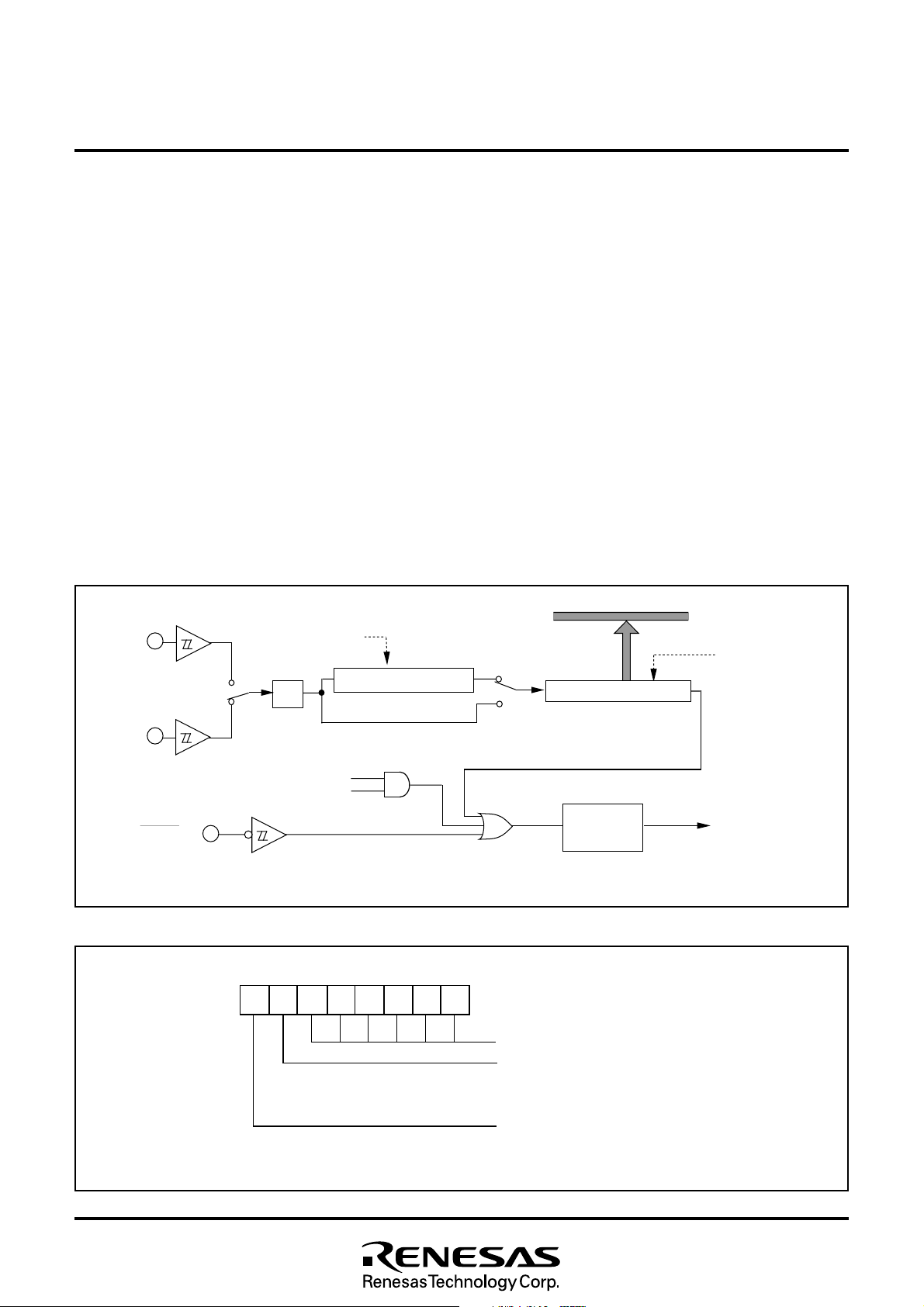

WATCHDOG TIMER

The watchdog timer gives a mean of returning to the reset status

when a program cannot run on a normal loop (for example, because of a software run-away). The watchdog timer consists of an

8-bit watchdog timer L and an 8-bit watchdog timer H.

Basic Operation of Watchdog Timer

When any data is not written into the watchdog timer control register (WDTCON) after resetting, the watchdog timer is in the stop

state. The watchdog timer starts to count down by writing an optional value into the watchdog timer control register (WDTCON) and

an internal reset occurs at an underflow of the watchdog timer H.

Accordingly, programming is usually performed so that writing to

the watchdog timer control register (WDTCON) may be started before an underflow. When the watchdog timer control register

(WDTCON) is read, the values of the high-order 6 bits of the

watchdog timer H, STP instruction disable bit, and watchdog timer

H count source selection bit are read.

Initial Value of Watchdog Timer

At reset or writing to the watchdog timer control register

(WDTCON), each watchdog timer H and L is set to “FF16”.

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

●Watchdog timer H count source selection bit operation

Bit 7 of WDTCON permits selecting a watchdog timer H count

source. When this bit is set to “0”, the count source becomes the

underflow signal of watchdog timer L. The detection time is set to

131.072 ms at f(XIN)=8 MHz and 32.768 s at f(XCIN)=32 kHz .

When this bit is set to “1”, the count source becomes the signal

divided by 16 for f(XIN) (or f(XCIN) in low speed mode). The detection time in this case is set to 512 µs at f(XIN)=8 MHz and 128 ms

at f(XCIN)=32 kHz . This bit is cleared to “0” after resetting.

●STP instruction disable bit

Bit 6 of WDTCON permits disabling the STP instruction when the

watchdog timer is in operation.

When this bit is “0”, the STP instruction is enabled.

When this bit is “1”, the STP instruction is disabled.

When this bit is “1”, the STP instruction execution cause an internal reset. When this bit is set to “1”, it cannot be rewritten to “0” by

program. This bit is cleared to “0” after resetting.

16” is set when

“FF

XCIN

Main clock division

ratio selection bits

(Note)

XIN

STP instruction disable bit

RESET

Note: Either high-speed, middle-speed or low-speed mode is selected by bits 7 and 6 of the CPU mode register.

watchdog timer

control register is

written to.

“10”

1/16

“00”

“01”

STP instruction

Fig. 21 Block diagram of Watchdog timer

b 7

Watchdog timer L (8)

“0”

“1”

Watchdog timer H count

source selection bit

b0

Watchdog timer H (8)

Watchdog timer control register

(WDTCON : address 001E

Watchdog timer H (for read-out of high-order 6 bit)

STP instruction disable bit

0: STP instruction enabled

1: STP instruction dis abled

Reset

circuit

Data bus

16” is set when

“FF

watchdog timer

control register is

written to.

Internal reset

16

)

Fig. 22 Structure of Watchdog timer control register

Watchdog timer H count source selection bit

0: Watchdog timer L underflow

1: f(X

IN

)/16 or f(X

CIN

)/16

27

Page 29

MITSUBISHI MICROCOMPUTERS

3885 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

PULSE WIDTH MODULATION (PWM)

OUTPUT CIRCUIT

The 3885 group has two PWM output circuits, PWM0 and PWM1,