Page 1

Mitsubishi 32-bit RISC Single-chip Microcomputers

M32R Family M32R/ECU Series

32172

32173

Group

User’s Manual

http://www.infomicom.maec.co.jp/indexe.htm

Before using this material, please visit the above website to confirm that this is

the most current document available.

Revision date: Oct. 5, 2001

Rev. 1.0

Page 2

Keep safety first in your circuit designs!

•

Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with

them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

•

These materials are intended as a reference to assist our customers in the selection of the

Mitsubishi semiconductor product best suited to the customer's application; they do not

convey any license under any intellectual property rights, or any other rights, belonging to

Mitsubishi Electric Corporation or a third party.

•

Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement

of any third-party's rights, originating in the use of any product data, diagrams, charts,

programs, algorithms, or circuit application examples contained in these materials.

•

All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these

materials, and are subject to change by Mitsubishi Electric Corporation without notice due

to product improvements or other reasons. It is therefore recommended that customers

contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product

distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Mitsubishi Electric Corporation assumes no responsibility for any damage, liability , or other

loss rising from these inaccuracies or errors.

Please also pay attention to information published by Mitsubishi Electric Corporation by

various means, including the Mitsubishi Semiconductor home page (http://

www.mitsubishichips.com).

•

When using any or all of the information contained in these materials, including product

data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information

and products. Mitsubishi Electric Corporation assumes no responsibility for any damage,

liability or other loss resulting from the information contained herein.

•

Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use

in a device or system that is used under circumstances in which human life is potentially at

stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any

specific purposes, such as apparatus or systems for transportation, vehicular, medical,

aerospace, nuclear, or undersea repeater use.

•

The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

•

If these products or technologies are subject to the Japanese export control restrictions,

they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/

or the country of destination is prohibited.

•

Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor

product distributor for further details on these materials or the products contained therein.

Page 3

REVISION HISTORY 32172/32173 GROUP USER’S MANUAL

Rev. Date Description

Page Summary

1.0 10/5/2001 - First edition issued

Page 4

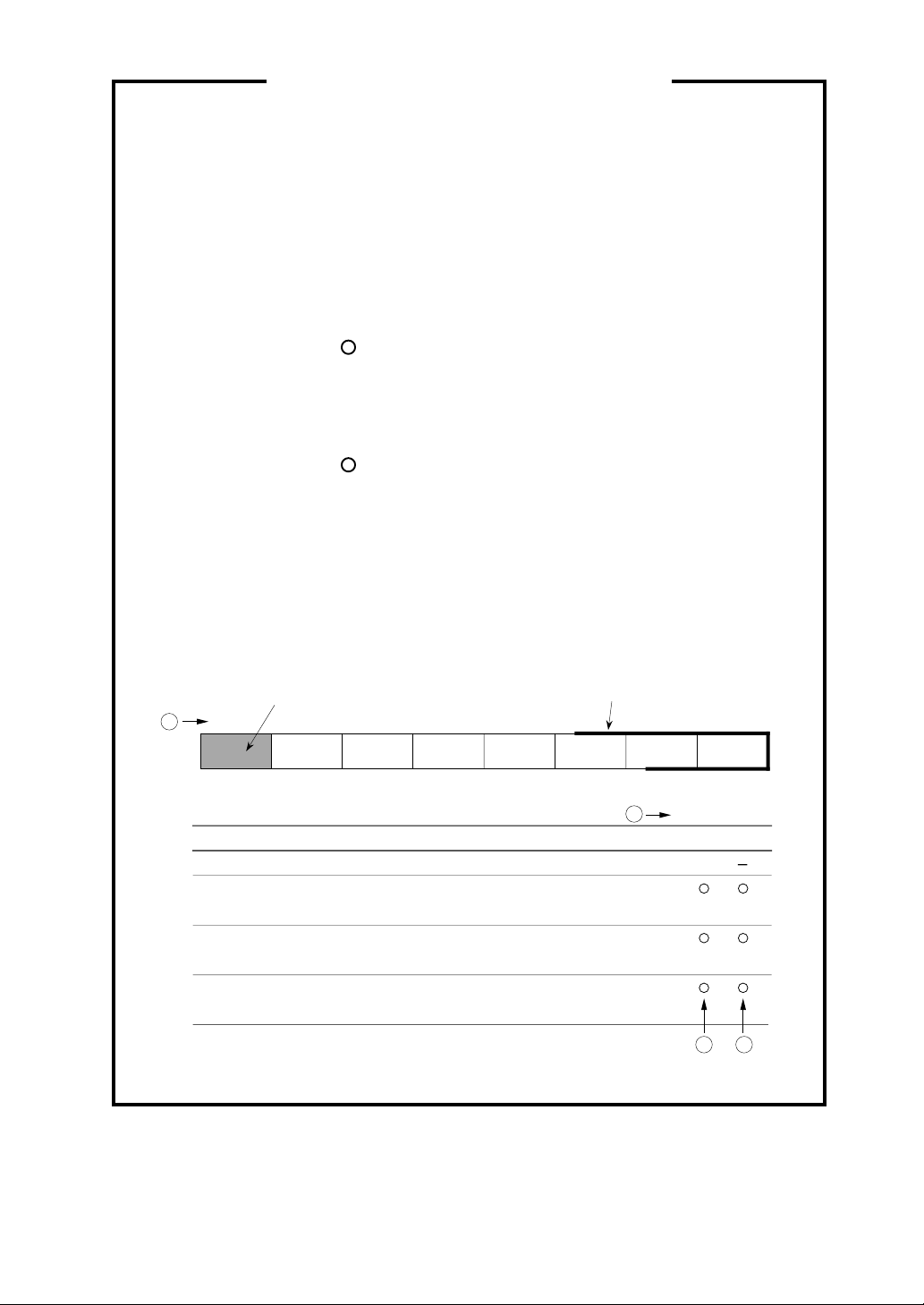

How to read internal I/O register tables

➀ Bit Numbers: Each register is connected with an internal bus of 16-bit

wide, so the bit numbers of the registers located at even

addresses are D0-D7, and those at odd addresses are

D8-D15.

➁ State of Register at Reset: Represents the initial state of each register

immediately after reset with hexadecimal numbers

(undefined bits after reset are indicated each in column ➂.)

➂ At read: ... read enabled

? ... read disabled (read value invalid)

0 ... Read always as 0

1 ... Read always as 1

④ At write: : Write enabled

∆ : Write enable conditionally

(include some conditions at write)

- : Write disabled (Written value invalid)

<Example of representation>

Not implemented

in the shaded portion.

1

D

0 Not assigned.

1 Abit

2

3

Bit name Function

(...................)

Bbit

(...................)

Cbit

(...................)

1234D0

Abit

Bbit Cbit

0: ----1: -----

0: ----1: -----

0: ----1: ----

Registers represented with thick rectangles

are accessible only with halfwords or words

(not accessible with bytes)

-

2

.

<at reset: H'04>

WR

0

3 4

Page 5

CONTENTS

CHAPTER 1 OVERVIEW

1.1 Overview................................................................................................................ 1-2

1.1.1 M32R Family CPU Core.....................................................................1-2

1.1.2 Built-in Multiply-Accumulate Operation Function................................ 1-3

1.1.3 Built-in Flash Memory and RAM......................................................... 1-3

1.1.4 Built-in Clock Multiplier Circuit............................................................1-4

1.1.5 Built-in Powerful Peripheral Functions ...............................................1-4

1.1.6 Built-in Full-CAN Function .................................................................. 1-5

1.1.7 Two Built-in D-A Converters...............................................................1-5

1.1.8 Built-in Timer/Arithmetic Circuits for PD (Phase Digital) Sensors ......1-6

1.1.9 Built-in Debug Function ...................................................................... 1-6

1.2 Block Diagram ........................................................................................................ 1-7

1.3 Pin Functions .......................................................................................................... 1-10

1.4 Pin Layout............................................................................................................... 1-18

CHAPTER 2 CPU

2.1 CPU Registers ....................................................................................................... 2-2

2.2 General-purpose Registers.................................................................................... 2-2

2.3 Control Registers ................................................................................................... 2-3

2.3.1 Processor Status Word Register: PSW (CR0) .........................................2-4

2.3.2 Condition Bit Register: CBR (CR1) ..........................................................2-5

2.3.3 Interrupt Stack Pointer: SPI (CR2) ...........................................................2-5

User Stack Pointer: SPU (CR3)

2.3.4 Backup PC: BPC (CR6) ...........................................................................2-5

2.4 Accumulator........................................................................................................... 2-6

2.5 Program Counter ................................................................................................... 2-6

(1)

Page 6

2.6 Data Formats ......................................................................................................... 2-7

2.6.1 Data Types ...............................................................................................2-7

2.6.2 Data Formats............................................................................................2-8

CHAPTER 3 ADDRESS SPACE

3.1 Outline of the Address Space ................................................................................. 3-2

3.2 Operation Modes .................................................................................................... 3-5

3.3 Internal ROM and External Extended Areas........................................................... 3-8

3.3.1 Internal ROM Area .............................................................................. 3-8

3.3.2 External Extended Area ...................................................................... 3-8

3.4 Internal RAM and SFR Areas ................................................................................. 3-9

3.4.1 Internal RAM Area...............................................................................3-9

3.4.2 SFR (Special Function Register) Area ................................................3-9

3.5 EIT Vector Entry ..................................................................................................... 3-35

3.6 ICU Vector Table .................................................................................................... 3-36

3.7 Precautions on Address Space .............................................................................. 3-38

CHAPTER 4 EIT

4.1 Outline of EIT.......................................................................................................... 4-2

4.2 EIT Events .............................................................................................................. 4-3

4.2.1 Exceptions...........................................................................................4-3

4.2.2 Interrupts .............................................................................................4-3

4.2.3 Trap ..................................................................................................... 4-3

4.3 EIT Processing Procedure...................................................................................... 4-4

4.4 EIT Processing Mechanism .................................................................................... 4-6

4.5 Accepting EIT Events ............................................................................................. 4-7

4.6 Saving and Restoring PC and PSW ....................................................................... 4-8

4.7 EIT Vector Entry ..................................................................................................... 4-10

4.8 Exception Handling................................................................................................. 4-11

4.8.1 Reserved Instruction Exception (RIE) .................................................4-11

4.8.2 Address Exception (AE) ......................................................................4-13

(2)

Page 7

4.9 Interrupt Handling ................................................................................................... 4-15

4.9.1 Reset Interrupt (RI).............................................................................. 4-15

4.9.2 System Break Interrupt (SBI) .............................................................. 4-16

4.9.3 External Interrupt (EI) .......................................................................... 4-18

4.10 Trap Handling ....................................................................................................... 4-20

4.10.1 Trap (TRAP) ...................................................................................... 4-20

4.11 EIT Priority ............................................................................................................ 4-22

4.12 Example of EIT Processing .................................................................................. 4-23

4.13 Precautions on EIT ............................................................................................... 4-25

CHAPTER 5 INTERRUPT CONTROLLER (ICU)

5.1 Outline of the Interrupt Controller (ICU).................................................................. 5-2

5.2 Interrupt Sources of Internal Peripheral I/Os .......................................................... 5-4

5.3 ICU Related Registers ............................................................................................ 5-6

5.3.1 Interrupt Vector Register ....................................................................5-7

5.3.2 Interrupt Mask Register ...................................................................... 5-8

5.3.3 SBI (System Break Interrupt) Control Register .................................. 5-9

5.3.4 Interrupt Control Registers .................................................................5-10

5.4 ICU Vector Table .................................................................................................... 5-14

5.5 Description of Interrupt Operation........................................................................... 5-17

5.5.1 Accepting Interrupts from Internal Peripheral I/O ............................... 5-17

5.5.2 Processing of Internal Peripheral I/O Interrupts by Handler...............5-20

5.6 Description of System Break Interrupt (SBI) Operation .......................................... 5-22

5.6.1 Accepting SBI Interrupt ......................................................................5-22

5.6.2 SBI Processing by Handler ................................................................5-22

CHAPTER 6 INTERNAL MEMORY

6.1 Outline of the Internal Memory .............................................................................. 6-2

6.2 Internal RAM.......................................................................................................... 6-2

6.3 Internal Flash Memory ........................................................................................... 6-2

6.4 Internal Flash Memory Related Registers ............................................................. 6-3

(3)

Page 8

6.4.1 Flash Mode Register ..........................................................................6-4

6.4.2 Flash Status Registers .......................................................................6-5

6.4.3 Flash Control Registers......................................................................6-8

6.4.4 Virtual-flash L Bank Registers ............................................................ 6-14

6.4.5 Virtual-flash S Bank Registers............................................................ 6-15

6.5 Programming the Internal Flash Memory .............................................................. 6-16

6.5.1 Outline of Flash Memory Programming.............................................. 6-16

6.5.2 Controlling Operation Modes during Flash Programming ...................6-22

6.5.3 Procedure for Programming the Internal Flash Memory ....................6-25

6.5.4 Flash Programming Time (Reference Data) ...................................... 6-36

6.6 Boot ROM .............................................................................................................. 6-37

6.7 Virtual-flash Emulation Function ............................................................................ 6-38

6.7.1 Virtual-Flash Emulation Areas............................................................6-40

6.7.2 Transition to Virtual-Flash Emulation Mode ....................................... 6-45

6.7.3 Application Example for Virtual-Flash Emulation Mode ..................... 6-46

6.8 Connecting a Serial Programmer .......................................................................... 6-48

6.9 Precautions on Rewriting Flash Memory ............................................................... 6-50

CHAPTER 7 RESET

7.1 Outline of Reset ..................................................................................................... 7-2

7.2 Reset Operation..................................................................................................... 7-2

7.2.1 Power-on Reset.................................................................................. 7-2

7.2.2 Reset during Operation ......................................................................7-2

7.2.3 Reset Vector Movement during Flash Rewrite...................................7-2

7.3 Internal State Immediately after Reset .................................................................. 7-3

7.4 Precautions to Be Taken Immediately after Reset ................................................ 7-5

CHAPTER 8 INPUT/OUTPUT PORTS AND PIN FUNCTIONS

8.1 Outline of Input/Output Ports .................................................................................. 8-2

8.2 Selecting Pin Functions ......................................................................................... 8-4

(4)

Page 9

8.3 Input/Output Port Related Registers....................................................................... 8-6

8.3.1 Port Data Registers ............................................................................. 8-8

8.3.2 Port Direction Registers ......................................................................8-9

8.3.3 Port Operation Mode Registers...........................................................8-10

8.4 Port Peripheral Circuits.......................................................................................... 8-31

8.5 Precautions on Input/Output Ports......................................................................... 8-39

CHAPTER 9 DMAC

9.1 Outline of DMAC.................................................................................................... 9-2

9.2 DMAC Related Registers....................................................................................... 9-5

9.2.1 DMA Channel Control Registers ........................................................9-7

9.2.2 DMA Request Extended Cause Register ........................................... 9-18

9.2.3 DMA Software Request Generation Registers...................................9-29

9.2.4 DMA Source Address Registers......................................................... 9-30

9.2.5 DMA Destination Address Registers .................................................. 9-31

9.2.6 DMA Transfer Count Registers ..........................................................9-32

9.2.7 DMA Interrupt Request Status Registers ...........................................9-33

9.2.8 DMA Interrupt Mask Registers ...........................................................9-35

9.3 Functional Description of DMAC............................................................................ 9-39

9.3.1 Cause of DMA Request...................................................................... 9-39

9.3.2 DMA Transfer Processing Procedure................................................. 9-49

9.3.3 Starting DMA ...................................................................................... 9-50

9.3.4 Priority of DMA Channels ................................................................... 9-50

9.3.5 Gaining and Releasing Control of the Internal Bus ............................9-51

9.3.6 Transfer Unit....................................................................................... 9-51

9.3.7 Transfer Count ................................................................................... 9-51

9.3.8 Address Space ................................................................................... 9-52

9.3.9 Transfer Operation .............................................................................9-52

9.3.10 End of DMA and Interrupt................................................................. 9-55

9.3.11 Register Status after End of DMA Transfer......................................9-55

9.4 Precautions on Using DMAC ................................................................................. 9-56

(5)

Page 10

CHAPTER 10 INPUT/OUTPUT TIMERS

10.1 Outline of the Input/Output Timers....................................................................... 10-2

10.2 Common Timer Unit............................................................................................. 10-8

10.2.1 Register Map of the Common Timer Unit.........................................10-8

10.2.2 Prescaler Unit...................................................................................10-10

10.2.3 Input Processing Control Unit........................................................... 10-11

10.2.4 Output Flip-flop Control Unit.............................................................10-20

10.2.5 Interrupt Control Unit ........................................................................ 10-24

10.3 TMS (Input Related 16-bit Timers) ...................................................................... 10-43

10.3.1 Outline of the TMS ........................................................................... 10-43

10.3.2 Functional Outline of the TMS..........................................................10-43

10.3.3 TMS Related Register Map .............................................................. 10-45

10.3.4 TMS Control Register.......................................................................10-46

10.3.5 TMS Counter (TMS0CT) ..................................................................10-47

10.3.6 TMS Measure Registers (TMS0MR3~0).......................................... 10-48

10.3.7 TMS Old Measure Registers (TMS0OLDMR3~0) ............................ 10-49

10.3.8 Operation of TMS Measure Input ..................................................... 10-50

10.4 TML (Input Related 32-bit Timers)....................................................................... 10-52

10.4.1 Outline of the TML............................................................................10-52

10.4.2 Functional Outline of the TML ..........................................................10-53

10.4.3 TML Related Register Map .............................................................. 10-54

10.4.4 TML Control Register .......................................................................10-55

10.4.5 TML Counters................................................................................... 10-56

10.4.6 TML Measure Registers ................................................................... 10-57

10.4.7 TML Old Measure Registers ............................................................ 10-58

10.4.8 Operation of TML Measure Input ..................................................... 10-59

10.5 TID (Input Related 16-bit Timers) ........................................................................ 10-61

10.5.1 Outline of the TID .............................................................................10-61

10.5.2 TID Related Register Map................................................................10-63

10.5.3 TID Control & Prescaler Enable Registers ....................................... 10-64

10.5.4 TID Counters (TID0CT and TID1CT) ............................................... 10-66

10.5.5 TID Reload Registers (TID0RL and TID1RL)...................................10-67

10.5.6 Outline of Each TID Operation Mode ...............................................10-68

10.6 TOM (Output Related 16-bit Timers) ................................................................... 10-75

(6)

Page 11

10.6.1 Outline of the TOM ...........................................................................10-75

10.6.2 Outline of Each TOM Operation Mode ............................................. 10-77

10.6.3 TOM Related Register Map.............................................................. 10-79

10.6.4 PWM Output Disable Registers........................................................ 10-82

10.6.5 PWM Output Disable Control Registers ........................................... 10-84

10.6.6 TOM Control Registers..................................................................... 10-88

10.6.7 TOM Counters..................................................................................10-90

10.6.8 TOM Reload 0 Registers..................................................................10-92

10.6.9 TOM Reload 1 Registers..................................................................10-94

10.6.10 TOM Enable Protect Registers....................................................... 10-96

10.6.11 TOM Count Enable Registers ........................................................ 10-98

10.6.12 TID Control & Prescaler Enable Registers ..................................... 10-100

10.6.13 Operation of TOM in PWM Output Mode .......................................10-103

10.6.14 Operation of TOM in Single-shot Output Mode .............................. 10-107

(without Correction Function)

10.6.15 Operation of TOM in Single-shot PWM Output Mode ....................10-109

(without Correction Function)

10.6.16 Operation of TOM in Successive Output Mode..............................10-111

(without Correction Function)

10.6.17 TOM Output Disable Function........................................................10-113

10.6.18 Example for Using the TOM in Motor Control Applications ............ 10-116

CHAPTER 11 A-D CONVERTERS

11.1 Outline of the A-D Converters.............................................................................. 11-2

11.1.1 Conversion Modes ...........................................................................11-7

11.1.2 Operation Modes..............................................................................11-8

11.1.3 Special Operation Modes ................................................................. 11-11

11.1.4 Interrupt and DMA Transfer Requests by A-D Converters...............11-14

11.2 A-D Converter Related Registers ........................................................................ 11-15

11.2.1 A-D Single Mode Registers 0 ........................................................... 11-19

11.2.2 A-D Single Mode Registers 1 ........................................................... 11-23

11.2.3 A-D Scan Mode Registers 0.............................................................11-26

11.2.4 A-D Scan Mode Registers 1.............................................................11-30

11.2.5 A-D Conversion Speed Control Registers........................................11-33

(7)

Page 12

11.2.6 A-D Digital Input Control Registers .................................................. 11-35

11.2.7 A-D Successive Approximation Registers........................................11-36

11.2.8 A-D Comparate Data Registers........................................................ 11-38

11.2.9 10-bit A-D Data Registers ................................................................ 11-40

11.2.10 8-bit A-D Data Registers ................................................................ 11-42

11.3 Functional Description of the A-D Converters ...................................................... 11-44

11.3.1 How to Find Analog Input Voltages ................................................... 11-44

11.3.2 A-D Conversion of Successive Approximation Method....................11-45

11.3.3 Comparator Operation...................................................................... 11-47

11.3.4 Calculating the A-D Conversion Time ..............................................11-48

11.3.5 Definition of the A-D Conversion Accuracy .......................................11-52

11.4 Precautions on Using the A-D Converters........................................................... 11-54

CHAPTER 12 SERIAL I/O

12.1 Outline of Serial I/O ............................................................................................. 12-2

12.2 Serial I/O Related Registers ................................................................................ 12-8

12.2.1 SIO Interrupt Related Registers ........................................................12-10

12.2.2 SIO Interrupt Control Registers ........................................................ 12-12

12.2.3 SIO Transmit Control Registers ....................................................... 12-19

12.2.4 SIO Transmit/Receive Mode Registers ............................................ 12-21

12.2.5 SIO Transmit Buffer Registers ......................................................... 12-24

12.2.6 SIO Receive Buffer Registers .......................................................... 12-25

12.2.7 SIO Receive Control Registers ........................................................ 12-26

12.2.8 SIO Baud Rate Registers ................................................................. 12-29

12.3 Transmit Operation in CSIO Mode ...................................................................... 12-31

12.3.1 Setting the CSIO Baud Rate ............................................................ 12-31

12.3.2 Initial Settings for CSIO Transmission.............................................. 12-32

12.3.3 Starting CSIO Transmission.............................................................12-34

12.3.4 Successive CSIO Transmission ....................................................... 12-34

12.3.5 Processing at End of CSIO Transmission ........................................ 12-35

12.3.6 Transmit Interrupt ............................................................................. 12-35

12.3.7 Transmit DMA Transfer Request...................................................... 12-35

12.3.8 Typical CSIO Transmit Operation .................................................... 12-37

12.4 Receive Operation in CSIO Mode ....................................................................... 12-39

(8)

Page 13

12.4.1 Initial Settings for CSIO Reception...................................................12-39

12.4.2 Starting CSIO Reception .................................................................. 12-41

12.4.3 Processing at End of CSIO Reception .............................................12-41

12.4.4 About Successive Reception............................................................ 12-42

12.4.5 Flags Indicating the Status of CSIO Receive Operation .................. 12-43

12.4.6 Typical CSIO Receive Operation ..................................................... 12-44

12.5 Precautions on Using CSIO Mode....................................................................... 12-46

12.6 Transmit Operation in UART Mode ..................................................................... 12-48

12.6.1 Setting the UART Baud Rate ........................................................... 12-48

12.6.2 UART Transmit/Receive Data Formats............................................12-49

12.6.3 Initial Settings for UART Transmission............................................. 12-51

12.6.4 Starting UART Transmission............................................................12-53

12.6.5 Successive UART Transmission ...................................................... 12-53

12.6.6 Processing at End of UART Transmission ....................................... 12-54

12.6.7 Transmit Interrupt ............................................................................. 12-54

12.6.8 Transmit DMA Transfer Request...................................................... 12-54

12.6.9 Typical UART Transmit Operation ...................................................12-56

12.7 Receive Operation in UART Mode ...................................................................... 12-58

12.7.1 Initial Settings for UART Reception..................................................12-58

12.7.2 Starting UART Reception ................................................................. 12-60

12.7.3 Processing at End of UART Reception ............................................12-60

12.7.4 Typical UART Receive Operation ....................................................12-62

12.8 Fixed Period Clock Output Function .................................................................... 12-64

12.9 Precautions on Using UART Mode...................................................................... 12-65

CHAPTER 13 CAN MODULES

13.1 Outline of the CAN Modules ................................................................................ 13-2

13.2 CAN Module Related Registers........................................................................... 13-5

13.2.1 CAN Control Registers .....................................................................13-13

13.2.2 CAN Status Registers ......................................................................13-17

13.2.3 CAN Extended ID Registers.............................................................13-21

13.2.4 CAN Configuration Registers ...........................................................13-22

13.2.5 CAN Time stamp Count Registers ...................................................13-25

(9)

Page 14

13.2.6 CAN Error Count Registers .............................................................. 13-26

13.2.7 CAN Baud Rate Prescalers..............................................................13-27

13.2.8 CAN Interrupt Related Registers......................................................13-28

13.2.9 CAN Mask Registers ........................................................................ 13-39

13.2.10 CAN Message Slot Control Registers ............................................13-43

13.2.11 CAN Message Slots .......................................................................13-48

13.3 CAN Protocol ....................................................................................................... 13-78

13.3.1 CAN Protocol Frames ...................................................................... 13-78

13.4 Initialization of the CAN Module........................................................................... 13-81

13.4.1 Initializing the CAN Module ..............................................................13-81

13.4.2 CAN Timing ...................................................................................... 13-84

13.5 Transmitting Data Frames ................................................................................... 13-85

13.5.1 Data Frame Transmission Procedure .............................................. 13-85

13.5.2 Data Frame Transmit Operation....................................................... 13-87

13.5.3 Transmit Abort Function ................................................................... 13-88

13.6 Receiving Data Frames ....................................................................................... 13-89

13.6.1 Data Frame Reception Procedure.................................................... 13-89

13.6.2 Data Frame Receive Operation........................................................ 13-91

13.6.3 Reading Out a Received Data Frame ..............................................13-93

13.7 Transmitting Remote Frames .............................................................................. 13-95

13.7.1 Remote Frame Transmission Procedure ......................................... 13-95

13.7.2 Remote Frame Transmit Operation.................................................. 13-97

13.7.3

Reading Out a Received Data Frame When Set for Remote Frame Transmission ...

13.8 Receiving Remote Frames .................................................................................. 13-102

13.8.1 Remote Frame Reception Procedure............................................... 13-102

13.8.2 Remote Frame Receive Operation................................................... 13-104

13-100

CHAPTER 14 REAL-TIME DEBUGGER (RTD)

14.1 Outline of the Real-Time Debugger (RTD) .......................................................... 14-2

14.2 Pin Function of the RTD ...................................................................................... 14-3

14.3 Functional Description of the RTD....................................................................... 14-4

14.3.1 Outline of RTD Operation.................................................................14-4

14.3.2 Operation of RDR (Real-time RAM Content Output)........................ 14-5

(10)

Page 15

14.3.3 Operation of WRR (RAM Content Forcible Rewrite) ........................ 14-7

14.3.4 Operation of VER (Continuous Monitor)........................................... 14-9

14.3.5 Operation of VEI (Interrupt Request)................................................ 14-10

14.3.6 Operation of RCV (Recover from Runaway) .................................... 14-11

14.3.7 Method to Set a Specified Address when Using the RTD................14-12

14.3.8 Resetting the RTD............................................................................14-13

14.4 Typical Connection with the Host ........................................................................ 14-14

CHAPTER 15 PD MODULE

15.1 Outline of the PD Module..................................................................................... 15-2

15.2 PD Module Related Registers ............................................................................. 15-5

15.2.1 Prescaler Unit...................................................................................15-7

15.2.2 DACNT Reload Register ..................................................................15-10

15.2.3 TIN Input Processing Control Register..............................................15-11

15.2.4 TIN Interrupt Control Register ..........................................................15-13

15.2.5 TIN Interrupt Status Register............................................................ 15-14

15.2.6 DACNT Control Register .................................................................. 15-16

15.2.7 TPD Control Register .......................................................................15-17

15.2.8 DACNT Counter ...............................................................................15-18

15.2.9 TPD Counter .................................................................................... 15-19

15.2.10 TPD Measure Registers ................................................................. 15-20

15.2.11 PD Calculation Interrupt Control Register ......................................15-22

15.2.12 PD Calculation Interrupt Status Register........................................ 15-23

15.2.13 Position Detection Accuracy Select Register .................................15-25

15.2.14 TEP Control Registers.................................................................... 15-26

15.2.15 TEP Counters.................................................................................15-28

15.2.16 PD Data Updating Disable Event Select Registers ........................ 15-30

15.2.17 PD Data Updating Control Registers.............................................. 15-31

15.2.18 ABD Mask Registers ......................................................................15-32

15.2.19 S Error Detection Range Select Registers ..................................... 15-33

15.2.20 ABD Compare Registers ................................................................ 15-34

15.2.21 PITCH Compare Registers............................................................. 15-35

15.2.22 FDLT Registers ..............................................................................15-36

15.2.23 PITCHLT Registers ........................................................................15-37

(11)

Page 16

15.2.24 ABDLT Registers............................................................................ 15-38

15.2.25 RSUMLT Registers ........................................................................ 15-39

15.2.26 SSLT Registers ..............................................................................15-40

15.3 Initialization for PD Sensor Support..................................................................... 15-41

15.4 Precautions on Using the PD Module.................................................................. 15-44

CHAPTER 16 D-A CONVERTERS

16.1 Outline of the D-A Converters.............................................................................. 16-2

16.2 D-A Converter Related Registers ........................................................................ 16-5

16.2.1 Prescaler Unit...................................................................................16-8

16.2.2 DACNT Reload Register ..................................................................16-9

16.2.3 DACNT Control Register .................................................................. 16-10

16.2.4 DACNT Counter ...............................................................................16-11

16.2.5 D-A Control Register ........................................................................16-12

16.2.6 D-A Conversion Registers................................................................16-13

16.2.7 D-A0 Data Registers ........................................................................ 16-14

16.3 Functional Description of the D-A Converters ..................................................... 16-15

16.3.1 Single Mode ..................................................................................... 16-15

16.3.2 Continuous Mode .............................................................................16-15

CHAPTER 17 EXTERNAL BUS INTERFACE

17.1 External Bus Interface Related Signals ............................................................... 17-2

17.2 Read/Write Operations ........................................................................................ 17-14

17.3 Bus Arbitration ..................................................................................................... 17-20

17.4 Example for Connecting External Extension Memory ......................................... 17-22

CHAPTER 18 WAIT CONTROLLER

18.1 Outline of the Wait Controller............................................................................... 18-2

18.2 Wait Controller Related Registers ....................................................................... 18-6

18.2.1 Wait States Control Register ............................................................ 18-7

18.3 Typical Operation of the Wait Controller.............................................................. 18-8

(12)

Page 17

CHAPTER 19 RAM BACKUP MODE

19.1 Outline ................................................................................................................. 19-2

19.2 Example of RAM Backup when Power is Down .................................................. 19-2

19.2.1 Normal Operating State.................................................................... 19-3

19.2.2 RAM Backup State ...........................................................................19-4

19.3 Example of RAM Backup for Saving Power Consumption .................................. 19-5

19.3.1 Normal Operating State.................................................................... 19-6

19.3.2 RAM Backup State ...........................................................................19-7

19.3.3 Precautions to Be Observed at Power-on ........................................ 19-8

19.4 Exiting RAM Backup Mode (Wakeup) ................................................................. 19-9

CHAPTER 20 OSCILLATION CIRCUIT

20.1 Oscillator Circuit................................................................................................... 20-2

20.1.1 Example of an Oscillator Circuit ...........................................................20-2

20.1.2 System Clock Output Function.............................................................20-3

20.1.3 Oscillation Stabilization Time at Power-on ........................................... 20-4

20.2 Clock Generator Circuit ....................................................................................... 20-5

CHAPTER 21 JTAG

21.1 Outline of the JTAG ............................................................................................. 21-2

21.2 Configuration of the JTAG Circuit ........................................................................ 21-3

21.3 JTAG Registers ................................................................................................... 21-4

21.3.1 Instruction Register (JTAGIR) ..........................................................21-4

21.3.2 Data Registers.................................................................................. 21-5

21.4 Basic Operation of the JTAG ............................................................................... 21-6

21.4.1 Outline of the JTAG Operation ......................................................... 21-6

21.4.2 IR Path Sequence ............................................................................21-8

21.4.3 DR Path Sequence........................................................................... 21-10

21.4.4 Examining and Setting Data Registers............................................. 21-12

21.5 Boundary Scan Description Language ................................................................ 21-14

21.6 Precautions on Board Design when Connecting the JTAG ................................. 21-37

21.7 Processing Pins when Not Using the JTAG ........................................................ 21-39

(13)

Page 18

CHAPTER 22 POWER-UP/POWER-SHUTDOWN SEQUENCE

22.1 Configuration of the Power Supply Circuit ........................................................... 22-2

22.2 Power-On Sequence ........................................................................................... 22-3

22.2.1 Power-On Sequence When Not Using RAM Backup.......................22-3

22.2.2 Power-On Sequence When Using RAM Backup ............................. 22-4

22.3 Power-Shutdown Sequence ................................................................................ 22-5

22.3.1 Power-Shutdown Sequence When Not Using RAM Backup............ 22-5

22.3.2 Power-Shutdown Sequence When Using RAM Backup ..................22-6

CHAPTER 23 ELECTRICAL CHARACTERISTICS

23.1 Absolute Maximum Ratings ................................................................................. 23-2

23.2 Recommended Operating Conditions.................................................................. 23-3

23.3 DC Characteristics............................................................................................... 23-5

23.3.1 Electrical Characteristics ................................................................... 23-5

23.3.2 Flash Related Electrical Characteristics...........................................23-9

23.4 A-D Conversion Characteristics........................................................................... 23-10

23.5 D-A Conversion Characteristics........................................................................... 23-11

23.5.1 D-A Conversion Characteristics ........................................................23-11

23.6 AC Characteristics ............................................................................................... 23-12

23.6.1 Timing Requirements .......................................................................23-12

23.6.2 Switching Characteristics .................................................................23-16

23.6.3 AC Characteristics............................................................................ 23-19

CHAPTER 24 STANDARD CHARACTERISTICS

24.1 A-D Conversion Characteristics............................................................................ 24-2

(14)

Page 19

APPENDIX 1 MECHANICAL SPECIFICATIONS

Appendix 1.1 Dimensional Outline Drawing ................................................................

APPENDIX 2 INSTRUCTION PROCESSING TIME

Appendix 2.1 M32R/E Instruction Processing Time ....................................................

APPENDIX 3 PRECAUTIONS ABOUT NOISE

Appendix 3.1 Precautions about Noise........................................................................

Appendix 3.1.1 Reduction of Wiring Length ................................................

Appendix 3.1.2

Appendix 3.1.3 Processing Analog Input Pin Wiring ...................................

Appendix 3.1.4 Consideration about the Oscillator .....................................

Appendix 3.1.5 Processing Input/Output Ports ...........................................

Inserting a Bypass Capacitor between VSS and VCC Lines ........

Appendix

Appendix

Appendix

Appendix

3-2

Appendix

3-4

Appendix

3-5

Appendix

3-6

Appendix

3-8

1-2

2-2

3-2

(15)

Page 20

*** This is a blank page ***

(16)

Page 21

CHAPTER 1CHAPTER 1

OVERVIEW

1.1 Overview

1.2 Block Diagram

1.3 Pin Functions

1.4 Pin Layout

Page 22

1

1.1 Overview

1.1.1 M32R Family CPU Core

(1) Uses the RISC architecture

• The 32172/32173 are 32-bit, RISC single-chip microcomputers built around the M32R family

CPU core (hereafter referred to as the "M32R") and incorporating flash memory, RAM, and

various other peripheral functions... all integrated into a single chip.

• The M32R uses the RISC architecture. Memory accesses are performed using Load and Store

instructions, and various arithmetic operations are executed using register-to-register

operating instructions. The M32R internally has sixteen 32-bit general-purpose registers and a

total of 83 discrete instructions.

• In addition to Load and Store instructions, the M32R supports compound instructions such as

Load & Address Update and Store & Address Update. These instructions are useful for

speeding up data transfers.

Overview

1.1 Overview

(2) 5-stage pipelined processing

• The M32R uses 5-stage pipelined instruction processing consisting of Instruction Fetch,

Decode, Execute, Memory Access, and Write Back. Not just load and store instructions or

register-to-register operation instructions, compound instructions such as Load & Address

Update and Store & Address Update also are executed in one cycle.

• Instructions are entered into the execution stage in the order they are fetched, but this does not

always mean that the first instruction entered is executed first. If the execution of a load or store

instruction entered earlier is delayed by one or more wait cycles inserted in memory access, a

register-to-register operation instruction entered later may be executed before said load or

store instruction. By using "out-of-order-completion" like this, the M32R controls instruction

execution without wasting clock cycles.

(3) Compact instruction code

• Instructions of the M32R come in either a 16-bit instruction or a 32-bit instruction format. Use of

the 16-bit instruction format especially helps to reduce the code size of a program.

• Some 32-bit instructions can branch directly to a location 32 Mbytes forward or backward from

the currently executed instruction address. The availability of such instructions makes

programming easier than for architectures with segmented address spaces.

1-2 Rev.1.0

Page 23

1

1.1.2 Built-in Multiply-Accumulate Operation Function

(1) Built in high-speed multiplier

• The M32R incorporates a 32-bit x 16-bit high-speed multiplier/accumulator which allows the

processor to execute a 32-bit x 32-bit integer multiplication instruction in three cycles (one

cycle is 25 ns when CPU memory clock = 40 MHz).

(2) Supports Multiply-Accumulate operation instructions comparable to DSP

• The M32R supports the following four modes of Multiply-Accumulate operation instructions (or

multiplication instructions) based on a 56-bit accumulator:

16 high-order register bits x 16 high-order register bits

16 low-order register bits x 16 low-order register bits

All 32 register bits x 16 high-order register bits

All 32 register bits x 16 low-order register bits

• The M32R has instructions to round off the value stored in the accumulator to 16 or 32 bits, as

well as instructions to shift the accumulator value to adjust digits and store the digit-adjusted

value in a register. These instructions also can be executed in one cycle, so that when

combined with high-speed data transfer instructions such as Load & Address Update and

Store & Address Update, they enable the M32R to exhibit high data processing capability

comparable to that of DSP.

Overview

1.1 Overview

1.1.3 Built-in Flash Memory and RAM

• The 32172/32173 contains flash memory and RAM that can be accessed with no wait states,

making it possible to build a high-speed embedded system.

• The internal flash memory allows for on-board programming (you can write to it while being

mounted on the printed circuit board). Use of flash memory means the chip engineered at the

development phase can be used directly in mass-production, so that you can smoothly migrate

from prototype to mass-production without changing the printed circuit board.

• The internal flash memory can be rewritten 100 times.

• The internal flash memory has a virtual-flash emulation function, allowing the internal RAM

tobe artificially mapped into part of the internal flash memory. This function, when combined

with the internal Real-Time Debugger (RTD), facilitates data tuning on ROM tables.

• The internal RAM can be accessed for read or rewrite from an external device independently of

the M32R by using RTD (real-time debugger). It is communicated with external devices by

RTD's exclusive clock-synchronized serial I/O.

1-3 Rev.1.0

Page 24

1

1.1.4 Built-in Clock Multiplier Circuit

• The 32172/32173 internally multiplies the frequency of the input clock signal by 4 (or by 2 for

the internal peripheral clock). When the input clock frequency is 10.0 MHz, the CPU clock

frequency is 40 MHz and that of the internal peripheral clock is 20 MHz.

1.1.5 Built-in Powerful Peripheral Functions

(1) Built-in input/output timers

• The timers used in the 32172/32173 consist of the following 26 channels of timers. (When not

using the PDC module as a sensor interface circuit, eight more channels of input timers are

available.)

16-bit output related timers x 16 channels

16-bit input related timers x 6 channels

32-bit input related timers x 4 channels

Each timer has multiple modes to choose from, depending on the purpose of use.

Overview

1.1 Overview

(2) Built-in 10-channel DMA

• The microcomputer contains 10 channels of DMA, allowing for data transfer between internal

peripheral I/Os and between internal RAM and internal peripheral I/O. DMA transfer requests

can be issued from the user-created software, as well as can be triggered by a signal

generated by the internal peripheral I/O (A-D converter, input/output timer, or serial I/O).

• The microcomputer also supports cascaded operation between DMA channels (starting DMA

transfer on a channel at the end of transfer on another channel). This makes advanced transfer

processing possible without causing any additional CPU load.

(3) Built-in two blocks of A-D converters

• The microcomputer contains an 8-channel A-D converter and a 4-channel A-D converter, both

capable of 10-bit resolution.

• In addition to ordinary A-D conversion, the converters support comparator mode in which a set

value and the A-D converted value are compared to determine which is larger or smaller than

the other.

• When A-D conversion is finished, the converters can generate a DMA transfer request, as well

as an interrupt.

(4) High-speed serial I/O

• The microcomputer contains eight channels of serial I/Os which can be set for clocksynchronized serial I/O or UART.

• The transfer rate in clock-synchronized serial I/O mode is a high 2 Mbits per second, allowing

for fast data transfer.

• The serial I/O has the function to generate a DMA transfer request when data reception is

1-4 Rev.1.0

Page 25

1

completed or the transmit register becomes empty.

(5) Built-in Real-time Debugger (RTD)

• The Real-time Debugger (RTD) provides a function for accessing directly from the outside to

the M32R/E's internal RAM. It uses a dedicated clock-synchronized serial I/O to communicate

with external devices.

• Use of the RTD allows the contents of the internal RAM to be read out or its data to be rewritten

from the outside, independently of the M32R.

• An RTD interrupt can be generated to indicate that RTD-based data transmission or reception

is completed.

(6) 8-level interrupt controller

• The Interrupt Controller controls interrupt requests from internal peripheral I/Os by using eight

priority levels (including interrupt-disabled state) which are assigned to each interrupt source. It

also handles external interrupt requests generated upon detection of power outage or

generated by the watchdog timer as System Break Interrupt (SBI).

(7) Three operation modes

Overview

1.1 Overview

• The M32R/E supports three operation modes: single-chip, external extended, and processor

modes. The M32R/E's address space and external pin functions are switched over according

to each mode. Modes are selected using the MOD0 and MOD1 pins.

(8) Wait controller

• The Wait Controller supports access to external devices. In other than single-chip mode, up to

4 Mbytes of space is available for an external extended area.

1.1.6 Built-in Full-CAN Function

• The microcomputer contains two CAN modules compliant with CAN Specification V2.0B

active, each of which has 16-channel message slots.

1.1.7 Two Built-in D-A Converters

• The microcomputer contains two blocks of 8-bit resolution D-A converters.

1-5 Rev.1.0

Page 26

1

• In addition to ordinary D-A conversion, these converters support the function to successively

output any data. Also, the converters have a 256-byte output buffer (available for only the DA0 converter).

1.1.8 Built-in Timer/Arithmetic Circuits for PD (Phase Digital) Sensors

• The microcomputer contains two blocks of timer/arithmetic circuits that operate along with PD

(Phase Digital) sensors.

• With various arithmetic circuits needed for position predictive operations incorporated, and the

timers interlocked with the D-A converters, fast data processing is possible.

• When not using the PD circuit, the PD sensor-handling timers can be used as ordinary input

measurement timers or input event counters.

1.1.9 Built-in Debug Function

Overview

1.1 Overview

• The 32172/32173 supports the JTAG interface. Using this JTAG interface, the microcomputer

can perform boundary scan test.

1-6 Rev.1.0

Page 27

1

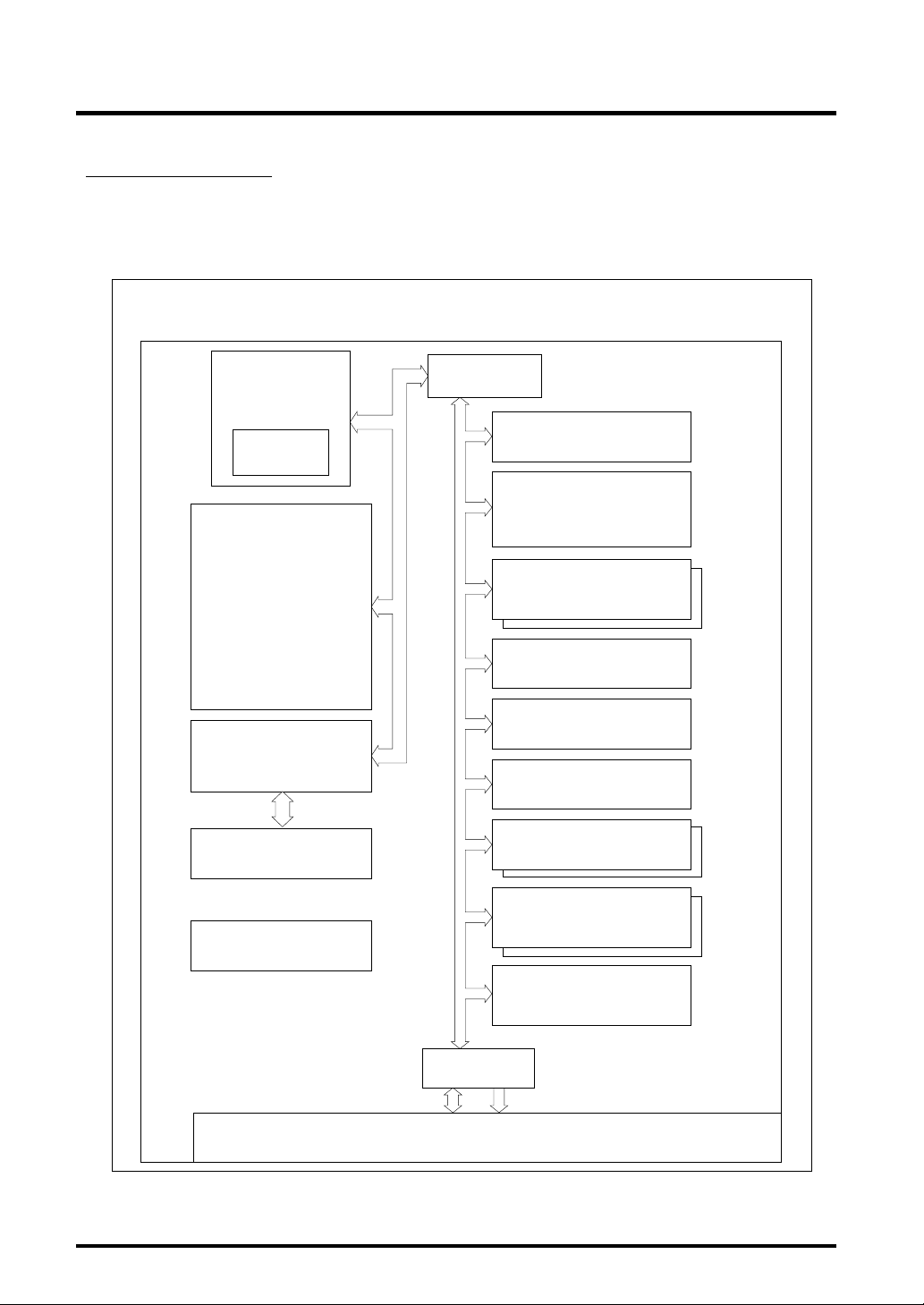

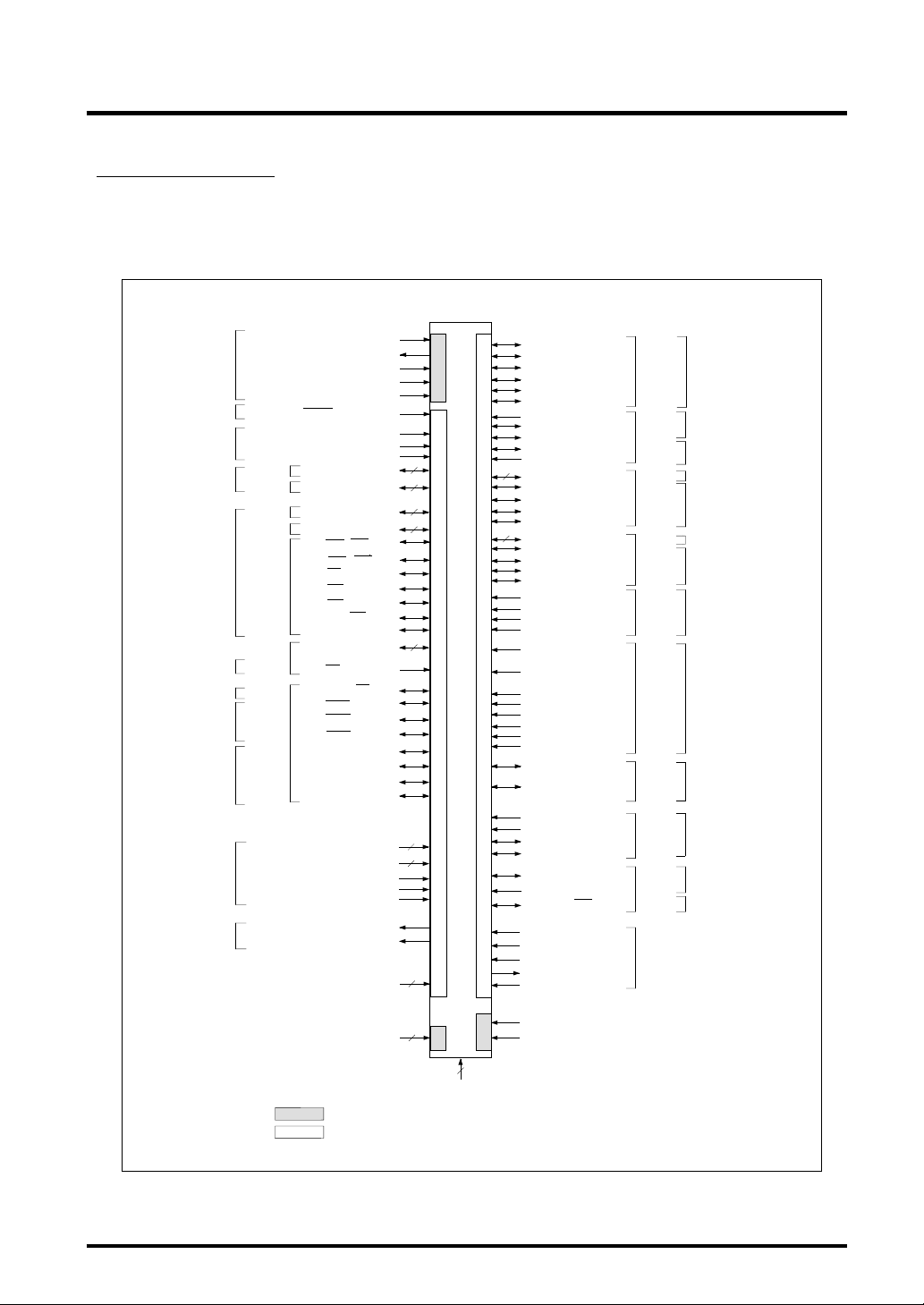

1.2 Block Diagram

1.2 Block Diagram

Figure 1.2.1 shows a block diagram of the 32172/32173. The features of each block are outlined in

Tables 1.2.1 to 1.2.3.

32172

32173

Internal Bus

M32R CPU Core

(max 40MHz)

Multiplieraccumulator

(32 x 16+56)

Internal Flash Memory

(256KB)

Interface

(A-D0: 10-bit A-D, 8 channels)

(A-D1: 10-bit A-D, 4 channels)

Internal 32-bit Bus

DMAC

(10 channels)

Input/output Timer

(26 channels)

A-D Converter x 2

Serial I/O

(8 channels)

Overview

Internal RAM

(M32172F2 : 16KB)

(M32173F2 : 32KB)

Real-time Debugger

(RTD)

PLL Clock Generating

Circuit

Figure 1.2.1 Block Diagram

Interrupt Controller

(interrupt sources in 8 levels)

Internal 16-bit Bus

External Bus

Interface

Input/output Ports (JTAG), 99 lines

Wait Controller

Full CAN

(2 channels)

D-A Converter x 2

(8 bits)

PD Controller

AddressData

1-7 Rev.1.0

Page 28

1

Table 1.2.1 Features of the M32R Family CPU Core

Functional Block Features

M32R family • Bus specifications

CPU core Basic bus cycle: 25 ns (when CPU clock = 40 MHz)

Logical address space: 4 Gbytes linear

External extended area: Maximum 4 Mbytes

External data bus: 16 bits

• Implementation: Five-stage pipelined processing

• CPU core internally configured in 32 bits

• Register configuration

General-purpose register: 32 bits x 16

Control register: 32 bits x 5

• Instruction set

16-bit/32-bit instruction formats

83 discrete instructions/6 addressing modes

• Built-in multiplier-accumulator (32 x 16 + 56)

Overview

1.2 Block Diagram

Table 1.2.2 Features of the Internal Memory

Functional Block Features

RAM • Capacity

M32172F2: 16 Kbytes

M32173F2: 32 Kbytes

• No-wait access

• By using the RTD (Real-time Debugger), the internal RAM can be accessed for

data read or rewrite from the outside, independently of the M32R.

Flash memory • Capacity: 256 Kbytes

• No-wait access

• Durability: Can be rewritten 100 times

1-8 Rev.1.0

Page 29

1

1.2 Block Diagram

Table 1.2.3 Features of Internal Peripheral I/Os

Functional Block Features

DMA • 10-channel DMA

• Supports data transfer between internal peripheral I/Os, between internal RAMs,

and between internal peripheral I/O and internal RAM

• Capable of fast DMA transfer when used in combination with internal peripheral I/O

• Capable of cascaded operation between DMA channels (starting DMA transfer on

a channel at the end of transfer on another)

Timer • 26-channel multifunction timers

• 16 channels of 16-bit output related timers, 6 channels of 16-bit input related

timers, and 4 channels of 32-bit input related timers

• Flexible timer configuration is possible by interconnecting each timer channel

A-D converter • One 8-channel A-D converter and one 4-channel A-D converter, both capable of

10-bit resolution

• Supports comparator mode

• Can generate an interrupt or start DMA transfer at completion of A-D conversion

• Can monitor pin levels on a total of 20 channels (with reduced accuracy, however)

Serial I/O • 8-channel serial I/O

• Can be set for clock-synchronized serial I/O or UART

• Capable of fast data transfer at 2 Mbits/second during clock-synchronized mode or

156 Kbits/second during UART mode

Real-time debugger • Can rewrite/monitor the internal RAM by command input from the outside,

independently of the CPU

• Comes with dedicated clock-synchronized serial port

Interrupt controller • Controls interrupt requests from internal peripheral I/Os

• Eight priority levels including interrupt-disabled state

Wait controller • Controls wait state when accessing external extended area

• Inserts 1 to 4 wait cycles by software setting + extends wait period by external

____

WAIT signal input

Clock PLL • Multiply-by-4 clock generating circuit

• CPU clock of maximum 40 MHz (CPU, internal ROM, and internal RAM access)

• Internal peripheral clock of maximum 20 MHz (peripheral module access)

• Maximum external input clock frequency of 10.0 MHz

D-A converter • Two channels of 8-bit resolution D-A converters

D-A0 converter: D-A output, successive data output function, 256-byte output

buffer available

D-A1 converter: D-A output only

PD Controller • Two blocks of PD sensor-accommodating timers and various arithmetic circuits for

position predictive operation

• 16-bit input measurement timer: 4 channels; 16-bit input related timer: 4 channels

• When not using the PD circuit, the above timers can be used as input

measurement timers or input event counters

CAN • Two blocks of CAN modules, each with 16-channel message slots

JTAG • Boundary scan function, Mitsubishi original SDI debug function included

Overview

1-9 Rev.1.0

Page 30

1

1.3 Pin Functions

1.3 Pin Functions

Figure 1.3.1 shows a pin function diagram of the 32172/32173. Table 1.3.1 provides a description

of pin functions.

Overview

Clock

Reset

Mode

Data bus

Address bus

Bus control

Interrupt

controller

Clock

Bus control

serial I/O

Realtime

debugger

A-D

converter

D-A

converter

Port 0

Port 1

Port 2

Port 3

Port 4

Port 6

Port 7

XIN

XOUT

VCNT

OSC-VCC

OSC-VSS

RESET

MOD0

MOD1

FP

P00 — P07/DB0 — DB7

P10 — P17/DB8 — DB15

P20 — P27 / A23 — A30

P30 — P37 / A15 — A22

P41 / BLW / BLE

P42 / BHW / BHE

P43 / RD

P44 / CS0

P45 / CS1

P46 / A13 / CS3

P47 / A14

P61 — P63

P64 / SBI

P70 / BCLK / WR

P71 / WAIT

P72 / HREQ

P73 / HACK /TXD3

P74 / RTDTXD

P75 / RTDRXD

P76 / RTDACK

P77 / RTDCLK

AD0IN0 — AD0IN7

AD1IN0 — AD1IN3

AVCC0

AVSS0

VREF0

DA0 (/ AD1IN4)

DA1 (/ AD1IN5)

VCCE

8

8

8

8

3

8

4

4

3.3V (Note)

5V

5V (Note)

M32172F2VFP, M32173F2VFP

P82 / TXD0

P83 / RXD0

P84 / SCLKI 0 / SCLKO 0

P85 / TXD1

P86 / RXD1

P87 / SCLKI 1 / SCLKO 1

P93 / RXD3 (/ AD0IN8)

P94 / TXD6

P95 / RXD6

P96 / CTX1

P97 / CRX1

4

P100 — P103 / TO8 — TO11

P104 / TO12 / SCLKI4

P105 / TO13 / SCLKO4

P106 / TO14 / TXD4

P107 / TO15 / RXD4

4

P110 — P113 / TO0 — TO3

P114 / TO4/ SCLKI5

P115 / TO5 / SCLKO5

P116 / TO6 / TXD5

P117 / TO7 / RXD5

P124 / TIN0A (/ AD0IN9)

P125 / TIN0B (/ AD1IN9)

P126 / TIN1A (/ AD0IN10)

P127 / TIN1B (/ AD1IN10)

P130 / TIN16 / PWMOFF0

(/AD0IN11)

P131 / TIN17 / PWMOFF1

(/AD1IN11)

P132 / TIN18 (/ AD0IN12)

P133 / TIN19 (/ AD1IN12)

P134 / TIN20 (/ AD0IN13)

P135 / TIN21 (/ AD1IN13)

P136 / TIN22 (/ AD0IN14)

P137 / TIN23 (/ AD1IN14)

P150 / TIN8 / TXD7

(/AD0IN15)

P153 / TIN9 / RXD7

(/AD1IN15)

P172 / TIN10 (/ AD1IN6)

P173 / TIN11 (/ AD1IN7)

P174 / TXD2

P175 / RXD2

P220 / CTX0

P221 / CRX0

P225 / A12 / CS2

JTMS

JTCK

JTRST

JTDO

JTDI

Port 8

Port 9

Port 10

Port 11

Port 12

Port 13

Port 15

Port 17

Port 22

JTAG

Serial I/O

Serial I/O

CAN

Input/output

timer

Input/output

timer serial I/O

Input/output

timer

Input/output

timer serial I/O

PD module

(A-D converter)

Input/output

timer

(A-D converter)

Input/output

timer serial I/O

(A-D converter)

Input/output

timer serial I/O

(A-D converter)

CAN

Bus control

address bus

3.3V

VDD

FVCC

Note

VCCI

: The [3.3V] blocks operate with a 3.3 V power supply.

3.3V

: The [5V] blocks operate with a 5 V or 3.3 V power supply.

5V

3

3.3V

5

VSS

Figure 1.3.1 Pin Function Diagram of 144LQFP Package

1-10 Rev.1.0

Page 31

1

Overview

1.3 Pin Functions

Clock

Reset

Mode

Data bus

Address bus

Bus control

Interrupt

controller

Clock

Bus control

serial I/O

Realtime

debugger

A-D

converter

D-A

converter

DEBUG

Port 0

Port 1

Port 2

Port 3

Port 4

Port 6

Port 7

Note

XIN

XOUT

VCNT

OSC-VCC

OSC-VSS

RESET

MOD0

MOD1

FP

P00 — P07/DB0 — DB7

P10 — P17/DB8 — DB15

P20 — P27 / A23 — A30

P30 — P37 / A15 — A22

P41 / BLW / BLE

P42 / BHW / BHE

P43 / RD

P44 / CS0

P45 / CS1

P46 / A13 / CS3

P47 / A14

P61 — P63

P64 / SBI

P70 / BCLK / WR

P71 / WAIT

P72 / HREQ

P73 / HACK /TXD3

P74 / RTDTXD

P75 / RTDRXD

P76 / RTDACK

P77 / RTDCLK

AD0IN0 — AD0IN7

AD1IN0 — AD1IN3

AVCC0

AVSS0

VREF0

DA0 (/ AD1IN4)

DA1 (/ AD1IN5)

TRCLK

TRSYNC

TRDATA

DBI

EVENT0

EVENT1

VCCE

VCCI

: The [3.3V] blocks operate with a 3.3 V power supply.

3.3V

: The [5V] blocks operate with a 5 V power supply.

5V

8

8

8

8

3

8

4

8

4

3

3.3V (Note)

5V (Note)

M32172F2VWG, M32173F2VWG

3.3V

5

VSS

P82 / TXD0

P83 / RXD0

P84 / SCLKI 0 / SCLKO 0

P85 / TXD1

P86 / RXD1

P87 / SCLKI 1 / SCLKO 1

P93 / RXD3 (/ AD0IN8)

P94 / TXD6

P95 / RXD6

P96 / CTX1

P97 / CRX1

4

P100 — P103 / TO8 — TO11

P104 / TO12 / SCLKI4

P105 / TO13 / SCLKO4

P106 / TO14 / TXD4

P107 / TO15 / RXD4

4

P110 — P113 / TO0 — TO3

P114 / TO4/ SCLKI5

P115 / TO5 / SCLKO5

P116 / TO6 / TXD5

P117 / TO7 / RXD5

P124 / TIN0A (/ AD0IN9)

5V

P125 / TIN0B (/ AD1IN9)

P126 / TIN1A (/ AD0IN10)

P127 / TIN1B (/ AD1IN10)

P130 / TIN16 / PWMOFF0

(/AD0IN11)

P131 / TIN17 / PWMOFF1

(/AD1IN11)

P132 / TIN18 (/ AD0IN12)

P133 / TIN19 (/ AD1IN12)

P134 / TIN20 (/ AD0IN13)

P135 / TIN21 (/ AD1IN13)

P136 / TIN22 (/ AD0IN14)

P137 / TIN23 (/ AD1IN14)

P150 / TIN8 / TXD7

(/ AD0IN15)

P153 / TIN9 / RXD7

(/ AD1IN15)

P172 / TIN10 (/ AD1IN6)

P173 / TIN11 (/ AD1IN7)

P174 / TXD2

P175 / RXD2

P220 / CTX0

P221 / CRX0

P225 / A12 / CS2

JTMS

JTCK

JTRST

JTDO

JTDI

VDD

FVCC

3.3V

Port 8

Port 9

Port 10

Port 11

Port 12

Port 13

Port 15

Port 17

Port 22

JTAG

Serial I/O

Serial I/O

CAN

Input/output timer

Input/output timer

serial I/O

Input/output timer

Input/output timer

serial I/O

PD module

(A-D converter)

Input/output timer

(A-D converter)

Input/output timer

serial I/O

(A-D converter)

Input/output timer

serial I/O

(A-D converter)

CAN

Bus control

address bus

Figure 1.3.2 Pin Function Diagram of 175FBGA Package

1-11 Rev.1.0

Page 32

1

1.3 Pin Functions

Table 1.3.1 Description of Pin Functions (1/6)

Classification Pin Name Description Type Function

Power supply VCCE Power supply –– Supplies power to external I/O ports (5 V).

VCCI Power supply –– Supplies power to the internal logic (3.3 V).

VDD RAM power supply –– Power supply pin for internal RAM backup (3.3 V).

FVCC Flash power supply –– Power supply pin for the internal flash memory (3.3 V).

VSS Ground –– Connect all VSS to ground (GND).

Clock XIN, Clock Input Clock input/output pin. With a PLL-based

XOUT Output frequency multiplier circuit included, enter a clock with

1/4 the operating frequency (XIN input = 10.0 MHz for

the CPU clock of 40 MHz).

______

BCLK/WR System Output When this signal is System Clock (BCLK), it outputs a

clock clock whose is twice that of extemal inpout clock.

OSC-VCC Power supply –– Power supply for the PLL circuit. Connect OSC-VCC to

OSC-VSS Ground –– Connect OSC-VSS to ground.

VCNT PLL control Input PLL circuit control pin. Connect a resistor and capacitor

Reset

Mode MOD0 Mode Input Sets operation mode.

Address A12-A30 Address Output To allow four blocks of up to 1 MB memory space to

bus bus be connected external to the chip, 19 address lines

_____

RESET Reset Input Resets the internal circuits.

MOD1 FP MOD0 MOD1 Mode

Use this clock for external synchronized design.

(BCLK output = 20 MHz when CPU clock operates at

40 MHz).

When this signal is Write (WR), during extemal write

access it indicates the valid data on the data bus to

transfer.

input clock (BCLK output = 20 MHz when the external

input clock is 10 MHz).

the power supply (3.3 V).

to this pin. (For details about an external circuit, refer to

Section 20.1.1, "Example of an Oscillator Circuit."

X 0 0 Single-chip mode

X 0 1 External extended mode

0 1 0 Processor mode

1 1 0 Boot mode

X 1 1 (Reserved)

(A12-A30) are provided. A31 is not output to the

outside.

__

Overview

Note: For details about boot mode, refer to Chapter 6, "Internal Memory."

1-12 Rev.1.0

Page 33

1

1.3 Pin Functions

Table 1.3.1 Description of Pin Functions (2/6)

Classification Pin Name Description Type Function

Data bus DB0-DB15 Data bus Input/Output 16-bit data bus for connecting external devices. In write

cycle, the CPU outputs BHW/BHE and BLW/BLE

indicating the valid byte position to write on the 16-bit

data bus. In read cycle, the CPU always reads data

from the full 16-bit data bus. However, data at only the

valid byte position is transferred to the internal circuit

Bus control

Input/ TIN8-TIN11, Timer input Input Input/output timer input pin.

output timer TIN16-TIN23

Interrupt

controller interrupt controller.

___ ___

CS0, CS1 Chip select Output Chip select signal for external devices. For details about

___ ___

CS2, CS3 areas for which the chip select signal is output, refer to

__

RD Read Output This signal is output when reading an external device.

___

___

BHW/BHE Byte high Output Indicates the byte position to which valid data will be

___

___

BLW/BLE Byte low Output

____

WAIT Wait Input

____

HREQ Hold request Input This input pin is provided for external devices to request

____

HACK Hold Output

TO0-TO15 Timer output Output Input/output timer output pin.

___

SBI System breakInput System Break Interrupt (SBI) input pin for the interrupt

write/enable

write/enable

acknowledge a hold state and relinquished control of the external bus.

of the M32R.

Chapter 3, "Address Space."

transferred when writing to an external device.BHW/

___

BHE is output for the upper address side (D0-D7 is

valid), while BLW/BLE is output for the lower address

side (D8-D15 is valid).

If input on WAIT is low when the M32R accesses an

external device, the wait cycle is extended.

control of the external bus. If input on the HREQ pin is

pulled low, the M32R goes to a hold state.

This signal is used to indicate that the M32R has entered

___

____

___

___

___

Overview

___

___

___

____

1-13 Rev.1.0

Page 34

1

1.3 Pin Functions

Table 1.3.1 Description of Pin Functions (3/6)

Classification Pin Name Description Type Function