Maxim DS1672U-2, DS1672U-3, DS1672U-33, DS1672-2, DS1672-3 Schematic [ru]

...

DS1672

I2C 32-Bit Binary Counter RTC

www.maxim-ic.com

GENERAL DESCRIPTION

The DS1672 incorporates a 32-bit counter and power-monitoring functions. The 32-bit counter is designed to count seconds and can be used to derive time-of-day, week, month, month, and year by using a software algorithm. A precision, temperature-compensated reference and comparator circuit monitors the status of VCC. When an out-of-tolerance condition occurs, an internal power-fail signal is generated that forces the reset to the active state. When VCC returns to an in-tolerance condition, the reset signal is kept in the active state for a period of time to allow the power supply and processor to stabilize.

FEATURES

32-Bit Counter I2C* Serial Interface

Automatic Power-Fail Detect and Switch Circuitry

Power-Fail Reset Output

Low-Voltage Oscillator Operation (1.3V min)

Trickle-Charge Capability

Underwriters Laboratory (UL) Recognized

-40°C to +85°C Operating Temperature Range

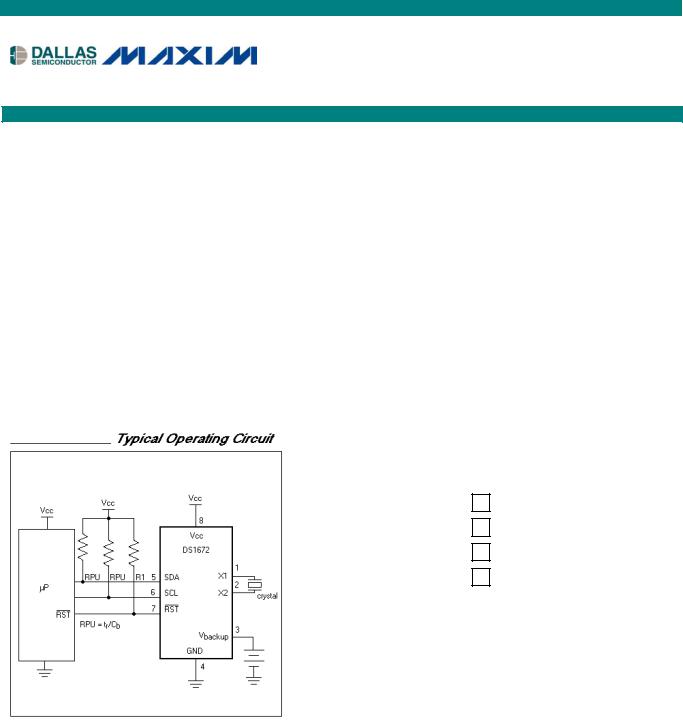

TYPICAL OPERATING CIRCUIT |

|

PIN CONFIGURATION |

|

|

|||

|

|

|

|

||||

|

|

TOP VIEW |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

X1 |

|

8 |

|

VCC |

|

|

|

X2 |

|

2DS16727 |

|

RST |

|

|

|

|

|

||||

|

|

VBACKUP |

|

3 |

6 |

|

SCL |

|

|

|

|

||||

|

|

GND |

|

4 |

5 |

|

SDA |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

DIP |

|

|

|

|

|

|

|

SO |

|

|

|

|

|

|

|

µSOP |

|

|

|

|

|

|

|

|

|

|

|

|

*Purchase of I2C components from Maxim Integrated Products, |

|||||

|

|

Inc., or one of its sublicensed Associated Companies, conveys a |

|||||

|

|

license under the Philips I2C Patent Rights to use these |

|||||

|

|

components in an I2C system, provided that the system conforms |

|||||

|

|

to the I2C Standard |

Specification |

defined by Philips. |

|||

1 of 15 |

REV: 031406 |

DS1672

ORDERING INFORMATION

PART |

TEMP RANGE |

VOLTAGE (V) |

PIN-PACKAGE |

TOP MARK* |

||

DS1672-2 |

-40°C to +85°C |

2.0 |

8 |

DIP (300 mils) |

DS1672-2 |

|

|

|

|

|

|

|

|

DS1672-3 |

-40°C to +85°C |

3.0 |

8 |

DIP (300 mils) |

DS1672-3 |

|

|

|

|

|

|

|

|

DS1672-33 |

-40°C to +85°C |

3.3 |

8 |

DIP (300 mils) |

DS1672-33 |

|

|

|

|

|

|

|

|

DS1672S-2 |

-40°C to +85°C |

2.0 |

8 |

SO (150 mils) |

DS1672-2 |

|

|

|

|

|

|

|

|

DS1672S-2+ |

-40°C to +85°C |

2.0 |

8 |

SO (150 mils) |

D1672-2 |

|

|

|

|

|

|

|

|

DS1672S-3 |

-40°C to +85°C |

3.0 |

8 |

SO (150 mils) |

DS1672-3 |

|

|

|

|

|

|

|

|

DS1672S-3+ |

-40°C to +85°C |

3.0 |

8 |

SO (150 mils) |

D1672-3 |

|

|

|

|

|

|

|

|

DS1672S-33 |

-40°C to +85°C |

3.3 |

8 |

SO (150 mils) |

DS167233 |

|

|

|

|

|

|

|

|

DS1672S-33+ |

-40°C to +85°C |

3.3 |

8 |

SO (150 mils) |

D167233 |

|

|

|

|

|

|

|

|

DS1672S-3/T&R |

-40°C to +85°C |

3.0 |

8 |

SO (150 mils)/Tape |

DS1672-3 |

|

|

|

|

and Reel |

|

||

DS1672S-3+T&R |

-40°C to +85°C |

3.0 |

8 |

SO (150 mils)/Tape |

D1672-3 |

|

|

|

|

and Reel |

|

||

DS1672S-33/T&R |

-40°C to +85°C |

3.3 |

8 |

SO (150 mils)/Tape |

DS167233 |

|

|

|

|

and Reel |

|

||

DS1672S-33+T&R |

-40°C to +85°C |

3.3 |

8 |

SO (150 mils)/Tape |

D167233 |

|

|

|

|

and Reel |

|

||

DS1672U-2 |

-40°C to +85°C |

2.0 |

8 |

µSOP (3mm) |

1672 |

|

rr -2 |

||||||

|

|

|

|

|

||

DS1672U-2+ |

-40°C to +85°C |

2.0 |

8 |

µSOP (3mm) |

1672 |

|

rr -2 |

||||||

|

|

|

|

|

||

DS1672U-3 |

-40°C to +85°C |

3.0 |

8 |

µSOP (3mm) |

1672 |

|

rr -3 |

||||||

|

|

|

|

|

||

DS1672U-3+ |

-40°C to +85°C |

3.0 |

8 |

µSOP (3mm) |

1672 |

|

rr -3 |

||||||

|

|

|

|

|

||

DS1672U-33 |

-40°C to +85°C |

3.3 |

8 |

µSOP (3mm) |

1672 |

|

rr -33 |

||||||

|

|

|

|

|

||

DS1672U-33+ |

-40°C to +85°C |

3.3 |

8 |

µSOP (3mm) |

1672 |

|

rr -33 |

||||||

|

|

|

|

|

||

DS1672U-33/T&R |

-40°C to +85°C |

3.3 |

8 |

µSOP (3mm)/Tape |

1672 |

|

and Reel |

rr -33 |

|||||

|

|

|

||||

DS1672U-33+T&R |

-40°C to +85°C |

3.3 |

8 |

µSOP (3mm)/Tape |

1672 |

|

and Reel |

rr -33 |

|||||

|

|

|

||||

+ Denotes a lead-free/RoHS-compliant device.

* A “+” anywhere on the top mark denotes a lead-free device. rr = 2-digit alphanumeric revision code.

2 of 15

DS1672

ABSOLUTE MAXIMUM RATINGS

Voltage Range on Any Pin Relative to Ground……………………………………………..-0.5V to +6.0V Operating Temperature Range (noncondensing) ...…………………………………………-40°C to +85°C Storage Temperature Range……………………………………………………………….-55°C to +125°C Soldering Temperature………………………………………….See IPC/JEDEC J-STD-020 Specification

This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time can affect device reliability.

RECOMMENDED DC OPERATING CONDITIONS

(TA = -40°C to +85°C)

|

PARAMETER |

SYMBOL |

MIN |

TYP |

MAX |

UNITS |

NOTES |

|

|

|

|

|

|

|

|

|

|

Supply |

|

DS1672-2 |

VCC |

1.8 |

2.0 |

2.2 |

V |

1 |

|

DS1672-3 |

VCC |

2.7 |

3.0 |

3.3 |

|||

Voltage |

|

|||||||

|

DS1672-33 |

VCC |

2.97 |

3.3 |

3.63 |

|

|

|

|

|

|

|

|||||

Logic 1 |

|

|

VIH |

0.7 x VCC |

|

VCC + 0.5 |

V |

1 |

Logic 0 |

|

|

VIL |

-0.5 |

|

+0.3 x VCC |

V |

1 |

Backup Supply Voltage |

VBACKUP |

1.3 |

3.0 |

3.63 |

V |

1 |

||

DC ELECTRICAL CHARACTERISTICS

(VCCMIN < VCC < VCCMAX, TA = -40°C to +85°C.)

PARAMETER |

SYMBOL |

MIN |

TYP |

MAX |

UNITS |

NOTES |

||

|

|

|

|

|

|

|

|

|

Active Supply Current |

ICCA |

|

|

600 |

µA |

2 |

||

Standby Current |

|

ICCS |

|

|

500 |

µA |

3 |

|

Power-Fail Voltage |

VPF |

2.70 |

2.88 |

2.97 |

V |

|

||

2.45 |

2.6 |

2.7 |

|

|||||

|

|

|

|

1.58 |

1.7 |

1.8 |

|

|

VBACKUP Leakage Current |

IBACKUPLKG |

|

25 |

50 |

nA |

|

||

|

|

|

|

|

|

|

|

|

Logic 0 Output (VOL = 0.4V) |

IOL |

|

|

3 |

mA |

1, 4 |

||

Logic 0 |

|

(VCC > 2V; |

|

|

|

3 |

|

|

|

VOL = 0.4V) |

IOL |

|

|

mA |

1, 4 |

||

Output |

|

|

|

|

||||

|

(VCC < 2V; |

|

|

|

||||

(DS1672-2) |

|

|

|

|

3 |

|

|

|

|

VOL = 0.2 x VCC) |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Note 1: All voltages referenced to ground.

Note 2: ICCA specified with SCL clocking at max frequency (400kHz), trickle charger disabled.

Note 3: ICCS specified with VCC = VCCTYP and SDA, SCL = VCCTYP, trickle charger disabled.

Note 4: SDA and RST.

3 of 15

|

|

|

|

|

|

|

|

DS1672 |

|

|

DC ELECTRICAL CHARACTERISTICS |

|

|

|

|

|

|||

|

(VCC = 0V, TA = -40°C to +85°C.) |

|

|

|

|

|

|

|

|

|

PARAMETER |

|

SYMBOL |

MIN |

TYP |

MAX |

UNITS |

NOTES |

|

|

|

|

|

|

|

|

|

|

|

|

VBACKUP Current (Oscillator On) |

|

IBACKUPOSC |

|

0.425 |

1 |

µA |

5 |

|

|

VBACKUP Current (Oscillator Off) |

|

IBACKUP |

|

|

200 |

nA |

|

|

Note 5: Using the recommended crystal on X1 and X2.

CRYSTAL SPECIFICATIONS*

PARAMETER |

SYMBOL |

MIN |

TYP |

MAX |

UNITS |

NOTES |

|

|

|

|

|

|

|

Nominal Frequency |

fO |

|

32.768 |

|

kHz |

|

Series Resistance |

ESR |

|

|

45 |

kΩ |

|

Load Capacitance |

CL |

|

6 |

|

pF |

|

*The crystal, traces, and crystal input pins should be isolated from RF generating signals. Refer to Application Note 58: Crystal Considerations for Dallas Real-Time Clocks for additional specifications

4 of 15

|

|

|

|

|

|

|

|

|

DS1672 |

|

|

AC ELECTRICAL CHARACTERISTICS |

|

|

|

|

|

|

|||

|

(VCC = 0V, TA = -40°C to +85°C.) |

|

|

|

|

|

|

|

||

|

PARAMETER |

SYMBOL |

CONDITIONS |

MIN |

TYP |

MAX |

UNITS |

NOTES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCL Clock |

fSCL |

|

Fast mode |

100 |

|

400 |

kHz |

|

|

|

|

|

|

|

|

|

|

|||

|

Frequency |

|

Standard mode |

|

|

100 |

|

|

||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Bus Free Time |

tBUF |

|

Fast mode |

1.3 |

|

|

|

|

|

|

Between a STOP and |

|

|

|

|

|

µs |

|

|

|

|

|

Standard mode |

4.7 |

|

|

|

|

|||

|

START Condition |

|

|

|

|

|

|

|

||

|

Hold Time |

tHD:STA |

|

Fast mode |

0.6 |

|

|

|

6 |

|

|

(Repeated) START |

|

|

|

|

|

µs |

|

||

|

|

Standard mode |

4.0 |

|

|

|

||||

|

Condition |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

LOW Period of SCL |

tLOW |

|

Fast mode |

1.3 |

|

|

µs |

|

|

|

|

|

|

|

|

|

|

|||

|

Clock |

|

Standard mode |

4.7 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

HIGH Period of SCL |

tHIGH |

|

Fast mode |

0.6 |

|

|

µs |

|

|

|

Clock |

|

Standard mode |

4.0 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Setup Time for a |

tSU:STA |

|

Fast mode |

0.6 |

|

|

|

|

|

|

Repeated START |

|

|

|

|

|

µs |

|

|

|

|

|

Standard mode |

4.7 |

|

|

|

|

|||

|

Condition |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Data Hold Time |

tHD:DAT |

|

Fast mode |

0 |

|

0.9 |

µs |

7, 8 |

|

|

|

|

|

|

|

|

||||

|

|

Standard mode |

0 |

|

|

|

||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Data Setup Time |

tSU:DAT |

|

Fast mode |

100 |

|

|

ns |

9 |

|

|

|

|

|

|

|

|

||||

|

|

Standard mode |

250 |

|

|

|

||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Rise Time of Both |

tR |

|

Fast mode |

20 + 0.1CB |

|

300 |

ns |

10 |

|

|

SDA and SCL |

|

|

|

|

|

|

|||

|

|

Standard mode |

|

|

1000 |

|

||||

|

Signals |

|

|

|

|

|

|

|

||

|

Fall Time of Both |

tF |

|

Fast mode |

20 + 0.1CB |

|

300 |

ns |

10 |

|

|

SDA and SCL |

|

|

|

|

|

|

|||

|

|

Standard mode |

|

|

300 |

|

||||

|

Signals |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Setup Time for STOP |

tSU:STO |

|

Fast mode |

0.6 |

|

|

µs |

|

|

|

|

|

|

|

|

|

|

|||

|

Condition |

|

Standard mode |

4.0 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Capacitive Load for |

CB |

|

|

|

|

400 |

pF |

10 |

|

|

Each Bus Line |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

I/O Capacitance |

CI/O |

|

|

|

10 |

|

pF |

|

|

Note 6: After this period, the first clock pulse is generated.

Note 7: A device must internally provide a hold time of at least 300ns for the SDA signal (referenced to the VIHMIN of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

Note 8:The maximum tHD:DAT has only to be met if the device does not stretch the LOW period (tLOW) of the SCL signal.

Note 9: A fast-mode device can be used in a standard-mode system, but the requirement tSU:DAT ≥ to 250ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line tR max + tSU:DAT = 1000 + 250 = 1250ns before the SCL line is released.

Note 10: CB–Total capacitance of one bus line in pF.

5 of 15

Loading...

Loading...