Page 1

Service

SA8400 /F1N/K1G/L1G/N1G/S1G

/N1B

SA8400

Manual

2nd EDITION

• The model no.SA8400/L1G/N1G/N1B was added in this service manual

SECTION PAG E

1. TECHNICAL SPECIFICATIONS AND UPDATE DISC .................................................................. 1

2. SERVICE HINTS AND TOOLS ..................................................................................................... 2

3. WARNING AND LASER SAFETY INSTRUCTIONS..................................................................... 3

4. TAKING THE DISC OUT OF EMERGENCY................................................................................. 4

5. UPDATA FIRMWARE .................................................................................................................... 5

6. SERVICE MODE........................................................................................................................... 6

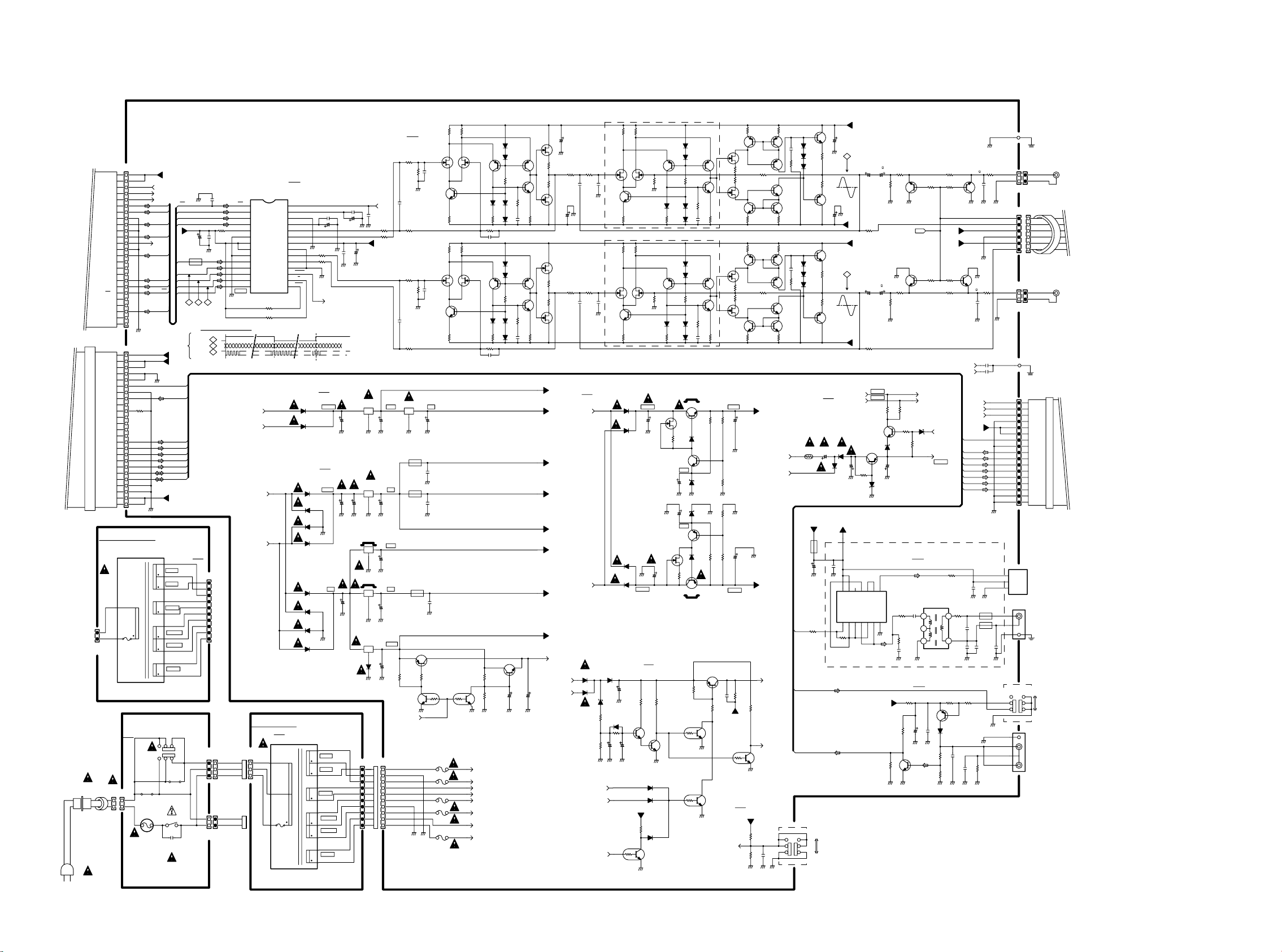

7. BLOCK DIAGRAM ........................................................................................................................ 7

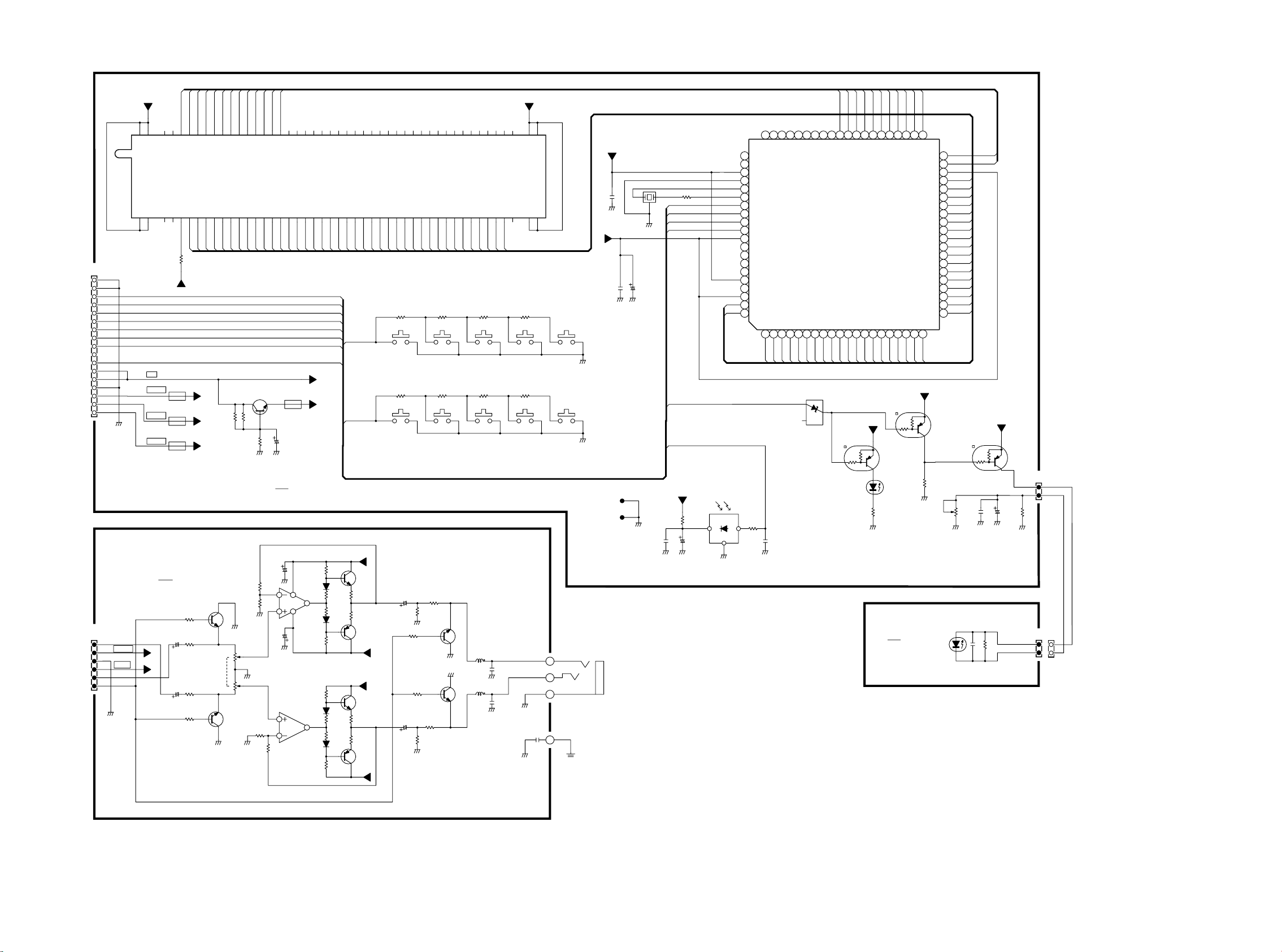

8. SCHEMATIC DIAGRAM................................................................................................................ 9

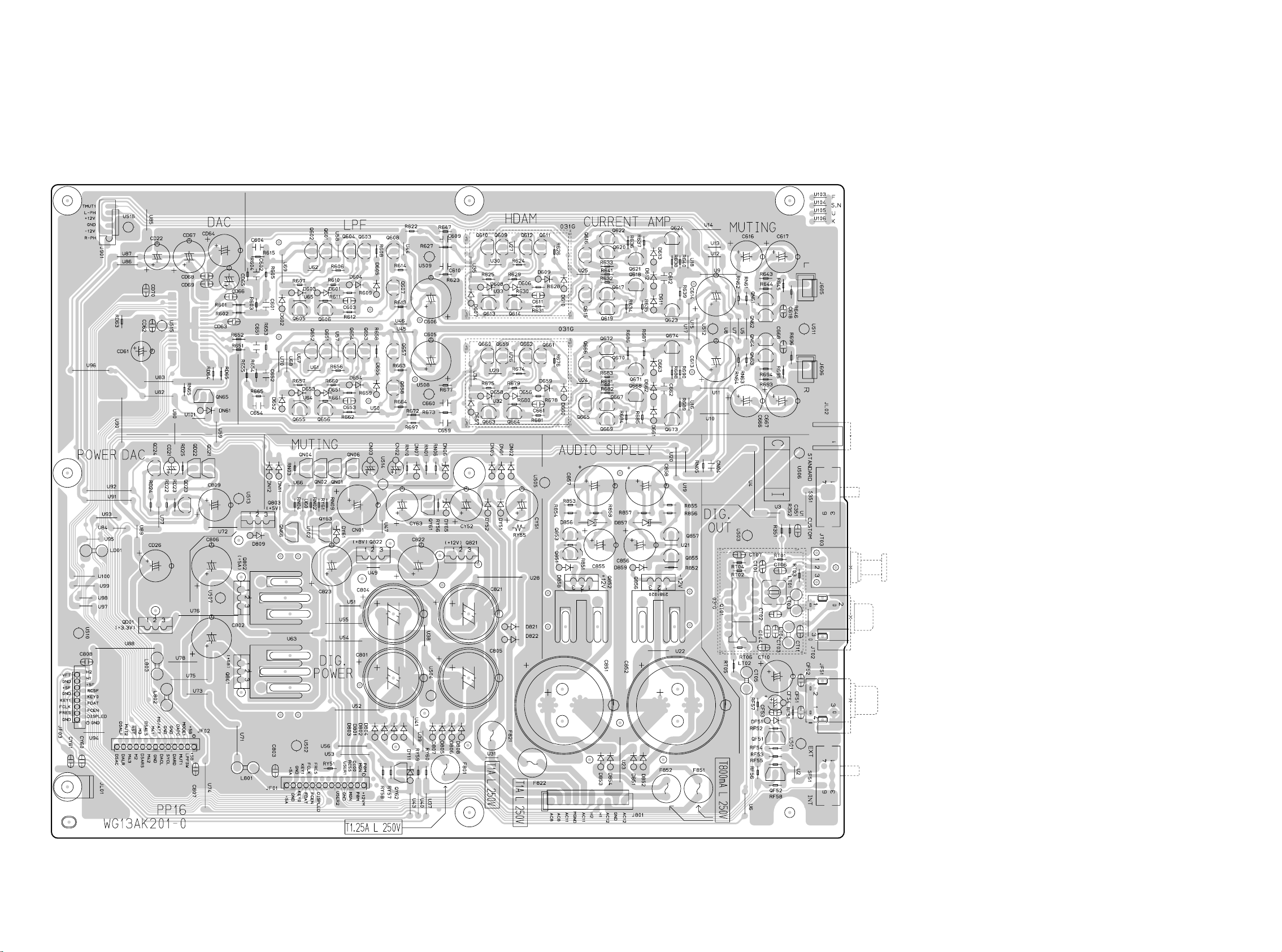

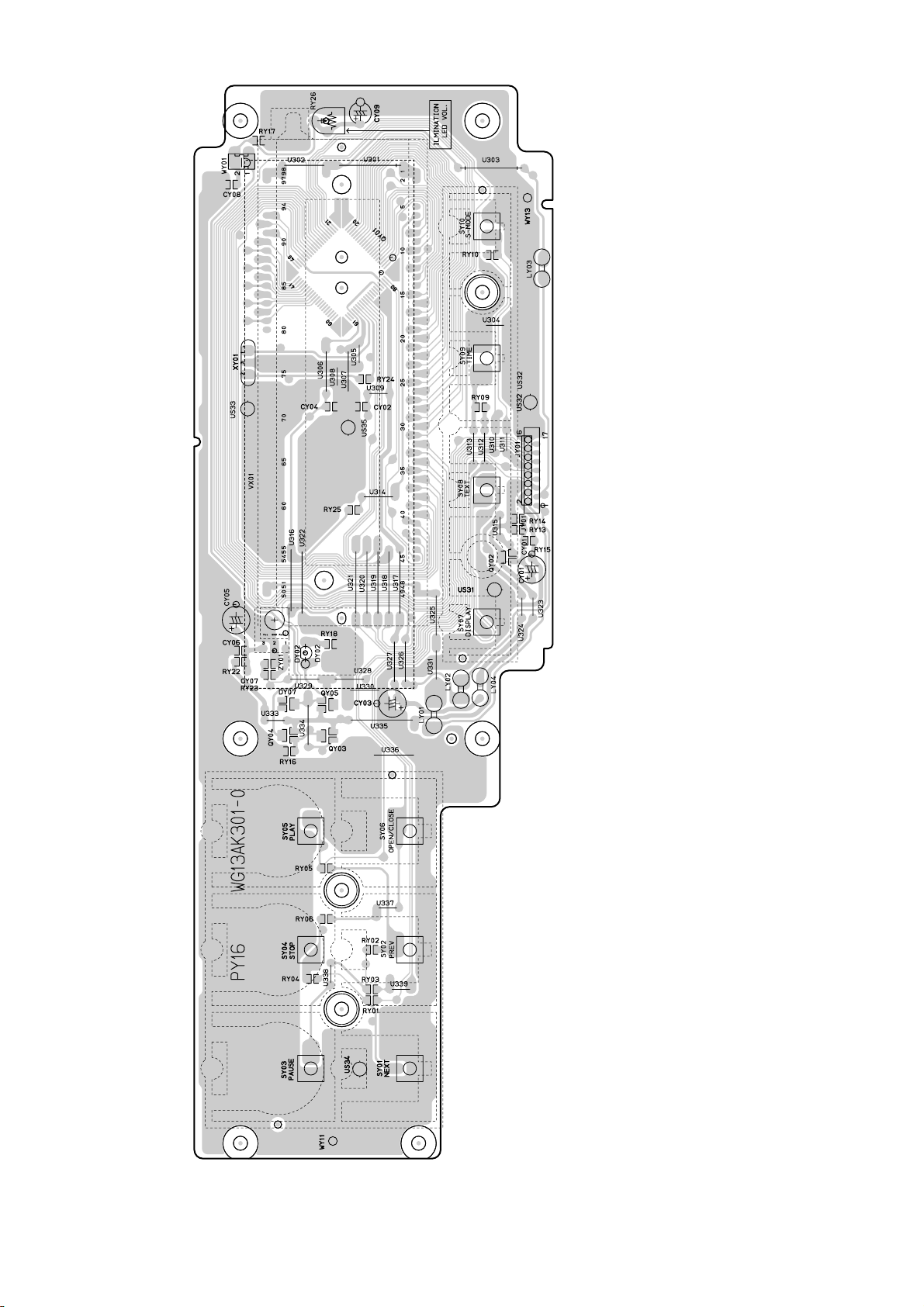

9. PARTS LOCATION...................................................................................................................... 13

10. MICROPROCESSOR AND IC DATA........................................................................................... 17

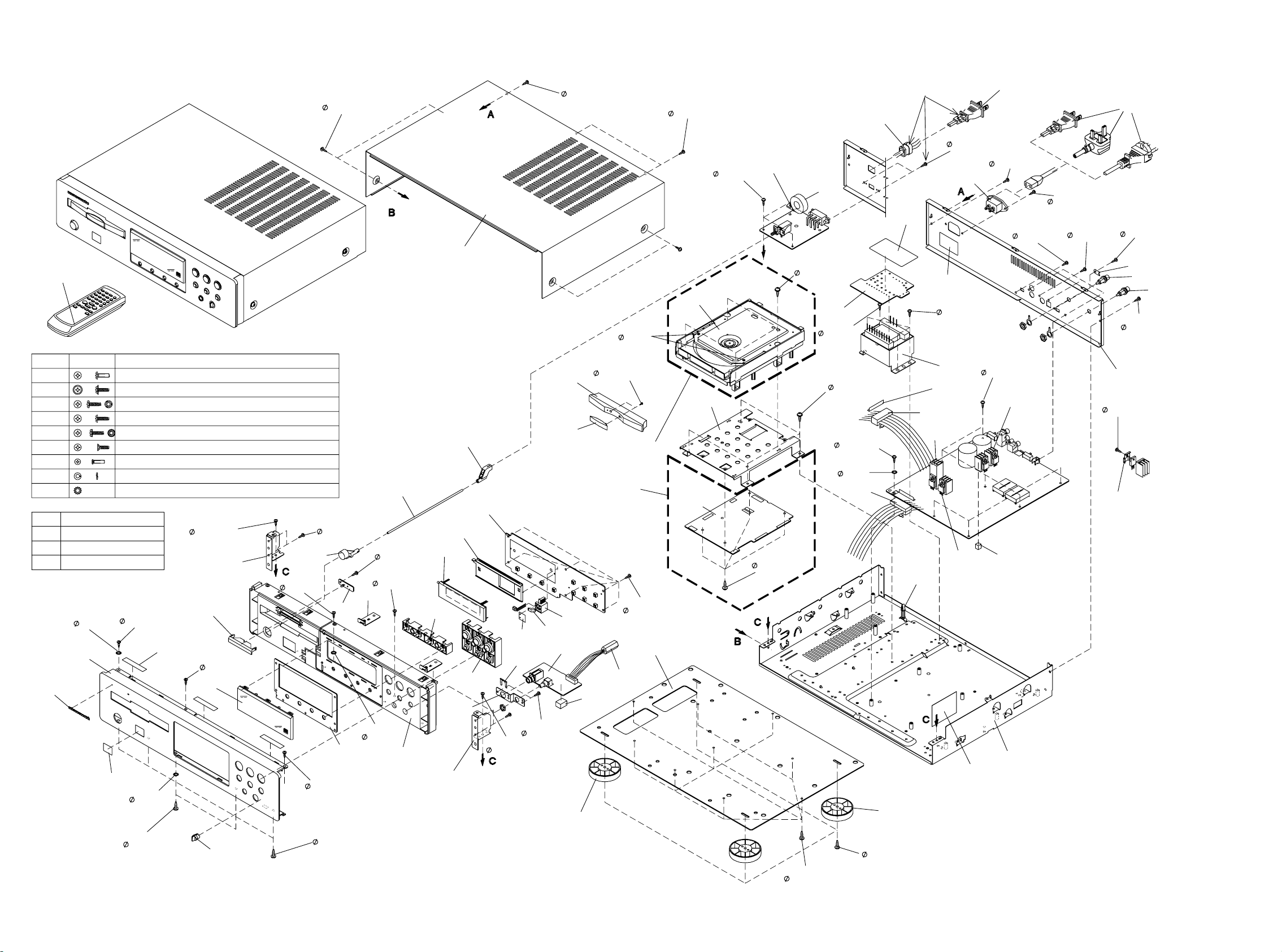

11. EXPLODED VIEW AND PARTS LIST ......................................................................................... 21

12.ELECTRICAL PARTS LIST.......................................................................................................... 24

Super Audio CD Player

SUPER AUDIO CD PLAYER SA8400

DISPLAY

OFF

POWER

ON/OFF

SOUND MODE

TIME

DISPLAY

TEXT

TABLE OF CONTENTS

OPEN/CLOSE

PLAY

PAUSE

STOP

/

/

LEVEL

PHONES

+

-

MECHA LOADER AND MECHA TRAVERSE

2.1 EXPLODED VIEW AND PARTS LIST........................................................................................ 2-1

SUPER AUDIO CD PCB MODULE

3.1 IC DATA...................................................................................................................................... 3-1

3.2 BLOCK DIAGRAM ................................................................................................................... 3-22

3.3 SCHEMATIC DIAGRAM........................................................................................................... 3-34

3.4 PARTS LOCATION................................................................................................................... 3-36

3.5 ELECTRICAL PARTS LIST...................................................................................................... 3-38

Please use this service manual with referring to the user guide ( D.F.U. ) without fail.

SA8400

Part no. 13AK855012

2nd Issue 2003.12

ecm

Page 2

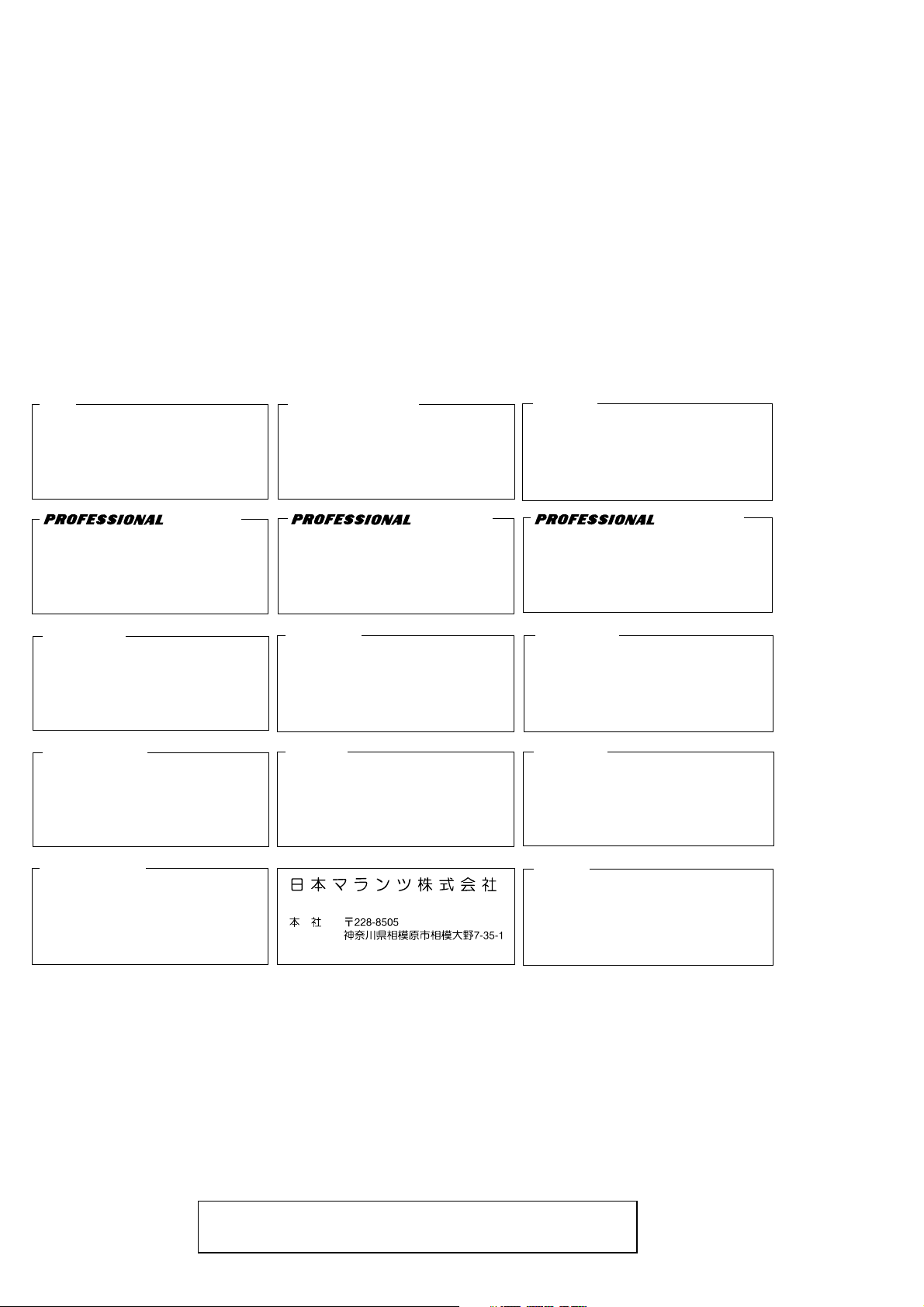

MARANTZ DESIGN AND SERVICE

Using superior design and selected high grade components,

Only original

MARANTZ

parts can insure that your

MARANTZ

MARANTZ

product will continue to perform to the specifi cations for which

company has created the ultimate in stereo sound.

it is famous.

Parts for your

MARANTZ

ORDERING PARTS :

equipment are generally available to our National Marantz Subsidiary or Agent.

Parts can be ordered either by mail or by Fax.. In both cases, the correct part number has to be specifi ed.

The following information must be supplied to eliminate delays in processing your order :

1. Complete address

2. Complete part numbers and quantities required

3. Description of parts

4. Model number for which part is required

5. Way of shipment

6. Signature : any order form or Fax. must be signed, otherwise such part order will be considered as null and void.

USA

MARANTZ AMERICA, INC

1100 MAPLEWOOD DRIVE

ITASCA, IL. 60143

USA

PHONE : 630 - 741 - 0300

FAX : 630 - 741 - 0301

AMERICAS

SUPERSCOPE TECHNOLOGIES, INC.

MARANTZ PROFESSIONAL PRODUCTS

2640 WHITE OAK CIRCLE, SUITE A

AURORA, ILLINOIS 60504 USA

PHONE : 630 - 820 - 4800

FAX : 630 - 820 - 8103

EUROPE / TRADING

MARANTZ EUROPE B.V.

P. O. BOX 8744, BUILDING SILVERPOINT

BEEMDSTRAAT 11, 5653 MA EINDHOVEN

THE NETHERLANDS

PHONE : +31 - 40 - 2507844

FAX : +31 - 40 - 2507860

AUSTRALIA

TECHNICAL AUDIO GROUP PTY, LTD

43-53 Bridge Rd.,

STANMORE NSW 2048

AUSTRALIA

PHONE : +61 - (0)2 - 9519 - 0900

FAX : +61 - (0)2 - 9519 - 0600

CANADA

LENBROOK INDUSTRIES LIMITED

633 GRANITE COURT,

PICKERING, ONTARIO L1W 3K1

CANADA

PHONE : 905 - 831 - 6333

FAX : 905 - 831 - 6936

HONG KONG

Jolly ProAudio Broadcast Engineering Ltd.

UNIT 2, 10F, WAH HUNG CENTRE,

41 HUNG TO ROAD, KWUN TONG, KLN.,

HONG KONG

PHONE : 852 - 21913660

FAX : 852 - 21913990

AUSTRALIA

QualiFi Pty Ltd,

24 LIONEL ROAD,

MT. WAVERLEY VIC 3149

AUSTRALIA

PHONE : +61 - (0)3 - 9543 - 1522

FAX : +61 - (0)3 - 9543 - 3677

NEW ZEALAND

WILDASH AUDIO SYSTEMS NZ

14 MALVERN ROAD MT ALBERT

AUCKLAND NEW ZEALAND

PHONE : +64 - 9 - 8451958

FAX : +64 - 9 - 8463554

JAPAN

MARANTZ JAPAN, INC.

35- 1, 7- CHOME, SAGAMIONO

SAGAMIHARA - SHI, KANAGAWA

JAPAN 228-8505

PHONE : +81 42 748 1013

FAX : +81 42 741 9190

Technical

THAILAND

MRZ STANDARD CO., LTD

746 - 754 MAHACHAI ROAD.,

WANGBURAPAPIROM, PHRANAKORN,

BANGKOK, 10200 THAILAND

PHONE : +66 - 2 - 222 9181

FAX : +66 - 2 - 224 6795

TAIWAN

PAI- YUING CO., LTD.

6 TH FL NO, 148 SUNG KIANG ROAD,

TAIPEI, 10429, TAIWAN R.O.C.

PHONE : +886 - 2 - 25221304

FAX : +886 - 2 - 25630415

SHOCK, FIRE HAZARD SERVICE TEST :

SINGAPORE

WO KEE HONG DISTRIBUTION PTE LTD

130 JOO SENG ROAD

#03-02 OLIVINE BUILDING

SINGAPORE 368357

PHONE : +65 6858 5535 / +65 6381 8621

FAX : +65 6858 6078

MALAYSIA

WO KEE HONG ELECTRONICS SDN. BHD.

2ND FLOOR BANGUNAN INFINITE CENTRE

LOT 1, JALAN 13/6, 46200 PETALING JAYA

SELANGOR DARUL EHSAN, MALAYSIA

PHONE : +60 - 3 - 7954 8088

FAX : +60 - 3 - 7954 7088

KOREA

MK ENTERPRISES LTD.

ROOM 604/605, ELECTRO-OFFICETEL, 16-58,

3GA, HANGANG-RO, YONGSAN-KU, SEOUL

KOREA

PHONE : +822 - 3232 - 155

FAX : +822 - 3232 - 154

CAUTION : After servicing this appliance and prior to returning to customer, measure the resistance between either primary AC

cord connector pins ( with unit NOT connected to AC mains and its Power switch ON ), and the face or Front Panel of product

and controls and chassis bottom.

Any resistance measurement less than 1 Megohms should cause unit to be repaired or corrected before AC power is applied,

and verifi ed before it is return to the user/customer.

Ref. UL Standard No. 1492.

In case of diffi culties, do not hesitate to contact the Technical

Department at above mentioned address.

030307MIT

Page 3

1. TECHNICAL SPECIFICATIONS AND UPDATE DISC

Super Audio CD CD

Audio Characteristics

Analog output

Channels 2channels 2channels

Frequency range 2Hz — 100kHz 2Hz — 20kHz

Frequency characteristics 2Hz — 50kHz (-3dB) 2Hz — 20kHz

Dynamic range 114dB More than 100dB

THD (1kHz) 0.0009% 0.0020%

Wow & Flutter Precision of quartz Precision of quartz

Output level 2.2V 2.2V

Digital output

Output level (Cinch JACK) — 0.5Vp-p (75Ω)

Output level (Optical) — -19dBm

Headphone output level 0.5W / 32Ω (max, Vol.) 0.5W / 32Ω (max, Vol.)

Optical Readout System

Laser AlGaAs AlGaAs

Wave length 650nm 780nm

Signal format 1-bit DSD 16-bit linear PCM

Sampling frequency 2.8224MHz 44.1kHz

Power Supply

Input Voltage, Frequency (/F).................................................................... AC 100V 50/60Hz

(/K/L)............................................................. AC 110/220V 50/60Hz

(/N)......................................................................... AC 230V 50Hz

(/S)......................................................................... AC 230V 50Hz

Power Consumption....................................................................................................... 20W

Cabinet, etc.

Dimensions ...............................................................................................

Net weight.....................................................................................................................7.5kg

Operating temperatures.................................................................................. +5°C ~ +35°C

Operating humidity............................................................................. 5 ~ 90% (without dew)

Accessories

• Remote control unit (RC8400SA) ......................................................................................1

Dimensions (Width × Height × Depth)..............................................

Net weight (without Batteries) .......................................................................................60g

• AAA (R03) Batteries ..........................................................................................................2

• AC Power cord...................................................................................................................1

• Audio cable...............................................................................................................1 pairs

• Remote connection Cable ................................................................................................1

• User’s Guide......................................................................................................................1

440 × 113 × 335mm

48.5 × 21.5 × 152.5mm

UPDATE DISC

Update of the CPU (IC731)..............................................................................*SA8400CDR

1

Page 4

2. SERVICE HINTS AND TOOLS

SERVICE HINTS

SERVICE TOOLS

Audio signals disc 4822 397 30184

Disc without errors (SBC444)+

Disc with DO errors, black spots and fingerprints (SBC444A) 4822 397 30245

Disc (65 min 1kHz) without no pause 4822 397 30155

Max. diameter disc (58.0 mm) 4822 397 60141

Torx screwdrivers

Set (straight) 4822 395 50145

Set (square) 4822 395 50132

13th order filter 4822 395 30204

DVD test disc (PAL) 4822 397 10131

DVD test disc (NTSC) ALMEDIO TDV-540

2

Page 5

3. WARNING AND LASER SAFETY INSTRUCTIONS

GB

WARNING

All ICs and many other semi-conductors are

susceptible to electrostatic discharges (ESD).

Careless handling during repair can reduce

life drastically.

When repairing, make sure that you are

connected with the same potential as the

mass of the set via a wrist wrap with

resistance.

Keep components and tools also at this

potential.

F

ATTENTION

D

WARNUNG

I

WAARSCHUWING

AVVERTIMENTO

NL

Alle IC’s en vele andere halfgeleiders zijn

gevoelig voor elektrostatische ontladingen

(ESD).

Onzorgvuldig behandelen tijdens reparatie

kan de levensduur drastisch doen

verminderen.

Zorg ervoor dat u tijdens reparatie via een

polsband met weerstand verbonden bent met

hetzelfde potentiaal als de massa van het

apparaat.

Houd componenten en hulpmiddelen ook op

ditzelfde potentiaal.

Tous les IC et beaucoup d’autres semiconducteurs sont sensibles aux décharges

statiques (ESD).

Leur longévité pourrait être considérablement

écourtée par le fait qu’aucune précaution

n’est prise a leur manipulation.

Lors de réparations, s’assurer de bien être

relié au même potentiel que la masse de

l’appareil et enfiler le bracelet serti d’une

résistance de sécurité.

Veiller a ce que les composants ainsi que les

outils que l’on utilise soient également a ce

potentiel.

GB

Safety regulations require that the set be restored to its original condition

and that parts which are identical with those specified be used.

NL

Veiligheidsbepalingen vereisen, dat het apparaat in zijn oorspronkelijke

toestand wordt terug gebracht en dat onderdelen, identiek aan de

gespecifieerde worden toegepast.

Alle IC und viele andere Halbleiter sind

empfindlich gegen elektrostatische

Entladungen (ESD).

Unsorgfältige Behandlung bei der Reparatur

kann die Lebensdauer drastisch vermindern.

Sorgen sie dafür, das Sie im Reparaturfall

über ein Pulsarmband mit Widerstand mit

dem Massepotential des Gerätes verbunden

sind.

Halten Sie Bauteile und Hilfsmittel ebenfalls

auf diesem Potential.

D

Bei jeder Reparatur sind die geltenden Sicherheitsvorschriften zu beachten.

Der Originalzustand des Gerats darf nicht verandert werden.

Fur Reparaturen sind Original-Ersatzteile zu verwenden.

I

Le norme di sicurezza esigono che l’apparecchio venga rimesso nelle

condizioni originali e che siano utilizzati pezzi di ricambiago idetici a quelli

specificati.

Tutti IC e parecchi semi-conduttori sono

sensibili alle scariche statiche (ESD).

La loro longevita potrebbe essere fortemente

ridatta in caso di non osservazione della piu

grande cauzione alla loro manipolazione.

Durante le riparazioni occorre quindi essere

collegato allo stesso potenziale che quello

della massa dell’apparecchio tramite un

braccialetto a resistenza.

Assicurarsi che i componenti e anche gli

utensili con quali si lavora siano anche a

questo potenziale.

F

“Pour votre sécurité, ces documents

doivent être utilisés par des

spécialistes agrées, seuls habilités à

réparer votre appareil en panne.”

Les normes de sécurité exigent que l’appareil soit remis a l’état d’origine et

que soient utilisées les pièces de rechange identiques à celles spécifiées.

LASER SAFETY

This unit employs a laser. Only a qualified service person should remove the cover or attempt to service this

device, due to possible eye injury.

USE OF CONTROLS OR ADJUSTMENTS OR PERFORMANCE OF PROCEDURE OTHER THAN THOSE

SPECIFIED HEREIN MAY RESULT IN HAZARDOUS RADIATION EXPOSURE.

AVOID DIRECT EXPOSURE TO BEAM

WARNING

The use of optical instruments with this product will increase eye hazard.

Repair handling should take place as much as possible with a disc loaded inside the player

WARNING LOCATION: INSIDE ON LASER COVERSHIELD

CAUTION VISIBLE AND INVISIBLE LASER RADIATION WHEN OPEN AVOID EXPOSURE TO BEAM

ADVARSEL SYNLIG OG USYNLIG LASERSTRÅLING VED ÅBNING UNDGÅ UDS

ADVARSEL SYNLIG OG USYNLIG LASERSTRÅLING NÅR DEKSEL Å PNES UNNGÅ EKSPONERING FOR STRÅLEN

VARNING SYNLIG OCH OSYNLIG LASERSTRÅLNING NÄR DENNA DEL ÄR ÖPPNAD BETRAKTA EJ STRÅLEN

VARO! AVATT AESSA OLET ALTTIINA NÄKYVÄLLE JA NÄKYMÄTTÖMÄLLE LASER SÄTEILYLLE. ÄLÄ KATSO SÄTEESEEN

VORSICHT SICHTBARE UND UNSICHTBARE LASERSTRAHLUNG WENN ABDECKUNG GEÖFFNET NICHT DEM STRAHL AUSSETSEN

DANGER VISIBLE AND INVISIBLE LASER RADIATION WHEN OPEN AVOID DIRECT EXPOSURE TO BEAM

ATTENTION RAYONNEMENT LASER VISIBLE ET INVISIBLE EN CAS D'OUVERTURE EXPOSITION DANGEREUSE AU FAISCEAU

Æ

TTELSE FOR STRÅLING

030804ecm

3

Page 6

4. TAKING THE DISC OUT OF EMERGENCY

1. To open the stucked tray, insert a pin into the eject pinhole and push the eject lever.

2. Use a pin φ4mm or less.

This picture shows the unit upside down. The eject lever is pointed by the arrow.

The lever is thin so aim the narrow area carefully.

4

Page 7

5. UPDATE FIRMWARE

Have UPDATE DISC. (*SA8400CDR)

Attention : Don't turn off the unit until disk tray opens

automatically during the updating. When the turn off the unit

halfway, The unit can't be operated any more.

1) Press the POWER button while pressing the PLAY and

OPEN/CLOSE buttons.

2) Press the OPEN/CLOSE button to open the tray, Insert

the update CD-ROM (part No.:*SA8400CDR).

3) Press the SOUND MODE and STOP buttons.

The Display indicates " VERSION UP ".

4) Press the OPEN/CLOSE button to close the tray.

The Display indicates " TOC Reading " >>> " FILE

CHECK " >>> " ERASE " >>> " WRITING ".

5) Software updating will be done automatically.

When the updating is fi nished, The disc tray opens

automatically.

(Updating takes about 1 minute.)

6) Remove the CD-ROM from the disc tray.

Update is completed, Press the POWER button to turn off the

unit.

5

Page 8

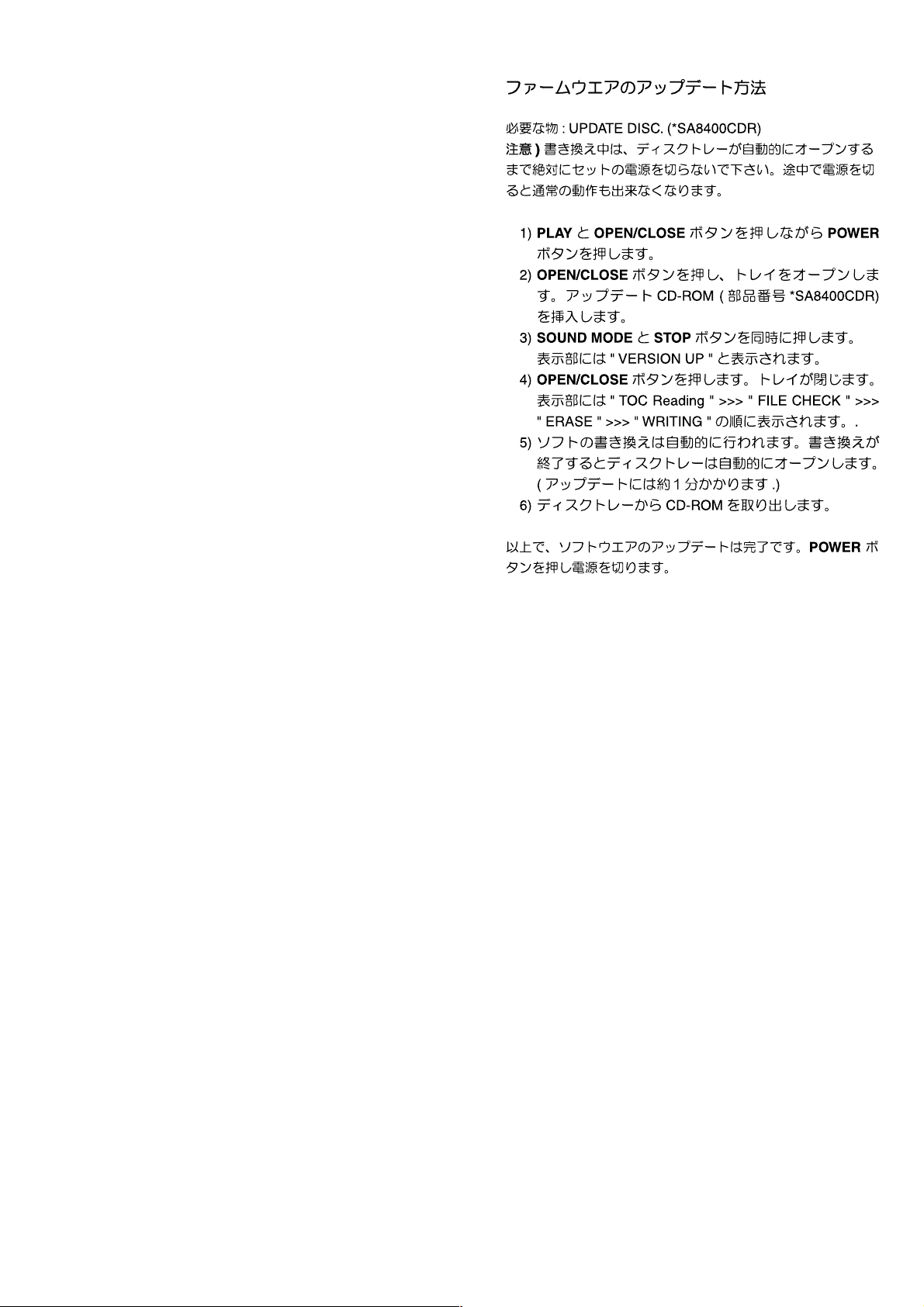

6. SERVICE MODE

The error code is indicated when a problem DISC is inserted fi rst.

Press the POWER button While pressing PLAY and OPEN/CLOSE Button

Press<

Press<

Press<

"SA8400" is displayed

>

Version of Backend(IC731) µ-COM is displayed

"B/E VXX.XX" is displayed

>

"DRV VXX.XX" is displayed

>

All area in the FLD light on

Press< >

All area in the FLD light off

Press< >

Press<

"H.R.SHORT" is displayed Appear Errer Code

"H.R.CHACKING" is displayed

> or Press PLAY< >

(Ex:E1 0000)

Press<

>

"H.R.NORMAL" is displayed

Remove Mains cord from plug

Errer Code

Error Code Error

E1 XXXX Operation time Error

E2 XXXX T.O.C Error

E2 XXXX Focus Error

E2 XXXX Read Error

E4 XXXX Tracking Error

E5 XXXX Tray Error

E6 XXXX Navigation Pack Read Error

E7 XXXX Check Sum Eroor and

NonAcknow I edgmen

NO DISC XXXX NO disc

(XXXX: The Operation number of times to the error

occurrence)

6

Page 9

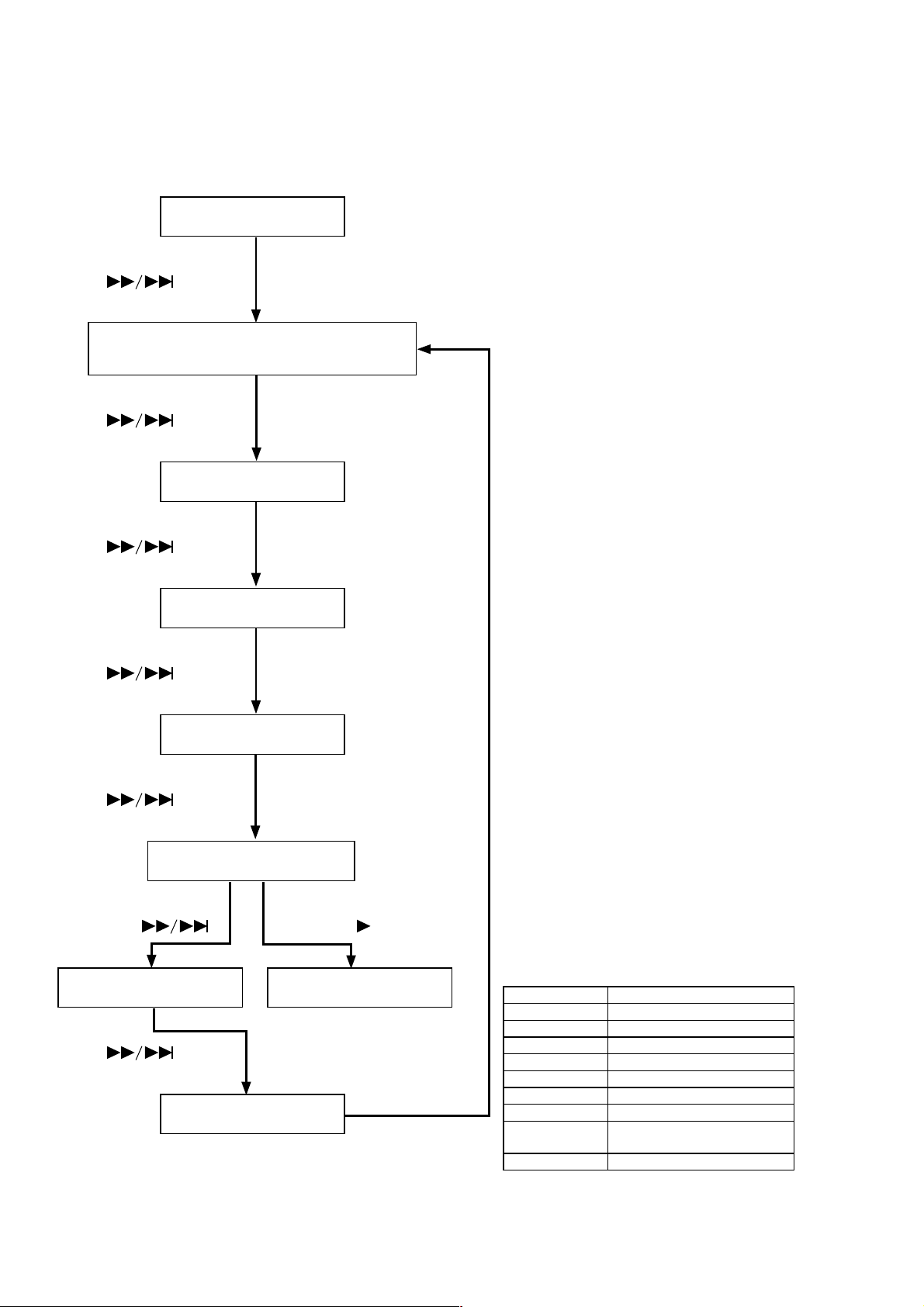

7. BLOCK DIAGRAM

SERVO BLOCK MAIN BLOCK

TURNTABLE

FOC,RAD,SLDG

3-AXICAL ACTUATOR

SPINDL

HOLL

MOTOR

photo

Laser

control

CD and DVD

LASER and MONITOR

LASER POWER CONT.

FAN8042

FOC,RAD,SLED

AN8471SA

SPINDLE DRIVER

CXD1881AR

IC501

RF-AMP, AGC, EQ

IC508

DRIVER

IC505

T14L1024N

IC732

SRAM(1M)

FOC

RAD

SLED

SPIN

M11L16161SA-45T

IC503

RFAC

D-RAM(16M)

AD6062

IC403

RF-AMP

CXD1885Q

IC502

DIGITAL SERVO

and PLL,

DEMODURATOR

EPM33128

IC404

FIFO

SYSTEM CLOCK

33.8688MHz

PCM DATA BUS LINE

M30624FGN

FEATUR and LOADING for SERVO-DSP

IC731

OSC IC734

DIGITAL I/O

EM636165TS-7

IC402

SDRAM(16M)

CXD2753R

IC401

PSP DECORD

and

DSD MULTI-

CHANNL

DECODER

CLK SELECTOR

IC735

384/192fs

DISPLAY and KEYS

DATA

SYCLSW

LRCK

DAPC

DARD

DACL

DSALF

DSAC

DSALS

DSARS

IC736

DSD/CD

DATA SWITCH

SYCL

DSCK

DSDO

DSCS1

DSRT1

ATT

MUTE1

384/192fs

MODE

and

DAC CONTROL

PCM/DSD DATA

KEYS DATA

DISPLAY and

POWER

SUPPLY

DIG. OUT PART

DIGITAL I/O

DAC PART

DAPC/DARD

DACL/LRCK

SYCL

CONTROL

CS4397

WOOFER/

CENTER

2CH DAC

HDAM

Diffrencial AMP

&

2th-LPF

HDAM

Diffrencial AMP

&

2th-LPF

HDAM

Current

Feedback AMP

&

2th-LPF

HDAM

Current

Feedback AMP

&

2th-LPF

COAX

OPT

L ch

R ch

POWER HEADPHONE

SUPPLY BLOCK

FRONT UNIT BLOCK BLOCK

IR sensor

RC-5

ML9207-01GP

FTD DRIVER

KEYS

PLAY/STOP/PAUSE/NEXT/PREVI/etc

DISPLAY and KEYS /RC-5 DATA

POWER SUPPLY

POWER

SUPPLLY

TRANSFORMER

HEADPHONE

L/R

HEADPHONE

7 8

Page 10

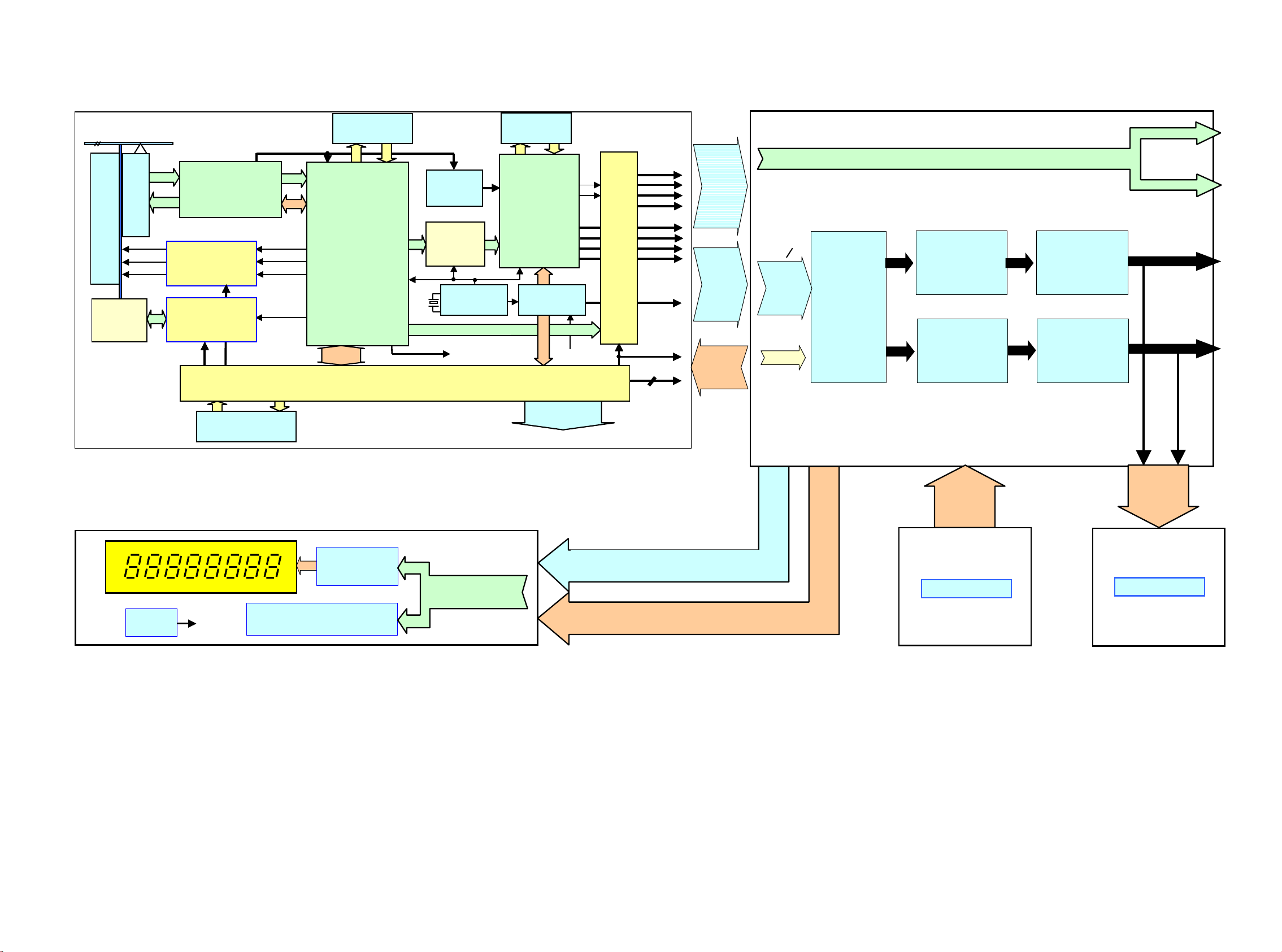

8. SCHEMATIC DIAGRAM

WF05

+5B

+5B

LPFSW

MODE1

MUT1

DAPC

DARD

GND

SYCL

GND

DACL

M0/ATT

GND

M41

M42

DSALS

TO SERVO PCB(PV16)

DSARS

DSD DATA IN AND POWER OUT

M3

M2

RST

M43

MUT2

DALR

DSALF

DSAC

WF04

+12M

P8M

P8M

MGN

MGN

DIGO

GND

RC5S

USER2

USER1

CDLED

SALED

MLTLED

LEY2

DISPLED

L012

HF70SH28X2X10

FRES

FCEN

FCLK

FDAT

KEY1

KEY0

GND

GND

+5A

+5A

TO SERVO PCB(PV16)

DSD DATA IN AND POWER OUT

FOR F,N,S

(PH26) TRANSF.PCB

L001

2

1

JH04

for F,S,N,U

J001

W003

HF-301

(F,N,S only)

(F,N,S only)

2

1

L003

TFCK-23-11-14

W001

(F,N,S only)

W002(K,L only)

(PP16)

MAIN PCB

JF02

25FMN-BTRK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

4

2

JF01

25FMN-BTRK

1

2

3

4

5

6

7

8

9

LPFSW

MODE1

MUT1

ATT

GND

M-GND

RY51

100

GND

(PH16)

POWER SW PCB

LPT

SH02

for K,L

12

JH01

UH04

2

for F,S,N,U

1

FH01

L 250V

T1.25A

JUMPER (F only)

POWER & DAC

+5B

RST

DAPC

M41

DARD

M3

M2

SYCL

3VDA

DACL

M41

SYCL

DACL

DALR

M3

DAPC

M2

DARD

RST

14

DALR

+12M

P8M+5A

DIGO

RC5S

DISPLED

FRES

FCEN

FCLK

FDAT

KEY1

KEY0

11

AC13V

12

AC13V

13

14

AC4.3V

15

16

AC11.8V

17

AC11.8V

18

19

AC7.3V

20

321

654

12

UH05

NC

SH01

21

GH01

0.01

AC250V

GND

0.1

CD61

100 25V

CD62

GND

LD01

384/192fs

12

15

16

DAC DATA INPUT FIG

15

DACK

DAD1,3,5

16

SCLK

14

LPT

WH02

10

9

8

7

6

5

4

3

2

1

JH03

for K,L

3

2

1

2

1

JH02

for F,S,N.U

QD61

1000p

CD70

RD63

10k

GND

M

CS4397

128

RST VREF

2

M4/ADD

3

M3/AD1

4

M2/SC1

5

M0/SDA

6

DGND

7

VD

8

VD

9

DGND

10

MCLK

11

SCLK

12

CMOD

13

SDAT

14

M1

CD=H

RD64

18k

RD65

18k

L,CH

L

3AC11

5AC11

1AC8

2AC8

FOR K,L

L001

JH05

for K,L

WH03

3

2

1

for F,S,N.U

2

1

for K,L

WH01

5

3

220V

3

2

110V

2

1

1

0V

4

2

1

2

LDA

27

FILT+

26

FILT-

25

CMOUT

24

-LO

23

+LO

22

VA

21

GND

20

+RD

19

-RD

18

GND

17

MUTEC

16

C/H

15

MUTE

R,CH

M

LPT

CD68

0.1

CD66

CD67

100 10V

10 25V

CD65

GND

GND

1.2k

R652

R651

L

CD63

1.2k

GND

GND

MUTEC

M

LPS

D822

+15.1V

1D3

D821

1D3

M-GND

C821

4700 25V

LPS

D803

11EQS10

+7.9V

D802

11EQS10

D804

11EQS10

D801

11EQS10

D807

11EQS10

D806

11EQS10

D808

11EQS10

D805

11EQS10

GND

GND

GND GND

+8V

GND

C801

6800 16V

C805

NJM78M05F

(PH26)

TRANSF.PCB

11

AC13V

12

AC13V

13

14

AC4.3V

15

16

AC11.8V

17

AC11.8V

18

19

AC7.3V

20

6800 16V

0.1

GND

GND

BA033T

Q803

LFB

R603

560

R604

QD01

Q802

0.1

IN

BA05T

10

C804

9

8

7

6

5

4

3

2

1

VREF

GND

CD64

100 25V

Q821

NJM7812F

COM

3300 16V

035G

TR SHILED

035G

TR SHILED

WH02

GND

2

M-GND

2

2

GND

2

GND

2

GND

Q801

BA05T

5V

0.1

CD69

13

OUT

13

COM

13

COM

13

COM

13

COM

D809

DTGDTG

C601

VREF

1800p

R605

R601

3.9k

1.2k

R602

1.2k

5.6VA

R653

560

R654

C651

1800p

R655

3.9k

Q822

NJM7808F

+12V

2

COM

C822

2200 16V

M-GND M-GND

M-GND

L802

12

L803

+5V

OUTIN

12

C802

3300 6.3V

GND

3.3V TO DAC

OUTIN

CD26

220 25V

GND

L801

+5V

OUTIN

OUTIN

11EQS10

12

C806

3300 6.3V

GND

+5.6V

C809

1000 10V

4.7k

RD22

GND

MODE1

J801

10

9

8

7

6

5

4

3

2

1

M-GND

120

R606

R607

Q601

2SK369 BL

D

D

3

3

+

1

G

2

2

S

S

330p

C602

1.8k

GND

2SC2240

C652

1.8k

330p

GND

2SC2240

+8V

OUTIN

13

C823

C807

GND

C808

GND

GND

123

E

C

QD23

2SA970

B

Y,GR

1.2k

RD23

1

3

QD21

DTC114TS

GND GND GND GND GND

T800mA L 250V

T800mA L 250V

T1A L 250V

GND

T1.25A L 250V

Q603

GR,BL

Q651

2SK369 BL

+

DTG DTG

Q653

GR,BL

2200 16V

0.10.1

0.1

C803

F852

F851

F822

F821

T1A

L 250V

F801

2SK369 BL

C

1

2

B

E

3

68

R608

120

R657

R656

D

D

3

3

1

G

2

2

S

S

2SK369 BL

C

1

2

B

E

3

68

R658

2

2

QD22

DTC114TS

10AC12

8AC12

H1

H2

5AC11

3AC11

2AC8

1AC8

DIFFERENCIAL

120

Q604

2SA970

3

E

GR,BL

-

1

2

G

B

1

C

Q602

D601

D604

560

D605

R609

5.1k

R615

C604

DAMG

120p

120

Q654

2SA970

3

E

GR,BL

-

1

2

G

B

1

C

Q652

D651

D654

560

R659

D655

5.1k

R665

120p

C654

DAMG

123

1.5k3.9k

RD24RD25

1

3

10AC12

8AC12

H1

H2

5AC11

3AC11

2AC8

1AC8

C

D602

Q605

2SA970

GR,BL

D603

2

B

Q606

2SC2240

GR,BL

33k

R610

2

B

R611

100

47p

C603

D652

Q655

2SA970

GR,BL

D653

2

B

Q656

2SC2240

GR,BL

33k

R660

2

B

100

R661

47p

C653

TO SERVO

TO SERVO

TO DIG. OUT

TO DAC(5.5/3.5V)

E

QD24

B

2SC2878

CD21

10 63V

Q607

2SK170

3

D

C605

V

220 16V

1

G

GND 2SA970

2

S

E

3

33

R622

R613

2SJ74

2SK170

2SJ74

CD22

2.2k

S

2

G

1

ARA

Q608

D

3

V

GND

C606

220 16V

Q657

D

3

V

1

G

S

2

33 33

R672

R663 R614

2.2k

33

R664

S

2

G

1

D

Q658

3

V

+12M

P8M

+5B

+5F

+5VD

3VDA

+5A

5.6VA

VREF

5AC11

3AC11

100 10V

C

C

E

560

R612

E

C

C

E

560

R662

TO SERVO

TO FRONT

TO SERVO

TO DAC

1

1

3

3

1

1

3

()

ARA

DTG

C609

1200p

DTG

C659

1200p

H:MUTE ON

L:MUTE OFF

H:MUTE ON

L:MUTE OFF

H:MUTE OFF

L:MUTE ON

LPS

8AC12

10AC12

DN02

ID3

DN01

ID3

R623

3.3k

R673

3.3k

560p

C610

GND

560p

C660

GND

RN01

M-GND M-GND

)(

)(

031G HDAM SHILED (S,K only)

120

120

R625

R624

Q609

2SK369 BL

D

D

3

3

+

1

1

G

G

2

2

S

S

GR,BL

Q610

2SK369 BL

1

C

Q611

2

B

3

E

68

R626

DTGDTG

2SC2240

031G HDAM SHILED (S,K only)

120

120

R675

R674

Q659

2SK369 BL

D

D

3

3

+

Q661

2SC2240

GR,BL

1

1

G

G

2

2

S

S

Q660

C

1

2SK369 BL

2

B

E

3

68

R676

D854

11EQS10

+12.6V

D853

11EQS10

GND

D852

11EQS10

D851

GND

11EQS10

-12.6V

LMU

DN05

ID3

CN01

1000 25V

M-GND

DN06

4.7V

RN09

47k

RN06

1.2k

QN06

DN07

2SC2458

C

1

Y,GR

2

B

RN10

2.2M

3

15k

ATT

MUT1

MUTEC

E

CN03

CN02

4.7 50V

QN01

1 100V

2SC2458

Y,GR

M-GND

3VDA

RN65

QN65

N.C.

1

2

3

GND

Q612

E

3

GR,BL

1

-

C

270

R627

GND

D606

560

R628

Q662

2SA970

E

3

GR,BL

1

-

C

270

R677

GND

D656

560

R678

S

G

C851

3300 25V

1

D

2SC2240

Q855

2SK246

GR

G

1

C852

3300 25V

RN02

10k

H:MUTE ON

L:MUTE OFF

C

1

2

B

E

3

M-GND

DN12

DN11

N.C.

N.C.

DN61

2

2

2

3

GR,BL

C856

R852

D607

D608

B

33k

R629

D609

D610

D657

D658

B

33k

R679

D659

D660

035G

TR SHILED

Q852

231

CBE

Q851

2SK246

GR

100

R851

Q853

6.2V

ARA

C855

10 25V

ARA

10 25V

6.2V

GR,BL

Q857

2SA970

S

2

D

3

100

C

231

Q856

DTC114TS

)(

2

DTC114TS

2

CURRENT LPF

Q613

2SA970

E

3

GR,BL

2

B

1

C

Q614

C

1

2SC2240

GR,BL

2

B

E

3

47

R630

33p

560

C611

R631

Q663

2SA970

E

3

GR,BL

2

B

1

C

Q664

C

1

2SC2240

GR,BL

2

B

E

3

47

R680

33p

560

C661

R681

2SD1415A

R858

D858

1

C

2

B

3

E

D856

HZ6L-3

GNDGND GND

GNDGND GND

D857

HZ6L-3

3

E

2

B

1

C

D859

3.3k

R857

B

E

2SB1020A

035G

TR SHILED

QN04

2SA1048

Y.GR

E

B

RN03

47k

RN04

47k

QN02

1

3

M-GND

QN66

1

3

M-GND

Q623

Q618

270270

R634

E

3

Q617

2SA970

GR,BL

Q615

1

C

2SK170

D

3

V

1

G

2

S

100

R632

Q616

100

R633

2SJ74

S

2

V

G

1

3

D

C

1

Q620

2SC2240

GR,BL

3

E

R636

270

R684

E

3

Q667

2SA970

GR,BL

Q665

1

C

2SK170

D

3

V

1

G

2

S

100

R682

Q666

100

R683

2SJ74

S

2

V

G

1

3

D

C

1

Q670

2SC2240

GR,BL

3

E

270

R686

TO AUDIO

11.4V

R853

C857

3.3k

2.7k

470 16V

GND

3.3k2.7k

R854R855

3.3k

R856

2

B

2

B

2

B

2

B

2SA970

GR,BL

2SA970

GR,BL

270

R635

2SA970

E

3

GR,BL

2

B

1

C

Q619

E

3

2

B

R641

1

120

C

C

1

2

2SC2240

B

GR,BL

3

E

C

1

2

2SC2240

B

GR,BL

3

E

270

R637

Q668

270

R685

2SA970

E

3

GR,BL

2

B

1

C

Q669

3

E

2

B

R691

1

120

C

C

1

2

2SC2240

B

GR,BL

3

E

C

1

2

2SC2240

B

GR,BL

3

E

270

R687

+12V

5AC11

3AC11

C

2SC2240

GR,BL

2

B

DTG

E

D611

680p

C612

D612

47

R638

D613

Q622

Q624

2SA970

E

GR,BL

2

B

Q621

C

Q673

C

2SC2240

GR,BL

2

B

DTG

E

D661

C662

680p

D662

47

R688

D663

Q672

Q674

2SA970

E

GR,BL

2

B

Q671

C

CY51

RY55

220 50V

10 1/4w

3AC11

+5VD

+12V

1

ARA

C613

3

220 16V

GND

66

33

R639

0

33

R640

3

ARA

1

GND

C614

220 16V

1

3

33

R689

0

33

R690

3

1

LLM

DY52

ID3

ID3

DY51

+5VD2

C617

0

R644

(JUMPER)

75

C616

100 25V

ARS

R647

-12V

100

+12V

66

C666

100 25V

ARS

R697

-12V

100

3

E

1

C

GND

GND GND

TMUT1

1

C

GND

C667

0

R694

3

(JUMPER)

E

75

47k 47k

R693 R643

GND

FOR DAC(BUS LINE)

AC4.3V

AC4.3V

2SC2458

QY61

2SA1048

Y.GR.

123

C

B

M-GND

H1

H2

47

47

RY60

RY59

C

1

QY62

2

B

Y,GR

RY57

10k

E

3

DY11

ETC

4.7V

-VFT5AC11

E

CY63

100 50V

M-GND

27V

DY65

H1

H2

CY52

220 50V

RY56

M-GND

4.7k

QN61

2SC2878

B

2

QN63

2SC2878

2

B

DY61

RY58

R645

75

QN62

E

3

2SC2878

TMUT1

DSOF

-VFT

-26.8V

B

RN62

2

4.7k

C

1

GND

+12V

-12V

QN64

C

1

2SC2878

2

GND

B

RN64

4.7k

E

3

0 (Jumper)

R695

75

GND

H1

H2

RC5F

KEY0

KEY1

FDAT

FCLK

FCEN

FRES

DISPLED

RN61

4.7k

RN63

4.7k

H1

H2

27V

47k

0 (Jumper)

GND

R696

C668

CY60

CY61

0.1

H2

-VFT

H1

+5F

JL02

EARTHGND

FRONT

NC

GND

GND

JF03

17FMN-BTK

L.CH

J607

W601

1

121

6

5

4

3

2

1

2

WF07

H2

-VFT

H1

GND

+5F

+5F

RC5F

GND

KEY0

KEY1

FDAT

FCLK

FCEN

FRES

DISPLED

GND

GND

L011

USB-4

W602

L013

HF70SH28X2X10

121

2

J608

(WHT)

FRONT

L.CH

FRONT

R.CH

(RED)

TO PHONE PWB

COMMAND INTERFACE

TO FRONT PCB(PY16)

2

J605

W901

J901

PH6P

PH6P

6

5

4

3

2

1

FRONT

R.CH

1

2

J606

JL01

EARTH

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

R646

C618

NC

0.1

H2

-VFT

H1

GND

031G SHILED

LT02

DIGO

RC5F

RC5S

12

ARS

CT05

100 25V

GND

RT05

1.2k

RC-5 IN/OUT

ARA ARA

GND

C858

470 16V

TO AUDIO

2

-12V

RN05

QY63

DTC114TS

-12V

TMUT1

100k

4.7k

RY61

DSOF

1

3

M-GND

-11.4V

123

C

0.1

CN04

0.1

CT10

GND

14 8910111213

NC

1234567

RT06

100k

DIG OUT

GND

QT01

74HC04

RT02

33

GND

+5VD2

4.7k

RF56

1

RF58

8.2k

3

GND

LTD

LT01

3

CT01

0.1

2

33

RT04

CT07

47p

GND GND

LRA

RF57

3

100

1

0.1

DF51

CF53

CF54

10

GNDGND

QF52

2SC2458

C

E

47k

RF54

2

B

18k

RF55

JT03

12

12

GND

22

GNDGNDGNDGND GND

123

OPTICAL

GNDGND

JT02

LT03

1

COAX

2

LT04

3

0.1

0.1

CT11

CT04

GND

SF51

EXT

RC-5

654

321

INT/EXT SW

INT

GND

JF51

4

RC-5

2

IN OUT

3

1

RT01

100

0.1

CT06

RT03

75

4

47p

CT02

51

CT03

2200p

RF53RF52

E

4.7k4.7k

2

B

QF51

C

2SA1048

470p

CF52

0.1

CF51

RF51

LFB

+5VD2

S351

LPFSW

4.7k

R351

8.2k

0.1

R352

C351

GNDGND

GND

654

STANDARD

321

CUSTOM

109

Page 11

G[1]

G[2]

G[3]

G[4]

G[5]

G[6]

G[7]

G[8]

G[9]

G[10]

G[11]

G[12]

H1

G[13]

H2

G[13]

G[12]

G[11]

G[10]

G[8]

G[9]

G[3]

G[4]

G[5]

G[6]

G[7]

GND

GND

ISPLED

FRES

FCEN

FCLK

FDAT

KEY1

KEY0

RC5F

+5VF

+5VF

GND

-VFT

RCH

-12V

GND

+12V

LCH

TMUT

JY01

17FMN-BTK

17

16

15

14

13

12

11

10

9

8

NC

7

6

5

4

3

H1

2

1

H2

D-GND

(PR16)

HEAD PHONE PCB

J902

PH 6P

1

-11.4V

2

3

11.4V

4

5

6

A-GND

95 53

VX01

FL DISPLAY

CH2099C

1 56789101112131415161718192021222324252627282930313233343536373839404142434445 482 49

S[27]

S[29]

S[32]

S[33]

S[34]

S[35]

STOP

PLAY

2

2

B

E

C

A-GND

A-GND

C

E

S[36]

12

12

3

1

1

3

150K

RY25

-VFT

+5V

LY03

AC4.3V

12

LY02

-26.8V

12

LY01

AC4.3V

12

(PY16)

DISPLAY PCB

LHP

C901

25V

47

-12V

+12V

C902

47 25V

R925

R902

R926

4.7k

R901

4.7k

S[2]

S[3]

S[4]

H1

-VFT

H2

S[9]

S[10]

S[11]

S[13]

S[14]

S[15]

S[16]

S[17]

S[20]

S[21]

S[22]

S[23]

S[24]

S[25]

S[26]

S[28]

S[30]

S[5]

S[6]

S[7]

S[8]

1K

RY13

10K

RY14

RY15

3.3K

2

CBE

3

D-GND

S[12]

1

QY02

2SC2712 G

D-GND

12

CY01

47

LY04

S[18]

S[19]

DISPLED

FRES

FCEN

FCLK

FDAT

KEY1

KEY0

KEY0

RC-5

+5V

+3.3V

KEY1

25V

OPEN/CLOSE

S_MODE

S[31]

RY06 RY04 RY09RY01

150 180 390270

12

RY10

150 390180 270

12

LLM

+12V

1

C

Q903

2

2SC2120

B

3

E

R911

33

R913

33

3

E

Q905

2

2SA950

B

1

C

-12V

+12V

1

C

1.5K

2

Q904

B

2SC2120

3

E

R912

33

R914

33

E

3

Q906

2

2SA950

B

1

C

-12V

C905

47

C906

47

R916

100K

25V

R917

100

100K

R915

A-GND

B

R923

4.7K

Q907

2SC2878

R924

4.7K

Q908

2SC2878

R918

100

25V

A-GND

NJM2114D

25V

C904

220

NJM2114D

Q901

Q901

R907

1.5K

D901

1SS176

R903

8

33

1

R905

33

4

D903

1SS176

R909

1.5K

R908

D902

1SS176

R904

7

33

R906

33

D904

1SS176

R910

1.5K

C903

25V

220

R919

A-GND

8.2K

Q909

2SC2878

1

C

2

B

A-GND

3

E

1.2K

1.2K

Q910

B

2

2SC2878

E

C

A-GND

31

R930

H.P VOL 10KB

A-GND

46

3

1

A-GND

2

R921

4.7K

3

A-GND

A-GND

2

5

5

R922

4.7K

6

R920

8.2K

L901

L902

S[37]

NEXT

PREV

RY02

SY02

S[38]

A-GND

A-GND

12

12

S[39]

C907

1000P

C908

1000P

464

S[40]

TIME

RY03RY05

PAUSE

A-GND

A-GND

SY03

C909

N.C.

505154555657585960616263646566676869707172737475767778798081828384858687888990919293949798

12

12

J903

CY04

0.047

SY07SY09SY01SY04SY06

12

DIS_OFF

D-GND

SY08SY10 SY05

12

TEXT

D-GND

H.P JACK(BLACK)

2

3

1

EARTH

-VFT

D-GND

+3.3V

D-GND D-GND

WY11

WY13

4MHz(CERALOCK)

25V

47

0.1

CY03

CY02

11

D-GND

XY01

D-GND

RY24

FRES

FCEN

FCLK

FDAT

DISPLED

RC-5

+5V

RY22

100

CY06

0.1

D-GND D-GND

CY05

220

680

ZY01

IR SENSER

10V

60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41

S[38]

S[37]

S[36]

S[35]

S[34]

S[33]

S[32]

S[31]

S[30]

S[29]

S[28]

S[27]

S[26]

S[25]

S[24]

S[23]

S[22]

RY26

N.C.

13

3

G[2]

G[1]

QY04

DTA114EK

CY08

N.C.

D-GND D-GND

+5V

1

CY09

2

N.C.

D-GND

RY17

270

WY01

SAN 2P L=60MM

1

2

COM22

COM21

COM20

COM19

COM18

COM17

COM16

COM15

COM14

COM13

COM12

COM11

COM10

COM 9

COM8

COM7

COM6

COM5

COM4

COM3

SEG14

3

QY05

DY02

SEG15

S[18]

DTA114EK

SEG16

S[19]

QY03

RY16

33K

SEG17

S[20]

S[21]

+5V

D-GND

COM2

COM1

VDISP1

SEG35

SEG34

SEG33

SEG32

SEG31

SEG30

SEG29

SEG28

SEG27

SEG26

SEG25

SEG24

SEG23

SEG22

SEG21

SEG20

SEG19

SEG18

1

2

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

2

D-GND

61

COM23

COM24

62

VFL1

63

GND

64

OSC0

65

OSC1

66

XRESET

67

XCS

68

XCP

69

DA

70

VDD

71

P1

72

P2

73

P3

74

P4

75

VFL2

76

NC

77

VDISP2

78

S[39]

AD1

79

S[40]

AD2

80

AD3

AD4

SEG1

SEG2

330p

CY07

SEG3

S[3]

S[4]

S[5]

S[6]

S[7]

31

02CZ3.9-X

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

S[2]

D-GND

1

RY23

1K

2

D-GND

3

SEG4

DY07

S[8]

SEG5

S[9]

SEG6

FL DRIVER

ML9207-01

SEG7

S[10]

2

S[11]

QY01

SEG8

3

S[12]

SEG9

SEG10

S[13]

RY18

470

SEG11

S[14]

D-GND

S[15]

+5V

SEG12

1

2

SEG13

S[17]

S[16]

DTA114EK

DISPLAY OFF

(PY26)

ILMINATION PCB

JY02

LLM

DY01

ILMINATION

0.1

CY10

10k

RY27

PH 2P

1

1

2

2

11 12

Page 12

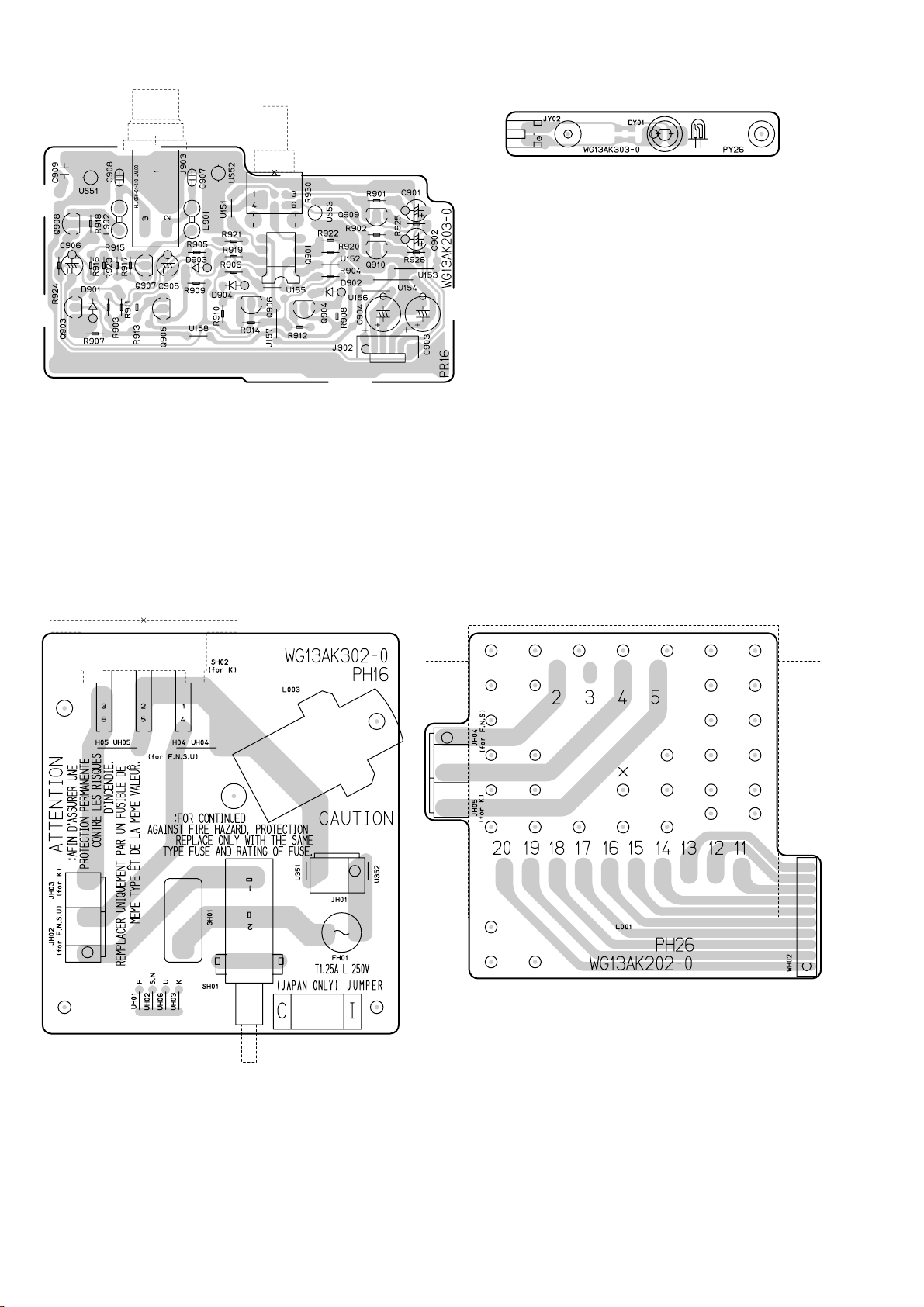

9. PARTS LOCATION

PP16

QD01

QD24- QD21

Q803 QN66 QY63

Q802 Q801

Q601 - Q608

Q651 - Q658QN65

QN04 QN02 QN01 QN06

Q822 Q821QY61 Q853 Q851 Q857 Q855

Q609 - Q614

Q659 - Q664 Q665 - Q672 Q673 Q674

Q615 - Q622 Q623 Q624 QN61 QN62

Q852

Q856

QN64 QN63

QT01

QF51 QF52QY62

1413

Page 13

PY16

QY01

QY07

QY05

QY04 QY03

QY02

15

Page 14

PR16

Q908

Q903

Q907

Q905

Q906

Q901

Q904

PY26

Q909

Q910

PH16

PH26

16

Page 15

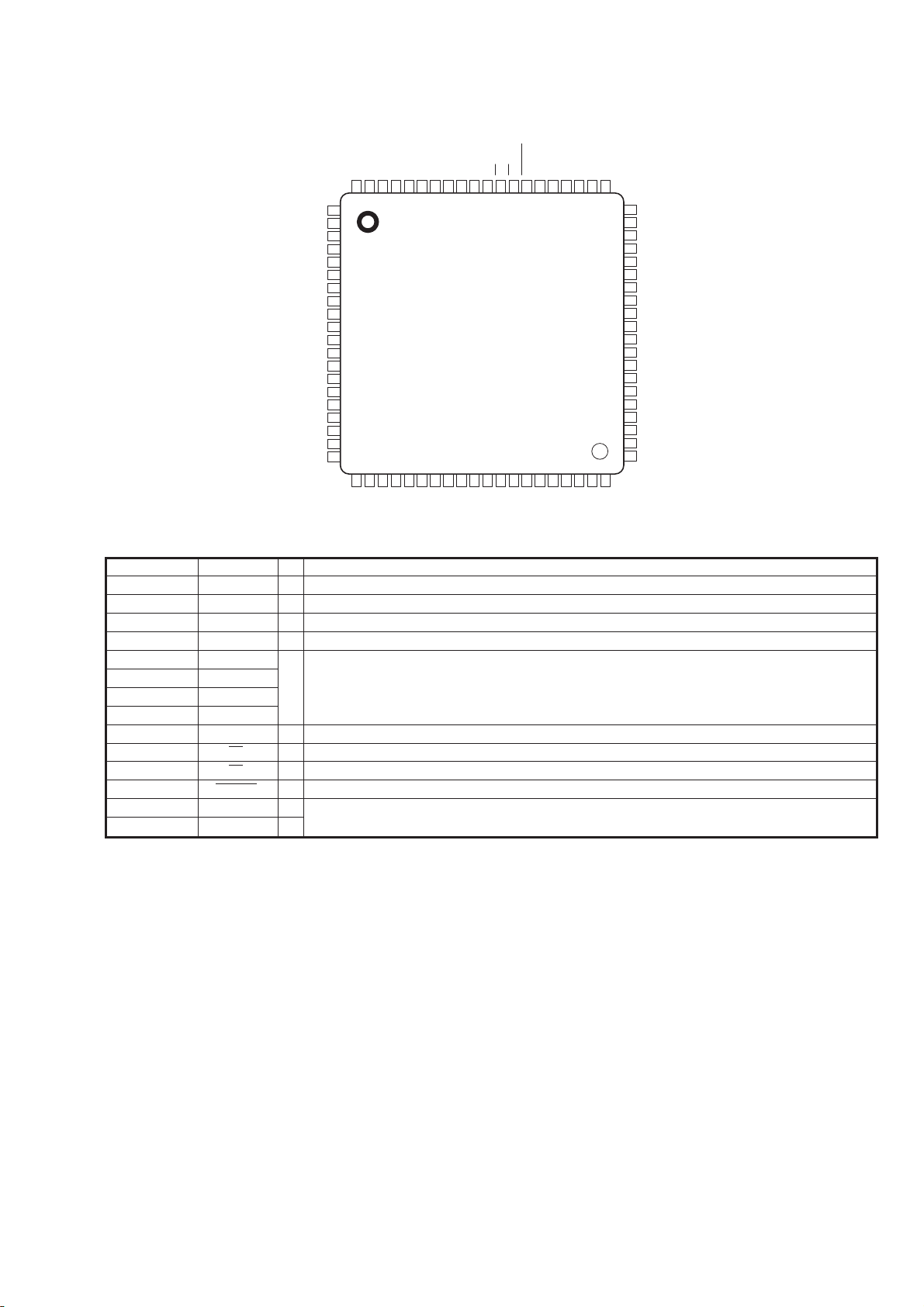

10. MICROPROCESSOR AND IC DATA

QY01 : ML9207-01

FL2

AD3

AD4

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

DISP2

NC

V

AD1

AD2

77

78

79

80

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

24

23

22

21

SEG22

SEG21

SEG20

SEG19

P4

V

75

76

26

25

SEG23

SEG24

P2

P3

73

74

28

27

SEG26

SEG25

72

29

SEG27

ML9207-01 Terminal Function

Pin Name FunctionPin No. I/O

3~37 SEG1~35 O FL display anode drive output pin

39~62 COM1~24 O FL display grid drive output pin

1,2, 79, 80 AD1~4 O FL display anode drive output pin

72~75 P1~4 O General port output pin

71 VDD

38, 78 VDISP1~2

64 GND

63, 76 VFL1~2

70 DA I Serial data input pin (positive logic)

69 CP I Shift clock input pin

68 CS I Chip select input pin

67 RESET I Reset input pin

65 OSC0 I

66 OSC1 O

VDD-GND: Power supply for logic block

VDISP-VFL: Power supply for FL display drive

For V

DD and VDISP, apply from same power source

Pin for self-oscillation

DA

VDDP1

70

71

31

30

SEG29

SEG28

CS

CP

68

69

33

32

SEG31

SEG30

OSC1

RESET

66

67

35

34

SEG33

SEG32

GND

OSC0

64

65

37

36

SEG35

SEG34

FL1

COM23

COM24

V

61

62

63

60

COM22

59

COM21

58

COM20

57

COM19

56

COM18

55

COM17

54

COM16

53

COM15

52

COM14

51

COM13

50

COM12

49

COM11

48

COM10

47

COM9

46

COM8

45

COM7

44

COM6

43

COM5

42

COM4

41

COM3

40

39

38

DISP1

V

COM2

COM1

17

Page 16

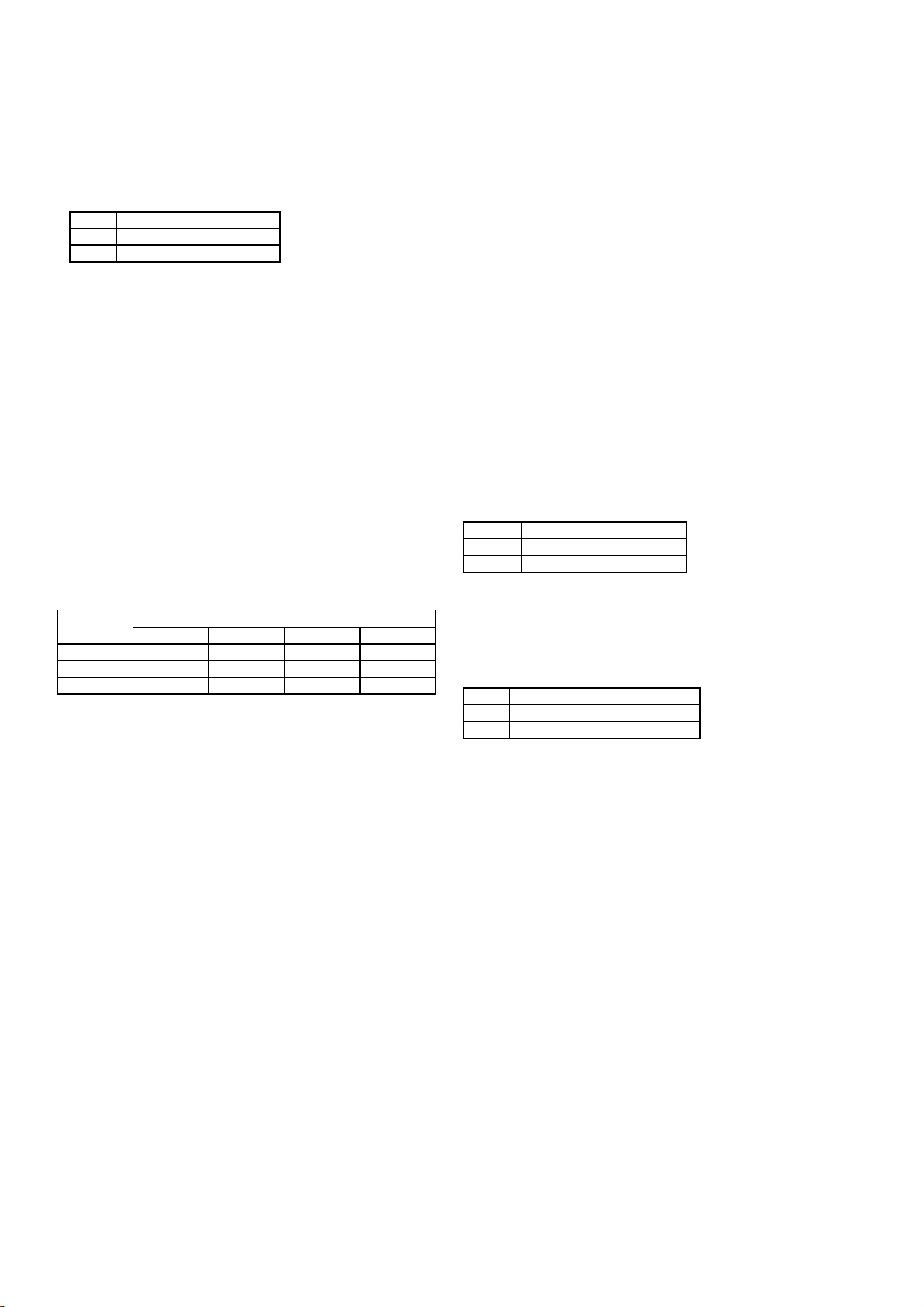

QD61 : CS4397

Reset - RST

Pin 1, Input

Function:

The device enters a low power mode and all internal state

machines registers are reset when low. When

high, the device will be in a normal operation mode .

clocked into SDATA via the serial clock

and the channel is determined by the Left/Right clock. The

required relationship between the Left/Right

clock, serial clock and serial data is defi ned by the Mode Control

Byte and the options are detailed inin

Figures 29-33

RST DESCRIPTION

0 Enabled

1 Normal operation mode

Digital Ground - DGND

Pins 6 and 9, Inputs

Function:

Digital ground reference.

Digital Power - VD

Pins 7 and 8, Input

Function:

Digital power supply. Typically 5.0 to 3.0 VDC.

Master Clock - MCLK

Pin 10, Input

Function:

The master clock frequency must be either 256x, 384x, 512x or

768x the input sample rate in Single

Speed Mode; either 128x, 192x 256x or 384x the input sample

rate in Double Speed Mode; or 64x, 96x

128x or 192x the input sample rate in Quad Speed Mode. Tables

4-6 illustrate the standard audio sample

rates and the required master clock frequencies.

Sample

Rate (kHz)

32 8.1920 12.2880 16.3840 24.5760

44.1 11.2896 16.9344 22.5792 33.8688

48 12.2880 18.4320 24.5760 36.8640

Table 4. Single Speed (16 to 50 kHz sample rates) Common Clock

Frequencies

Serial Clock - SCLK

Pin 11, Input

Function:

Clocks individual bits of serial data into the SDATA pin. The

required relationship between the Left/Right

clock, serial clock and serial data is defi ned by either the Mode

Control Byte in Control Port Mode or the

M0 - M4 pins in Hardware Mode. The options are detailed in

Figures 29-33

Left/Right Clock - LRCK

Pin 12, Input

Function:

The Left/Right clock determines which channel is currently being

input on the serial audio data input,

SDATA. The frequency of the Left/Right clock must be at the input

sample rate. Audio samples in

Left/Right sample pairs will be simultaneously output from the

digital-to-analog converter whereas

Right/Left pairs will exhibit a one sample period difference. The

required relationship between the

Left/Right clock, serial clock and serial data is defi ned by the

Mode Control Byte and the options are de-

tailed in Figures 29-33

256x 384x 512x 768x

MCLK (MHz)

Soft Mute - MUTE

Pin 15, Input

Function:

The analog outputs will ramp to a muted state when enabled. The

ramp requires 1152 left/right clock cy-

cles in Single Speed, 2304 cycles in Double Speed and 4608

cycles in Quad Speed mode. The bias volt-

age on the outputs will be retained and MUTEC will go active at

the completion of the ramp period.

The analog outputs will ramp to a normal state when this function

transitions from the enabled to disabled

state. The ramp requires 1152 left/right clock cycles in Single

Speed, 2304 cycles in Double Speed and

4608 cycles in Quad Speed mode. The MUTEC will release

immediately on setting MUTE = 1.

The converter analog outputs will mute when enabled. The bias

voltage on the outputs will be retained

and MUTEC will go active during the mute period.

Mute DESCRIPTION

0 Enabled

1 Normal operation mode

Control Port / Hardware Mode Select - C/H

Pin 16, Input

Function:

Determines if the device will operate in either the Hardware Mode

or Control Port Mode.

C/H DESCRIPTION

0 Hardware Mode Enabled

1 Control Port Mode Enabled

Mute Control - MUTEC

Pin 17, Output

Function:

The Mute Control pin goes low during power-up initialization,

reset, muting, master clock to left/right clock

frequency ratio is incorrect or power-down. This pin is intended to

be used as a control for an external mute

circuit to prevent the clicks and pops that can occur in any single

supply system. Use of Mute Control is not

mandatory but recommended for designs requiring the absolute

minimum in extraneous clicks and pops.

Analog Ground - AGND

Pins 18 and 21, Inputs

Function:

Analog ground reference.

Differential Analog Outpus - AOUTR- , AOUTR+ and AOUTL- ,

AOUTL+

Pins 19, 20, 23 and 24, Outputs

Function:

The full scale differential analog output level is specifi ed in the

Analog Characteristics specifi cations table.

Serial Audio Data - SDATA

Pin 13, Input

Function:

Serial audio data is input on this pin. The selection of the Digital

Interface Format is determined by set-

tings of the Mode select as detailed in Figures 29-33. The data is

Analog Power - VA

Pin 22, Input

Function:

Power for the analog and reference circuits. Typically 5VDC.

18

Page 17

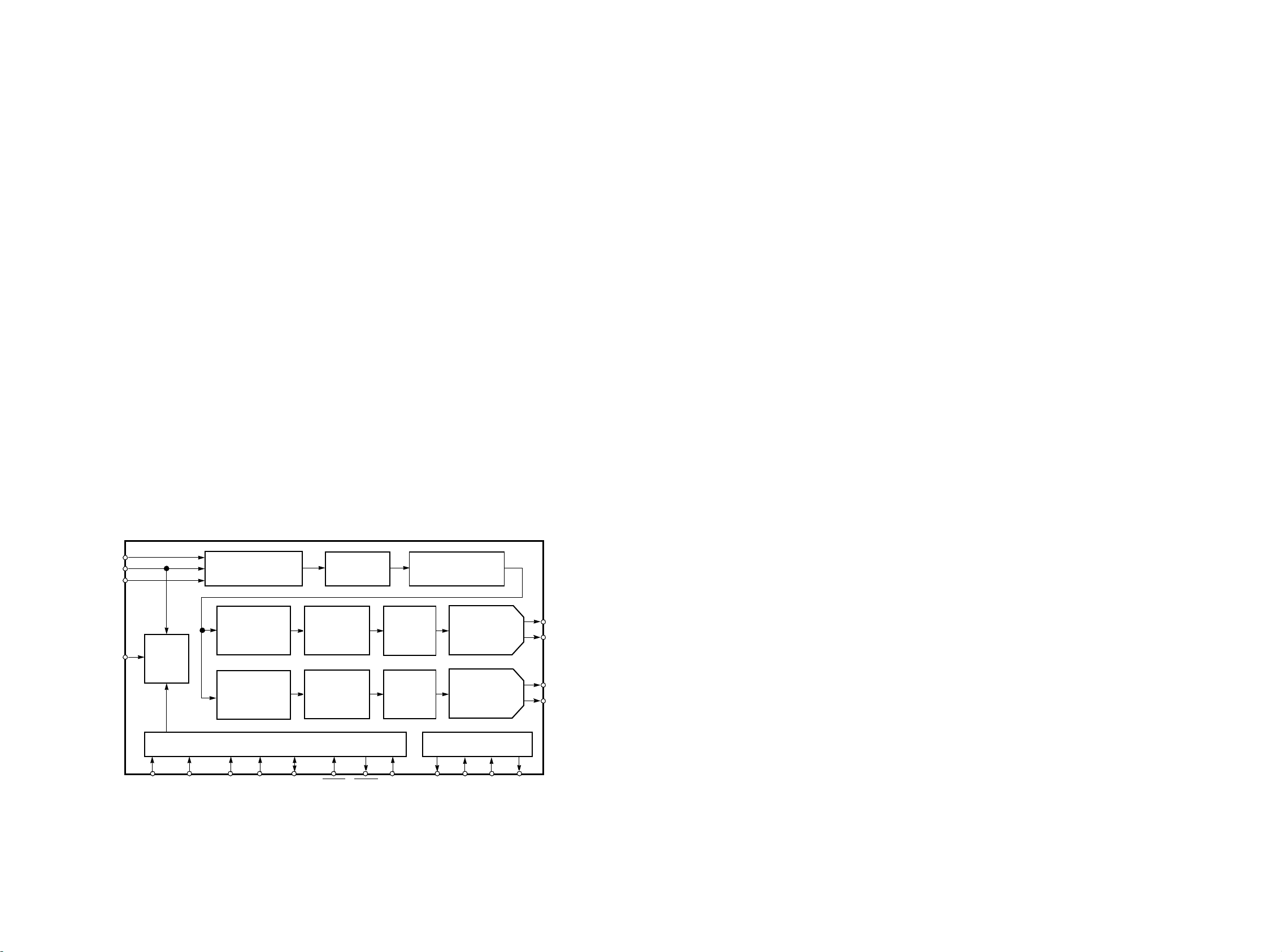

QD61 : CS4397

Common Mode Voltage - CMOUT

Pin 25, Output Function:

Filter connection for internal bias voltage, typically 50% of VREF.

Capacitors must be connected from CMOUT to analog ground,

as shown in Figure 6. CMOUT has a typical source impedence

of 25 kΩ and any current drawn from this pin will alter device

performance

Reference Ground - FILT-

Pin 26, Input Function:

Ground reference for the internal sampling circuits. Must be

connected to analog ground.

Reference Filter - FILT+

Pin 27, Output Function:

Positive reference for internal sampling circuits. External

capacitors are required from FILT+ to analog ground, as shown in

Figure 6. FILT+ is not intended to supply external current.

Voltage Reference Input- VREF

Pin 28, Input Function:

Analog voltage reference. Typically 5VDC.

HARDWARE MODE

Mode Select - M0, M1, M2, M3, M4

Pins 2, 3, 4, 5 and 14, Inputs Function:

The Mode Select pins determine the operational mode of the

device as detailed in Tables 9-14. The op-tions include;

Selection of the Digital Interface Format which determines the

required relationship between the Left/Right clock, serial clock

and serial data as detailed in Figures 29-33 Selection of the

standard 15 µs/50 µs digital de-emphasis fi lter response, Figure

28, which requires re-confi guration of the digital fi lter to maintain

the proper fi lter response for 32, 44.1 or 48 kHz sample rates.

Selection of the appropriate clocking mode to match the input

sample rates. Access to the Direct Stream Digital Mode Access

to the 8x Interpolation Input Mode

CONTROL PORT MODE

Address Bit 0 / Chip Select - AD0 / CS

Pin 2, Input Function:

2

In I

C mode, AD0 is a chip address bit. CS is used to enable the

control port interface in SPI mode. The device will enter the SPI

mode at anytime a high to low transition is detected on this pin.

Once the device has entered the SPI mode, it will remain until

either the part is reset or undergoes a power-down cycle.

Address Bit 1 / Control Data Input - AD1/CDIN

Pin 3, Input Function:

In I2C mode, AD1 is a chip address bit. CDIN is the control data

input line for the control port interface in SPI mode.

Serial Control Interface Clock - SCL/CCLK

Pin 4, Input Function:

In I2C mode, SCL clocks the serial control data into or from

SDA/CDOUT.

In SPI mode, CCLK clocks the serial data into AD1/CDIN and out

of SDA/CDOUT.

Serial Control Data I/O - SDA/CDOUT

Pin 5, Input/Output Function:

In I2C mode, SDA is a data input/output. CDOUT is the control

data output for the control port interface in SPI mode.

M1 - Mode Select

Pin 14, Input Function:

This pin is not used in Control Port Mode and must be terminated

to ground.

SCLK

LRCK

SDATA

MCLK

CLOCK

DIVIDER

M4

(AD0/CS)

SERIAL INTERFACE

AND FORMAT SELECT

INTERPOLATION

INTERPOLATION

HARDWARE MODE CONTROL

M3 M2

(AD1/CDIN) (SCL/CCLK)

FILTER

FILTER

(CONTROL PORT)

M1

M0

(SDA/CDOUT)

SOFT MUTE

MULTI-BIT

∆Σ

MODULATOR

MULTI-BIT

∆Σ

MODULATOR

RESET MUTEC MUTE

DYNAMIC

ELEMENT

MATCHING

LOGIC

DYNAMIC

ELEMENT

MATCHING

LOGIC

DE-EMPHASIS

FILTER

SWITCHED

CAPACITOR-DAC

AND FILTER

SWITCHED

CAPACITOR-DAC

AND FILTER

VOLTAGE REFERENCE

VREF CMOUTFILT-

FILT+

AOUTL+

AOUTL-

AOUTR+

AOUTR-

19 20

Page 18

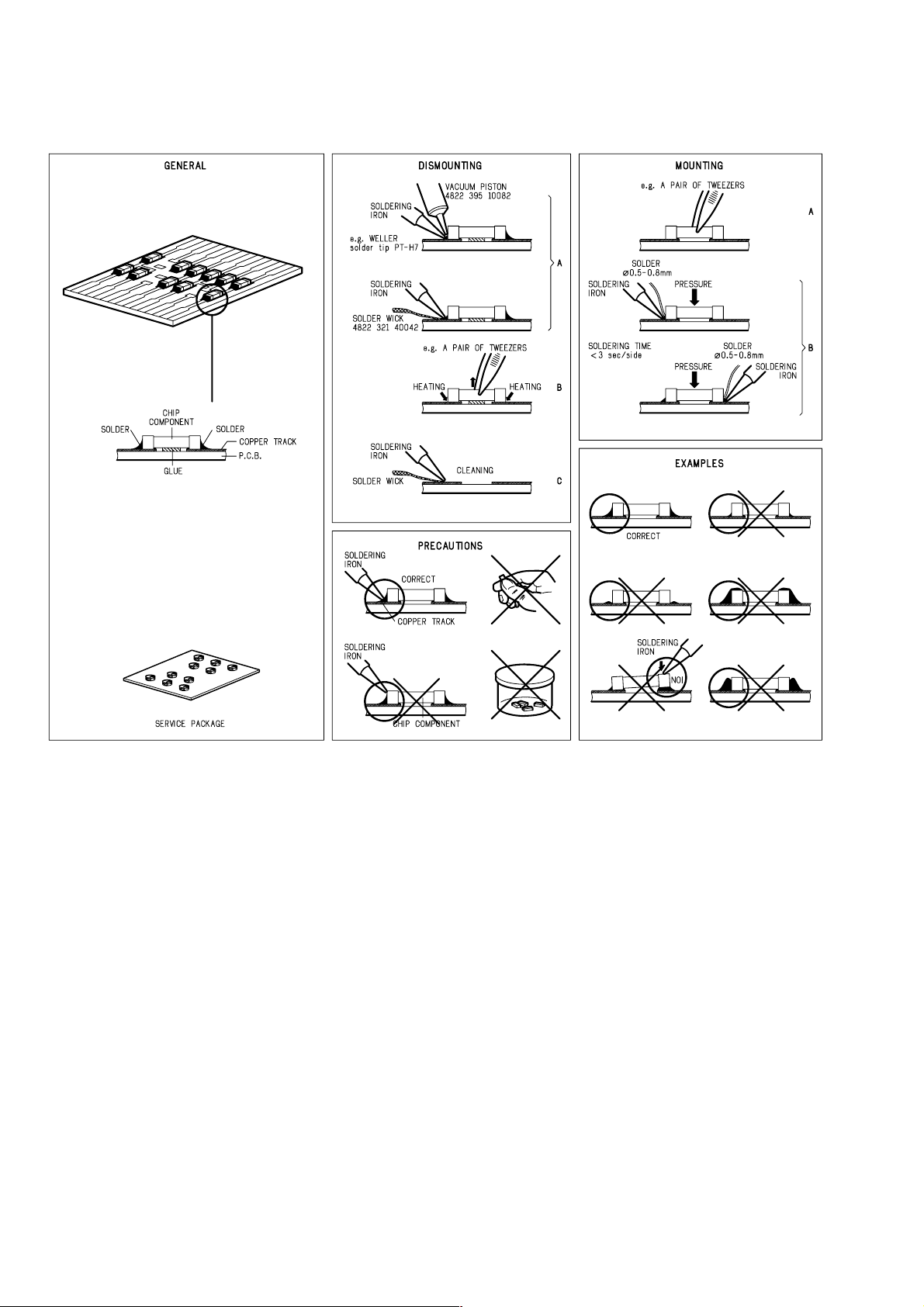

11. EXPLODED VIEW AND PARTS LIST

S

U

P

E

R

A

U

D

I

O

C

D

T100

SYMBOL ST YL E

5110

5126

5127

5128

5129

5150

5192

5404

5405

MARK

MATERIA L/ FINISH

(M)

STEEL /C OPPER

(U )

STEEL /BLACK

(A )

STEEL /CHROMATE

5405

3( M)

001B

017B

011B

PARTS NAME

+B .H .M .SCREW

+B .H .T APTITE SC REW W/ WASHER

+B .H .T APTITE SC REW (W /)

+B .H .T APTITE SC REW (B TYPE )

+B .H .T APTITE SC REW (W /T.L .WASHER )

+F .H .TAP TITE SCREW (B TY PE )

+P .H .M .SCR EW (M INUTE)

SPRING L OC K WASHER S

TOOT HED L OCK WASHER S

5129

3X8( M)

008B

5128

3X10( M)

003B

035Bx3

5128

3X8( M)

012B

5405

3( M)

5128

3X12( M)

x2

029B

5128

3X8( M)

020B

5128

3X10( M)

5126

3X10( M)

5128

3X8( M)

5126

3X8( M)

x4

x4

PY26

040B

x3

010B

x2

5405

3( M)

031B

5128

3X8( M)

5126

3X10( M)

002B

VX01

022B

009B

001D

030B

013B

021B

026B

PY16

016B

027B

5126

3X8( M)

007M

008M

015B

PR16

5128

3X8( M)

x2

5129

3X8( M)

1. 7X9( U)

S

U

P

E

R

A

U

D

I

O

Mecha Loader and

Mecha Traverse

Super Audio CD

PCB Module

014B

025G

032G

x2

5192

x2

C

D

L011

5405

2( M)

x2

5128

3X8( M)

x9

030G

5128

3X8( M)

x2

( 002M)

( 003M)

(006M)

5148

3X6( M)

x3

PH16

( 5110)

3X6( M)

x4

L003

( 5128)

2. 6X6( U)

x4

5129

3X8( M)

5128

3X8( M)

x9

PH26

5129

3X8( M)

x4

5110

3X6( M)

5405

3( M)

L013

/K/L ONLY

908G

024G

033G

x2

5128

3X10( M)

x4

L012

022L

002G

5128

3X8( M)

J001

925G

5126

3X8( M)

x3

L001

023G

x4

035Gx2

x2

027G

W002

5129

3X8( M)

5148

3X6( M)

x7

021L

x3

022G

001G

/F Only

5128

3X8( M) x2

5127

3X8( M)

PP16

031Gx2

/K/S ONLY

/S Only

5127

3X8( M)

x4

035G

W001

/N Only

5128

3X5( M)

920G

J608

5126

3X8( M)

901G

5110

3X8( M)

J607

2221

Page 19

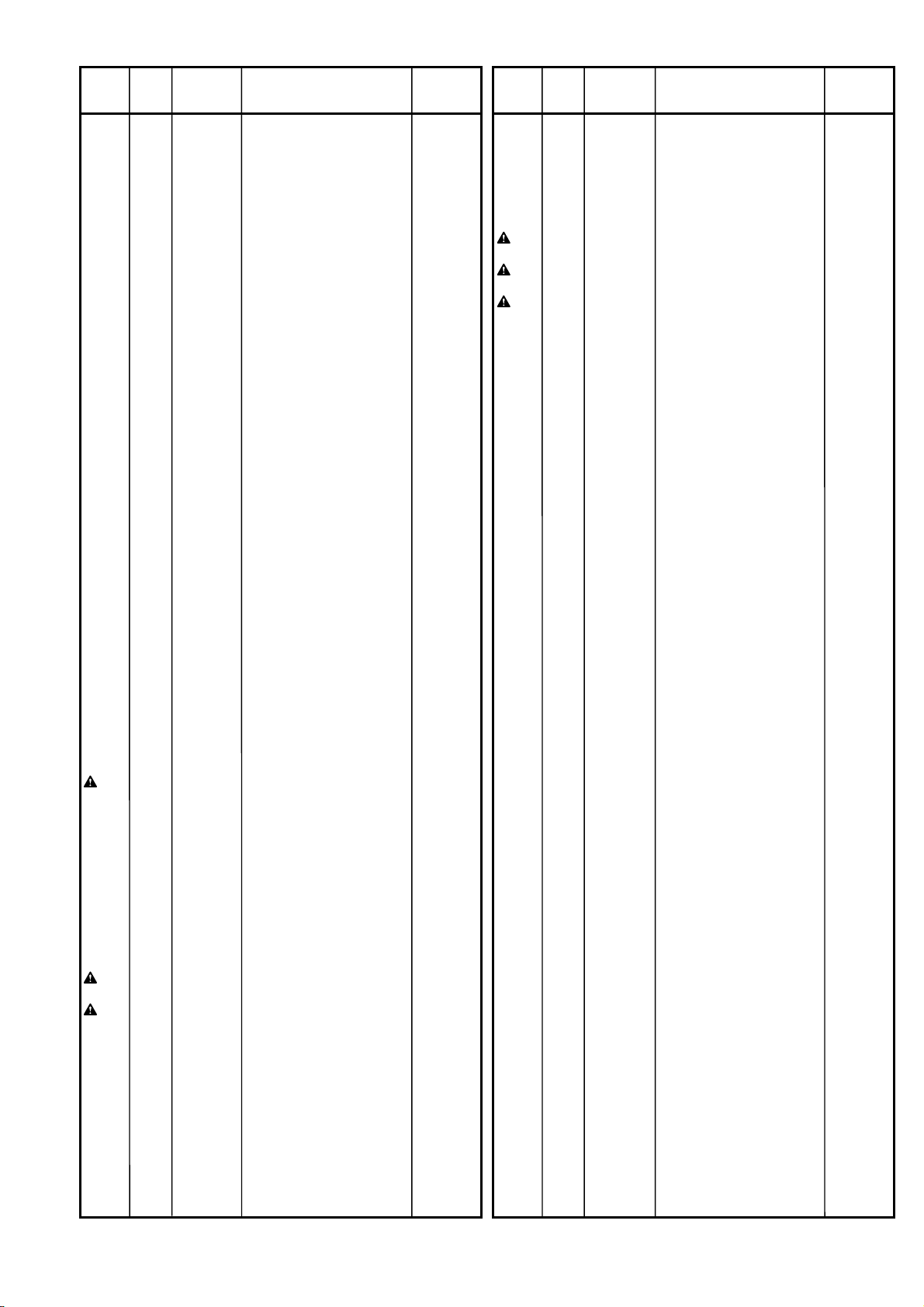

POS.

NO

VERS.

COLOR

PART NO.

(FOR EUR)

DESCRIPTION

PART NO.

(MJI)

POS.

NO

VERS.

COLOR

PART NO.

(FOR EUR)

DESCRIPTION

PART NO.

(MJI)

001B GOLD 13AK248110 FRONT AL PANEL GOLD 13AK248110

001B BLACK 13AK248010 FRONT AL PANEL BLACK 13AK248010

002B GOLD 13AK105120 CHASSIS

13AK105120

FRONT MOLD PANEL GOLD

002B BLACK 13AK105020 CHASSIS

13AK105020

FRONT MOLD PANEL BLACK

003B 13AK355010 LENS ESCUTCHEON 13AK355010

011B 01AK251010 BADGE SUPER AUDIO CD LOGO 01AK251010

012B 01AK158020 WINDOW 01AK158020

015B 382K355010 LENS 382K355010

017B 24AW251010 BADGE NEW MARANTZ LOGO 24AW251010

020B GOLD 05AK270110 BUTTON POWER GOLD 05AK270110

020B BLACK 05AK270010 BUTTON POWER BLACK 05AK270010

021B GOLD 13AK270110 BUTTON 6 GOLD 13AK270110

021B BLACK 13AK270010 BUTTON 6 BLACK 13AK270010

022B GOLD 13AK270120 BUTTON 4 GOLD 13AK270120

022B BLACK 13AK270020 BUTTON 4 BLACK 13AK270020

029B GOLD 284T154250 KNOB PHONE VOLUME GOLD 284T154250

029B BLACK 284T154310 KNOB PHONE VOLUME BLACK 284T154310

030B 376K121010 LINK FOR POWER BUTTON 376K121010

040B GOLD 13AK063120 ESCUTCHEON GOLD 13AK063120

040B BLACK 13AK063020 ESCUTCHEON BLACK 13AK063020

032G 183J057010 LEG FRONT 183J057010

033G 183J057110 LEG REAR 183J057110

908G /K/L nsp BUSHING FOR MAINS CORD 450H259010

002M 13AK304010 MECHA LOADER AND

13AK304010

MECHA TRAVERSE

006M ZK13AK0020 SUPER AUDIO CD PCB MODULE ZK13AK0020

007M GOLD 13AK063110 ESCUTCHEON

13AK063110

FOR CD TRAY GOLD

007M BLACK 13AK063010 ESCUTCHEON

13AK063010

FOR CD TRAY BLACK

008M 392K063160 ESCUTCHEON

392K063160

SUPER AUDIO CD LOGO

J001 /F/N/S YJ04002550 JACK MAINS INLET TYPE HF-301 YJ04002550

J607 YT02011290 TERMINAL

YT02011290

EW-2560T-LH-W FOR L-CH

J608 YT02011280 TERMINAL

YT02011280

EW-2560T-LH-R FOR R-CH

L003 FC50230010 FERRITE CORE TFCK-23-11-14

FC50230010

FOR W002, W003

L011 FC50270040 FERRITE CORE USB-4 FOR W901 FC50270040

L012 FC90280010 FERRITE CORE

FC90280010

HF70SH28*2*10 FOR WF04

L013 FC90280010 FERRITE CORE

FC90280010

HF70SH28*2*10 FOR WF07

W002 /K nsp MAINS CORD

YC01800880

CCEE APP.AC250V 10A+ VAR2P

W002 /L nsp MAINS CORD

YC01800950

CCEE APP.AC250V 10A+ VAR2P

WF04 YU25110520 JUMPER LEAD JF01-CY251

YU25110520

FFC 1MM-PITCH 25P

WF05 YU25110520 JUMPER LEAD JF01-CY252

YU25110520

FFC 1MM-PITCH 25P

WF07 YU17120520 JUMPER LEAD JF03-JY01

YU17120520

FFC 1MM-PITCH 17P

PACKING

001T /F nsp USER GUIDE SA8400 /F 13AK851110

001T /K/L/S nsp USER GUIDE SA8400 /K/L/S 13AK851350

001T /N 13AK851310 USER GUIDE SA8400 /N 13AK851310

T100 ZK13AK0010 REMOTE CONTROLLER

ZK13AK0010

RC8400SA

W001 /F nsp MAINS CORD

ZC01802080

AC 125V 12A FOR F OFC

W001 /N ZC01803080 MAINS CORD

ZC01803080

AC 250V 10A CLASS2

W001 /S nsp MAINS CORD

ZC01804100

AC 250V 10A FOR UK

NOT STANDARD

SPARE PART

001S nsp PACKING CASE 13AK801010

002S nsp CUSHION L/R 02AJ809010

001D GOLD nsp LID TOP COVER GOLD 02AJ257120

001D BLACK nsp LID TOP COVER BLACK 02AJ257020

NOTE : "nsp" PART IS LISTED FOR REFERENCE ONLY, MARANTZ WILL NOT SUPPLY THESE PARTS.

23

Page 20

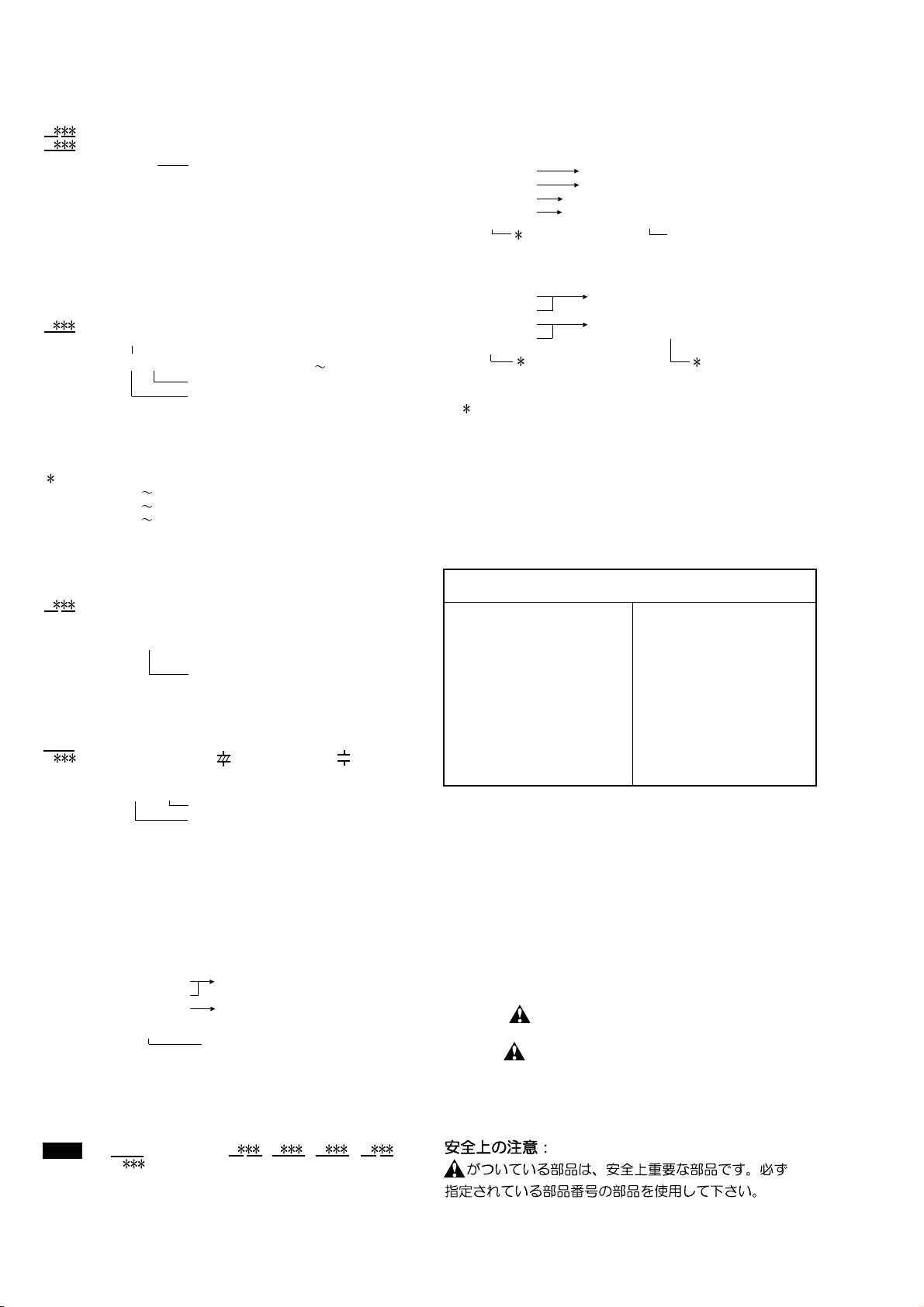

12. ELECTRICAL PARTS LIST

ASSIGNMENT OF COMMON PARTS CODES.

RESISTORS

R : 1) GD05 × × × 140, Carbon film fixed resistor, ±5% 1/4W

R : 2) GD05 × × × 160, Carbon film fixed resistor, ±5% 1/6W

Examples ;

Resistance value

➀

0.1 Ω.... 001 10 Ω .... 100 1 kΩ .... 102 100 kΩ.... 104

0.5 Ω.... 005 18 Ω .... 180 2.7 kΩ .... 272 680 kΩ .... 684

1 Ω .... 010 100 Ω .... 101 10 kΩ .... 103 1 MΩ.... 105

6.8 Ω.... 068 390 Ω .... 391 22 kΩ .... 223 4.7 MΩ.... 475

Note : Please distinguish 1/4W from 1/6W by the shape of parts

used actually.

CAPACITORS

C : CERAMIC CAP.

3) DD1 × × × × 370, Ceramic capacitor

Examples ;

Tolerance (Capacity deviation)

➁

±0.25 pF .... 0

Tolerance of COMMON PARTS handled here are as follows :

C : CERAMIC CAP.

Examples ;

C : 5) ELECTROLY CAP. ( ), 6) FILM CAP. ( )

Examples ;

0.5 pF 5 pF .... ±0.25 pF

Capacity value

➂

0.5 pF ....005 3 pF .... 030 100 pF .... 101

1.5 pF ....015 47 pF .... 470 560 pF .... 561

4) DK16 × × × 300, High dielectric constant ceramic

Capacity value

➃

100 pF .... 101 1000 pF ....102 10000 pF .... 103

470 pF .... 471 2200 pF ....222

5) EA × × × × × × 10, Electrolytic capacitor

Capacity value

➄

0.1 µF.... 104 4.7 µF .... 475 100 µF ....107

0.33 µF.... 334 10 µF .... 106 330 µF ....337

Working voltage

➅

{

➂

{

{

➅

Resistance value

Disc type

Temp.coeff.P350 N1000, 50V

Capacity value

Tolerance

capacitor

Disc type

Temp.chara. 2B4, 50V

Capacity value

One-way lead type, Tolerance ±20%

Working voltage

Capacity value

2200 µF ....228

➀

{

➁

±0.5 pF .... 1

±5% .... 5

6 pF 10 pF .... ±0.5 pF

12 pF 560 pF .... ±5%

1 pF .... 010 10 pF .... 100 220 pF .... 221

➃

{

➄

1 µF....105 22 µF .... 226 1100 µF ....118

6.3V.... 006 25V .... 025

10V .... 010 35V .... 035

16V .... 016 50V .... 050

NOTE ON SAFETY FOR FUSIBLE RESISTOR :

The suppliers and their type numbers of fusible resistors

are as follows;

1. KOA Corporation

Part No. (MJI) Type No. (KOA) Description

NH05 × × × 140 RF25S × × × × ΩJ(±5% 1/4W)

NH05 × × × 120 RF50S × × × × ΩJ(±5% 1/2W)

NH85 × × × 110 RF73B2A × × × × ΩJ(±5% 1/10W)

NH95 × × × 140 RF73B2E × × × × ΩJ(±5% 1/4W)

2. Matsushita Electronic Components Co., Ltd

Part No. (MJI) Type No. (MEC) Description

NF05 × × × 140 ERD-2FCJ × × × (±5% 1/4W)

RF05 × × × 140

NF02 × × × 140

RF02 × × × 140

Examples ;

{

Resistance value

ERD-2FCG

{

Resistance value

Resistance value

0.1 Ω.... 001 10 Ω .... 100 1 kΩ .... 102 100 kΩ.... 104

0.5 Ω.... 005 18 Ω .... 180 2.7 kΩ .... 272 680 kΩ .... 684

1 Ω .... 010 100 Ω .... 101 10 kΩ .... 103 1 MΩ.... 105

6.8 Ω.... 068 390 Ω .... 391 22 kΩ .... 223 4.7 MΩ.... 475

{

Resistance value

(0.1 Ω − 10 kΩ)

× × × (±2% 1/4W)

{

Resistance value

ABBREVIATION AND MARKS

ANT. : ANTENNA BATT. : BATTERY

CAP. : CAPACITOR CER. : CERAMIC

CONN. : CONNECTING DIG. : DIGITAL

HP : HEADPHONE MIC. : MICROPHONE

µ-PRO : MICROPROCESSOR REC. : RECORDING

RES. : RESISTOR SPK : SPEAKER

SW : SWITCH TRANSF. : TRANSFORMER

TRIM. : TRIMMING TRS. : TRANSISTOR

VAR. : VARIABLE X’TAL : CRYSTAL

NOTE ON FUSE :

Regarding to all parts of parts code FS20xxx2xx, replace

only with Wickmann-Werke GmbH, Type 372 non glass type

fuse.

6) DF15 × × × 350 Plastic film capacitor

DF15 × × × 310 One-way type, Mylar ±5% 50V

DF16 × × × 310 Plastic film capacitor

Examples ;

Capacity value

➆

0.001 µF (1000 pF) ....... 102 0.1 µF .... 104

0.0018 µF ........................ 182 0.56 µF .... 564

0.01 µF........................ 103 1 µF ....105

0.015 µF ........................ 153

: 1) The above CODES ( R , R , C , C and

NOTE

C ) are omitted on the schematic diagram in some

case.

2) On the occasion, be confirmed the common parts on

the parts list.

3) Refer to “Common Parts List” for the other common

parts (RI05, DD4, DK4).

➆

{

One-way type, Mylar ±10% 50V

Capacity value

NOTE ON SAFETY :

Symbol Fire or electrical shock hazard. Only original

parts should be used to replaced any part marked with

symbol . Any other component substitution (other

than original type), may increase risk of fire or electrical

shock hazard.

010728MIT

24

Page 21

POS.

NO

VERS.

COLOR

PART NO.

(FOR EUR)

DESCRIPTION

PART NO.

(MJI)

POS.

NO

VERS.

COLOR

PART NO.

(FOR EUR)

DESCRIPTION

PART NO.

(MJI)

PH16-POWER SWITCH

CIRCUIT BOARD

FH01 /K/L/N /SFS20125200 FUSE T1.25A 250V VDE SEMKO FS20125200

GH01 DF77103500 FILM 0.01µF M 250V AC DF77103500

JH01 YP04000760 PLUG CONNECTOR B2P3-VH YP04000760

JH02 /F/N/S YP04000760 PLUG CONNECTOR B2P3-VH YP04000760

JH03 /K/L nsp PLUG CONNECTOR B3P5-VH YP04000920

SH01 SP01012480 PUSH SWITCH

SP01012480

ESB92S94B TV-5 1.5MM

SH02 /K/L nsp VOLTAGE SELECTOR SDKGA4 SS02021510

PH26-TRANSFORMER

CIRCUIT BOARD

JH04 /F/N/S YP04000760 PLUG CONNECTOR B2P3-VH YP04000760

JH05 /K/L nsp PLUG CONNECTOR B3P5-VH YP04000920

L001 /F nsp TRANSF. EI66-30 AC100V F TS16679010

L001 /K/L nsp TRANSF. EI66-30 AC110V/220 K TS16679020

L001 /N/S TS16679030 TRANSF. EI66-30 AC230V S TS16679030

PP16-POWER/AUDIO (L R)

CIRCUIT BOARD

PP16-CAPACITORS

C601 OF55182570 FILM DTG 1800pF 100V OF55182570

C602 OF55331570 FILM DTG 330pF 100V OF55331570

C604 OF55121560 FILM DAMG 120pF 630V OF55121560

C605 nsp ELECT. 220µF 16V ARA

C606 nsp ELECT. 220µF 16V ARA

CERAFINE

CERAFINE

OA22701650

OA22701650

C609 OF55122570 FILM DTG 1200pF 100V OF55122570

C610 OF55561570 FILM DTG 560pF 100V OF55561570

C612 OF55681570 FILM DTG 680pF 100V OF55681570

C613 nsp ELECT. 220µF 16V ARA

C614 nsp ELECT. 220µF 16V ARA

CERAFINE

CERAFINE

OA22701650

OA22701650

C616 nsp ELECT. 100µF 25V ARS OA10702540

C651 OF55182570 FILM DTG 1800pF 100V OF55182570

C652 OF55331570 FILM DTG 330pF 100V OF55331570

C654 OF55121560 FILM DAMG 120pF 630V OF55121560

C659 OF55122570 FILM DTG 1200pF 100V OF55122570

C660 OF55561570 FILM DTG 560pF 100V OF55561570

C662 OF55681570 FILM DTG 680pF 100V OF55681570

C666 nsp ELECT. 100µF 25V ARS OA10702540

C801 OA68801620 ELECT. 6800µF 16V ± 20% RA-2 OA68801620

C802 nsp ELECT. 3300µF M 6.3V RA-2 OA33800620

C804 nsp ELECT. 3300µF 16V RA2 TYPE OA33801620

C805 nsp ELECT. 6800 µF 16V RA2 OA68801620

C806 nsp ELECT. 3300µF M 6.3V RA-2 OA33800620

C809 nsp ELECT. 1000µF 10V M RA-2 OA10801020

C821 OA47802520 ELECT. 4700µF 25V RA-2 OA47802520

C822 nsp ELECT. 2200µF 16V OA22801620

C823 nsp ELECT. 2200µF 16V OA22801620

C851 OB33802510 ELECT. 3300µF 25V ±20%

C852 OB33802510 ELECT. 3300µF 25V ±20%

FOR HIFI

FOR HIFI

OB33802510

OB33802510

C855 nsp ELECT. 10µF 25V ARA OA10602550

C856 nsp ELECT. 10µF 25V ARA OA10602550

C857 nsp ELECT. 470 µF M 16V ARA OA47701650

C858 nsp ELECT. 470 µF M 16V ARA OA47701650

CD21 nsp ELECT. 10 µF 63V RA-2 OA10606320

CD22 nsp ELECT. 100 µF M 10V RA-2 OA10701020

CD26 nsp ELECT. 220 µF M 25V RA-2 OA22702520

CD61 nsp ELECT. 100 µF M 25V RA-2 OA10702520

CD64 nsp ELECT. 100 µF M 25V RA-2 OA10702520

CD65 nsp ELECT. 10µF 25V ARA OA10602550

CD67 nsp ELECT. 100µF 10V ARA OA10701050

CF54 nsp ELECT. 10 µF 63V RA-2 OA10606320

CN01 nsp ELECT. 1000 µF M 25V RA-2 OA10802520

CN02 nsp ELECT. 1 µF M100V RA-2 OA10510020

CN03 nsp ELECT. 4.7 µF M 50V RA-2 OA47505020

CN04 DF15104350 FILM 0.1µF J N 50V DF15104350

CT05 nsp ELECT. 100µF 25V ARS OA10702540

CY51 OA22705020 ELECT. 220 µF M 50V RA-2 OA22705020

CY52 OA22705020 ELECT. 220 µF M 50V RA-2 OA22705020

CY63 nsp ELECT. 100 µF M 50V RA-2 OA10705020

PP16-RESISTORS