Marantz SA-7S1 Service Manual

Service

SA-7S1

SA-7S1 /

F N/K1G/N1G/U1G

Manual

SECTION 1 PAGE

1. TECHNICAL SPEC I FI CA TIONS AND UPDATE DISC .......................................................1-1

2. SERVICE HINTS AND TOOLS .......................................................................................... 1-2

3. WARNING AND LASER SAFETY IN STRUC TIONS ......................................................... 1-3

4. TAKING THE DISC OUT OF EMERGENCY .................................................................... 1-4

5. UPDATA FIRMWARE ......................................................................................................... 1-5

6. SERVICE MODE ...............................................................................................................1-6

7. L/R OUTPUT LEVEL ADJUSTMENT PROCEDURE .........................................................1-7

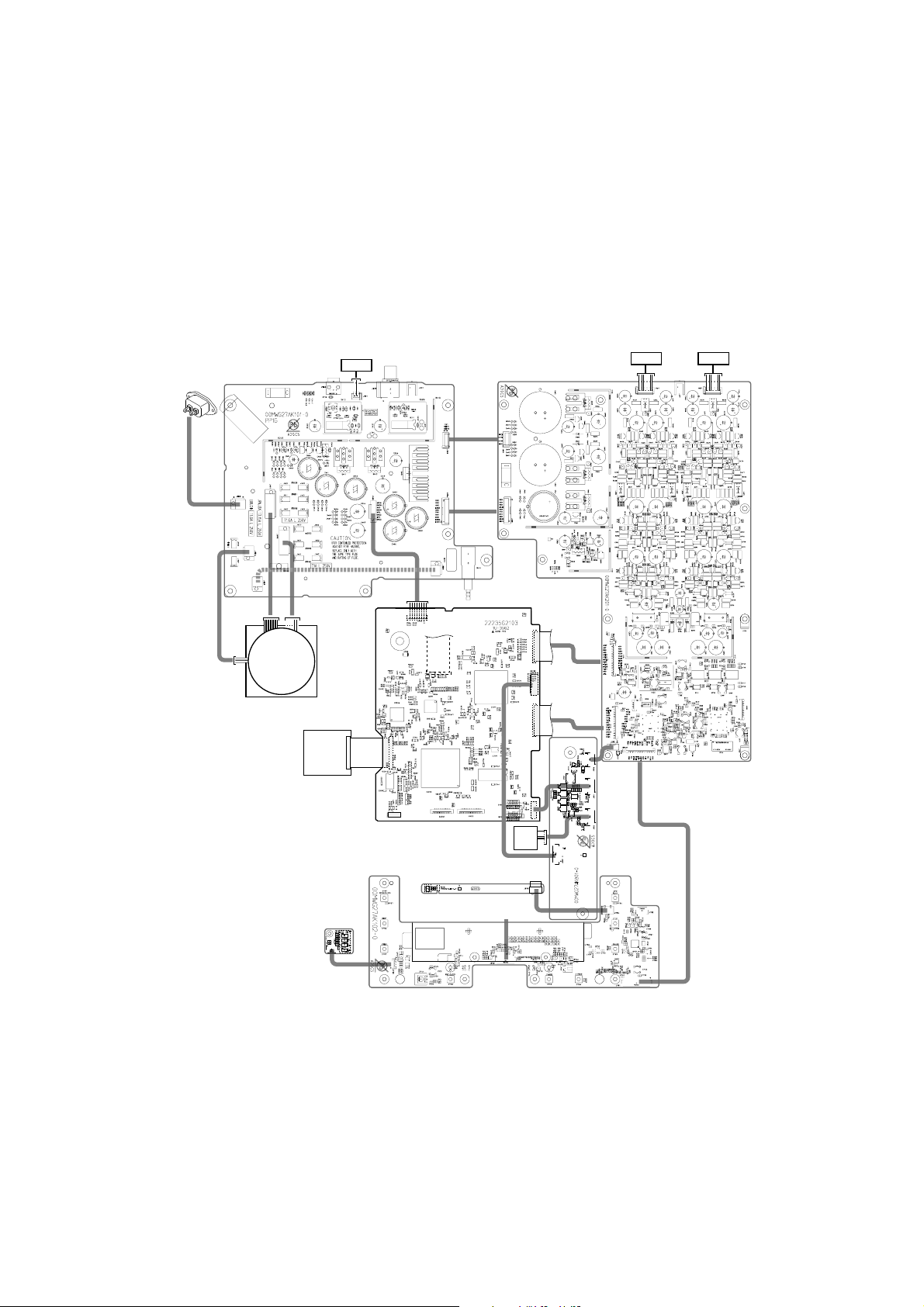

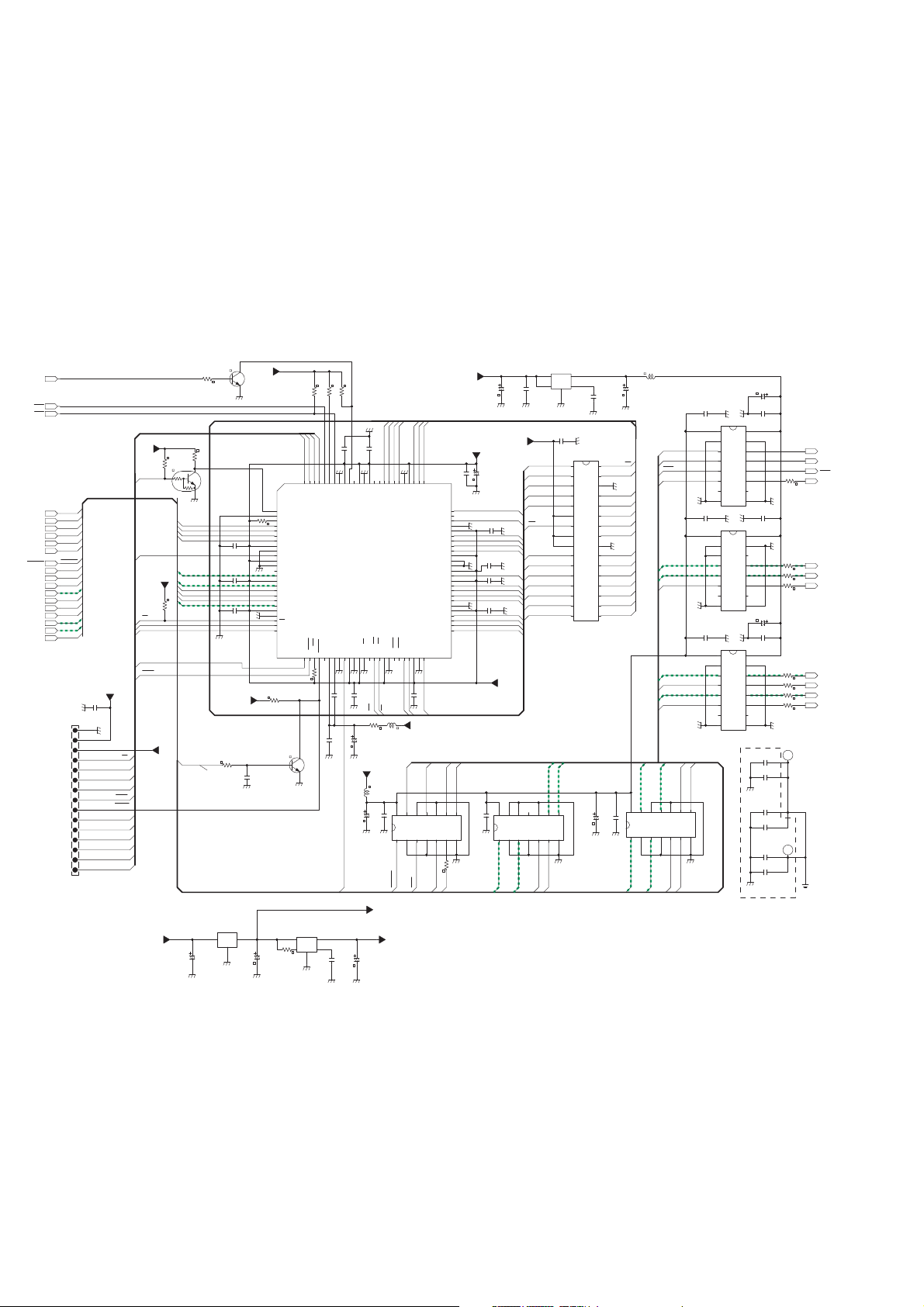

8. WIRING DIAGRAM ............................................................................................................ 1-9

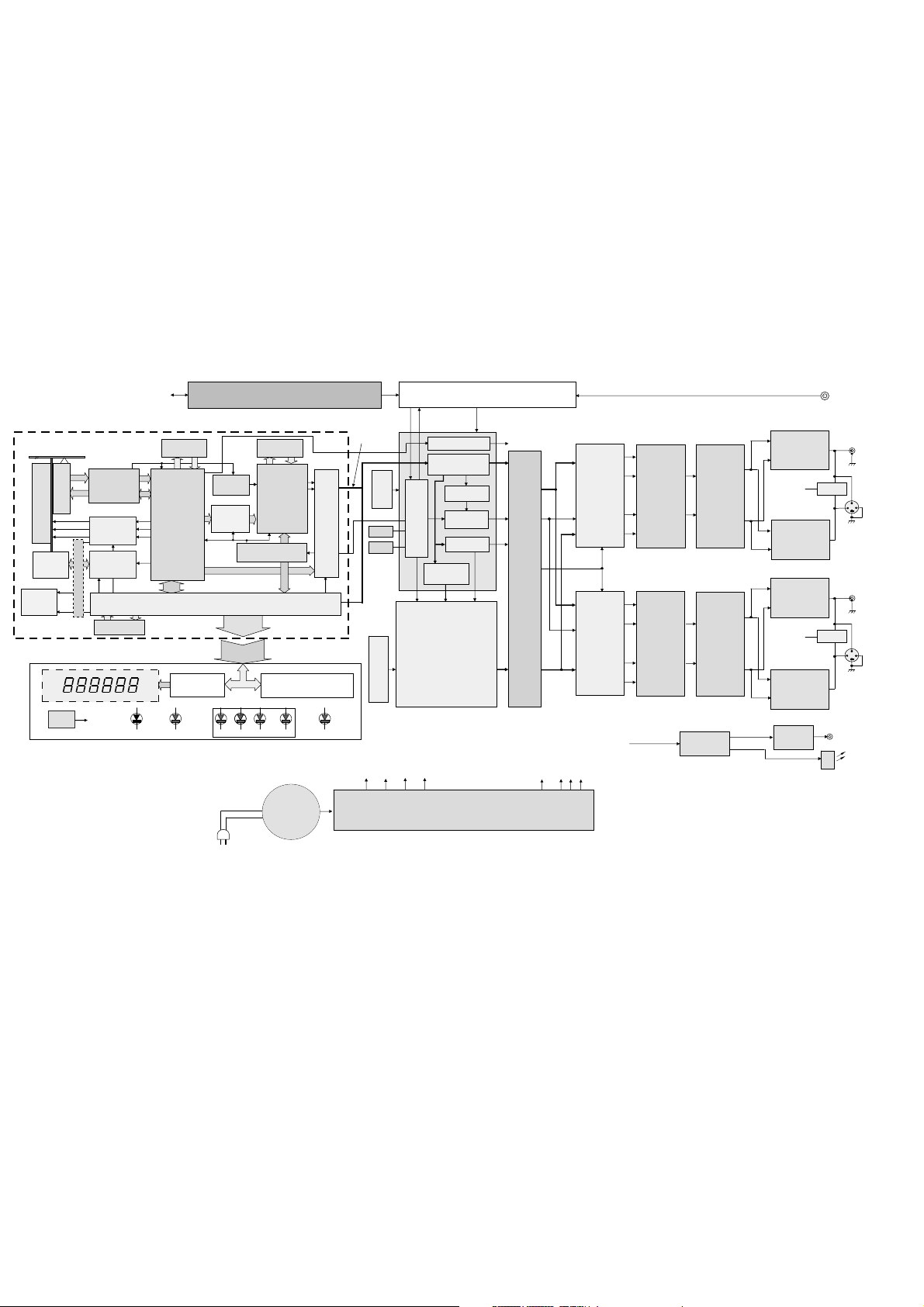

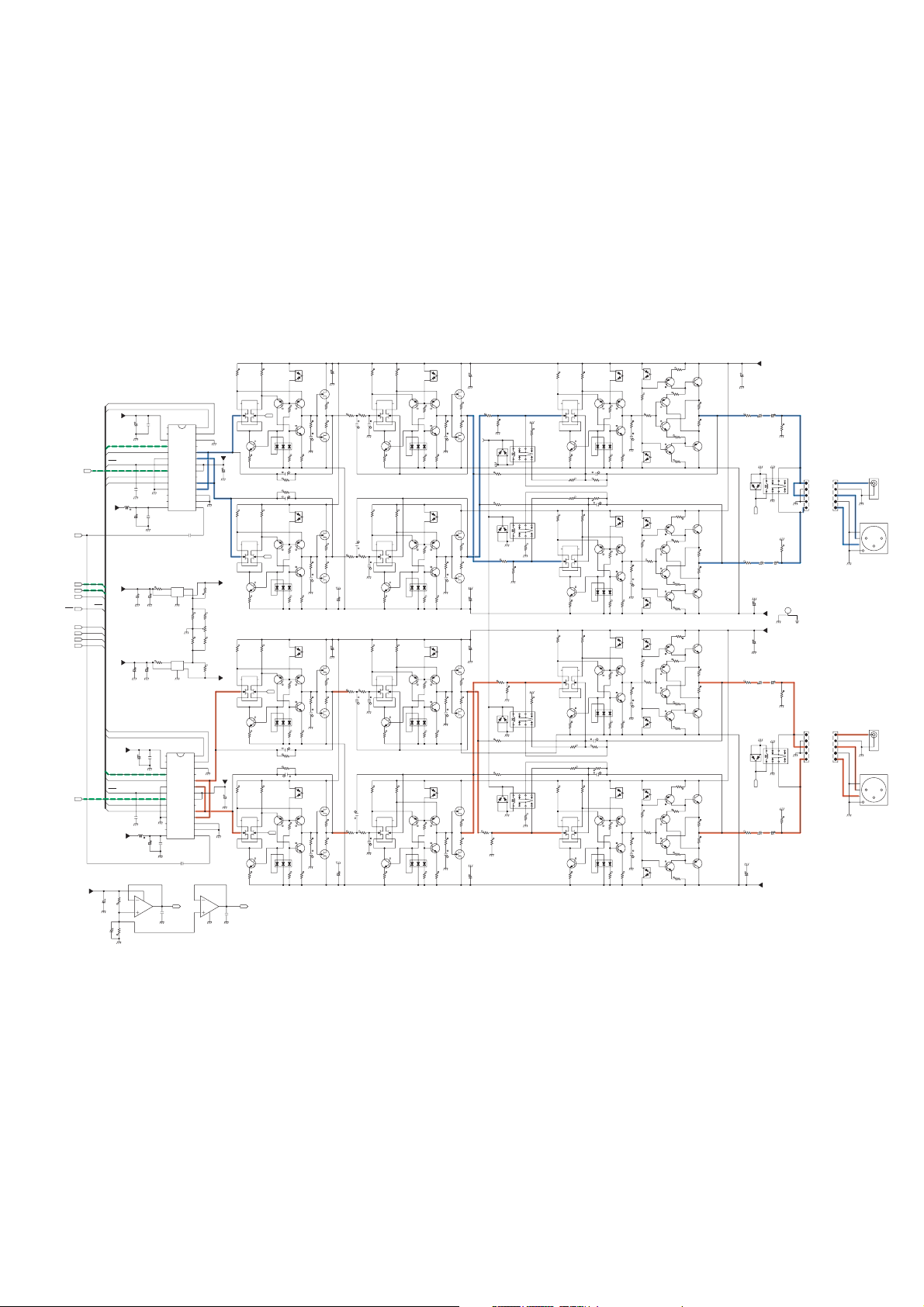

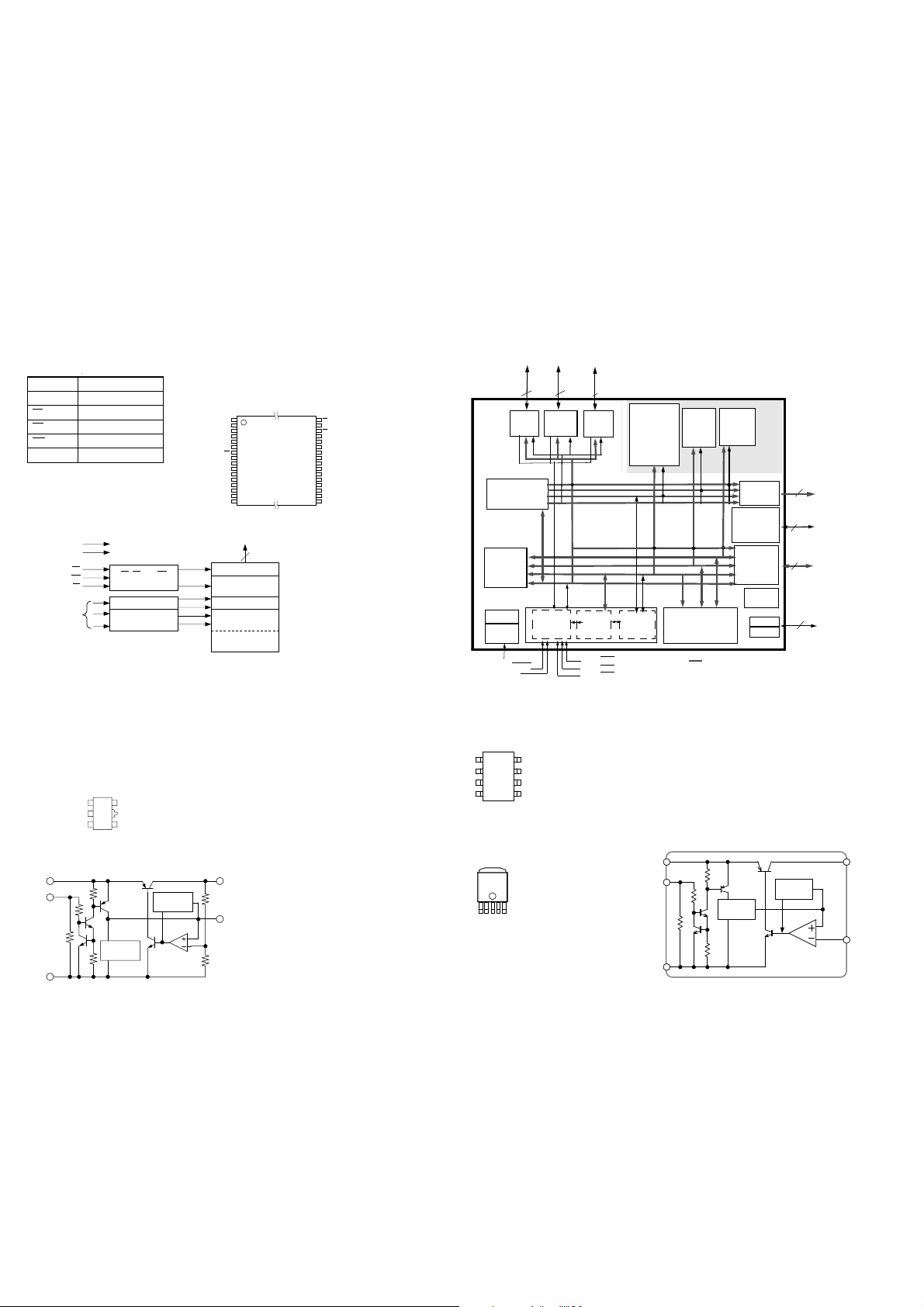

9. BLOCK DIAGRAM ............................................................................................................1-11

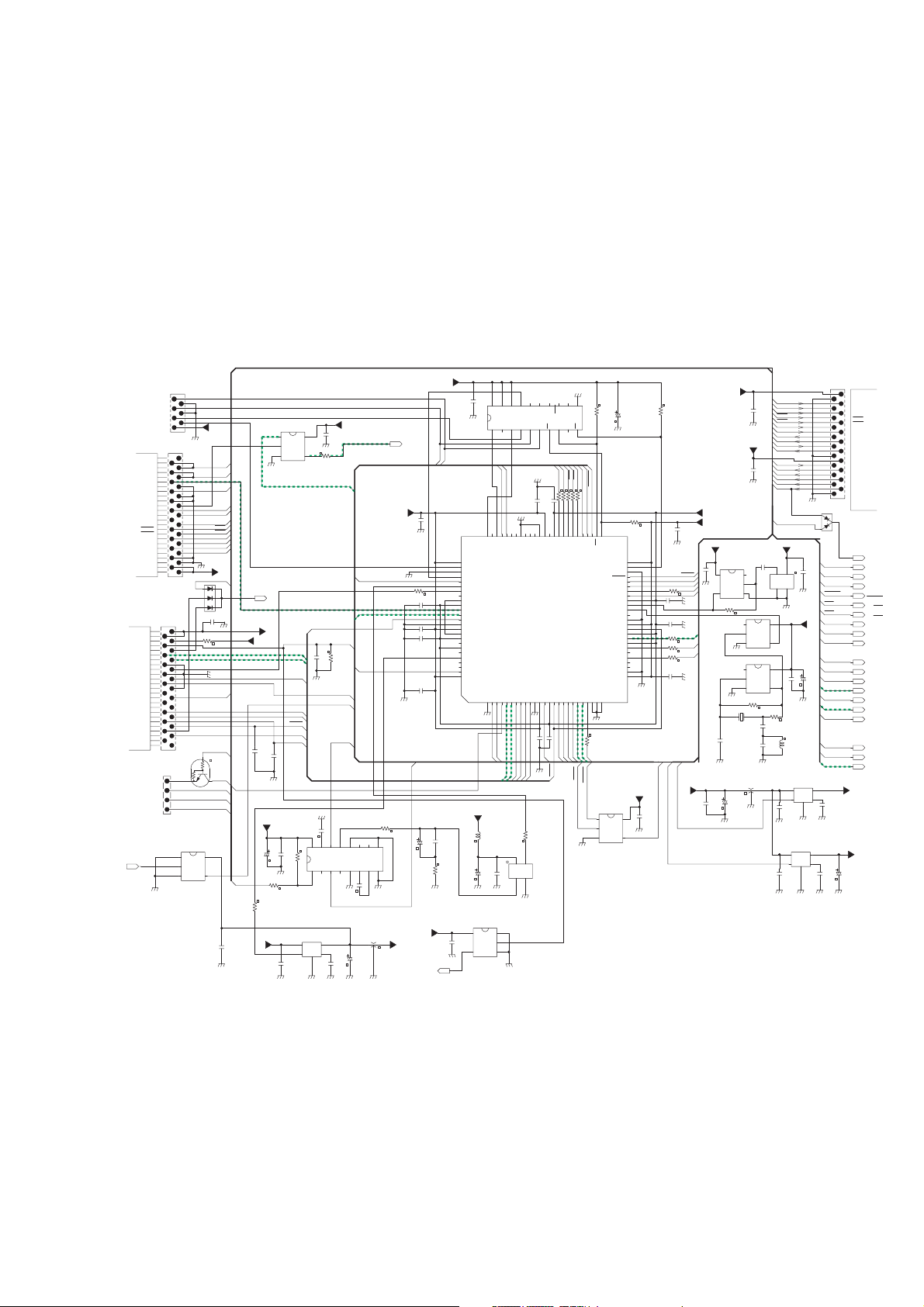

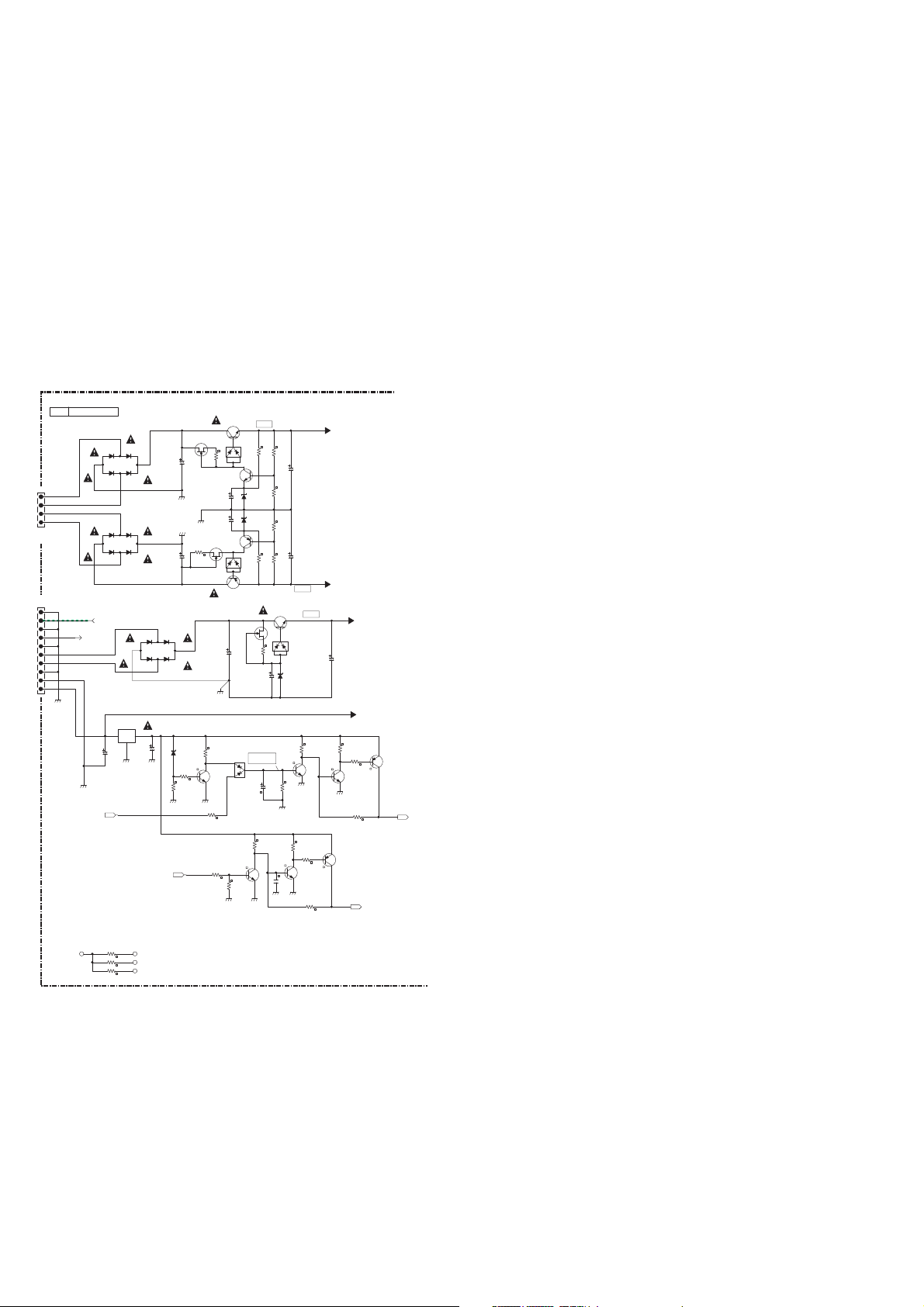

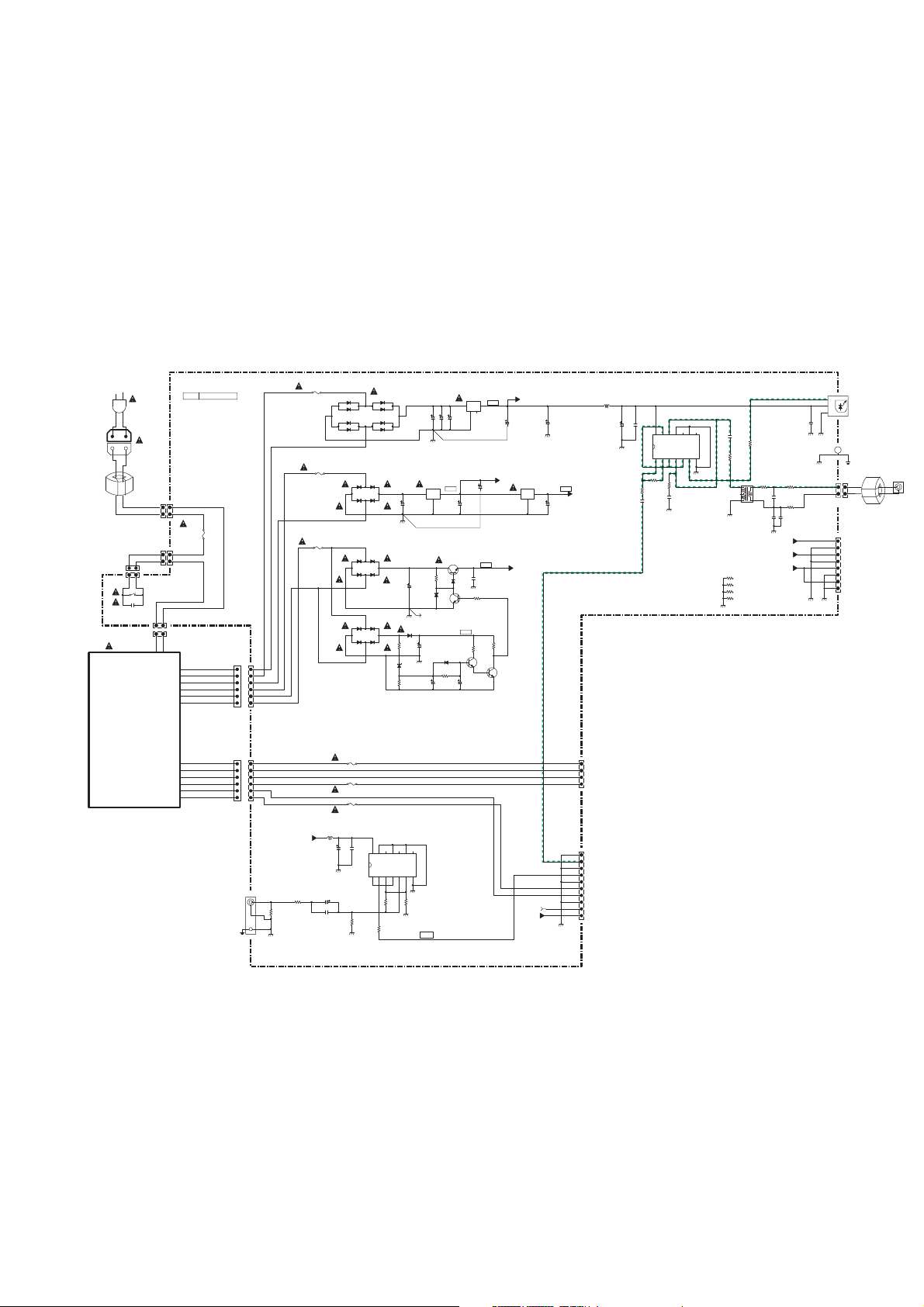

10. SCHEMATIC DIAGRAM ................................................................................................... 1-13

11. PARTS LOCATION .......................................................................................................... 1-25

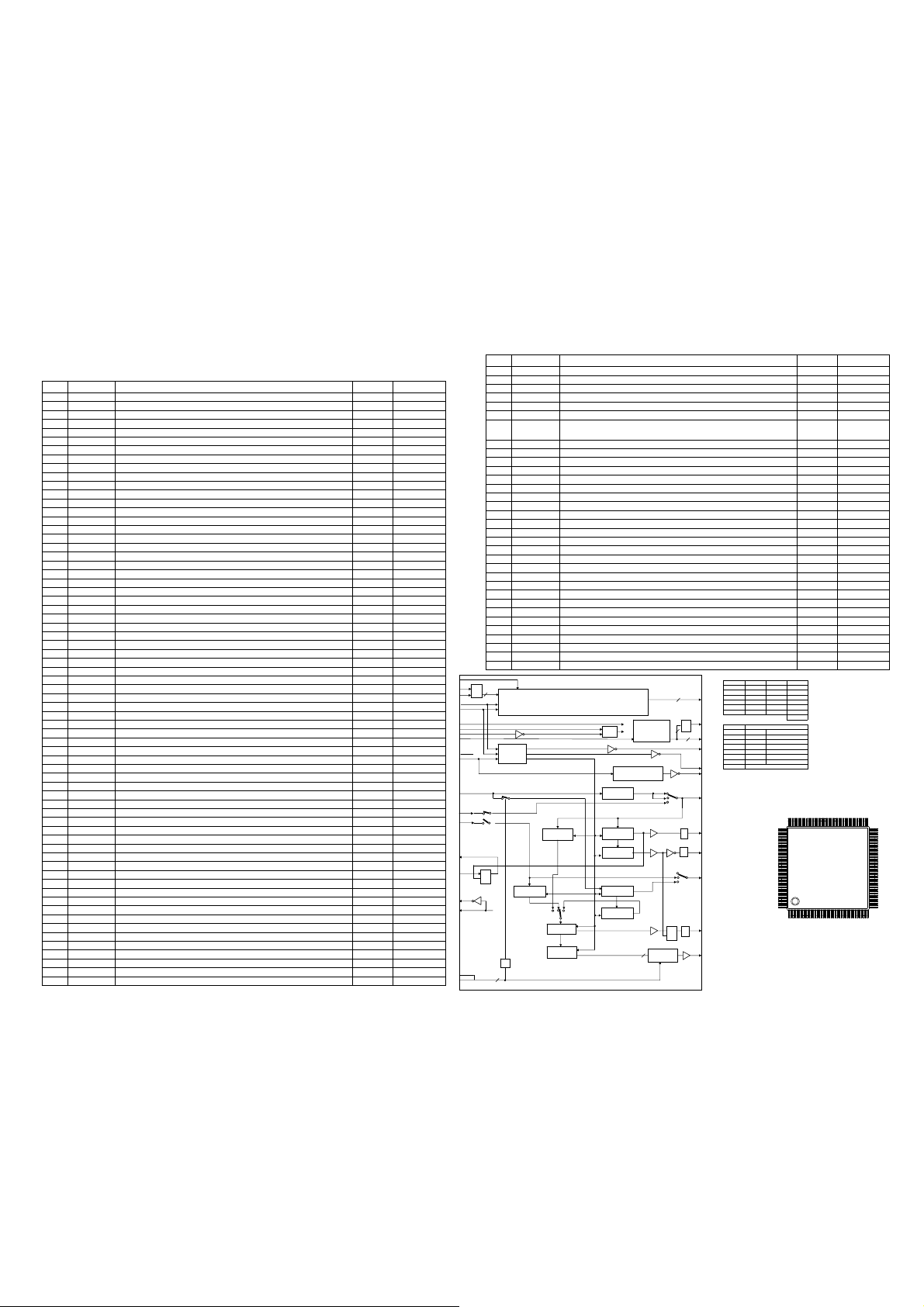

12. MICROPROCESSOR AND IC DATA ............................................................................... 1-33

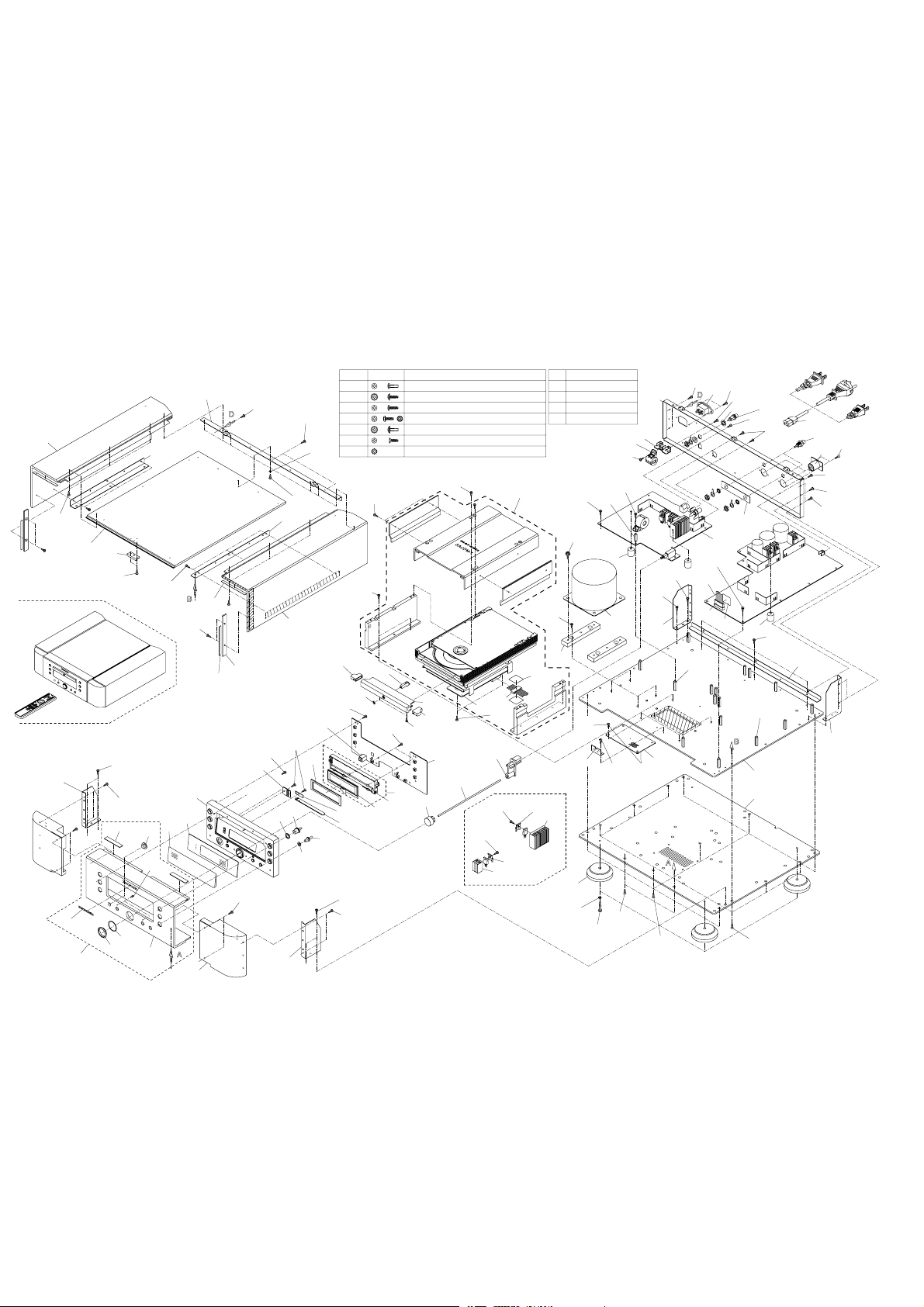

13. EXPLODED VIEW AND PARTS LIST ............................................................................. 1-39

14. ELECTRICAL PARTS LIST .............................................................................................. 1-43

15. ABOUT REPLACE THE MICROPROCESSOR WITH A NEW ONE ............................... 1-58

TABLE OF CONTENTS

Super Audio CD Player

SECTION 2 (MECHA LOADER AND MECHA TRAVERSE)

1. EXPLODED VIEW AND PARTS LIST ............................................................................... 2-2

SECTION 3 (SUPER AUDIO CD PWB MODULE / TRAY DRIVE PWB)

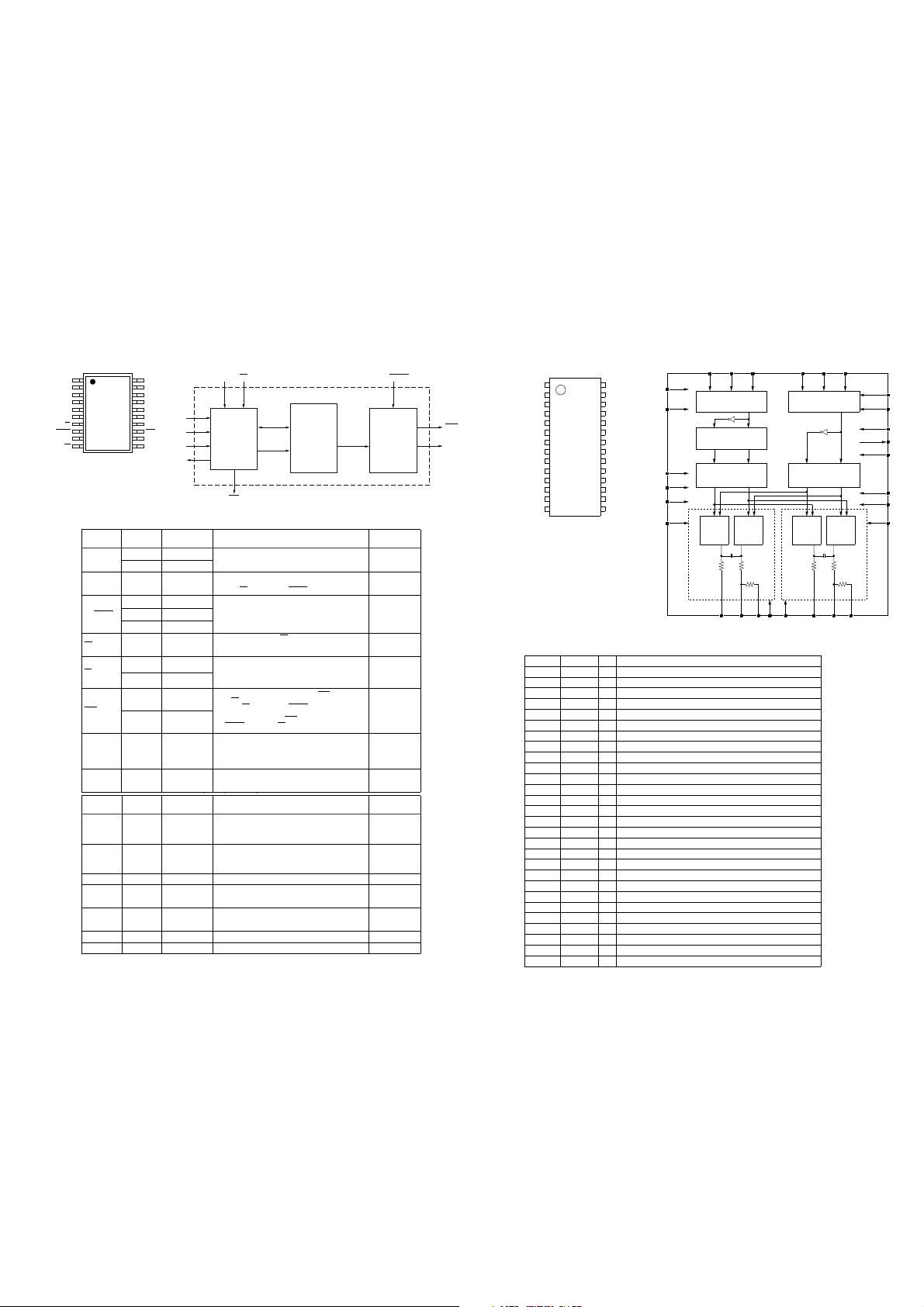

1. IC DATA .............................................................................................................................. 3-2

2. BLOCK DI A GRAM ........................................................................................................... 3 -23

3. SCHEMATIC DIAGRAM .................................................................................................. 3-24

4. PARTS LOCATION .......................................................................................................... 3-37

5. ELECTRICAL PARTS LIST .............................................................................................. 3-42

Please use this service manual with referring to the user guide ( D.F.U. ) without fail.

SA-7S1

Part no. 90M27AK855010

First Issue 2006.09

MZ

MARANTZ DESIGN AND SERVICE

Using superior design and selected high grade components,

Only original

MARANTZ

parts can insure that your

MARANTZ

MARANTZ

product will continue to perform to the specifi cations for which

company has created the ultimate in stereo sound.

it is famous.

Parts for your

MARANTZ

ORDERING PARTS :

equipment are generally available to our National Marantz Subsidiary or Agent.

Parts can be ordered either by mail or by Fax.. In both cases, the correct part number has to be specifi ed.

The following information must be supplied to eliminate delays in processing your order :

1. Complete address

2. Complete part numbers and quantities required

3. Description of parts

4. Model number for which part is required

5. Way of shipment

6. Signature : any order form or Fax. must be signed, otherwise such part order will be considered as null and void.

USA

MARANTZ AMERICA, INC

100 CORPORATE DRIVE

MAHWAH, NEW JERSEY 07430

USA

AUSTRALIA

QualiFi Pty Ltd,

24 LIONEL ROAD,

MT. WAVERLEY VIC 3149

AUSTRALIA

PHONE : +61 - (0)3 - 9543 - 1522

FAX : +61 - (0)3 - 9543 - 3677

EUROPE / TRADING

MARANTZ EUROPE B.V.

P. O. BOX 8744, BUILDING SILVERPOINT

BEEMDSTRAAT 11, 5653 MA EINDHOVEN

THE NETHERLANDS

PHONE : +31 - 40 - 2507844

FAX : +31 - 40 - 2507860

THAILAND

MRZ STANDARD CO., LTD

746 - 754 MAHACHAI ROAD.,

WANGBURAPAPIROM, PHRANAKORN,

BANGKOK, 10200 THAILAND

PHONE : +66 - 2 - 222 9181

FAX : +66 - 2 - 224 6795

CANADA

MARANTZ CANADA INC.

5-505 APPLE CREEK BLVD.

MARKHAM, ONTARIO L3R 5B1

CANADA

PHONE : 905 - 415 - 9292

FAX : 905 - 475 - 4159

SINGAPORE

WO KEE HONG DISTRIBUTION PTE LTD

No.1 JALAN KILANG TIMOR

#08-03 PACIFIC TECH CENTRE

SINGAPORE 159303

PHONE : +65 6376 0338

FAX : +65 6376 0166

NEW ZEALAND

WILDASH AUDIO SYSTEMS NZ

14 MALVERN ROAD MT ALBERT

AUCKLAND NEW ZEALAND

PHONE : +64-9-8451958

FAX :+64-9-8463554

JAPAN

D&M Holdings Inc.

D&M BUILDING, 2-1 NISSHIN-CHO,

KAWASAKI-KU, KAWASAKI-SHI,

KANAGAWA, 210-8569 JAPAN

TAIWAN

PAI- YUING CO., LTD.

6 TH FL NO, 148 SUNG KIANG ROAD,

TAIPEI, 10429, TAIWAN R.O.C.

PHONE : +886 - 2 - 25221304

FAX : +886 - 2 - 25630415

MALAYSIA

WO KEE HONG ELECTRONICS SDN. BHD.

2ND FLOOR BANGUNAN INFINITE CENTRE

LOT 1, JALAN 13/6, 46200 PETALING JAYA

SELANGOR DARUL EHSAN, MALAYSIA

PHONE : +60 - 3 - 7954 8088

FAX :+60-3-79547088

KOREA

MARANTZ KOREA CO., LTD.

ROOM 604, ELECTRO OFFICE, 16-58,

HANGGANG-RO 3GA, YONGSAN-KU,

SEOUL, 140-013, KOREA

PHONE : +82 - 2 - 323 - 2155

FAX : +82 - 2 - 323 - 2154

CHINA

MARANTZ SHANGHAI TRADING LTD.

ROOM.506 SHANGHAI LIGHT INDUSTRY MANSION

1578 NANJING (WEST) ROAD SHANGHAI

CHINA

TEL : 021 - 6248 - 1064

FAX : 021 - 6248 - 3565

SHOCK, FIRE HAZARD SERVICE TEST :

CAUTION : After servicing this appliance and prior to returning to customer, measure the resistance between either primary AC

cord connector pins ( with unit NOT connected to AC mains and its Power switch ON ), and the face or Front Panel of product and

controls and chassis bottom.

Any resistance measurement less than 1 Megohms should cause unit to be repaired or corrected before AC power is applied, and

verifi ed before it is return to the user/customer.

Ref. UL Standard No. 6500.

In case of diffi culties, do not hesitate to contact the Technical

Department at above mentioned address.

060607MZ

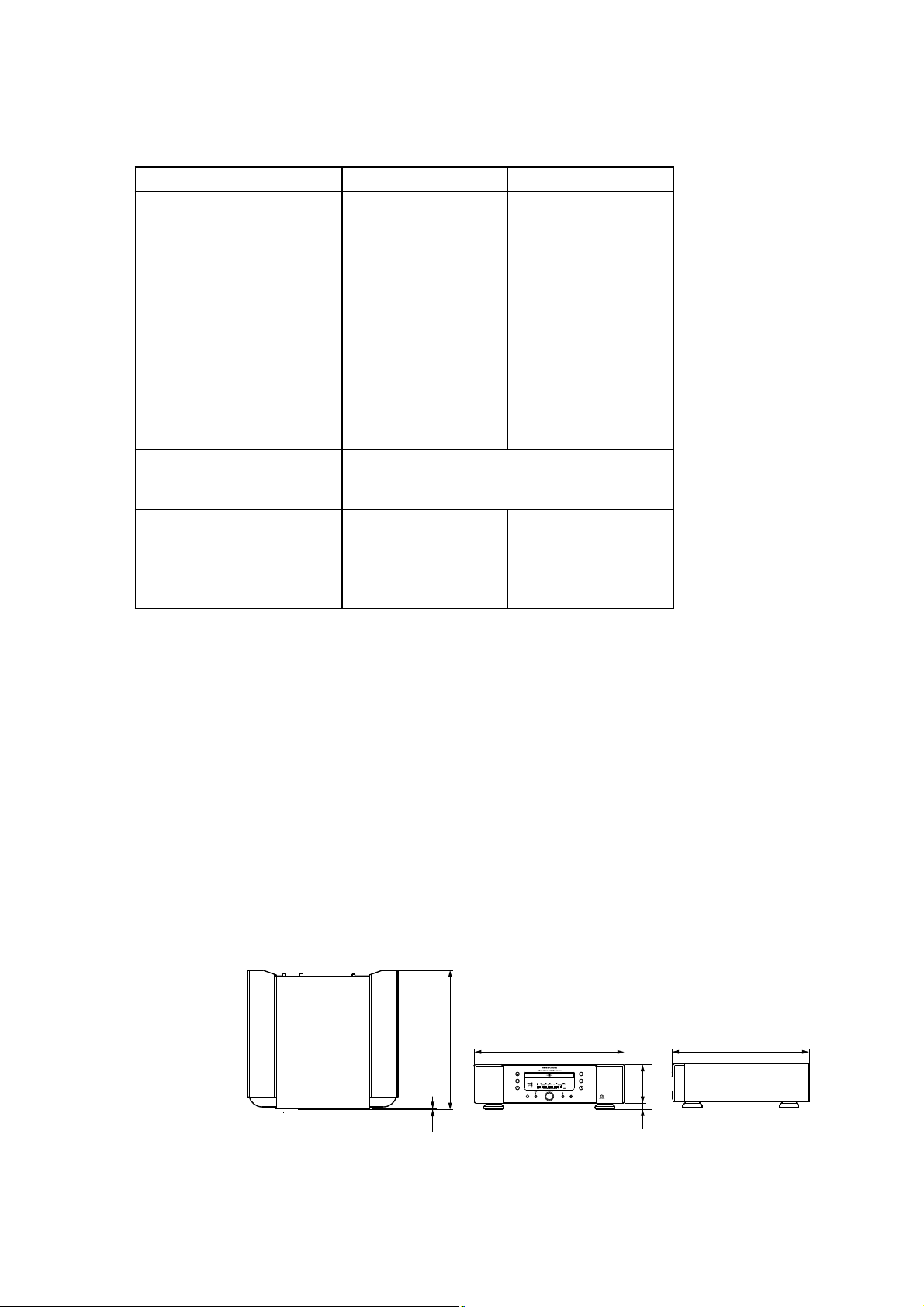

1. TECHNICAL SPECIFICATIONS AND UPDATE DISC

Super Audio CD CD

Audio Characteristics

Analog output

Channels 2channels 2channels

Frequency range 2Hz — 100kHz 2Hz — 20kHz

Frequency characteristics 2Hz — 50kHz (-3dB) 2Hz — 20kHz

Dynamic range 112dB 100dB

THD (1kHz) 0.0010% 0.0020%

Wow & Flutter Precision of quartz Precision of quartz

Output level 2.3V RMS stereo 2.3V RMS stereo

Digital output

Output level (Cinch JACK) — 0.5Vp-p (75Ω)

Output level (Optical) — -19dBm

Headphone output level 0.5W / 32Ω (max, Vol.) 0.5W / 32Ω (max, Vol.)

Ext. Clock input

Clock frequency

Input level (BNC terminal)

Optical Readout System

Laser AlGaAs AlGaAs

Wave length 650nm 780nm

Signal format 1-bit DSD 16-bit linear PCM

Sampling frequency 2.8224MHz 44.1kHz

44.1kHz, 88.2kHz, 176.4kHz

1V — 5Vp-p (75Ω)

Power Supply

Input Voltage, Frequency [/F] .................................................................... AC 100V 50/60Hz

[/K] .................................................................... AC 220V 50/60Hz

[/N] ......................................................................... AC 230V 50Hz

[/U] ......................................................................... AC 120V 60Hz

Power Consumption ....................................................................................................... 26W

Cabinet, etc.

Dimensions ................................... 459 × 136 × 425.5mm (18 1/8 × 5 5/16 × 16 13/16 inch)

Net weight ...................................................................................................................22.3kg

Operating temperatures .................................................................................. +5°C ~ +35°C

Operating humidity .............................................................................5 ~ 90% (without dew)

Accessories

• Remote control unit ...........................................................................................................1

• AAA (R03) Batteries ..........................................................................................................2

• AC Power cord ...................................................................................................................1

• Audio cable ........................................................................................................................1

• User’s Guide ......................................................................................................................1

Dimensions (Unit : mm)

425.5

459

425.5

118

3.5

UPDATE DISC

Update of the CPU (IC731) .......................................................................90M-SA11S1DVD

1-1

18

2. SERVICE HINTS AND TOOLS

SERVICE HINTS

SERVICE TOOLS

Audio signals disc 4822 397 30184

Disc without errors (SBC444)+

Disc with DO errors, black spots and fingerprints (SBC444A) 4822 397 30245

Disc (65 min 1kHz) without no pause 4822 397 30155

Max. diameter disc (58.0 mm) 4822 397 60141

Torx screwdrivers

Set (straight) 4822 395 50145

Set (square) 4822 395 50132

13th order filter 4822 395 30204

DVD test disc (PAL) 4822 397 10131

DVD test disc (NTSC) ALMEDIO TDV-540

1-2

3. WARNING AND LASER SAFETY INSTRUCTIONS

GB

WARNING

All ICs and many other semi-conductors are

susceptible to electrostatic discharges (ESD).

Careless handling during repair can reduce

life drastically.

When repairing, make sure that you are

connected with the same potential as the

mass of the set via a wrist wrap with

resistance.

Keep components and tools also at this

potential.

F

ATTENTION

D

WARNUNG

I

WAARSCHUWING

AVVERTIMENTO

NL

Alle IC’s en vele andere halfgeleiders zijn

gevoelig voor elektrostatische ontladingen

(ESD).

Onzorgvuldig behandelen tijdens reparatie

kan de levensduur drastisch doen

verminderen.

Zorg ervoor dat u tijdens reparatie via een

polsband met weerstand verbonden bent met

hetzelfde potentiaal als de massa van het

apparaat.

Houd componenten en hulpmiddelen ook op

ditzelfde potentiaal.

Tous les IC et beaucoup d’autres semiconducteurs sont sensibles aux décharges

statiques (ESD).

Leur longévité pourrait être considérablement

écourtée par le fait qu’aucune précaution

n’est prise a leur manipulation.

Lors de réparations, s’assurer de bien être

relié au même potentiel que la masse de

l’appareil et enfiler le bracelet serti d’une

résistance de sécurité.

Veiller a ce que les composants ainsi que les

outils que l’on utilise soient également a ce

potentiel.

GB

Safety regulations require that the set be restored to its original condition

and that parts which are identical with those specified be used.

NL

Veiligheidsbepalingen vereisen, dat het apparaat in zijn oorspronkelijke

toestand wordt terug gebracht en dat onderdelen, identiek aan de

gespecifieerde worden toegepast.

Alle IC und viele andere Halbleiter sind

empfindlich gegen elektrostatische

Entladungen (ESD).

Unsorgfältige Behandlung bei der Reparatur

kann die Lebensdauer drastisch vermindern.

Sorgen sie dafür, das Sie im Reparaturfall

über ein Pulsarmband mit Widerstand mit

dem Massepotential des Gerätes verbunden

sind.

Halten Sie Bauteile und Hilfsmittel ebenfalls

auf diesem Potential.

D

Bei jeder Reparatur sind die geltenden Sicherheitsvorschriften zu beachten.

Der Originalzustand des Gerats darf nicht verandert werden.

Fur Reparaturen sind Original-Ersatzteile zu verwenden.

I

Le norme di sicurezza esigono che l’apparecchio venga rimesso nelle

condizioni originali e che siano utilizzati pezzi di ricambiago idetici a quelli

specificati.

Tutti IC e parecchi semi-conduttori sono

sensibili alle scariche statiche (ESD).

La loro longevita potrebbe essere fortemente

ridatta in caso di non osservazione della piu

grande cauzione alla loro manipolazione.

Durante le riparazioni occorre quindi essere

collegato allo stesso potenziale che quello

della massa dell’apparecchio tramite un

braccialetto a resistenza.

Assicurarsi che i componenti e anche gli

utensili con quali si lavora siano anche a

questo potenziale.

F

“Pour votre sécurité, ces documents

doivent être utilisés par des

spécialistes agrées, seuls habilités à

réparer votre appareil en panne.”

Les normes de sécurité exigent que l’appareil soit remis a l’état d’origine et

que soient utilisées les pièces de rechange identiques à celles spécifiées.

LASER SAFETY

This unit employs a laser. Only a qualified service person should remove the cover or attempt to service this

device, due to possible eye injury.

USE OF CONTROLS OR ADJUSTMENTS OR PERFORMANCE OF PROCEDURE OTHER THAN THOSE

SPECIFIED HEREIN MAY RESULT IN HAZARDOUS RADIATION EXPOSURE.

AVOID DIRECT EXPOSURE TO BEAM

WARNING

The use of optical instruments with this product will increase eye hazard.

Repair handling should take place as much as possible with a disc loaded inside the player

WARNING LOCATION: INSIDE ON LASER COVERSHIELD

CAUTION VISIBLE AND INVISIBLE LASER RADIATION WHEN OPEN AVOID EXPOSURE TO BEAM

ADVARSEL SYNLIG OG USYNLIG LASERSTRÅLING VED ÅBNING UNDGÅ UDS

ADVARSEL SYNLIG OG USYNLIG LASERSTRÅLING NÅR DEKSEL Å PNES UNNGÅ EKSPONERING FOR STRÅLEN

VARNING SYNLIG OCH OSYNLIG LASERSTRÅLNING NÄR DENNA DEL ÄR ÖPPNAD BETRAKTA EJ STRÅLEN

VARO! AVATT AESSA OLET ALTTIINA NÄKYVÄLLE JA NÄKYMÄTTÖMÄLLE LASER SÄTEILYLLE. ÄLÄ KATSO SÄTEESEEN

VORSICHT SICHTBARE UND UNSICHTBARE LASERSTRAHLUNG WENN ABDECKUNG GEÖFFNET NICHT DEM STRAHL AUSSETSEN

DANGER VISIBLE AND INVISIBLE LASER RADIATION WHEN OPEN AVOID DIRECT EXPOSURE TO BEAM

ATTENTION RAYONNEMENT LASER VISIBLE ET INVISIBLE EN CAS D'OUVERTURE EXPOSITION DANGEREUSE AU FAISCEAU

1-3

Æ

TTELSE FOR STRÅLING

030804ecm

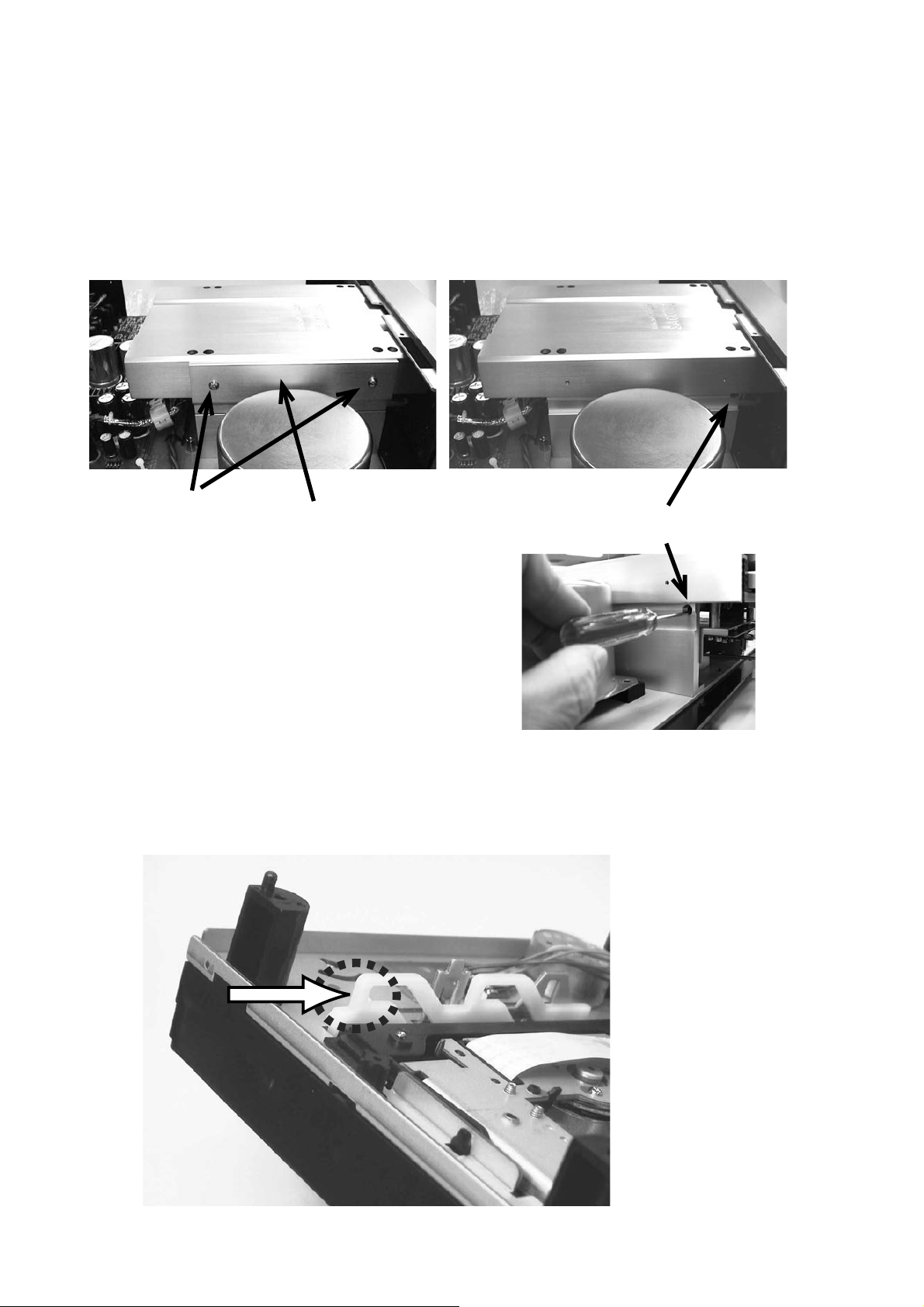

4. TAKING THE DISC OUT OF EMERGENCY

Push the Eject Lever, Disc tray is opened and Disc is taken

out.

1. Remove 2 screws and remove a side panel.

2. Push the eject lever by the pin (φ6mm or less).

3. The Disc tray opens, Now you can remove the disc

Remove 2 Screws

ネジ2本をはずします

Remove a side panel

サイドパネルを取り外します

Discの取り出しは、イジェクトレバーを押すとトレーが開きデ

ィスクを取り出せます。

1. ネジ2本を外しサイドパネルを取り外します。

2. ピン(直径6mm以下)でイジェクトレバーを押します。

3. ディスクトレーが開きディスクを取り出せます。

This hole is used

この穴にピンを差し込みます

This picture shows the unit upside down. The eject lever is

pointed by the arrow.

The lever is thin so aim the narrow area carefully.

この図はメカニズムの裏側です。矢印がイジェクトレバーで

す。

イジェクトレバーの押す部分の幅は狭いので、注意し押してく

ださい。

1-4

5. UPDATE FIRMWARE

ファームウエアのアップデート方法

Necessary Equipment

• UPDATE DISC. (90M-SA11S1DVD)

Attention : Don't turn off the unit until disc tray opens

automatically during the updating. When the

turn off the unit halfway, The unit can't be

operated any more.

Writing Procedure

1. Press the POWER button while pressing the PLAY and

STOP buttons.

2. Press the OPEN/CLOSE button to open the tray, Insert the

update DVD-ROM (part No.:90M-SA11S1DVD).

3. Press the SOUND MODE and STOP buttons.

The Display indicates " VERSION UP ".

4. Press the OPEN/CLOSE button to close the tray.

The Display indicates " TOC Reading " >>> " FILE CHECK

" >>> " ERASE " >>> " WRITING ".

5. Software updating will be done automatically.

When the updating is finished, The disc tray opens

automatically.

(Updating takes about 1 minute.)

6. Remove the DVD-ROM from the disc tray.

必要機器

• UPDATE DISC. (90M-SA11S1DVD)

注意 ) 書き換え中は、ディスクトレーが自動的にオープン

するまで絶対にセットの電源を切らないで下さい。

途中で電源を切ると通常の動作も出来なくなりま

す。

手順

1. PLAYとSTOPボタンを押しながらPOWERボタンを押しま

す。

2. OPEN/CLOSEボタンを押し、トレイをオープンします。

アップデート

入します。

3. SOUND MODEとSTOPボタンを同時に押します。

表示部には" VERSION UP "と表示されます。

4. OPEN/CLOSEボタンを押します。トレイが閉じます。

表示部には" TOC Reading " >>> " FILE CHECK " >>> "

ERASE " >>> " WRITING "

5.

ソフトの書き換えは自動的に行われます。書き換えが終了

するとディスクトレーは自動的にオープンします。

(アップデートには約1分かかります.)

6.

ディスクトレーからDVD-ROMを取り出します。

DVD-ROM (部品番号90M-SA11S1DVD)を挿

の順に表示されます。.

Update is completed, Press the POWER button to turn off the

unit.

以上で、ソフトウエアのアップデートは完了です。

タンを押し電源を切ります。

POWER ボ

1-5

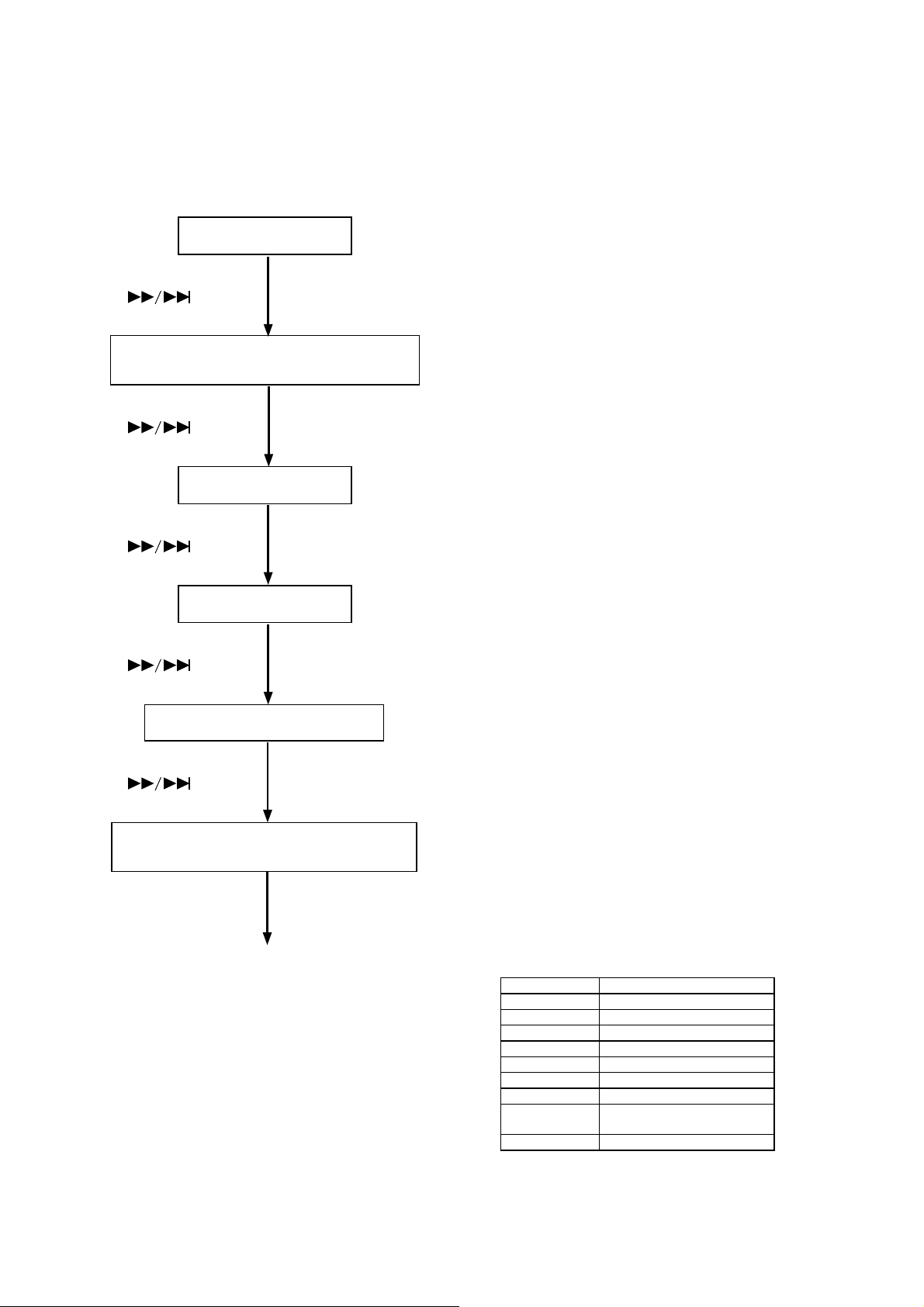

6. SERVICE MODE

The error code is indicated when a problem DISC is inserted first.

Press the POWER button While pressing PLAY and STOP button

Press<

Press<

Press<

Press<

"SA-11S1_1" is displayed

>

Version of Backend(IC731) μ-PRO is displayed

"B/E VXX.XX" is displayed

>

"DRV VXX.XX" is displayed

>

All area in the LCD light on

>

Each Segment is displayed one by one

Press<

When press the button, button name is displayed

Check of key

Press the POWER button to quit Service Mode

Errer Code

Error Code Error

E1 XXXX Operation time Error

E2 XXXX T.O.C Error

E2 XXXX Focus Error

E2 XXXX Read Error

E4 XXXX Tracking Error

E5 XXXX Tray Error

E6 XXXX Navigation Pack Read Error

E7 XXXX Check Sum Eroor and

NonAcknow I edgmen

NO DISC XXXX NO disc

(XXXX: The Operation number of times to the error

occurrence)

1-6

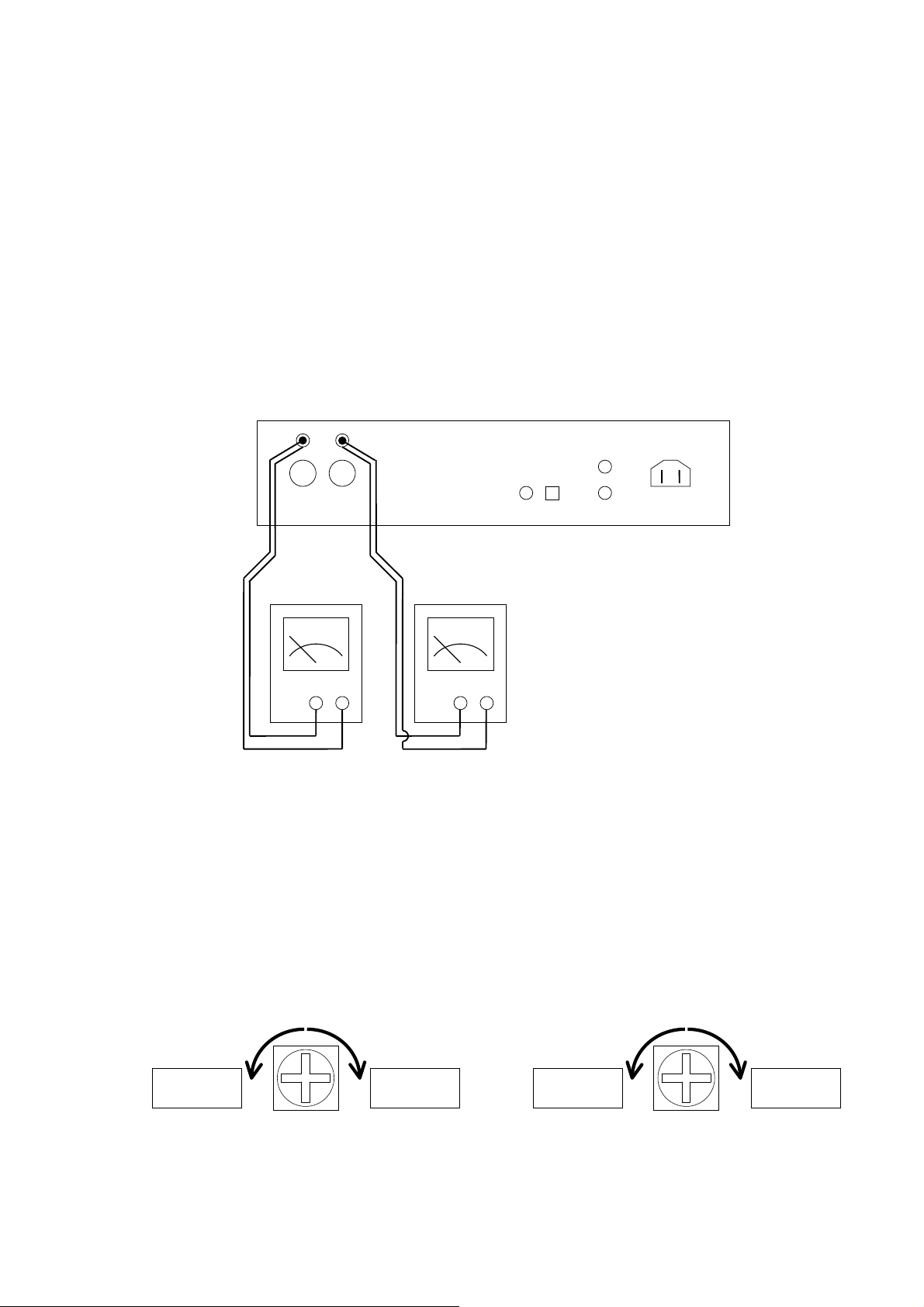

7. L/R OUTPUT LEVEL ADJUSTMENT

PROCEDURE

7. L/R出力レベル調整手順

Cases adjustment is needs

When a Q201 or Q251 is replaced.

Necessary equipments

• AC voltmeter 2 sets (or Oscilloscope)

• CD TEST DISC: CBC429 Audio signal disc1 (4822-397-

30155)

Connection procedure

• Connect the ANALOG OUTPUTS terminal (L/R) on the

rear panel and AC voltmeter with cable as follow.

RL

調整が必要な場合

Q201またはQ251を交換した時に調整が必要になります。

必要機器

• 交流電圧計 2台 (またはオシロスコープ)

• CD

テストディスク CBC429 Audio signal disc1 (4822-

397-30155)

接続図

• リアパネルにあるANALOG OUTPUTS端子L、Rをそれぞ

れ交流電圧計に接続します。

––

++

Adjustment procedure

1. Play back the Track 1 (1 kHz 0dB L+R) of the TEST DISC

(SBC429).

2. Adjust trimming resister (R205) according to AC

voltmeter readings of L ch output level and R ch output

level.

3. The output level difference of the L ch and R ch is

adjusted to less than 50mV.

If R205 is turned clockwise, the level of L ch will become

large, and if it turns to anticlockwise rotation, the level of

R ch will become large.

R ch: Larger

L ch: Smaller

R205

R ch: Smaller

L ch: Larger

調整方法

1. テストディスク(SBC429)のTr.1 (1kHz 0dB L+R)を再生し

ます。

2. 交流電圧計でL ch、R chの出力レベル差50mV未満になる

ように

R205で調整します。

R205を時計方向に回すとL chのレベルが大きくなり、反時

計方向に回すと

R chレベル大

L chレベル小

R chのレベルが大きくなります。

R chレベル小

L chレベル大

R205

1-7

Personal notes:

1-8

8. WIRING DIAGRAM

POWER

PP16 PWB

DIG OUT

COAX

AUDIO

PA16 PWB

OUTPUT

L

J401

OUTPUT

R

J451

PY36 PWB

J856

J806

CX052

Loading

Motor

CY251

CY252

CX131

JY09

PM16 PWB

TRAY

DRIVE

JM03

J101

J102

J105

JM04

JM01

JM02

J104

J1

J855

CY082

CX151

CX033

J804

JH06

Super Audio CD

MODULE UNIT

CX241

J80

JH01

J850

JH04

JH05

JH04

MAINSTRANSF

LH01

Spindle

Motor

J805

FRONT 3

FRONT 2

PY26 PWB

JY06

FRONT 1

PY16 PWB

JY05

TO LCD DISPLAY

JY02

JY08

JY12

JY01

1-9 1-10

9. BLOCK DIAGRAM

SA 7 Engine

TURNTABLE

PHOTO

Laser

control

CD and DVD

LASER and MONITOR

FOC, RAD, SLDG

3-AXICAL ACTUATOR

SPINDLE

hole Motor

LD +/

LOADING

Motor

FRONT UNIT BLOCK

OPN/CLS SW

IR sensor

PM16 TRAY DRIVE PWB

RC 5

CXD1881AR

RF AMP AGC EQ

LASER POWER

CONTROL

FAN8042

FOC RAD SLED

DRIVER

AN8471SA

SPINDLE DRIVER

IDT71V124SA12

SRAM(1M)

RC 5/KEY

LED Control

M11L1616SA 45

D RAM(16M)

RFAC

CXD1885Q

IC502

FOC

RAD

DIGITAL SERVO

SLED

and PLL,

DEMODURATOR

SPIN

FEATUR and LOADING for SERVO DSP

Display off

star

AD6062

RF AMP

FIFO

DATA BUS LINE

SUB MPU

EM636165TS 7

SDRAM(16M)

CXD2753R

PSP DECORD

DSD DECODER

CLK buffer

768fs

DIGO

and

IC736

DSD/CD

MODE

Additional MPU (RC-5 Detection and fs/porarity control)

DIGIO

EPM33128

PCM

M3062LFGPGP

DISPLAY

KEYS DATA

DISPLAY

KEYS

LCD DRIVER

44 1k 88 2k 176 4k

KEYS

PLAY/STOP/PAUSE/NEXT/PREVI/etc

Locked

INV phase

DATA SWITCH

DAPC

DACL

DALR

DARD

DSRST1

DSCK

DSDO

DSCS1

ATT

MUTE1

MODE

15V

CRISTAL

DIGO

TCXO

BACK LIGHT

FPGA ROM

768fs

DSP ROM

12V

EXCK Ref

frqu

and DIVIDER

MASTER CLK SW

384fs

Digital Fi ter

8fs FIR Filter with

3 Coeffecient, DC filter

N Shaper

8V

MOTOR

MOTOR

+5V

EXT c ock Seect and PLL VCXO

FPGA XC2S15

CD DIGITAL OUT

RE CLOCKING

DSD/CD

data switch

TIMING

GENERATOR

DAC CLK

Switch

CONTOROL

Polarity

INV

Fi ter

DAPC

ATT

O

N Shaper

DACLO

Mute

DALRO

PE777f2

(DSP56364)

DIGITAL

LRDA

DRDA

DLDA

CLDA

to DIGITAL I/O buffer

SPDIFO

DSD

SYSO

Digital interface

GMR iGiant Magnetoresistor

MUTE

DATA

EXT Fs

(BNC input)

+LA

+LA

DEM

+LB

LB

+RA

RA

DEM

+RB

RB

from FPGA XC2S15

SPDIFO

BESSEL FILTER STAGE

Double HDAM

I/V AMP

&

1th LPF

Double HDAM

I/V AMP

&

1th LPF

+L1

Double HDAM

L1

2th-LPF

+R1

Double HDAM

R1

2th-LPF

DIGITAL I/O

buffer

Differencial

HDAM

SA2-amp

+L2

control

L2

Differencial

HDAM

SA2-amp

Differencial

HDAM

SA2-amp

+R2

control

R2

Differencial

HDAM

SA2-amp

Puls

Transformer

Mutng relay

Mutng relay

COAX

OUT

GND

BALANCE

+BAL

3

OUT

2

1

BAL

GND

COAX

OUT

GND

BALANCE

+BAL

3

OUT

2

1

-BAL

GND

CAOX

D G TAL OUT

OPT

SM5866AS

DAC 23Multi Lebel

M0D

M1D

DAC +7.5V

+11.5V

DAC 23Multi Lebel

-11.5V

PCM

for Re ay

TROIDAL

TRANSFORMER

POWER SUPPLY and MUTING

1-121-11

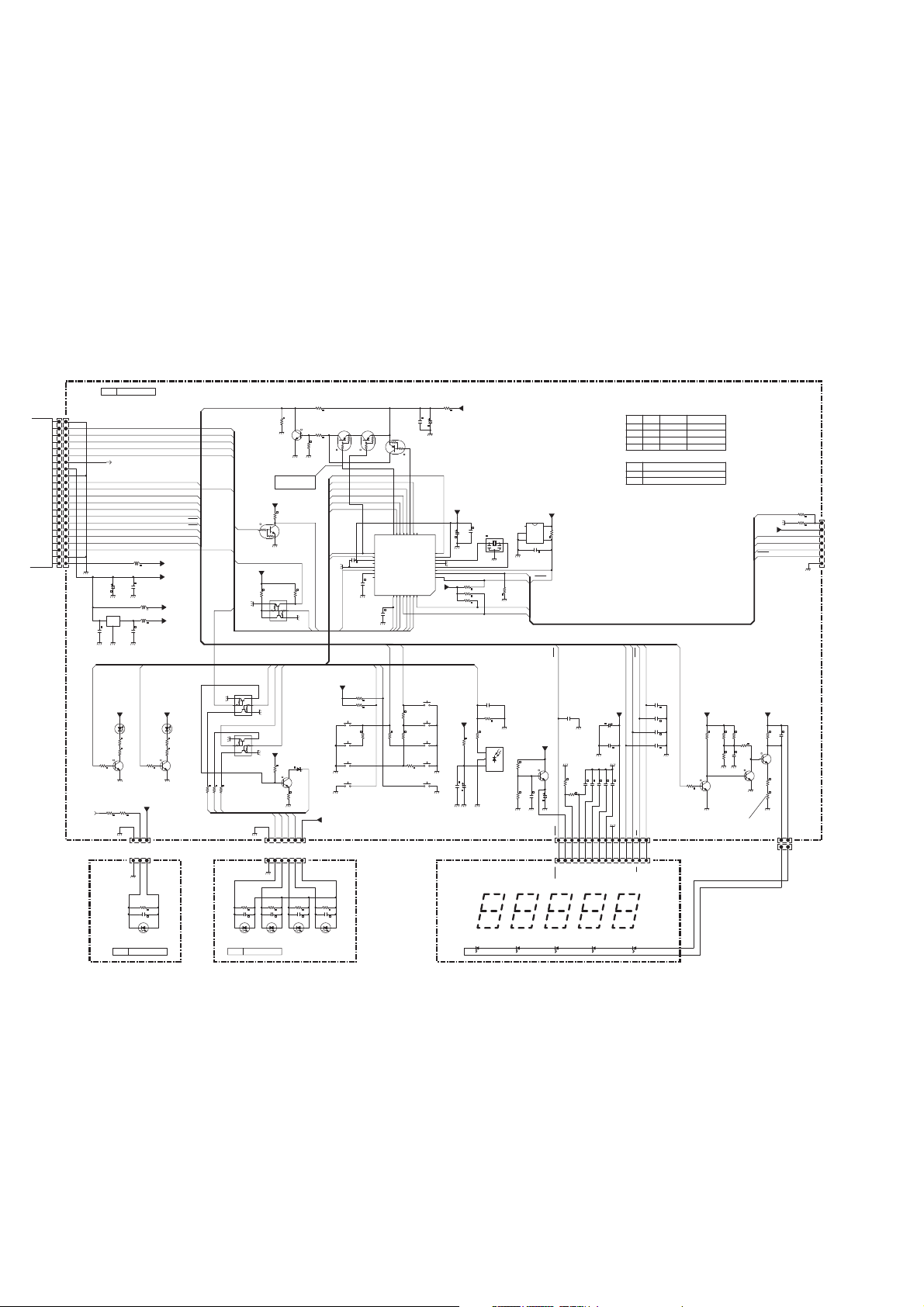

10. SCHEMATIC DIAGRAM

TO FROMT PWB (PY16)

WF04

+12V

+8V

+8V

MGN

MGN

DIGO

GND

IRIN

USER2

USER1

D OFF

SA F LAMP

SRLED

KEY2

DISP

FRES

FCEN

FCLK

FDAT

DSD DATA IN AND POWER OUT

KEY1

TO Super Audio CD MODULE UNIT

KEY0

GND

GND

+5A

+5A

WF05

+5B

+5B

F LTI

MODE

MUT1

DAPC

DARD

GND

SYCL

GND

DACL

ATT

GND

DSCS1

DISP2

DSALS

DSARS

DSDO

DSCK

TO Super Audio CD MODULE UNIT

DSD DATA N AND POWER OUT

DSRST1

DSCS3

MUT2

DALR

DSALF

DSAC

EXFS

FTCK

GND

FTMS

GND

FTDI

FTDO

VCC

D GND

10

12

14

16

18

20

22

24

TO PWB (PM16)

1

3

5

7

2

4

6

8

10

12

14

16

18

20

22

24

J102

25FMN

2

4

6

8

FROM DROWER

J105

7P FFC

J101

25FMN

DTC114EUA

1

2

3

4

J103

IMN10

1

3

5

7

9

1

3

5

7

9

21

23

25

Q113

2

4

6

D GND

1

3

5

7

9

11

13

15

17

19

21

23

25

D101

NC

NC

NC

NC

NC

Q130

TC7SH86FU

1

B

2

A

3

GND4Y

1

+33D

NC

D GND

654

C116

01u

R121

VCC

DATA INTERFACE

M+8V

MGN

RC 5

FLAMP

F RS

DISP

FRES

FCEN

FCLK

FDAT

KEY1

KEY0

+5VA

FSMUT

123

D GND

47k

D-GND

DSP2

FLAMP

CLOS

D INV

M+8V

MGN

SYSR

5

ERR

C130

01u

D GND

PA16 PWB -1/4

Q127

TC7SZ08FU

1

B

VCC

2

A

3

GND

Y

D GND

AMUT

+5VB

+33D

DAPC

DARD

DACL

D GND

DSDO

DSCK

DSCS3

DALR

DSRST1

C137

6800p

C158

nc

D GND

PL33V

C134

100u

1k

R127

+5VA PL33V

D GND

R132

47k

D GND

C132

C133

01u

R131

10k

12345678

Q128

PQ1U331M2ZP

1

VIN

VC NR

3

GND

01u

C126

D GND DGND D GND D GND

LFA(100)

+5VA

5

C125

01u

D GND

4

100

R113

SPDIF

DACL

MODE

R122

100k

C157

100p

ATT

FSI

FSIO

D GND

Q131

74HC4046

NC

D GND D GND D GND D GND

5

VOUT

4

2

C128

01u

C127

10u/16

FSX

SPDF

FTCK

C131

NC

910111213141516

L131

12

3

TO PA16 -4/4

R134

27k

+33D

01u

C117

D GND

DGO

FTCK

FTMS

+33D

C109

01u

D GND

76

33V

77

TDO

78

GND

79

TDI

D GND

R130

D GND

80

FSX

81

EXCLK

82

SYCL

68

83

NC

84

ECKO

85

01u

C110

C111

C112

C113

FSX

25V

86

DGI

87

DGO

88

BCLK

89

GND

90

01

33V

91

CKI

92

01

25V

93

NC

94

25V

95

NC

96

EXON

97

NC

98

NC

99

TCK

100

33V

01u

D GND DGND

PL33V

C136

C135

1u63V

NC

R135

47

C139

33u16

D GND

Q129

TC7SH86FU

+5VA

5

VCC

01u

C129

D GND

SATT

Q102

XCF01SV020C

18

19

VCC20VCC

VCC

NC13CLK4TD5TMS6TCK7CF8OE9NC210CE

1D02

FS

FSO

D GND

C108

01u

D GND

NCNCNC

NC

NC

NC

FS

GND

FSO

CCLK

DN_DO

Q101

XC2S15

GND

TMS

MODE

D_NV

DAPC

DAR

DALR

DSDO

DSCK

RESET3

FTMS

MODE

DARD

DAPC

CONT GND

01u

C138

1

B

2

A

3

D GND

GND

101112131415161718192021222324

01u

C101

D GND

DALR

DSCK

DSDO

DSRST

10

R138

X103

VCXO

6777376MHZ

43

Vdd OUT

12

D GND

123456789

L133

GND4Y

C107

GND

33VCX25V

D GND

11

33k

R109

GND12NC313CEO14NC415NC516NC617TDO

FL3

FL1CA0

FL2

MD0

DC F

N-SH

000000

00

100

R116

R117

R119

R120

R118

01u

DCF

25VNC33V

NSH

FLT3

FLT2

FLT1

DSCS3

CA0

CB0

SACLO

SYSR

SARO

01u

O

C102

SACLO

SARO

CX

SAL

SYSR

CB0

DSCS3

DSRST

D GND

MD1

MD0

SALO

384F

DACRES

DACRES

MDA

DSP_RST

384sM1GND

D GND

R102

100

51525354555657585960616263646566676869707172737475

NT

PROG

M0

25

Q112

TC7SH86FU

1

B

2

A

3

GND4Y

D GND

DSRST

CD IN

SACD IN

LATCH

DAPCO

DALRO

DACLO

M2(GND)

C155

100u/6

R108

47k

50

33V

49

DONE

48

GND

47

46

8Fs

45

192fs

44

SYO

43

XON

42

25V

41

40

39

NC

38

GND

37

33V

36

35

25V

34

33

25V

32

31

NC

30

29

NC

28

NC

27

26

33V

D GND

+33D

5

VCC

D GND

1-13 1-14

D GND

1SS301

43

C114

01u

12

D GND

SAV+

C122

33u/16

01u

D GND

Q110

5

1

VN

VOUT

VC NR

4

3

GND

2

01u

C154

D GNDD GND

Q109

5

VIN

VOUT

VC NR

4

GND

2

01u

C153

D GND DGND D GND

J104

WF07

1

+15V

2

MGN

3

ERR

4

F RS

5

DSP

6

FRES

7

FCEN

8

FCLK

9

FDAT

10

KEY1

11

KEY0

12

DSP2

13

RC 5

14

GND

15

+5VB

16

CLS

17

NVS

18

20

22

D102

3

1

IMD1

IMD0

DSPR

DACRES

DC F

N SH

FIL3

FIL2

FIL1

192F

8FS

SYSO

SALO

SACLO

SARO

384F

DALRO

DACLO

DAPCO

C151

01u

TO FRONT 1 PWB (PY16)

LCD CONTROL DATA OUT

A0

19

B0

SYSR

21

FSMUT

GND

2

DMUT

IMD1

IMD0

1

DSPR

DACRES

DC F

1

N SH

1

FIL3

1

FIL2

1

FIL1

1

192F

1

8FS

1

SYSO

(512/768)

1

SALO

1

SACLO

1

SARO

1

1

1

1

1

SAV+

01u

C148

CDV+

C152

33u16

384F

DALRO

DACLO

DAPCO

TO PA16 -2/4

TO PA16 -2/4

+33D

330

R107

+33D

01u

D GND

DSRST

8FS

192F

R114

SYSO

100

C105

01u

C104

01u

R105

33

DAPCO

R104

33

DALRO

R103

33

DACLO

01u

C103

SX

CX

DSPR

C150

01u

F15V

+25V

+33D

C106

CDV+ CDV+

C115

01u

Q105

TC7SGU04FE

D GND

45

SX

D GND

18k

R106

Q104

D-GND

TC7SGU04FE

D GND

Q103

TC7SGU04FE

D GND

D GND

X101

677376MHz

C120

3p

D GND D GND

+5VB

C140

01u

C149

10u16

D GND

ERR

F RS

DSP

01u01u

C124C123

FRES

FCEN

FCLK

D GND

FDAT

KEY1

KEY0

DSP2

+5VB

RC 5

CLOS

D INV

CA0

CB0

SYSR

D GND

FSMUT

ATT

X102

DSB321SD

123

C144

VddOUT

10p

CONTGND

D GND

123

45

123

45

C121

R112

1M

R111

560

C118

680p

L101

C119

22uH

6p

L103

PQ1U331M2ZP

0022u

12

3

D GND

D GND

PQ1U331M2ZP

1

3

D GND

FROM PA16 -1/4

DACRES

DALRO

DACLO

DAPCO

SALO

SARO

SACLO

DMUT

DSPR

SYSO

PA16 PWB -2/4

N SH

DC F

F L3

F L2

F L1

384F

192F

8FS

DACRES

DALRO

DACLO

DAPCO

IMD0

IMD1

SACLO

15

14

13

12

11

10

TEST PINS FOR JTAG and EEROM

Q117

2SC4116

(GR BL)

R157

DMUT

+3 3D

R161

22k

MODDI

Q115

DTC124EUA

FIL3

FIL2

FIL1

384F

192F

8FS

DSPR

IMD0

IMD1

SYSO

SALO

SARO

FROM INTERFACE CIRCUIT

C177

0 1u

D-GND

9

8

7

6

5

4

3

2

1

J106

15FMN

HCKT

R156

22k

SS

MOSI

MISO

SCK

HREQ

+3 3D

D-GND

MODDI

HREQ

MRST

+5VB

SS

MOSI

M SO

SCK

HCKT

TMS

TCK

TDI

TD

O

+5VB

22k

R162

22k

D GND

8FS

DALRO

192F A15

DACLO

DLDA

+3 3D

DRDA

FIL1

FIL2

FIL3

DAPCO

D GND

DSPR

Nomal=LoW

XC6203P332PR

231

C156

470u/16

D GND

D GND

+3 3D

D GND

1

MODD

2

MODB

3

R163

MODA

4

22k

8FS

5

DALRO

6

192F

7

DLCO

8

VCCS

9

GNDS

0 1u

C161

C163

Q106

10

HCKT/PC5

11

VCCLQ

12

GNDQ

13

C162

0 1u

R152

22k

OUT

GND

HCKR/PC2

14

D GND

DLDA

15

VCCHQ

16

DRDA

17

F L1

18

F L2

19

F L3

20

DAPCO

21

VCCS

22

GNDS

0 1u

23

D GND

SS HA2

24

MOSI HA0

25

MISO SDA

R153

22k

+3 3D

Q116

2SC4116

(GR BL)

C160

100p

D GND

C141

100u/6

D GND

22k

22k

R159

22k

R160

R158

ATT

D GND

0 1u

TD

TCK

TDO

TMS

100

TMS

SCK

26272829303132333435363738394041424344454647484950

D GND

Q107

NJM2880U25 TE1

5

VIN

VOUTN

CONT

1

NPAS

R150

GND

10k

D GND

C174

0 1u

C176

DEEM

D GND

D GND

99

GP O0

GP O1

GP O2

GP O3

TD

TD0

TCK

VCCS

VCCHQ

GNDS

NC

GNDQ

Q111

DSP56364

PEC 777f2

(Phase Error Compensation 777 filter)

NC

RESET

R154

D GND

D GND

VCCP

D GND D GND

22k

C164

C142

TA

PCAP

GNDP

GNDQ

EXTAL

VCCHQ

VCCQL

GND

0 1u

0 1u

C166

D GND

R155

0 1u

C165

C167

100u/6

D GND

+5VB

L180

C181

100u/6

D GND

384F

C143

22u/6

0 1u

D GND

HREQ

P N T/NM

4

3

2

D5

D7

D4

D6

D GND

VCCLQ

D4D5D6

D7

NC

NC

WR

RD

CAS

VCCC

GNDC

AA1 RAS1

AA0 RAS0

D GND

A0

RD

WR

L151

10

C182

0 1u

D GND

1234567

DACRES

+3 3D

+2 5V

D1

D2

D3

C173

0 1u

7677787980818283848586878889909192939495969798

D1D2D3

VCCQ

GNDQ

A0

MD1

A1

D GND

+3 3D

A1

D GND

75

D0

74

A17

73

A16

72

GNDA

71

VCCA

70

A15

69

A14

68

A13

67

A12

66

VCCLQ

65

GNDQ

64

GNDA

63

VCCA

62

A11

61

VCCQH

60

A10

59

A9

58

A8

57

A7

56

GNDA

55

VCCA

54

A6

53

A5

52

A4

51

A3

A2

VCCA

GNDA

C168

0 1u

A2

MX1

MX0

MD0

891011121314

D GND

R151

0

RST1

SYSO

SYCL1

+8V

A GND A GND A GND

+3 3D

C175

100u/

6

D GND

GND

0 1u

C172

0 1u

C171

D-GND

0 1u

C170

0 1u

C169

D GND

+3 3D

C183

0 1u

D GND

1234567

SARO

C196

47u/16

-GND

D-GND

D G D

Q180

PQU501M2ZP

5

1

VIN

VOUT

4

VC NR

3

GND

0 1u

C198

2

A GND

+3 3D

A11

A9

A8

A13

A14

D0

A16

WR

A14

A13

A12

A16

A15

A12

A11

A7

A9

A8

A6

A7

A5

D GND

A4

A6

A5

A4

A3

Q182Q181

TC74VHC86FTTC74VHC86FT

SAR1

SACLO

D-GND

C178

0 1u

12345678910111213141516

Q114

AT49BV001ANT-55T

SAL1

SALO

C185

33u/16

891011121314

D GND

D GND

SACL1

22u6

C195

0 1u

C197

A GND

RD

A10

D-GND

D7

D6

D5

D4

D3

D-GND

D2

D1

D0

A0A10

A1

A2

A3

17 18 19 20 21 22 23 24 2625 27 28 29 30 31 32

C184

0 1u

D GND

1234567

DRDA

DLDA

L181

DLDA1

Q183

TC74VHC86FT

DRDA1

IMX1

IMX0

RST1

SYCL1

SAL1

SAR1

SACL1

DLDA1

192F1

DRDA1

8FS1

C189

22u/6

C188C186

0 1u0 1u

D-GND

A GND

12345678

IM1X2

Q184

L715

D GND

C190

0 1u

C192

0 1u

D-GND D-GND

192F

192F1

891011121314

D GND

8FS

8FS1

9 10111213141516

D-GND

C191

A GND

0 1u

12345678

Q185Q186

L715L715

9 10111213141516

22u 6

C193

C194

0 1u

D-GND

A GND

12345678

R167

R168

R169

R170

9 10111213141516

Only U

C180

1000p

C179

0 1u

A GND

C147

1000p

C159

0 1u

C145

1000p

C146

0 1u

D GND

IM0X2

RST3

SYCL2

R171

33

A GND

A-GND

R164

33

SAL2

R165

SAR2

33

SACL2

R166

33

TO PA16 -3/4

TO DAC CIRCUIT

33

DLDA2

33

192F2

33

DRDA2

33

8FS2

TO PA16 -3/4

A-GND

J108

J109

EARTH

1-161-15

FROM PA16 -2/4FROM PA16 -2/4

FROM PA16 -2/4

SAL2

SAR2

DRDA2

SYCL2

SACL2

192F2

IM0X2

IM1X2

DLDA2

RST3

8FS2

PA16 PWB -3/4

DAC/FILTER/BALANCE

(LDA/LPF/LBA)

M0X2

M1X2

+5L

C203

100u10

AGND

SAL2

SACL2

RST3

192F2

8FS2

C209

1000p

AGND

L201

+5L

C205

100u10

SAL2

+8V

SAR2

SACL2

C201

470u/25

RST3

192F2

8FS2

IM0X2

IM1X2

+8V

C251

470u25

AGND A GND

M0X2

M1X2

+5R

C253

100u10

SAR2

SACL2

RST3

192F2

8FS2

C259

1000p

AGND

+5R

L251

Q292

2/2)

NJM3414AM(TE3)

+8V

6

R291

511K

C297

10u/35

5

A-GND

R292

226k

C294

10u/35

A-GND

C221

3

2SC3324 B

10

D227

3

2SC3324 B

D252

3

2SC3324 B

10

M

D277

3

2SC3324 B

Q214

2SA1312BL

Q215

R215

M

330p

681k

681k

330p

2SA1312BL

Q230

456

321

R231

R265

M

330p

681k

681k

330p

Q 79

2SA1312BL

Q280

456

321

R281

1

3

3

562

1

Q229

3

3

562

3

1

Q264

2SA1312BL

3

Q265

3

562

3

1

3

3

562

2

2SK170-V/TPE2

1

2

R218

100

2

1

C212

33p

A-GND

R217

562

2

2SK170-V/TPE2

1

2

R233

100

2

1

C227

33p

A-GND

R232

562

2

2SK170V TPE2

1

2

R268

100

2

1

C262

33p

A-GND

R267

562

2

2SK170-V/TPE2

1

2

R283

100

2

1

C277

33p

A-GND

R282

562

470u/25

R303

R304

D302

121

Q282

2

2

2

2

2

2

2

R285 R284 R270 R269 R235 R234

2

A-GND

R220 R219

1

3

470u/25

A-GND

2SJ74-V/TPE2

10 10 10 10 10 10 10 10

2SJ74-V/TPE2

2SJ74-V/TPE2

C222

C271

AGND

C272

121

Q301

2SK389FM-BL

1

8

NC

OPEN

2

7

D2

D

R301

R302

75k

91k

3

6

G2

G

45

S S

C301

C302

150p

330p

A-GND

2SJ74V TPE2

2SC2873(Y)

R305

681

R328

R329

121

121

Q326

2SK389FM-BL

8

1

OPEN

NC

C326

330p

2

7

R327

91k

3456

G1

G

R326

S

S

75k

C327

150p

A-GND

A-GND

470u/25

470u/25

R330

681

R354

R353

121

121

Q351

2SK389FM-BL

1

8

NC

OPEN

2

7

R351

R352

91k

75k

3

6

G2

G

45

S S

330p

150p

C351

C352

A-GND

R355

681

R379

R378

121

121

C376

Q376

330p

2SK389FM-BL

1

8

NC

OPEN

2

7

R377

R376

75k

91k

3456

GSSG1

150p

C377

A-GND

R380

681

Q216

Q217

Q231

Q232

Q267

Q268

Q281

1SS302TE85L

Q303

2SA1312BL

1

2

456

321

1SS302TE85L

Q328

2SA1312BL

1

2

1SS302TE85L

Q353

2SA1312BL

1

2

456

321

1SS302/TE85L

2SA1312BL

1

2

2

2SK170V TPE2

1

2

R309

100

2

1

C303

33p

A-GND

R308

562

2

Q331

2SK170-V/TPE2

1

2

R334

100

2

1

C328

33p

A-GND

R333

562

2

2SK170V TPE2

1

2

R359

100

2

1

C353

33p

A-GND

R358

562

2

2SK170V TPE2

1

2SA1312BL

2

R384

100

2

1

C378

33p

A-GND

R383

562

C321

470u25

Q306

A-GND

2

1010101010101010

R310R311R335R336R360R361R385R386

R401

226k

A D

R402

301k

R403

A-GND

1SS301TE85L

DN22

3

DGND

R404

681k

R429

681k

1SS301/TE85L

DN23

3

R451

226k

1SS301/TE85L

DN24

3

R454

681k

R479

681k

3

R477

301k

2

2

D-GND

R426

226k

2

D-GND

2

D-GND

1

234

1 234

R428

75K

R427

301k

A-GND

R452

301k

AGND

8 765

1 234

R478

75K

76 5

A-GND

A-GND

75K

LN22

UB2-12NUN

LN23

UB2-12NUN

AGND

R453

75K

LN24

UB2-12NUN

LN25

UB2-12NUN

ATT_RELAY

2

Q307

2

2SJ74-V/TPE

2

2

Q332

A- D

2

C322C371

470u/25470u25

2SJ74V TPE

Q356

A-GND

2

2

Q357

2

2SJ74-V/TPE

1SS301/TE85L

DN25

Q381

2

R476

226k

2

A-GND

Q382

A-GND

2

C372

2SJ74-V/TPE

470u/25

1

Q304

2SA1312BL

3

3

R306

332k

Q305

2SC3324 B)

3

D301

10

R307

562

D327

1

Q329

2SA1312BL

3

3

R331

332k

Q330

2SC3324 B

3

D326

N10

456

321

R332

562

3

D352

1

Q354

2SA1312BL

3

3

R356

332k

Q355

2SC3324 B

3

D351

IMN10

R357

562

D377

1

Q379

Q378

3

3

R381

332k

Q380

2SC3324 B

3

D376

10

456

321

R382

562

R407

121

2SK389FMBL

1

2

3

45

Q402

2SC2873(Y)

R406

R431

R432

121

2SK389FMBL

8

7

Q427

2SC2873 Y)

R434

681

R457

121

2SK389FMBL

1

2

3

45

Q452

2SC2873 Y

R456

R481

R482

121

2SK389FMBL

8

7

Q477

NC

D2

G

S S

OPEN

NC

D2

G

S S

OPEN

R408

D402

1SS302

121

Q403

2SA1312BL

Q401

1

81

OPENNC

3

7

D

2

R410

6

G

332k

SC3324(B)

D401

IMN10

456

321

R409

681

10p

C402

226k

91k

R405

R430

91k

226k

10p

C427

R433

D427

121

1SS302

Q428

2SA1312BL

Q426

1

1

NC

3

2

2

R435

3456

2SG

332k

SC3324

D426

10

R458

D452

121

1SS302

Q453

2SA1312BL

Q451

1

8

OPEN

3

7

D

2

R460

6

G

332k

SC3324(B)

D451

0

456

321

)

R459

681

C452

0p

91k

226k

R455

91k

R480

226k

10p

C477

R483

D477

121

1SS302

Q478

2SA1312BL

Q476

1

1

NC

3

2

2

R485

3456

2SG

332k

2 C3324 B)

R484

D476

681

MN10

R212

R211

121

121

D202

1SS302/TE85L

Q213

2SA1312BL

Q211

1

2SK389FM-BL

8

OPEN

2

7

D2

D

2

R214

3

6

G2

G

Q201

SM5866AS-G

1234567891011121314

01u

C204

TSTN

IMD1

TO

IMD0

DVDD

AVSSA

SDI

RA

A-GND

SBCKA

OUTA

SBCKD

RSTN

DI

BCKI

WCKI

DVSS

BCPOL

AGND

DSPOL

CVDD CKI

01u

C206

AGND

Q202

R201

NJM2887DL2

22k

CONT

1

VIN4VOUT

2

C202

470u/25

A-GNDAGNDA GND

Q252

R251

NJM2887DL2

22k

CONT

1

VIN4VOUT

2

C252

470u25

A-GND

SM5866AS-G

1234567891011121314

TSTN

C254

TO

01u

DVDD

AGND

SDI

SBCKA

SBCKD

RSTN

DI

BCKI

WCKI

DVSS

BCPOL

A-GND

DSPOL

CVDD CKI

C256

C255

01u

100u/10

AGND

8

7

C293

01u

+5L

IOUTAN

AVDDA

C208

AVDDB

100u10

RB

A-GND

OUTB

IOUTBN

AVSSB

CVSS

15 16 17 18 19 20 21 22 23 24 2625 27 28

A-GND

C210

100p

+5L

VADJ

5

R204

681k

3

GND

R202

332k

A-GND

R252

332k

5

3

GND

Q251

AVSSA

IOUTAN

AVDDA

AVDDB

IOUTBN

AVSSB

C260

100p

REF L

2SC2873(Y) 2SC2873(Y)

56k56k

R203R253

47k

R205

1

VAD

R254

681k

+5R

2SC2873(Y 2SC2873 (Y

IMD1

IMD0

RA

A-GND

+5R

OUTA

C258

00u10

RB

A-GND

OUTB

CVSS

15 16 17 18 19 20 21 22 23 24 2625 27 28

A-GND

2SC2873(Y) 2SC2873 (Y) 2SC2873 Y

(12)

Q292

NJM3414AM(TE3)

2

1

3

4

C296

01u

A-GND A-GNDAGND

332k

REF L

45

S S

D201

456

Q212 Q302

321

SC2873 Y)

R213

681

C211

R216

R229

C226

R227

R226

121

121

1SS302TE85L

Q228

2SA1312BL

Q226

1

2SK389FM-BL

1

8

NC

OPEN

2

7

2

R230

3456

GSSG1

332k

REF L

D226

MN10

Q227 Q327

R228

681

R262

R261

121

121

1SS302/TE85L

Q263

2SA1312BL

1

Q261

2SK389FM-BL

1

8

NC

OPEN

2

7

2

R264

3

6

G2

G

332k

45

REF R

S S

D251

456

Q262 Q352

321

R263

681

C26

R266

R279

C276

R277

R276

121

121

1SS302TE85L

Q278

2SA1312BL

Q276

1

2SK389FM-BL

1

8

NC

OPEN

2

7

2

R280

3456

G

G1

332k

REF R

SS

Q277 Q377

R278

D276

681

MN10

REF R

Q404

2SA1312BL

Q405

R411

2SA1312BL

Q430

456

R436

2SA1312BL

Q455

R461

562

SA1312BL

Q480

456

R486

2SA1312BL

D404

R417

Q409

2

2

1

2

1SS302

1

3

R413

100

3

C403

33p

A-GND

R412

562

562

2

1

1SS302

Q429

3

R438

100

(B)

3

33p

C428

A-GND

R437

562

562

2

1

1SS302

Q454

3

R463

3

C453

A-GND

R462

562

2

1

1SS302

Q479

3

R488

100

3

33p

C478

A-GND

R487

562

562

464

1

R414

464k464k464k464k

3

R416

100

3

Q412

2SC3324(B)

D403

1SS302

3

2

1

2SC3324(B)

2SA1312BL

D429

2

1

R439

3

R441

100

3

Q437

2SC3324(B)

D428

1SS302

3

2

1

2SC3324(B)

Q459

2SA1312BL

D454

2

1

R464R489

3

R466

100

3

Q462

2SC3324(B)

D453

33

1SS302

3

2

1

2SC3324(B)

Q484

2SA1312BL

D479

2

1

3

R491

100

Q487

2SC3324(B)

D478

1SS302

3

2

1

2SC3324(B)

Q414

2SC2705

1

1

R418

121

1010101010101010

Q410

2

R422R423R447R448R472R473R497R498

2SA1312BL

2

1

1

R420

121

Q415

2

3

2SA1145

2

1

R419

Q413

464

Q434

R442

2

1

464

Q439

2SC2705

1

1

R443

121

Q435

2

2SA1312BL

2

1

R445

1

121

Q440

2

3

2SA1145

2

1

R444

Q438

464

R467

2

1

464

Q464

2SC2705

1

1

R468

121

2

Q460

2SA1312BL

2

1

R470

121

1

Q465

3

2SA1145

2

1

Q463

R469

64

R492

2

1

464

Q489

2SC2705

1

1

R493

121

2

Q485

2SA1312BL

2

1

R495

121

1

Q490

3

2SA1145

2

1

464

Q488

R494

+11V

C421

470 25

A-GND

C405

220u16

R424

220u16

C406

464

R425

100k

A-GND

D D

A D

DN21

LN21

1SS301

UB2-12NUN

J401

6 5

B5B-EHTS

1

1

2

3

4

A-GND

5

A-GND

M RELAY

A ND

R450

100k

C430

220u16

R449

C431

464

220u16

A-GND

J407

C422

470u/25

11V

EARTH

A-GND

+11V

C471

470u25

A-GND

C455

220u16

R474

C456

464

220u16

R475

100k

A-GND

B5B-EHTS

LN26

1

UB2-12NUN

2

D D

A D

3

6 5

4

1

5

A-GND

DN26

1SS301

A-GND

M RELAY

A- D

R500

100k

C480

220u16

R499

C481

464

220u16

A-GND

C472

470u/25

-11V

ANALOG OUT

LCH

J402

W401

L-CH

EHR5WIRE

1

5

4

2

-

3

2

+

A-GND

1

J403

CANON

1

2

12

3

3

4

G

BALANCED

AGND

5

4

3

2

1

W451

EHR5WIRE

RCH

J452

RCH

1

2

-

+

A-GND

J453

CANON

1

2

12

3

3

4

G

BALANCED

A-GND

451

1-17 1-18

FROM POWER PWB (PP16)

FROM POWER PWB (PP16)

11V0

N11V0

N11V1

11V1

J806

GND

DGO

GND

EXFS

GND

P8V

N8V

GND

FGND

F15V

PA16 PWB -4/4

PA16

J856

1

2

3

4

1

2

3

4

5

6

7

8

9

10

D GND

00MW 27AK201

D851D854

11EQS1011EQS10

C851

D855

11EQS10

D856

11EQS10

QN05

NJM78M12FA

IN

OUT

GND

D GND

4700u 35

A GND

A GND

C852

4700u 35

D842

D843

11EQS10

11EQS10

D841

D844

11EQS10

11EQS10

DN19

CN08

9 1V 22k

100u/25

D GND

RN09

22k

RN10

4 7k

D GND

SATT

D853 D852

11EQS10 11EQS10

D858

11EQS10

D857

11EQS10

FROM PA16 -1/4

DGO

EXFS

CN06 RN13

47u/25

D GND

AMUT

Q853

2SK246 GR

3

A GND

2SK246 GR

R852

100

Q854

D GND

R851

100

RN15

2

1

1000u/35

RN11

47k

QN07

2SC4081

1k

R601

1

4 7k

A GND

2

C841

2SD1415A

Q855

2SC2240

C853C854

100u 25100u/25

Q856

2SA970

3

Q852

2SB1020A

D GND

Q851

2SK246 GR

DN20

1SS301

3

1

2SC4081

R602

4 7k

123

123

D859

1SS301

1SS301

R603

Q601

D860

Q842

22k

D861

HZ6L 3

D862

HZ6L 3

2

R841

100

100u/25

PLAY 0V

MUTE 07V

2

D GND

+11V

R855

2 74k

R853

3 32k

C855

470u 16

R857

3 32k

R858

3 32k

C856

470u 16

R856

2 74k

R854

3 32k

11V

Q841

2SD1415A

+8V

3

1

123

D845

1SS301

D846

C842

9 1V

RN16

QN10

2SC4081

D GND

CN10

RN17

10u/16

NON

D GND

R604

22k

R605

3 3k

12

Q602

2SC4081

C601

NON

D GND

D GND

R606

220k

2SB798

Q603

RN12

QN08

2SC4081

+11V

11V

+8V

C843

470u 16

F15V

22k

3 3k

12

2SB798

QN09

D GND

RN14

220k

M RELAY

ATT RELAY

COMM

0

R691

F

0

R692

N/K

0

R693

U

1-201-19

W001

ACCORD

1

2

12

J001

INLET 2P

12

L003

WH01

21

12

JH06

B2P3

12

SH01

GH01

001u

LH01

Transformmer

PP16 PWB

00MWG27AK101

PP16

JH01

B2P3

2

2

1

FH01

JH02

T315A L 250V

forF U

T16A L 250V

forN K

WH05

2

1

1

1

JH03

1

2

JH05

B2P3

JH04

B2P3

2

2

6

5

4

3

2

1

J801

B6P VH

F801

T16A L 250V

T1AL 250V

T1AL 250V

JT02

TOTX179L

3

IN

2

OPT

VCC

1

GND

CT10

01u

GND GND

RT08

0

47p

RT09

CT05

0

CT07CT06

01u2200p

+12M

+8M

+5V

GND GND

DIG. OUT

J810

GND

EARTH

LT11

+12M

GNDM

+8M

GNDM

+5V

GND

+5V

GND

COAX

JT03

1

2

JT01

B2B EH

1

2

J805

B8B PH

8

7

6

5

4

3

2

1

TO Super Audio CD MODULE UNIT

D806

D807

D808

11EQS10

11EQS10

11EQS10

D814 D811

11EQS10 11EQS10

DN14

11EQS10

DN03

11EQS10

11EQS1011EQS10

11EQS1011EQS10

DN11

11EQS10

11EQS10

DN01DN04

11EQS1011EQS10

D801 D808

D804D805

11EQS1011EQS10

D803

11EQS10

D802

11EQS10

C802

6800u/16

D801

11EQS10

D812D813

C811

4700u/25

GND

DN12DN13

CN04

2200u35

GND

DN02

DN05

11EQS10

RN01

12K

GND

DN07

10V

RN02

15K

J803J802

F811

J812J811

F821

J822J821

Q801

PG05RD21

132

IN

OUT

GND

CTL

C806

6800u/16

C803

6800u/16

GND

Q811

+12V

OUT

GND

C813

4700u/16

QN04

2SD1415A

DN16

RN08

1SS254

27k

GND

QN03

DN15

RN06

18V

FGND

+21V

CN01

100u35

QN01

DN07

22M

RN03

CN02

CN03

1u100

47u 50

+5V

+5V

4

C805

C804

220u253300u6 3

GND

+12M

Q812

NJM7808FANJM7812FA

C814

220u/16

N

OUTN

GND

C815

220u50

+15V

+15VF

CN05

01u

10K

RN05

RN04

10k

47K

QN02

LT04

BL02RN2R

CT09

100u25

CT02

01u

GND

RT02

DGO

RT01

12K

CT01

01u

+8V

+8M

QT01

MC74HCU04AN

1234567

100K

RT03

22

CT03

100p

GND

891011121314

CT04

01u

100

RT07

33

RT04

GND

RT05

75

136

2

LT01

GND

GND

FORF

R891

0

FORU

R892

0

FORN K

R893

0

R894

0

GND

BNCINPUT

EXTERNAL Fs CLK

J850

B6P VH

1

2

3

4

5

6

JE01

1PBNC

RE02

1k

1

RE01

2

75

3

GND

F853

T1AL 250V

J854J853

J851

J852

F851

T1AL 250V

J841 J842

F841

T1AL 250V

LE01

BL02RN2R

+5V

CE04

01u

100u25

CE03

GND

CE02

1u/50

01u

CE01

RE06

100k

GND

QE01

MC74HCU04AN

1234567

RE04

47k

GND

RE05

47

891011121314

GND

RE03

22k

EXFS

J855

1

11V0

2

N11V0

3

N11V1

4

11V1

TO AUDIO PWB (PA16)

J804

10R FJ

10

GND

DGO

9

DGO

8

GND

7

ENFS

6

GND

5

P8V

4

N8V

3

GND

2

FGND

+15VF

FGND

1

TO AUDIO PWB (PA16)

+15VF

GND

1-21 1-22

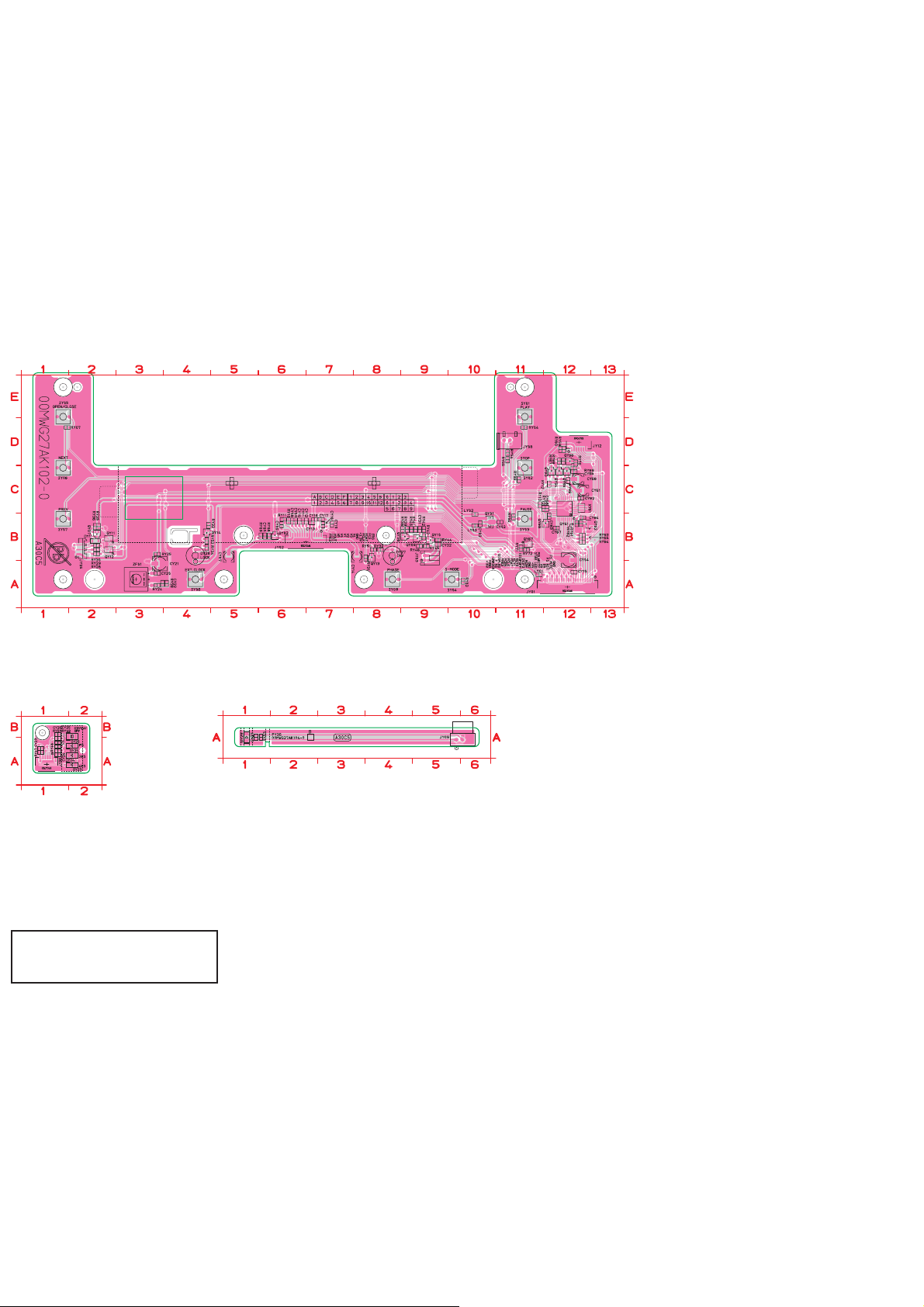

DSP2 D SPOFF)

FROM AUDIO PWB (PA16)

WY01

FFC22P 1 0MM

PMODE

FS MUTE

FS RST

POLARITY

STAR LED

RC5F

KEY0

KEY1

FDAT

FCLK

FCEN

FRES

DSPLED

F RS

UNKOCK

FGND

PY16

00MWG27AK102

PY16 PWB

JY01

22FMN

1

2

3

4

B0

5

A0

6

7

STAR LED

8

+5V

9

GND

0

1

2

3

4

5

6

7

8

9

0

1

2

+15V

G

STAR LED

BLM11B601SPT

CY04

47u/63

GND GND

QY01

NJU7222U33

213

N

OU

GND

CY02 CY03

01u 01u

GND GND

GND

LOCK

DY28 DY27

12

LOCK INV

QY14

RY33 RY31

47k 4 7k

GND

RY54RY55

15k15k

GND

PY36 PWB

PY36

LY01

CY15

01u

LY02

BLM11B601SPT

LY03

BLM11B601SPT

NV

+15VF

GND

RY53

CY27

DY29

STARLED

00MWG27AK104

123

JY08

123

JY09

10k

01u

+15VF

+5V

+5VF

+15VF+15VF

12

GND

RC5F

FS MUTE

FS RST

B0

A0

POL

RC5F

DSPOFFI

KEY0

KEY1

FDAT

FCLK

FCEN

FRES

DISPLED

F RS

UNLOCK

DSPOFFI

+33VF

RY32RY34

27k2 7k

RY51RY52

27k2 7k

QY13

33k

33k

RY28

RY29

4FS

2FS

FS

PY26 PWB

33k

RY73

DSPOFFI

QY68

DTC114EUA

FS RST

+33VF

22k

RY71

GND

4FS

QY11

UMH10NTN

456

GND

123

GND

456

GND

123

GND

QY12

UMH10NTN

33k

RY30

6

GND

12345

GND

NC

RY49 RY48 RY47RY50

01u 0 1u 0 1u 0 1u

CY26 CY25 CY24 CY23

DY26

DSPLAY OFF FS 2FS 4FS

PY26

00MWG27AK103

RY69

47k

82k

RY70

RY67

47k

GND

QY66

RY68

18k

GNDGND

RC SW

H IR Sensor Out

L ucom Out

+5V

GND

22k

RY72

123

456

GND

UMH10NTN

FS RSTO

DSPOFFO

QY67

FS

2FS

+33VF

33k

RY35

DY11

75V

QY07

1k

RY36

GND

ODSPOFF

FS

4FS

2FS

ODSPOFF

JY05

12345

JY06

6

10k 10k 10k

DY25 DY24 DY23

QY63QY64

NCNC

QY65

DTA114EUA

KI POL

IFS

I2FS

I4FS

ILOCK

IINV

RCIN

KI FSSW

GND

DSPOFFO

+5V

RY12

RY13

SY05

OPENCLOSE

SY06

NEXT

SY07

PREV

GND

SY08

EXTCLOCK

GND GND

+15VF

RC_SW

17

18

RCN

19

KI FSSW

20

VCC

CY68

01u

21

NC

22

GND

23

KSTOP

24

IVCC

NC

CY63

01u

UNLOCK

25262728293031

GND

CY67

01u

GND

UNLOCK

FS_RSTO

KEY0

K POL

K_FSSW

NC

NC

12

RY07

RY06

330

150

12

12

12

LED_NV

R8C/12

FS_RST

LED4FS

LED_LOCK

QY61

FS_MUTE

MODE

KEY1

CY65

01u

GND

11910

1213141516

RCOUT

LED_FS

LED 2FS

LED_FSOF

KI POL

VCC

XIN

GND

XOUT

XRESET

CNVSS

RXD

POL

FSSWB

FSSWA

TXD

32

0

POL0FS_MUTE

SY04

S MODE

12

SY01

RY03

PLAY

150

12

SY02

RY04

STOP

180

12

SY03

PAUSE

12

RY05

270

SY09

PHASE

12

RY66

100

+5V

CY66

NC

+5V

CY61

10u16

CY62

01u

1

GND

8

7

6

5

4

GN

3

2

1

+5V

RY63

33k

RY64

33k

RY65

33k

RCN

CY22

RY26

+5VF

1k

RY24

100

1

RY25

2

GND

3

RPM 6936 V4

01u

47u6 3

CY21

CY20

ND

GND

GND

LCD DISPLAY ASSY

D001 D002

Fs SELECTOR; SE02(CONTROL)

AIN BIN HC4052 OPERAT

LL

OUTPUT POLARITY

INV

L

H

+5V

QY62

BD4742G

123

XY61

16MHz

3

2

GND

RY62

51k

GND

470p

NC

GND

ZF01

RY61

33k

45

CY64

GND

01u

CNVSS

RESET

RXD

TXD

MODE

FCLK

F_RS

FRES

CY06

470p

GND

+15VF

80V

GND

QY02

2SC4081

47k

RY08

47k

RY09

GND

RY11

76V

22k

RY10

047u

CY05

CY07

22u/50

56k

GND

GND

70V

14V

57V

33V

VOUT14REST

13

V0V1V2V3V4

VR

VOUT

RESET

D003

FDAT

FCEN

+33VF

CY14

10u16

CY13

01u

GND

GND

047u

047u

047u

047u

047u

CY12

CY09

CY08

CY10

CY11

46V

34V

23V

17V

GND

V210V111V012VR

SCL

GND

RS

CS

+33V

123S4

5

6

7V48V39

S

CS

SCL

GND

+33V

D005

D004

LLH

H

HH

1000p

1000p

1000p

1000p

14FMN

FREXBLWIRE

RS

OFF

0X

Fs

1X

2Fs

2X

3Fs

3X

POLARITY

NORMAL

INVERT

RY59

0

CNVSS

+5V

RXD

TXD

MODE

RESET

DSPLED

CY19

CY18

CY17

CY16

JY02

GND

002

J

+33VF +15VF

RY40

1k

RY39

560

RY42

18k

GND

RY38

22k

QY08

GND

15V

0V/15V ON/OFF)

RY41

680

RY43

1k

CY31

01u

GND

QY09

GND

0OHM43mA

33OHM 19mA vF 96v

120OHM 12mA

10k

01u

RY44

CY32

QY10

47

RY45

33

RY46

GND

JY03

2

S2B PH

001J

2

LEDWIRE

JY12

07FMN

1

GND

NC

RY60

2

3

4

5

6

7

GND

FROM AUDIO PWB (PA16)

1

1

1-241-23

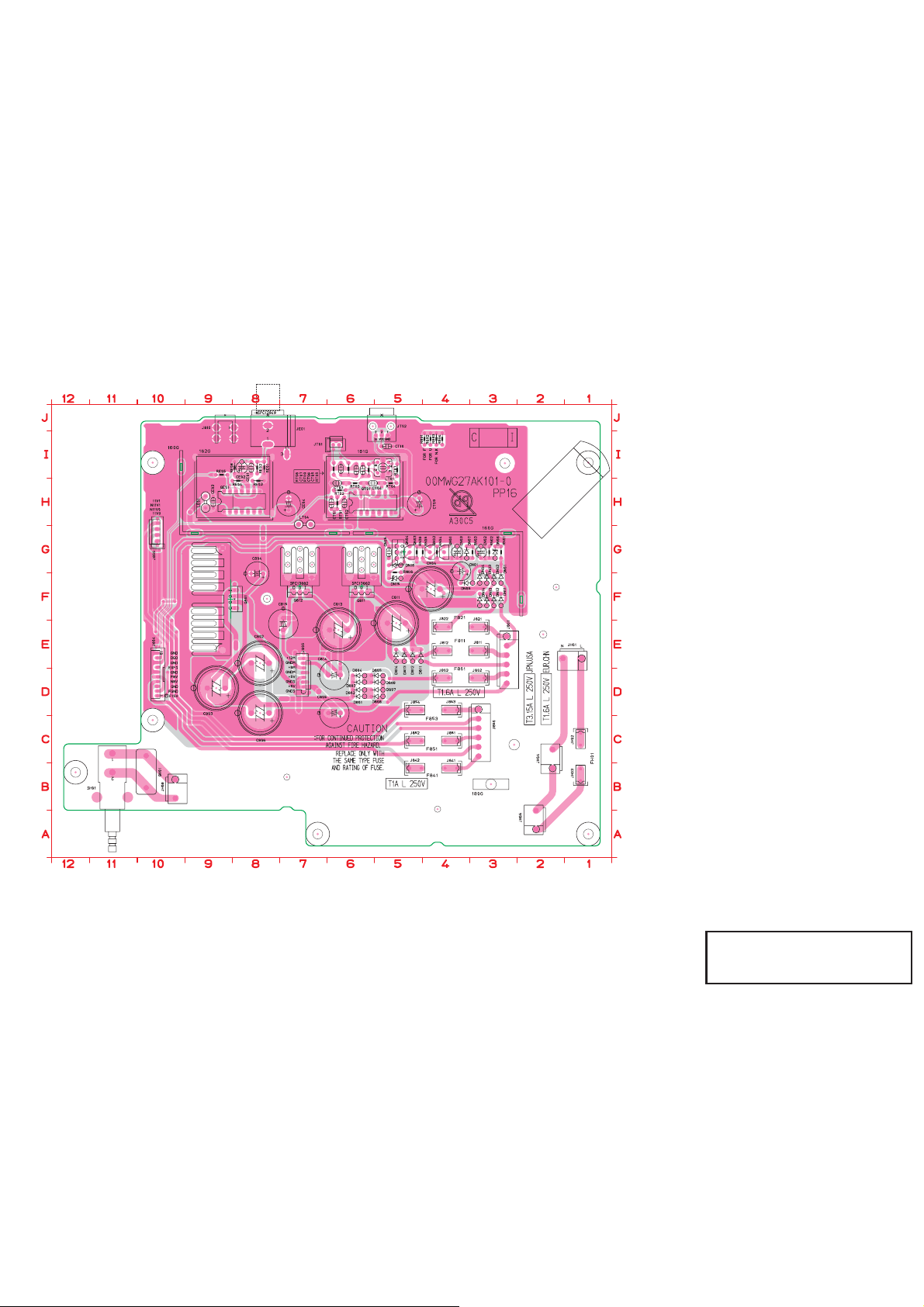

11. PARTS LOCATION

鉛フリー半田

PP16 PWB B

C802 E8

C803 D9

C804 F8

C805 D6

C806 D8

C811 E5

C813 E6

C814 D6

C815 E7

CE01 I8

CE02 I8

CE03 H9

CE04 H7

CN01 G4

CN02 G3

CN03 G4

CN04 F4

CN05 G5

CT01 H6

CT02 H6

CT03 H6

CT04 H5

CT05 I6

CT06 I6

CT07 I6

CT09 H5

CT10 I5

D801 D6

D802 D6

D803 D6

D804 D6

D805 D5

D806 D5

D807 D5

D808 D5

D811 E5

D812 E5

D813 E5

D814 E5

DN01 F3

DN02 F3

DN03 F3

DN04 F3

DN05 F3

DN06 G3

DN07 G4

DN11 F3

DN12 F3

DN13 F3

DN14 F3

DN15 F5

DN16 G5

GH01 B10

J801 E3

J802 D3

J803 D4

J804 D10

J805 D7

J810 J9

J811 E3

J812 E4

J821 E3

J822 E4

J841 B4

J842 B5

J850 D3

J851 C4

J852 C5

J853 D4

J854 D5

J855 G10

JE01 J8

JH01 E1

JH02 C1

JH03 B1

JH04 B2

JH05 A2

JH06 B10

JT01 I6

JT02 J5

LE01 H9

LT01 I5

LT04 H7

Q801 F8

Q811 F6

Q812 F7

QE01 H9

QN01 G4

QN02 G4

QN03 G5

QN04 G5

QT01 H6

R891 I4

R892 I4

R893 I4

R894 I4

RE01 I8

RE02 I8

RE03 H8

RE04 H8

RE05 I9

RE06 I8

RN01 G3

RN02 G3

RN03 G3

RN04 G4

RN05 G4

RN06 G5

RN08 G5

RT01 H6

RT02 H6

RT03 H6

RT04 H5

RT05 I6

RT07 I5

RT08 I6

RT09 I6

SH01 B11

1-25 1-26

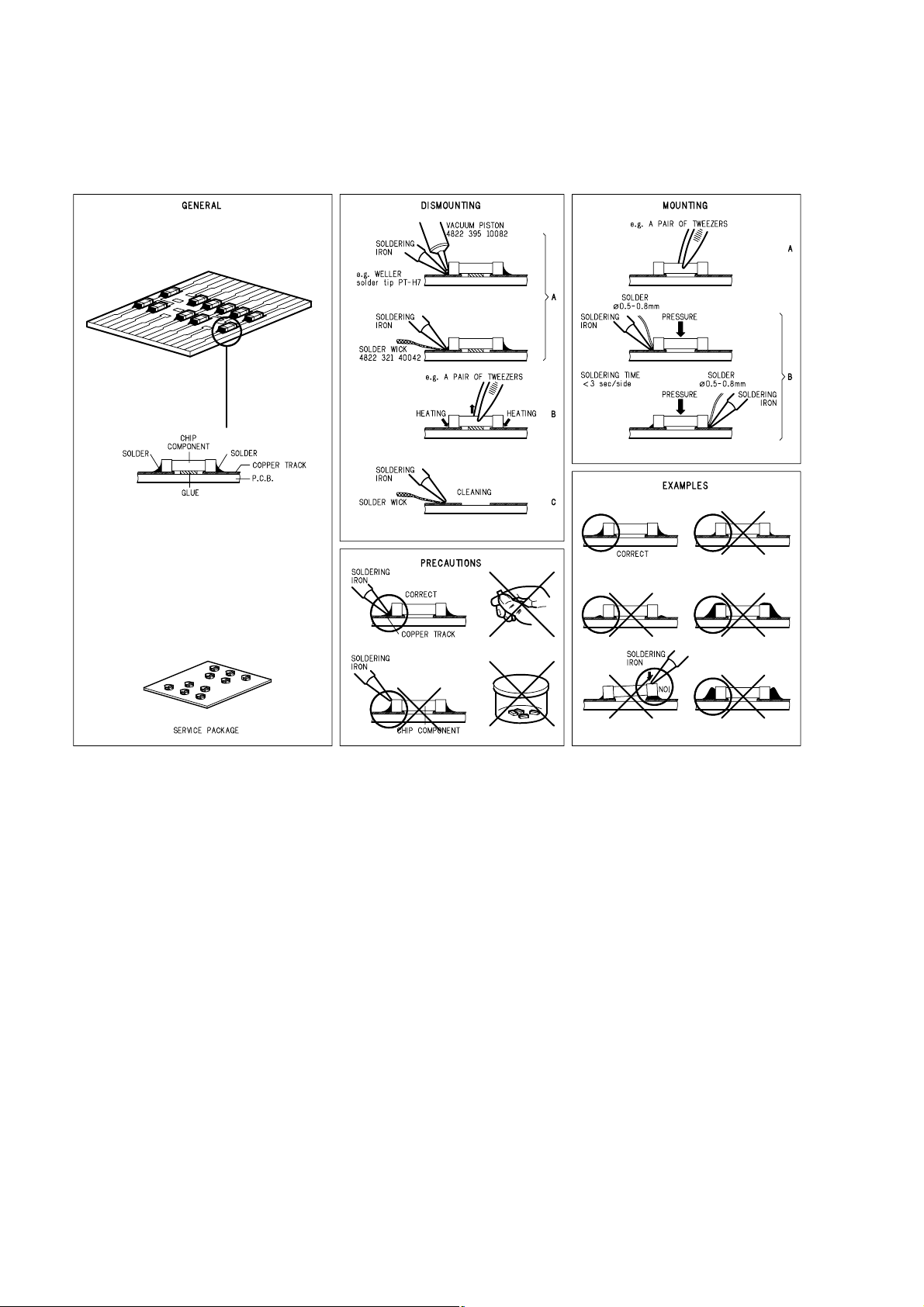

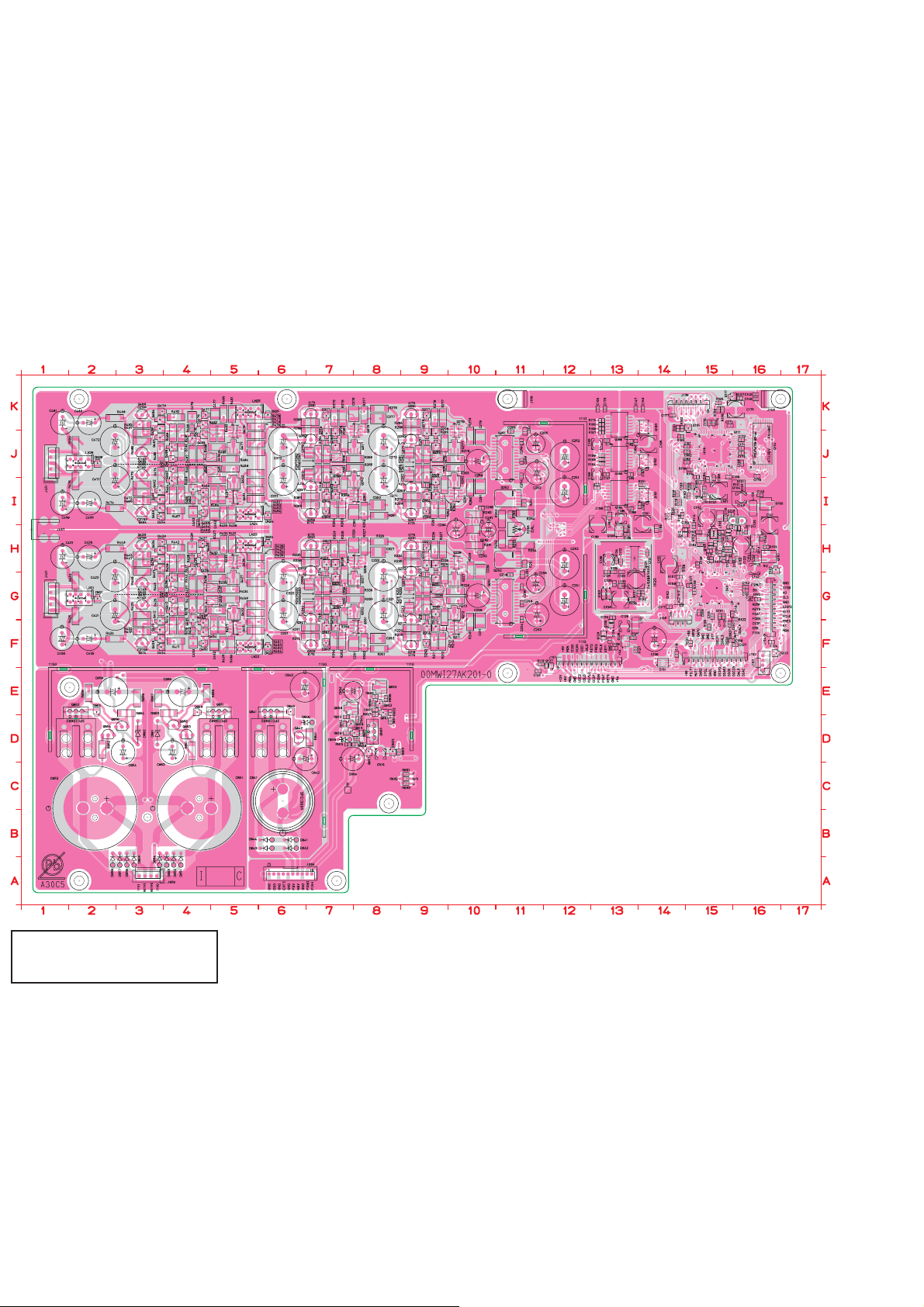

鉛フリー半田

半田付けには、鉛フリー半田

Lead-free Solder

When soldering, use the Lead-free Solder (Sn-Ag-Cu).

(Sn-Ag-Cu)

を使用してください。

鉛フリー半田

PA16 PWB A

半田付けには、鉛フリー半田

Lead-free Solder

When soldering, use the Lead-free Solder (Sn-Ag-Cu).

(Sn-Ag-Cu)

を使用してください。

1-281-27

鉛フリー半田

PA16 PWB

C101 G16

C102 G16

C103 H15

C104 H15

C105 H15

C106 H15

C107 G15

C108 G15

C109 G15

C110 G15

C111 G15

C112 G15

C113 G15

C114 H15

C115 H15

C116 F14

C117 G14

C118 I15

C119 I15

C120 H16

C121 H15

C122 H16

C123 G16

C124 F16

C125 E11

C126 F13

C127 F13

C128 F13

C129 F13

C130 G13

C131 H14

C132 H13

C133 H13

C134 G13

C135 H13

C136 H13

C137 F16

C138 G13

C139 G13

C140 I16

C141 H16

C142 H16

C143 H16

C144 H15

C145 K16

C146 K16

C147 K13

C148 H16

C149 I16

C150 H15

C151 H15

C152 I15

C153 H15

C154 H16

C155 H14

C156 F14

C157 F15

C158 F15

C159 K14

C160 I14

C161 J15

C162 J15

C163 J15

C164 I15

C165 I15

C166 I15

C167 I15

C168 J15

C169 J16

C170 J16

C171 J16

C172 J16

C173 K15

C174 K15

C175 K16

C176 K15

C177 K14

C178 J16

C179 K13

C180 K13

C181 I14

C182 I14

C183 J14

C184 J13

C185 J14

C186 I13

C188 I13

C189 J13

C190 J13

C191 J13

C192 J13

C193 J13

C194 J13

C195 I13

C196 I13

C197 H13

C198 H13

C201 G12

C202 H12

C203 F11

C204 G11

C205 G11

C206 G11

C208 G10

C209 G11

C210 G11

C211 F10

C212 G9

C221 F8

C222 G8

C226 H10

C227 G9

C251 I12

C252 J12

C253 I11

C254 J11

C255 J11

C256 J11

C258 J10

C259 J11

C260 J11

C261 I10

C262 J9

C271 I8