Page 1

Service

SA14/

F1N, /C1G, /S1G,/U1G, /U1B

SA-14

Manual

SECTION PAGE

1. MAIN UNIT

1.1 TECHNICAL SPECIFICATIONS ......................................................................................................... 1-1

1.2 TEST MODE ........................................................................................................................................ 1-2

1.3 BLOCK DIAGRAM ............................................................................................................................... 1-3

1.4 WIRING DIAGRAM ............................................................................................................................. 1-5

1.5 SCHEMATIC DIAGRAM ...................................................................................................................... 1-7

1.6 PARTS LOCATION ........................................................................................................................... 1-19

1.8 IC DATA

1.10 ELECTRICAL PARTS LIST .............................................................................................................. 1-29

............................................................................................................................................

Super Audio CD Player

SUPER AUDIO CD PLAYER SA-14

REP 1

TRACK

RND

PROGRAM TOTAL

POWER

PLAY

SACD CD

OPEN/CLOSE

PLAY

SACD/CD

DISPLAY

TABLE OF CONTENTS

......................................................................................................... 1.7 ELECTRICAL ADJUSTMENTS

............................................................................................... 1.9 EXPLODED VIEW AND PARTS LIST

PAUSESTOP

1-23

1-24

1-26

2. CDM-15M ( SACD MODULE )

2.1 REMOVING AND REINSTALLING THE MAIN PARTS ...................................................................... 2-2

2.2 BLOCK DIAGRAM ............................................................................................................................... 2-5

2.3 SCHEMATIC DIAGRAM ...................................................................................................................... 2-9

2.4 PARTS LOCATION ........................................................................................................................... 2-13

2.5 IC DATA ............................................................................................................................................ 2-17

2.3 EXPLODED VIEW AND PARTS LIST ............................................................................................... 2-36

2.4 ELECTRICAL PARTS LIST ............................................................................................................... 2-37

Please use this service manual with referring to the user guide ( D.F.U. ) without fail.

SA-14

R

Printed in Japan

410K855010 KKI

First Issue

2001. 03

Page 2

MARANTZ DESIGN AND SERVICE

MARANTZ AMERICA, INC.

Using superior design and selected high grade components, MARANTZ company has created the ultimate in stereo sound.

Only original

MARANTZ parts can insure that your MARANTZ product will continue to perform to the specifications for which

it is famous.

Parts for your

MARANTZ equipment are generally available to our National Marantz Subsidiary or Agent.

ORDERING PARTS :

Parts can be ordered either by mail or by Fax.. In both cases, the correct part number has to be specified.

The following information must be supplied to eliminate delays in processing your order :

1. Complete address

2. Complete part numbers and quantities required

3. Description of parts

4. Model number for which part is required

5. Way of shipment

6. Signature : any order form or Fax. must be signed, otherwise such part order will be considered as null and void.

USA

MARANTZ AMERICA, INC

440 MEDINAH ROAD

ROSELLE, ILLINOIS 60172

USA

PHONE : 630 - 307 - 3100

FAX : 630 - 307 - 2687

AMERICAS

SUPERSCOPE TECHNOLOGIES, INC.

MARANTZ PROFESSIONAL PRODUCTS

2640 WHITE OAK CIRCLE, SUITE A

AURORA, ILLINOIS 60504 USA

PHONE : 630 - 820 - 4800

FAX : 630 - 820 - 8103

AUSTRALIA

QualiFi Pty Ltd,

24 LIONEL ROAD,

MT. WAVERLEY VIC 3149

AUSTRALIA

PHONE : +61 - (0)3 - 9543 - 1522

FAX : +61 - (0)3 - 9543 - 3677

NEW ZEALAND

WILDASH AUDIO SYSTEMS NZ

14 MALVERN ROAD MT ALBERT

AUCKLAND NEW ZEALAND

PHONE : +64 - 9 - 8451958

FAX : +64 - 9 - 8463554

EUROPE / TRADING

MARANTZ EUROPE B.V.

P.O.BOX 80002, BUILDING SFF2

5600 JB EINDHOVEN

THE NETHERLANDS

PHONE : +31 - 40 - 2732241

FAX : +31 - 40 - 2735578

AUSTRALIA

TECHNICAL AUDIO GROUP PTY, LTD

558 DARLING STREET,

BALMAIN, NSW 2041,

AUSTRALIA

PHONE : 61 - 2 - 9810 - 5300

FAX : 61 - 2 - 9810 - 5355

THAILAND

MRZ STANDARD CO.,LTD

746 - 754 MAHACHAI ROAD.,

WANGBURAPAPIROM, PHRANAKORN,

BANGKOK, 10200 THAILAND

PHONE : +66 - 2 - 222 9181

FAX : +66 - 2 - 224 6795

TAIWAN

PAI- YUING CO., LTD.

6 TH FL NO, 148 SUNG KIANG ROAD,

TAIPEI, 10429, TAIWAN R.O.C.

PHONE : +886 - 2 - 25221304

FAX : +886 - 2 - 25630415

BRAZIL

PHILIPS DA AMAZONIA IND. ELET. ITDA

CENTRO DE INFORMACOES AO

CEP 04698-970

SAO PAULO, SP, BRAZIL

PHONE : 0800 - 123123

FAX : +55 11 534. 8988

(Discagem Direta Gratuita)

CANADA

LENBROOK INDUSTRIES LIMITED

633 GRANITE COURT,

PICKERING, ONTARIO L1W 3K1

CANADA

PHONE : 905 - 831 - 6333

FAX : 905 - 831 - 6936

SINGAPORE

WO KEE HONG DISTRIBUTION PTE LTD

130 JOO SENG ROAD

#03-02 OLIVINE BUILDING

SINGAPORE 368357

PHONE : +65 858 5535 / +65 381 8621

FAX : +65 858 6078

MALAYSIA

WO KEE HONG ELECTRONICS SDN. BHD.

SUITE 8.1, LEVEL 8, MENARA GENESIS,

NO. 33, JALAN SULTAN ISMAIL,

50250 KUALA LUMPUR, MALAYSIA

PHONE : +60 3 - 2457677

FAX : +60 3 - 2458180

JAPAN

MARANTZ JAPAN, INC.

35- 1, 7- CHOME, SAGAMIONO

SAGAMIHARA - SHI, KANAGAWA

JAPAN 228-8505

PHONE : +81 42 748 1013

FAX : +81 42 741 9190

Technical

KOREA

MK ENTERPRISES LTD.

ROOM 604/605, ELECTRO-OFFICETEL, 16-58,

3GA, HANGANG-RO, YONGSAN-KU, SEOUL

KOREA

PHONE : +822 - 3232 - 155

FAX : +822 - 3232 - 154

SHOCK, FIRE HAZARD SERVICE TEST :

CAUTION : After servicing this appliance and prior to returning to customer, measure the resistance between either primary AC

cord connector pins ( with unit NOT connected to AC mains and its Power switch ON ), and the face or Front Panel of product and

controls and chassis bottom.

Any resistance measurement less than 1 Megohms should cause unit to be repaired or corrected before AC power is applied, and

verified before it is return to the user/customer.

Ref. UL Standard No. 1492.

In case of difficulties, do not hesitate to contact the Technical

Department at above mentioned address.

001120KKI

Page 3

1.1 TECHNICAL SPECIFICATIONS

Audio Characteristics

Channels 2channels 2channels

Frequency range 2 Hz - 100 kHz 2 Hz - 20 kHz

Frequency characteristics 2 Hz - 50 kHz (-3 dB) 2 Hz - 20 kHz

Dynamic range 113 dB 100 dB

THD (1 kHz) 0.0015 % 0.0020 %

wow & flutter Precision of quartz Precision of quartz

Analog output

output level (unbalanced) 2.2 V 2.2 V

output level (balanced) 4.3 V 4.3 V

Digital output

output level (cinch JACK) - 0 .5 Vp-p (75 ohm)

output level (optical) - -19 dBm

Optical Readout System

Laser AlGaAs AlGaAs

Wave length 650 nm 780 nm

Super Audio CD CD

Sampling frequency 2.8224 MHz 44.1 kHz

Power Supply

/F1N version ................................................................................................ AC 100 V 50Hz/60 Hz

/U1G, U1B version ................................................................................................ AC 120 V 60 Hz

/N1G, /S1G version ................................................................................................ AC 230 V 60 Hz

/C1G version ................................................................................................ AC 220 V 60 Hz

Power Consumption ...................................................................................................................... 21 W

Cabinet, etc.

Dimensions (Width x Height x Depth) ................................................................... 458 x110 x 392 mm

Net weight ................................................................................................................................. 11.8 kg

Operating temperatures ................................................................................................+5 ˚C ~ +35 ˚C

Operating humidity ....................................................................................... 5 % ~ 90 % (without dew)

Accessories

Remote control unit (RC-14SA) .......................................................................................................... 1

Dimensions (Width x Height x Depth) ............................................................... 44 x 17.5 x 239 mm

Net weight (without Batteries) .................................................................................................. 175 g

AAA (R03) Batteries ............................................................................................................................ 2

Stereo audio cable with cinch pins ...................................................................................................... 1

AC Power Cord ................................................................................................................................... 1

User’s Guide ....................................................................................................................................... 1

Specifications subject to change without prior notice.

1-1

Page 4

1.2. TEST MODE

1. How to enter the initial test mode

Turn the power on, press the SACD/CD button and the

track down button more than two seconds.

Display: F 0 TEST

2. Version check mode

1 Press the SACD/CD button to enter this mode.

Display: 1 0

2 Model number (Press the PLAY button in the step 1 .)

Display: 1 0 0 0 0 1 0

3 Version (Press the PLAY button in the step 2 .)

Display: 1 0 A 0 0 0 1

4 Then press the PLAY button to return to the initial test

mode.

Display: F 0 TEST

3. Laser test mode

1 Press the PAUSE button to enter this mode.

(In case of the no disc mode, eject the tray.)

Display: 3 0 0 0 0 0 0

2 Enter the laser test mode.

Display: 3 1 0 0 0 0 0

3 CD laser lit up (Press the STOP button in the step 2 or

4.)

Display: 3 1 0 0 0 0 0

4 SACD laser lit up (Press the PAUSE button in the step 2

or 3.)

Display: 3 1 0 0 0 0 0

5 Laser test mode completed (Press the PLAY button in

the step 2, 3 or 4.)

Display: F 0 TEST

9 0 9 2 8

Year/Month/Day

Model number

Version number

4. FIP test

1 Press the PLAY button to enter this mode

Display: All lamps lit up.

2 Press the PLAY button again to return to the initial test

mode

Display: F 0 TEST

5. How to exit the test mode

In case of finish the test mode, press the mains switch

(POWER button)

1-2

Page 5

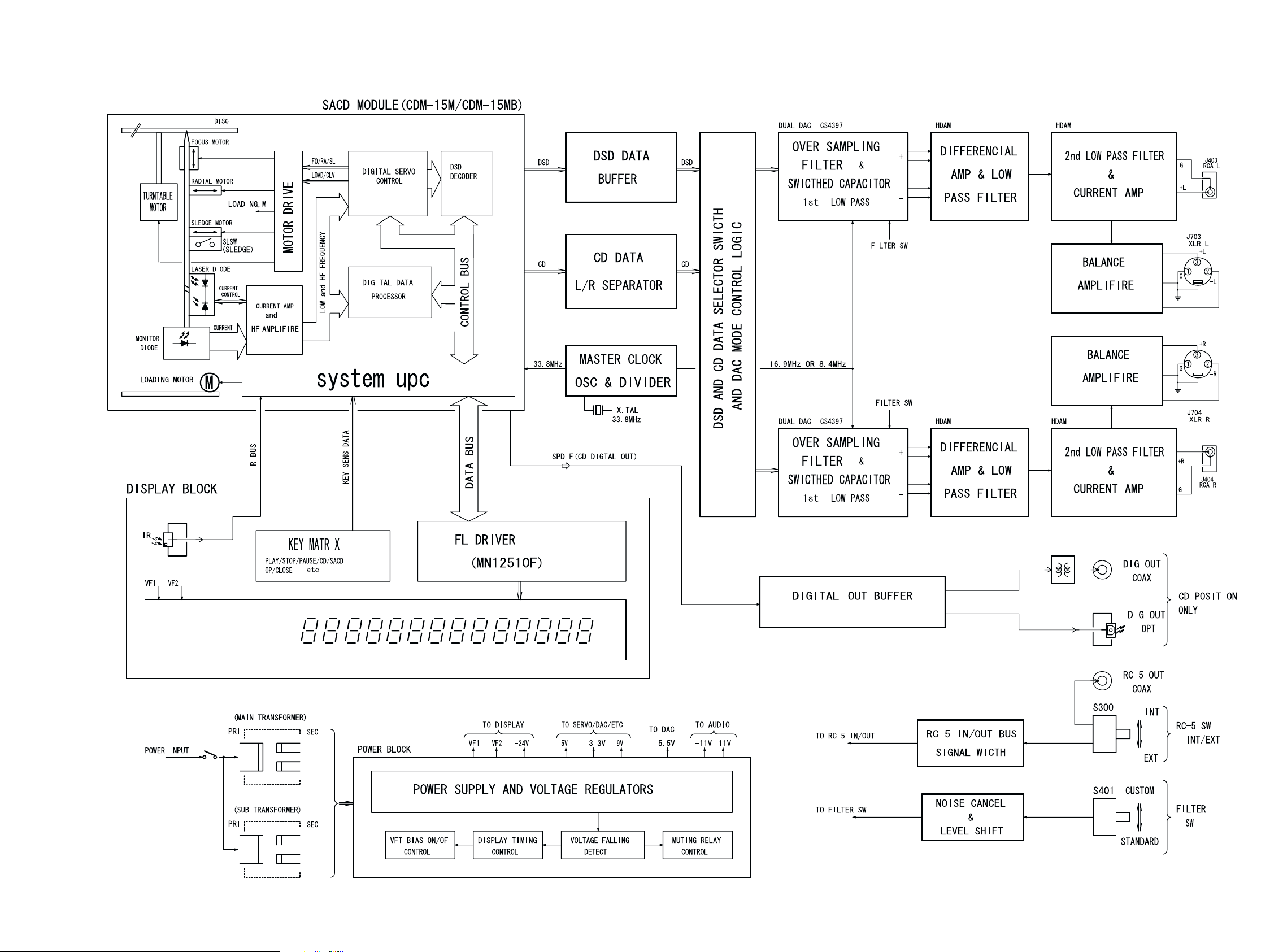

1.3 BLOCK DIAGRAM

1-3 1-4

Page 6

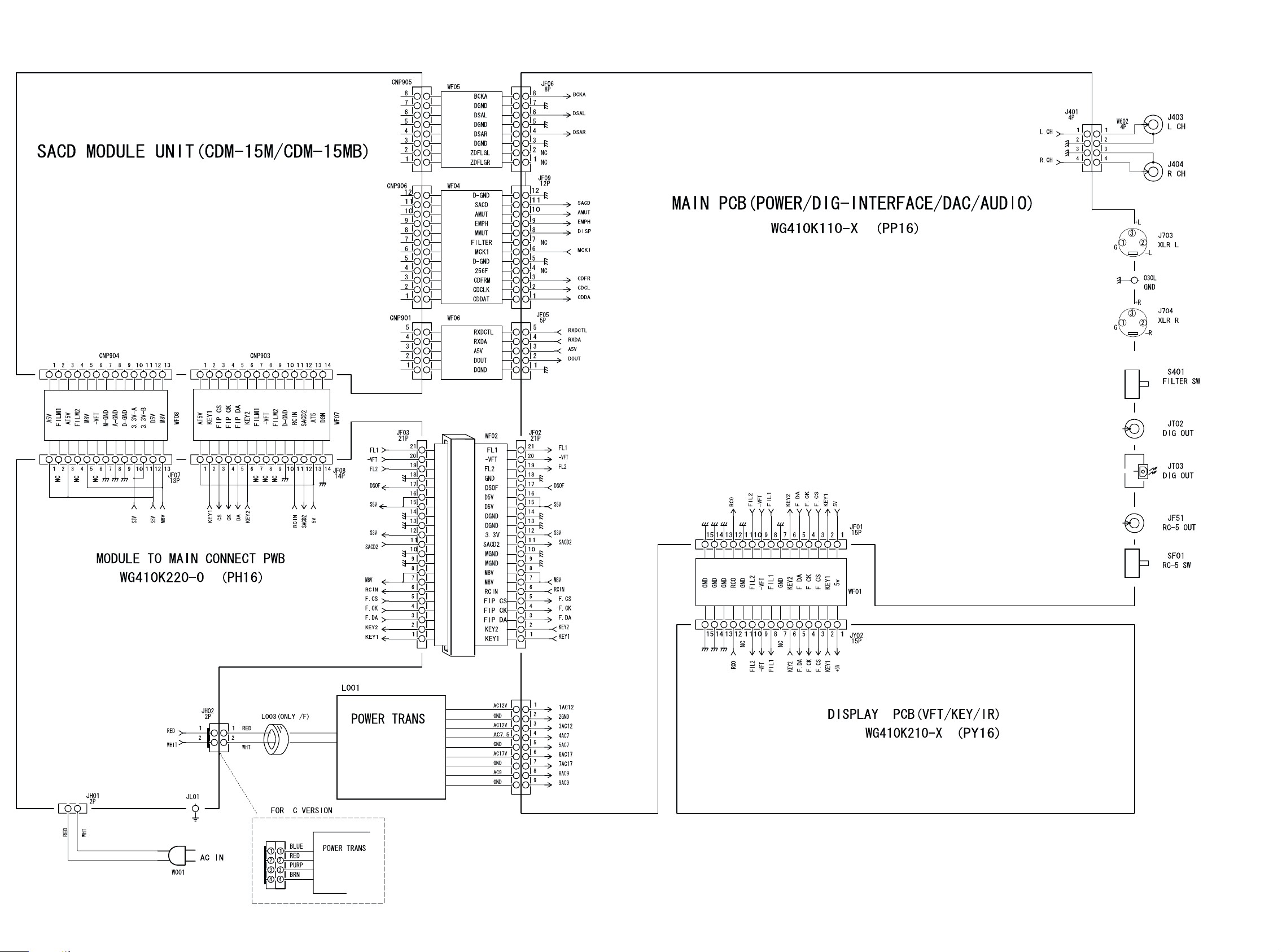

1.4 WIRING DIAGRAM

1-5 1-6

Page 7

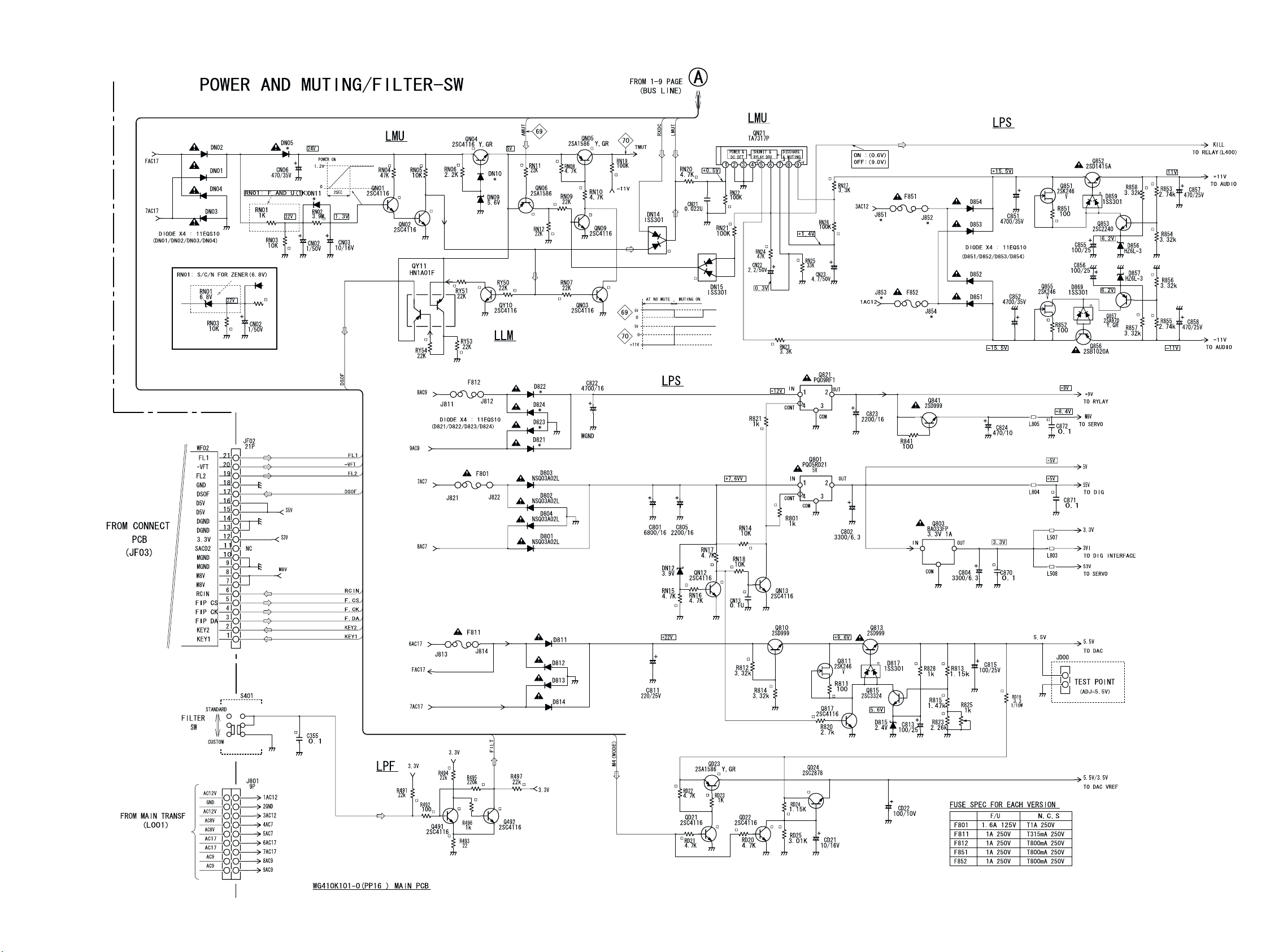

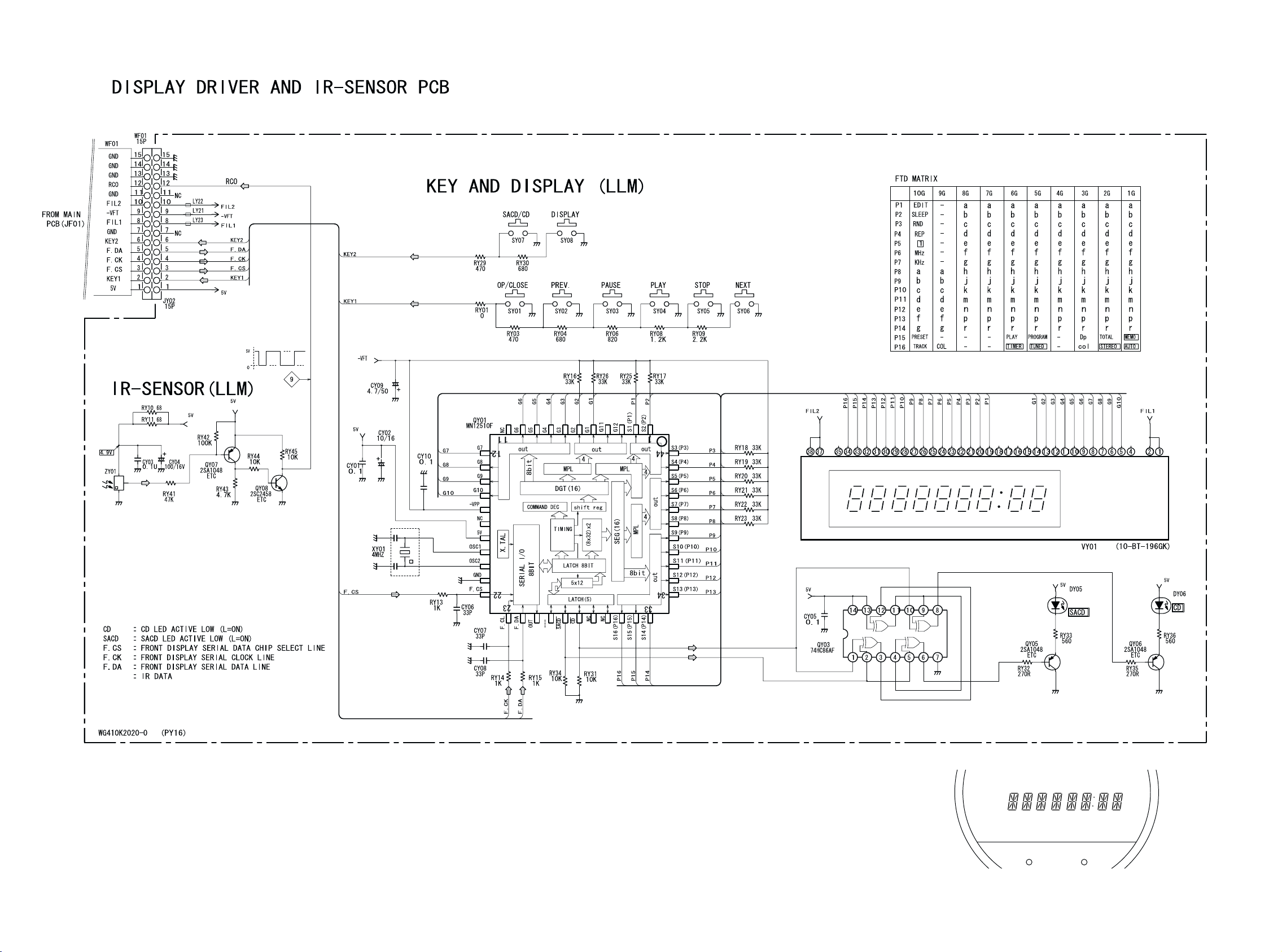

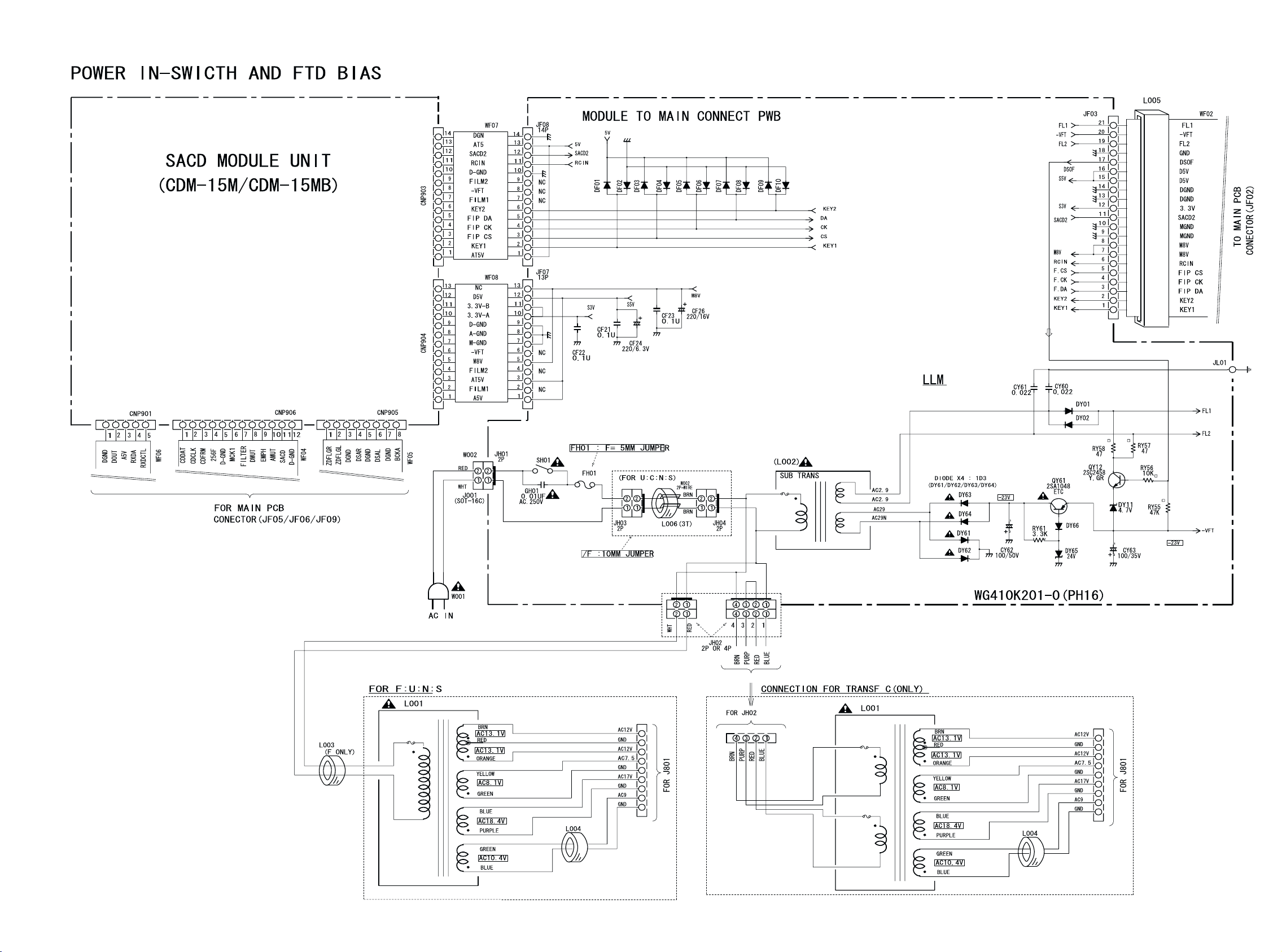

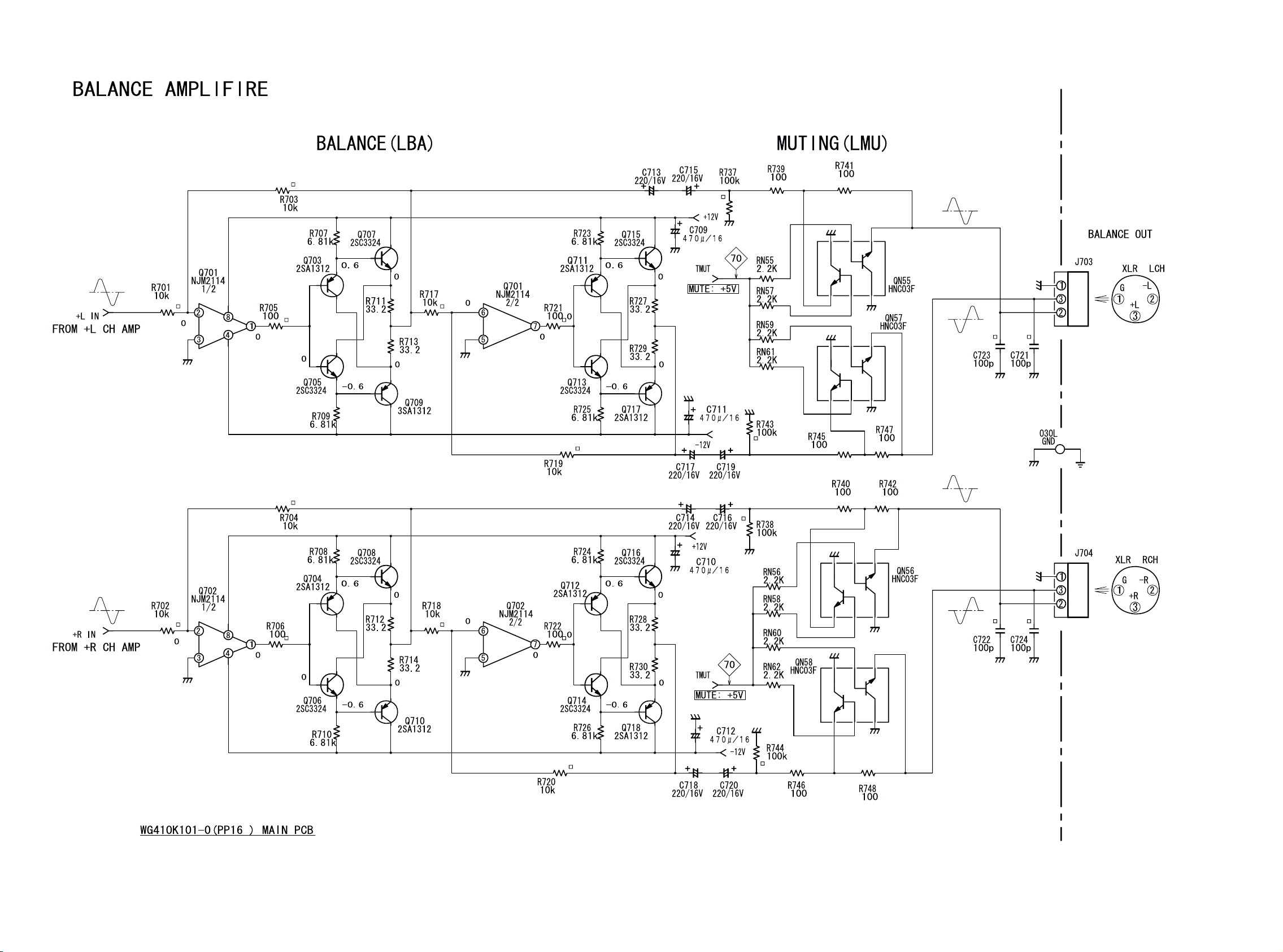

1.5 SCHEMATIC DIAGRAM

1-7 1-8

Page 8

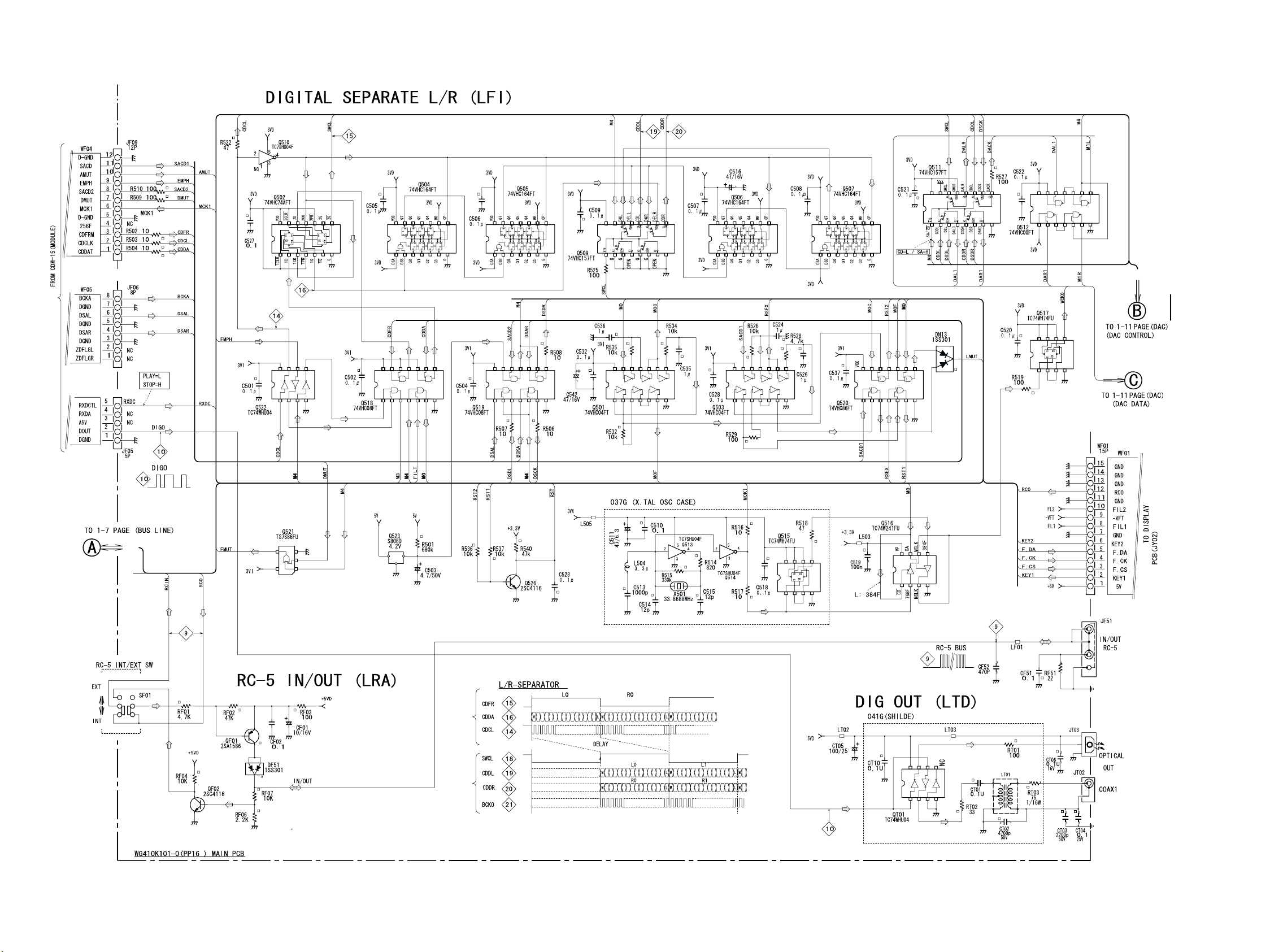

1-9 1-10

Page 9

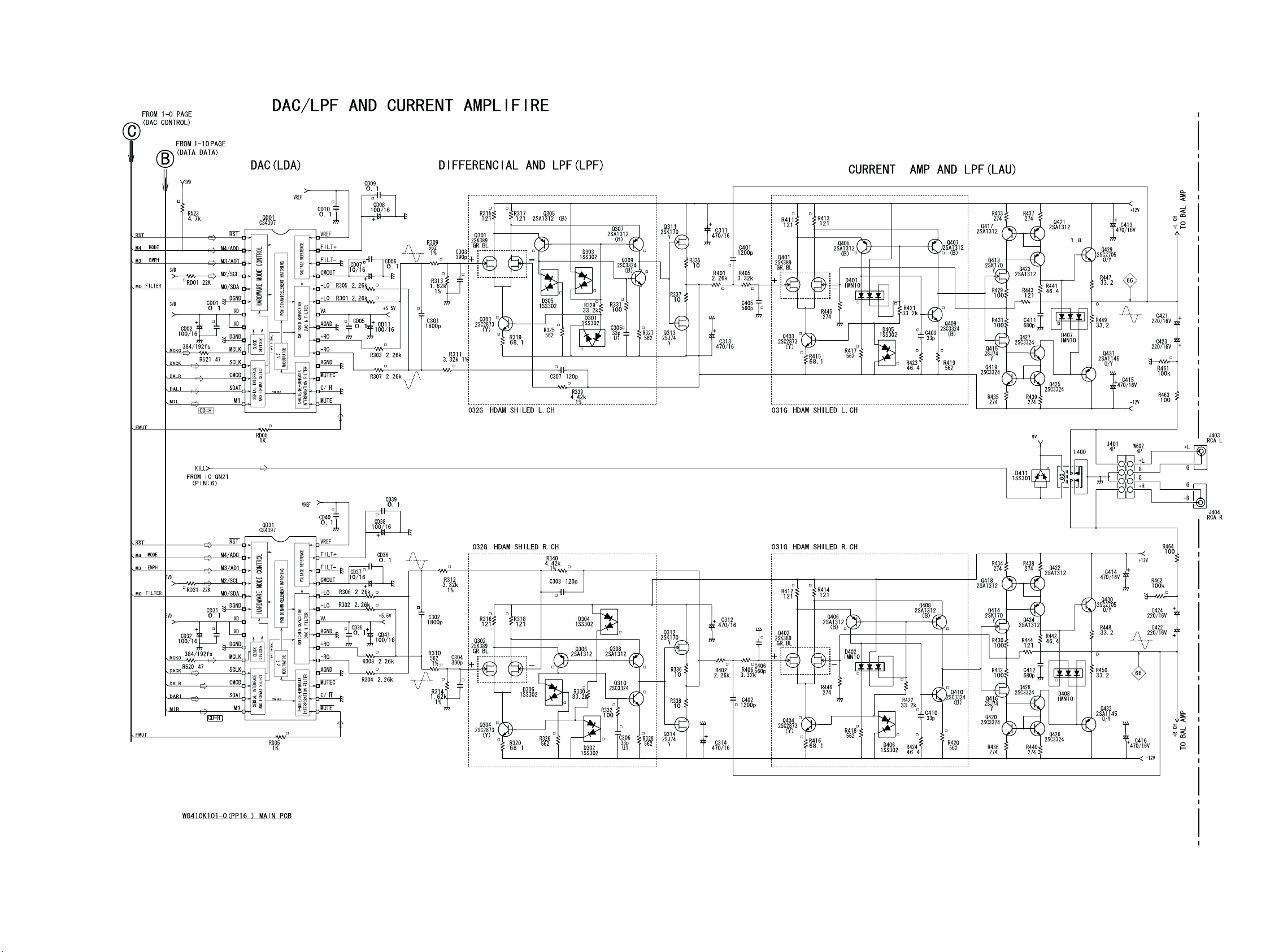

1-11 1-12

Page 10

REP 1

RND

TRACK

PROGRAM TOTAL

PLAY

1-13 1-14

SACD

CD

Page 11

1-15 1-16

Page 12

1-17 1-18

Page 13

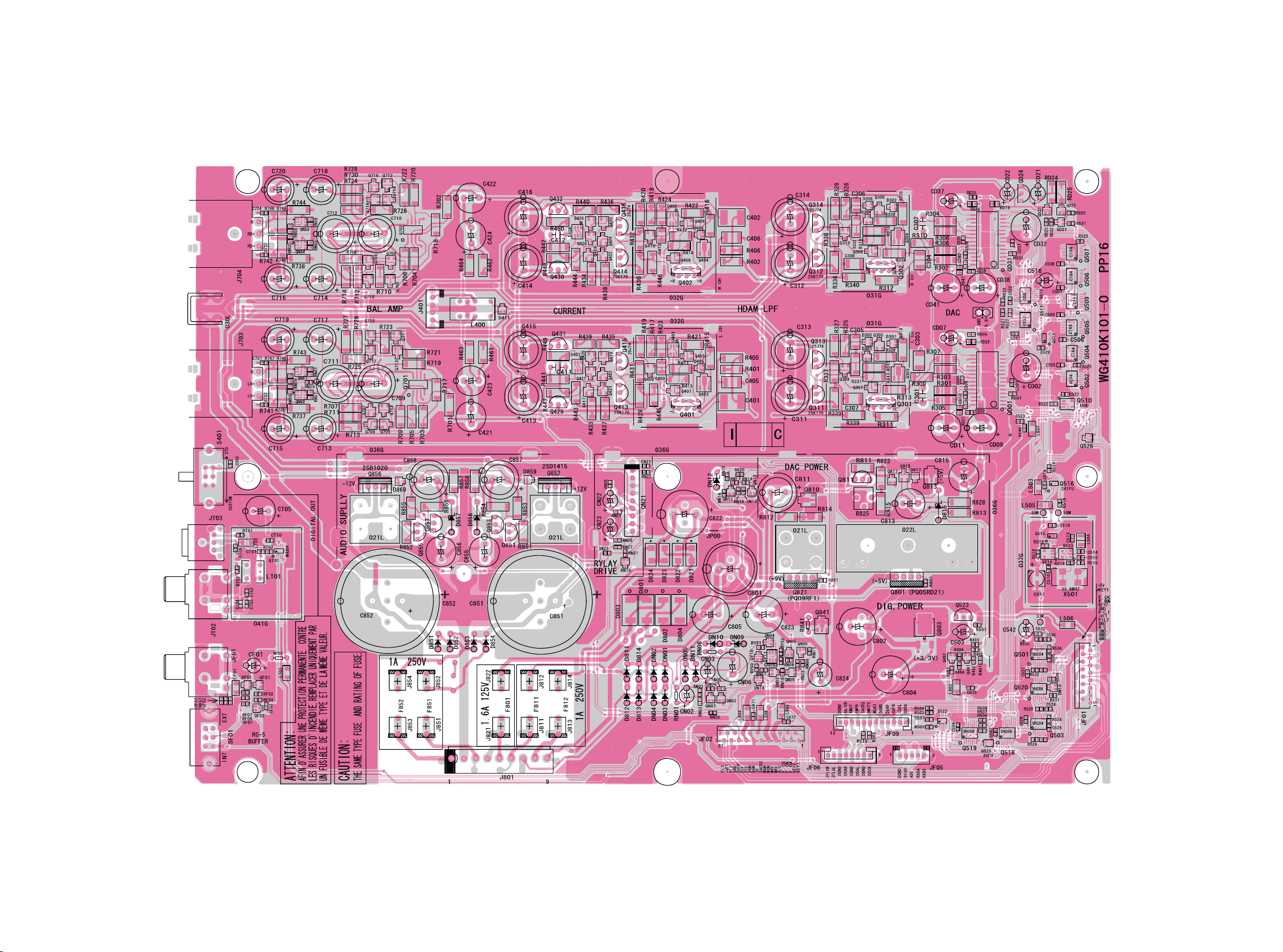

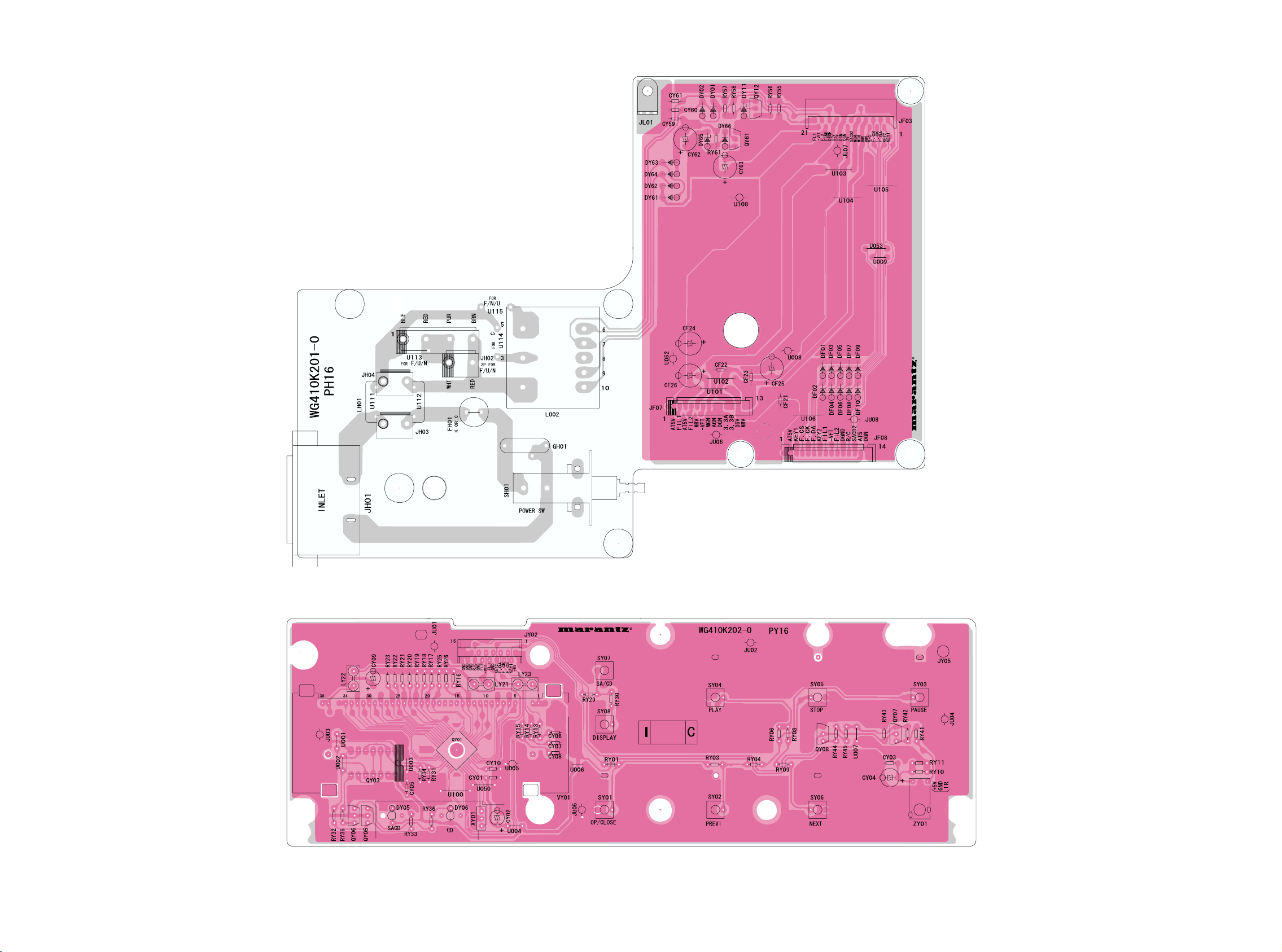

1.6 PARTS LOCATION

QN58

QN56

QN57

QN55

Q716 Q712

Q718 Q714

Q702

Q708 Q704

Q710 Q706

Q715 Q711

Q717 Q713

Q701

Q707 Q703

Q709 Q705

Q432 Q416

Q426 Q420

Q428 Q424

Q418 Q422

Q430 Q414

Q431 Q415

Q425 Q419

Q427 Q423

Q417 Q421

Q429 Q413

Q410 Q406

Q408 Q404

Q402

Q409 Q405

Q407 Q403

Q401

Q314

Q312

Q313

Q311

Q310 Q308 Q304

Q302

Q305 Q303

Q309 Q307 Q301

QD24 - QD21 Q507

QD31 Q506

Q509

Q512 Q505

Q504

Q511 Q502

QD01 Q517 Q510 Q526

QF01 QT01

QF02

Q856 Q857 Q853 Q852

Q855 Q851 QN21

QN12 QN13 Q810 Q811 Q817 Q815 Q813

Q821 Q801

QN04 QN05 Q492 Q491

QY10 QN06

QY11 QN03

QN09

QN01 QN02

1-19 1-20

Q516

Q515

Q514 Q513

Q501

Q520

Q503

Page 14

PH16

QY61 QY12

PY16

QY05 QY03

QY06

QY01 QY08

1-21 1-22

QY07

Page 15

1.7 ELECTRICAL ADJUSTMENTS

. Adjustment the Voltage of DAC (CS4397)

.Purpose

Set the Voltage of Audio part CS4397(QD01, QD31).

Adjustment point : R825(2.2Kohm)

Test point : J800

Equipment : Digital Multi Meter(DC voltage)

.Adjust the voltage at that status 5.4V to 5.5V by the trim

resister R825.

.If there incorrect adjust, the unit shouls be defective of

DISTORTION and AUDIO OUT PUT Voltage.

QD01/QD31(CS4397)

Fig-1 and Fig-2 chart are condition for DAC and pin of IC.

Select the CD/SACD mode by Fig-1 and Fig-2

Note

1. Set the CMOD of SACD(12pin=H)

2. When replay CD disc, A frequency of 44.1KHz input CMOD

3. The master CLK(192/384fs) for MCLK change by mode.

1-23

Page 16

1.8 IC DATA

QD01/QD31 CS4397

Block Diagram

SCLK

LRCK

SDATA

SERIAL INTERFACE

AND FORMAT SELECT

SOFT MUTE

DE-EMPHASIS

FILTER

Pin Configuration

MCLK

3.3 V

Digital

CLOCK

DIVIDER

M3 M2

M4

(AD0/CS)

(AD1/CDIN) (SCL/CCLK)

+

Mode

Select

(Control Po rt)

Audio

Data

Processor

External Clock

INTERPOLATION

FILTER

INTERPOLATION

FILTER

HARDWARE MODE CONTROL

(CONTROL POR T)

M0

M1

(SDA/CDOUT)

7

VD

5

M0 (SDA/CDOUT)

14

M1 (GND)

4

M2 (SCL/CCLK)

3

M3 (AD1/CDIN)

2

M4 (AD0/CS)

16

C/H

12

LRCK

11

SCLK

13

SDATA

15

MUTE

1

RST

10

MCLK

VD

CS4397

DGND

6

MULTI-BIT

DS

MODULATOR

MULTI-BIT

DS

MODULATOR

RESET MUTEC MUTE

8

22

VREF

FILT+

FILT-

CMOUT

AOUTL-

AOUTL+

MUTEC

AOUTR-

AOUTR+

AGND

21

VA

189

DYNAMIC

ELEMEN T

MATCHING

LOGIC

DYNAMIC

ELEMEN T

MATCHING

LOGIC

28

27

26

25

24

23

17

19

20

SWITCHED

CAPACITOR-DAC

AND FILTER

SWITCHED

CAPACITOR-DAC

AND FILTER

VOLTAGE REFERENCE

VREF CMOUTFILT-

FILT+

+

Analog

Conditioning

Analog

Conditioning

+5.5V

Analog

+

+

AOUTL+

AOUTL-

AOUTR+

AOUTR-

+5.5/3.5V

Analog

Q801

PQ05RD21

PQ15RW11

&

PQ09RF1

Q821

Pin Configuration

23

4

1

1 DC input(Vin)

2 DC output(Vo)

3 GND

4 Output voltage adjustment

terminal(Vadj)

1-24

1

Input

Block Diagram

Specific IC

3

GND

2

Output

4

Output voltage

adjustment terminal

Page 17

TA7317P(QN21)

CS4397

Pin Function

No. Pin Name I/O Description

1 RST I Reset input (Low active)

2 M4(AD0/CS) I See Fig-1

3 M3(AD1/CDIN) I See Fig-1

4 M2(SCL/CCLK)) I See Fig-1

5 M0(SDA/CDOUT) I/O See Fig-1

6 DGND Digital ground

7 VD Digital power supply +3.3V

8 VD Digital power supply +3.3V

9 DGND Digital ground

10 MCLK I Master clock

PCM mode:384Fs(16.9344MHz)

DSD mode:192Fs (8.4672MHz/16.9344MHz)

11 SCLK I Serial data clock

12 LRCK(PCM) I PCM mode:Left/Right channel clock(44.1KHz)

CLKMODE(DSD) I DSD mode:Select H(3.3V)

13 SDATA(PCM) I PCM mode:Serial audio data

DSD_L(DSD)

14 M1(PCM) I PCM mode:(Low)

DSD_R(DSD) DSD mode:Direct Stream Digital audio data (Right)

15 MUTE I Mute input (Low active)

16 C/H I Control port (H) /Hardware (L) mode select

17 MUTEC O Mute control (Low active)

18 AGND Analog ground

19 AOUTR- O Right channel negative Analog out

20 AOUTR+ O Right channel positive Analog out

21 AND Analog ground

22 VA Analog power supply +5.5V

23 AOUTL+ O Left channel positive Analog out

24 AOUTL- O Left channel negative Analog out

25 CMOUT O Common mode voltage

26 FILT- I Reference ground

27 FILT+ O Reference filter

28 VREF Voltage reference input

DSD mode:Direct Stream Digital audio data (Left)

1-25

Page 18

1.9 EXPLODED VIEW AND PARTS LIST

VERS.

POS.

COLOR

NO

001B /C1G

/S1G

/U1G

001B /F1N FRONT PANEL ASSY GOLD

001B /U1B FRONT PANEL ASSY BLACK

002B /C1G

/S1G

/U1G

002B /F1N FRONT PANEL GOLD

002B /U1B FRONT PANEL BLACK 410K248010

003B /C1G

/S1G

/U1G

003B /F1N 4822 426 10497 ESCUTCHEON GOLD 269J063110

003B /U1B 4822 426 10496 ESCUTCHEON BLACK 269J063010

005B GOLD 4822 381 12016 LENS IR GOLD 256J355030

005B BLACK 4822 381 12015 LENS IR BLACK 256J355040

006B GOLD RING GOLD NO.4 410K353120

006B BLACK RING BLACK NO.1 410K353010

007B SPRING FOR RING 410K115010

008B GOLD 9965 000 01554 BADGE MNTZ GOLD 313J251110

008B BLACK 9965 000 01553 BADGE MNTZ BLACK 313J251010

009B WINDOW 410K158010

010B GOLD BUSHING POWER/TRAY

010B BLACK BUSHING POWER/TRAY

012B GOLD BUSHING FL/PLAY BUTTON

012B BLACK BUSHING FL/PLAY BUTTON

014B INDICATOR SACD LOGO 410K265010

015B INDICATOR SACD/CD LENS 410K265020

016B LENS SACD/CD 392K355020

018B GOLD BUTTON POWER GOLD 410K270110

018B BLACK BUTTON POWER BLACK 410K270010

019B GOLD BUTTON PLAY/STOP GOLD 410K270120

019B BLACK BUTTON PLAY/STOP BLACK 410K270020

021B GOLD BUTTON OPEN/CLOSE GOLD 410K270130

021B BLACK BUTTON OPEN/CLOSE

028B BADGE SACD LOGO 410K251010

001D GOLD LID TOP GOLD 410K257110

001D BLACK LID TOP BLACK 410K257010

002D SHEET FOR TOP LID INSIDE 313J107010

005D GOLD 4822 502 14425 SCREW FOR TOP LID 323S010020

005D BLACK 4822 502 21693 SCREW FOR TOP LID 323S010030

006D GOLD 4822 426 10499 SIDE PANEL GOLD 269J249110

006D BLACK 4822 426 10498 SIDE PANEL BLACK 269J249010

009D GOLD 4822 502 14425 SCREW FOR SIDE PANEL 323S010020

009D BLACK 4822 502 21693 SCREW FOR SIDE PANEL 323S010030

PART NO.

(PCS)

4822 426 10497 ESCUTCHEON GOLD 269J063110

DESCRIPTION

ASSY GOLD BLAST 410K248520

AIR

LAST

FRONT PANEL GOLD BLAST 410K248110

HAIR LINE

GOLD

BLACK

GOLD

BLACK

BLACK

PART NO.

(MJI)

410K248530

410K248510

410K248120

410K259110

410K259010

410K259120

410K259020

410K270030

VERS.

POS.

COLOR

NO

A001 GOLD MECHANISM SACD CDM-15M 392K304510

A001 BLACK MECHANISM SACD

L001 /C1 MAINS TRANSF. 110/220V TS46010040

L001 /F1 MAINS TRANSF. 100V TS46010010

L001 /S1 MAINS TRANSF.MAIN 230V TS46010020

L001 /U1 MAINS TRANSF.MAIN 120V TS46010030

W001 /C1G MAINS CORD CORDSET

W001 /F1N 4822 321 11337 MAINS CORD MITY

W001 /S1G MAINS CORD S PORE

W001 /U1B MAINS CORD UL/CSA

W001 /U1G MAINS CORD UL/CSA

001T /C1,/S1 USER GUIDE SA-14 410K851350

001T /F1 USER GUIDE SA-14 410K851110

001T /U1 USER GUIDE SA-14 410K851250

T100 UNIT KIT REMOTE

001S PACKING CASE 410K801010

002S CUSHION LEFT 410K809010

003S CUSION RIGHT 410K809020

006S PROTECTOR TRAY

PART NO.

(PCS)

DESCRIPTION

CDM-15MB

7A 250V

3P 12A 125V F

2P 10A 250V

10A 125V

10A 125V

PACKING

CONTROLLER RC-14SA

NOT STANDARD SPARE

PARTS

ESCUTCHEON

PART NO.

(MJI)

392K304520

ZC02009010

ZC01802080

ZC01804100

ZC01803100

ZC01803100

ZK410K0010

392K269010

004G LEG GOLD 163J057410

011G 9965 000 00588 POWER BUTTON LINK 376K121010

012G INSULATOR SHAFT

POWER BUTTON

001M SCREW MECHANISM 410K010010

002M GOLD ESCUTCHEON GOLD 392K063150

002M BLACK ESCUTCHEON BLACK 392K063050

003M ESCUTCHEON SACD LOGO 392K063160

410K120010

1-26

Page 19

1-27

1-28

Page 20

1.10 ELECTRICAL PARTS LIST

ASSIGNMENT OF COMMON PARTS CODES.

RESISTORS

R : 1) GD05 140, Carbon film fixed resistor, 5% 1/4W

R : 2) GD05 160, Carbon film fixed resistor, 5% 1/6W

Examples ;

Resistance value

0.1 001 10 100 1 k 102 100 k 104

0.5 005 18 180 2.7 k 272 680 k 684

1 010 100 101 10 k 103 1 M 105

6.8 068 390 391 22 k 223 4.7 M 475

Note : Please distinguish 1/4W from 1/6W by the shape of par ts

used actually.

CAPACITORS

C : CERAMIC CAP.

3) DD1 370, Ceramic capacitor

Examples ;

Tolerance (Capacity deviation)

±

Tolerance of COMMON PARTS handled here are as follows :

C : CERAMIC CAP.

Examples ;

C : 5) ELECTROLY CAP. ( ), 6) FILM CAP. ( )

Examples ;

Examples ;

NOTE

0.5 pF 5 pF .... 0.25 pF

Capacity value

0.5 pF .... 005 3 pF .... 030 100 pF .... 101

1.5 pF .... 015 47 pF .... 470 560 pF .... 561

4) DK16 300, High dielectric constant ceramic

Capacity value

100 pF .... 101 1000 pF .... 102 10000 pF .... 103

470 pF .... 471 2200 pF .... 222

5) EA

Capacity value

0.1 µF ....104 4.7 µF ....475 100 µF ....107

0.33 µF ....334 10 µF ....106 330 µF ....337

Working voltage

6) DF15 350 Plastic film capacitor

DF15 310 One-way type, Mylar 5% 50V

DF16 310 Plastic film capacitor

Capacity value

0.001 µF (1000 pF) ....... 102 0.1 µF .... 104

0.0018 µF ........................ 182 0.56 µF....564

0.01 µF ........................ 103 1 µF .... 105

0.015 µF ........................ 153

: 1) The above CODES ( R , R , C , C and

C ) are omitted on the schematic diagram in some

2) On the occasion, be confirmed the common parts on

3) Refer to “Common Parts List” for the other common

{

Resistance value

{

0.25 pF .... 0

±

0.5 pF .... 1

±5% .... 5

6 pF 10 pF .... 0.5 pF

12 pF 560 pF .... 5%

1 pF .... 010 10 pF .... 100 220 pF .... 221

{

{

1 µF....105 22 µF .... 226 1100 µF ....118

6.3V ....006 25V ....025

10V ....010 35V .... 035

16V ....016 50V .... 050

{

case.

the parts list.

parts (RI05, DD4, DK4).

Disc type

Temp.coeff.P350 N1000, 50V

Capacity value

Tolerance

±

±

±

capacitor

Disc type

Temp.chara. 2B4, 50V

Capacity value

10, Electrolytic capacitor

{

One-way lead type, Tolerance 20%

Working voltage

Capacity value

2200 µF ....228

One-way type, Mylar 10% 50V

Capacity value

±

±

NOTE ON SAFETY FOR FUSIBLE RESISTOR :

The suppliers and their type numbers of fusible resistors

are as follows;

1. KOA Corporation

Part No. (MJI) Type No. (KOA) Description

NH05 140 RF25S J ( 5% 1/4W)

NH05 120 RF50S J ( 5% 1/2W)

NH85 110 RF73B2A J ( 5% 1/10W)

NH95 140 RF73B2E J ( 5% 1/4W)

2. Matsushita Electronic Components Co., Ltd

Part No. (MJI) Type No. (MEC) Description

NF05 140 ERD-2FCJ ( 5% 1/4W)

RF05 140

NF02 140

RF02 140

Examples ;

{

Resistance value

ERD-2FCG

{

Resistance value

Resistance value

0.1 001 10 100 1 k 102 100 k 104

0.5 005 18 180 2.7 k 272 680 k 684

1 010 100 101 10 k 103 1 M 105

6.8 068 390 391 22 k 223 4.7 M 475

{

( 2% 1/4W)

±

±

±

±

Resistance value

(0.1 10 k )

±

±

{

Resistance value

ABBREVIATION AND MARKS

ANT. : ANTENNA BATT. : BATTERY

CAP. : CAPACITOR CER. : CERAMIC

CONN. : CONNECTING DIG. : DIGITAL

HP : HEADPHONE MIC. : MICROPHONE

µ-PRO : MICROPROCESSOR REC. : RECORDING

RES. : RESISTOR SPK : SPEAKER

SW : SWITCH TRANSF. : TRANSFORMER

TRIM. : TRIMMING TRS. : TRAMSISTOR

VAR. : VARIABLE X’TAL : CRYSTAL

±

NOTE ON SAFETY :

Symbol Fire or electrical shock hazard. Only original

parts should be used to replaced any part marked with

symbol

than original type), may increase risk of fire or electrical

shock hazard.

. Any other component substitution (other

VERS.

POS.

COLOR

NO

CF24 4822 124 90364 ELECT 220

CF26 4822 124 90364 ELECT 220

CY60 4822 122 40588 CER. 0.022

CY61 4822 122 40588 CER. 0.022

CY62 4822 124 90355 ELECT 100

CY63 4822 124 41536 ELECT 100

R

DF01

DF10

DY01 4822 130 82421 DIODE 1D3 1A/200V HD20002710

DY02 4822 130 82421 DIODE 1D3 1A/200V HD20002710

DY61

DY64

DY65 4822 130 80116 ZENER DIODE 24V HD32401000

DY66 4822 130 32362 DIODE 1SS176 MA165 1SS254

QY12 4822 130 60839 TRS. 2SC2458 (Y GR) HT324582B0

QY61 4822 130 42715 TRS. 2SA1048 2SA933S

FH01 /C1,/S1,

/U1

GH01 4822 121 43732 FILM 0.01 F M 250V AC DF77103500

JF03 JACK 21FE-ST-VK-N YJ07020170

JH01 JACK MAINS INLET M1818-A YJ04002510

L002 /C1,/S1 4822 146 10891 MAINS TRANSF. SUB 115/230V TS13517060

L002 /F1 MAINS TRANSF.SUB 100V TS13517050

L002 /U1 MAINS TRANSF.SUB 120V TS13517070

SH01 4822 276 13364 PUSH SWITCH SDDLD1

CD01 4822 126 11687 CER. 0.1

CD02 4822 124 90354 ELECT 100

CD05 4822 126 11687 CER. 0.1

CD06 4822 126 11687 CER. 0.1

CD07 4822 124 22237 ELECT 10

CD08 4822 124 23514 ELECT 100

CD09 4822 126 11687 CER. 0.1

CD10 4822 126 11687 CER. 0.1

CD11 4822 124 23514 ELECT 100

CD21 4822 124 90352 ELECT 10

CD22 4822 124 90353 ELECT 100

CD31 4822 126 11687 CER. 0.1

CD32 4822 124 90354 ELECT 100

CD35 4822 126 11687 CER. 0.1

CD36 4822 126 11687 CER. 0.1

CD37 4822 124 22237 ELECT 10

CD38 4822 124 23514 ELECT 100

CD39 4822 126 11687 CER. 0.1

CD40 4822 126 11687 CER. 0.1

CD41 4822 124 23514 ELECT 100

PART NO.

(PCS)

4822 130 32362 DIODE 1SS176 MA165 1SS254

4822 130 82421 DIODE 1D3 1A/200V HD20002710

4822 252 11189 FUSE T2.5A/250V TR5 N

DESCRIPTION

PH16-POWER SW/SUB TRANS

CIRCUIT BOARD

PH16-CAPACITORS

F M 16V OA22701620

F M 16V OA22701620

F 20% DA17223110

F 20% DA17223110

F M 50V OA10705020

F M 35V OA10703520

PH16-RESISTORS(COMMON)

CARBON FILM FIXED RES.

5% 1/6W : RY55-RY58 RY61

PH16-SEMICONDUCTORS

30V 0.1A

30V 0.1A

2SA1267

PH16-MISCELLANEOUS

O.19372

POWER TV-3

PP16-MAIN/DAC/AUDIO

CIRCUIT BOARD

PP16-CAPACITORS

F +80% -20% 25V DK98104200

F M 16V OA10701620

F +80% -20% 25V DK98104200

F +80% -20% 25V DK98104200

F 16V OA10601650

F 16V OA10701650

F +80% -20% 25V DK98104200

F +80% -20% 25V DK98104200

F 16V OA10701650

F M 16V OA10601620

F M 10V OA10701020

F +80% -20% 25V DK98104200

F M 16V OA10701620

F +80% -20% 25V DK98104200

F +80% -20% 25V DK98104200

F 16V OA10601650

F 16V OA10701650

F +80% -20% 25V DK98104200

F +80% -20% 25V DK98104200

F 16V OA10701650

PART NO.

(MJI)

HD20002000

HD20002000

HT10001000

FS20250200

SP01011990

VERS.

POS.

COLOR

NO

CF01 4822 124 90352 ELECT 10 F M 16V OA10601620

CF02 4822 126 11687 CER. 0.1

CF51 4822 126 11687 CER. 0.1

CF52 4822 126 11568 CER. 470pF

CN02 4822 124 41543 ELECT 1

CN03 4822 124 90352 ELECT 10

CN06 4822 124 41541 ELECT 470

CN13 4822 126 11687 CER. 0.1

CN21 4822 126 11567 CER. 0.022

CN22 4822 124 90357 ELECT 2.2

CN23 4822 124 22274 ELECT 4.7

CT01 4822 126 11687 CER. 0.1

CT02 4822 126 11685 CER. 4700 pF

CT03 4822 126 12339 CER. 2200pF

CT04 4822 126 11687 CER. 0.1

CT05 4822 124 80119 ELECT 100

CT06 4822 126 11687 CER. 0.1

CT10 4822 126 11687 CER. 0.1

C301 FILM 1800pF

C302 FILM 1800pF

C303 MICA CHIP 390pF

C304 MICA CHIP 390pF

C305 4822 123 30422 MICA CHIP 33pF 500WV DF95330500

C306 4822 123 30422 MICA CHIP 33pF 500WV DF95330500

C307 MICA CHIP 120pF 500WV DF95121500

C308 MICA CHIP 120pF 500WV DF95121500

C311 /C1,/S1 4822 124 80958 ELECT 470

C311 /F1,/U1 4822 124 11953 ELECT 470

C312 /C1,/S1 4822 124 80958 ELECT 470

C312 /F1,/U1 4822 124 11953 ELECT 470

C313 /C1,/S1 4822 124 80958 ELECT 470

C313 /F1,/U1 4822 124 11953 ELECT 470

C314 /C1,/S1 4822 124 80958 ELECT 470

C314 /F1,/U1 4822 124 11953 ELECT 470

C355 4822 126 11687 CER. 0.1

C401 MICA CHIP 1200pF 100WV DF95122510

C402 MICA CHIP 1200pF 100WV DF95122510

C405 4822 123 30362 MICA CHIP 560pF 100WV DF95561510

C406 4822 123 30362 MICA CHIP 560pF 100WV DF95561510

C409 4822 123 30422 MICA CHIP 33pF 500WV DF95330500

C410 4822 123 30422 MICA CHIP 33pF 500WV DF95330500

C411 9965 000 01564 FILM 680pF

C412 9965 000 01564 FILM 680pF

C413 /C1,/S1 4822 124 80958 ELECT 470

C413 /F1,/U1 4822 124 11953 ELECT 470

C414 /C1,/S1 4822 124 80958 ELECT 470

C414 /F1,/U1 4822 124 11953 ELECT 470

C415 /C1,/S1 4822 124 80958 ELECT 470

C415 /F1,/U1 4822 124 11953 ELECT 470

C416 /C1,/S1 4822 124 80958 ELECT 470

C416 /F1,/U1 4822 124 11953 ELECT 470

C421

C424

C501 4822 126 11687 CER. 0.1

C502 4822 126 11687 CER. 0.1

C503 4822 124 22274 ELECT 4.7

C504

C510

C511 4822 124 11131 TANTAL CHIP 47

C513 5322 126 11578 CER. 1000pF

C514 4822 126 11663 CER. 12pF

C515 4822 126 11663 CER. 12pF

PART NO.

(PCS)

4822 124 80123 ELECT 220 F 16V OA22701640

4822 126 11687 CER. 0.1 F +80% -20% 25V DK98104200

DESCRIPTION

F +80% -20% 25V DK98104200

F +80% -20% 25V DK98104200

10% 50V DK96471300

F 50V OA10505020

F M 16V OA10601620

F M 35V OA47703520

F +80% -20% 25V DK98104200

F 10% 25V DK96223200

F M 50V OA22505020

F M 50V OA47505020

F +80% -20% 25V DK98104200

10 % 50V DK96472300

10% 50V DK96222300

F +80% -20% 25V DK98104200

F 25V OA10702540

F +80% -20% 25V DK98104200

F +80% -20% 25V DK98104200

5% 160V OF55182550

5% 160V OF55182550

5% DF95391500

5% DF95391500

F 16V OA47701640

F M 16V OA47701650

F 16V OA47701640

F M 16V OA47701650

F 16V OA47701640

F M 16V OA47701650

F 16V OA47701640

F M 16V OA47701650

F +80% -20% 25V DK98104200

5% 100V OF55681540

5% 100V OF55681540

F 16V OA47701640

F M 16V OA47701650

F 16V OA47701640

F M 16V OA47701650

F 16V OA47701640

F M 16V OA47701650

F 16V OA47701640

F M 16V OA47701650

F +80% -20% 25V DK98104200

F +80% -20% 25V DK98104200

F M 50V OA47505020

F 6.3V EY47600620

10% B 50V DK96102300

5 % 50V DD95120300

5 % 50V DD95120300

PART NO.

(MJI)

1-29 1-30

Page 21

POS.

NO

VERS.

COLOR

PART NO.

(PCS)

DESCRIPTION

PART NO.

(MJI)

POS.

NO

VERS.

COLOR

PART NO.

(PCS)

DESCRIPTION

PART NO.

(MJI)

C516 4822 124 41539 ELECT 47 F M 16V OA47601620

C518

4822 126 11687 CER. 0.1 F +80% -20% 25V DK98104200

C523

C524 4822 126 13303 CER. 1

C526 4822 126 13303 CER. 1

C527 4822 126 11687 CER. 0.1

C528 4822 126 11687 CER. 0.1

C532 4822 126 11687 CER. 0.1

C535 4822 126 13303 CER. 1

C536 4822 126 13303 CER. 1

C537 4822 126 11687 CER. 0.1

C542 4822 124 41539 ELECT 47

C709 /C1,/S1 4822 124 80958 ELECT 470

C709 /F1,/U1 4822 124 11953 ELECT 470

C710 /C1,/S1 4822 124 80958 ELECT 470

C710 /F1,/U1 4822 124 11953 ELECT 470

C711 /C1,/S1 4822 124 80958 ELECT 470

C711 /F1,/U1 4822 124 11953 ELECT 470

C712 /C1,/S1 4822 124 80958 ELECT 470

C712 /F1,/U1 4822 124 11953 ELECT 470

C713

4822 124 90365 ELECT 220 F M 25V OA22702520

C720

C721

/C1,/S1/U14822 126 11759 CER. 100pF

C724

C801 4822 124 22243 ELECT 6800

C802 4822 124 80773 ELECT 3300

C804 4822 124 80773 ELECT 3300µF

C805 4822 124 40723 ELECT 2200

C811 4822 124 90051 ELECT 220

C813 /F1N 4822 124 22238 ELECT 100

C815 4822 124 22238 ELECT 100

C822 4822 124 80582 ELECT 4700

C823 4822 124 40723 ELECT 2200

C824 4822 124 90371 ELECT 470

C851 ELECT 4700

C852 ELECT 4700

C855 /C1,/S1 4822 124 80119 ELECT 100

C855 /F1,/U1 4822 124 22238 ELECT 100

C856 /C1,/S1 4822 124 80119 ELECT 100

C856 /F1,/U1 4822 124 22238 ELECT 100

C857 4822 124 22242 ELECT 470

C858 4822 124 22242 ELECT 470

C870 4822 126 11687 CER. 0.1

C871 4822 126 11687 CER. 0.1

C872 4822 126 11687 CER. 0.1

PP16-RESISTORS

RD01 4822 051 30223 CHIP 22k

RD05 4822 051 30102 CHIP 1k

!RD19 4822 117 10145 FUSIBLE 3.3

RD20 4822 051 30472 CHIP 4.7k

RD21 4822 051 30472 CHIP 4.7k Ω

RD22 4822 051 30472 CHIP 4.7k

RD23 4822 051 30102 CHIP 1k

RD24 1.15k

RD25 3.01k

RD31 4822 051 30223 CHIP 22k

RD35 4822 051 30102 CHIP 1k

RF01 4822 051 30472 CHIP 4.7k

RF02 4822 051 30473 CHIP 47k

RF04 4822 051 30103 CHIP 10k

RF06 4822 051 30222 CHIP 2.2k

RF07 4822 051 30103 CHIP 10k

F +80% -20% 10V DK98105200

F +80% -20% 10V DK98105200

F +80% -20% 25V DK98104200

F +80% -20% 25V DK98104200

F +80% -20% 25V DK98104200

F +80% -20% 10V DK98105200

F +80% -20% 10V DK98105200

F +80% -20% 25V DK98104200

F M 16V OA47601620

F 16V OA47701640

F M 16V OA47701650

F 16V OA47701640

F M 16V OA47701650

F 16V OA47701640

F M 16V OA47701650

F 16V OA47701640

F M 16V OA47701650

5% 50V DD95101300

F 20% 16V OA68801620

F 20% 6.3V OA33800620

20% 6.3V OA33800620

F 16V OA22801620

F M 25V OA22702550

F 20% 25V OA10702550

F 20% 25V OA10702550

F 20% 16V OA47801620

F 16V OA22801620

F 20% 10V OA47701020

F M 35V OB47803520

F M 35V OB47803520

F 25V OA10702540

F 20% 25V OA10702550

F 25V OA10702540

F 20% 25V OA10702550

F M 25V OA47702550

F M 25V OA47702550

F +80% -20% 25V DK98104200

F +80% -20% 25V DK98104200

F +80% -20% 25V DK98104200

5% 1/16W NN05223610

5% 1/16W NN05102610

5% 1/10W NH85033110

5% 1/16W NN05472610

5% 1/16W NN05472610

5% 1/16W NN05472610

5% 1/16W NN05102610

1% 1/4W GM11411510

1% 1/4W GM11430110

5% 1/16W NN05223610

5% 1/16W NN05102610

5% 1/16W NN05472610

5% 1/16W NN05473610

5% 1/16W NN05103610

5% 1/16W NN05222610

5% 1/16W NN05103610

RF51 4822 117 12139 CHIP 22

RN01 /C1,/S1 4822 130 80132 ZENER DIODE 3.9V HD30391000

RN02 4822 117 11977 CHIP 3.9M

RN03 /C1,/S1 4822 116 83819 CHIP 18k

RN03 /F1,/U1 4822 051 30103 CHIP 10k

RN04 4822 051 30473 CHIP 47k

RN05 4822 051 30103 CHIP 10k

RN07 4822 051 30223 CHIP 22k

RN08 4822 051 30472 CHIP 4.7k

RN09 4822 051 30223 CHIP 22k

RN10 4822 051 30472 CHIP 4.7k

RN11 4822 051 30223 CHIP 22k

RN12 4822 051 30223 CHIP 22k

RN14 4822 051 30103 CHIP 10k

RN15 4822 051 30472 CHIP 4.7k

RN16 4822 051 30472 CHIP 4.7k

RN17 4822 051 30472 CHIP 4.7k

RN18 4822 051 30103 CHIP 10k

RN19 4822 051 30104 CHIP 100k

RN20 4822 051 30472 CHIP 4.7k

RN21 4822 051 30104 CHIP 100k

RN22 4822 051 30104 CHIP 100k

RN23 4822 051 30332 CHIP 3.3k

RN24 4822 051 30473 CHIP 47k

RN25 4822 051 30333 CHIP 33k

RN26 4822 051 30104 CHIP 100k

RN27 4822 051 30332 CHIP 3.3k

RN55

4822 111 90906 CHIP 2.2k 5% 1/10W NI05222110

RN62

RY50

4822 051 30223 CHIP 22k 5% 1/ 16W NN05223610

RY54

RT01 4822 051 30101 CHIP 100 5% 1/16W NN05101610

RT02 4822 051 30339 CHIP 33

RT03 4822 051 30759 CHIP 75

R301

2.26k 1% 1/4W GM11422610

R308

R309 562

R310 562

R311 3.32k

R312 3.32k

R313 1.62k

R314 1.62k

R315

R318

R319 68.1

R320 68.1

R325

R328

R329 33.2k

R330 33.2k

R331 100

R332 100

R335

R338

R339 4.42k

R340 4.42k

R401 2.26k

R402 2.26k

5% 1/16W NN05220610

5% 1/16W NN05395610

5% 1/16W NN05183610

5% 1/16W NN05103610

5% 1/16W NN05473610

5% 1/16W NN05103610

5% 1/16W NN05223610

5% 1/16W NN05472610

5% 1/16W NN05223610

5% 1/16W NN05472610

5% 1/16W NN05223610

5% 1/16W NN05223610

5% 1/16W NN05103610

5% 1/16W NN05472610

5% 1/16W NN05472610

5% 1/16W NN05472610

5% 1/16W NN05103610

5% 1/6W NN05104610

5% 1/16W NN05472610

5% 1/16W NN05104610

5% 1/16W NN05104610

5% 1/16W NN05332610

5% 1/16W NN05473610

5% 1/16W NN05333610

5% 1/16W NN05104610

5% 1/16W NN05332610

5% 1/16W NN05330610

5% 1/16W NN05750610

1% 1/4W GM11456200

1% 1/4W GM11456200

1% 1/4W GM11433210

1% 1/4W GM11433210

1% 1/4W GM11416210

1% 1/4W GM11416210

121 1% 1/4W GM11412100

1% 1/4W GM114681G0

1% 1/4W GM114681G0

562 1% 1/4W GM11456200

1% 1/4W GM11433220

1% 1/4W GM11433220

1% 1/4W GM11410000

1% 1/4W GM11410000

10 1% 1/4W GM114100G0

1% 1/4W GM11444210

1% 1/4W GM11444210

1% 1/4W GM11422610

1% 1/4W GM11422610

1-31

Page 22

POS.

NO

VERS.

COLOR

PART NO.

(PCS)

DESCRIPTION

PART NO.

(MJI)

POS.

NO

VERS.

COLOR

PART NO.

(PCS)

DESCRIPTION

PART NO.

(MJI)

R405 3.32k 1% 1/4W GM11433210

R406 3.32k

R411

R414

R415 68.1

R416 68.1

R417

R420

R421 33.2k

R422 33.2k

R423 46.4

R424 46.4

R429

R432

R433

R440

R441 46.4

R442 46.4

R443 121

R444 121

R445 274

R446 274

R447

R450

R461 100k

R462 100k

R463 100

R464 100

R491 4822 051 30223 CHIP 22k

R492 4822 051 30101 CHIP 100

R493 4822 117 12139 CHIP 22

R494 4822 051 30223 CHIP 22k

R495 4822 051 30224 CHIP 220k

R496 4822 051 30102 CHIP 1k

R497 4822 051 30223 CHIP 22k

R501 4822 051 30684 CHIP 680k

R502 4822 051 30109 CHIP 10

R503 4822 051 30109 CHIP 10

R504 4822 051 30109 CHIP 10

R506 4822 051 30109 CHIP 10

R507 4822 051 30109 CHIP 10

R508 4822 051 30109 CHIP 10

R509 4822 051 30101 CHIP 100

R510 4822 051 30101 CHIP 100

R514 4822 117 12968 CHIP 820

R515 4822 051 30334 CHIP 330k

R516 4822 051 30109 CHIP 10

R517 4822 051 30109 CHIP 10

R518 4822 051 30479 CHIP 47

R519 4822 051 30101 CHIP 100

R520 4822 051 30479 CHIP 47

R521 4822 051 30479 CHIP 47

R522 4822 051 30479 CHIP 47

R523 4822 051 30472 CHIP 4.7k

R525 4822 051 30101 CHIP 100

R526 4822 051 30103 CHIP 10k

R527 4822 051 30101 CHIP 100

R528 4822 051 30103 CHIP 10k

R529 4822 051 30101 CHIP 100

R532 4822 051 30101 CHIP 100

R534 4822 051 30472 CHIP 4.7k

R535 4822 051 30103 CHIP 10k

R536 4822 051 30103 CHIP 10k

1% 1/4W GM11433210

121 1% 1/4W GM11412100

1% 1/4W GM114681G0

1% 1/4W GM114681G0

562 1% 1/4W GM11456200

1% 1/4W GM11433220

1% 1/4W GM11433220

1% 1/4W GM114464G0

1% 1/4W GM114464G0

100 1% 1/4W GM11410000

274 1% 1/4W GM11427400

1% 1/4W GM114464G0

1% 1/4W GM114464G0

1% 1/4W GM11412100

1% 1/4W GM11412100

1% 1/4W GM11427400

1% 1/4W GM11427400

33.2 1% 1/4W GM114332G0

1% 1/4W GM11410030

1% 1/4W GM11410030

1% 1/4W GM11410000

1% 1/4W GM11410000

5% 1/16W NN05223610

5% 1/16W NN05101610

5% 1/16W NN05220610

5% 1/16W NN05223610

5% 1/16W NN05224610

5% 1/16W NN05102610

5% 1/16W NN05223610

5% 1/16W NN05684610

5% 1/16W NN05100610

5% 1/16W NN05100610

5% 1/16W NN05100610

5% 1/16W NN05100610

5% 1/16W NN05100610

5% 1/16W NN05100610

5% 1/16W NN05101610

5% 1/16W NN05101610

5% 1/16W NN05821610

5% 1/16W NN05334610

5% 1/16W NN05100610

5% 1/16W NN05100610

5% 1/16W NN05470610

5% 1/16W NN05101610

5% 1/16W NN05470610

5% 1/16W NN05470610

5% 1/16W NN05470610

5% 1/16W NN05472610

5% 1/16W NN05101610

5% 1/16W NN05103610

5% 1/16W NN05101610

5% 1/16W NN05103610

5% 1/16W NN05101610

5% 1/16W NN05101610

5% 1/16W NN05472610

5% 1/16W NN05103610

5% 1/16W NN05103610

R537 4822 051 30103 CHIP 10k

R540 4822 051 30473 CHIP 47k

R701

R704

R705 100

R706 100

R707

6.81k 1% 1/4W GM11468110

R710

R711

R714

R717

R720

R721 100

R722 100

R723

6.81k 1% 1/4W GM11468110

R726

R727

R730

R737 100k

R738 100k

R739

R742

R743 100k

R744 100k

R745

R748

R801 4822 051 30102 CHIP 1k

R811 100

R812 3.32k

R813 1.15k

R814 3.32k

R815 1.47k

R820 4822 051 30272 CHIP 2.7k

R821 4822 051 30102 CHIP 1k

R823 2.26k

R825 4822 100 11758 TRIMMING RH068 1KB 0.3

R828 1k

R851 100

R852 100

R853 2.74k

R854 3.32k

R855 2.74k

R856 3.32k

R857 3.32k

R858 3.32k

PP16-RESISTORS(COMMON)

R

DF51 4822 130 83715 CHIP DIODE 1SS301 DAN202U HZ21005000

DN01

DN05

DN09 4822 130 33948 ZENER DIODE 5.6V HD30561000

DN10 4822 130 32362 DIODE 1SS176 MA165 1SS254

CARBON FILM FIXED RES.

5% 1/6W : RF03

[RN01(/F1,/U1)] RN06 R841

PP16-SEMICONDUCTORS

DIODE 11EQS10 1A 100V HD20055100

30V 0.1A

5% 1/16W NN05103610

5% 1/16W NN05473610

10k 1% 1/4W GM11410020

1% 1/4W GM11410000

1% 1/4W GM11410000

33.2 1% 1/4W GM114332G0

10k 1% 1/4W GM11410020

1% 1/4W GM11410000

1% 1/4W GM11410000

33.2 1% 1/4W GM114332G0

1% 1/4W GM11410030

1% 1/4W GM11410030

100 1% 1/4W GM11410000

1% 1/4W GM11410030

1% 1/4W GM11410030

100 1% 1/4W GM11410000

5% 1/16W NN05102610

1% 1/4W GM11410000

1% 1/4W GM11433210

1% 1/4W GM11411510

1% 1/4W GM11433210

1% 1/4W GM11414710

5% 1/16W NN05272610

5% 1/16W NN05102610

1% 1/4W GM11422610

RA01021100

1% 1/6W GM11410010

1% 1/4W GM11410000

1% 1/4W GM11410000

1% 1/4W GM11427410

1% 1/4W GM11433210

1% 1/4W GM11427410

1% 1/4W GM11433210

1% 1/4W GM11433210

1% 1/4W GM11433210

HD20002000

1-32

Page 23

POS.

NO

VERS.

COLOR

PART NO.

(PCS)

DESCRIPTION

PART NO.

(MJI)

POS.

NO

VERS.

COLOR

PART NO.

(PCS)

DESCRIPTION

PART NO.

(MJI)

DN11 4822 130 32362 DIODE 1SS176 MA165 1SS254

30V 0.1A

DN12 4822 130 80132 ZENER DIODE 3.9V HD30391000

DN13 4822 130 83715 CHIP DIODE 1SS301 DAN202U HZ21005000

DN14 4822 130 83715 CHIP DIODE 1SS301 DAN202U HZ21005000

DN15 4822 130 83715 CHIP DIODE 1SS301 DAN202U HZ21005000

D301

4822 130 81324 CHIP DIODE 1SS302 HZ20018050

D306

D401 4822 130 81148 CHIP DIODE IMN10 ARRAY HZ20007210

D402 4822 130 81148 CHIP DIODE IMN10 ARRAY HZ20007210

D405 4822 130 81324 CHIP DIODE 1SS302 HZ20018050

D406 4822 130 81324 CHIP DIODE 1SS302 HZ20018050

D407 4822 130 81148 CHIP DIODE IMN10 ARRAY HZ20007210

D408 4822 130 81148 CHIP DIODE IMN10 ARRAY HZ20007210

D411 4822 130 83715 CHIP DIODE 1SS301 DAN202U HZ21005000

D801

CHIP DIODE NSQ03A02L HZ20009100

D804

D811

DIODE 11EQS10 1A 100V HD20055100

D814

D815 4822 130 31253 ZENER DIODE

HZ2CLL 2.4V

D817 4822 130 83715 CHIP DIODE 1SS301 DAN202U HZ21005000

D821

D824

D851

D854

D856 4822 130 33664 ZENER DIODE HZ6L 6.2V HD30021010

D857 4822 130 33664 ZENER DIODE HZ6L 6.2V HD30021010

D859 4822 130 83715 CHIP DIODE 1SS301 DAN202U HZ21005000

D869 4822 130 83715 CHIP DIODE 1SS301 DAN202U HZ21005000

QD01 IC CS4397 24BIT 192KHZ DAC HC10008880

QD21 4822 130 61541 CHIP TRS. 2SC4116 HX341162B0

QD22 4822 130 61541 CHIP TRS. 2SC4116 HX341162B0

QD23 4822 130 63598 CHIP TRS. 2SA1586 (O Y) HX115862A0

QD24 4822 130 43818 TRS. 2SC2878 (A B) HT328782A0

QD31 IC CS4397 24BIT 192KHZ DAC HC10008880

QF01 4822 130 63598 CHIP TRS. 2SA1586 (O Y) HX115862A0

QF02 4822 130 61541 CHIP TRS. 2SC4116 HX341162B0

QN01

QN04

QN05 4822 130 63598 CHIP TRS. 2SA1586 (O Y) HX115862A0

QN06 4822 130 63598 CHIP TRS. 2SA1586 (O Y) HX115862A0

QN09 4822 130 61541 CHIP TRS. 2SC4116 HX341162B0

QN12 4822 130 61541 CHIP TRS. 2SC4116 HX341162B0

QN13 4822 130 61541 CHIP TRS. 2SC4116 HX341162B0

QN21 4822 209 83312 IC TA7317P RELEY DRIVER IC HC10042050

QN55

QN58

QT01 IC TC7WHU04FU HC008005K0

QY10 4822 130 61541 CHIP TRS. 2SC4116 HX341162B0

QY11 4822 111 92195 SEMICON.COMP

Q301 4822 130 42843 F.E.T. 2SK389 (GR BL) HF203892A0

Q302 4822 130 42843 F.E.T. 2SK389 (GR BL) HF203892A0

Q303 4822 130 61425 CHIP TRS. 2SC2873 (Y) HX328731B0

4822 130 11513 CHIP DIODE RB161L-40

1A 40V

DIODE 11EQS10 1A 100V HD20055100

4822 130 61541 CHIP TRS. 2SC4116 HX341162B0

4822 130 63844 SEMICON.COMP HN1C03F(B) BA20016050

HN1A01F(Y GR)

HD20002000

HD30067010

HZ20057210

BA10011050

Q304 4822 130 61425 CHIP TRS. 2SC2873 (Y) HX328731B0

Q305

4822 130 63928 CHIP TRS. 2SA1312 (B) HX113121B0

Q308

Q309 4822 130 63929 CHIP TRS. 2SC3324 (B) HX333241B0

Q310 4822 130 63929 CHIP TRS. 2SC3324 (B) HX333241B0

Q311 5322 130 41844 F.E.T. 2SK170 V HF201701H0

Q312 5322 130 41844 F.E.T. 2SK170 V HF201701H0

Q313 4822 130 62649 F.E.T. 2SJ74 V HF100741H0

Q314 4822 130 62649 F.E.T. 2SJ74 V HF100741H0

Q401 4822 130 42843 F.E.T. 2SK389 (GR BL) HF203892A0

Q402 4822 130 42843 F.E.T. 2SK389 (GR BL) HF203892A0

Q403 4822 130 61425 CHIP TRS. 2SC2873 (Y) HX328731B0

Q404 4822 130 61425 CHIP TRS. 2SC2873 (Y) HX328731B0

Q405

4822 130 63928 CHIP TRS. 2SA1312 (B) HX113121B0

Q408

Q409 4822 130 63929 CHIP TRS. 2SC3324 (B) HX333241B0

Q410 4822 130 63929 CHIP TRS. 2SC3324 (B) HX333241B0

Q413 5322 130 41844 F.E.T. 2SK170 V HF201701H0

Q414 5322 130 41844 F.E.T. 2SK170 V HF201701H0

Q415 4822 130 62649 F.E.T. 2SJ74 V HF100741H0

Q416 4822 130 62649 F.E.T. 2SJ74 V HF100741H0

Q417 4822 130 63928 CHIP TRS. 2SA1312 (B) HX113121B0

Q418 4822 130 63928 CHIP TRS. 2SA1312 (B) HX113121B0

Q419 4822 130 63929 CHIP TRS. 2SC3324 (B) HX333241B0

Q420 4822 130 63929 CHIP TRS. 2SC3324 (B) HX333241B0

Q421

4822 130 63928 CHIP TRS. 2SA1312 (B) HX113121B0

Q424

Q425

4822 130 63929 CHIP TRS. 2SC3324 (B) HX333241B0

Q428

Q429 4822 130 43283 TRS. 2SC2705 (O Y) HT327052A0

Q430 4822 130 43283 TRS. 2SC2705 (O Y) HT327052A0

Q431 4822 130 42999 TRS. 2SA1145 (O Y) HT111452A0

Q432 4822 130 42999 TRS. 2SA1145 (O Y) HT111452A0

Q491 4822 130 61541 CHIP TRS. 2SC4116 HX341162B0

Q492 4822 130 61541 CHIP TRS. 2SC4116 HX341162B0

Q501 IC TC74VHC04FT HC008105K0

Q502 IC TC74VHC74FT HC005605K0

Q503 IC TC74VHC04FT HC008105K0

Q504

IC TC74VHC164FT HC006005K0

Q507

Q509 9965 000 04633 IC TC74VHC157FT HC005805K0

Q510 4822 209 32984 IC TC7SHU04F HC10427050

Q511 9965 000 04633 IC TC74VHC157FT HC005805K0

Q512 9965 000 04632 IC TC74VHC00FT HC005105K0

Q513 4822 209 32984 IC TC7SHU04F HC10427050

Q514 4822 209 32984 IC TC7SHU04F HC10427050

Q515 IC TC7WH74FU HC007905K0

Q516 IC TCWH241FU HC008305K0

Q517 IC TC7WH74FU HC007905K0

Q518 IC TC74VHC08FT HC008205K0

Q519 IC TC74VHC08FT HC008205K0

Q520 IC TC74VHC86FT HC008405K0

Q521 IC TS7S86FU HC10414050

Q522 IC TC7WHU04FU HC008005K0

Q523 4822 209 15921 IC RESET IC S-806D-Z HC10077530

Q526 4822 130 61541 CHIP TRS. 2SC4116 HX341162B0

Q701 4822 209 91175 IC NJM2114M HC10175090

Q702 4822 209 91175 IC NJM2114M HC10175090

Q703 4822 130 63928 CHIP TRS. 2SA1312 (B) HX113121B0

Q704 4822 130 63928 CHIP TRS. 2SA1312 (B) HX113121B0

1-33

Page 24

POS.

NO

VERS.

COLOR

PART NO.

(PCS)

DESCRIPTION

PART NO.

(MJI)

POS.

NO

VERS.

COLOR

PART NO.

(PCS)

DESCRIPTION

PART NO.

(MJI)

Q705

4822 130 63929 CHIP TRS. 2SC3324 (B) HX333241B0

Q708

Q709

4822 130 63928 CHIP TRS. 2SA1312 (B) HX113121B0

Q712

Q713

4822 130 63929 CHIP TRS. 2SC3324 (B) HX333241B0

Q716

Q717 4822 130 63928 CHIP TRS. 2SA1312 (B) HX113121B0

Q718 4822 130 63928 CHIP TRS. 2SA1312 (B) HX113121B0

Q801 IC PQ05RD21 5V 2A HC31905320

Q803 9965 000 03397 IC BA033FP HC96J33210

Q810 4822 130 43954 CHIP TRS. 2SD999 HX409992A0

Q811 4822 130 42836 F.E.T. 2SK246 (GR) HF202461C0

Q813 4822 130 43954 CHIP TRS. 2SD999 HX409992A0

Q815 4822 130 63929 CHIP TRS. 2SC3324 (B) HX333241B0

Q817 4822 130 61541 CHIP TRS. 2SC4116 HX341162B0

Q821 IC PQ09RF1 HC31909320

Q841 4822 130 43954 CHIP TRS. 2SD999 HX409992A0

Q851 4822 130 42836 F.E.T. 2SK246 (GR) HF202461C0

Q852 TRS. 2SD1415A HT41415100

Q853 4822 130 43233 TRS. 2SC2240 (GR BL) HT322402A0

Q855 4822 130 42836 F.E.T. 2SK246 (GR) HF202461C0

Q856 TRS. 2SB1020A HT21020100

Q857 4822 130 42949 TRS. 2SA970 (GR BL) HT109702A0

PP16-MISCELLANEOUS

FZ01 SERAMIC VIB. 432KHz

CSB432EB

F801 /C1,/S1 4822 070 31002 FUSE 1 A 250V BS LISTED FS10100850

F801 /F1,/U1 FUSE 1.6A 250V UL CSA FS10160350

F811 /C1,/S1 4822 253 30394 FUSE T315MA 250V

BS LISTED

F811 /F1,/U1 FUSE 1A 250V UL CSA FS10100350

F812 /C1,/S1 4822 070 38001 FUSE 800 MA 250V BS LISTED FS10080850

F812 /F1,/U1 FUSE 1A 250V UL CSA FS10100350

F851 /C1,/S1 4822 070 38001 FUSE 800 MA 250V BS LISTED FS10080850

F851 /F1,/U1 FUSE 1A 250V UL CSA FS10100350

F852 /C1,/S1 4822 070 38001 FUSE 800 MA 250V BS LISTED FS10080850

F852 /F1,/U1 FUSE 1A 250V UL CSA FS10100350

JF51 4822 267 41009 TERMINAL RCA PIN JACK 2P YT02020890

JT02 4822 290 81638 TERMINAL RCA PIN JACK 1P YT02010790

JT03 4822 267 31369 OPT. CONNECTOR GP1F32T YJ15000090

J403 4822 290 61214 TERMINAL RCA PIN JACK 1P

GOLD

J404 4822 290 61214 TERMINAL RCA PIN JACK 1P

GOLD

J703 4822 265 20653 JACK XLR CANON PLUG YJ01003810

J704 4822 265 20653 JACK XLR CANON PLUG YJ01003810

LF01 4822 158 60654 FERRITE CORE BLM31A02 FC90030070

LT01 4822 142 60422 PULSE TRANSF. TP41042030

LT02 4822 158 60654 FERRITE CORE BLM31A02 FC90030070

LT03 4822 158 60654 FERRITE CORE BLM31A02 FC90030070

L400 4822 280 10353 RELAY NA-9-WK DC9V LY20090090

L503 4822 158 60654 FERRITE CORE BLM31A02 FC90030070

L504 CHIP INDUCTANCE

3.3

H NL322522

L505

4822 158 60654 FERRITE CORE BLM31A02 FC90030070

L508

L803 4822 158 60654 FERRITE CORE BLM31A02 FC90030070

L804 4822 158 60654 FERRITE CORE BLM31A02 FC90030070

FQ04323030

FS10031850

YT02010820

YT02010820

LU12332010

L805 4822 158 60654 FERRITE CORE BLM31A02 FC90030070

SF01 4822 277 21559 SLIDE SWITCH SS02021150

S401 4822 277 21559 SLIDE SWITCH SS02021150

X501 4822 242 10818 CRYSTAL 33.8688MHz JX33001380

ZY01 PHOTO UNIT RPM6936-H4 HW10008210

PY16-FRONT CIRCUIT BOARD

PY16-CAPACITORS

CF21 4822 126 11558 CER. 0.1

CF22 4822 126 11558 CER. 0.1

CF23 4822 126 11558 CER. 0.1

CY01 4822 126 11558 CER. 0.1

CY02 4822 124 90352 ELECT 10

CY03 4822 126 11558 CER. 0.1

CY04 4822 124 90354 ELECT 100

CY05 4822 126 11558 CER. 0.1

CY06 4822 126 13089 CER. 33pF

CY07 4822 126 13089 CER. 33pF

CY08 4822 126 13089 CER. 33pF

CY09 4822 124 22274 ELECT 4.7

CY10 4822 126 11558 CER. 0.1

PY16-RESISTORS(COMMON)

R

DY05 4822 130 80326 L.E.D. LT3D8B RED HI10062320

DY06 4822 130 80326 L.E.D. LT3D8B RED HI10062320

DY11 4822 130 10667 ZENER DIODE 4.7V HD30471000

QY01 IC MN12510F FTD DRIVER HC10171020

QY03 4822 209 63184 IC LC74HC86 HC708600B0

QY05 4822 130 42715 TRS. 2SA1048 2SA933S

QY06 4822 130 42715 TRS. 2SA1048 2SA933S

QY07 4822 130 42715 TRS. 2SA1048 2SA933S

QY08 4822 130 41947 TRS. 2SC2458 2SC1740S

JY02 JACK 15FE-ST-VK-N YJ07020110

LY21 FERRITE CORE

LY22 FERRITE CORE

LY23 FERRITE CORE

SY01

4822 276 13537 PUSH SWITCH SKHVBF

SY08

VY01 4822 135 00194 DISPLAY UNIT 10-BT-196GK HQ31004410

XY01 4822 242 72527 SERAMIC VIB. CST4.00MGW FQ04004030

CARBON FILM FIXED RES.

5% 1/6W : RY03 RY04 RY06

RY08-RY11 RY13-RY23 RY25

RY26 RY29-RY36 RY41-RY45

PY16-SEMICONDUCTORS

2SA1267

2SA1267

2SA1267

2SC3199

PY16-MISCELLANEOUS

BL02RN2-R62T2 BEAD

BL02RN2-R62T2 BEAD

BL02RN2-R62T2 BEAD

260GF RED

F Z 50V DA17104110

F Z 50V DA17104110

F Z 50V DA17104110

F Z 50V DA17104110

F M 16V OA10601620

F Z 50V DA17104110

F M 16V OA10701620

F Z 50V DA17104110

5% DA15330110

5% DA15330110

5% DA15330110

F M 50V OA47505020

F Z 50V DA17104110

HT10001000

HT10001000

HT10001000

HT30001000

FC90050130

FC90050130

FC90050130

SP01012030

1-34

Page 25

Service

CDM-15M

CDM-15MB

Manual

SACD Module

TABLE OF CONTENTS

SECTION PAGE

2. CDM-15M( SACD MODULE )

2.1 REMOVING AND REINSTALLING THE MAIN PARTS ...................................................................... 2-2

2.2 BLOCK DIAGRAM............................................................................................................................... 2-5

2.3 SCHEMATIC DIAGRAM...................................................................................................................... 2-9

2.4 PARTS LOCATION ........................................................................................................................... 2-13

2.5 IC DATA ............................................................................................................................................ 2-17

2.6 EXPLODED VIEW AND PARTS LIST............................................................................................... 2-36

2.7 ELECTRICAL PARTS LIST ............................................................................................................... 2-37

Please use this service manual with referring to the user guide ( D.F.U. ) without fail.

R

CDM-15M / CDM-15MB

Page 26

2.1 REMOVING AND REINSTALLING THE MAIN

PART S

SACD MECHANISM SECTION

Perform steps of the disassembly method to remove the

SACD mechanism.

(H1)x4

ø

2.6x6mm

(G1)x1

ø1.7x3mm

(G1)x4

ø3x6mm

CD Servo PWB

Top Plate

Tray Ass'y

(H1)x1

ø

2.6x6mm

(H1)x2

ø

2.6x6mm

Tray Sensor

PWB

(H1)x2

ø

2x5mm

701x2

Pickup

Sensor PWB

(G1)x2

ø2x5mm

Mode Switch

PWB

308

(G2)x2

705x2

313

(G3)x1

714

(G3)x1

(G2)x1

701x2

312x2

326

327

716

711

317

719x2

343

M703 710

328

715

329

711x2

711x4

324

309x2

2-2

318

301

303

325

PWB-D2

PWB-D3

712

SW52

SW51

711x2

713x2

325

711x2

PWB-D1

Page 27

How to remove the loading motor (See Fig. 2-1.)

1. Remove the lift lever.

2. Remove the screws (A1) x 4 pcs., to remove the gear cover.

3. Remove the screws (A2) x 2 pcs., to remove the loading motor.

(Adjusting the SACD mechanism completed products)

It is necessary to position the spindle motor, the sub-shaft

(mechanism), and the pickup to play a nonstandardized SACD

disc. If the pickup or motor is replaced at the service division,

these adjustments cannot be performed because of the facility

and measuring equipment matters.

The SACD mechanism completed products are adjusted for

the above reasons.

After installing:

After installing the SACD mechanism completed product,

remove the two solders shown below.(See Fig. 2-2.)

[REMARK]

• The two solders are used to eliminate static electricity before

installing the SACD mechanism completed product.

Loading

Motor

Lift Cover

(A2) x2

ø1.7x2mm

Gear Cover

Remove these two solders after installing

the SACD mechanism completed product.

(A1) x4

ø2x5mm

Figure 2-2Figure 2-1

2-3

Page 28

Adjusting the tension of the timing belt

Remove the gear unit and connect the ammeter to the DC

power as shown in Fig. 2-3.

If measurement of the loading motor current is possible,

move the motor in the direction of the arrow so as to obtain

40 - 50 mA, and fix the motor with screws (A1) x 2 pcs.

(See Fig. 2-4.)

Connector

3.5V

Figure 2-3

Loading

Motor

M

DC Power

Gear

Unit

(A1) x1

Shaft

Timing Belt

12

Ampere

ø1.7x2mm

Motor

Pully Ass'y

Meter

Drive

Pulley

(A1) x1

ø1.7x2mm

Figure 2-4

2-4

Page 29

10

17

15

IC507

HC4053FS

ANALOG SWITCH

1/3

3/3

IC507

HC4053FS

ANALOG SWITCH

IC507

HC4053FS

ANALOG SWITCH

2/3

IC601

AD8052AR

DUAL

OPE AMP.

IC505

NJM324V

4-CIRCUIT

OPE AMP.

2

4

11

10

1

2

3

4

5

6

7

8

9

4

3

2

12

13

15

16

17

1

29

27

23

26

19

9

11

25

8

22

IC604

TC7W74FU

1/2 DIVIDING

X602

54MHz

IC605

TC7WU04FU

3-CIRCUIT

INVERTER

SW52

STOP

SW51

PLAY

CNP502

CNP501

IC603

SC514870SJ

4Mbit DRAM

IC504

IX2842AF

SPINDLE

MOTOR

DRIVER

IC606

IX1473GE

DIGITAL SERVO

IC506

BA6796FP

LOADING/FOCUS/TRACKING/

SPIN/SLED DRIVER

IC503

TB6504F

STEPPING

MOTOR

DRIVER

IC602

IX1474GE

SACD DATA

PROCESSOR

IC502

IX1517GE

RF SIGNAL

PROCESSOR

DOUT

BCK

IPF

LRCK

AOUT

RF_LT

BUCK

EMPH

BUS3

SBSY

CCE

0

DATA

PLCK

DATA

PLCK

D15

8

D

18

H1,0

HDRD

HCEN

D8

SDCK

RSTN

SREQ

SVAL

HINT

HDWT

SD7

SOSO

SD0

SERR

15

10

,

2724

2 ~ 5

A9R A0~A3 A4~A8

16

10

33MHz

MCK1

XO

74

59

68

88

50

53

24MHz

54MHz

9

3

4

5

12

13

14

INV

Buff

Vref

TO IC901

WARF

TP506

4

LDO2

SACD

APC

CD APC

A5V

A5V

IN-SW

EJ-SW

SPEED-SW

M

MDI2

45

5

44

6

LDO1

VrA

MDI1

4

DOUT

DMO

52

51

48

23

RAS 8

WE227

OE

RVDD

RASN

5347

55

MWEN

56

ED7

CK54M

3

CK27M

32

24

1

PLCK

RF

Vref

TE

AGND

TP510

FE

TP507

TP509

TP508

TP513

PLCK

DATA

DGNDTP511

TP512

52

SEL

Vref

STCK

STDA

97

98

D

9

10

11

23

22

HCEN

HDRD

H1,0

HINT

SD0

90

89

85

79

21

SERR

8

SOSO

SD7

HDWT

SDCK

RSTN

SVAL

SREQ

91

92

94

95

24

32

60

63

3

35

2

61

64

59

58

P2FN

PSC

P2FP

P2FP

P2TP

P2CI

P2BI

P2AI

P2DI

100

3

6

IPF

BCK

AOUT

LRCK

CCE

SBSY

BUS0~BUS3

BUCK

EMPH

92

91

85

13

99

SCD

SCL

SCB

VRCK

13

14

15

16

28RFO

EQB

EQF 4243

15

2

10

1

VRef

TEB

DPD1

DPD2

DFTN

FEO

TEO

RPO

RPZ

LVL

11

12

1933 21242520

22

M

MECSW

EJ-SW

LD-SW

MECSW2

LD-FWD

LD-RVS

IN-SW

DFCT

SEEK

CHOP

OFTRK

TE

LVL

FE

RFRP

SLING

SLIN

25

OPIN+

OPOUT

OPIN-

1

27

28

VREF

Vref

59

DFCT

SHC

JOO

56

67

61

19

TESIO1

62

TESIO0

JO2

JO3

4748TEBC

50

FMO

DMO

TEIN

FEIN

TEZI

SBAD39

42

38

41

RFRP

RFIN

RFZI

RFCT35

36

33

37

FOO

TRO 44

43

23

19

22

20

FO-IN

TR-ING

FO-ING

TR-IN

SS

ECR

5

7

4

LD-CTL

6

LD-RVS

MUTE

LD-FWD

LD-

SL-

LD+

SL+

14

10

13

11

VDD

3

12

54

49

47

50

46

P1TP

VREF_IN

18

16

17

TR-

FO+

TR+

FG 12

GAIN2

GAIN0

SPIN-FG

GAIN1

DVD_L

27

25

28

24

21

22

A11

A21

A12

A31

A22

6

9

3

2

5

8

7

H2-

H3-

H1-

H1+

H2+

H3+

VH

VS

VS

PD

PD

LD

LD

U

V

W

H-

H1+

H1-

H2+

H2-

H3+

H3-

H-

VC

VA

VB

VD

VOSC

TR+

FO+

TRFO-

9

15

16

17

18

19

S/DUAL

GAIN1

GAIN2

f_OUT

c_OUT

a_OUT

d_OUT

e_OUT

b_OUT

TO MECHA

4

6

7

f_IN

c_IN

1

a_IN

d_IN

e_IN

55

P1FN

P1CI

53

P1AI

P1DI

52

P1FP

P1BI

VF

VE

VC

VA

8

IC501

TA1244FN

I/V CONVERTER

AMP.

TO PICK UP

P1TN

RFIN

DVR

A32

FO-

54

9

CAS

2

13

~~

~

~

~

~

~

~

~

20

MOEN

MA9~MA0

M703

LOADING MOTOR

SLED MOTOR

24

I/O1~ I/O4 I/O5~ I/O8

DMO

FOON

Q503

Q504

Q501

Q502

Q506

Q505

Q507

Q601

Q602

2.2 BLOCK DIAGRAM

2-5 2-6

Page 30

SRV_AD

EMPH

SBSY

RFLT

SBCS

BUCK

BUS3

BUS0

TE

FE

RFRP

FL801

20MHz

XTAL

7877EXTAL

UART_RXD

56

UART_CTL

58

99

TE

FE

100

RFRP

101

SRV_AD

102

EMPH64

SBSY

28

106

RFLT

SBCS

107

108

BUCK

BUS3

109

~

~

112

BUS0

DFCT

LD_RVS

LD_FWD

CHOP

OFTRK

105

DFCT

CHOP

OFTRK

LD_RVS

LD_FWD

IC801

SYSTEM

MICROCOMPUTER

IX1478GE

AV_INT30EXP_CS

RST

RESET

120

73

65

60

EJ_SW

LD_SW

66636829697071

EJ_SW

LD_SW

XMSREDY

HWR

FROM_CS

SRAM_CS

118

8384

IN_SW

IN_SW

MSDATO

ECC_CS

ECCINT

SMUTE

A4~A11

A12~A23

D12~D15

RD

KEY1

KEY2

S/E_CS

S/E_CK

S/E_DA

JOG1

JOG2

XMSLA

MSDATI

MSCK

A0~A3

D0~D3

D4~D11

R/C

32

95

96

87

57

86

67

26

88

89

90

92

91

117

31

66

16

34

39

48

IC903

16Mbit SDRAM

IX2840AF

XMSLAT

7

MSCK

8

MSDATI

9

MSDATO

10

XMSREDY

11

9

13 , 16~~

A1

~

A2~A10

51 , 52 , 55 63

A0

21

2

~

5 , 24

~

70 ~ 77

D7~D0

IC901

CXD2751Q

27

6 , 7 , 22 , 23

69

68

66

67

XWE

XCAS

XRAS

XOE

WCK

80

81WRFD

PCLK

DATA

WARF

SACD PLAYBACK

SIGNAL

SMUTE

~

2

5

~

7

14

~

23

~

37

~

46

~

51

136 XRST

MCKI14

PROCESSOR

WAD08982

~

WAD7

12

3

~

D0

~

~

D7

12

CLK

VIN

17

IC902

A/D CONVERTER

ADC08351

WR

A1,A0

D15 8

RST0_1

SEEK

GAIN0

GAIN1

GAIN2

DVD_L

4

RD

~

59

27

54

57

5856SBUFAI

IC803

RESET

PST9129N

MRST

EXPPAU3

BUFD1

SBUFB1

SBUFAO

~

HDAT0

~

8 15

24

HCS

HDATA7

5

6

47

HADR

EXPD2

HRD

HWR

7

45EXPD0

EXPC5

21

EXPC0

EXPPAL3

464438

EXPD1

IC802

IX1535GE

INPUT/OUTPUT

EXPANDER

28

29

22

EXPBL1

EXPBL0

EXPPAU0

30

EXPBL3

EXPBL2

344331

EXPC4

EXPBU0

39

EXPC1

EXPPAU2

SBUFB0

BUFC0

EXCK01

ZDFLGR

ZDFLGL

17

50

49

356

4

2

KEY1

AT5V

FIP_CS

XSRQ

XSHD

2

1

SBGN

SREQ

FIP_DA

FIP_CK

5

SDCK

7

KEY2

99

SERR

8

FIL

SD7

~

91

100

SENB

9

10

FIL

AT-30V

SD0

98

~

SD7 0

12

11

R/C

D_GND

ECC_CS

ECCINT

13

14

AT5V

DISPLAY

D_GND

1

2

A_5V

FIL(+)

356

4

7

FIL(-)

AT5V

AT8V

AT-30V

CNP902

1

2

3

4

5

6

7

8

9

10

11

8

9

A_GND

M_GND

DACCK

DACDT

DSDCTL

VOLCS

EXTCK

EXTDO

EXTST

EXTDI

D_GND

DACRST

RXDA

10

11

D_GND

D3.3V(L)

D3.3V(H)

TO MAIN

12

13

VM

D5V

DSAR

DSAL

BCKA

48

47

46

~

2

12 , 23 , 25

A16 ~ A0

CE1

22

24

OE

29

R/W

53BUFD0

26

55

61

643

5

8

7

DSAL

BCKA

D_GND

D_GND

DSAR

D_GND

2

ZFLGL

11

2628/CE

1

ZFLGR

WR

/OE

1Mbit SRAM

13 15 , 17 21

~~

8 , 16 24 , 25 , 28

1

FLASH ROM (4M)

D0 ~ D16

~~

29 36 , 38 45

1

2

CDDAT

CDCLK

, 26, 27 , 28

A11,A9,A8,A13

A10

IC804

IX2839AF

I/O1

~ I/O3

~~

A18 ~ A0

IC805

IX1539GE

35

4

MCKI

256FS

D_GND

CDFRM

I/O4

8

7

MMUTE

~ I/O8

/RP

12

9

10

EMPH

DISPLAY

12

11

SA/CD

AMUTE

D_GND

1

2

DOUT

D_GND

356

4

D5V

RXDA

RXDCTL

1

~

XSAK

SDEF

SDCK

CDDAT

CDCLK

CDFRM

CDERR

EMPH

CLK1 33MHz

CNP905

TO MAIN TO MAIN TO MAIN

CNP906

CNP901

CNP903

TO DISPLAY

2-7 2-8

CNP904

TO POWER

Page 31

2.3 SCHEMATIC DIAGRAM

PICKUP UNIT

ACTUATOR

HOLOGRAM

LASER UNIT

(DVD)

Gnd

OSC

HOLOGRAM

LASER UNIT (CD)

SLED MOTOR

Fo+

TrTr+

Fo-

LD

PD

VA

VB

VC

VD

V/2

VDD

Gnd

VDS

VDD

VA

VB

VC

VE

VF

V/2

Gnd

LD

PD

M

SPINDLE MOTOR

R606

A_5V_R605

TP506

TP507

TP513

R608 220K

C610

330P

(CH)

C605

0.1

C606

100/6.3

L601

47µH

C603

100/6.3

+B

(SEL)

+B

4 .9V

680

1 2 3 4

2 .2V

R610

33

RF

A_GND

FE

TE

VREF

D_GND

PLCK

DATA

R609

10K

C604

0.0033

C613

0.01

(LD_CTL)

(/MUTE)

C611

0.01

+B

C609

100P

(CH)

C672

10P(CH)

C626

0.01

33MHZ

3.8

0.4

C631

47/6.3

5678

2.1V

0V

0 V

26

1K

27

0 V

0 V

28

0 V

29

0 V

30

31

5.0 V

4.3 V

32

0V

33

1.7V

34

1.7V

35

R619

36

270K

37

3.4V

38

C616

39

0.01

40

0V

41

1.7V

42

1.7V

43

1.7V

44

3.4V

45

0.85V

46

3.4V

47

1.7V

48

0V

49

3.4V

50

(D3.3V_L601)

C627

100/6.3

10K

R622

150

(LVL)

(FOO)

(TRO)

R620

10K

C625

0.01

0V

DMO

2VREF

SEL

/FOON

/DFCT

/SRCH

/SHC

VDD

VSS

IO0

IO1

IO2

IO3

DMOUT

CKSE

DACT

TESIN

TESIO1

VSS

PXI

PXO

VDD

XVSS

XI

XO

XVDD

DVDDRODVSS

767778 798081 828384 8586 87888990 919293 949596 979899

5.0V

C628

0

+B

IC601

(A1)

(A0)

(ECCINT)

1K

R626

AD8052AR

1.8V

5.0V0V5.0V

0.2V

0V

(MDX)

(MDY)

(MDY)

(MDXD)

ED_I/F

DATA_SLICE

1.5V

PLL

RLL_DETECTER

SLCO

AVSS

AVR

(PVK)

VRC

PVR

AFC_CONTROL

AVDD

AFC_CONTER

RVR2

AFC_CONTROL

RVDD

AFC_CONTER

RFIN

BRAKE

RVSS

RVR1

MEMORY_MANAGEMENT_UNIT/ADDRESS_GEN

PWM

5152 53545556 575859 606162 636465 666768 697071 727374 75

1.8V

1.8V

5.0V

5.0V

5.0V

5.0V

R623

(CASN)

(MOEN)

(MWEN)

(RASN)

5.6K

C629

0.1

0.1

C637

IC603

SC514870SJ

4M Bit DRAM

R630

(TE)

12K

C633

C634

0.0047

0.0047

12K

R629

330

0.01

R624

C635

330

C638

R625

2.1V

2.1V

2.1V

2.5V

2.1V

2.1V

2.1V

2.1V

2.1V

TRO

FVO

2.6V

0.01

FMO

PWM

SERVO

CTL

0V

TEBC

RFGC

CK

GEN.

1bit

DAC

LPF

2.5V

2.6V

DVRLODVDD

C630

0.047

VREF

5.0V

C632

R627

TEZI

FOO

TEIN

D/A

5.0V

TEST1

TEST2

TEST3

BUS0

5.0V

5.0V

5.0V

0.01

10K

R628

10K

(BUS0)

C619

0.01

C612

0.01

R611

2.0V

2.2V

R615

470

C615

0.033

C617

22P(CH)

C621

0.01

C623

470P

C622

0.01

10K

5.0V

R613

4.2V

5.0V

5.0V

5.0V

5.0V

5.0V

5.0V

5.0V

5.0V

5.0V

5.0V

1.9V

2.1V

5.0V

10K

C614

0.047

0V

0V

0V

0V

0V

0V

0V

R616

C618

C620

0V

0V

0V

R612

680

2.1V

2.2V

R614

33

R618

470

1.65V

0.93V

1.3V

1

1

R621

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

(D13)

(D14)

(D12)

(4.2MHz)

(370KHz)