LG Display LC420EUH-SCR1 Specification

Product Specification

LCM ENGINEERING

SPECIFICATION

LC420EUH

Ver. 1.1

*MODEL LC420EUH

SUFFIX SCR1-7R1

Update 2010.02.01

( ) Preliminary Specification

(

) Final Specification

●

1 /33

Product Specification

CONTENTS

LC420EUH

Number ITEM

COVER 1

CONTENTS

RECORD OF REVISIONS

1 GENERAL DESCRIPTION

2 ABSOLUTE MAXIMUM RATINGS

3 ELECTRICAL SPECIFICATIONS

3-1 ELECTRICAL CHARACTERISTICS

3-2 INTERFACE CONNECTIONS

3-3 SIGNAL TIMING SPECIFICATIONS

3-4 DATA MAPPING AND TIMING 15

3-5 PANEL PIXEL STRUCTURE

3-6 POWER SEQUENCE

4 OPTICAL SPECIFICATIONS

5 MECHANICAL CHARACTERISTICS

Page

2

3

4

5

6

6

9

12

16

17

18

22

6 RELIABILITY

7 INTERNATIONAL STANDARDS

7-1 SAFETY

7-2 Environment

8 PACKING

8-1 DESIGNATION OF LOT MARK

9 PRECAUTIONS

9-1 MOUNTING PRECAUTIONS 28

9-2 OPERATING PRECAUTIONS

9-3 ELECTROSTATIC DISCHARGE CONTROL

9-4 PRECAUTIONS FOR STRONG LIGHT EXPOSURE

9-5 STORAGE 29

9-6 HANDLING PRECAUTIONS FOR PROTECTION FILM

Ver. 1.1

25

26

26

26

27

27

28

28

29

29

29

2 /33

Product Specification

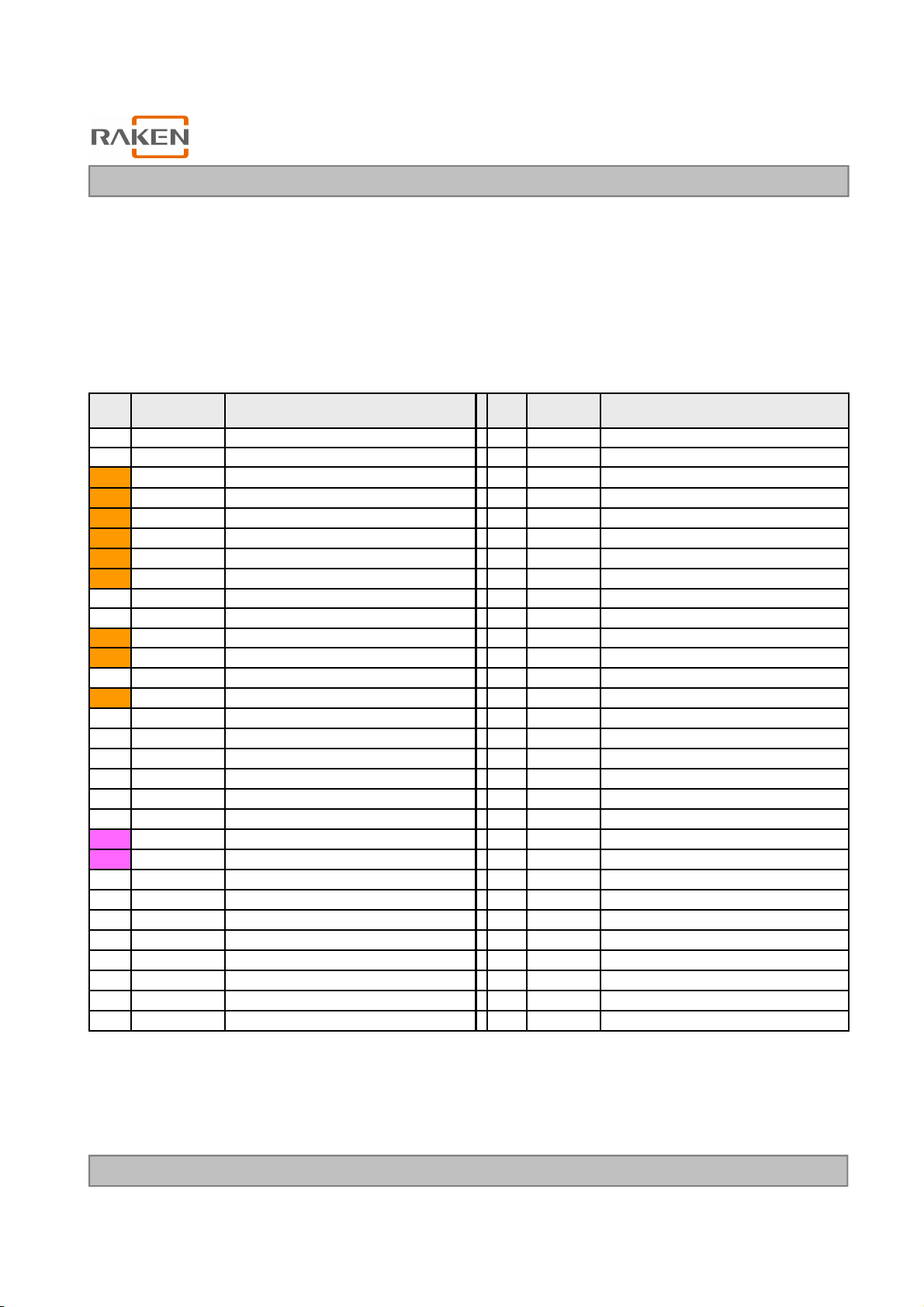

RECORD OF REVISIONS

Revision No. Revision Date Page Description

0.1 Oct. 18. 2009 - Preliminary Specification(First Draft)

1.0 Jan. 28. 2010 6 Changed Electrical Characteristics

Jan. 28. 2010 8 Changed Table 3. ELECTRICAL CHARACTERISTICS (Continue)

Jan. 28. 2010 17 Changed power sequence (note)

Jan. 28. 2010 19 Changed Table 9. GRAY SCALE SPECIFICATION

Jan. 28. 2010 31 LED Array Electrical Spec

1.1 Feb. 01. 2010 - Final Specification

LC420EUH

Ver. 1.1

3 /33

LC420EUH

Gamma Reference Voltage

Product Specification

1. General Description

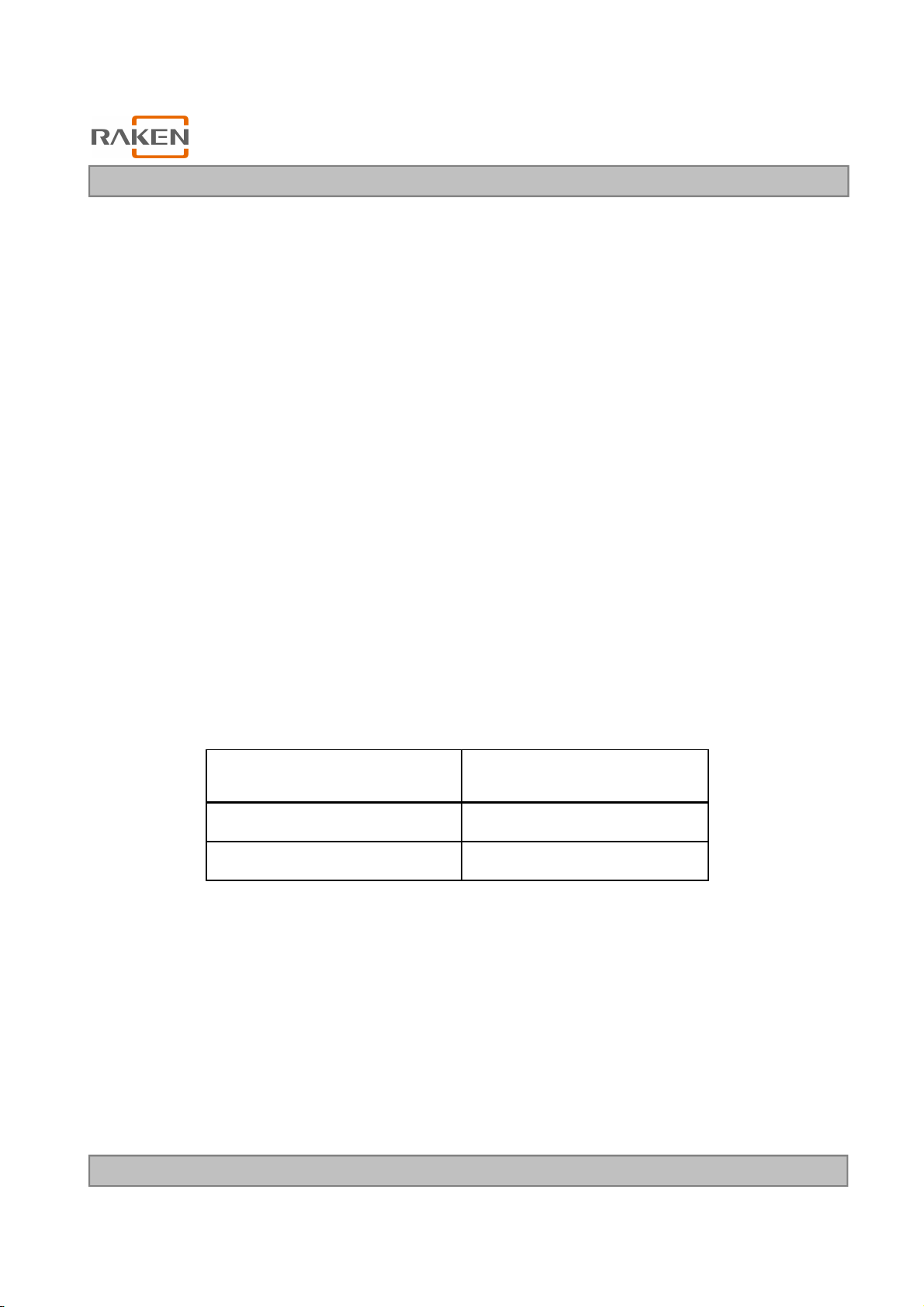

The LC420EUH is a Color Active Matrix Liquid Crystal Display with an integral Light Emitting Diode (LED)

back l ight s ys t e m . T h e m a t r i x e m p l o ys a- Si Thin Film Tr a n s i s t o r a s the active element.

It is a transmissive type display operating in the normally black mode. It has a 42.02 inch diagonally measured

act i v e display area wit h WUXG A res oluti o n (1 080 v ertica l by 1920 hor i zonta l pix e l ar r ay).

Each pixel is divided into Red, Green and Blue sub-pixels or dots which are arranged in vertical stripes.

Gray scale or the luminance of the sub-pixel color is determined with a 8-bit gray scale signal for each dot.

Therefore, it can present a palette of more than 16.7M(true) colors.

It is intended to support LCD TV, PCTV where high brightness, super wide viewing angle, high color gamut,

high color depth and fast response time are important.

Power (VCC, VDD, VGH, VGL)

Source Control Signal

Gate Control Signal

Gamma Reference Voltage

mini-LVDS (RGB) for Left drive

CN1

(60pin)

S1 S1920

G1

Source Driver Circuit

Power (VCC, VDD, VGH, VGL)

Source Control Signal

Gate Control Signal

mini-LVDS (RGB) for Right drive

LED Anode

LED Cathode

CN2

(60pin)

CN1 (12pin)

CN2 (13pin)

G1080

TFT - LCD Panel

(1920 × RGB × 1080 pixels)

[Gate In Panel]

V : 2Block

Local Dimming : 12 Block

General Features

Active Screen Size 42.02 inches(1067.31mm) diagonal

Outline Dimension 973.2(H) x 566.2 (V) x 10.8 mm(B)/25.3(D) (Typ.)

Pixel Pitch 0.4845 mm x 0.4845 mm

Pixel Format 1920 horiz. by 1080 vert. Pixels, RGB stripe arrangement

Color Depth

Drive IC Data Interface

Luminance, White 450 cd/m2 (Center 1point ,Typ.)

Viewing Angle (CR>10) Viewing angle free ( R/L 178 (Min.), U/D 178 (Min.))

8-bit, 16.7 M colors (※ 1.06B colors @ 10 bit (D) System Output )

Source D-IC : 8-bit mini-LVDS, gamma reference voltage, and control signals

Gate D-IC : Gate In Panel

H : 6 Block

Power Consumption Total 98 W (Typ.) (Logic=10 W with T-CON, LED Backlight =88W @ with Driver )

Weight 11.1Kg (Typ.)

Display Mode Transmissive mode, Normally black

Surface Treatment Hard coating (3H), Anti-glare treatment of the front polarizer (Haze 10%)

Ver. 1.1

4 /33

LC420EUH

Operating Ambient Humidity

HOP1090%RH

Operating Ambient Humidity

HOP1090%RH

Product Specification

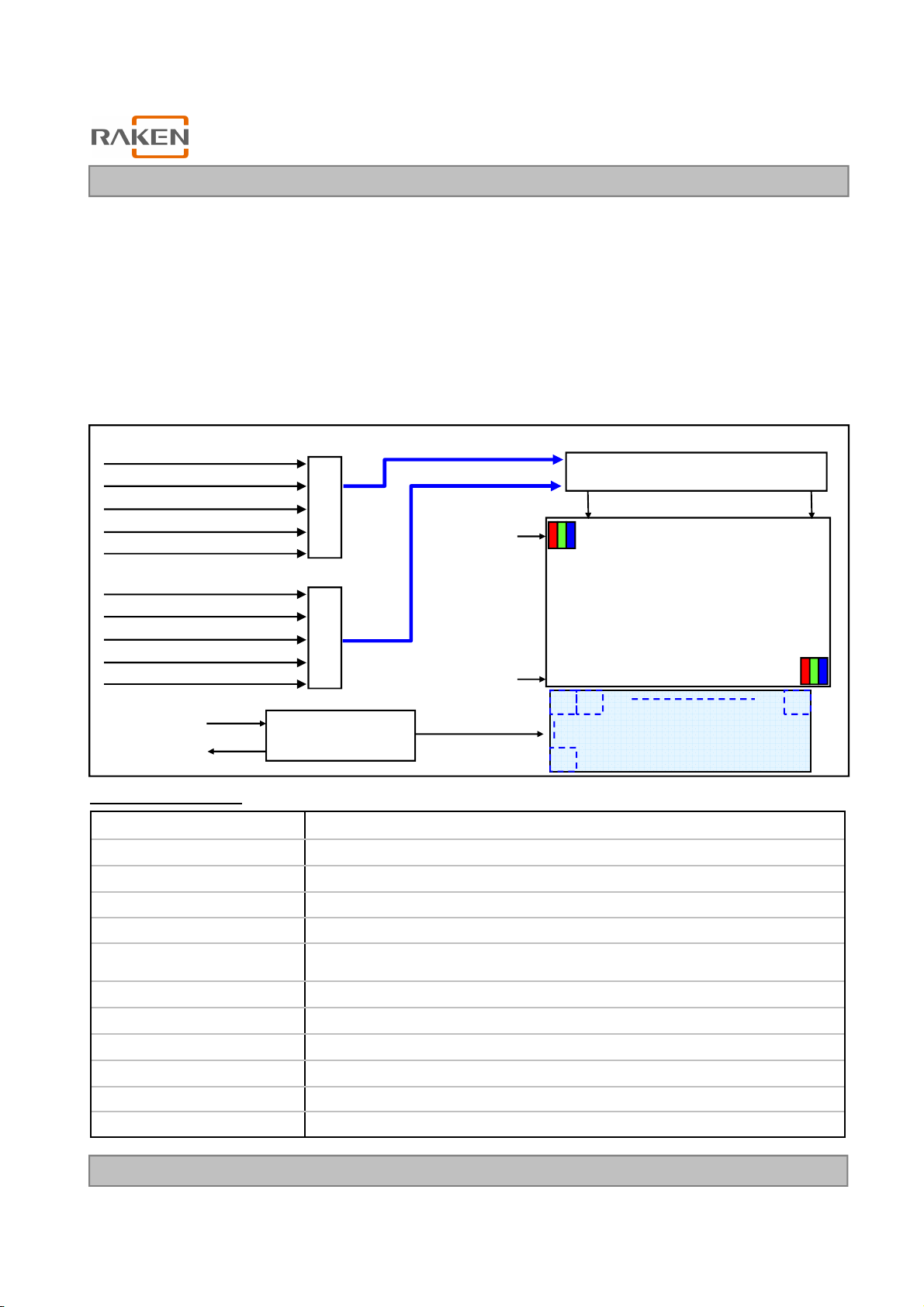

2. Absolute Maximum Ratings

The following items are maximum values which, if exceeded, may cause faulty operation or damage to the

LCD module.

Table 1. ABSOLUTE MAXIMUM RATINGS

Parameter Symbol

Logic Power Voltage VCC -0.5 +4.0 VDC

Gate High Voltage VGH +18.0 +30.0 VDC

Gate Low Voltage VGL -8.0 -4.0 VDC

Source D-IC Analog Voltage VDD -0.3 +18.0 VDC

Gamma Ref. Voltage (Upper) VGMH ½VDD-0.5 VDD+0.5 VDC

Gamma Ref. Voltage (Low) VGML -0.3 ½ VDD+0.5 VDC

LED Input Voltage Vf - +180.0 VDC

Panel Front Temperature TSUR - +68

Operating Temperature TOP 0 +50

Storage Temperature TST -20 +60

Storage Humidity HST 10 90 %RH

Note:

1. Ambient temperature condition (Ta = 25 ± 2 °C )

Value

Unit Note

Min Max

°C

°C

°C

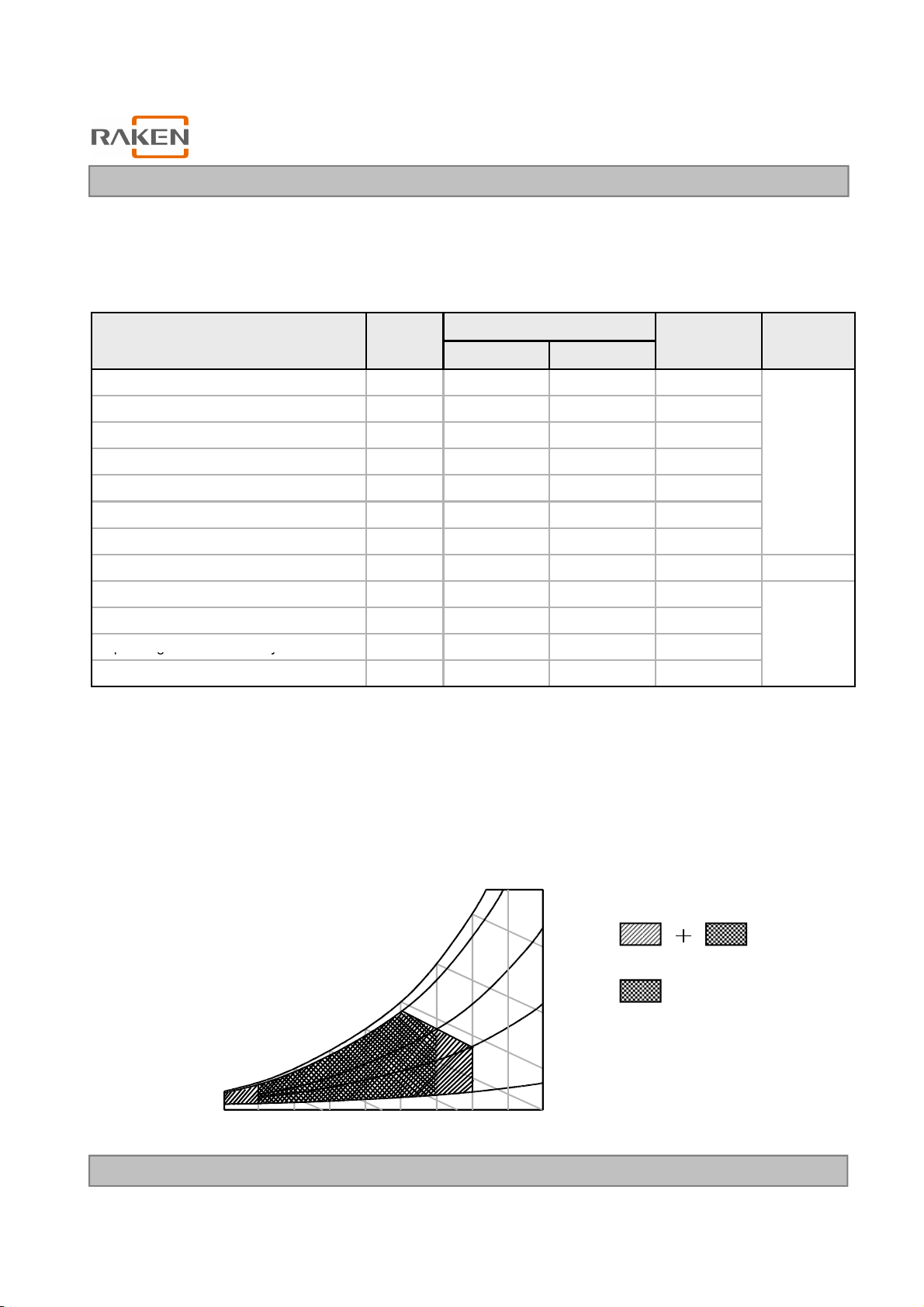

2. Temperature and relative humidity range are shown in the figure below. Wet bulb temperature

should be Max 39 °C and no condensation of water.

3. Gravity mura can be guaranteed below 40℃ condition.

4. The maximum operating temperature is based on the test condition that the surface temperature

of display area is less than or equal to 68 ℃ with LCD module alone in a temperature controlled

chamber. Thermal management should be considered in final product design to prevent the surface

temperature of display area from being over 68 ℃. The range of operating temperature may

degrade in case of improper thermal management in final product design.

90%

60

60%

1

4

2,3

Ver. 1.1

Wet Bulb

Temperature [°C]

20

10

0

10 20 30 40 50 60 70 800-20

Dry Bulb Temperature [°C]

30

40

50

40%

10%

Storage

Operation

Humidity

[(%)RH]

5 /33

LC420EUH

(Center)

− VID / 2

Product Specification

3. Electrical Specifications

3-1. Electrical Characteristics

It requires several power inputs. The VCC is the basic power of LCD Driving power sequence, Which is used

to logic power voltage of Source D-IC and GIP.

Table 2. ELECTRICAL CHARACTERISTICS

Parameter Symbol Condition MIN TYP MAX

Logic Power Voltage VCC - 3.0 3.3 3.6 VDC

Logic High Level Input Voltage VIH 2.7 VCC VDC

Logic Low Level Input Voltage VIL 0 0.6 VDC

Source D-IC Analog Voltage VDD - 16.05 16.25 16.45 VDC

Half Source D-IC Analog

Voltage

Gamma Reference Voltage

Common Voltage Vcom

Mini-LVDS Clock frequency CLK 3.0V≤VCC ≤3.6V 312 MHz

mini-LVDS input Voltage

mini-LVDS input Voltage

Distortion (Center)

mini-LVDS differential

Voltage range

mini-LVDS differential

Voltage range Dip

Gate High Voltage VGH

Gate Low Voltage VGL -5.2 -5.0 -4.8 VDC

GIP Bi-Scan Voltage

GIP Refresh Voltage

GIP Start Pulse Voltage VST - VGL - VGH V

GIP Operating Clock GCLK - VGL - VGH V

Total Power Current

Total Power Consumption

1. The specified current and power consumption are under the VLCD=12V., 25 ± 2°C, fV=120Hz

Note:

H_VDD - 7.89 8.1 8.31 VDC

V

GMH

V

GML

VIB 0.7 + (VID/2)

∆VIB 0.8 V

VID 150 800 mV

∆VID 25 800 mV

VGI_P

VGI_N

VGH

even/odd

ILCD - 815 938 mA 2

PLCD - 9.78 11.25 Watt 2

(GMA1 ~ GMA9) ½*VDD VDD-0.2

(GMA10 ~ GMA18) 0.2 ½*VDD

Normal 6.56 6.86 7.16 V

Reverse 6.56 6.86 7.16 V

(VCC-1.2)

Mini-LVDS Clock

and Data

@ 25℃

@ 0℃

- VGL - VGH VDC

- VGL - VGH V

27.7 28 28.3 VDC

28.7 29 29.3 VDC

UnitNo

condition whereas mosaic pattern(8 x 6) is displayed and fVis the frame frequency.

2. The above spec is based on the basic model.

3. All of the typical gate voltage should be controlled within 1% voltage level

4. Ripple voltage level is recommended under 10%

5. In case of mini-LVDS signal spec, refer to Fig 2 for the more detail.

6. Logic Level Input Signal : SOE,POL,GSP,H_CONV,OPT_N

7. HVDD Voltage level is half of VDD and it should be between Gamma9 and Gamma10.

Ver. 1.1

te

V

5

6 /33

VCM (0V)

VIB

VIB VIB

VIB

VIB

VIB VIB

VIB

VCM (0V)

VCM (0V) VCM (0V)

VGH

VGHM

GND

VGL

VID

VID

VIDVID

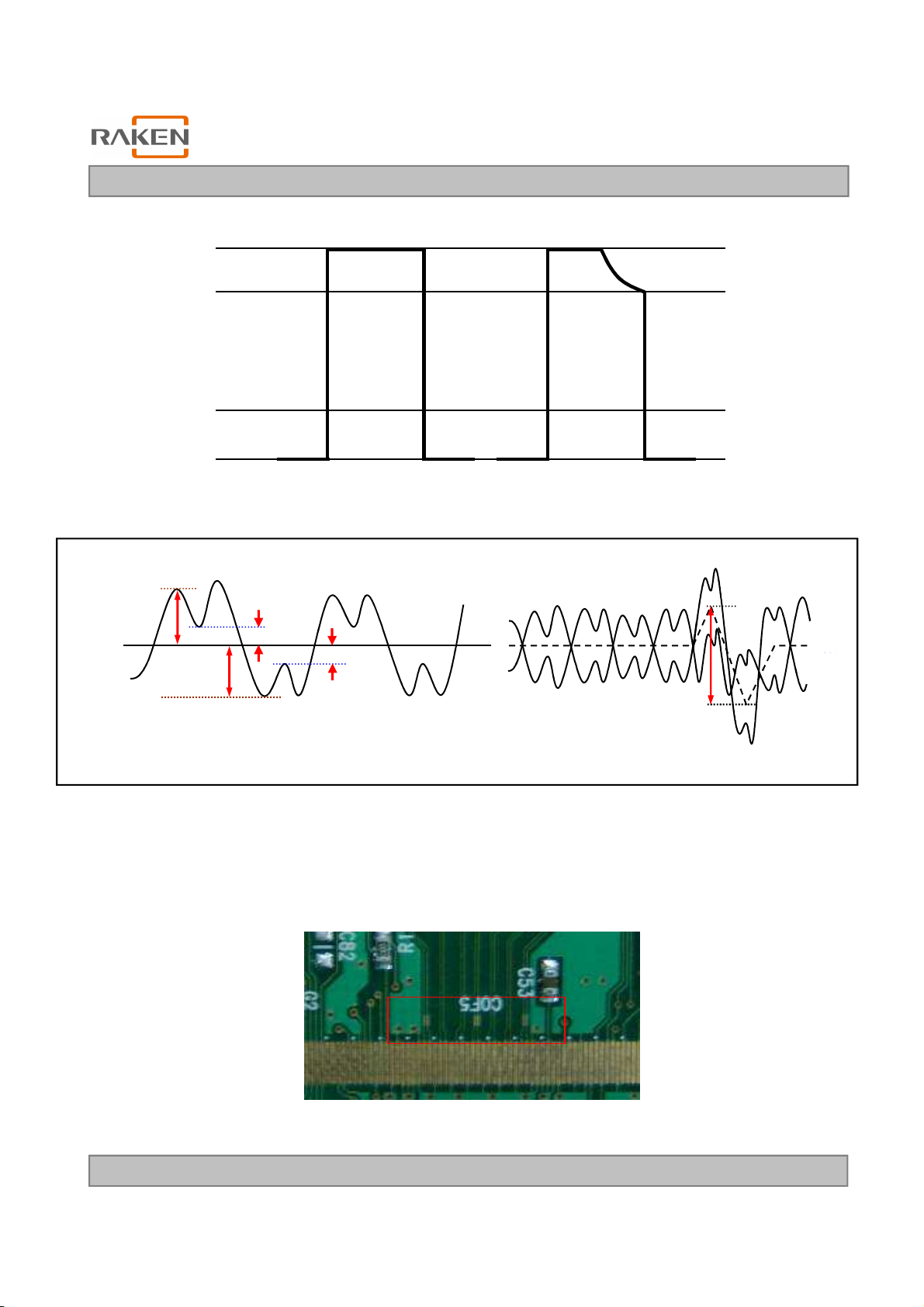

Product Specification

Without GPM With GPM

FIG. 1 Gate Output Wave form without GPM and with GPM

△△△△VID

VID

VID VID

△△△△VIB

VIB

VIBVIB

LC420EUH

VID

VID

VIDVID

* Differential Probe

* Differential Probe

* Differential Probe* Differential Probe

△△△△VID

VID

VID VID

* Active Probe

* Active Probe

* Active Probe* Active Probe

FIG. 2 Description of VID, ∆VIB, ∆VID

*

* S o u rc e P C B

S o u rc e P C B

* *

S o u rc e P C BS o u rc e P C B

FIG. 3 Measure point

Ver. 1.1

7 /33

Product Specification

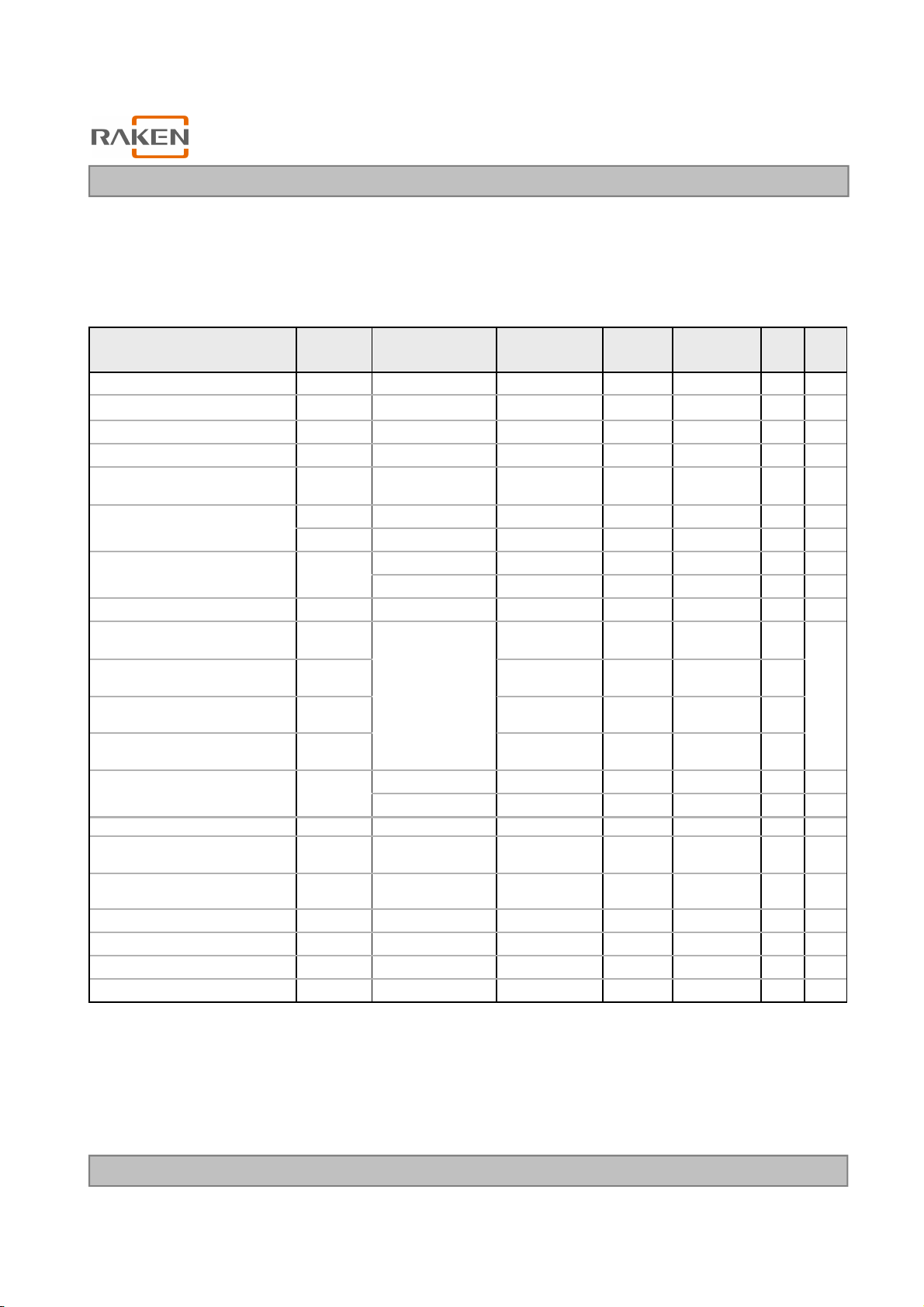

Table 3. ELECTRICAL CHARACTERISTICS (Continue)

LC420EUH

Parameter Symbol

Backlight Assembly :

Forward Current

(one array)

Forward Voltage V

Forward Voltage Variation

Power Consumption P

Burst Dimming Duty On duty 1 100 %

Burst Dimming Frequency 1/T 95 182 Hz 8

LED Array : (APPENDIX-ⅢⅢⅢⅢ)

Life Time 30,000 50,000 Hrs 7

Notes :

The design of the LED driver must have specifications for the LED array in LCD Assembly.

Anode I

Cathode I

F (anode)

F (cathode)

F

△V

F

BL

Min Typ Max

52.25 55 57.75 mAdc

110.2 117.8 125.4 Vdc 4

72.7 77.8 82.7 W 6

Values

165 mAdc

1.7 Vdc 5

Unit Note

The electrical characteristics of LED driver are based on Constant Current driving type.

The performance of the LED in LCM, for example life time or brightness, is extremely influenced by the

characteristics of the LED Driver. So, all the parameters of an LED driver should be carefully designed.

When you design or order the LED driver, please make sure unwanted lighting caused by the mismatch of the

LED and the driver (no lighting, flicker, etc) has never been occurred. When you confirm it, the LCD–

Assembly should be operated in the same condition as installed in your instrument.

1. Electrical characteristics are based on LED Array specification.

2. Specified values are defined for a Backlight Assembly. (IBL : 4 LED array, 165mA/LED array)

3. Each LED array has one anode terminal and three cathode terminals.

The forward current(I

) of the anode terminal is 165mA and it supplies 55mA into three strings, respectively

F

19 (LED Pakage / 1string)

±5%

2, 3

Anode

°°°° °°°° °°°°

°

°

°

°

°

°

°

°

°

°

°

°

°°°° °°°° °°°°

°°°° °°°° °°°°

Cathode #1

Cathode #2

3 (LED String / 1 Array)

Cathode #3

4. The forward voltage(VF) of LED array depends on ambient temperature (Appendix-Ⅲ)

5. ∆VFmeans Max VF-Min VFin one Backlight. So VFvariation in a Backlight isn’t over Max. 1.7V

6. Maximum level of power consumption is measured at initial turn on.

Typical level of power consumption is measured after 1hrs aging at 25 ± 2°C.

7. The life time(MTTF) is determined as the time at which brightness of the LED is 50% compared to that of

initial value at the typical LED current on condition of continuous operating at 25 ± 2°C, based on duty 100%.

8. The reference method of burst dimming duty ratio.

It is recommended to use synchronous V-sync frequency to prevent waterfall

(Vsync x 1 =Burst Frequency)

Though PWM frequency is over 182Hz (max252Hz), function of backlight is not affected.

Ver. 1.1

8 /33

LC420EUH

12

VGH_EVEN

GIP Panel VDD for Even GATE TFT

42

SOE

Source Output Enable SIGNAL

Product Specification

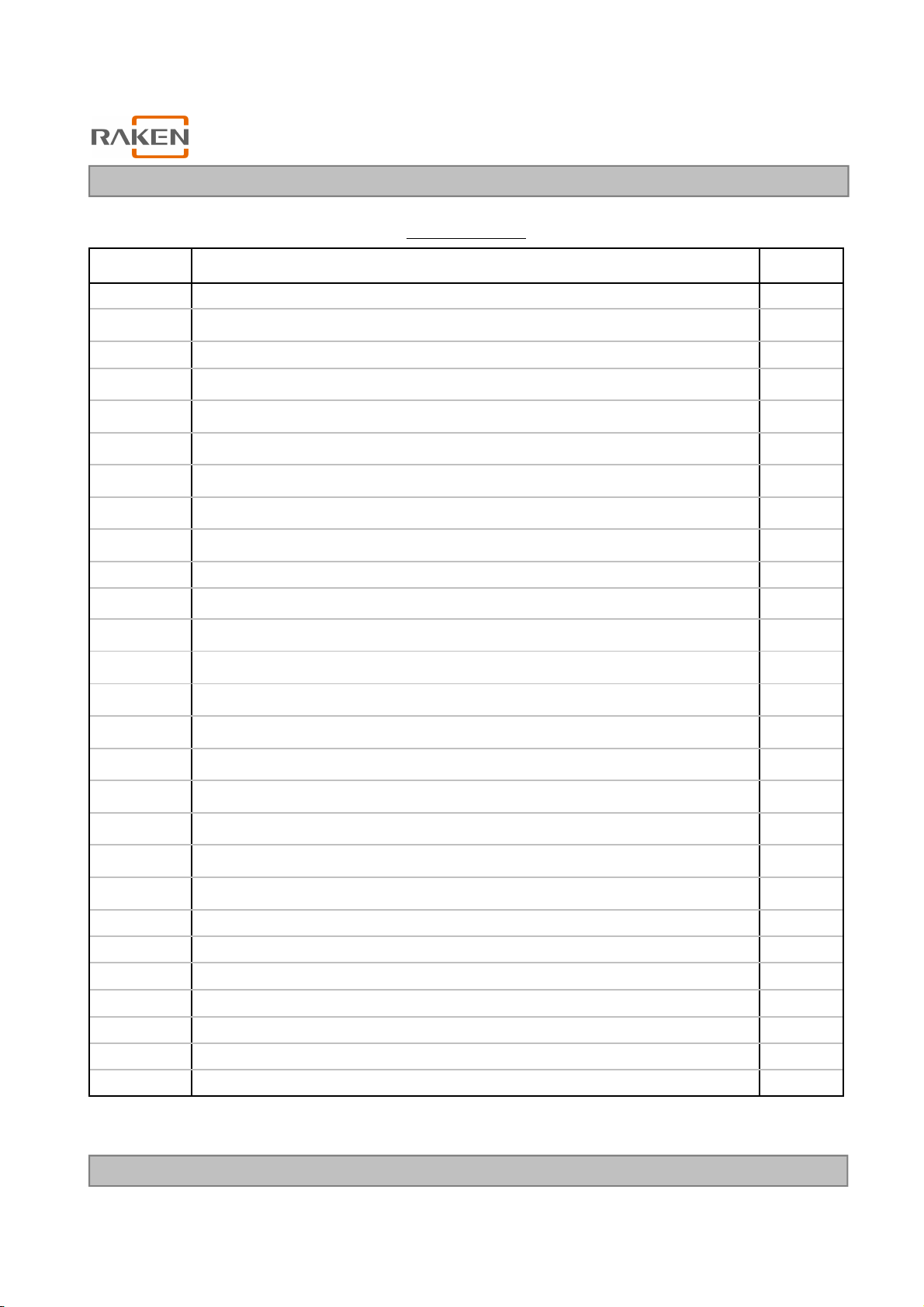

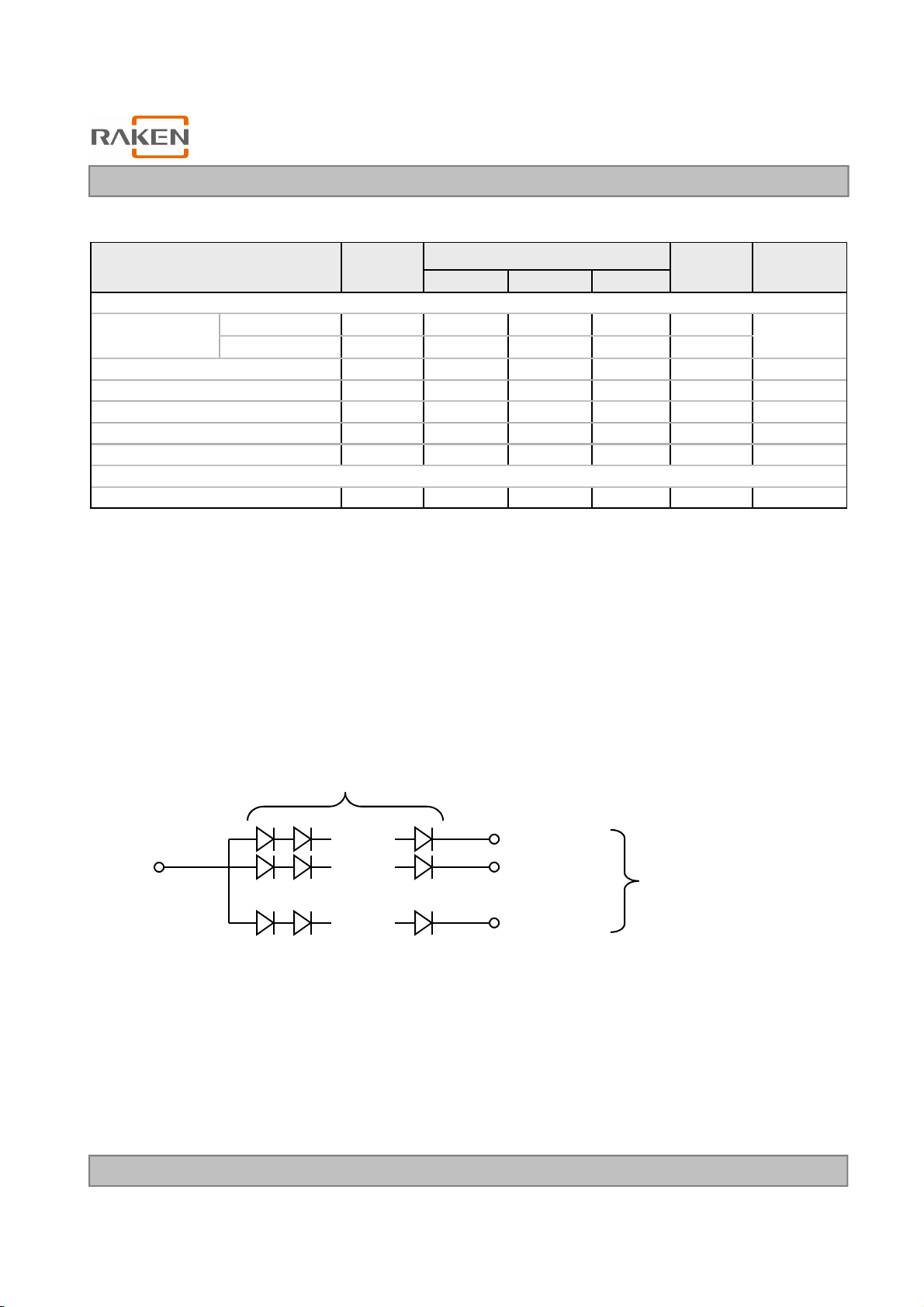

3-2. Interface Connections

This LCD module employs two kinds of interface connection, two 60-pin FFC connector are used for the

module electronics and 12-pin,13-pin connectors are used for the integral backlight system.

3-2-1. LCD Module

-LCD Connector (CN1): TF06L-60S-0.5SF (Manufactured by HRS) or Equivalent

Table 4-1. MODULE CONNECTOR(CN1) PIN CONFIGURATION

No Symbol Description No Symbol Description

1

2 LTD_OUT LTD OUTPUT

3

4

5

6

7

8

9

10

11

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

GND Ground 31 LLV3 - Left Mini LVDS Receiver Signal(3-)

32 LLV3 + Left Mini LVDS Receiver Signal(3+)

GCLK1 GIP GATE Clock 1 33 LCLK - Left Mini LVDS Receiver Clock Signal(-)

GCLK2 GIP GATE Clock 2 34 LCLK + Left Mini LVDS Receiver Clock Signal(+)

GCLK3 GIP GATE Clock 3 35 LLV2 - Left Mini LVDS Receiver Signal(2-)

GCLK4 GIP GATE Clock 4 36 LLV2 + Left Mini LVDS Receiver Signal(2+)

GCLK5 GIP GATE Clock 5 37 LLV1 - Left Mini LVDS Receiver Signal(1-)

GCLK6 GIP GATE Clock 6 38 LLV1 + Left Mini LVDS Receiver Signal(1+)

VGI_N GIP Bi-Scan (Normal =VGL Rotate = VGH) 39 LLV0 - Left Mini LVDS Receiver Signal(0-)

VGI_P GIP Bi-Scan (Normal =VGH Rotate = VGL) 40 LLV0 + Left Mini LVDS Receiver Signal(0+)

VGH_ODD GIP Panel VDD for Odd GATE TFT 41 GND Ground

VGL GATE Low Voltage 43 POL Polarity Control Signal

VST VERTICAL START PULSE 44 GSP GATE Start Pulse

GND Ground 45 H_CONV "H“ H 2dot Inversion/ "L" H 1dot Inversion

VCOM_L_FB VCOM Left Feed-Back Output 46 OPT_N “H” Normal Display / “L” Rotation Display

VCOM_L VCOM Left Input 47 GND Ground

GND Ground 48

VDD Driver Power Supply Voltage 49

VDD Driver Power Supply Voltage 50

H_VDD Half Driver Power Supply Voltage 51

H_VDD Half Driver Power Supply Voltage 52

GND Ground 53

VCC Logic Power Supply Voltage 54

VCC Logic Power Supply Voltage 55

GND Ground 56

LLV5 - Left Mini LVDS Receiver Signal(5-) 57

LLV5 + Left Mini LVDS Receiver Signal(5+) 58

LLV4 - Left Mini LVDS Receiver Signal(4-) 59

LLV4 + Left Mini LVDS Receiver Signal(4+) 60 GND Ground

GMA 18 GAMMA VOLTAGE 18 (Output From LCD)

GMA 16 GAMMA VOLTAGE 16

GMA 15 GAMMA VOLTAGE 15

GMA 14 GAMMA VOLTAGE 14

GMA 12 GAMMA VOLTAGE 12

GMA 10 GAMMA VOLTAGE 10 (Output From LCD)

GMA 9 GAMMA VOLTAGE 9 (Output From LCD)

GMA 7 GAMMA VOLTAGE 7

GMA 5 GAMMA VOLTAGE 5

GMA 4 GAMMA VOLTAGE 4

GMA 3 GAMMA VOLTAGE 3

GMA 1 GAMMA VOLTAGE 1 (Output From LCD)

Note :

1. Please refer to application note for details.

(GIP & Half VDD & Gamma Voltage & H_CONV setting)

2. These 'input signal' (OPT_N,H_CONV) should be connected

Ver. 1.1

9 /33

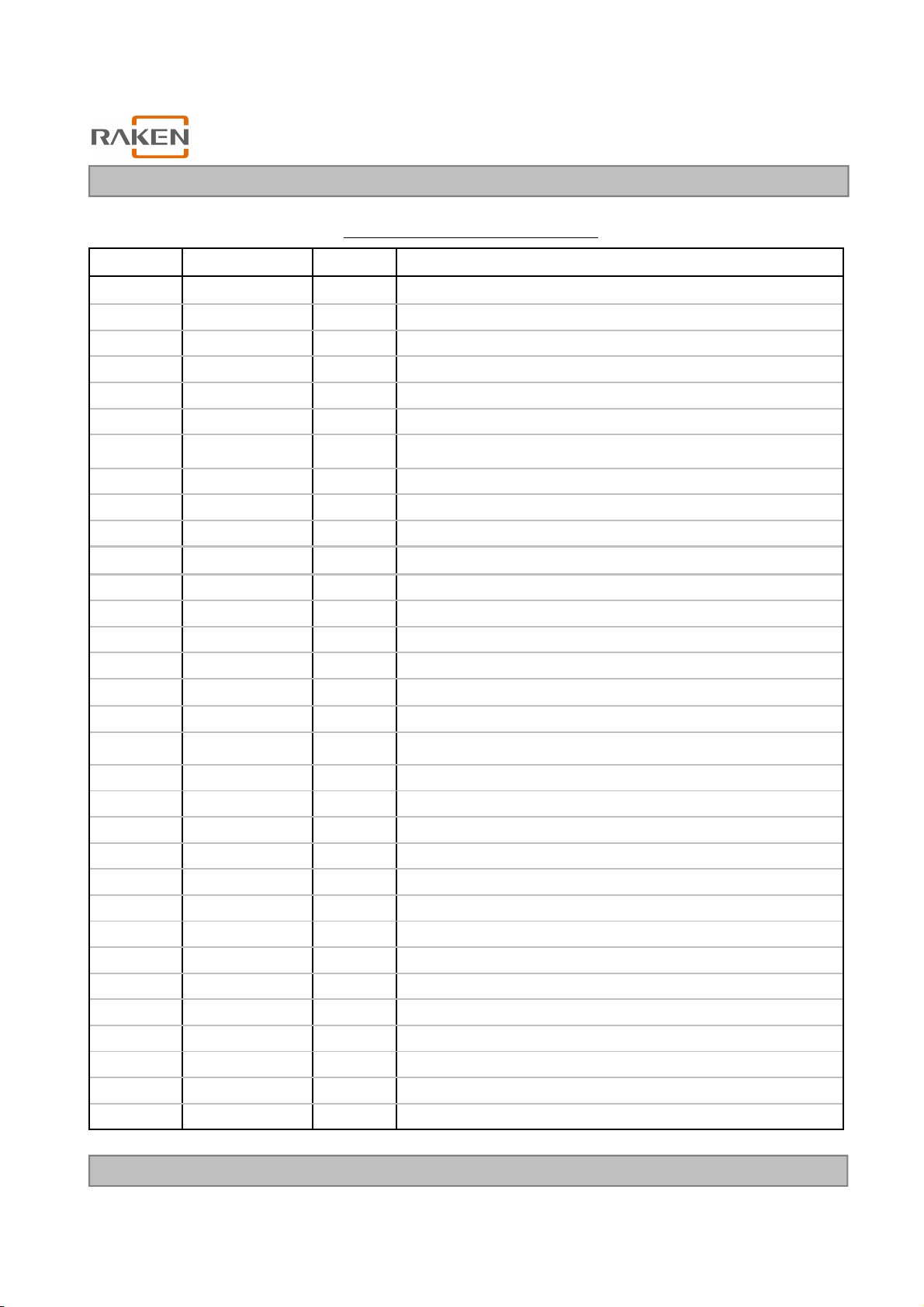

Product Specification

17

GSP

GATE Start Pulse

47

VST

VERTICAL START PULSE

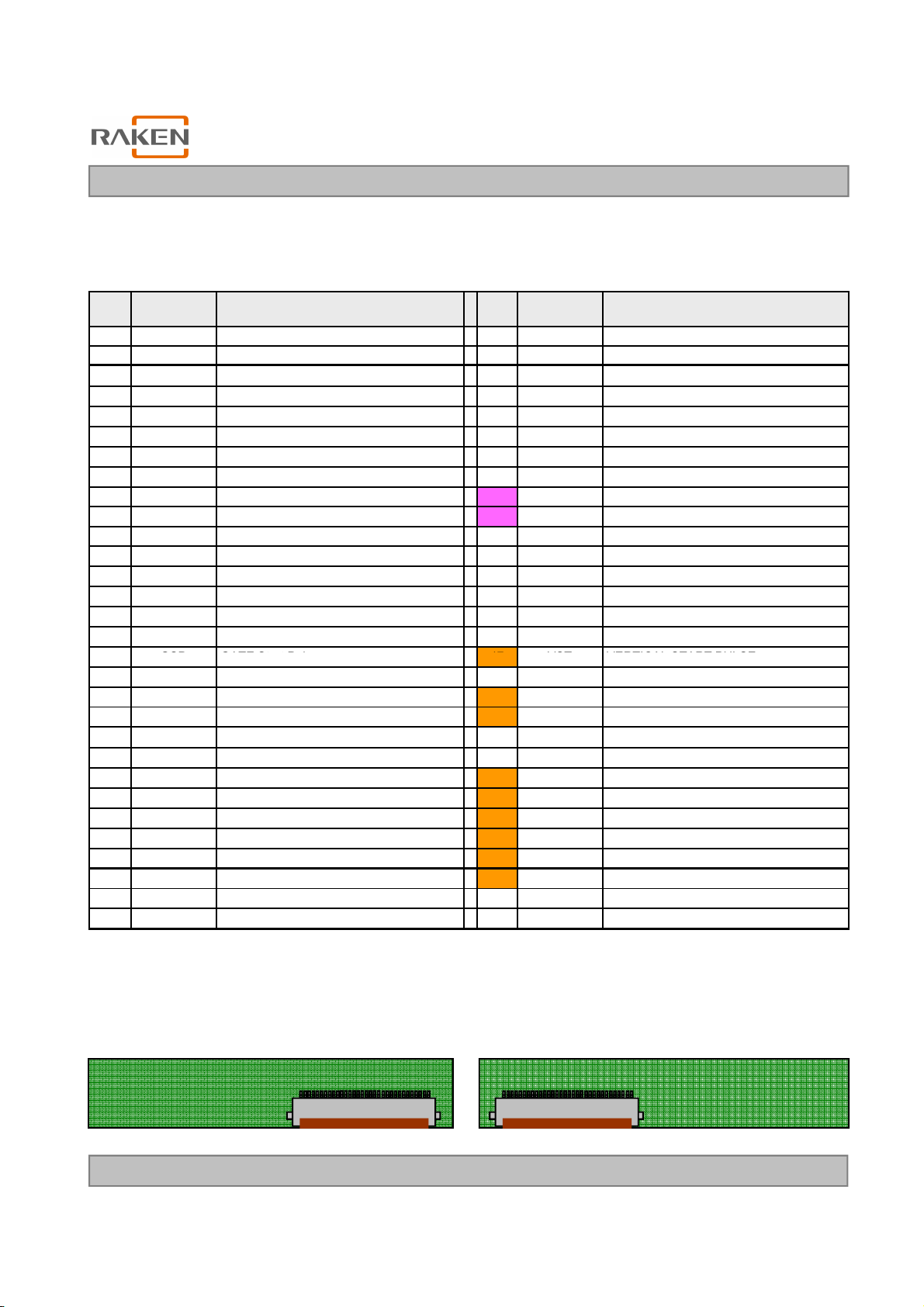

-LCD Connector (CN2): TF06L-60S-0.5SF(Manufactured by HRS) or Equivalent

Table 4-2. MODULE CONNECTOR(CN2) PIN CONFIGURATION

No Symbol Description No Symbol Description

LC420EUH

1

2 GMA 1 GAMMA VOLTAGE 1 (Output From LCD)

3 GMA 3 GAMMA VOLTAGE 3

4 GMA 4 GAMMA VOLTAGE 4

5 GMA 5 GAMMA VOLTAGE 5

6 GMA 7 GAMMA VOLTAGE 7

7 GMA 9 GAMMA VOLTAGE 9 (Output From LCD)

8 GMA 10 GAMMA VOLTAGE 10 (Output From LCD)

9 GMA 12 GAMMA VOLTAGE 12

10 GMA 14 GAMMA VOLTAGE 14

11 GMA 15 GAMMA VOLTAGE 15

12 GMA 16 GAMMA VOLTAGE 16

13 GMA 18 GAMMA VOLTAGE 18 (Output From LCD)

14

15

16

18

19

20

21

22

23

24

25

26

27

28

29

30

GND Ground 31 RLV1 - Right Mini LVDS Receiver Signal(1-)

32 RLV1 + Right Mini LVDS Receiver Signal(1+)

33 RLV0 - Right Mini LVDS Receiver Signal(0-)

34 RLV0 + Right Mini LVDS Receiver Signal(0+)

35 GND Ground

36 VCC Logic Power Supply Voltage

37 VCC Logic Power Supply Voltage

38 GND Ground

39 H_VDD Half Driver Power Supply Voltage

40 H_VDD Half Driver Power Supply Voltage

41 VDD Driver Power Supply Voltage

42 VDD Driver Power Supply Voltage

43 GND Ground

GND Ground 44 VCOM_R VCOM Right Input

OPT_N “H” Normal Display / “L” Rotation Display 45 VCOM_R_FB VCOM Right Feed-Back Output

H_CONV "H“ H 2dot Inversion/ "L" H 1dot Inversion 46 GND Ground

POL Polarity Control Signal 48 VGL GATE Low Voltage

SOE Source Output Enable SIGNAL 49 VGH_EVEN GIP Panel VDD for Even GATE TFT

GND Ground 50 VGH_ODD GIP Panel VDD for Odd GATE TFT

RLV5 - Right Mini LVDS Receiver Signal(5-) 51 VGI_P GIP Bi-Scan (Normal =VGH Rotate = VGL)

RLV5 + Right Mini LVDS Receiver Signal(5+) 52 VGI_N GIP Bi-Scan (Normal =VGL Rotate = VGH)

RLV4 - Right Mini LVDS Receiver Signal(4-) 53 GCLK6 GIP GATE Clock 6

RLV4 + Right Mini LVDS Receiver Signal(4+) 54 GCLK5 GIP GATE Clock 5

RLV3 - Right Mini LVDS Receiver Signal(3-) 55 GCLK4 GIP GATE Clock 4

RLV3 + Right Mini LVDS Receiver Signal(3+) 56 GCLK3 GIP GATE Clock 3

LCLK - Right Mini LVDS Receiver Clock Signal(-) 57 GCLK2 GIP GATE Clock 2

LCLK + Right Mini LVDS Receiver Clock Signal(+) 58 GCLK1 GIP GATE Clock 1

RLV2 - Right Mini LVDS Receiver Signal(2-) 59

RLV2 + Right Mini LVDS Receiver Signal(2+) 60 GND Ground

LTD_OUT LTD OUTPUT

Note :

1. Please refer to application note for details

2. These 'input signal' (OPT_N,H_CONV) should be connected

Source Right PCB

Ver. 1.1

(GIP & Half VDD & Gamma Voltage & H_CONV setting)

CN 2

#1 #60

#1 #60

CN 1

Source Left PCB

10 /33

Loading...

Loading...