( ) Preliminary Specification

SUFFIX

RDV2

(●) Final Specification

Title 42.0” WUXGA TFT LCD

LC420EUG

Product Specification

SPECIFICATION

FOR

APPROVAL

BUYER LGE

MODEL

APPROVED BY

/

/

/

SIGNATURE

DATE

SUPPLIER RAKEN Co., Ltd.

*MODEL LC420EUG

*When you obtain standard approval,

please use the above model name without suffix

APPROVED BY

Charlie.Ko/ Team Leader

REVIEWED BY

Power.Zheng/ Engineer

PREPARED BY

Suxi.Jiang/ Engineer

SIGNATURE

DATE

Please return 1 copy for your confirmation with

your signature and comments.

Ver. 1.0

TV R&D LCM Qualification Dept.

RAKEN Co., Ltd.

0 /35

Product Specification

LCM ENGINEERING

SPECIFICATION

*MODEL LC420EUG

SUFFIX RDV2

Update July. 05. 2011

( ) Preliminary Specification

(

) Final Specification

●

LC420EUG

APPROVED BY

Peter. Kim / TV RD Leader

Charlie. Ko / LCM Qualification Leader

Herbert. Jung / EE Dept Leader

Brainy. Jeong / ME Dept Leader

Marco.Du / Power Dept Leader

SIGNATURE DATE

Ver. 1.0

TV R&D Center. RAKEN Co., Ltd.

File No. :________________

1 /35

Product Specification

4

OPTICAL SPECIFICATIONS

17

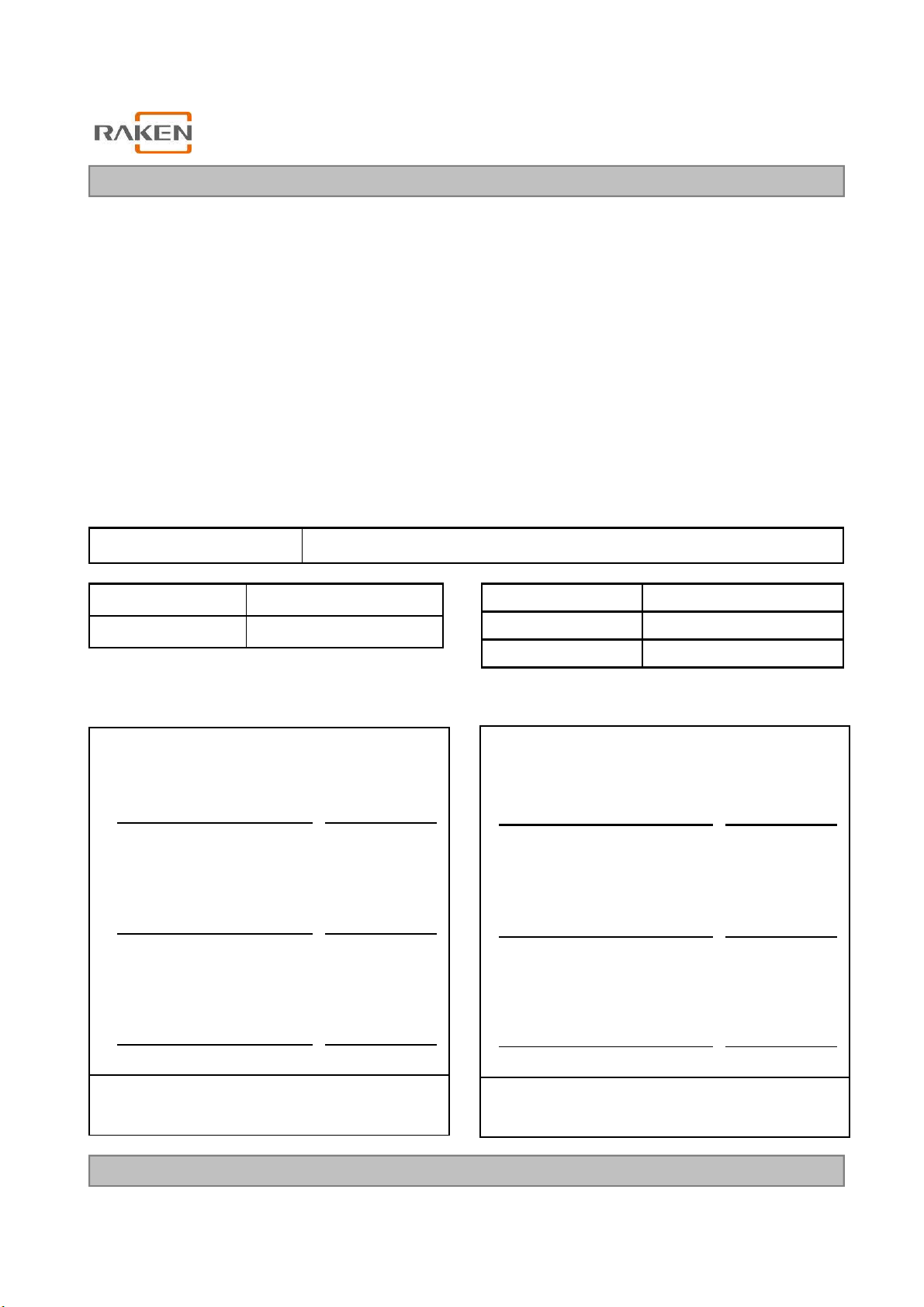

CONTENTS

LC420EUG

Number ITEM

COVER 1

CONTENTS

RECORD OF REVISIONS

1 GENERAL DESCRIPTION

2 ABSOLUTE MAXIMUM RATINGS

3 ELECTRICAL SPECIFICATIONS

3-1 ELECTRICAL CHARACTERISTICS

3-2 INTERFACE CONNECTIONS

3-3 SIGNAL TIMING SPECIFICATIONS

3-4 DATA MAPPING AND TIMING

3-5 Color Data Reference

3-6 POWER SEQUENCE

5 MECHANICAL CHARACTERISTICS

Page

2

3

4

5

6

6

8

10

11

14

15

21

6 RELIABILITY

7 INTERNATIONAL STANDARDS

7-1 ENVIRONMENT

8 PRECAUTIONS

8-1 MOUNTING PRECAUTIONS

8-2 OPERATING PRECAUTIONS

8-3 ELECTROSTATIC DISCHARGE CONTROL

8-4 PRECAUTIONS FOR STRONG LIGHT EXPOSURE

8-5 STORAGE

8-6 HANDLING PRECAUTIONS FOR PROTECTION FILM

Ver. 1.0

26

27

27

28

28

28

29

29

29

29

2 /35

Product Specification

RECORD OF REVISIONS

Revision No. Revision Date Page Description

1.0 July 05, 2011 - Final Specification

LC420EUG

Ver. 1.0

3 /35

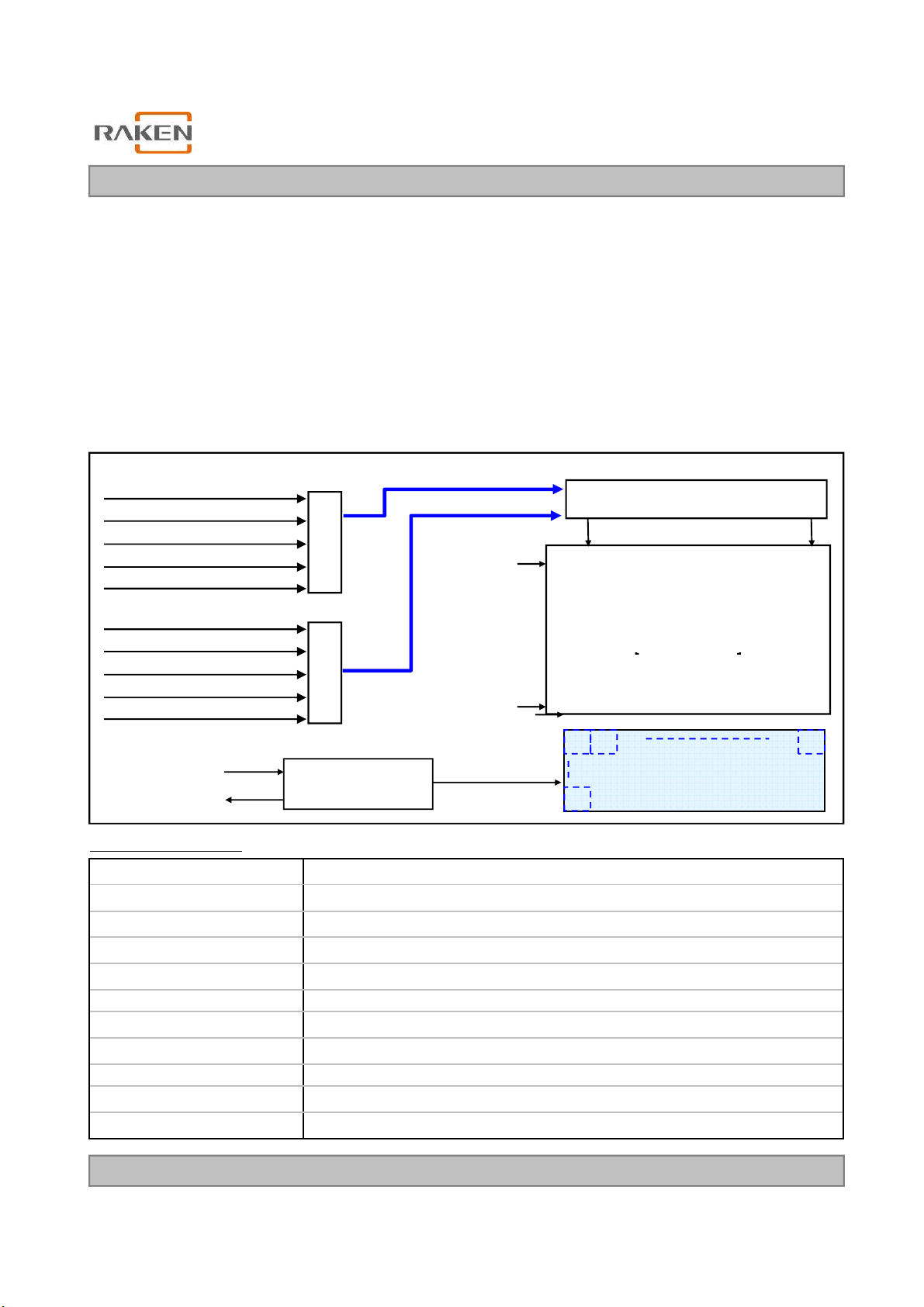

LC420EUG

[Gate In Panel]

[Gate In Panel]

Product Specification

1. General Description

The LC420EUG is a Color Active Matrix Liquid Crystal Display with an integral the Source PCB and Gate

implanted on Panel (GIP). The matrix employs a-Si Thin Film Transistor as the active element.

It is a transmissive type display operating in the normally black mode. It has a 42.02 inch diagonally measured

active display area wi th W UXGA res olution (1 080 vertic al by 1920 hor izo ntal pix el arr a y).

Each pixel is divided into Red, Green and Blue sub-pixels or dots which are arranged in vertical stripes.

Gray scale or the luminance of the sub-pixel color is determined with a 8-bit gray scale signal for each dot.

Therefore, it can present a palette of more than 16.7M(true) colors.

It is intended to support LCD TV, PCTV where high brightness, super wide viewing angle, high color gamut,

high color depth and fast response time are important.

Power (VCC,VDD,HVDD,VGH,VGL)

Source Control Signal

Gate Control Signal

Gamma Reference Voltage

mini-LVDS (RGB) for Left drive

CN1

(60pin)

S1 S1920

G1

Source Driver Circuit

TFT - LCD Panel

Power (VCC,VDD,HVDD,VGH,VGL)

Source Control Signal

Gate Control Signal

Gamma Reference Voltage

mini-LVDS (RGB) for Right drive

LED Anode

LED Cathode

CN2

(60pin)

CN1 (14pin)

G1080

General Features

Active Screen Size 42.02 inches(1067.31mm) diagonal

Outline Dimension

Pixel Pitch 0.4845 mm x 0.4845 mm

Pixel Format 1920 horiz. by 1080 vert. Pixels, RGB stripe arrangement

968.4(H) × 564(V) X 10.8(B)/18.3 mm(D) (Typ.)

(1920 × RGB × 1080 pixels)

H : 5Block

Local Dimming : 10 Block

V : 2Block

Color Depth 8bit, 16,7 M colors

Luminance, White 360 cd/m2 (Center 1point ,Typ.)

Viewing Angle (CR>10) Viewing angle free ( R/L 178 (Min.), U/D 178 (Min.))

Power Consumption Total 92.9W (TBD.) [Logic= 7.3W, LED Backlight=85.6W (Ext.PWM=100%)]

Weight 8.8 Kg (Typ.)

Display Operating Mode Transmissive mode, normally black

Surface Treatment Hard coating(3H), Anti-glare treatment of the front polarizer (Haze 10%)

Ver. 1.0

4 /35

LC420EUG

Operating Ambient Humidity

HOP1090%RH

Product Specification

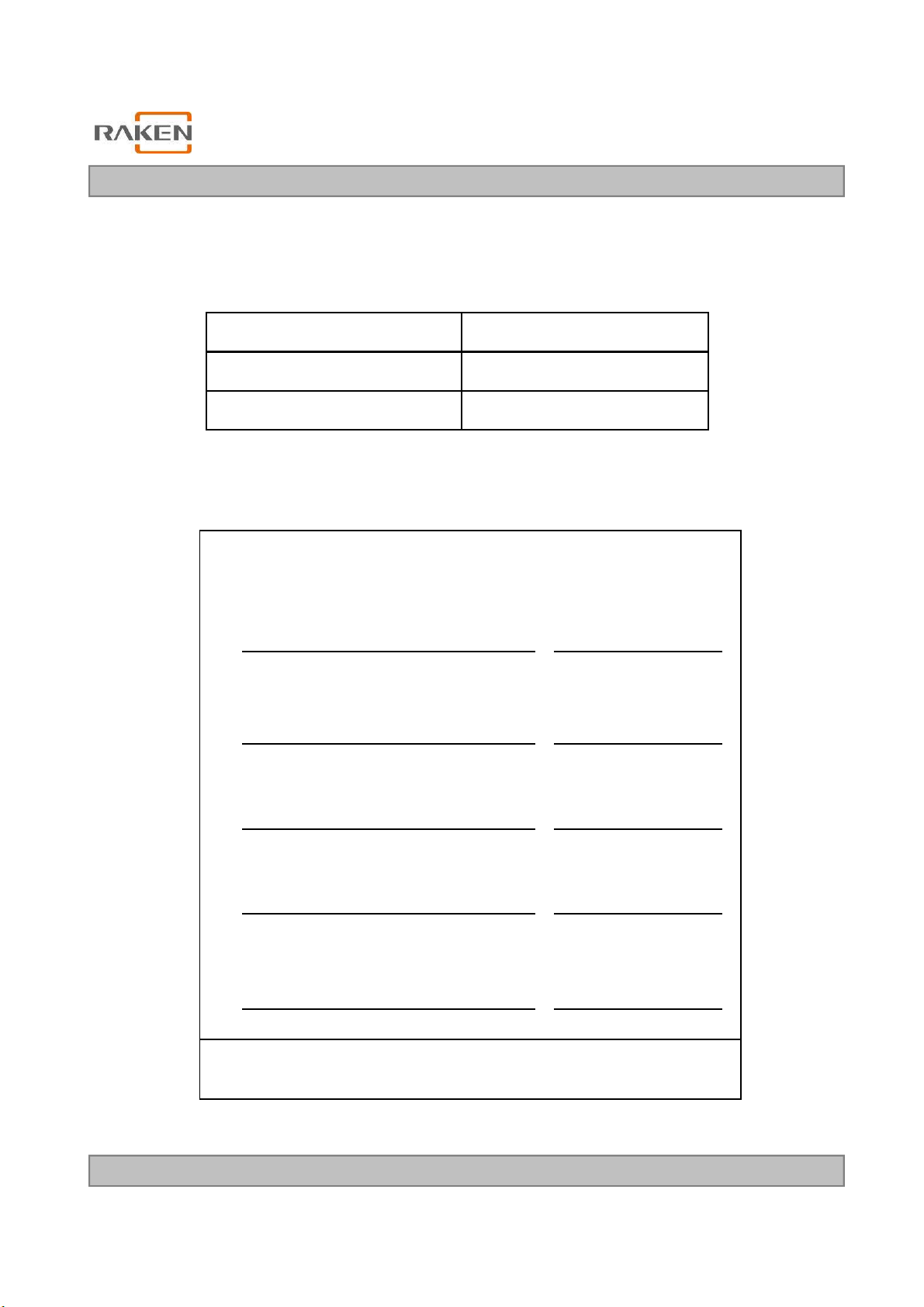

2. Absolute Maximum Ratings

The following items are maximum values which, if exceeded, may cause faulty operation or permanent damage

to the LCD module.

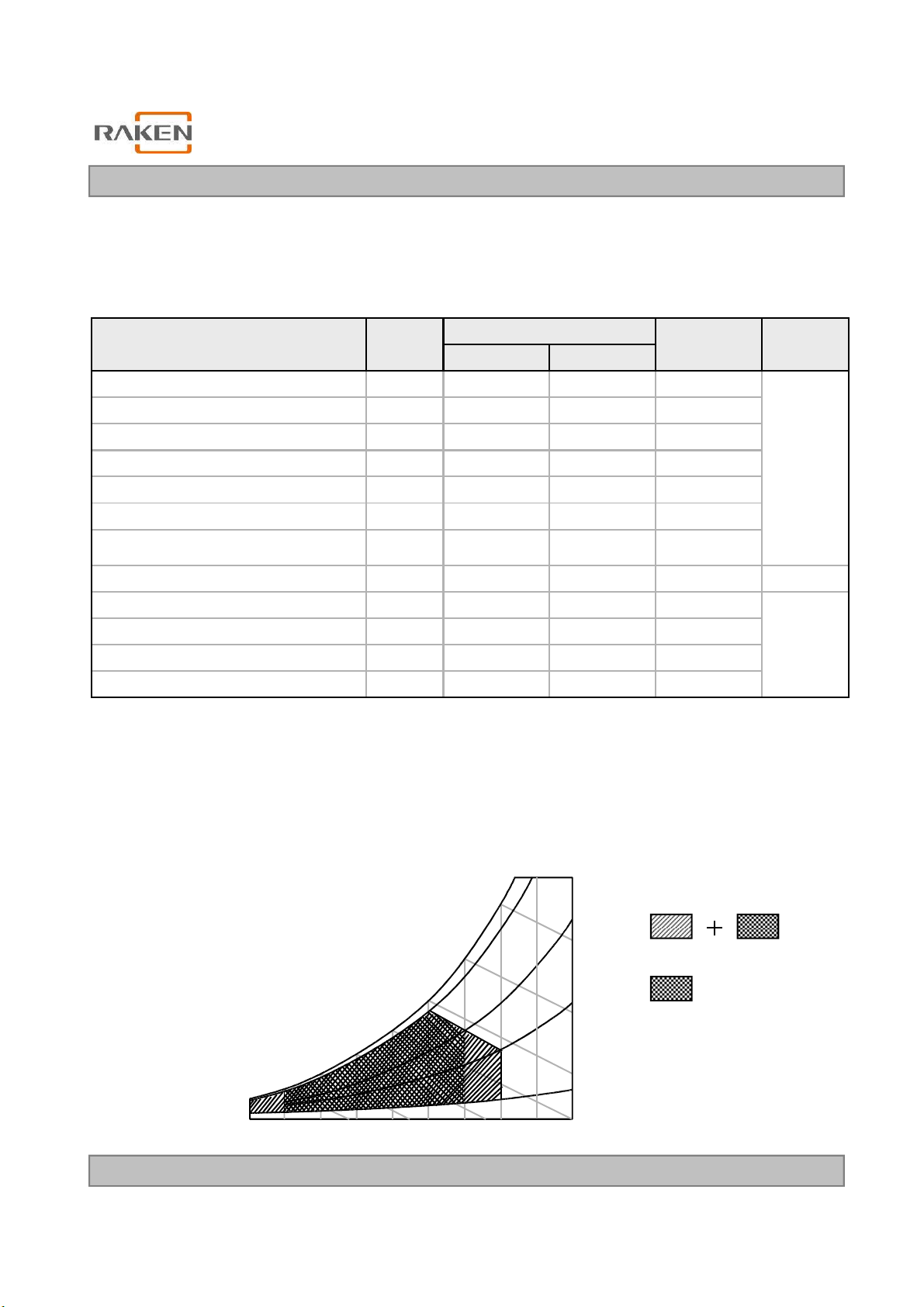

Table 1. ABSOLUTE MAXIMUM RATINGS

Parameter Symbol

Min Max

Logic Power Voltage VCC -0.5 +4.0 VDC

Gate High Voltage VGH +18.0 +30.0 VDC

Gate Low Voltage VGL -8.0 -4.0 VDC

Value

Unit Note

Source D-IC Analog Voltage VDD -0.3 +18.0 VDC

Gamma Ref. Voltage (Upper) VGMH ½VDD-0.5 VDD+0.5 VDC

Gamma Ref. Voltage (Low) VGML -0.3 ½ VDD+0.5 VDC

LED Input voltage (Forward voltage)

Panel Front Temperature TSUR - +68

Operating Temperature TOP 0 +50

Storage Temperature TST -20 +60

Storage Humidity HST 10 90 %RH

Note

1. Ambient temperature condition (Ta = 25 ± 2 °C )

Vf - +TBD VDC

°C

°C

°C

2. Temperature and relative humidity range are shown in the figure below.

Wet bulb temperature should be Max 39°C, and no condensation of water.

3. Gravity mura can be guaranteed below 40°C condition.

4. The maximum operating temperatures is based on the test condition that the surface temperature

of display area is less than or equal to 68°C with LCD module alone in a temperature controlled chamber.

Thermal management should be considered in final product design to prevent the surface temperature of

display area from being over 68℃. The range of operating temperature may be degraded in case of

improper thermal management in final product design.

90%

60

60%

1

4

2,3

Ver. 1.0

Wet Bulb

Temperature [°C]

20

10

0

10 20 30 40 50 60 70 800-20

Dry Bulb Temperature [°C]

30

40

50

40%

10%

Storage

Operation

Humidity [(%)RH]

5 /32

LC420EUG

Mini-LVDS Clock

Distortion (Center)

∆VIB--0.8

V

Product Specification

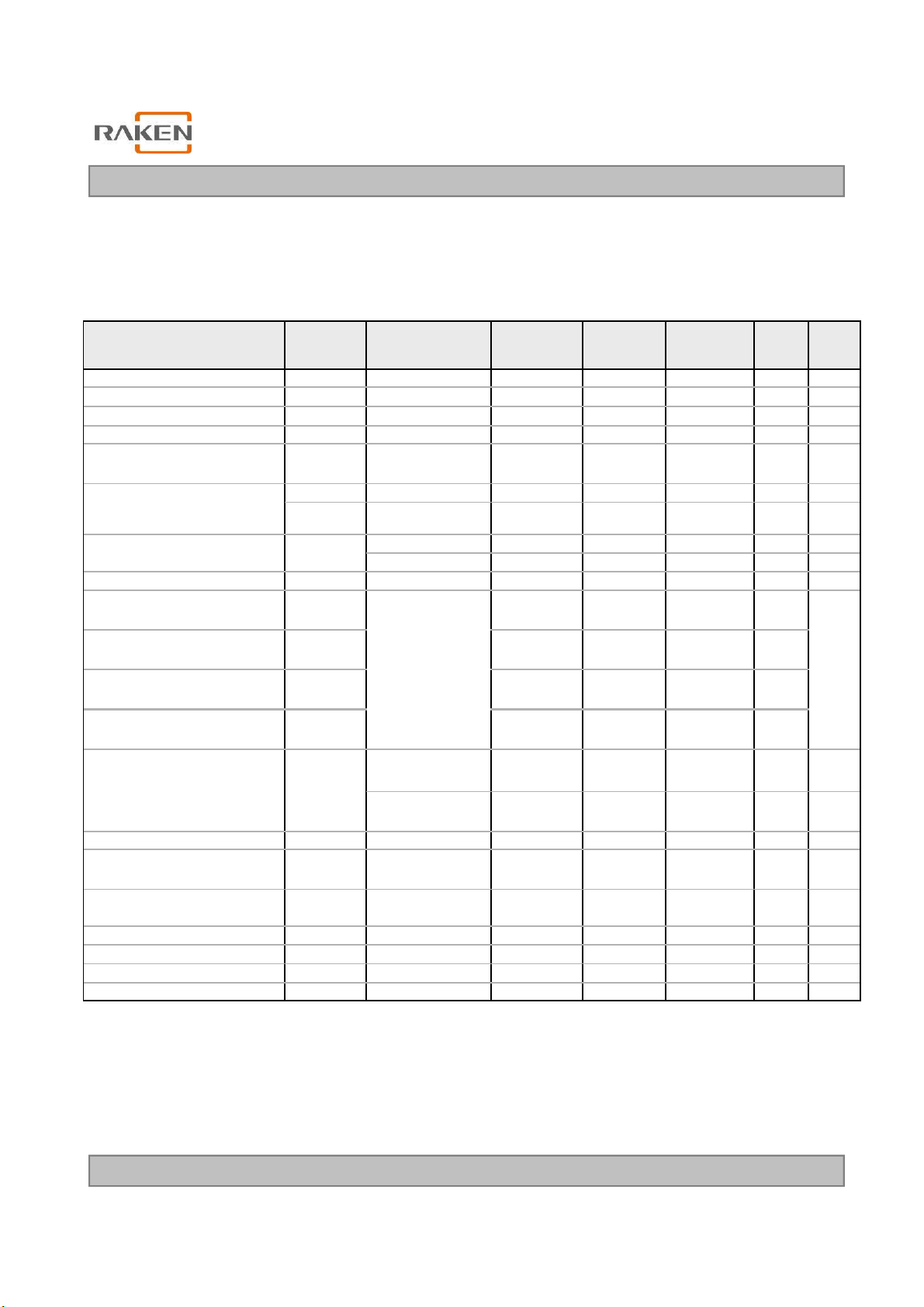

3. Electrical Specifications

3-1. Electrical Characteristics

It requires several power inputs. The VCC is the basic power of LCD Driving power sequence, Which is used

to logic power voltage of Source D-IC and GIP.

Table 2. ELECTRICAL CHARACTERISTICS

Parameter Symbol Condition MIN TYP MAX Unit

Logic Power Voltage VCC - 3.0 3.3 3.6 VDC

Logic High Level Input Voltage VIH - 2.7 - VCC VDC

Logic Low Level Input Voltage VIL - 0 - 0.6 VDC

Source D-IC Analog Voltage VDD - 16.5 16.7 16.9 VDC

Half Source D-IC Analog

Voltage

Gamma Reference Voltage

Common Voltage Vcom

Mini-LVDS Clock frequency CLK 3.0V≤VCC ≤3.6V - 156 MHz

mini-LVDS input Voltage

(Center)

mini-LVDS input Voltage

H_VDD - 8.05 8.35 8.55 VDC 7

V

V

GMH

GML

VIB

(GMA1 ~ GMA9) 8.35 - 16.5 VDC

(GMA10 ~ GMA18) 0.2 - 8.35 VDC

Normal 6.75 7.05 7.35 V

Reverse 6.75 7.05 7.35 V

0.7 + (VID/2) -

(VCC-1.2)

− VID / 2

V

Not

e

mini-LVDS differential

Voltage range

mini-LVDS differential

Voltage range Dip

Gate High Voltage VGH

Gate Low Voltage VGL - -5.2 -5.0 -4.8 VDC

GIP Bi-Scan Voltage

GIP Refresh Voltage

GIP Start Pulse Voltage VST - VGL - VGH V

GIP Operating Clock GCLK - VGL - VGH V

Total Power Current

Total Power Consumption

1. The specified current and power consumption are under the VLCD=12V., 25 ± 2°C, f

Note:

VID 200 - 800 mV

∆VID 25 - 800 mV

VGI_P

VGI_N

VGH

even/odd

ILCD - 610 790 mA 1

PLCD - 7.32 8.05 Watt 1

and Data

@ 25℃

@ 0℃

- VGL - VGH VDC

- VGL - VGH V

27.7 28 28.3 VDC

28.7 29 29.3 VDC

=60Hz

V

condition whereas mosaic pattern(8 x 6) is displayed and fVis the frame frequency.

2. The above spec is based on the basic model.

3. All of the typical gate voltage should be controlled within 1% voltage level

4. Ripple voltage level is recommended under 10%

5. In case of mini-LVDS signal spec, refer to Fig 2 for the more detail.

6. Logic Level Input Signal : SOE,POL,GSP

7. HVDD Voltage level is half of VDD and it should be between Gamma9 and Gamma10.

Ver. 1.0

5

6 /35

VCM (0V)

VIB

VIB VIB

VIB

VIB

VIB VIB

VIB

VCM (0V)

VCM (0V) VCM (0V)

VGH

VGHM

GND

VGL

VID

VID

VIDVID

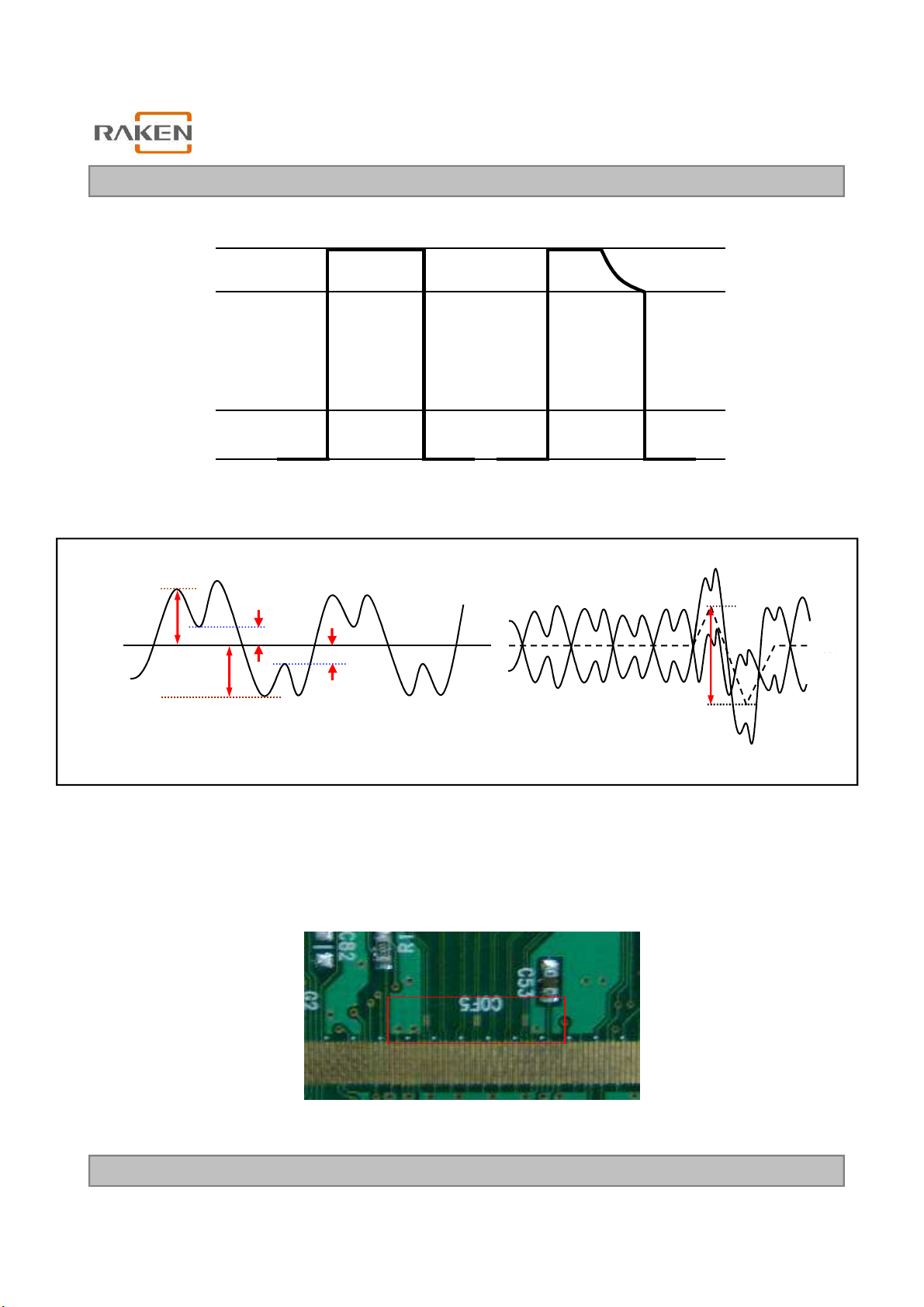

Product Specification

Without GPM With GPM

FIG. 1 Gate Output Wave form without GPM and with GPM

△△△△VID

VID

VID VID

△△△△VIB

VIB

VIBVIB

LC420EUG

VID

VID

VIDVID

*

* Differential Probe

Differential Probe

* *

Differential ProbeDifferential Probe

△△△△VID

VID

VID VID

*

* Active Probe

Active Probe

* *

Active ProbeActive Probe

FIG. 2 Description of VID, ∆VIB, ∆VID

*

* S o u rc e P C B

S o u rce P C B

* *

S o u rce P C BS o u rce P C B

FIG. 3 Measure point

Ver. 1.0

7 /35

Product Specification

Table 3. ELECTRICAL CHARACTERISTICS (Continue)

LC420EUG

Parameter Symbol

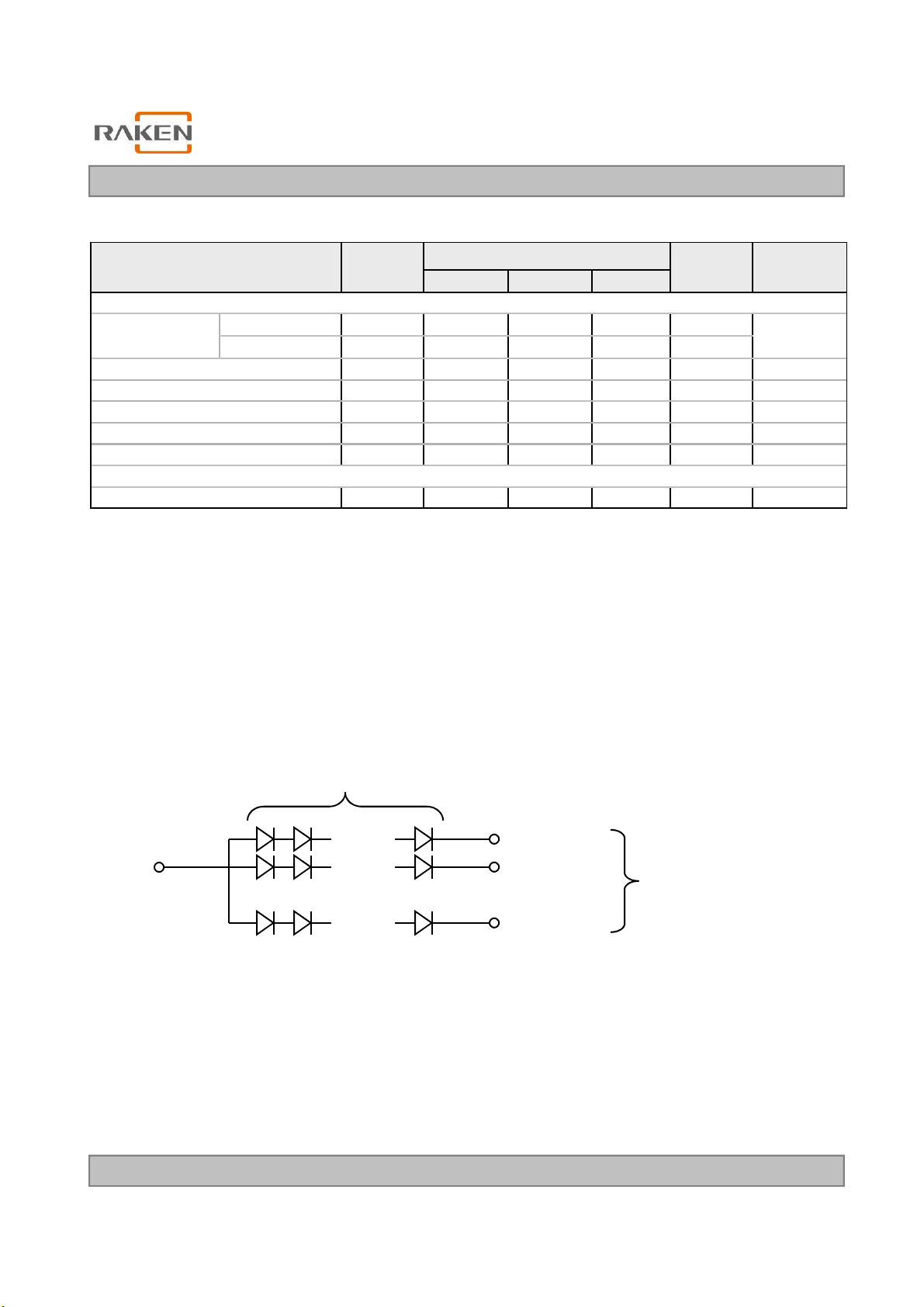

Backlight Assembly :

Forward Current

(one array)

Forward Voltage V

Forward Voltage Variation

Power Consumption P

Burst Dimming Duty On duty 1 90 %

Burst Dimming Frequency 1/T 95 182 Hz 8

LED Array : (APPENDIX-V)

Life Time 30,000 50,000 Hrs 7

The design of the LED driver must have specifications for the LED array in LCD Assembly.

Note :

Anode I

Cathode I

F (anode)

F (cathode)

F

△V

F

BL

Min Typ Max

99.8 105 110.3 mAdc

63.8 70.4 77.0 Vdc 4

- 85.6 95.0 W 6

Values

525 mAdc

1.7 Vdc 5

Unit Note

The electrical characteristics of LED driver are based on Constant Current driving type.

The performance of the LED in LCM, for example life time or brightness, is extremely influenced by the

characteristics of the LED Driver. So, all the parameters of an LED driver should be carefully designed.

When you design or order the LED driver, please make sure unwanted lighting caused by the mismatch of the

LED and the driver (no lighting, flicker, etc) has never been occurred. When you confirm it, the LCD–

Assembly should be operated in the same condition as installed in your instrument.

1. Electrical characteristics are based on LED Array specification.

2. Specified values are defined for a Backlight Assembly. (IBL : 2 LED array, 525mA/LED array)

3. Each LED array has one anode terminal and five cathode terminals.

The forward current(I

) of the anode terminal is 525mA and it supplies 105mA into five strings, respectively

F

11(LED Pakage / 1string)

±5%

2, 3

Anode

° ° °

° ° °

° ° °

° ° °

Cathode #1

Cathode #2

5 (LED String / 1 Array)

Cathode #5

4. The forward voltage(VF) of LED array depends on ambient temperature (Appendix-V)

5. ∆VFmeans Max VF-Min VFin one Backlight. So VFvariation in a Backlight isn’t over Max. 1.7V

6. Maximum level of power consumption is measured at initial turn on.

Typical level of power consumption is measured after 1hrs aging at 25 ± 2°C.

7. The life time(MTTF) is determined as the time at which brightness of the LED is 50% compared to that of

initial value at the typical LED current on condition of continuous operating at 25 ± 2°C, based on duty 100%.

8. The reference method of burst dimming duty ratio.

It is recommended to use synchronous V-sync frequency to prevent waterfall

(Vsync x 1 =Burst Frequency)

Though PWM frequency is over 182Hz (max252Hz), function of backlight is not affected.

Ver. 1.0

8 /35

LC420EUG

Product Specification

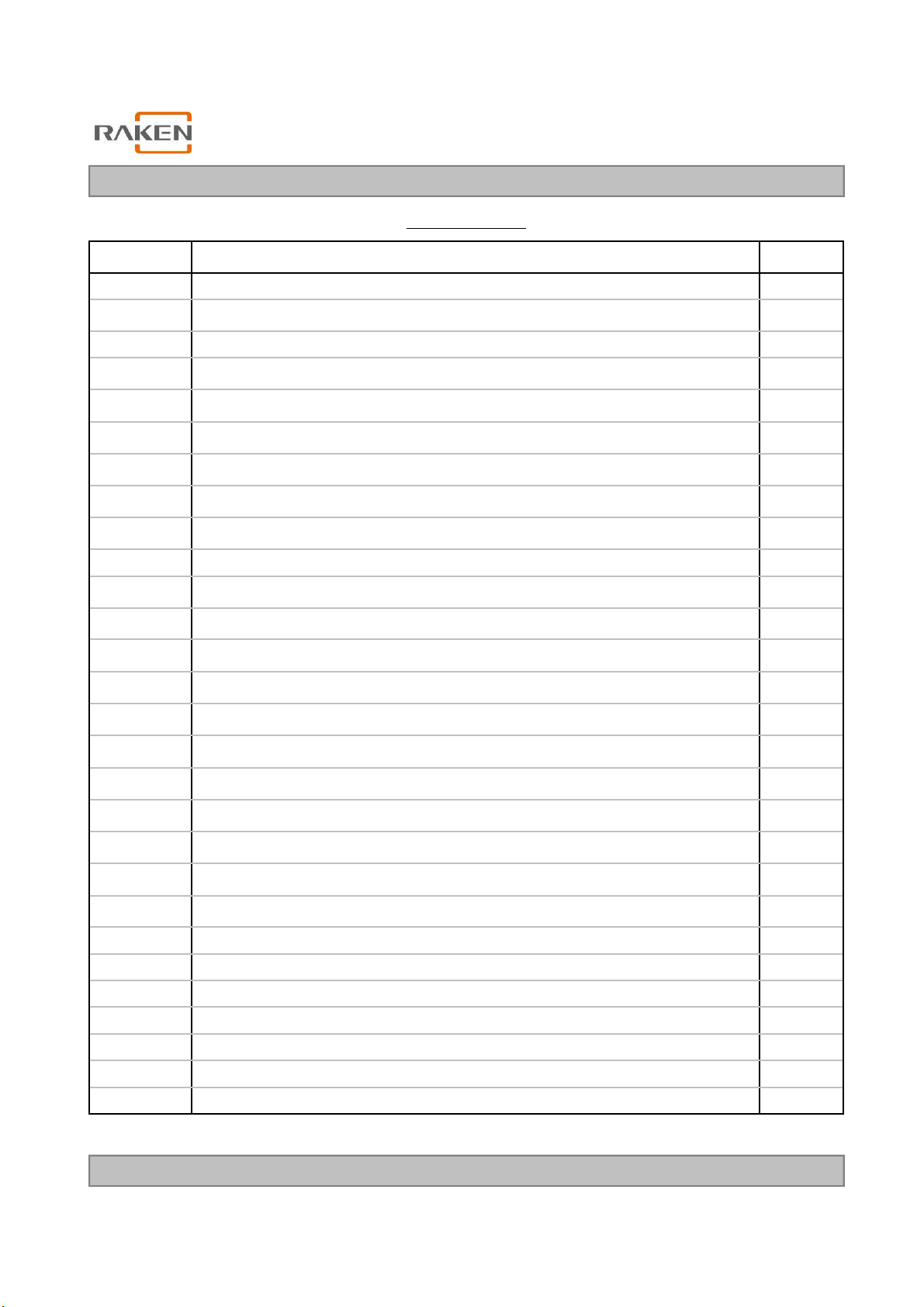

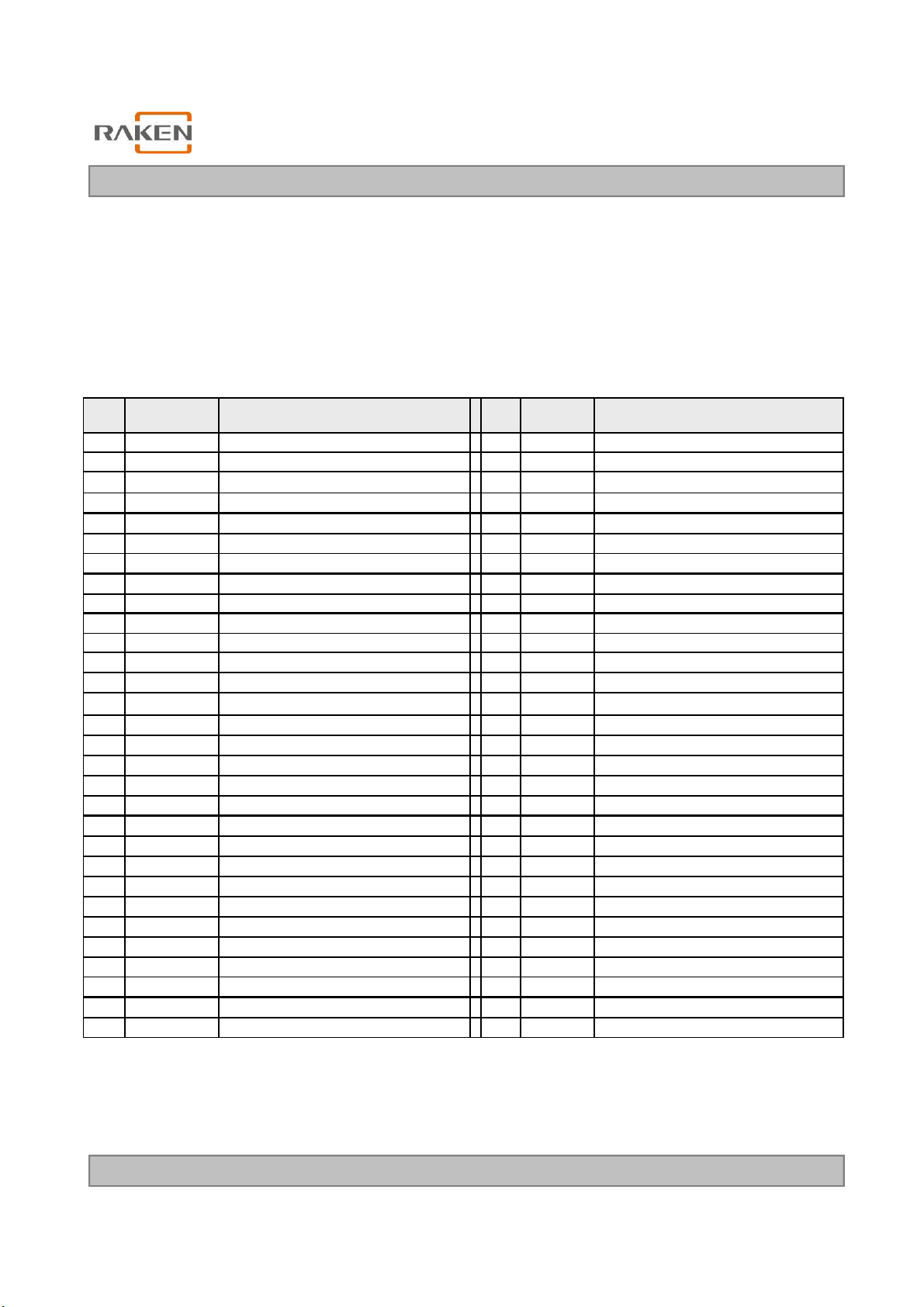

3-2. Interface Connections

This LCD module employs two kinds of interface connection, two 60-pin FFC connector are used for the

module electronics.

3-2-1. LCD Module

-LCD Connector (CN1): TF06L-60S-0.5SH (Manufactured by HRS)

Table 3-1. MODULE CONNECTOR(CN1) PIN CONFIGURATION

No Symbol Description No Symbol Description

1 LTD_OUT LTD OUTPUT

2 NC No Connection

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28 NC No Connection

29 NC No Connection

30 NC No Connection

GCLK1 GIP GATE Clock 1 33

GCLK2 GIP GATE Clock 2 34 LCLK - Left Mini LVDS Receiver Clock Signal(-)

GCLK3 GIP GATE Clock 3 35 LCLK + Left Mini LVDS Receiver Clock Signal(+)

GCLK4 GIP GATE Clock 4 36 LLV2 - Left Mini LVDS Receiver Signal(2-)

GCLK5 GIP GATE Clock 5 37 LLV2 + Left Mini LVDS Receiver Signal(2+)

GCLK6 GIP GATE Clock 6 38 LLV1 - Left Mini LVDS Receiver Signal(1-)

VGI_N GIP Bi-Scan (Normal =VGL Rotate = VGH) 39 LLV1 + Left Mini LVDS Receiver Signal(1+)

VGI_P GIP Bi-Scan (Normal =VGH Rotate = VGL) 40 LLV0 - Left Mini LVDS Receiver Signal(0-)

VGH_ODD GIP Panel VDD for Odd GATE TFT 41 LLV0 + Left Mini LVDS Receiver Signal(0+)

VGH_EVEN GIP Panel VDD for Even GATE TFT 42 GND Ground

VGL GATE Low Voltage 43 SOE Source Output Enable SIGNAL

VST VERTICAL START PULSE 44 POL Polarity Control Signal

GIP_Reset GIP Reset 45 GSP GATE Start Pulse

VCOM_L_FB VCOM Left Feed-Back Output 46 H_CONV "H“ H 2dot Inversion/ "L" H 1dot Inversion

VCOM_L VCOM Left Input 47 OPT_N “H” Normal Display / “L” Rotation Display

GND Ground 48 GND Ground

GND Ground 49

VDD Driver Power Supply Voltage 50

VDD Driver Power Supply Voltage 51

H_VDD Half Driver Power Supply Voltage 52

H_VDD Half Driver Power Supply Voltage 53

GND Ground 54

VCC Logic Power Supply Voltage 55

VCC Logic Power Supply Voltage 56

GND Ground 57

31

32

58

59

60

NC No Connection

NC No Connection

NC No Connection

GMA 18 GAMMA VOLTAGE 18 (Output From LCD)

GMA 16 GAMMA VOLTAGE 16

GMA 15 GAMMA VOLTAGE 15

GMA 14 GAMMA VOLTAGE 14

GMA 12 GAMMA VOLTAGE 12

GMA 10 GAMMA VOLTAGE 10 (Output From LCD)

GMA 9 GAMMA VOLTAGE 9 (Output From LCD)

GMA 7 GAMMA VOLTAGE 7

GMA 5 GAMMA VOLTAGE 5

GMA 4 GAMMA VOLTAGE 4

GMA 3 GAMMA VOLTAGE 3

GMA 1 GAMMA VOLTAGE 1(Output From LCD)

Note :

1. Please refer to application note for details.

(GIP & Gamma Voltage setting)

Ver. 1.0

9 /35

Product Specification

17

POL

Polarity Control Signal

47

VST

VERTICAL START PULSE

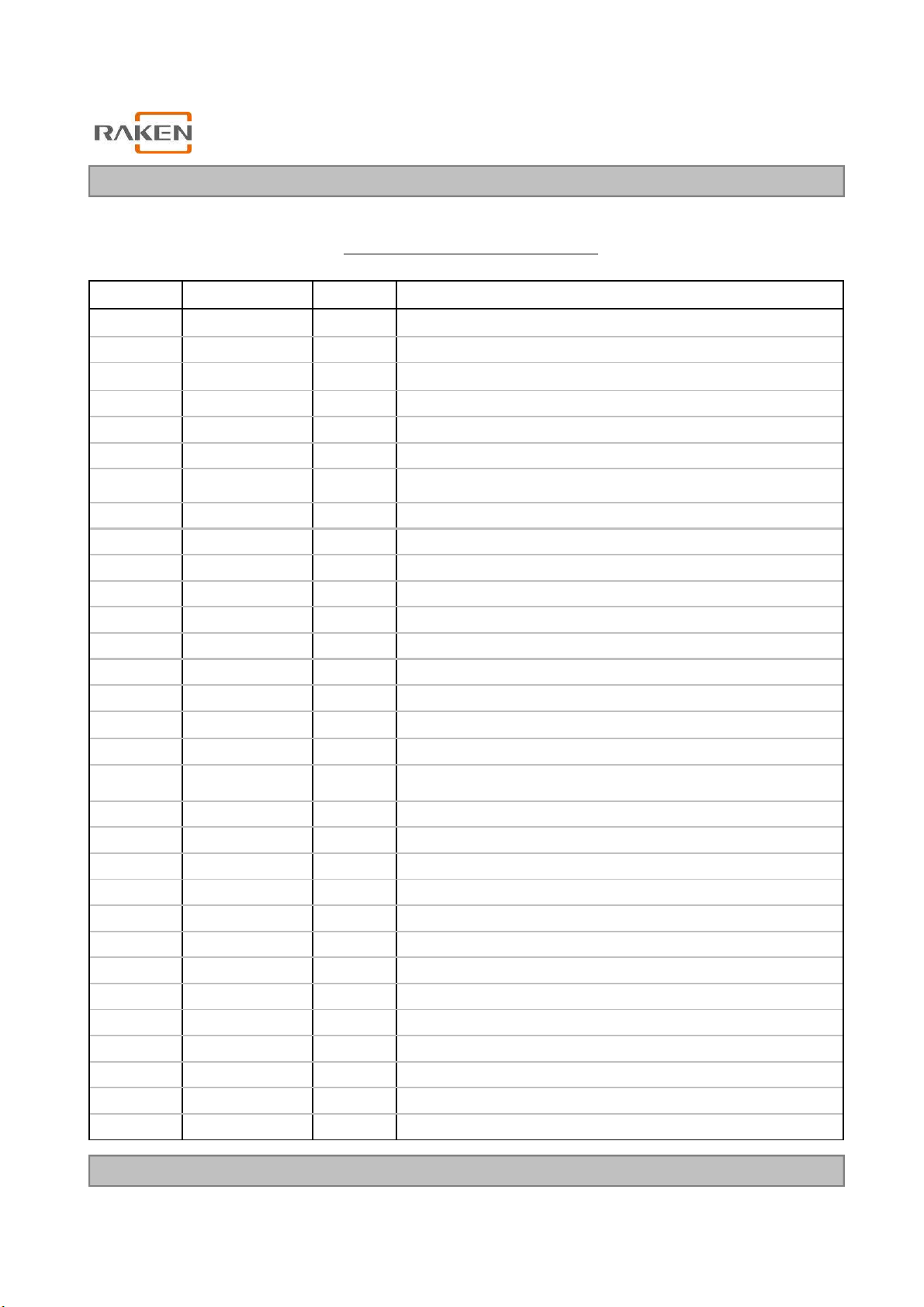

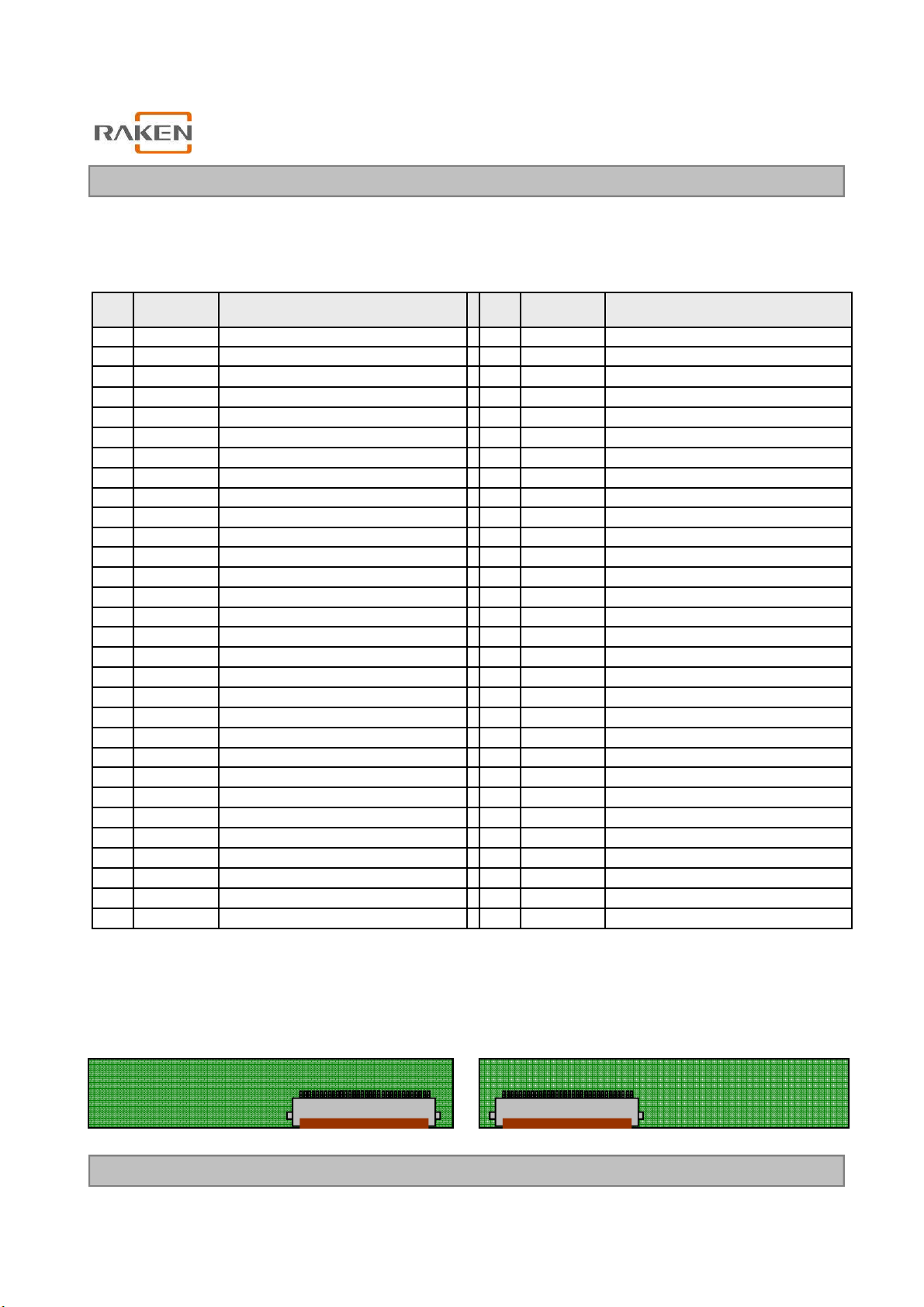

-LCD Connector (CN2): TF06L-60S-0.5SH(Manufactured by HRS)

Table 3-2. MODULE CONNECTOR(CN2) PIN CONFIGURATION

No Symbol Description No Symbol Description

LC420EUG

1 GMA 1 GAMMA VOLTAGE 1 (Output From LCD)

2 GMA 3 GAMMA VOLTAGE 3

3 GMA 4 GAMMA VOLTAGE 4

4 GMA 5 GAMMA VOLTAGE 5

5 GMA 7 GAMMA VOLTAGE 7

6 GMA 9 GAMMA VOLTAGE 9 (Output From LCD)

7 GMA 10 GAMMA VOLTAGE 10 (Output From LCD)

8 GMA 12 GAMMA VOLTAGE 12

9 GMA 14 GAMMA VOLTAGE 14

10 GMA 15 GAMMA VOLTAGE 15

11 GMA 16 GAMMA VOLTAGE 16

12 GMA 18 GAMMA VOLTAGE 18 (Output From LCD)

13

14

15

16

18

19

20 NC No Connection

21 NC No Connection

22 NC No Connection

23 NC No Connection

24 NC No Connection

25 NC No Connection

26

27

28

29

30

GND Ground 43 GND Ground

OPT_N “H” Normal Display / “L” Rotation Display 44 VCOM_R VCOM Right Input

H_CONV "H“ H 2dot Inversion/ "L" H 1dot Inversion 45 VCOM_R_FB VCOM Right Feed-Back Output

GSP GATE Start Pulse 46 GIP_Reset GIP Reset

SOE Source Output Enable SIGNAL 48 VGL GATE Low Voltage

GND Ground 49 VGH_EVEN GIP Panel VDD for Even GATE TFT

RCLK - Right Mini LVDS Receiver Clock Signal(-) 56 GCLK3 GIP GATE Clock 3

RCLK + Right Mini LVDS Receiver Clock Signal(+) 57 GCLK2 GIP GATE Clock 2

RLV2 - Right Mini LVDS Receiver Signal(2-) 58 GCLK1 GIP GATE Clock 1

RLV2 + Right Mini LVDS Receiver Signal(2+) 59

RLV1 - Right Mini LVDS Receiver Signal(1-) 60

31 RLV1 + Right Mini LVDS Receiver Signal(1+)

32 RLV0 - Right Mini LVDS Receiver Signal(0-)

33 RLV0 + Right Mini LVDS Receiver Signal(0+)

34 GND Ground

35 VCC Logic Power Supply Voltage

36 VCC Logic Power Supply Voltage

37 GND Ground

38 H_VDD Half Driver Power Supply Voltage

39 H_VDD Half Driver Power Supply Voltage

40 VDD Driver Power Supply Voltage

41 VDD Driver Power Supply Voltage

42 GND Ground

50 VGH_ODD GIP Panel VDD for Odd GATE TFT

51 VGI_P GIP Bi-Scan (Normal =VGH Rotate = VGL)

52 VGI_N GIP Bi-Scan (Normal =VGL Rotate = VGH)

53 GCLK6 GIP GATE Clock 6

54 GCLK5 GIP GATE Clock 5

55 GCLK4 GIP GATE Clock 4

NC No Connection

LTD_OUT LTD OUTPUT

Note :

Source Right PCB

Ver. 1.0

1. Please refer to application note for details

(GIP & Gamma Voltage setting)

CN 2

#1 #60

CN 1

Source Left PCB

#1 #60

10 /35

Product Specification

3-2-2. Backlight Module

- LED Array assy Connector(Plug) : 20022HS - 14B2 or Equivalent

- Mating Connector(Receptacle) : 20022WR - H14B1 (Yeonho) or Equivalent

Table 5. BACKLIGHT CONNECTOR PIN CONFIGURATION(CN201,CN202)

Pin No Symbol Description Note

LC420EUG

1

Anode R1~R5 LED Input Current

2

3

4

5

6

7

8

9

10

11

12

R1 Cathode LED Output Current

R2 Cathode LED Output Current

R3 Cathode LED Output Current

R4 Cathode LED Output Current

R5 Cathode LED Output Current

L5 Cathode LED Output Current

L4 Cathode LED Output Current

L3 Cathode LED Output Current

L2 Cathode LED Output Current

L1 Cathode LED Output Current

13

14

Anode L1~L5 LED Input Current

◆ Rear view of LCM

N.C Open

N.C Open

Ver. 1.0

14pin

L5

L5

L5

L5

L4

L4

L4

L4

L3

L3

L3

L3

L2

L2

L2

L2

L1

L1

L1

L1

1

CN201

T-con

R5

R5

R5

R5

R4

R4

R4

R4

R3

R3

R3

R3

R2

R2

R2

R2

R1

R1

R1

R1

11 /35

3-3. Signal Timing Specifications

Reset High Period

T

13

-3-

-

Table 4. Timing Requirements

Parameter Symbol Condition Min Typ Max Unit Note

LC420EUG

Product Specification

Mini Clock pulse period

Mini Clock pulse low period

Mini Clock pulse high period

Mini Data setup time

Mini Data hold time

Reset low to SOE rising time

SOE to Reset input time

Receiver off to SOE timing

POL signal to SOE setup time

POL signal to SOE hold time

SOE signal GSP setup time

SOE signal GSP Hold time

SOE signal Pulse Width

Note :

1. Mini-LVDS timing measure conditions

: 268MHz < Clock Frequency < 312MHz , 200mV < VID < 800mV @ 3.0<VCC<3.3

2. Setup time and hold time couldn’t be satisfied at the same time

T1

T2

T3

T6

T7

T8

T9

T10

T11

T12

T14

T15

T16

- 3.2 3.4 - ns

- 1.6 - - ns

- 1.6 - - ns

- 0.55 - - ns

- 0.55 - - ns

- 0 - - ns

- 200 - - ns

- 10 - -

- -5 - - ns

- 6 - - ns

- 100 - - ns

- 100 - - ns

- 200 - - ns

CLK

cycle

CLK

cycle

1

Ver. 1.0

CLK-

CLK+

LV0+, -

to

LV2+,-

T1

70%

T7

T2

T5

70%

30%

T5

30%

30%

30%

T4

70%

T4

T6 T7

50%

T3

T6

FIG 4. Source D-IC Input Data Latch Timing Waveform

70%

VDIFF

VDIFF

12 /35

Product Specification

LC420EUG

CLK+

LV0+,-

LV1+,LV2+,-

SOE

Read The Reset=H

Read The Reset=L 1stDATA

T1

T2

T3

NA

R=H R=H R=H NAR=L R=L NA D D DR=L DD

T13

NA

T8

70%

30%

NA NA NA NANA NA NA D D DNA DD

T9

FIG 5-1. Input Data Timing for 1stSource D-IC Chip

Last DATA

Ver. 1.0

CLK+

LV0+,-

LV1+,LV2+,-

SOE

(640)

D D D

D D D

(641)

NA NA NA NA NA R=LNA R=L R=L

NA NA NA NA NA NANA NA NA

T10

FIG 5-2. Last Data Latch to SOE Timing

T8

70%

30%

13 /35

Product Specification

LC420EUG

SOE

POL

GSP

GSP

70%

T16

T14

T11

70%

30%

30%

70%

T15

T12

70%

30%

70%

30%

70%

Ver. 1.0

SOE

1stline data 1stline output

FIG 6. POL, GSP and SOE Timing Waveform

14 /35

Product Specification

3-4. Data Mapping and Timing

Display data and control signal (RESET) are input to LV0 to LV2.

3-4-1. Control signal input mode

CLK +

LC420EUG

LV0 +

RESET RESET RESET RESET RESET RESET RESET RESET RESET RESET

3-4-2. Display data input mode

CLK+

LV0+

LV1+

LV2+

Note :

1. For data mapping, please refer to panel pixel structure Fig.8

D01 D02 D03 D04 D05 D06D00

D11 D12 D13 D14 D15 D16D10 D17

D21 D22 D23 D24 D25 D26D20 D27

DATA INPUT CYCLE

D07 D00

Fig. 7 Mini-LVDS Data

D10

D20

Ver. 1.0

15 /35

3-5. Panel Pixel Structure

G1078

D1 D2 D3 D4 D5 D1918 D1919 D1920 D1921

G1

G2

G3

G4

G5

G6

LC420EUG

Product Specification

G1079

G1080

FIG. 8 Panel Pixel Structure

Ver. 1.0

16 /35

3-6. Power Sequence

..

GCLK

1~6

..

3-6-1. LCD Driving circuit

Power Supply For LCD VCC

Power Supply For LCD

VDD,VGH, Gamma Ref.

Voltage

Power Supply For LCD

VGL

0V

0V

Product Specification

70%

50%

100%

T1

T2

VGH

90%

LC420EUG

T7

GIP Signal For LCD

Power For LED

Table 3. POWER SEQUENCE

Parameter

T1 0.5 - - ms

T2 0.5 -

T3 0 -

T4 10 T5 0 - - ms

T6 / T6’ 20 - - ms 6

T7 2 - - s

VGH

even/Odd

VST

T3

T4

T5

T6

Value

Min Typ Max

-

-

-

..

..

T6’

LED on

Ta= 25±2°C, fV=60Hz,

Unit Notes

ms

ms

ms 2

Note : 1. Power sequence for Source D-IC must follow the Case1 & 2.

※ Please refer to Appendix IV for more details.

2. VGH Odd signal should be started “High” status and VGH even & odd can not be “High at the

same time.

3. Power Off Sequence order is reverse of Power On Condition including Source D-IC.

4. GCLK On/Off Sequence

Normal : GCLK4 GCLK5 GCLK6 GCLK1 GCLK2 GCLK3.

Reverse :GCLK3 GCLK2 GCLK1 GCLK6 GCLK5 GCLK4.

5. VDD_odd/even transition time should be within V_blank

6. In case of T6’, If there is no abnormal display, no problem

Ver. 1.0

17 /35

LC420EUG

Contrast Ratio

CR

1000

1400

-

1

Product Specification

4. Optical Specification

Optical characteristics are determined after the unit has been ‘ON’ and stable in a dark environment at 25±2°C.

The values are specified at distance 50cm from the LCD surface at a viewing angle of Φ and θ equal to 0 °.

FIG. 1 shows additional information concerning the measurement equipment and method.

Optical Stage(x,y)

LCD Module

Pritchard 880 or

equivalent

50cm

FIG. 1 Optical Characteristic Measurement Equipment and Method

Table 10. OPTICAL CHARACTERISTICS

Ta= 25±2°C, V

=12.0V, fV=60Hz, Dclk=72.4MHz,

LCD

EXTVBR_B=100%

Value

Parameter Symbol

Unit Note

Min Typ Max

Surface Luminance, white L

Luminance Variation δ

Response Time

Color Coordinates

[CIE1931]

Color Temperature 10,000 K

Color Gamut 68 %

Viewing Angle (CR>10)

Gray Scale - 7

Variation G to G

Gray to Gray(BW) G to G BW 8 12 ms 4

RED

GREEN

BLUE

WHITE

x axis, right(φ=0°)

x axis, left (φ=180°)

y axis, up (φ=90°)

y axis, down (φ=270°)

WH

5P - - 1.3 3

WHITE

σ

Rx

Ry 0.341

Gx 0.325

Gy 0.600

Bx 0.152

By 0.051

Wx 0.279

Wy 0.292

θr 89 - -

θl 89 - -

θu 89 - -

θd 89 - -

290 360 cd/m

6 9 ms 5

0.637

Typ

-0.03

Typ

+0.03

2

degree 6

2

Ver. 1.0

18 /35

Product Specification

6. Viewing angle is the angle at which the contrast ratio is greater than 10. The angles are

Notes : 1. Contrast Ratio (CR) is defined mathematically as :

CR =

It is measured at center 1-point.

2. Surface luminance is determined after the unit has been ‘ON’ and 1Hour after lighting the

backlight in a dark environment at 25±2°C. Surface luminance is the luminance value at center

1-point across the LCD surface 50cm from the surface with all pixels displaying white.

For more information see the FIG. 2.

3. The variation in surface luminance , δ WHITE is defined as :

Surface Luminance at all white pixels

Surface Luminance at all black pixels

δ WHITE(5P) = Maximum(L

on1,Lon2

, L

on3

, L

on4

, L

) / Minimum(L

on5

on1,Lon2

, L

on3

, L

on4

, L

on5

LC420EUG

)

Where L

on1

to L

are the luminance with all pixels displaying white at 5 locations .

on5

For more information, see the FIG. 2.

4. Response time is the time required for the display to transit from any gray to white (Rise Time, TrR)

and from any gray to black (Decay time, TrD). For additional information see the FIG. 3.

※ G to GBWSpec stands for average value of all measured points.

Photo Detector : RD-80S / Field : 2 °

5. G to G σ is Variation of Gray to Gray response time composing a picture

G to G (σ) =

√

Σ(Xi- u)

N

2

Xi = Individual Data

u = Data average

N : The number of Data

determined for the horizontal or x axis and the vertical or y axis with respect to the z axis which

is normal to the LCD module surface. For more information, see the FIG. 4.

7. Gray scale specification

Gamma Value is approximately 2.2. For more information, see the Table 11.

Table 11. GRAY SCALE SPECIFICATION

Gray Level Luminance [%] (Typ.)

L0

L15

L31

L47

L63

L79

L95

L111

L127

L143

L159

L175

L191

L207

L223

L239

L255

Ver. 1.0

0.08

0.27

1.04

2.49

4.68

7.66

11.5

16.1

21.6

28.1

35.4

43.7

53.0

63.2

74.5

86.7

100

19 /35

Product Specification

Measuring point for surface luminance & measuring point for luminance variation.

H

A

③③③③②②②②

LC420EUG

V

①①①①

B

A : H / 4 mm

④④④④

FIG. 2 5 Points for Luminance Measure

Response time is defined as the following figure and shall be measured by switching the input signal for

“Gray(N)” and “Gray(M)”.

TrR

100

90

⑤⑤⑤⑤

TrD

B : V / 4 mm

@ H,V : Active Area

Ver. 1.0

Optical

Response

10

0

Gray(N)

N,M = Black~White, N<M

FIG. 3 Response Time

Gray(M)

Gray(N)

20 /35

Dimension of viewing angle range

LC420EUG

Product Specification

φ

= 180°, Left

φ

= 270°, Down

Normal

θ

φ

FIG. 4 Viewing Angle

E

Y

φ

= 90°, Up

φ

= 0°, Right

Ver. 1.0

FIG. 4 Viewing Angle

21 /35

Product Specification

5. Mechanical Characteristics

Table 12 provides general mechanical characteristics.

Table 12. MECHANICAL CHARACTERISTICS

Item Value

Horizontal 969.2 mm

LC420EUG

Outline Dimension

Vertical 564.0 mm

Depth 21.3 mm

Horizontal 944.8 mm (*1)

Bezel Area

Vertical 531.0 mm

Horizontal 930.24 mm

Active Display Area

Vertical 523.26 mm

Weight

7.0 Kg (Typ.),7.4Kg(Max.)

Note : Please refer to a mechanical drawing in terms of tolerance at the next page.

Ver. 1.0

22 /35

[ FRONT VIEW ]

LC420EUG

Product Specification

Ver. 1.0

23 /35

[ REAR VIEW ]

LC420EUG

Product Specification

Ver. 1.0

24 /35

Product Specification

6. Reliability

Table 13. ENVIRONMENT TEST CONDITION

No. Test Item Condition

LC420EUG

1 High temperature storage test

2 Low temperature storage test

3 High temperature operation test

4 Low temperature operation test

5 Humidity condition Operation

Ta= 60°C 240h

Ta= -20°C 240h

Ta= 50°C 50%RH 240h

Ta= 0°C 240h

Ta= 40 °C ,90%RH

Note : Before and after Reliability test, LCM should be operated with normal function.

Ver. 1.0

25 /32

Product Specification

7. International Standards

7-1. Environment

a) RoHS, Directive 2002/95/EC of the European Parliament and of the council of 27 January 2003

LC420EUG

Ver. 1.0

26 /35

LC420EUG

chemical damage to the polarizer

Product Specification

8. Precautions

Please pay attention to the followings when you use this TFT LCD module.

8-1. Mounting Precautions

(1) You must mount a module using specified mounting holes (Details refer to the drawings).

(2) You should consider the mounting structure so that uneven force (ex. Twisted stress) is not applied to

t h e

module. And the case on which a module is mounted should have sufficient strength so that external

force is not transmitted directly to the module.

(3) Please attach the surface transparent protective plate to the surface in order to protect the polarizer.

Transparent protective plate should have sufficient strength in order to the resist external force.

(4) You should adopt radiation structure to satisfy the temperature specification.

(5) Acetic acid type and chlorine type materials for the cover case are not desirable because the former

generates corrosive gas of attacking the polarizer at high temperature and the latter causes circuit break

by electro-chemical reaction.

(6) Do not touch, push or rub the exposed polarizers with glass, tweezers or anything harder than HB

pencil lead. And please do not rub with dust clothes with chemical treatment.

Do not touch the surface of polarizer for bare hand or greasy cloth.(Some cosmetics are detrimental

to the polarizer.)

(7) When the surface becomes dusty, please wipe gently with absorbent cotton or other soft materials like

chamois soaks with petroleum benzine. Normal-hexane is recommended for cleaning the adhesives

used to attach front / rear polarizers. Do not use acetone, toluene and alcohol because they cause

(8) Wipe off saliva or water drops as soon as possible. Their long time contact with polarizer causes

deformations and color fading.

(9) Do not open the case because inside circuits do not have sufficient strength.

8-2. Operating Precautions

(1) The spike noise causes the mis-operation of circuits. It should be lower than following voltage :

V=±200mV(Over and under shoot voltage)

(2) Response time depends on the temperature.(In lower temperature, it becomes longer.)

(3) Brightness depends on the temperature. (In lower temperature, it becomes lower.)

And in lower temperature, response time(required time that brightness is stable after turned on)

becomes longer

(4) Be careful for condensation at sudden temperature change.Condensation makes damage to polarizer or

electrical contacted parts. And after fading condensation, smear or spot will occur.

(5) When fixed patterns are displayed for a long time, remnant image is likely to occur.

(6) Module has high frequency circuits. Sufficient suppression to the electromagnetic interference shall be

done by system manufacturers. Grounding and shielding methods may be important to minimized the

interference.

(7) Please do not give any mechanical and/or acoustical impact to LCM. Otherwise, LCM can’t be operated

its full characteristics perfectly.

(8) A screw which is fastened up the steels should be a machine screw.

(if not, it can causes conductive particles and deal LCM a fatal blow)

(9) Please do not set LCD on its edge.

(10) The conductive material and signal cables are kept away from LED driver inductor to prevent abnormal

display, sound noise and temperature rising.

Ver. 1.0

27 /35

LC420EUG

8-6. Handling Precautions for Protection Film

Product Specification

8-3. Electrostatic Discharge Control

Since a module is composed of electronic circuits, it is not strong to electrostatic discharge. Make certain that

treatment persons are connected to ground through wrist band etc. And don’t touch interface pin directly.

8-4. Precautions for Strong Light Exposure

Strong light exposure causes degradation of polarizer and color filter.

8-5. Storage

When storing modules as spares for a long time, the following precautions are necessary.

(1) Store them in a dark place. Do not expose the module to sunlight or fluorescent light. Keep the temperature

between 5°C and 35°C at normal humidity.

(2) The polarizer surface should not come in contact with any other object.

It is recommended that they be stored in the container in which they were shipped.

(3) Storage condition is guaranteed under packing conditions.

(4) The phase transition of Liquid Crystal in the condition of the low or high storage temperature will be

recovered when the LCD module returns to the normal condition

(1) The protection film is attached to the bezel with a small masking tape.

When the protection film is peeled off, static electricity is generated between the film and polarizer.

This should be peeled off slowly and carefully by people who are electrically grounded and with well ion-

blown equipment or in such a condition, etc.

(2) When the module with protection film attached is stored for a long time, sometimes there remains a very

small amount of glue still on the bezel after the protection film is peeled off.

(3) You can remove the glue easily. When the glue remains on the bezel surface or its vestige is recognized,

please wipe them off with absorbent cotton waste or other soft material like chamois soaked with normal-

hexane.

Ver. 1.0

28 /35

# APPENDIX- II-1

■ LCM Label

LC420EUG

Product Specification

Model

UL, TUV Mark

LGD Logo

US PATENT No.

LC420EUG

(RD)(V2)

420

Serial No.

Origin

Ver. 1.0

29 /35

LC420EUG

GREEN4

45

TCLK

-

ROCLKN

19

23

Product Specification

# APPENDIX- II-1

■ Required signal assignment for Flat Link (Thine : THC63LVD103) Transmitter(Pin7= “L” or “NC”)

Host System

30 Bit

RED0

RED1

RED2

RED3

RED4

RED5

RED6

RED7

RED8

RED9

GREEN0

GREEN1

GREEN2

GREEN3

GREEN5

GREEN6

GREEN7

GREEN8

GREEN9

BLUE0

BLUE1

BLUE2

BLUE3

BLUE4

BLUE5

BLUE6

BLUE7

BLUE8

BLUE9

Hsync

Vsync

Data Enable

CLOCK

THC63LVD103

or Compatible

33

34

35

36

37

38

59

61

4

5

40

41

42

44

46

62

63

6

8

48

49

50

52

53

54

64

1

9

11

55

57

58

12

TA-

TA+

TB-

TB+

TC-

TC+

TCLK+

TD-

TD+

TE-

TE+

31

30

29

28

25

24

22

21

20

19

18

GND

FI-RE51S-HF

12

13

14

15

16

17

20

22

23

24

25

7

100Ω

100Ω

100Ω

100Ω

100Ω

100Ω

LCM Module

Timing

Controller

RO0N

RO0P

RO1N

RO1P

RO2N

RO2P

ROCLKP

RO3N

RO3P

RO4N

RO4P

VESA/ JEIDA

Note: 1. The LCD module uses a 100 Ohm[Ω] resistor between positive and negative lines of each receiver

input.

2. Refer to LVDS Transmitter Data Sheet for detail descriptions. (THC63LVD103 or Compatible)

3. ‘9’ means MSB and ‘0’ means LSB at R,G,B pixel data.

Ver. 1.0

30 /35

Product Specification

GREEN4

40

TCLK

-

ROCLKN

19

23

# APPENDIX- II-2

■ Required signal assignment for Flat Link (Thine : THC63LVD103) Transmitter(Pin7= “H” )

LC420EUG

Host System

30 Bit

RED0

RED1

RED2

RED3

RED4

RED5

RED6

RED7

RED8

RED9

GREEN0

GREEN1

GREEN2

GREEN3

GREEN5

GREEN6

GREEN7

GREEN8

GREEN9

BLUE0

BLUE1

BLUE2

BLUE3

BLUE4

BLUE5

BLUE6

BLUE7

BLUE8

BLUE9

Hsync

Vsync

Data Enable

CLOCK

THC63LVD103

or Compatible

4

5

59

61

33

34

35

36

37

38

6

8

62

63

41

42

44

45

46

9

11

64

1

48

49

50

52

53

54

55

57

58

12

TA-

TA+

TB-

TB+

TC-

TC+

TCLK+

TD-

TD+

TE-

TE+

31

30

29

28

25

24

22

21

20

19

18

VCC

FI-RE51S-HF

12

13

14

15

16

17

20

22

23

24

25

7

100Ω

100Ω

100Ω

100Ω

100Ω

100Ω

LCM Module

Timing

Controller

RO0N

RO0P

RO1N

RO1P

RO2N

RO2P

ROCLKP

RO3N

RO3P

RO4N

RO4P

VESA /JEIDA

Note :1. The LCD module uses a 100 Ohm[Ω] resistor between positive and negative lines of each receiver

input.

2. Refer to LVDS Transmitter Data Sheet for detail descriptions. (THC63LVD103 or Compatible)

3. ‘9’ means MSB and ‘0’ means LSB at R,G,B pixel data.

Ver. 1.0

31 /35

B11

B10

G11

G10XR11

R10’

R10

R11’

X”

RDP

# APPENDIX- IV

B11

B10

G11

G10XR11

R10’

R10

R11’X”RDP

■ LVDS Select : “H” Data-Mapping (JEIDA format)

RCLKP

RCLKM

LC420EUG

Product Specification

LVDS Data-Mapping info. (8bit)

RAP

RBP

RCP

R17 R16 R15 R14G12 R13R12’ R12R13’ G12”

B12 G17 G16 G15B13 G14G13’ G13G14’ B13”

V

SYNCHSYNC

B17 B16DE B15B14’ B14B15’ DE”

■ LVDS Select : “L” Data-Mapping (VESA format)

RCLKP

RCLKM

RAP

RBP

R15 R14 R13 R12G10 R11R10’ R10R11’ G10”

B10 G15 G14 G13B11 G12G11’ G11G12’ B15”

Ver. 1.0

RCP

RDP

V

SYNCHSYNC

B17 B16 G17 G16X R17R16’ R16R17’ X”

B15 B14DE B13B12’ B12B13’ DE”

32 /35

Product Specification

System Side

LCM Side

# APPENDIX- V

Option Pin Circuit Block Diagram

Circuit Block Diagram of LVDS Format Selection pin

VCC

Open

LC420EUG

LVDS Select

(Pin 9)

Selector

1KΩ

50KΩ

ASIC

(TCON)

Ver. 1.0

33 /35

# APPENDIX- IV

■ Source D-IC Power Sequence

LC420EUG

Product Specification

- Input Signal : SOE,POL,GSP,H_CONV,OPT_N, mini-LVDS

Ver. 1.0

34 /35

Product Specification

# APPENDIX- VI

■■■■ Scanning and OPC Design Guide

◊ When OPC Enable is “L", OPC Output = System Dimming.

OPC Output( PWM Signal) is synchronized with V-Sync Freq. of System in T-Con Board.

(8pin)

#1 : PWM_TOUT #1

#2 : PWM_TOUT #2

#3 : PWM_TOUT #3

#4 : PWM_TOUT #4 (Or NC)

#5 : PWM_TOUT #5 (Or NC)

#6 : PWM_TOUT #6 (Or NC)

#7 : NC

#8 : GND

(51pin)

#8 : Ext_PWM

#10 : OPC_EN

#1

#8

#1 51

LC420EUG

LCM T-con Board

T-Con

CNT1 51pin

#8

B/L Signal

Generation

Block

#1

LED

Driver

14pin

◊ PWM Specification ( VDD = 3.3V ) @ OPC

1. PWM High Voltage Range : 2.5V~3.6V

2. PWM Low Voltage Range : 0.0V~0.8V

EXTVBR-B

Frequency

50 Hz for PAL

60 Hz for NTSC

CNT4

System

Main IC

(PWM Generator)

<With Driver Model>

VDD

VDD*0.9

OPC On

3.3V

OPC Off

Chassis

Rising Time

Rising Time MAX 10.0 µs

Falling Time MAX 10.0 µs

Ver. 1.0

Falling Time

VDD*0.1

0

35 /35

Loading...

Loading...