Page 1

Date: May, 2008 / Issue 1.0

Service Manual

Model : KF755d

Service Manual

KF755d

Internal Use Only

Page 2

- 3 -

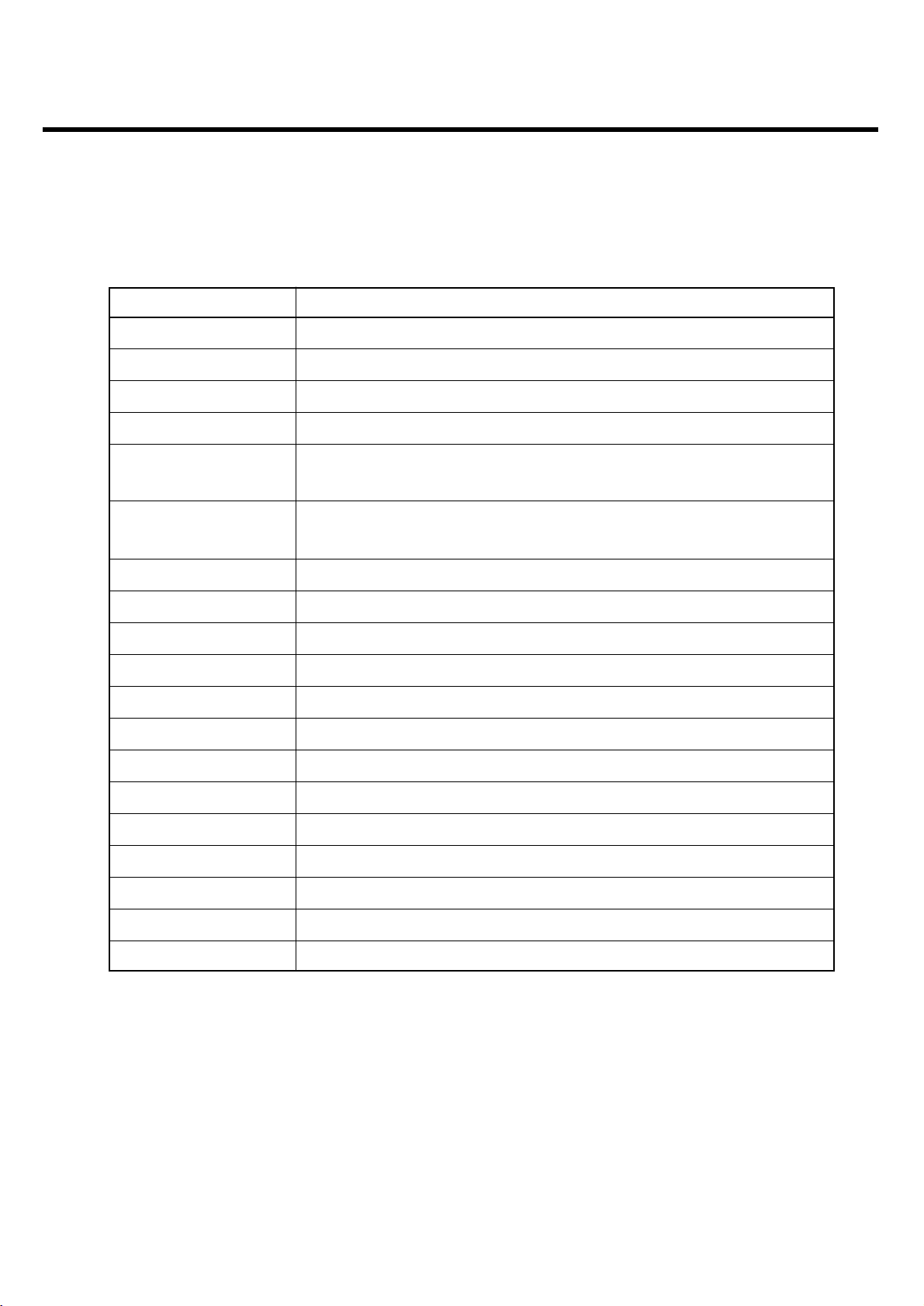

1. INTRODUCTION .............................. 5

1.1 Purpose................................................... 5

1.2 Regulatory Information............................ 5

2. PERFORMANCE...............................7

2.1 System Overview .....................................7

2.2 Usable environment .................................8

2.3 Radio Performance ..................................9

2.4 Current Consumption.............................18

2.5 RSSI.......................................................18

2.6 Battery Bar .............................................18

2.7 Sound Pressure Level............................19

2.8 Charging ................................................20

3. TECHNICAL BRIEF ........................21

3.1 Digital Baseband(DBB) & Multimedia

Processor...............................................21

3.2 GAM Hardware Subsystem ...................45

3.3 Audio Part ..............................................57

3.4 GPADC(General Purpose ADC) and

AUTOADC2 ...........................................65

3.5 Charger control ......................................66

3.6 Voltage Regulation.................................72

3.7 RF Technical Description.......................73

4. TROUBLE SHOOTING ...................84

4.1 Power ON Trouble .................................84

4.2 USB Trouble ..........................................85

4.3 SIM Detect Trouble ................................86

4.4 MicroSD card Trouble ............................87

4.5 Keypad, Touch Button and

Touch Screen Trouble ...........................88

4.6 Multi EL lighting Trouble ........................93

4.7 Camera Trouble .....................................97

4.8 Main LCD Trouble................................103

4.9 Keypad Backlight Trouble ....................105

4.10 Folder ON/OFF Trouble .....................107

4.11 Audio Trouble Shooting .....................109

4.12 Charger Trouble Shooting..................128

4.13 Checking Bluetooth Block ..................131

4.14 RF Component...................................138

4.15 Procedure to check ............................139

4.16 Checking Common Power

Source Block......................................140

4.17 Checking VCXO Block .......................145

4.18 Checking Front End Module Block.....150

4.19 Checking Front End Module

Block input logic .................................151

4.20 Checking WCDMA Block ...................154

4.21 Checking GSM Block .........................169

5. DOWNLOAD .................................184

5.1 LGDP2 .................................................184

5.2 Download .............................................186

6. BLOCK DIAGRAM ........................188

7. Circuit Diagram ............................191

8. BGM Pin Map................................203

9. PCB LAYOUT................................209

10. Calibration & RF Auto Test

Program (Hot Kimchi)................219

10.1 General Description ...........................219

10.2 XCALMON Environment ....................219

10.3 Calibration Environment.....................220

10.4 Program Operation ............................221

11. Stand-alone Test ........................226

11.1 General Description ...........................226

11.2 Program Operation ............................227

11.3 Stand-alone Test................................230

12. EXPLODED VIEW &

REPLACEMENT PART LIST ......233

12.1 EXPLODED VIEW .............................233

12.2 Replacement Parts ............................235

12.3 Accessory ..........................................256

Table Of Contents

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Page 3

- 4 -

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Page 4

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

- 5 -

1.1 Purpose

This manual provides the information necessary to repair, calibration, description and download the

features of this model.

1.2 Regulatory Information

A. Security

Toll fraud, the unauthorized use of telecommunications system by an unauthorized part (for example,

persons other than your company’s employees, agents, subcontractors, or person working on your

company’s behalf) can result in substantial additional charges for your telecommunications services.

System users are responsible for the security of own system.

There are may be risks of toll fraud associated with your telecommunications system. System users

are responsible for programming and configuring the equipment to prevent unauthorized use. The

manufacturer does not warrant that this product is immune from the above case but will prevent

unauthorized use of commoncarrier telecommunication service of facilities accessed through or

connected to it. The manufacturer will not be responsible for any charges that result from such

unauthorized use.

B. Incidence of Harm

If a telephone company determines that the equipment provided to customer is faulty and possibly

causing harm or interruption in service to the telephone network, it should disconnect telephone

service until repair can be done. A telephone company may temporarily disconnect service as long as

repair is not done.

C. Changes in Service

A local telephone company may make changes in its communications facilities or procedure. If these

changes could reasonably be expected to affect the use of the phones or compatibility with the net

work, the telephone company is required to give advanced written notice to the user, allowing the user

to take appropriate steps to maintain telephone service.

D. Maintenance Limitations

Maintenance limitations on the phones must be performed only by the manufacturer or its authorized

agent. The user may not make any changes and/or repairs expect as specifically noted in this manual.

Therefore, note that unauthorized alternations or repair may affect the regulatory status of the system

and may void any remaining warranty.

1. INTRODUCTION

1. INTRODUCTION

Page 5

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

E. Notice of Radiated Emissions

This model complies with rules regarding radiation and radio frequency emission as defined by local

regulatory agencies. In accordance with these agencies, you may be required to provide information

such as the following to the end user.

F. Pictures

The pictures in this manual are for illustrative purposes only; your actual hardware may look slightly

different.

G. Interference and Attenuation

A phone may interfere with sensitive laboratory equipment, medical equipment, etc. Interference from

unsuppressed engines or electric motors may cause problems.

H. Electrostatic Sensitive Devices

ATTENTION

Boards, which contain Electrostatic Sensitive Device (ESD), are indicated by the sign.

Following information is ESD handling:

• Service personnel should ground themselves by using a wrist strap when exchange system boards.

• When repairs are made to a system board, they should spread the floor with anti-static mat which is

also grounded.

• Use a suitable, grounded soldering iron.

• Keep sensitive parts in these protective packages until these are used.

• When returning system boards or parts like EEPROM to the factory, use the protective package as

described.

1. INTRODUCTION

- 6 -

Page 6

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

- 7 -

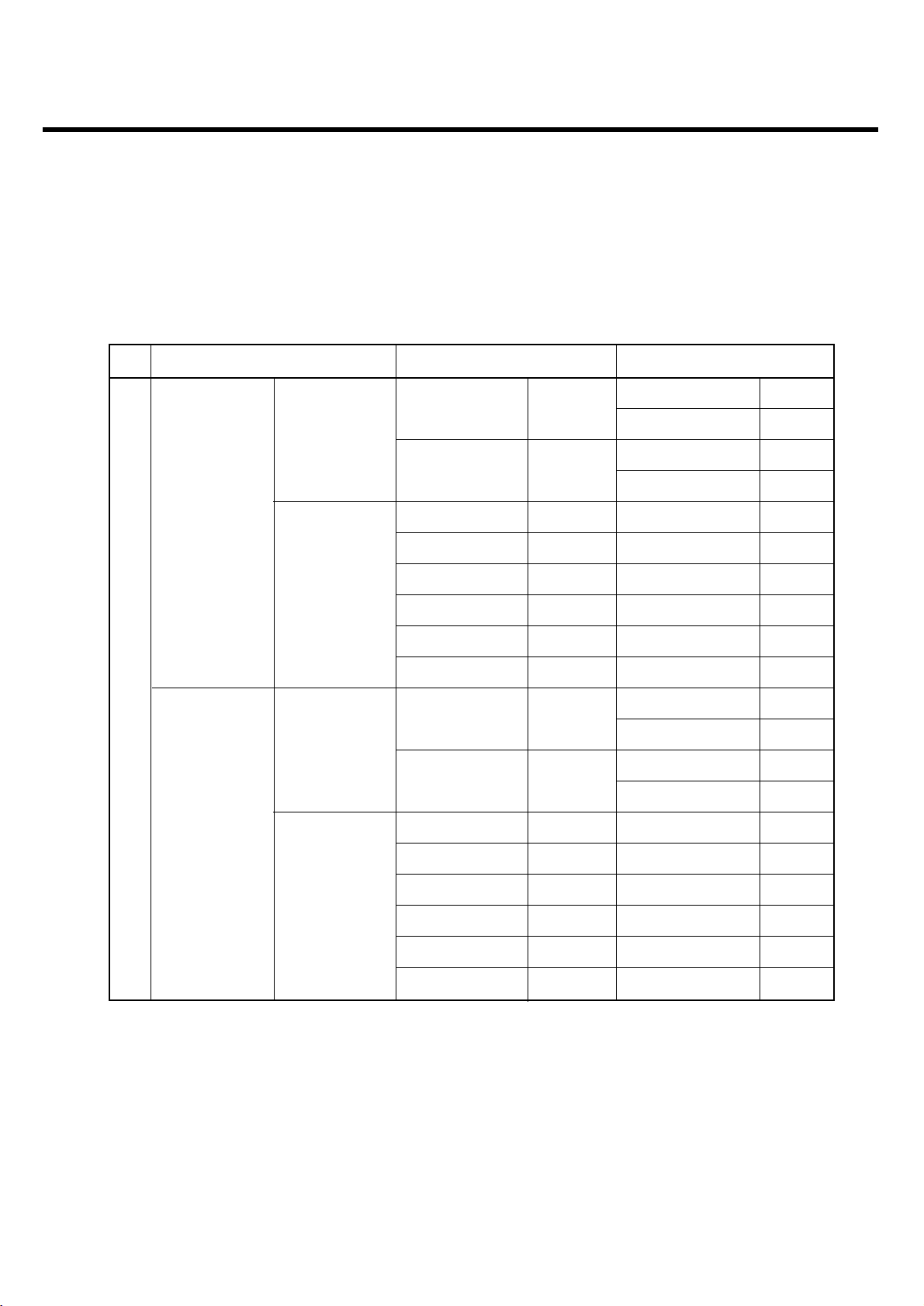

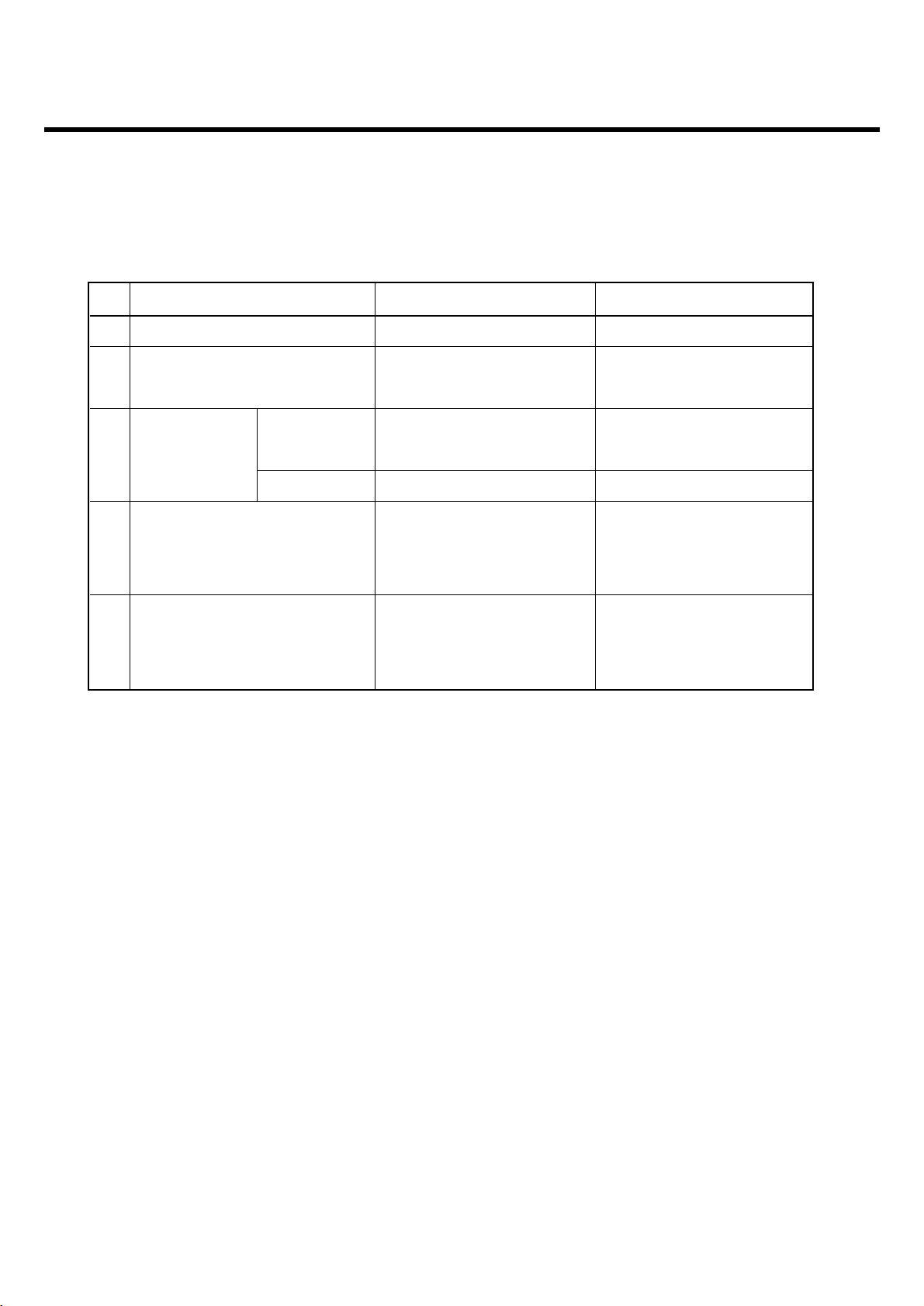

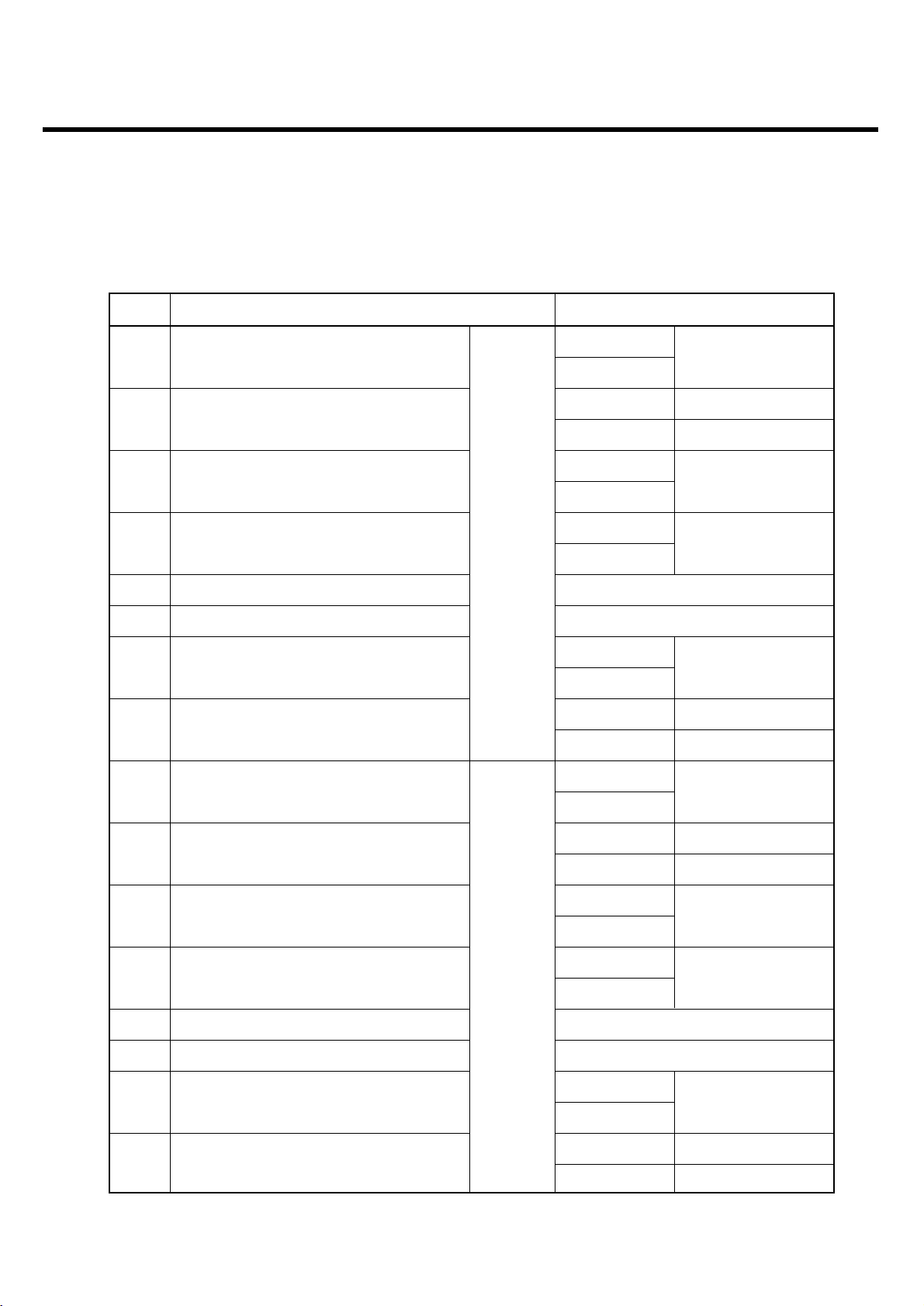

2.1 System Overview

2. PERFORMANCE

Item Specification

Shape GSM900/1800/1900 & WCDMA Slide type - Dual Mode Handset

Size 50.8X102.8X11.8 mm

Weight 116g (with standard battery)

Power 800mAh Li-Ion

Talk Time Over 170 Min (WCDMA, Tx=12 dBm, Voice)

Over 190 Min (GSM, Tx=Max, Voice)

Standby Time Over 220 hrs (WCDMA, DRX=2.56)

Over 220 hrs (GSM, Paging period=5)

Antenna Intenna type

Main LCD 2.4"(320x240), 260K TFT Color LCDs

Main LCD BL White LED Backlight

Vibrator Yes (Coin Type)

Speaker Yes

MIC Yes (SMD Type)

Receiver Yes

Earphone Jack Yes

SIM Socket Yes(SIM Block Type) : 3.0V & 1.8V

Volume Key Push Type ( + , - )

Voice Key Push Type

External Memory T - Flash Socket

I/O Connect 18 Pin

Page 7

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

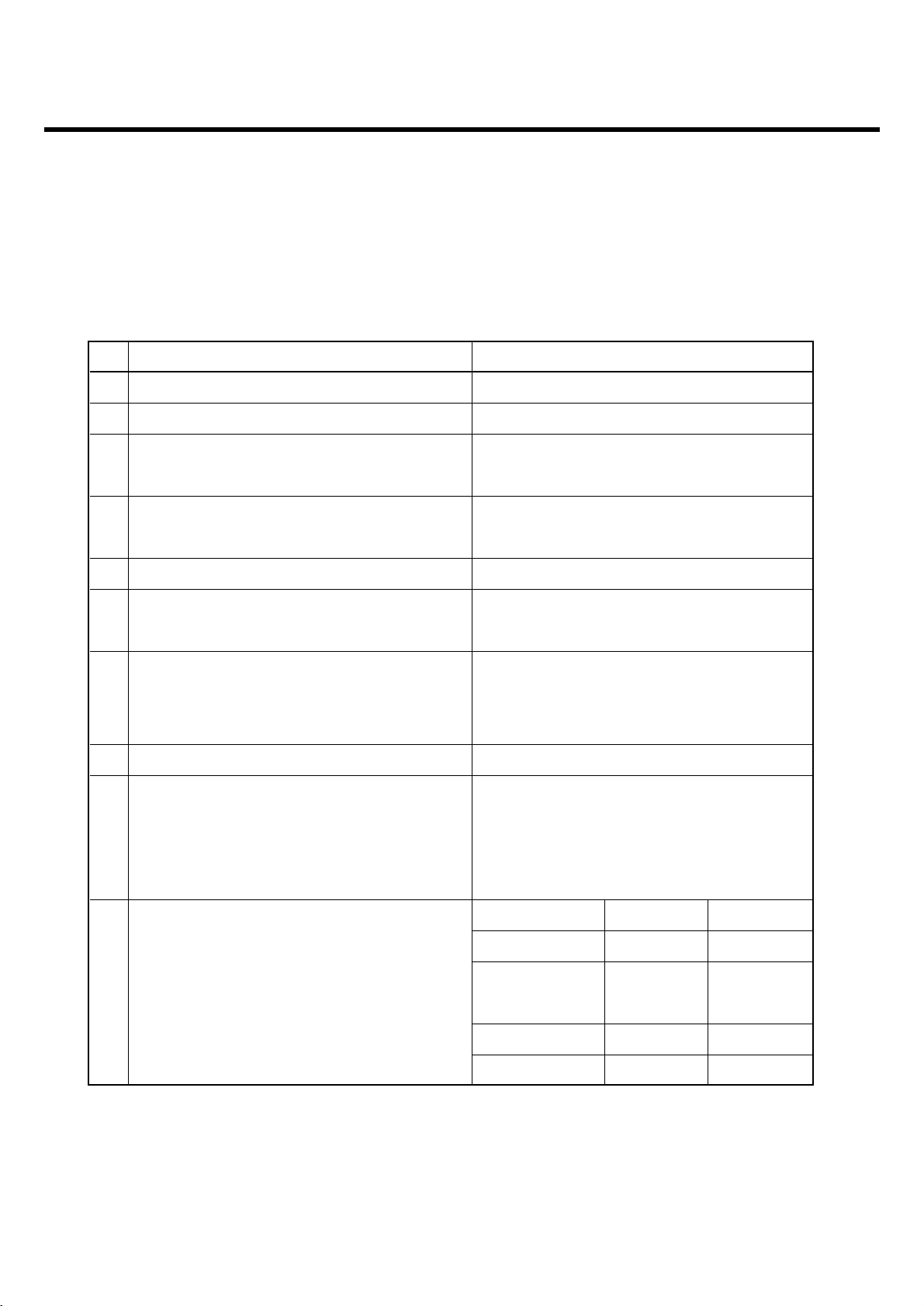

2.2 Usable environment

1) Environment

2) Environment (Accessory)

* CLA : 12~24V(DC).

2. PERFORMANCE

- 8 -

Item Specification Unit

Voltage 3.7 (Typ), 3.4 (Min), (Shut Down: 3.23) V

Operation Temp -20 ~ + 60 °C

Storage Temp -30 ~ + 85 °C

Humidity max. 85 %

Item Spec. Min Typ. Max Unit

Power Available power 100 220 240 Vac

Page 8

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

- 9 -

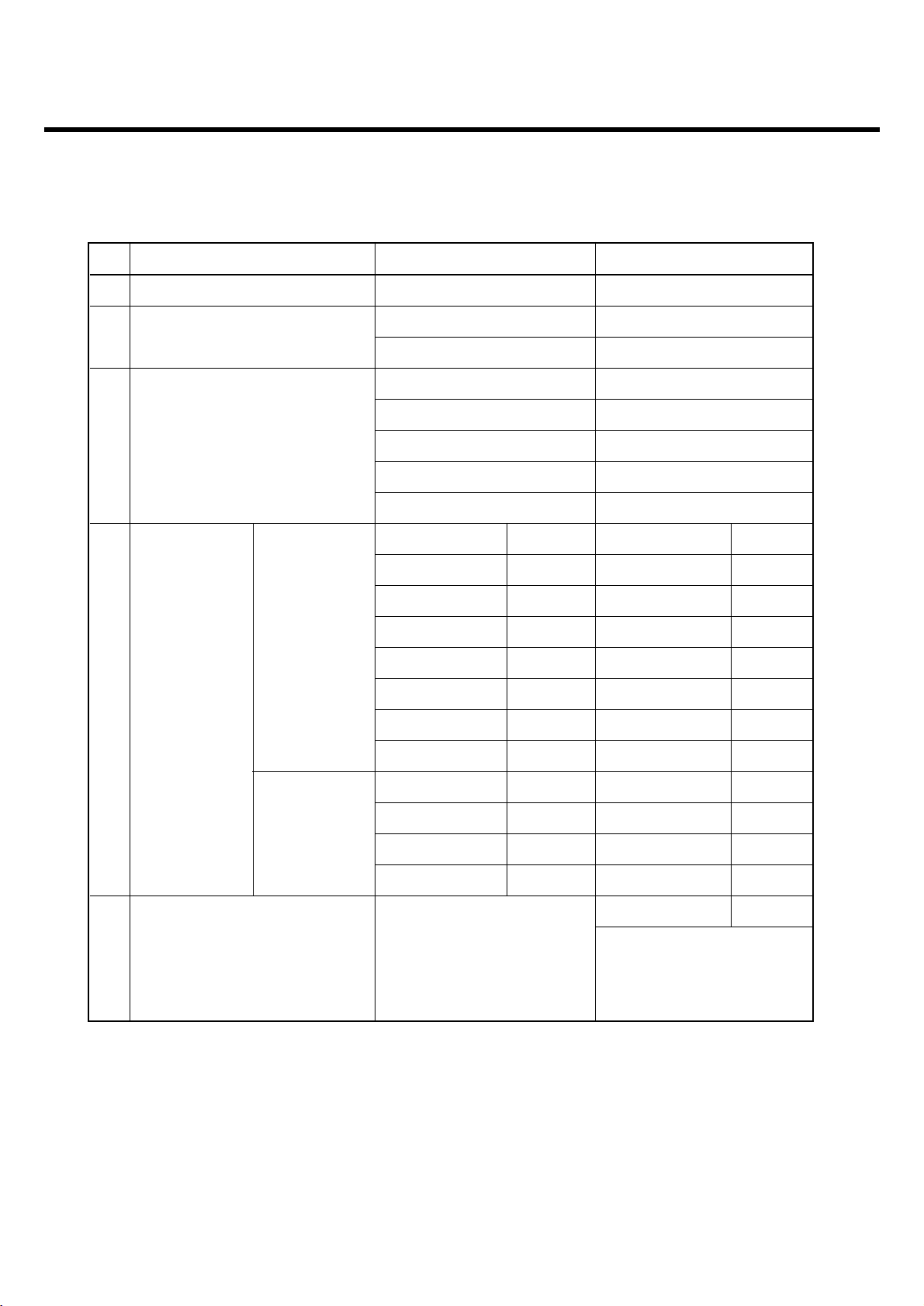

2.3 Radio Performance

1) Transmitter-GSM Mode

No Item GSM DCS/PCS

1 Conducted MS allocated 100k~1GHz -39dBm 9k~1GHz -39dBm

Spurious Channel 1G~1710MHz -33dBm

Emission 1G~12.75GHz -33dBm 1710M~1785MHz -39dBm

1785M~12.75GHz -33dBm

Idle Mode 100k~880MHz -60dBm 100k~880MHz -60dBm

880M~915MHz -62dBm 880M~915MHz -62dBm

915M~1000Mz -60dBm 915M~1000MHz -60dBm

1G~1.71GHz -50dBm 1G~1.71GHz -50dBm

1.71G~1.785GHz -56dBm 1.71G~1.785GHz -56dBm

1.785G~12.75GHz -50dBm 1.785G~12.75GHz -50dBm

Radiated MS allocated 30M~1GHz -36dBm 30M~1GHz -36dBm

Spurious Channel 1G~1710MHz -30dBm

Emission 1G~4GHz -30dBm 1710M~1785MHz -36dBm

1785M~4GHz -30dBm

Idle Mode 30M ~ 880MHz -57dBm 30M~880MHz -57dBm

880M ~ 915MHz -59dBm 880M~915MHz -59dBm

915M~1GHz -57dBm 915M~1GHz -57dBm

1G~1.71GHz -47dBm 1G 1.71GHz -47dBm

1.71G~1.785GHz -53dBm 1.71G~1.785GHz -53dBm

1.785G~4GHz -47dBm 1.785G~4GHz -47dBm

Page 9

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

- 10 -

No Item GSM DCS/PCS

2 Frequency Error ± 0.1ppm ± 0.1ppm

3 Phase Error ± 5(RMS) ± 5(RMS)

± 20(PEAK) ± 20(PEAK)

4 Frequency Error 3dB below reference sensitivity 3dB below reference sensitivity

Under Multipath and RA250 : ± 200Hz RA250: ± 250Hz

Interference Condition HT100 : ± 100Hz HT100: ± 250Hz

TU50 : ± 100Hz TU50: ± 150Hz

TU3 : ± 150Hz TU1.5: ± 200Hz

5 Output RF Due to 0 ~ 100kHz +0.5dB 0 ~ 100kHz +0.5dB

Spectrum modulation 200kHz -30dB 200kHz -30dB

250kHz -33dB 250kHz -33dB

400kHz -60dB 400kHz -60dB

600 ~ 1800kHz -66dB 600 ~ 1800kHz -60dB

1800 ~ 3000kHz -69dB 1800 ~ 6000kHz -65dB

3000 ~ 6000kHz -71dB ≥ 6000kHz -73dB

≥ 6000kHz -77dB

Due to 400kHz -19dB 400kHz -22dB

Switching 600kHz -21dB 600kHz -24dB

transient 1200kHz -21dB 1200kHz -24dB

1800kHz -24dB 1800kHz -27dB

7 Intermodulation attenuation - Frequency offset 800kHz

Intermodulation product should

be Less than 55dB below the

level of Wanted signal

Page 10

No Item GSM DCS/PCS

8 Transmitter Output Power Level Power Toler. Level Power Toler.

533 ±3030 ±3

631 ±3128 ±3

729 ±3226 ±3

827 ±3324 ±3

925 ±3422 ±3

10 23 ±3 5 20 ±3

11 21 ±3 6 18 ±3

12 19 ±3 7 16 ±3

13 17 ±3 8 14 ±3

14 15 ±3 9 12 ±4

15 13 ±3 10 10 ±4

16 11 ±5 11 8 ±4

17 9 ±5 12 6 ±4

18 7 ±5 13 4 ±4

19 5 ±5 14 2 ±5

15 0 ±5

9 Burst timing Mask IN Mask IN

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

- 11 -

Page 11

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

- 12 -

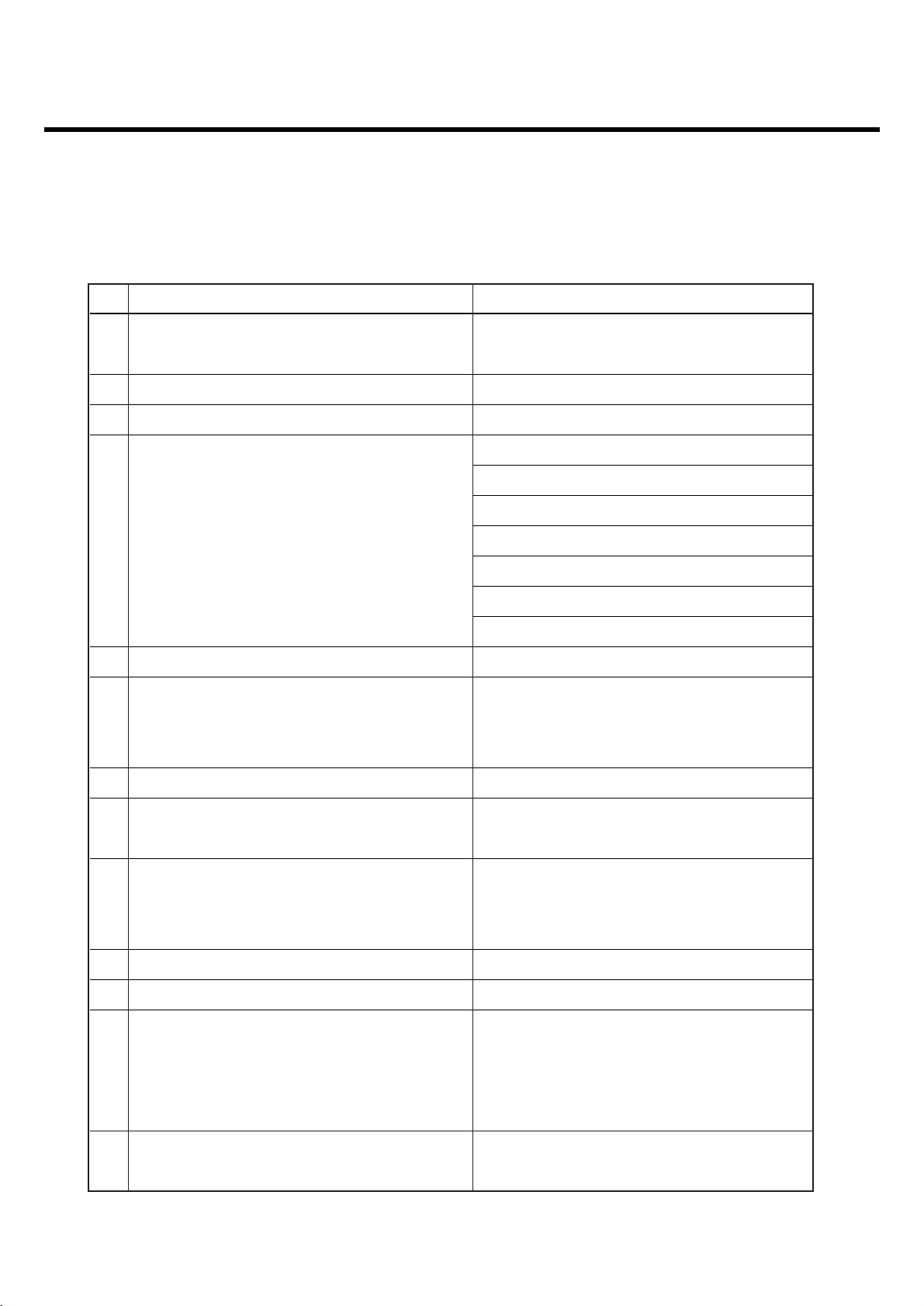

2) Transmitter-WCDMA Mode

No Item Specification

1 Maximum Output Power Class 3 : +24dBm(+1/-3dB)

Class4: +21dBm(±2dB)

2 Frequency Error ± 0.1ppm

3 Open Loop Power control in uplink ± 9dB@normal, ± 12dB@extreme

4 Inner Loop Power control in uplink Adjust output(TPC command)

cmd 1dB 2dB 3dB

+1 +0.5/1.5 +1/3 +1.5/4.5

0 -0.5/+0.5 -0.5/+0.5 -0.5/+0.5

-1 -0.5/-1.5 -1/-3 -1.5/-4.5

Group (10 equel command group)

+1 +8/+12 +

5 Minimum Output Power -50dBm(3.84MHz)

6 Out-of-synchronization handling of output power Qin/Qout : PCCH quality levels

Toff@DPCCH/Ior : -22 -> -28dB

Ton@DPCCH/Ior : -24 -> -18dB

7 Transmit OFF Power -56dBm(3.84MHz)

8 Transmit ON/OFF Time Mask ± 25us

PRACH,CPCH,uplinlk compressed mode

9 Change of TFC ± 25us

Power varies according to the data rate DTX :

DPCH off (minimize interference between UE)

10 Power setting in uplink compressed ± 3dB(after 14slots transmission gap)

11 Occupied Bandwidth(OBW) 5MHz(99%)

12 Spectrum emission Mask -35-15*(∆f-2.5)dBc@∆f=2.5~3.5MHz,30k

-35-1*(∆f-3.5)dBc@∆f=3.5~7.5MHz,1M -39-

10*(∆f-7.5)dBc@∆f=7.5~8.5MHz,1M

-49dBc@∆f=8.5~12.5MHz,1M

13 Adjacent Channel Leakage Ratio(ACLR) 33dB@5MHz, ACP>-50dBm

43dB@10MHz, ACP>-50dBm

Page 12

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

- 13 -

No Item Specification

14 Spurious Emissions (*: additional requirement) -36dBm@f=9~150KHz, 1K BW -

-36dBm@f=150KHz~30MHz, 10k

-36dBm@f=30~1000MHz, 100k

-30dBm@f=1~12.75GHz, 1M

-41dBm*@1893.5~1919.6MHz, 300k

-67dBm*@925~935MHz, 100k

-79dBm*@935~960MHz, 100k

-71dBm*@1805~1880MHz, 100k

15 Transmit Intermodulation -31dBc@5MHz, Interferer -40dBc

-41dBc@10MHz, Interferer -40dBc

16 Error Vector Magnitude (EVM) 17.5%(>-20dBm)

(@12.2K, 1DPDCH+1DPCCH)

17 Transmit OFF Power -15dB@SF=4, 768kbps,

multi-code transmission

Page 13

- 14 -

2. PERFORMANCE

3)Receiver-GSM Mode

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

No Item GSM850/900 DCS & PCS

1 Sensitivity (TCH/FS Class II) -105dBm -105dBm

2 Co-Channel Rejection (TCH/FS C/Ic=7dB C/Ic=7dB

Class II, RBER, TU high/FH)

3 Adjacent 200kHz C/Ia1=-12dB C/Ia1=-12dB

Channel

Rejection 400kHz C/Ia2=-44dB C/Ia2=-44dB

4 Intermodulation Rejection Wanted Signal: -98dBm Wanted Signal :-96dBm 1st

1’st interferer: -44dBm 1’st interferer: -44dBm

2’st interferer: -45dBm 2’st interferer: -44dBm

5 Blocking Response Wanted Signal: -101dBm Wanted Signal: -101dBm

(TCH/FS Class II, RBER) Unwanted Signal: Unwanted Signal:

Depend on freq. Depend on freq.

Page 14

- 15 -

2. PERFORMANCE

4) Receiver-WCDMA Mode

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

No Item Specification

1 Reference Sensitivity Level -106.7dBm(3.84M)

2 Maximum Input Level -25dBm(3.84MHz)

-44dBm/3.84MHz(DPCH_Ec)

UE@+20dBm output power(class3)

3 Adjacent Channel Selectivity (ACS) 33dB

UE@+20dBm output power(class3)

4In-band Blocking -56dBm/3.84MHz@10MHz

UE@+20dBm output power(class3)

-44dBm/3.84MHz@15MHz

UE@+20dBm output power(class3)

5 Out-band Blocking -44dBm/3.84MHz@f=2050~2095 &

2185~2230MHz, band a)

UE@+20dBm output power(class3)

-30dBm/3.84MHz@f=2025~2050 &

2230~2255MHz, band a)

UE@+20dBm output power(class3)

-15dBm/3.84MHz@f=1~2025 &

2255~12500MHz, band a)

UE@+20dBm output power(class3)

6 Spurious Response -44dBm CW

UE@+20dBm output power(class3)

7 Intermodulation Characteristic -46dBm CW@10MHz &

-46dBm/3.84MHz@20MHz

UE@+20dBm output power(class3)

-57dBm@f=9KHz~1GHz, 100k BW

8 Spurious Emissions -47dBm@f=1~12.75GHz, 1M

-60dBm@f=1920~1980MHz, 3.84MHz

-60dBm@f=2110~2170MHz, 3.84MHz

Page 15

- 16 -

2. PERFORMANCE

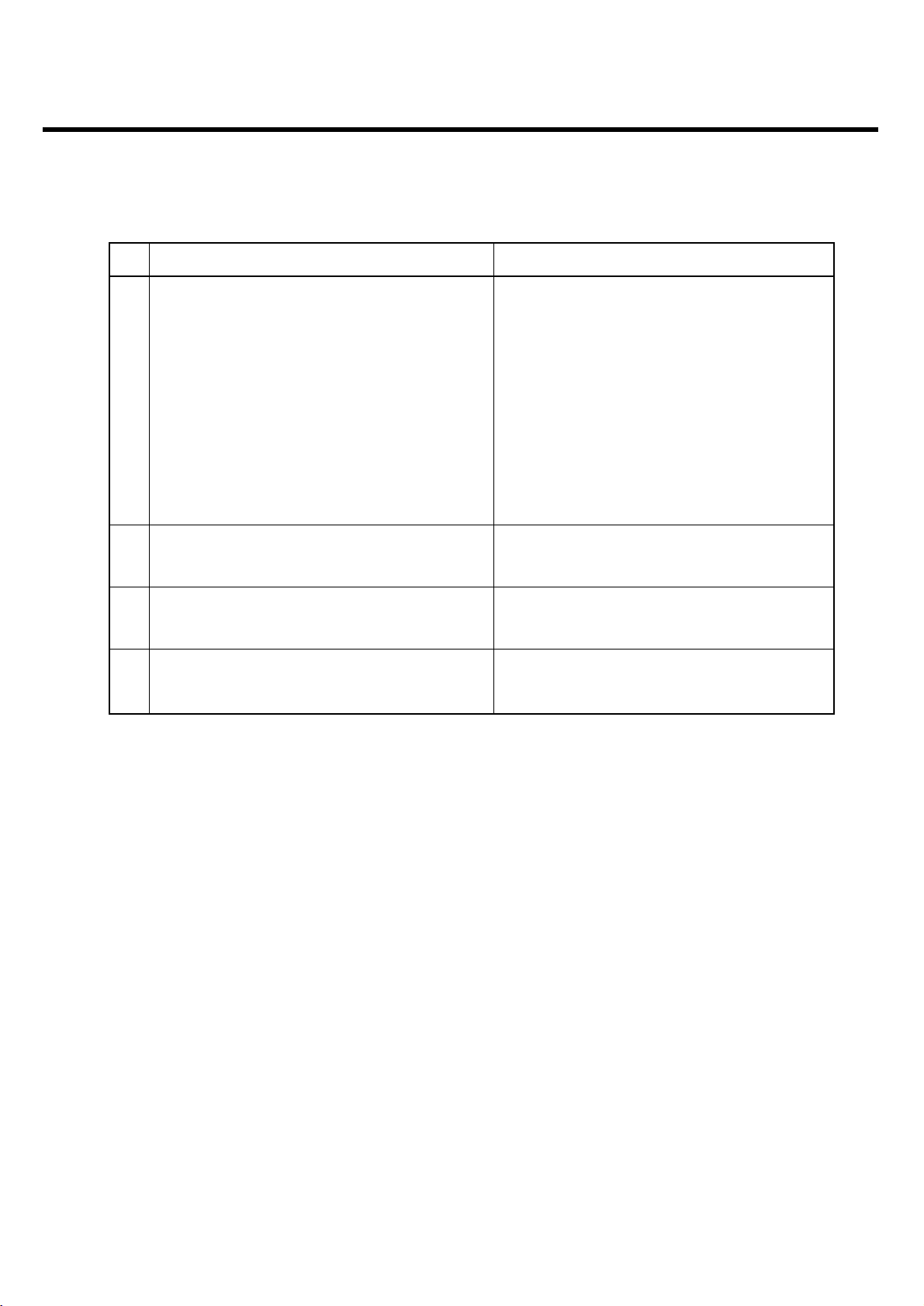

5) Transmitter

5.1 Transmitter

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

No Item Specification

1 Out Power Class 2 : -6~4dBm

2 Power Density Power density < 20dBm per 100kHz EIRP

3 Power Control Option

2dB ≤ step size ≤ 8dB

4 TX Output Spectrum -Frequency range fmax & fmin @ below the level of -30dBm

(100khz BW) within 2.4GHz~2.4835GHz

5 TX Output Spectrum -20dB Bandwidth ≤ 1MHz

6 Tx Output Spectrum -Adjacent channel Po ≤ -20dBm @ C/I = 2MHz

≤ -40dBm @ C/I ≥ 3MHz

7 Modulation Characteristics 140kHz ≤ delta f1 avg ≤ 175kHz

delta f2max ≥ 115kHz at least 99.9% of all

deltaf2max delta f2avg/deata f1avg ≥ 0.8

8 Init. Carrier Freq. Tolerance ≤ ±75KHz

9 Carrier Frequency Drift 1 slot : ≤ ±25kHz

3 slot : ≤ ±40kHz

5 slot : ≤ ±40kHz

Maximum drift rate ≤ 20KHz/50usec

10 Out of Band Spurious Emissions Freq.Range Operating Standby

30MHz~1GHz -36dBm -57dBm

Above 1GHz~ -30dBm -47dBm

12.75GHz

1.8~1.9GHz -47dBm -47dBm

5.15~5.3GHz -47dBm -47dBm

Page 16

- 17 -

2. PERFORMANCE

5.2 Transmitter

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

No Item Specification

1 Sensitivity single slot packets BER ≤ 0.1%@-70dBm

2 Sensitivity multi slot packets BER ≤ 0.1%@-70dBm

3 C/I performance BER ≤ 0.1%@ (Low,Mid,High Frequency)

2405MHz, 2441MHz, 2477MHz

Interference Ratio

Co-Channel interference, C/I co-channel 11dB

Adjacent(1MHz)interference, C/I 1MHz 0dB

Adjacent(2MHz)interference, C/I 2MHz -30dB

Adjacent( ≥ 3MHz)interference, C/I ≥ 3MHz -40dB

Adjacent( ≥ 3MHz)interference to in band -9dB

mirror frequency, C/I image ±1MHz -20dB

4Blocking Characteristic BER ≤ 0.1%@wanted signal -67dBm

interfering Signal Frequency Power Level

30MHz~2000MHz -10dBm

2000MHz~2400MHz -27dBm

2500MHz~3000MHz -27dBm

3000MHz~12.75GHz -10dBm

5 Intermodluation Performance BER ≤ 0.1%@wanted signal -64dBm

static sinwave signal at f1=-39dBm

a BT modulated signal f2=-39dBm(payload PRBS15)

6 Maximum Input Level BER ≤ 0.1%@-20dBm

Page 17

- 18 -

2. PERFORMANCE

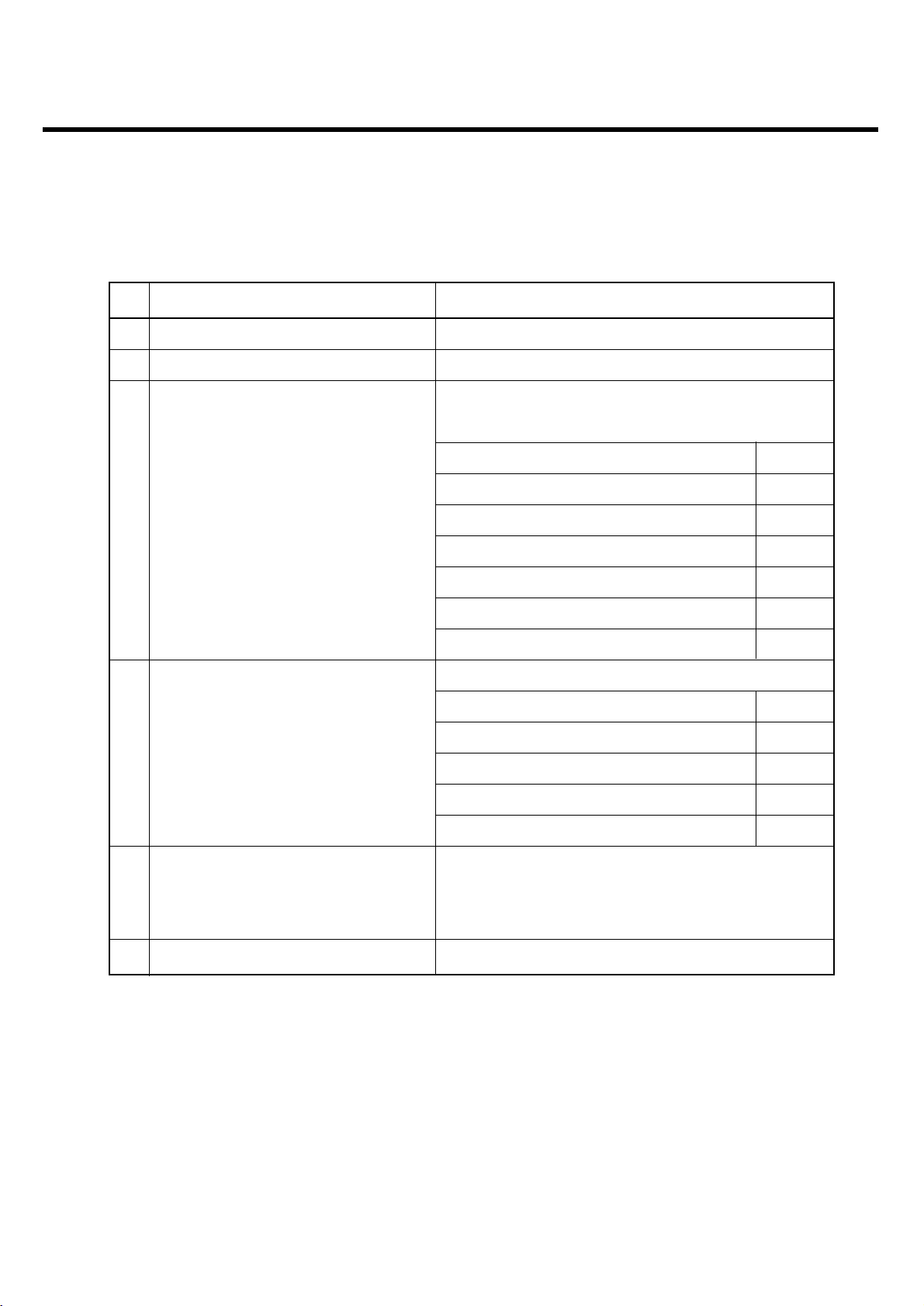

2.4 Current Consumption

(VT test : Speaker off, LCD backlight On)

2.5 RSSI

2.6 Battery Bar

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Stand by Voice Call VT

WCDMA Only 220 Hours = 3.6 mA 170 Min = 280 mA 125 Min= 380 mA

(DRX=2.56) (Tx=12dBm) (Tx=12dBm)

GSM 220 Hours = 3.6 mA 190 Min = 250 mA

(paging=5period) (Tx=Max)

No WCDMA GSM

1 BAR 7 → 5-93 (+/- 2dB) -90 (+/- 2dB)

2 BAR 5 → 4 -98 (+/- 2dB) -104 (+/- 2dB)

3 BAR 4 → 2 -101 (+/- 2dB) -108 (+/- 2dB)

4 BAR 2 → 1 -104 (+/- 2dB) -110 (+/- 2dB)

5 BAR 1 → 0 -106 (+/- 2dB) -112 (+/- 2dB)

Indication Standby

Bar 3 → 2 3.69 ± 0.05V

Bar 2 → 1 3.53 ± 0.05V

Bar 1 → Icon Blinking 3.40 ± 0.05V

Low voltage, warning message 3.40 ± 0.05V

Power OFF 3.26 ± 0.05V

Page 18

- 19 -

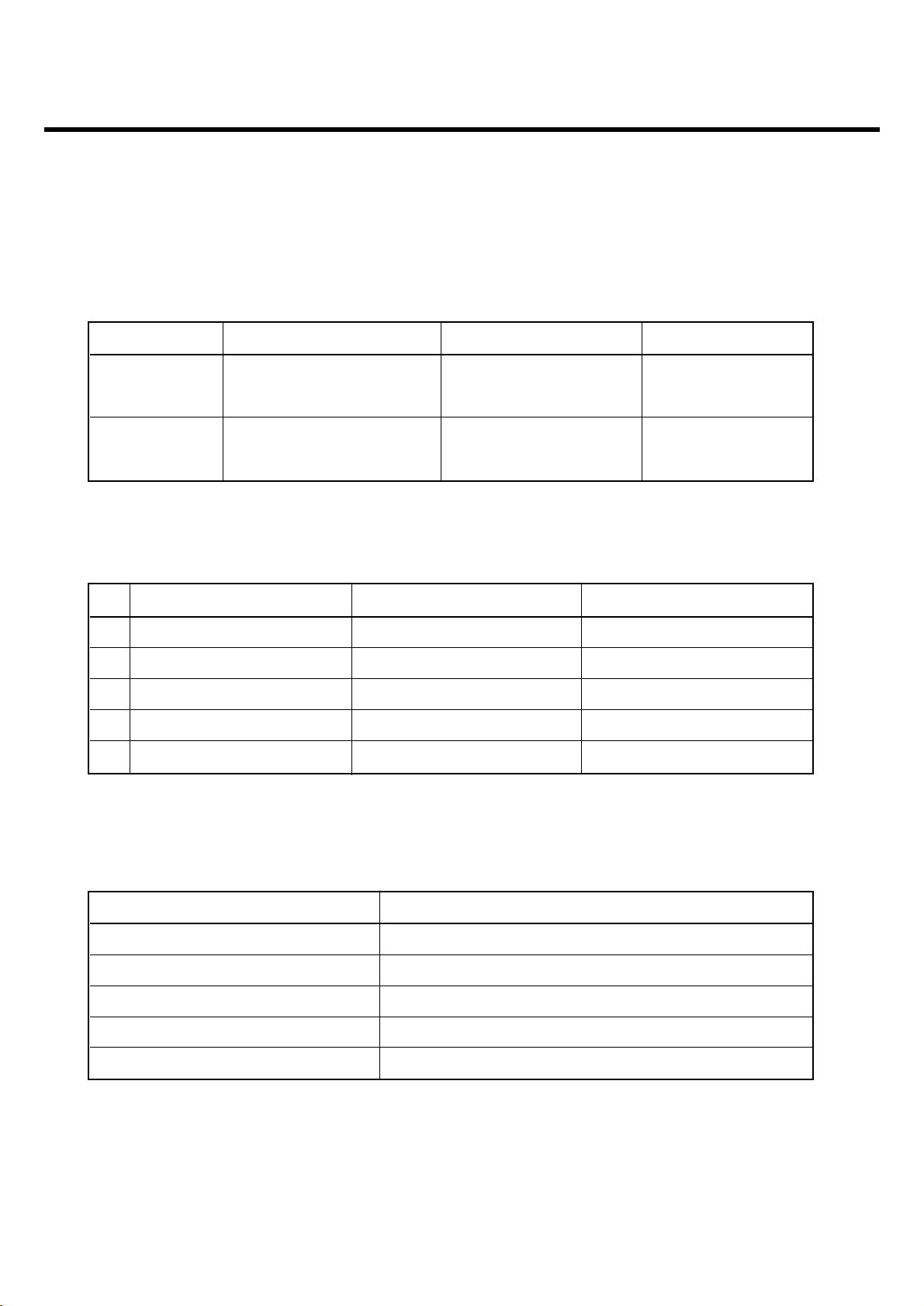

2. PERFORMANCE

2.7 Sound Pressure Level

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

No Test Item Specification

1 Sending Loudness Rating (SLR)

NOM

8 ± 3 dB

MAX

2 Receiving Loudness Rating (RLR)

NOM -1 ± 3dB

MAX -15 ± 3dB

3 Side Tone Masking Rating (STMR)

NOM

17dB over

MAX

4 Echo Loss (EL)

NOM

40dB over

MAX

5 Sending Distortion (SD) refer to TABLE 30.3

6 Receiving Distortion (RD) refer to TABLE 30.4

7 Idle Noise-Sending (INS)

NOM

-64dBm0p under

MAX

8 Idle Noise-Receiving (INR)

NOM -47dBPA under

MAX -36dBPA under

9 Sending Loudness Rating (SLR)

NOM

8 ± 3dB

MAX

10 Receiving Loudness Rating (RLR)

NOM -1 ± 3dB

MAX -12 ± 3dB

11 Side Tone Masking Rating (STMR)

NOM 25dB over

MAX

12 Echo Loss (EL)

NOM

40dB over

MAX

13 Sending Distortion (SD) refer to TABLE 30.3

14 Receiving Distortion (RD) refer to TABLE 30.4

15 Idle Noise-Sending (INS)

NOM

-55dBm0p under

MAX

16 Idle Noise-Receiving (INR)

NOM -45dBPA under

MAX -40dBPA under

MS

HEAD SET

Page 19

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

- 20 -

2.8 Charging

• Normal mode: Complete Voltage: 4.2V

Charging Current: 500mA

• Await mode: In case of During a Call, should be kept 3.9V

(GSM: It should be kept 3.9V in all power level

WCDMA: It will not be kept 3.9V in some power level)

• Extend await mode: At Charging prohibited temperature(0°C under or 45°C over)

(GSM: It should be kept 3.7V in all power level

WCDMA: It will not be kept 3.7V in some power level)

No Test Item Specification

TDMA NOISE

GSM

SEND

GSM: Power Level: 5 REV.

DCS: Power Level: 0

DCS

SEND

17

(Cell Power: -90 ~ -105dBm) REV.

Acoustic(Max Vol.)

GSM

SEND

MS/HEADSET SLR: 8 ± 3dB REV.

MS/HEADSET RLR: -13 ± 1dB/-15dB

DCS

SEND

(SLR/RLR: mid-Value Setting) REV.

MS

Headset

-62dBm

under

Page 20

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 21 -

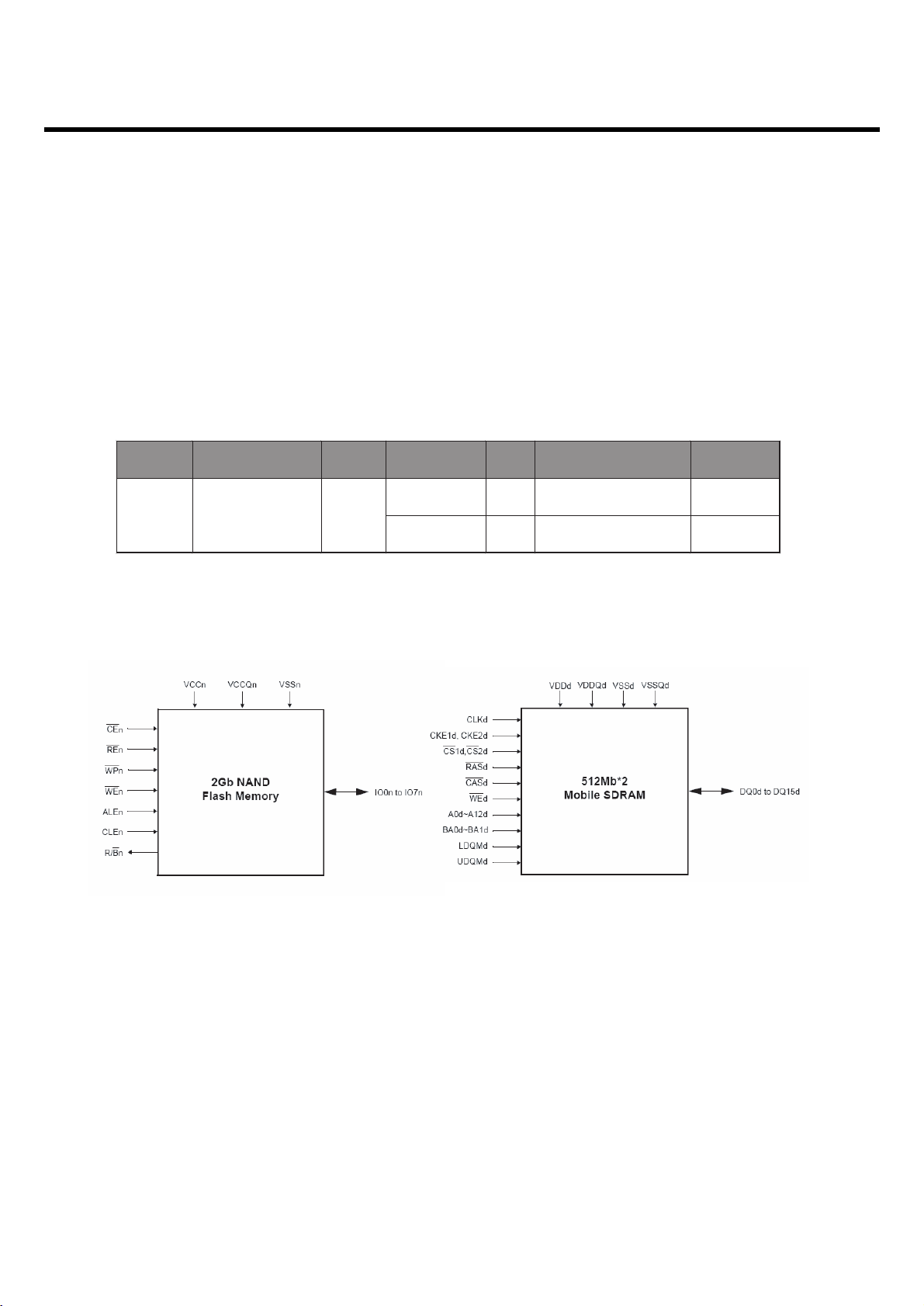

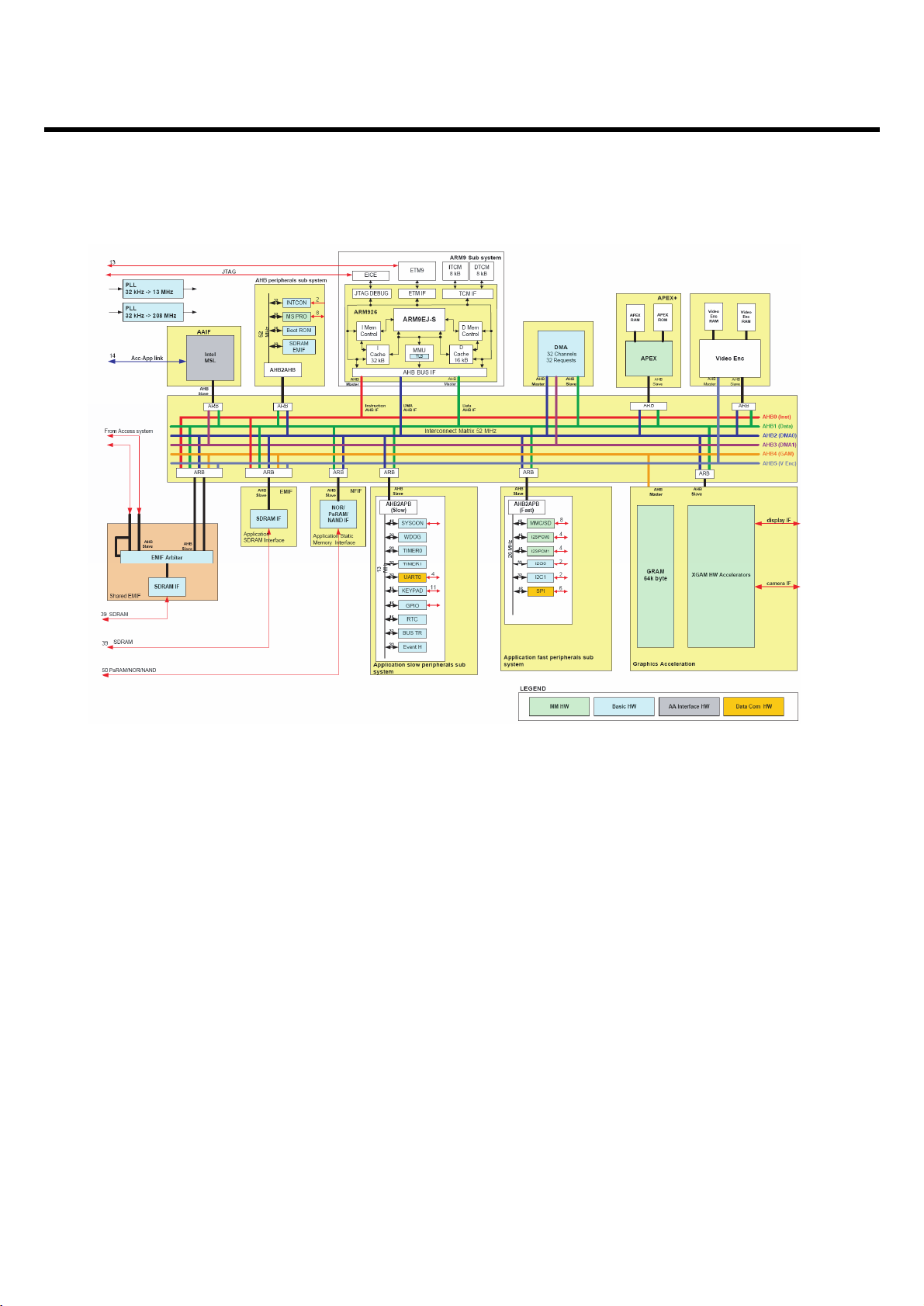

3.1 Digital Baseband(DBB) & Multimedia Processor

3.1.1 General Description

• Access subsystem

- Access Central Processing Unit (CPU) subsystem - ARM926, Joint Test Action Group (JTAG),

Embedded Trace Module (ETM), Instruction and Data (I&D)-cache, and I&D-TCM

- Access peripheral subsystems - Subscriber Identity Module (SIM) interface, IrDA®, Universal

Serial Bus (USB), Universal Asynchronous Receiver/Transmitter (UART), and so on

- Digital Signal Processor (DSP) subsystem - CEVA-X1620, JTAG, Static Random Access Memory

(SRAM), and Program Data Read Only Memory (PDROM)

- EDGE/GSM/GPRS (EGG) subsystem - EGG hardware accelerators

- WCDMA subsystem - WCDMA hardware accelerators

• Application subsystem

- Application CPU subsystem - containing ARM926, JTAG, ETM, I&D-cache, and I&D-TCM

- Application peripheral subsystems - I2C¢‚, keypad, UART, and so on

- Graphics subsystem - XGAM subsystem

- Audio Processing Execution (APEX) and video encoder subsystems In addition to the two

subsystems above, there is also a test block, chip control block, and a pad multiplexing block

residing at the top level

• DSP

- The Digital Signal Processor Subsystem (DSPSUB) includes a DSP megacell, which contains the

DSP CPU together with a tightly coupled memory. The DSP is the Ceva-X 1620 core with a 64 kB

instruction RAM and a 64 kB data RAM. It also contains debug logic and interfaces. In addition to

the megacell, the DSPSUB includes external memories, peripheral units, and interfaces. The DSP

megacell is clocked at 208 MHz.

- The DSPSUB includes an AHB master and an AHB slave interface. The AHB master provides a

direct access to the Internal Random Access Memory (IRAM) in the EGG core through the AHB.

The AHB slave interface allows the CPU and the DMA to access in the program and data RAM

residing in the DSPSUB.

3. TECHNICAL BRIEF

Page 21

- 22 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

• Multi-media Processor(MMIC : ZR3453X )

- The ZR3453X is an advanced multimedia coprocessor for cellular devices. ZR3453X is an MCP

that includes a multimedia core and SDRAM memory chip. The multimedia core performs audio

and video recording, playback, and editing; still image capture (DSC), viewing, and editing;

MIDI/MP3 playback (for ring tones); 3D acceleration (for gaming). The memory chip in the MCP is

a 16MB (2MB) mobile SDRAM (that can be enlarged by packaging to 64MB), used both for

program code and for working data (both stream data and frame buffers).

• WCDMA subsystem

- The digital baseband controller WCDMA subsystem incorporate a WCDMA modem

- An interface to the WCMDA together with memory control and an internal single port RAM. The

WCDMA subsystem has three AHB slave interfaces.

- The Ericsson DB 3150 also includes HSDPA class 6 functionality.

- The WCDMA subsystem is handled and provided by Ericsson.

• XGAM subsystem

- The XGAM subsystem is a graphics acceleration module that provides hardware support in the

creation of visual imagery and the transfer of this data to a display. The XGAM also provides

support for connecting a Camera module. The visual data could be graphics, still images, or video.

- The XGAM subsystem is handled and provided by Ericsson.

• Operation and Services

- I

2

C™ Interface

- SIM Interfaces

- General Purpose I/O (GPIO) Interface

- External Memory Interface that supports NAND, NOR, PSRAM, SDRAM

- JTAG

- RTC

- ETM (in Prototype Package)

Page 22

- 23 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

(

Figure 3-1-1 KF755d Block Diagram

<LCD>

t Sensor

Ligh

From Zoran LCD IF

EMIF

EMIF1

ory

MMem

SDRAM (1G)

NAND (2G)

A

NT

GSM/ EDGE

PA

+ Ant Sw.

P

LED

2

DI

VGA>

<

CDI

SUB PMIC

Digital Baseband Process or (Dual

<Numeric Key>

Application

CPU

DB

cc ess

A

CPU

RF3000

GSM /

EDGE

Transceive

<u- SD card >

Key_IF

315

0

)

core

r

I2C_2

Transceiv

Touc

GPIO_I2C_2

Touch Panel

GPIO_I2C_1

EL Controller

SD_IF

GPIO_I2C_2

Accelerometer

RF3100

WCDMA

r

e

h Button

I2S

S

PI

USB

I2S_1

<BT + FM Radio>

< USB

Transceiver >

I2C_1

Baseban

_0

PCM

AB3000

Analog

Process

or

Audio)

(

d

Headset

FM_ANT

USB

TV_Out

Connector

Connector

18Pin Cradle

18Pin Cradle

AB3000

Analog

Baseband

Processor

(Power

Manageme

<Spk>

BAT_IF

SIM_IF

nt)

Vibrator_IF(PWM)

<Mic

U

<Battery>

<SIM>

Amp

Zoran_GPIO

>

Zoran_CD

<5 Mega>

Zoran_I2

< Zoran >

To EMP CAM IF

nocomeR

kcajraE

TRA

BSU

tuO VT

<Vibrator>

C

SH0.2

I

Page 23

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 24 -

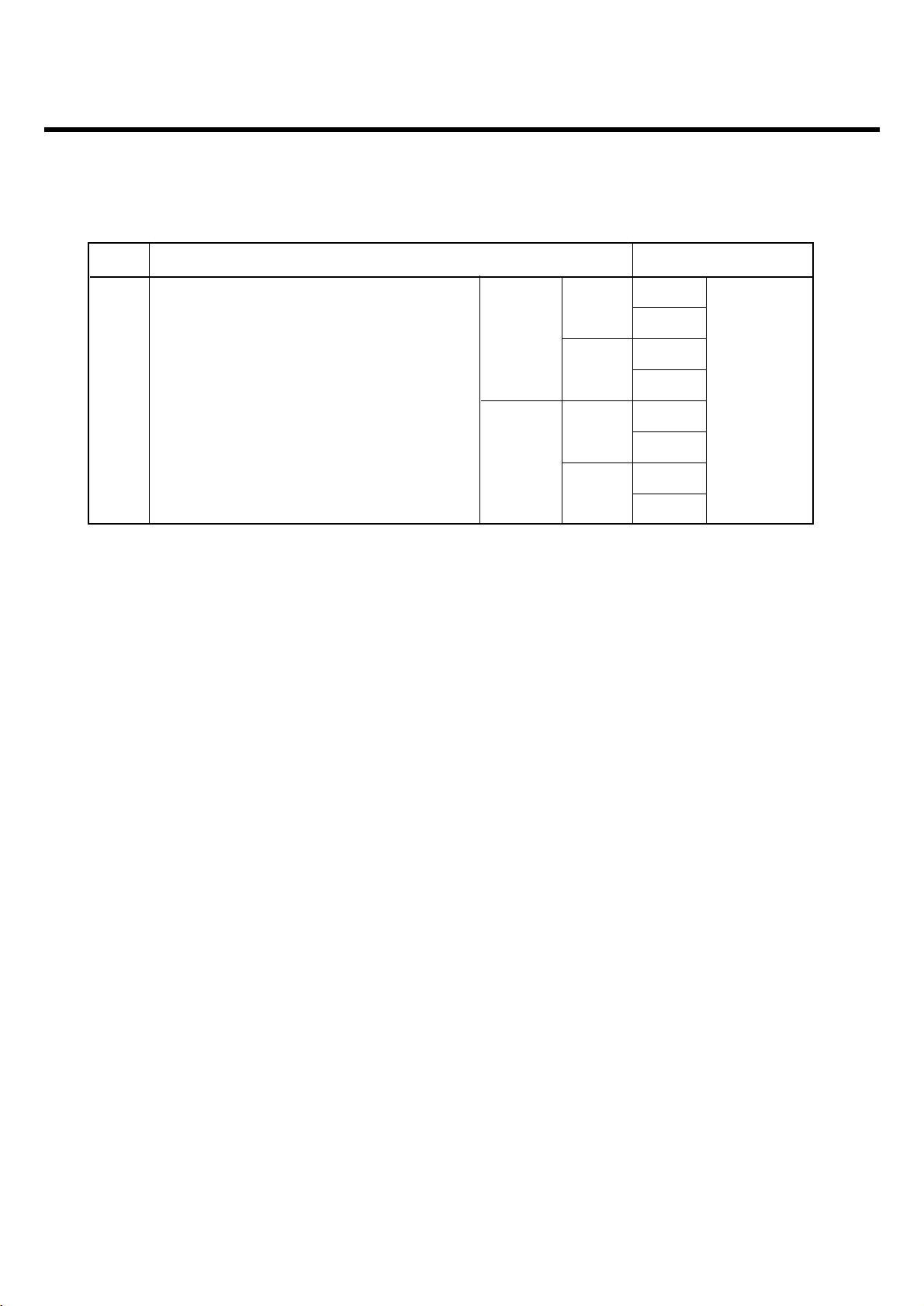

3.1.2 External memory interface

RF calibration data, Audio parameters and battery calibration data etc are stored in flash memory

area.

A. KF755d

• 2Gb NAND flash memory +1G SDRAM

DD evicece P art Nam e M akerer Itemem Tim e S ize Speeeed

Program sp eed 2 00µs1Page=(2K + 64)Bytes 10 .32M Byte/s

Erase spee d 1 .5m s 1Block=(128K+4K)Bytes 88M B yte/s

NAND flash KAL0 0900BM -DJ55 Samsung

Figure 3-1-1 KF755d Block Diagram

Figure 3- 1- 2. External Memory Configuration of KF755d

• Data Communication

- IrDA ® (SIR)

- UARTs (ACB, EDB (RS232))

- Slave USB

• Package

- 12 by 12 mm 344 balls, 0.5mm pitch

FPBGA Production Package

Page 24

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 25 -

3.1.3 Hardware Architecture

A. Block Diagram

Figure 3-1-3. Access system of Ericsson DB3150

Page 25

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 26 -

Figure 3-1-4. Application system of Ericsson DB3150

Page 26

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 27 -

B. CPU Subsystem

• Access CPU subsystem

The digital baseband controller includes an access CPU subsystem, which includes the submodules

described below.

- 32 KiB I-cache

- 16 KiB D-cache

- Page table

- Memory Management Unit (MMU)

- JTAG

- ETM9

- 26 KiB I-TCM

- 8 KiB D-TCM

• Application CPU subsystem

The digital baseband controller includes an Application CPU subsystem, which includes the

submodules described below.

- 32 KiB I-cache

- 16 KiB D-cache

- Page table

- MMU

- JTAG

- ETM9

- 8 KiB I-TCM

- 8 KiB D-TCM

C. Peripheral Hardware Subsystem

The digital baseband controller includes hardware that supports mobile terminal peripherals such as a

MMC, SD, UART, I2C, USB, keypad, and infrared. Collectively, this hardware comprises the

Peripheral subsystem.

The functional blocks of the Peripheral subsystem connect to the peripheral bus through four separate

bridges, which provide a simple interface to support different timing and memory access

arrangements.

Page 27

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

D. DSP Hardware Subsystem

The Digital Signal Processor Subsystem (DSPSUB) includes a DSP megacell, which contains the DSP

CPU together with a tightly coupled memory. The DSP is the Ceva-X 1620 core with a 64 kB

instruction RAM and a 64 kB data RAM. It also contains debug logic and interfaces. In addition to the

megacell, the DSPSUB includes external memories, peripheral units, and interfaces. The DSP

megacell is clocked at 208 MHz.

The DSPSUB includes an AHB master and an AHB slave interface. The AHB master provides a direct

access to the Internal Random Access Memory (IRAM) in the EGG core through the AHB. The AHB

slave interface allows the CPU and the DMA to access in the program and data RAM residing in the

DSPSUB.

E. XGAM Subsystem

The XGAM subsystem is a graphics acceleration module that provides hardware support in the

creation of visual imagery and the transfer of this data to a display. The XGAM also provides support

for connecting a Camera module. The visual data could be graphics, still images, or video.

The XGAM subsystem is handled and provided by Ericsson.

F. System Control Subsystem

The SYSCON resides at the top level of the circuit architecture and is responsible for clock generation

and clock and reset distribution within the digital baseband controller, as well as to external devices.

The block is a slave peripheral under control of the ARM processor. The programming of the SYSCON

controls the fundamental modes of operation within the digital baseband controller. Individual blocks

can also be reset and their clocks held inactive by accessing the appropriate control registers.

3. TECHNICAL BRIEF

- 28 -

Page 28

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 29 -

3.1.4 RF Interface

A. Asta Interface

Asta controls GSM RF part using these signals through GSM RF chip-Gimli.

• RF_DATA_A

• RF_DATA_B

• RF_DATA_C

• RF_DATA_STRB

B. WCDMA Radio Link Interface

• RF_WCDMA_PA_0_EN

• RF_WCDMA_PA_1_EN

• RF_WCDMA_DCDC_EN

• RF_WCDMA_PWRDET_EN

Y4

RF_DATA_A

RF_DATA_B

AA2

Y3

RF_DATA_C

Y2

RF_DATA_STRB

QDATA_AMP_MSB

IDATA_FREQ_MSB

AMP_LSB_FREQ_LSB

DCLK_DATSTR

Figure 3-1- 5. Schematic of Asta RF Interface

Figure 3-1-6. Schematic of WCDMA RF Interface

RF_DATA_STRB

RF_WCDMA_PA_0_EN

RF_WCDMA_PA_1_EN

RF_WCDMA_DCDC_EN

RF_WCDMA_PWRDET_EN

RF_DATA_A

RF_DATA_B

RF_DATA_C

ADC_I_NEG

ADC_I_POS

ADC_Q_NEG

ADC_Q_POS

Y4

AA2

Y3

Y2

AB8

V7

AB5

AB6

Y10

W10

W9

Y9

QDATA_AMP_MSB

IDATA_FREQ_MSB

AMP_LSB_FREQ_LSB

DCLK_DATSTR

WTX_BAND_1_EN

TP300

WDCDC_EN

WPOW_DET_EN

WRX_I_N

WRX_I_P

WRX_Q_N

WRX_Q_P

DAC_I_NEG

DAC_I_POS

Y8

W8

W7

WTX_I_N

WTX_I_P

Page 29

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

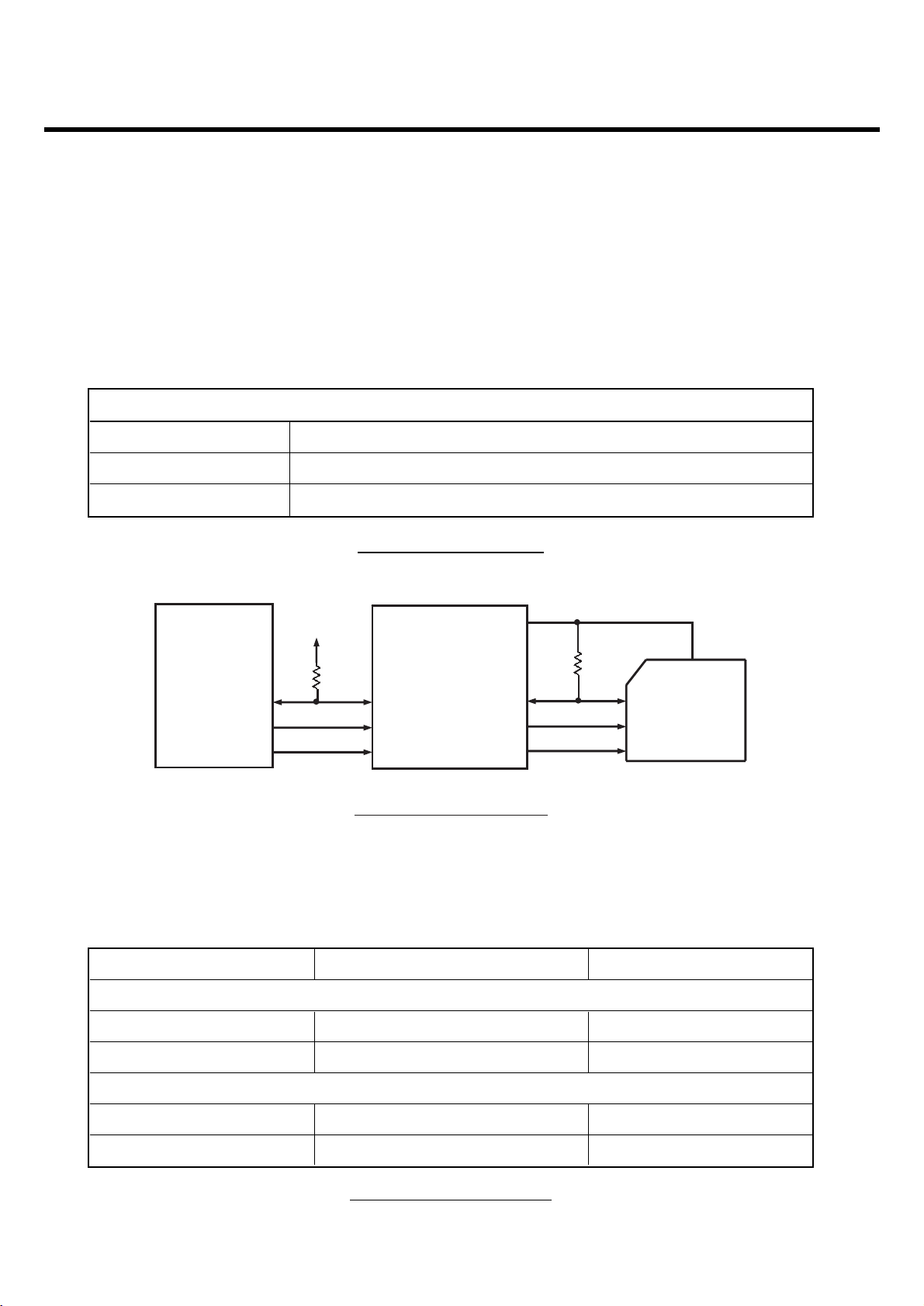

3.1.5 SIM Interface

SIM interface scheme is shown in Figure3-1-6.

SIMDAT0, SIMCLK0, SIMRST0 ports are used to communicate DBB(Asta) with ABB(Veronica) and

filter.

3.1.6 UART Interface

UART signals are connected to Asta GPIO through IO connector

3. TECHNICAL BRIEF

- 30 -

SIM (Interface between DBB and ABB)

SIMDAT0 SIM card bidirectional data line

SIMCLK0 SIM card reference clock

SIMRST0 SIM card async/sync reset

Resource Name Note

UART0

ACC_GPIO_2 ACC_UART_RX ACC Receive Data

ACC_GPIO_3 ACC_UART_TX ACC Transmit Data

UART1

APP_GPIO_0 APP_UART_RX APP Receive Data

APP_GPIO_1 APP_UART_TX APP Transmit Data

Table 3-1-2. SIM Interface

Table 3-1-3. UART Interface

Figure 3-1-7. SIM Interface

Asta

SIMDAT0

SIMCLK0

SIMRST0

VDD

E

10K

SDAT SIMDAT

SCLK SIMCLK

SRST

SIMVCC

Veronica

SIMRST

10K

VDD

DAT

CLK CARD

RST

Page 30

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3.1.7 GPIO (General Purpose Input/Output) map

In total 39 allowable resources. This model is using 39 resources.

GPIO Map, describing application, I/O state, and enable level are shown in below table.

3. TECHNICAL BRIEF

- 31 -

Table 3-1-4. Asta ACC GPIO Map Table

DB3150's GPIO GPIO Mapping Init Status

ACC_GPIO_0 ACC_GP00_USB_STP Output low

ACC_GPIO_1 ACC_GP01_USB_DIR input

ACC_GPIO_2 ACC_GP02_UART0_RX input

ACC_GPIO_3 ACC_GP03_UART0_TX Output

ACC_GPIO_4 ACC_GP04_USB_CLK input

ACC_GPIO_5 ACC_GP05_USB_NXT input

ACC_GPIO_6 ACC_GP06_USB_DAT4 input / Output

ACC_GPIO_7 ACC_GP07_USB_DAT5 input / Output

ACC_GPIO_8 ACC_GP10_USB_DAT6 input / Output

ACC_GPIO_9 ACC_GP11_USB_DAT7 input / Output

ACC_GPIO_10 ACC_GP12_TOUCH_LDO_EN Output low

ACC_GPIO_11 ACC_GP13_SPK_AMP_EN Output low

ACC_GPIO_12 ACC_GP14_BT_SPI_INT Input

ACC_GPIO_13 ACC_GP15_FLIPSENSE Input

ACC_GPIO_14 ACC_GP16_FM_GPIO2 Input

ACC_GPIO_15 ACC_GP17_PHFSENSE Input

ACC_GPIO_16 ACC_GP20_USB_CS_PD input / Output

ACC_GPIO_17 ACC_GP21_VC_IO_OFF Output low

ACC_GPIO_18 ACC_GP22_USB_DAT3 input / Output

ACC_GPIO_19 ACC_GP23_BT_SPI_CS0n Output

ACC_GPIO_20 ACC_GP24_BT_SPI_DAT0 Output low

ACC_GPIO_21 ACC_GP25_BT_SPI_DAT1 Input

ACC_GPIO_22 ACC_GP26_BT_SPI_CLK Output low

ACC_GPIO_23 ACC_GP27_AMP_SW_EN Output low

Page 31

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 32 -

Table 3-1-5. Asta APP GPIO Map Table

Table 3-1-5. MMIC APP GPIO Map Table

DB3150's GPIO GPIO Mapping Init Status

APP_GPIO_0 APP_GP00_UART_RX Input

APP_GPIO_1 APP_GP01_UART_TX Output

APP_GPIO_2 APP_GP02_MMP_INT_n Input

APP_GPIO_3 APP_GP03_MMP_PWR_EN Output low

APP_GPIO_4 APP_GP04_TOUCH_SCREEN_INT Input

APP_GPIO_5 APP_GP05_TOUCH_SCREEN_SCL Output

APP_GPIO_6 MICROSD_DAT3 Input

APP_GPIO_7 APP_GP07_3AXIS_INT Input

APP_GPIO_8 APP_GP10_MMP_RESET_N Output low

APP_GPIO_9 APP_GP11_REMOTE_INT Input

APP_GPIO_10 APP_GP12_LCD_ID Input

APP_GPIO_11 APP_GP13_MC_CLKRET Input

APP_GPIO_12 SUB_PM_RESETB Output low

APP_GPIO_13 MOTOR_EN Output low

APP_GPIO_14 APP_GP16_TOUCH_SCREEN_SDA input / Output

DB3150's GPIO GPIO Mapping Init Status

GPIO_0 CI_VSYNC_WITHOUT_FF Output low

GPIO_1 APP_GP05_TOUCH_RESET Output low

GPIO_2 CI_VSYNC Output low

GPIO_3

GPIO_4 MMP_CAM_RESET_N Output low

GPIO_5 MMP_CAM_PWR_EN Output low

GPIO_6 MMP_CAM_PWDN Output low

GPIO_7 FLASH_LED_EN Output low

GPIO_8 FLASH_LED_TORCH Output low

GPIO_9 FLASH_LED_INH Output low

Page 32

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 33 -

3.1.8 USB

The USB block supports the implementation of a °∞High-speed" device fully compliant to USB 2.0

standard. It provides an interface between the CPU (embedded local host) and the USB wire, and

handles USB transactions with minimal CPU intervention.

The USB specification allows up to 15 pairs of endpoints. Data for each endpoint is buffered in RAM

within the USB block and is read/written from the endpoint FIFO using DMA transfers or FIFO register

access. High-speed (high throughput) endpoints can use DMA while slower endpoints can use FIFO

register access.

The USB block can request up to six DMA channels, three for IN endpoints and three for OUT

endpoints.

USB Function Note

USB_STP ULPI stop signal

USB_DIR ULPI direction signal

USB_CLK USB clock

USB_NXT ULPI next signal

USB_DAT0 USB data0

USB_DAT1 USB data1

USB_DAT2 USB data2

USB_DAT3 USB data3

USB_DAT4 USB data4

USB_DAT5 USB data5

USB_DAT6 USB data6

USB_DAT7 USB data7

USB_CS_PD USB chip select

VBUS Power supply for Asta USB block

Table 3-1-6. USB Signal Interface of Asta

Page 33

- 34 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

A

A

A

A

Figure 3-1-8. Schematic of Asta USB block

A

Figure 3-1-9. Schematic of USB Transceiver

PTS_BSU_00PG_CCA

RID_BSU_10PG_CCA

C

C

0PG_

A

X

_0TRAU_2

R

XT_0TRAU_30PG_CCA

KLC_BSU_40PG_CCA

TXN_BSU_50PG_CCA

4TAD_BSU_60PG_CC

5TAD_BSU_70PG_CC

C

U_

_

C

D

BS

01PG

6TA

_

7TAD_BSU_11PG_CC

USB_DAT1

USB_DAT0

USB_DAT2

9J

9K

2P

A

9

N

A

9M

4N

3P

A

4P

A

R

4

3R

2

R

L4

USB_DAT_VP

L3

USB_SE0_VM

M4

USB_OE

CCA

0_OIPG_CCA

1_OIPG

_CCA

2_OIPG_CC

3_OIPG_CC

4_OIPG_

5_OIPG_CCA

6_OIPG_CC

7_OIPG_CC

8_OIPG_CCA

9_OIPG_CCA

TABV

8V

1_EDDV

106C

00

6C

u7

.4

u1.0

60

30

V01

F1

F2

F3

C

3

DP_SC_BSU_02PG_CC

R603 51K

A

CA

KLC_BSU_40PG_CCA

0TAD_BSU

1TAD_BSU

2TAD_BS

U

3TAD_BSU_22PG_CCA

4TAD_BSU_60PG_CCA

5

TAD_BSU_70PG_CCA

6TAD_BSU_01PG_CCA

7TAD_BSU_11PG_CC

N_BSU_50PG_CCA

TX

PTS_BSU_00PG_CCA

ID_BSU_10PG_C

R

0.1uC603

4.7u

C602

C

4

A

C

1B

1A

TAD

2A

3A

D

5A

6A

6B

6C

5

D

6

D

P

TS

5E

RID

1E

6E

0

306

NC1

NC2

LES_PIHC

VCC

KCOL

0ATAD

1A

2ATAD

106U

3ATA

4ATAD

5ATAD

6ATAD

7ATAD

0GFC

8V1FER

GND1

GND2

GND3

E4

D2

4

TSET

5B

1OI_CCV

2B

2OI_CCV

2C

RR

FE

1C

MD

1D

PD

2E

TEA8051PSI

TLUAF

3D

DI

3B

2

GFC

4B

1

GFC

4

D

N_WSPTXN

F

4

SUBV

3E

3

V3GER

5

F

1LATX

6F

TX

2LA

C5

0.1uC604

60

0.1u

1%

30

R606 12K

C605

6R

2.2uC607

4.7uC606

3060

U

MD_BS

PD

U

_BS

K150

U_SUBV

XRT_BS

1LATX_BSU

deepS hgiH rof reviecsnarT BSU

Page 34

- 35 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3.1.9 Slider ON/OFF Detection

There is a magnet to detect the slide module status, up or down.

If a magnet is close to the hall-effect switch U101, the voltage at Pin 4 of U101 goes to 0V.

Otherwise 1.8V.

This SLIDE_DET signal is delivered to Asta ACC_GP15_FLIPSENSE.

Figure 3-1-10. Slider On/Off Detector

LS

I

57V2_GDDV

1

DV

D

2

901C

u1.0

3

1DNG

N

C

TCETED ED

DV

5MB21006KT101U

6

DDV_OI

5

2DNG

4

UO

T

8V1_ED

NESPILF_51PG_CCA

ES

211

C

u1.0

Page 35

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 36 -

3.1.10 Bluetooth Interface

KF755d supports Bluetooth operation using STLC2593C Bluetooth module.

A. General Description

The Bluetooth interface utilizes the SPI interface for control signals going to and from the Bluetooth

module. The SPI is also used for data transmissions.

It uses the PCM interface for transmitting audio to and from the Bluetooth module.

The Bluetooth module uses both the 26 MHz master clock signal and the 32,768 kHz low-frequency

clock signal for internal timing within the Bluetooth module. The intention is to use the low-frequency

clock as a low-power timing provider and to use the 26 MHz as a high precision timing reference used

mainly by the Bluetooth radio during operation.

The clock request mechanism is used to minimize current consumption for the total system.

The intention is to use the CLKREQ signal to ask for the master clock when needed, for example,

when the Bluetooth radio is operating.

B. SPI Interface

The physical SPI interface is made up of 5 signals : clock, chip select, data in, data out and interrupt.

When the SPI mode is selected , these signals are available through the BT_UART and

BT_HOST_WAKEUP pins.

The SPI interface is Master at the Host side, and Slave at the BT Controller side.

It is designed to work with the H4 protocol. It does not support HCI synchronous data packet transfer.

Data are transferred on the SPI interface in byte format, LSB first.

The SPI interface can operate only in half duplex mode.

C. PCM Interface

The PCM interface is used to send audio to and from the Bluetooth module. The interface is a

synchronous interface using a PCM clock and a PCM sync signal for synchronization. Two data

signals are used for data, one in each direction.

The PCM clock signal operates at frequencies as high as 1 MHz. The word length of the audio data

can be 8 or 16 bits. Furthermore, the PCM interface has a function known as MP-PCM, which is an

addressing scheme, used to have more than two devices talking on the bus.

To add this function, the data pins have to be bi-directional. Additionally, the position of the audio data

relative to the frame sync pulse must be selectable. During the periods within a frame that a device is

not transmitting audio data, it must put both PCM data signals in a high-impedance state to allow other

devices access.

Page 36

D. Master Clock and Clock Request Interface

The master clock (MCLK) is a 26 MHz signal used as the high precision clock signal for the Bluetooth

module. The signal can be switched on and off by the platform. The master clock request (CLKREQ) is

used by the Bluetooth module to ask for the master clock.

If the Bluetooth module asserts the signal high, it gets the master clock. The other alternative for the

Bluetooth module is to set the clock request output to high impedance state, indicating that it does not

need the master clock. The Bluetooth module receives the master clock, if other parts of the chipset

request it.

E. Low Frequency Clock Interface

The low-frequency clock signal (RTCCLK) is used by the Bluetooth module as a low-power clock. The

clock is used in different Bluetooth modes, like sniff and park, to have a correct timing on the Bluetooth

air interface without having the master clock running.

The low-frequency clock is always present, in some applications even when the chipset is powered

down.

F. STLC2593C

■ WFBGA 5.0 x 7.5 x 0.8 mm lead-free/RoHs compliant 100 pins

■ External component: B-BPF (Bluetooth)

■ PCB footprint < 45mm2

■ Based on Ericsson Technology Licensing Baseband Core (EBC)

■ Bluetooth¢‚ specification compliance: V2.0 + EDR.

- Point-to-point, point-to-multi-point (up to 7 slaves) and scatternet capability

- Support ACL and SCO links

- Extended SCO (eSCO) links

- Faster Connection

■ HW support for packet types

- ACL: DM1, DM3, DM5, DH1, DH3, DH5, 2-DH1, 2-DH3, 2-DH5, 3-DH1, 3-DH3, 3-DH5

- SCO: HV1, HV3 and DV

- eSCO: EV3, EV4, EV5, 2-EV3, 2-EV5, 3-EV3, 3-EV5

- Adaptive Frequency Hopping (AFH)

■ Transmit Power

- Power Class 2 and Power Class 1.5 (above 4dBm)

- Programmable output power

- Power Class 1 compatible

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 37 -

Page 37

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 38 -

■ HCI

- HCI H4 Transport Layer

- HCI proprietary commands (e.g. peripherals control)

- Single HCI command for patch/upgrade download

■ Supports Pitch-Period Error Concealment (PPEC)

■ Efficient and flexible support for WLAN coexistence in collocated scenario

■ Low power consumption

- Ultra low power architecture with 3 different low-power levels

- Deep Sleep modes, including Host power saving feature

- Dual Wake-up mechanism: initiated by the Host or by the Bluetooth device

■ Communication interfaces

- Fast UART up to 4Mbit/s

- SPI interface

- PCM interface

- Up to 10 additional flexibly programmable GPIOs

- External interrupts possible through the GPIOs

- Fast master I2C interface

■ Clock support

- System clock input (digital or sine wave) at9.6, 10, 13, 16, 16.8, 19.2, 26, 33.6 or 38.4MHz

- Low Power clock input at 32.768 kHz

■ ARM7TDMI CPU

■ Memory organization

- On chip RAM, including provision for patches

- On chip ROM, preloaded with SW up to HCI

■ Ciphering support up to 128 bits key

■ Single power supply with internal regulators for core voltage generation

■ Supports 1.65 to 2.85 Volts IO systems

■ Auto calibration (VCO, Filters)

Page 38

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 39 -

G. KF755d Bluetooth Schematic

• Clock

- Clock request

→ Connected to CLKREQ of Asta and Veronica, input to Gimly

- Fast clock : 26MHz

→ Supplied MCLK from Gimly

→ Frequency deviation : ± 20ppm

- Low power clock : 32.768kHz

→ Supplied RTCCLK from Veronica

• Power

- Supplied 2.75V, 1.8V from internal regulators of Veronica

• Reset

- RESOUT2_n signal of Asta controls STLC2593C reset.

• SPI

- Connected to SPI of Asta

- HCI interface between Asta and STLC2593C

• PCM

- Audio signal interface between Asta/Veronica and STLC2593C

• ANT

- 2.4GHz, 50 ohm matching

A

Figure 3-1-11. Schematic of STLC2593C

108PT

0

1

U

8

308

R

KLC_TB

0

008C

IND

8V1_EDDV

ABV

T

8V1_EDDV

R808

100K

C

2OIPG_MF_61PG_C

8

DDV

V1_E

R

n_2TUOSE

108C

IND

EGNAHC TON OD

KLCCTR

1TAD_IPS_TB

A

_52PG_CC

KLC_IPS_TB_62PG_CCA

C

A

NYS_MCP_CC

KLC_MCP_CCA

DLD_MCP_CCA

DLU_MCP_CCA

NI_IPS_TB_41PG_CCA

T

n_QERKLC_TB

57V2_KDDV

R807 0

C809 0.1u

PT

418

UOSER

n_1T

L

A

CS_C2I_PP

KLCCTR

7K

6

F

B

K

9

9L

9H

K

6

B

N

4

MCP_T

B

4

M

5K

A_MCP_TB

5M

MCP_T

B_

B

3

M

118PT

908PT

018PT

218PT

3K

K

4

B

3J

3

L

TB

9G

B

7E

9

F

8E

7

L

7M

B

6

N

8J

2B

RVSR_T

B

C

3

B

8

M

RVS

R_TB

1C

C

2

2M

B

4J

C_GE

R_TB

N

7

DVH_T

B

6E

B

0.1u

4

D

CN

1

7

F

2CN

C810

8F

3C

N

4

L

4CN

5

L

CN

5

6L

6CN

4A

AV_MF

3

B

DV_MF

7A

1OIPG_MF

6A

2OIPG_MF

5

A

MF

3OIPG_

8

B

PIMF_MF

9C

BTSR_MF

7

D

K

LCR_MF

D

9

NES_MF

B

9E

KLCS_MF

10p

22nC815

C814 22n

C816

2

T

95

3

C

S

L

7J

1_T

NTESER_TB

KLC_PL_TB

P

UEKAW_TB

R_TRAU_TB

YS_

9_OIPG_TB

1

1_OIPG_TB

01_OIPG_T

61_OIPG_TB

8_OIPG_

0_OIPG_T

W_TSOH_TB

_GIFNOC_TB

_GIFNOC_T

_GIFNOC_TB

D_

N_RVSR_TB

FR_RVSR_T

DLC_DDV_T

UO_QER_KLC_TB

_KLC_FER_T

NI

DX

STC_TRAU_T

CN

KLC_MCP_TB

1_NI_QER_KLC_TB

NI_QER_KLC_TB

2_

PUEKA

1

2

3

1LC_

2LC_RVSR_T

MSD_RVSR_TB

LRT

7G

T_TRAU_TB

DX

6

J

STR_TRAU_

TB

1K

PFR_TB

1J

NFR_T

B

6

M

A_OIV_TB

9J

B_O

IV_TB

3

N

C_OIV_TB

5N

D_OIV_TB

8G

E_OIV_TB

H

6

GIDSSV_TB

1

7H

DSSV_TB

2GI

H

8

3GIDSSV_TB

8K

DSSV_T

4GI

B

8L

5GIDSSV_TB

1D

B

1ANASSV_T

2D

2ANASSV_TB

3E

ASSV_

3AN

TB

1F

ANASSV_TB

4

F

2

5AN

TB

ASSV_

3F

6ANASSV_TB

4F

B

7ANASSV_T

1G

B

8ANASSV_T

3G

9AN

TB

ASSV_

G

4

01ANASSV_TB

3H

2_TUO_QER_KLC_TB

ASSV_T

11AN

B

4

H

1ANASSV_TB

2

1H

RSSV_TB

1F

L

1

FRSSV_TB

2

2

J

RSSV_

3F

TB

K

2

FRSSV_TB

4

2L

1AVH_TB

3

D

VH_T

2A

B

1E

3AVH_TB

2E

4AVH_TB

4E

5AVH_TB

2H

B

1TSET_T

2G

B

2TSET_T

6G

GRP_FA_TB

5C

T

UOR_MF

B

5

UOL_M

T

F

D

6

OIV_MF

8D

OI

DS_MF

A

3

1D

MF

NG_

B

4

2

DNG_MF

B

6

3DNG_MF

7B

4

DNG_MF

C

4

5D

MF

NG_

6C

6

DNG_MF

C

7

7

DNG_MF

5D

DNG_MF

8

C

8

F

DNGFR_M

F+( htooteulB

DV

ANA_TB_SSV

FR_TB_SSV

808C

0

u1.

ANA_TB_SSV

)oidaR M

0TAD_IPS_TB_42PG_CCA

n0SC_IPS_TB_32PG_CCA

5

B

4

B

8V

1_ED

08BF

0

06

408

C

u1.0

KDDV

_EDDV

DS_C2I_PPA

A

0

1C3407-TB054212AED008LF

1

U

1P

PB_

2

D_PB2P

C

G2

3G16

V

FR_TB_SSV

7V2_

5

8V1

318C

u1.

C817

120p

C803

8TUO

10

1nH

08CHn9.3

2

008L

n3.

H

3

FR_TB_SS

u1118C

u1

21

8C

O

U

O

308TU

208T

p

2.1

108L

FR_TB_SSV

PR_M

F

PL_MF

TNA_MF

Page 39

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 40 -

3.1.11 MicroSD Interface card

KF755d supports the MicroSD card interface as external memory card.

MicroSD card has 4-data line, so KF755d uses 4-data line.

All control and data line is connected to Asta.

Cause of the difference between Asta and MicroSD card, a level shifter should be added.

• Card detection

- When there are no card in MicroSD card socket, REAL_MICROSD_DAT3 pin is high cause of an

internal pull-up.

- If Card is inserted in socket, The pull up can be disconnected by using SET_CLR_DETECT

command.

- VDDG_2V75 always supply power.

A

Figure 3-1-12. MicroSD card and Schematic of MicroSD card Interface

MicroSD card Interface

MICROSD_CMD Command/Response

MICROSD_CLK Clock

MICROSD_DAT Data line

VDDG_2V75 Supply voltage from Veronica internal LDO

Table 3-1-7. MicroSD card Interface

8V1_EDDV

246

8

RA1

0TAD_DSORCIM

CIM

M

M

RID_TAD_DSOR

TAD_DSORCI

1

2TAD_DSORCIM

TAD_DSORCI

3

RID_DMC_DSORCIM

D

MC_DSORCIM

KLC_DSORCIM

TERKLC_CM_3

1PG_PP

135

100K

7

R907

470K

5A

CV

AC

C

5

TAD

RID_0

2B

A0TAD

C

1

RID_321TAD

D

A1TA

B

4

A

4

D

A3TA

B

5

C

RID_DM

1B

ADMC

3A

AKLC

A

1

F_KL

C

3B

1DNG

3C

NG

109C

u1.0

2D

RYXZE604ACVA47NS009U

D

5

CCV

B

2D

B0TA

D

1D2A

D

B1TA

C

4

B2TADA2TAD

4D

B3TAD

C

2

BDMC

3D

BKLC

57V2_GDDV

246

8

RA2

309C

0

u1.

100K

3

5

7

1

R916 100K

TAD_DSORCIM_LAER

0

1TAD_DSORCIM_LAER

2TAD_DSORCIM_LAER

RCIM_LAER

3TAD_DSO

DMC_DSORCIM_LAER

KLC_DSORCIM_LAER

DNI

R941

Page 40

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 41 -

3.1.1 Power On Sequence

User presses END key and then ONSWAn signal is changed to Low.

Veronica initiates the internal oscillator and powers on the regulators.

Veronica generates a power for Asta.

Veronica releases the power reset signal(PWRRSTn) and generates an interrupt(IRQ0n) to Asta.

Figure 3-1-13. Power On Sequence

Press

END key

ONSWA

Veronica

Power for Asta

PWRRST

n

ONSWA

IRQ

PWRRSTn

IRQ0n

Asta

RESPOW_N

IR

Q0_N

Page 41

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 42 -

3.1.13 KeyPad, Touch button and Touch screen

There are 21 buttons and 5 side keys and touch button in Figure 2-1-13/14. Shows the Keypad circuit.

‘END’ Key is connected ONSWAn for Veronica.

When Touch button and Touch screen is touched, Interrupt is given to Asta than, she read the status

register what button is touched by I2C. I2C is realize by Asta GPIO.

Figure 3-1-14. KEY CIRCUIT

Table 3-1-8. Key Matrix Mapping Table

KEYIN0 KEYIN1 KEYIN2 KEYIN3 KEYIN4 KEYIN5

KEYOUT0 VOLUME1 VOLUME2

KEYOUT1 1 2 3 MULTI SEND OK

KEYOUT2 4 5 6 CAMAF CLR

KEYOUT3 7 8 9 CAMSHOT

KEYOUT4 * 0 # HOME

8V1_EDD

V

246

8

10

1AR

101

K

01

135

7

YEK

1TUO

K

2TUOYE

3TUOYEK

0NIYEK

4TUOYEK

1NIYEK

2NIYEK

3

NIYEK

DNE

S

1TUOYEK

2TUOYEK

4NIY

EK

5NIYEK

8

V1_EDDV

RLC

009RK

01

109R

K01

1

015

4

45

701

7

4TO

H

K

O

009D

03-S125BR

YEK_REBMUN

1

2

1

0

8019

8

011

0

3

0120

3

601

6

1

0

9

201TOH101TOH

H

5TO

n_AWSNO

n_AWSNO

009AV

R

I

F053X4150SVC

_

K WS

NO

YE

2TUOYEK

3TUOYEK

3NIYE

K

1TUOYEK

4TUOYEK

3NIYEK

DNE

4

3

0TUOYE

K

0NIYEK

I

1

YEK

N

1

011WS

1

2

ITLU

M

EMOH

307NC

1

2

3

4

Page 42

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 43 -

A

Figure 3-1-15. Touch button and Touch screen connector

I2C interface

V1.3_HCUOT

109NC

8171

1

2

3

4

5

6

41

31

21

11

0

1

9

87

6151

R905

DNI

R906

4.7K

R907

4.7K

TNI_NEERCS_HCUOT

LCS_NEERCS_HCUOT

DS_NEERCS_HCUOT

Page 43

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 44 -

3.1.14 Multi EL lighting

There are 13 EL lighting channel. Each lighting channel is operated independently. EL

controller(U901) control AC generator and EL driver(U900). AC generator generate 190V AC signal.

And this 190V AC signal is switched by EL driver. Through EL driver, AC signal of the each lighting

channel is switched independently. Finally, switched AC signal illuminate EL sheet.

Figure 3-1-16. Multi EL lighting

EL controller AC generator EL driver EL lighing channel

output (connected with

EL sheet)

VREG_6.1V

C902

2.2u

TOUCH_3.1V

0.1u

C904

TP902

28

32

33

GND

VSS1

1

P0_1

2

P2_7

3

P2_5

4

P2_3

5

P2_1

6

P3_3

7

P3_1

8

P1_7

P1_3

P1_5

9

10

30

29

31

P0_5

P0_3

U901

CY8C21434

VSS2

P1_1

12

13

11

P0_7

P1_0

26

27

25

VDD

P0_4

P0_6

P0_2

24

P0_0

23

P2_6

22

P2_4

21

P2_2

20

P2_0

19

P3_2

18

P3_0

17

XREX

P1_2

P1_4

P1_6

14

15

16

0

R909

L900

100uH

D5

D1 D2 D3 D4

Q900

SIA450DJ

G

S1 S2

R912

100K

TOUCH_SCREEN_SCL

TOUCH_SCREEN_SDA

I2C

D901

RF051VA2S

TOUCH_RST

R910

C903

470pF

R913

TP905

TP906

TP907

TOUCH_BUTTON_SCL

TOUCH_BUTTON_SDA

100K 10M

ISSP

C905

150p

TOUCH_3.1V

C907

0.1u

C906

0.1u

U900

SLUG

NC5

NC4

NC3

NC2

NC1

_POL

_LE

GND

DOUT

CLK

DIN

VDD

HV509

33

25

23

18

16

13

21

22

15

24

19

17

20

HVGND

HVOUT16

HVOUT15

HVOUT14

HVOUT13

HVOUT12

HVOUT11

HVOUT10

HVOUT9

HVOUT8

HVOUT7

HVOUT6

HVOUT5

HVOUT4

HVOUT3

HVOUT2

HVOUT1

VBIAS

VPP

28

BP

27

TP903

29

30

31

32

1

2

3

4

5

6

7

8

9

10

11

12

14

26

R91556K

HV_OUT_14

HV_OUT_13

HV_OUT_12

HV_OUT_11

HV_OUT_10

HV_OUT_9

HV_OUT_8

HV_OUT_7

HV_OUT_6

HV_OUT_5

HV_OUT_4

HV_OUT_3

HV_OUT_2

BP

Page 44

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 45 -

3.2 GAM Hardware Subsystem

3.2.1 General Description

The Graphics Accelerator Module (GAM) subsystem provides hardware support in the creation of

visual imagery and the transfer of this data to the display. GAM also provides support for the camera

module. The visual data could be graphics, still images or video. The GAM subsystem consists of five

modules:

• GRAM : graphics memory (160 kB).

• GAMCON : GAM controller.

• GRAPHCON : graphics controller.

• PDI/SSI : programmable display interface for parallel/serial displays.

• CDI : camera data interface.

Figure 3-2-1. GAM Subsystem Functional Block Diagram

Page 45

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 46 -

3.2.2 Block Description

A. GAM Controller(GAMCON)

The GAM Controller (GAMCON) is responsible for clock gating and distribution within the GAM

module. GAMCON receives the HCLK from SYSCON and distributes to GRAPHCON, GRAM, PDI and

CDI. GAMCON also distributes the GAM reset signal to GRAPHCON, GRAM, PDI and CDI.

The reset signals CIRES_N and PDIRES_N are distributed from GAMCON to the camera and display

module respectively, see Figure 2.28. The CIPCLK is used to clock the received data into the camera

data interface. The CIPCLK can be in the range of 100 kHz to 16 MHz.

B. Graphics RAM (GRAM) Block

GAM includes 160 kB of graphics memory (GRAM) in order to support display screen sizes of QCIF +

alfa display size and three frame buffers when decoding QCIF video.

The GRAM can be accessed in 8, 16 or 32-bit mode. Write access takes a single AHB clock cycle.

Non-sequential read and the first access of a sequential read access takes two AHB clock cycles.

Subsequent sequential read access take a single AHB clock cycle.

The GRAM contains both frame buffer and temporary data. There are three image areas with one

used for normal MMI graphics and the other two areas used for still images, video frames or camera

frames. The three image areas can be combined into one frame buffer.

GRAM is required to transfer a VGA (640 by 480 pixels) image from the camera data interface (CDI)

over DMA at 100 MBit/s, within a 50 ms timeframe. The GRAM is used as a buffer, but the average

transfer bandwidth required is approximately 3 Mword/s (32-bit word), that is 12 MByte/s.

C. Graphics Controller (GRAPHCON) Block

GRAPHCON is controlled by the application CPU and can perform operations on pixels and image

areas. Images can be moved and merged with other images and text.

The GRAPHCON block receives graphical objects from GRAM and performers the appropriate

graphical manipulation. The resulting data is transfers to the display interface (PDI).

GRAPHCON can receive images from the camera data interface (CDI) and send them to the PDI

automatically.

GRAPHCON performs conversion from YUV to RGB and can scale (zoom) still or video images.

D. Programmable Display Interface (PDI) Block

The programmable display interface (PDI) is designed to interface both parallel and serial display

modules. The display data is transferred from the 32 word FIFO on GAMCON to the display module

via the PDI block. The PDI block is built around a micro controller and executes 16-bit instruction

words to individually control the I/O ports. It has a 128 byte program memory, programmable by the

CPU, which can store up to 64 instructions.

Page 46

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 47 -

The CPU transfers all set-up and control data to the display. Data is transferred to PDI as 32- bit

words, which in turn writes 8-bit data to the display. The programmable PDI block is configured at the

software build stage, to support either parallel interface such as PPI or serial interface such as SSI or

I2C.

E. Camera Data Interface (CDI) Block

The camera data interface (CDI) block is designed to support a range of still image camera modules.

An 8-bit parallel bus supports data transfer from the camera module to the CDI.

The pixel clock is an output clock from the camera module to the CDI and qualifies the data on the

parallel bus. One byte of data is captured on each rising edge of the pixel clock. CDI allows the pixel

clock to be in the range of 100 kHz to 16 MHz.

The horizontal synchronization line is an input from the camera module and defines one scanline of

image data. The horizontal synchronization line can be programmed to be active high or low. The

vertical synchronization line is an input from the camera module and defines one image frame (image

height) of data. The vertical synchronization line can be programmed to be active high or low.

The frame rate can be adjusted by skipping frames and various interrupts are used to inform the

application CPU regarding the progress of incoming images and potential errors. The normal data

format on the data bus is YUV 4:2:2 (raw binary image data) according to the CCIR-656 standard. A

function within the CDI can be programmed to reorder the YUV parameters as they pass through the

CDI. In addition, the CDI is able to detect the end of an image and perform some truncation as well as

overflow conditions. There is nothing preventing the use of other data types such as JPEG or RGB (as

long as the timing is followed), but only YUV data can be sent to the display.

Camera images can also be sent to a DMA channel to store the image in external memory.

The I2C interface and GPIO are part of the interface to the camera module, but they are not part of the

CDI block. The I2C is used to set-up and control the camera module.

The camera module I2C lines must go high impedance when the supply is removed from the camera.

The I2C commands needed to control the camera, as well as the functional behavior of the module,

are also different for each implementation.

The ON-signal (GPIO) is used to power-on the camera from Standby or Off mode (implementation

dependent). This signal must be held low when the mobile equipment is powered down and during the

mobile equipment reset period. The GPIO pin can also be an input or high impedance during mobile

equipment reset and start. In this case, it must have pull-down to ground.

The camera module reset signal is an output to the camera module.

Page 47

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 48 -

3.2.3 Camera & Camera Interface

Figure 3-2-2. Camera Interface (DB3150 and Zoran)

Figure 3-2-3. 5M Camera Connector(34Pin - Main Board)

VGA Camera 5 Mega Camera

21P

KLCMV

0

1P

LCPV

K

CI_PCLK

CI_RES_N

F20

E20

E19

CI_PCLK

CI_RES_n

CI_HSYNC

CI_VSYNC

F19

F18

CI_VSYNC

CI_HSYNC

CI_D1

CI_D0

G21

CI_D0

CI_D1

CI_D2

F21

CI_D2

CI_D3

G20

CI_D3

CI_D4

H21

CI_D4

CI_D5

G19

CI_D5

CI_D6

G22

CI_D6

CI_D7

H22

CI_D7

21M

FERHV

21K

S

VV

8P

ADIV

8N

B

DIV

9P

C

DIV

M

01

DDIV

01N

DIV

E

9N

F

DIV

N

11

GDIV

11P

HDIV

N

21

IDIV

7N

JD

IV

L

8

KDI

V

31P

DIV

L

9

L

V

DI

M

31

N

DIV

N

11M

ODIV

9M

PDIV

C

T

AR

5

I

N

EMAC M

E

FRE

A

CAM_AVDD_2.8V

CAM_VDD_1.8V

KLCM_MAC_PMM

C_PM

M

M

M

M

MM

C_PM

M

M

M

M

_PM

KLCP_MA

C

NYSH_MAC_PM

CNYSV_MAC_PMM

]0[ATAD_MAC_PMM

]1[ATAD_MAC_PM

]2[ATAD_MAC_PMM

]3[ATAD_MAC_PMM

]4[ATAD_MAC_PMM

]5[ATAD_MAC_PM

[ATAD_MAC_PMM

]6

]7[ATAD_MAC_P

]8[A

TAD_MA

]9[ATAD_MAC_PM

ATAD_MAC_PM

]01[

]11[ATAD_MAC

V8.2_FA_DDV_MA

C

9

]8[ATAD_MAC_PMM

_MAC_PMM

]9[ATAD

]

MM

01[ATAD_MAC_P

]11[ATAD_MAC_PMM

]7[ATAD_MAC_PMM

[ATAD_MAC_PM

]6

M

C_P

]5[ATAD_MA

MM

[ATAD_MAC_PMM

]4

D_MAC_PMM

]3[ATA

C_PM

]2[ATAD_MA

M

]1[ATAD_MAC_PMM

C_P

]0[ATAD_MA

MM

NI

8

7

I

6

NI

8101EVCI

9

8

7

6

NI

9

NI

8

I

7

6

007LF

1R070E48101EVCI

RF00

1

1A_TUONI

1B_TUO

2

I

2A_TUON

2B_TUONI

3

ONI

3B_TUON

3A_TU

4

I

4B_TUO

4A_TUON

G110G2

5

107LF

RF001R070E4

1

1A_TUONI

1B_TUONI

2

I

2A_TUON

2B_TUONI

3

3A_TUONI

3B_TUONI

4

4A_TUONI

4B_TUO

G1

G2

5

10

207LF

RF001R070E48101EVCI

1

1A_TUONI

1B_TUO

2

I

2B_TUON

2A_TUON

3

3A_TUONI

3B_TUONI

4

4A_TUONI

4B_TUONI

G15G2

10

]8[ATAD_MAC_M5

]9[ATAD_MAC_M5

01[ATA

]

D_MAC_M5

11[ATAD_MAC_M

]

5

3320

7R

CM_MAC

M

KL

_PM

CP_MAC_

KL

PMM

_MAC_

]0[ATAD

M5

]1[ATAD_MAC_M5

]2[ATAD_MAC_M5

]7[ATAD_MAC_M5

]

_MAC_M5

6[ATAD

]5[ATAD_MAC_M5

]

TAD_MAC_M5

4[A

_MAC_M

]3[ATAD

5

M5

]2[ATAD_MAC_

]1[ATAD_MAC_M5

]0[ATAD_MAC_M5

]3[ATAD_MAC_M5

]4[ATAD_MAC_M5

]5[ATAD_MAC_M5

_M5

]6[ATAD_MAC

]7[ATAD_MAC_M5

]8[ATAD_MAC_M5

M5

]9[ATAD_MAC_

]01[ATAD_MAC_M5

1[A

]1

TAD_MAC_M5

01

307R

VA701

607

507

C

C

IND

IND

VA702ICVL0518100Y500FR

ICVL0518100Y500FR

107C

1.0

u

60

30

107NC

1

3

4

3

2

3

23

3

4

3

1

3

5

0

2

9

6

2

8

7

2

7

8

2

6

9

2

01

5

2

4

11

32

21

2

2

31

2

41

1

51

02

1

61

9

8

171

207C

u1

0

u1.

3060

01407

R

01507R

060

3

M

3060

607R

01

M

01707R

3060

M

_PM

060

3

M

30

FB700

4

07C

u1.0

306

0

VA700ICVL0518100Y500FR

C708

707C

0

u1.

3060

p01

C711

C710

C709

060

3060

p013

60

3060

01

p01

p

007C

307C

01

u

N_TESER_MAC_PMM

A

MM

DS_C2I_P

LCS_C2I_PM

NYSV_MAC_PM

C

NYSH_MAC

C

NDWP_MAC_PM

A

hgiH evitc

Page 48

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

- 49 -

A

A

Figure 3-2-5. VGA LCD FPCB Connector

V8.2_DDV_AGV

V8.

1_DDV_AGV

201

C

0

K

X

A