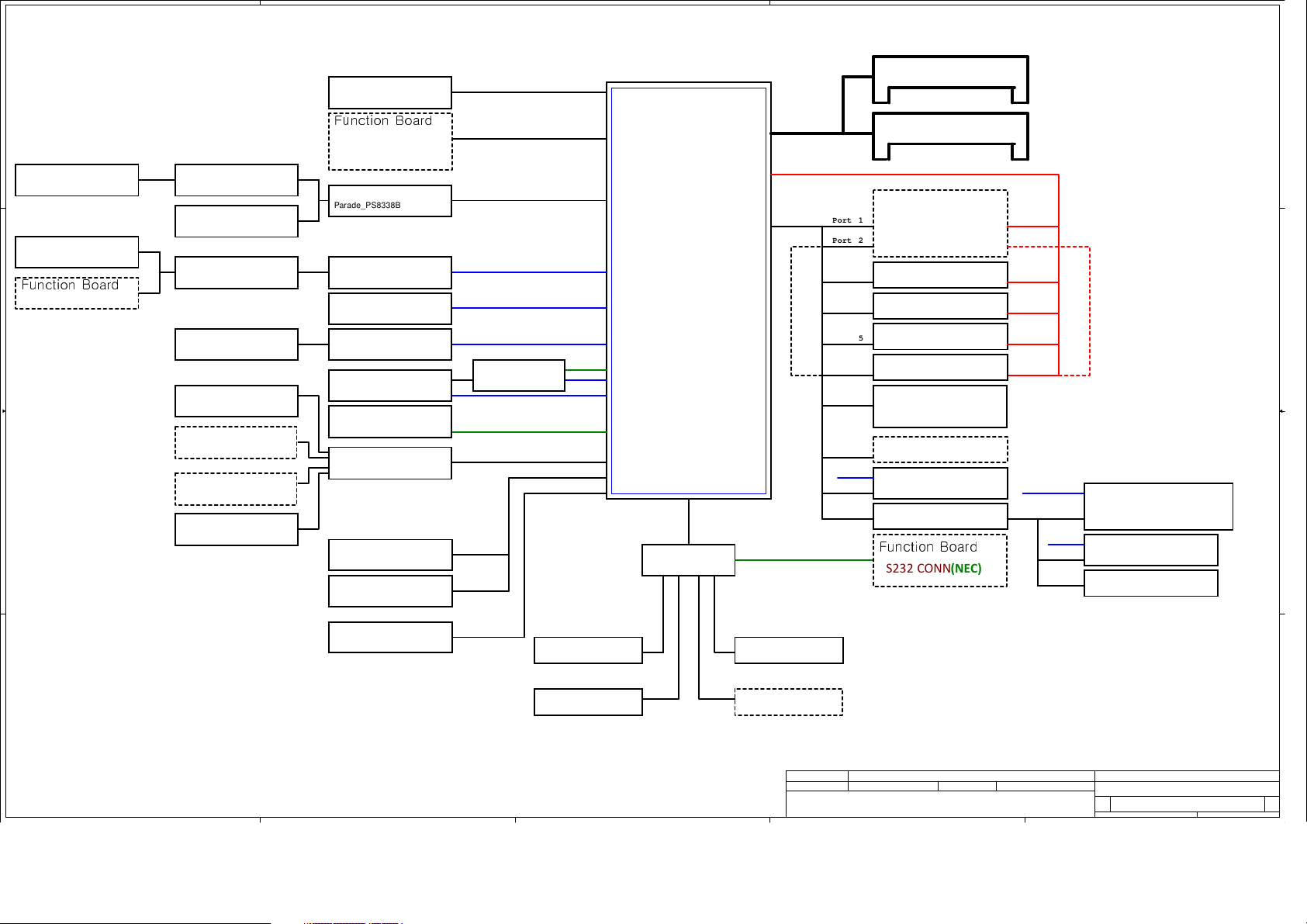

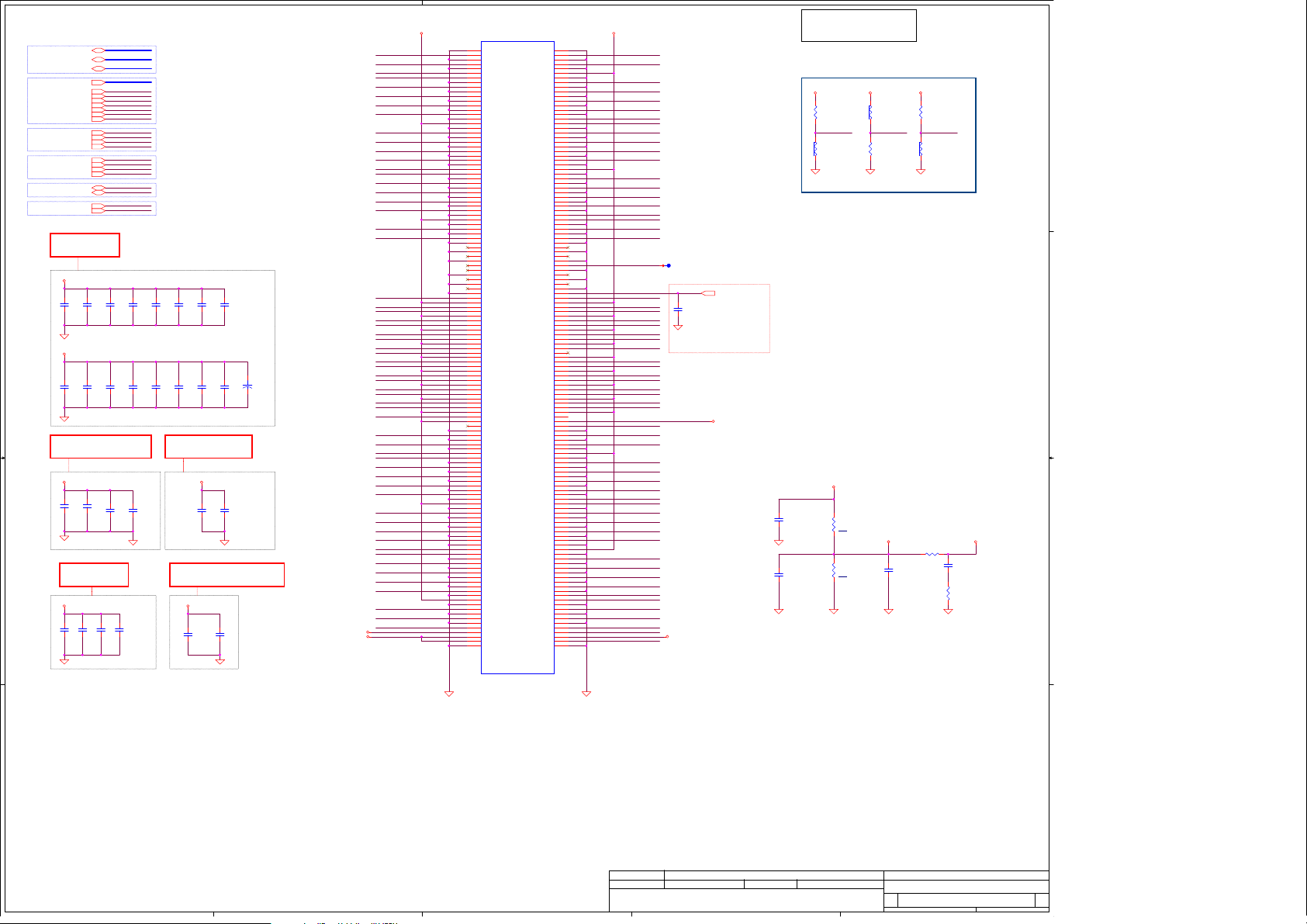

Lenovo YOGA 370 Schematic

1

2

3

4

5

Model Name : CILL1 (Lenovo)

A A

CILL2 (NEC)

File Name : LA-C422P

B B

Compal Confidential

Lin-2 M/B Schematics Document

Intel Kabylake U Processor with DDR4

C C

Rev. 1.0

D D

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET I NFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPTAS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE I NFORMATION IT CONTAINS

DEPARTMENT EXCEPTAS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE I NFORMATION IT CONTAINS

DEPARTMENT EXCEPTAS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE I NFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2016/03/21 2017/03/01

2016/03/21 2017/03/01

2016/03/21 2017/03/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Cover_Page

Cover_Page

Cover_Page

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

LA-C422P

LA-C422P

LA-C422P

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

5

1 58Tuesday, November 15, 2016

1 58Tuesday, November 15, 2016

1 58Tuesday, November 15, 2016

1.0

1.0

1.0

A

www.schematic-x.blogspot.com

B

C

D

E

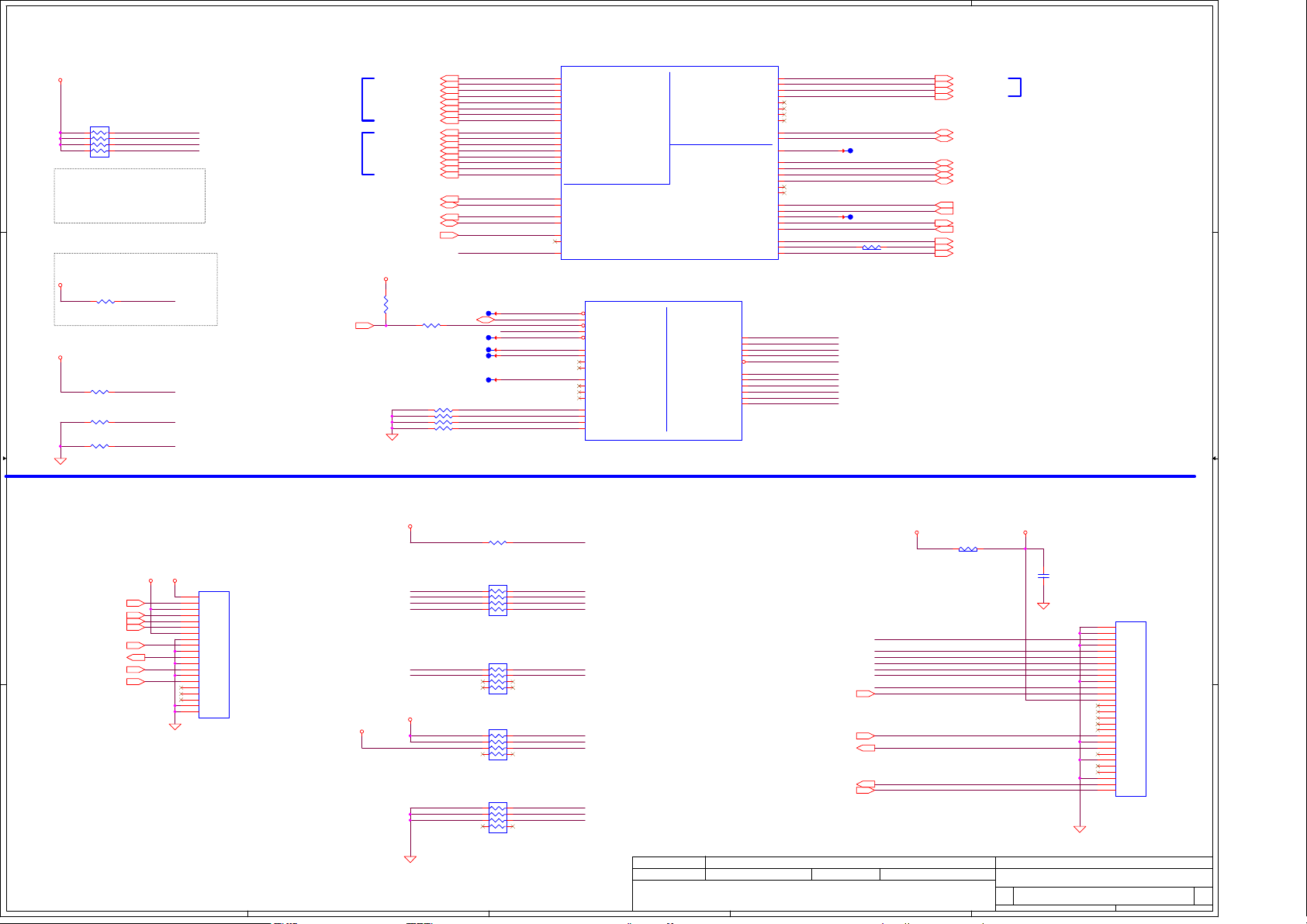

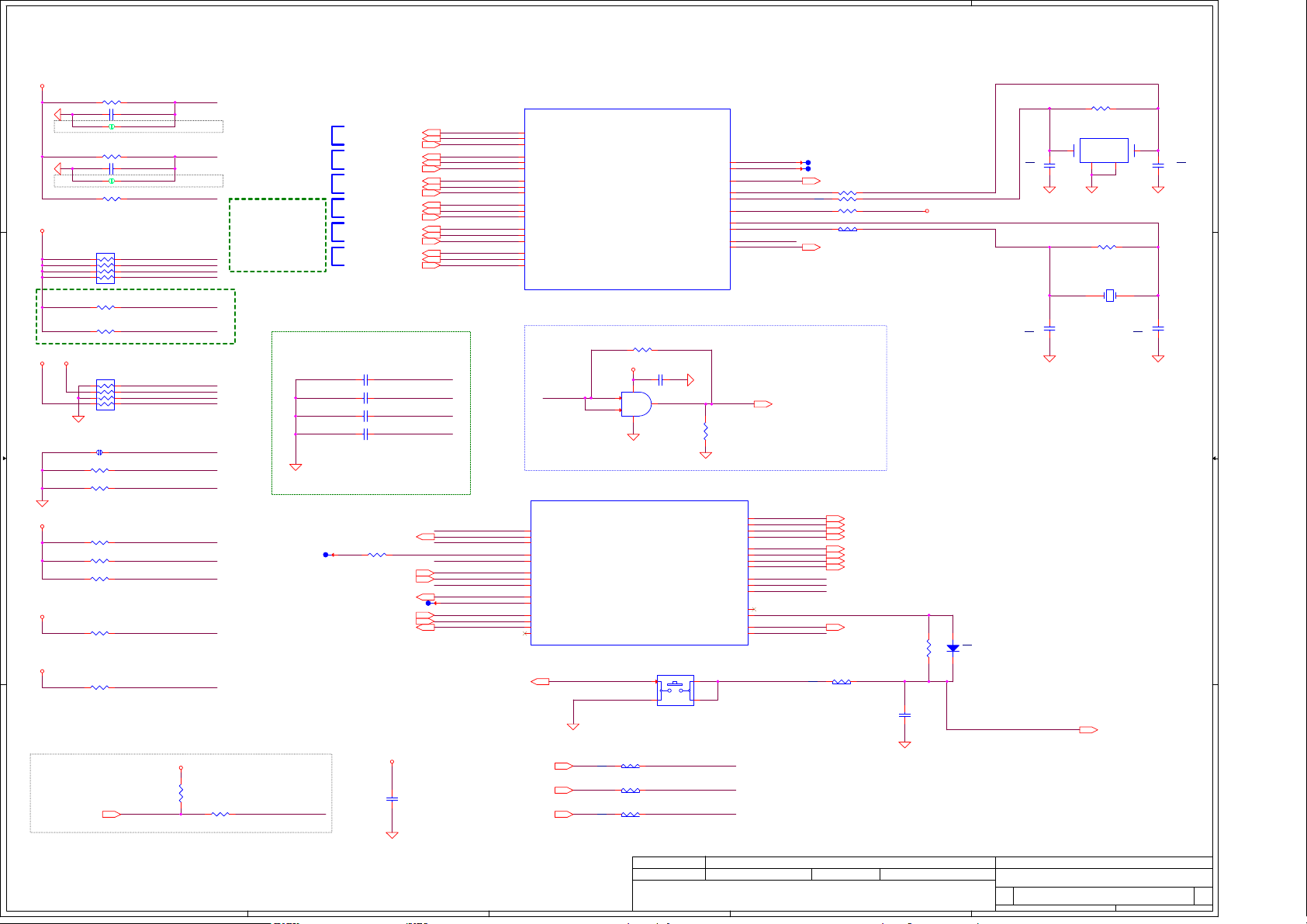

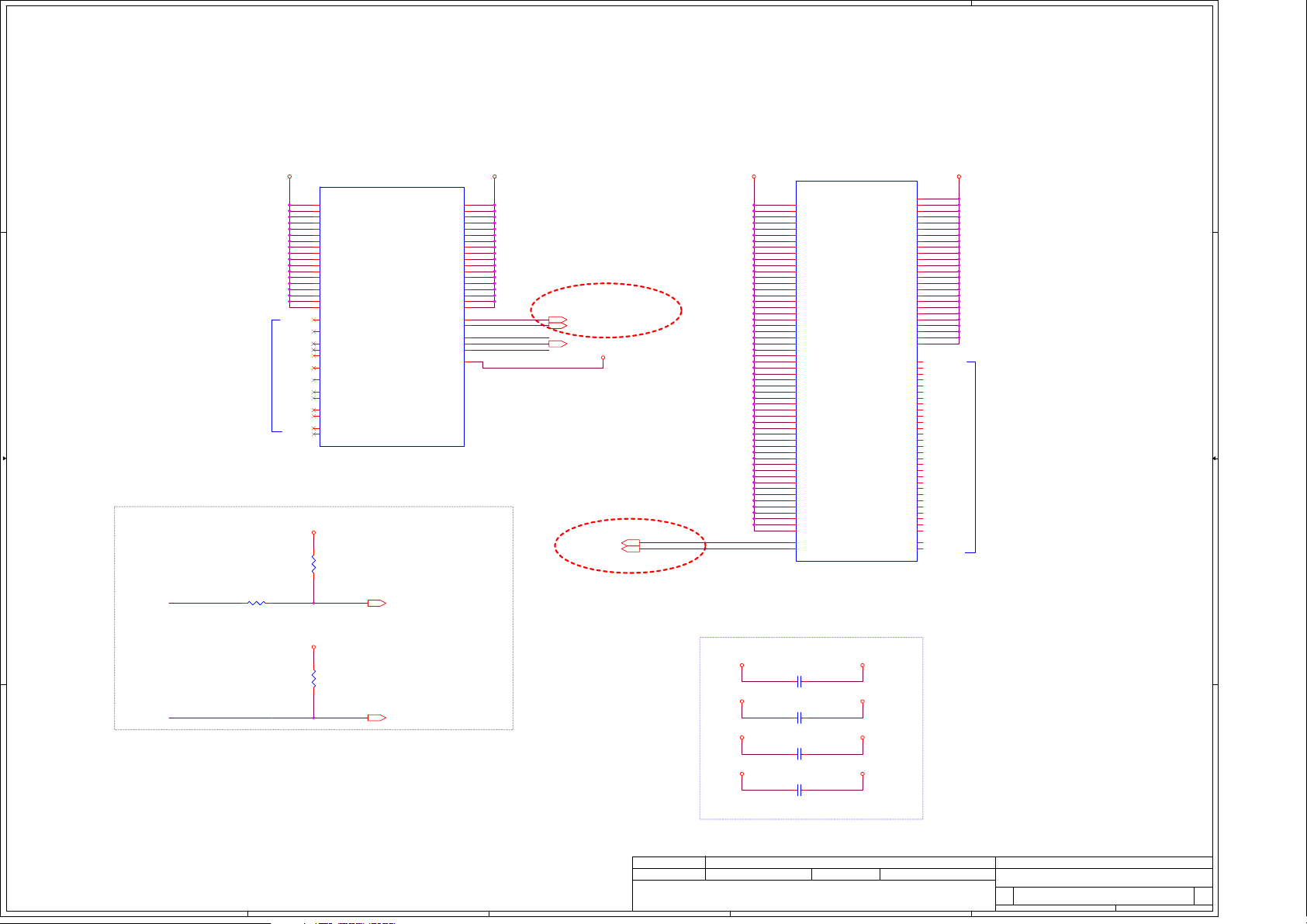

A-ch DDR4-SO-DIMM X1

P.32

eDP

DDI 1

DDI 2

PCIE3

PCIE9

PCIE2

SATA0

PCIE5

PCIE6

SATA1

HD Audio

SPI

I2C

KabyLake U

+

KabyLake PCH-LP

ULT (15W)

BGA

P.5~P .16

LPC BUS

EC

nuvoton NPCE388N

P.45

Memory Bus

DDR4 2133MHz (2.5V)

USB 3.0

USB 2.0

Port 1

Port 2

Port 3

Port 4

Port 5

Port 2 Port 2

Port 6

Port 7

Port 8

Port 10

B-ch DDR4-SO-DIMM X1

USB Board

USB 3.0 CONN

USB 3.0 CONN

USB 3.0 CONN

USB 3.0 CONN

USB 3.0 CONN (AOU)

Docking (Lenovo)

FPR

NFC (FeliCa)

CAM Module

PCIE4

M.2 WLAN / BT

USB 2.0 HUB

Genesys_GL850G

Function Board

RS232 CONN(NEC)

1 1

eDP CONN

P.19

Function Board

mDP CONN (Lenovo)

HDMI CONN (NEC)

VGA CONN

Docking

(Lenovo)

P.47

Function Board

RJ45 CONN

2 2

P.42

DP to VGA

NXP_PTN3355

Docking

LAN Switch

Pericom_PI3L720ZHEX

(Lenovo)

P.21P.22

P.47

P.23

(NEC)

P.27

DP

DP

DeMux

Parade_PS8338 B

LAN

Intel_Jacksonville

Card Reader

O2_BH611FJ1LN

PCI Bridge

O2_OZ600

HDD CONN

2 Channel Speaker

P.39

SATA Express

ODD CONN

CAM Module

DMIC *2

P.19

Audio Codec

ALC3245

Audio Board

3 3

Docking

Combo Jack

P.43

(Lenovo)

P.47

I2S

SPI ROM

16M

TPM

Nuvoton_NP CT650LA0YX

P.42

P.20

P.23

.24

P

(NEC)PCMCIA CONN

P.26

DMUX

P.32

P.37

P.38

P.41

PCIE/SATA

P.7

(NEC)

P.42

P.33

P.34

P.35

P.47

(Lenovo)

(NEC)

P.36

P.19

P.28

(Lenovo)

P.36

P.42

P.17

P.18

Port 1

Port 2

Port 3

Port 4

Port 5

PCIE11

PCIE12 /

USB 2.0

SATA2

M.2 WWAN/Optane/SSD

PCIE10

ExpressCard

Smart Card

(Lenovo)

P.25

(Lenovo)

P.36

P.29

Accelerometer

Kionix_KX023-1025

4 4

A

P.37

B

Click Pad

Int.KBD

P.40

P.40

C

Thermal Sensor

Fintek F75303M

Lid Board

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

P.40

P.19

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

2016/03/21 2017/03/01

2016/03/21 2017/03/01

2016/03/21 2017/03/01

D

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Block_Diagram

Block_Diagram

Block_Diagram

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

LA-C422P

LA-C422P

LA-C422P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

2 58Tuesday, November 15, 2016

2 58Tuesday, November 15, 2016

2 58Tuesday, November 15, 2016

1.0

1.0

1.0

5

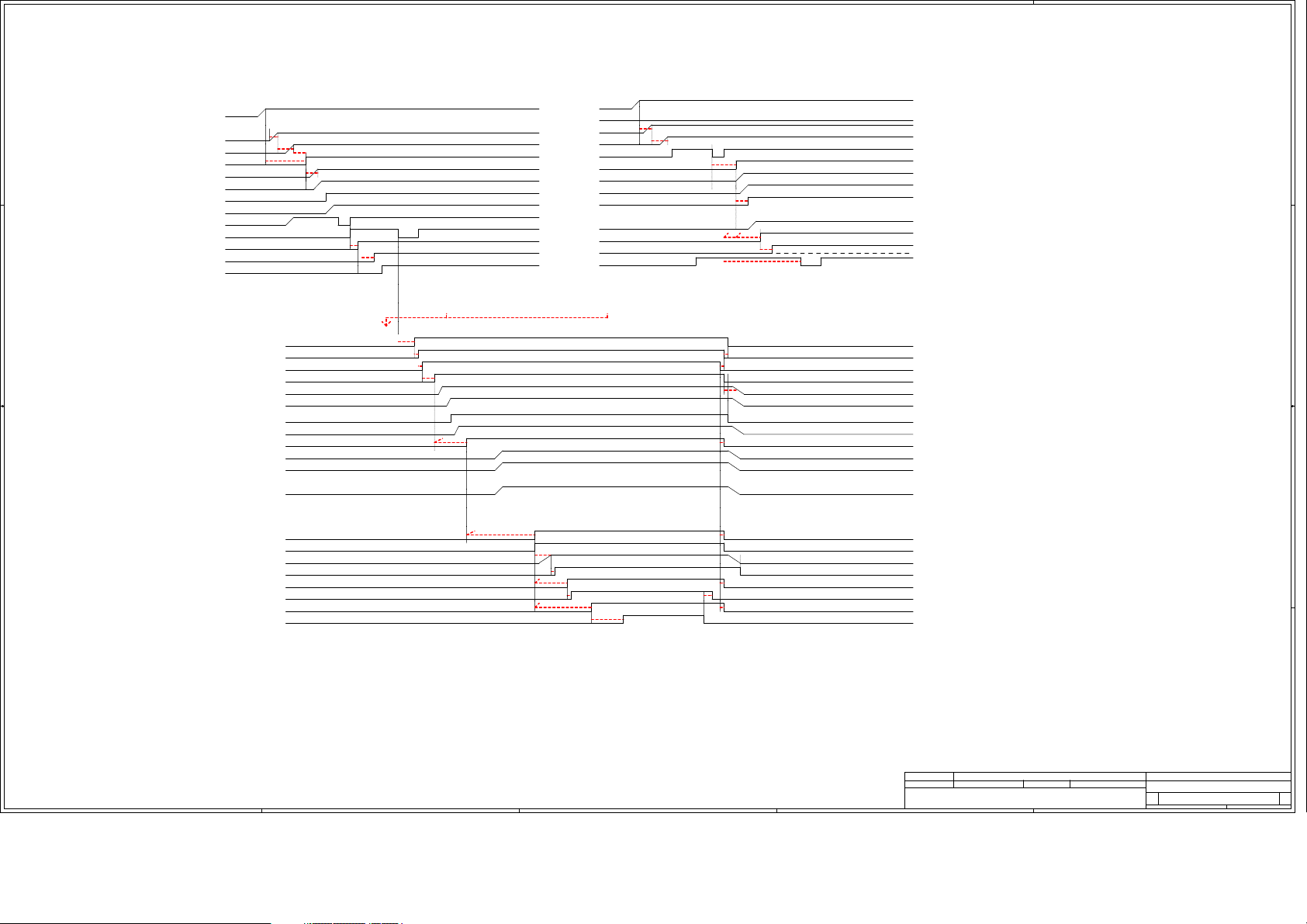

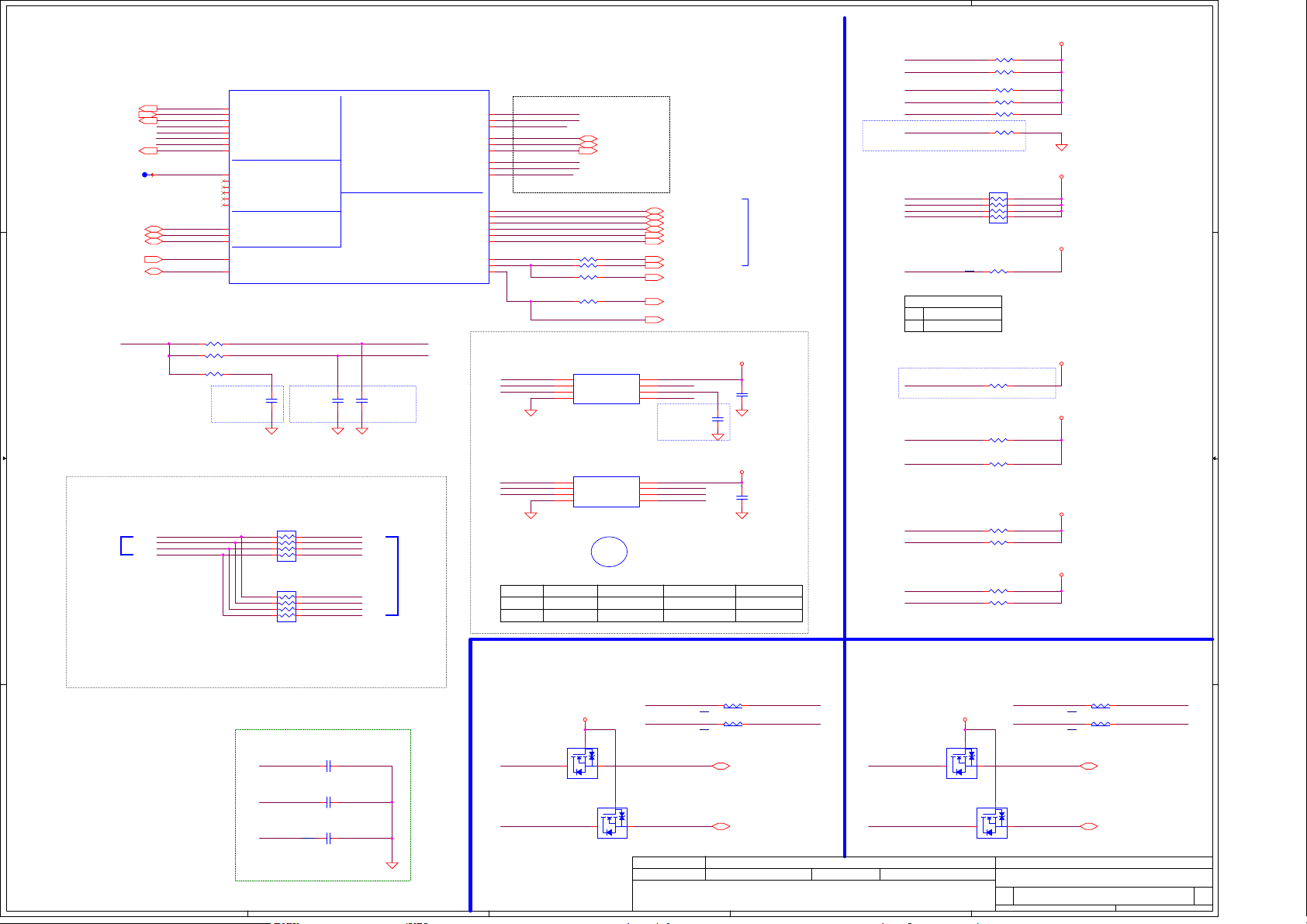

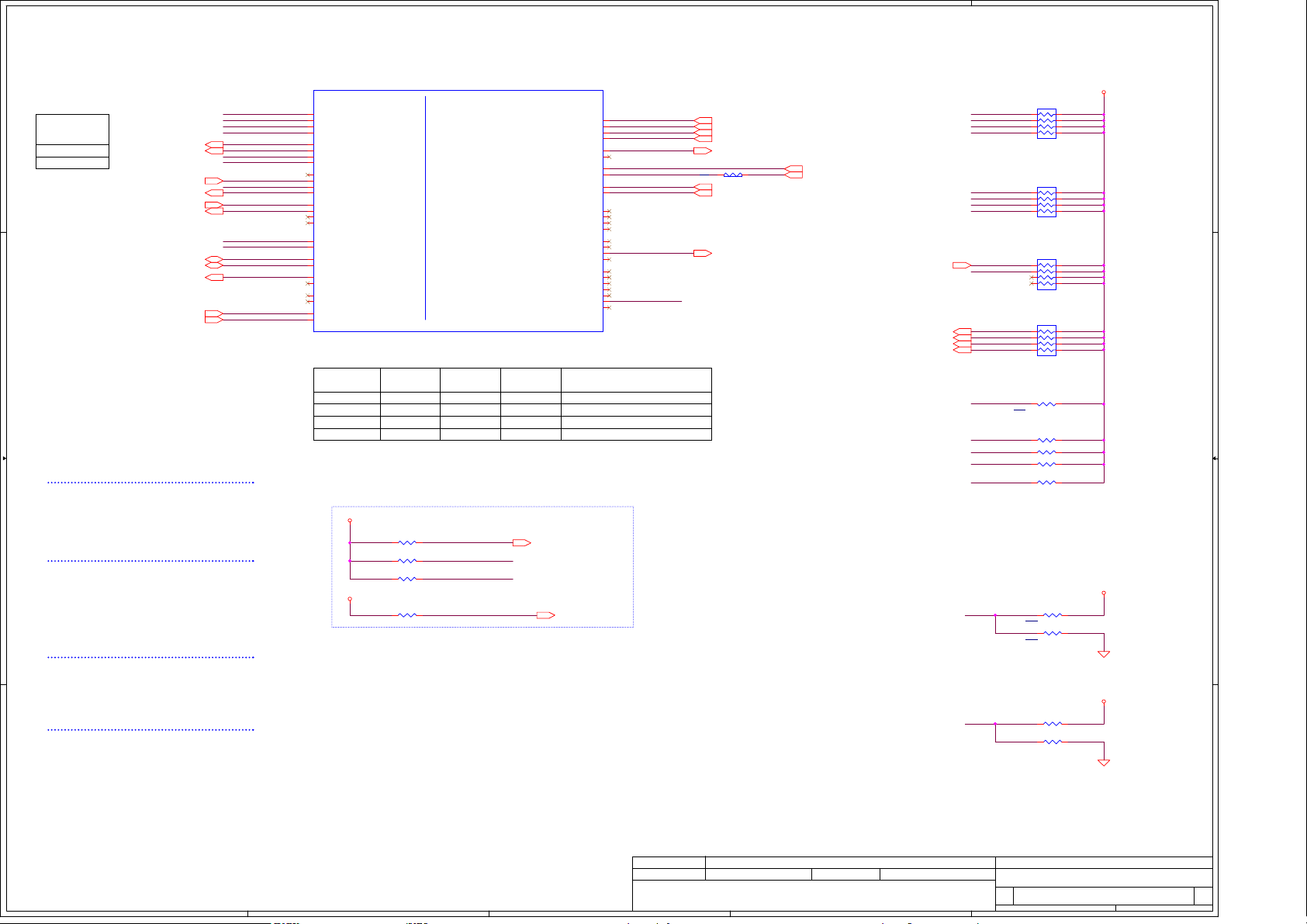

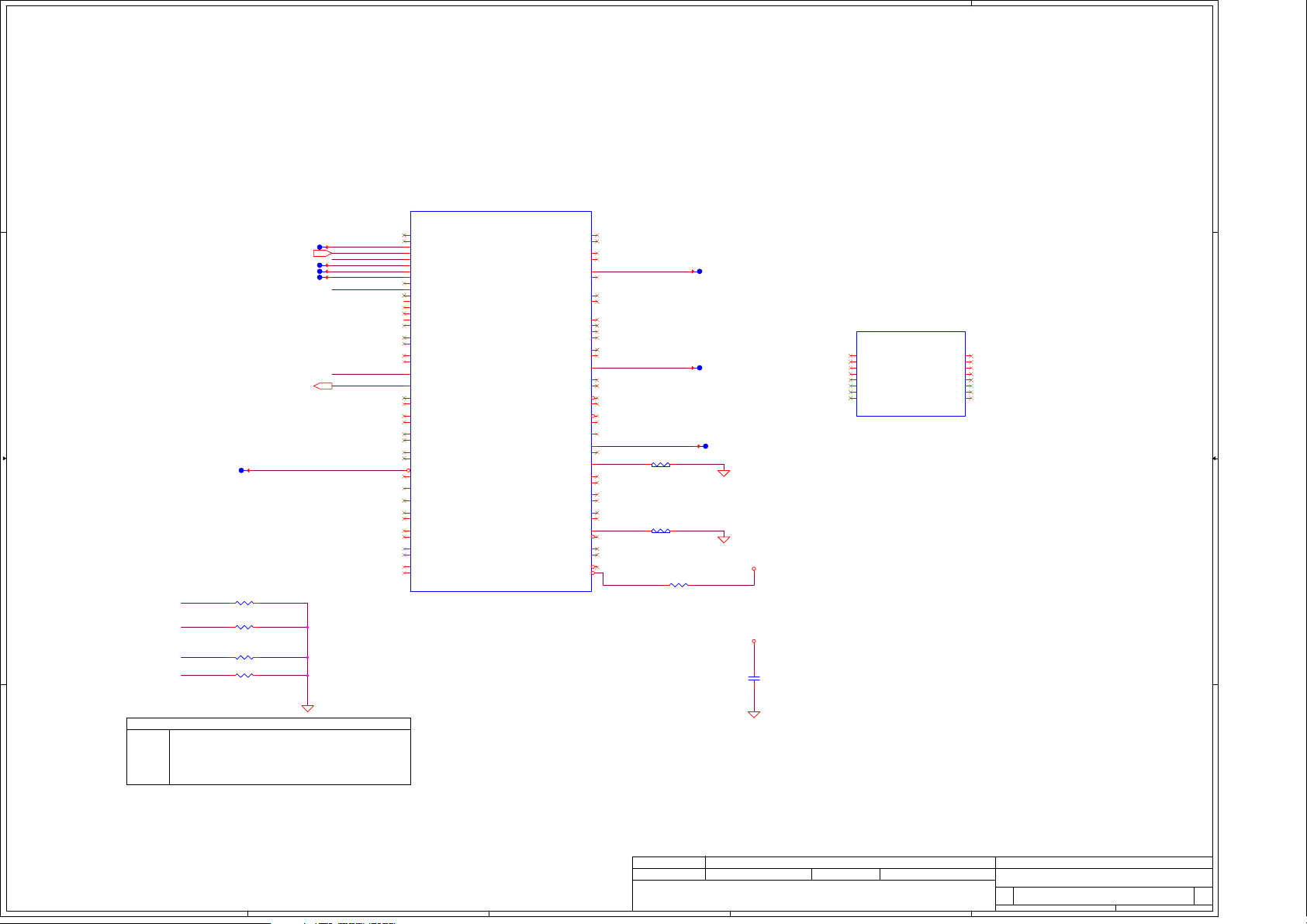

[CILL1 PWR Sequence_KBL-U_DDR4_Non-Deep Sx]

4

3

2

1

D D

C C

[AC Mode]

AC_IN

B+

+3VLP/+VL

EN_3V

+3VALW

+1.0V_PRIM

PCH_PWR_EN

+1.8V_PRIM

ON/OFFBTN#

PBTN_ OUT#

EC_RSMRST#

SUSPWRDNACK

AC_PRES ENT

moniter AC_I N (51_ON)

Moniter ON/OFFBTN# rising e dge

20ms

PM_SLP_ S5#

PM_SLP_ S4#

PM_SLP_ S3#

SYSON

+2.5V_VDD Q

+1.2V_VDD Q

DDR_P G_CTRL

+0.6VS_VT T

SUSP# After PM_SLP_S3# moniter SYSON rising edge.

+5VS

+3VS

Montier PBTN_OUT# falling edge.

T=20m s

[DC Mode]

BATT+

AC_PRES ENT

B+

+3VLP/+VL

ON/OFFBTN#

EN_5V/EN_3V

+5VALW/+3VALW

+1.0V_PRIM

PCH_PWR_EN

+1.8V_PRIM

EC_RSMRST#

SUSPWRDNACK

PBTN_ OUT#

T=10m s

Moniter ON/OFFBTN#

T=10m s

oniter ON/OFFBTN# and EN_3/5V both of ri sgin edge

M

T=110m s

20ms

immediately, After PM_SLP_S4# falling e dge

immediately, After PM_SLP_S3# falling e dge

Moniter ON/OFFBTN# rising e dge

+1.5VS

B B

VCCST_PG_EC (ALL_SYS_PWRGD,non CPU code VR)

VR_ON

+VCC_CORE

VGATE

H_CPUPWRGD_R

SYS_PWROK

PLT_RST#

T=20m s

After SUSP# risign edge

immediately, VCCST_PG_PWR & VCCST_PG_EC risign edge

Vboot

T=10m s

After VCCST_PG_EC rising edgePCH_PWROK

T=99m s

After VCCST _PG_EC assertion

After CPUPWRGD/PCH_PWRGD/SYS_PWROK assertion

immediately, After SUSP# falling edge

immediately, After SUSP# falling edge

immediately, After SUSP# falling edge

A A

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRETINFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENTDIVISION OF R&D

AND TRADE SECRETINFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENTDIVISION OF R&D

AND TRADE SECRETINFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENTDIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZEDBY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZEDBY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZEDBY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENTOF COMPAL ELECTRONICS,INC.

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENTOF COMPAL ELECTRONICS,INC.

5

4

3

MAYBE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENTOF COMPAL ELECTRONICS,INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

2016/03/21 2017/03/01

2016/03/21 2017/03/01

2016/03/21 2017/03/01

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Sequence

Power Sequence

Power Sequence

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

D

D

D

LA-C422P

LA-C422P

LA-C422P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

3 58Tuesday, Novem ber 15, 2 016

3 58Tuesday, Novem ber 15, 2 016

3 58Tuesday, Novem ber 15, 2 016

1.0

1.0

1.0

1

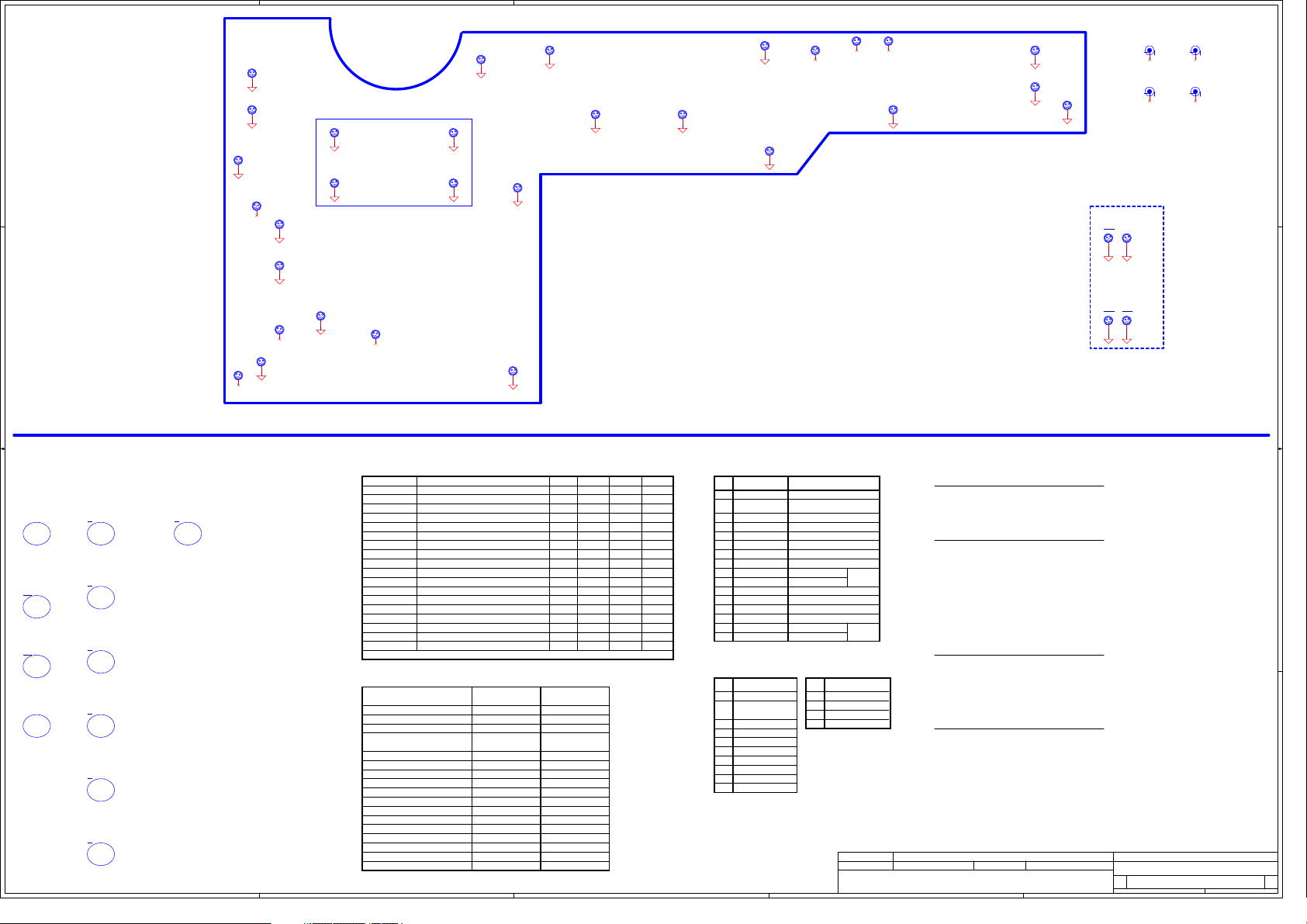

H8

H_4P4

1

Screw

H6

H30

Screw

H_2P5N

H26

H_3P0X3P5N

H_4P4

1

Screw

H_2P3

1

H31

1

H12

Screw

1

Screw

H18

1

Screw

H27

H_3P0X2P5N

1

Screw

H15

H_2P7

1

Screw

Screw

1

H17

H_3P4

1

Screw

H13

H_3P4X3P6

1

Screw

H_3P0

H_3P0

H24

H_3P0

1

Screw

A A

B B

H_2P2N

2

H5

H_2P5

1

Screw

H14

H_3P4X3P6

1

Screw

H16

H_3P6

1

Screw

H32

1

Screw

H22

H_3P0

1

Screw

H9

Screw

H19

H_2P7

1

Screw

H28

H_3P0

1

Screw

3

H29

1

Screw

H_3P2

1

H10

H_3P2

1

Screw

H2

Screw

H3

H_3P0

1

H_3P0N

1

Screw

H_3P0

4

H33

H34

H_1P5N

H_1P5N

1

1

Screw

Screw

H11

H_3P3

1

Screw

H23

H_4P4

1

Screw

H25

H_4P4

1

H1

Screw

H_3P0

1

Screw

5

FD1

1

FIDUCIAL_C40M80

FD3

1

FIDUCIAL_C40M80

FD2

@

@

1

FIDUCIAL_C40M80

FD4

@

@

1

FIDUCIAL_C40M80

Shielding Clip

Larger

CLIP1

CLIP2

HOLEA

HOLEA

@

@

1

1

Smaller

CLIP7

CLIP6

HOLEA

HOLEA

@

@

1

1

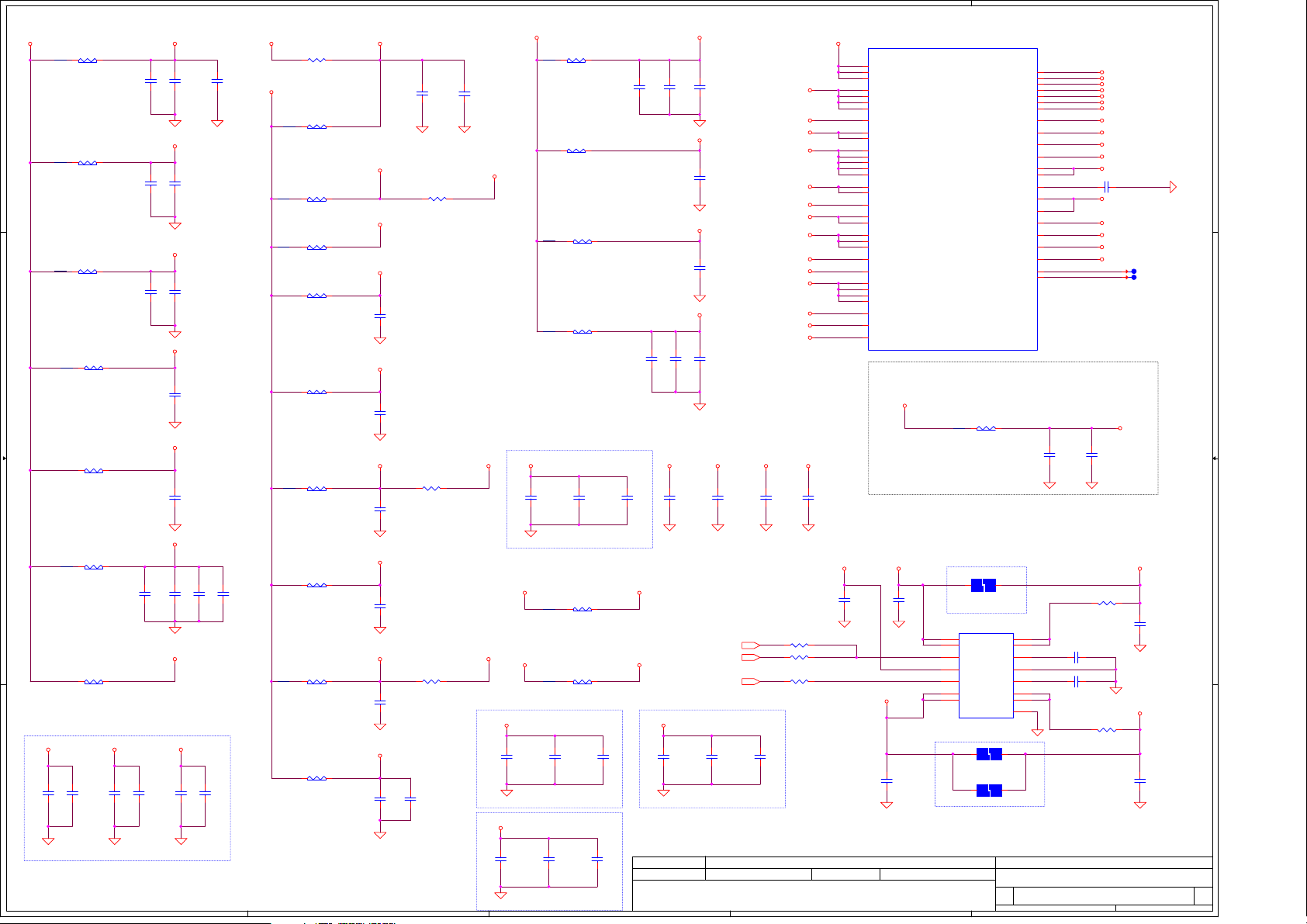

Voltage Rails

S

3 S4/S5Power Plane Descript i on

S0ix

S0

ON

PCB

ZZZ

PCB

DAZ1SS00100

C C

X4E

ZZZ1

EMC_LNV

Lenovo@

ZZZ2

EMC_NEC

NECPremium@

ZZZ3

EMC_NEC

NECBase@

D D

CPU

U1

CPU13@

SA0000ADM30

FJ8067702739934 SR34A H0 2.2G

U1

CPU14@

SA0000A38G0

FJ8067702739738 SR2ZW H0 2.4G

U1

CPU15@

SA0000A37G0

FJ8067702739739 SR2ZU H0 2.5G

U1

CPU16@

SA0000ADO30

FJ8067702739633 SR340 H0 2.6G

U1

CPU17@

SA0000A34E0

FJ8067702739740 SR2ZV H0 2.7G

U1

CPU18@

SA0000ADP30

FJ8067702739628 SR33Z H0 2.8G

1

U1

CPU19@

SA0000ADL40

FJ8067702739933 SR349 H0 1.8G

+3VL_RTC RTC power

+3VLP +19VB to +3VLP power rail

+5VALW

+3VALW System +3VALW always on power rail

+3VALW_DSW +3VALW power for PCH DSW rails

+3V_PRIM +3VALW power for PCH suspend rails

+1.8V_PRIM

1.0V_PRIM

+

+1.0V_MPHYPLL +1.0V power for PCH MODPHY rails

+2.5V DDR4 +2.5V power rail

+0.6VS_VTT

+VCC_CO RE

+1.0VS_VCCIO +1.0VS IO power rail

+VCC_GT Sliced graphics power rail

+VCC_SA System Agent power rail

+5VS System +5VS power rail

+3VS

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF

System +5VALW power rail

System +1.8V power rail

System +1.0V power rail

DDR4 +1.2V power rail+1.2V_VDDQ

DDR +0.6VS power rail for DDR terminator

Core voltage for CPU

System +3VS power rail

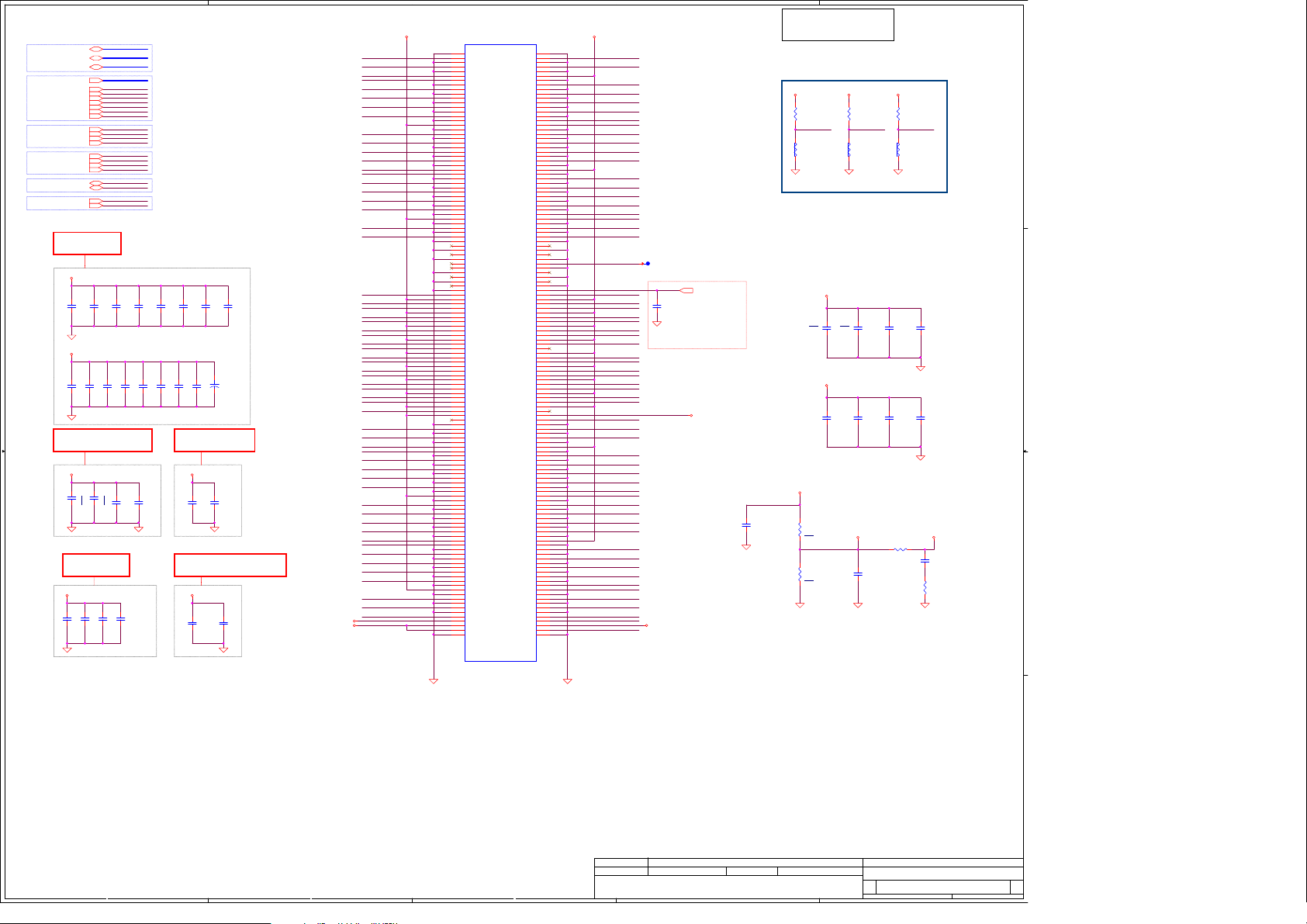

SIT BOM Structure Table

BTO Item

vPRO

non vPRO

FPR/Do cking

USB Hub/WWAN/

Express/Smart card

PCMCI A/NFC

TPM_In fineon

TPM_S T

APS_K ionix

APS_S T

Premi un-U

ESD requirement

ESD reserve

EMI requirement

EMI reserve

RF requirement

RF reserve

XDP

2

BOM Structure

M3@

NOM3 @

Lenov o@

LNVHU B@ LNV Premium-U

NEC@

TPMi @

TPMs @

APSk @

APSs @

Premi um@

ESD@

@ESD @

EMI@

@EMI @

RF@

@RF@

XDP@

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON/OFF

ON/OFF

ON

ON

OFF

ON

OFF

ON

OFF

ON

OFF

ON

ON

ON

ON

ON

ON

Remar k

vPRO sku

non vPRO sku

LNV

NEC

LNV N EC

NECLNV

LNV

NEC

NA

Premiun-U Sku

NECLNV

NA

NECLNV

NA

NECLNV

NA

NECLNV

ON

ON

ON

ON

ON

ON

ON

ON

ON/OFF

ONONON

ON

OFF

OFF

OFF

FF

O

OFF

OFF

ON/OFF

3

ON

ON

ON*

ON*

ON*

ON*

ON*

ON*

OFF

OFF

OFF

OFF

OFF

O

OFFOFFOFF

OFF

OFF

FF

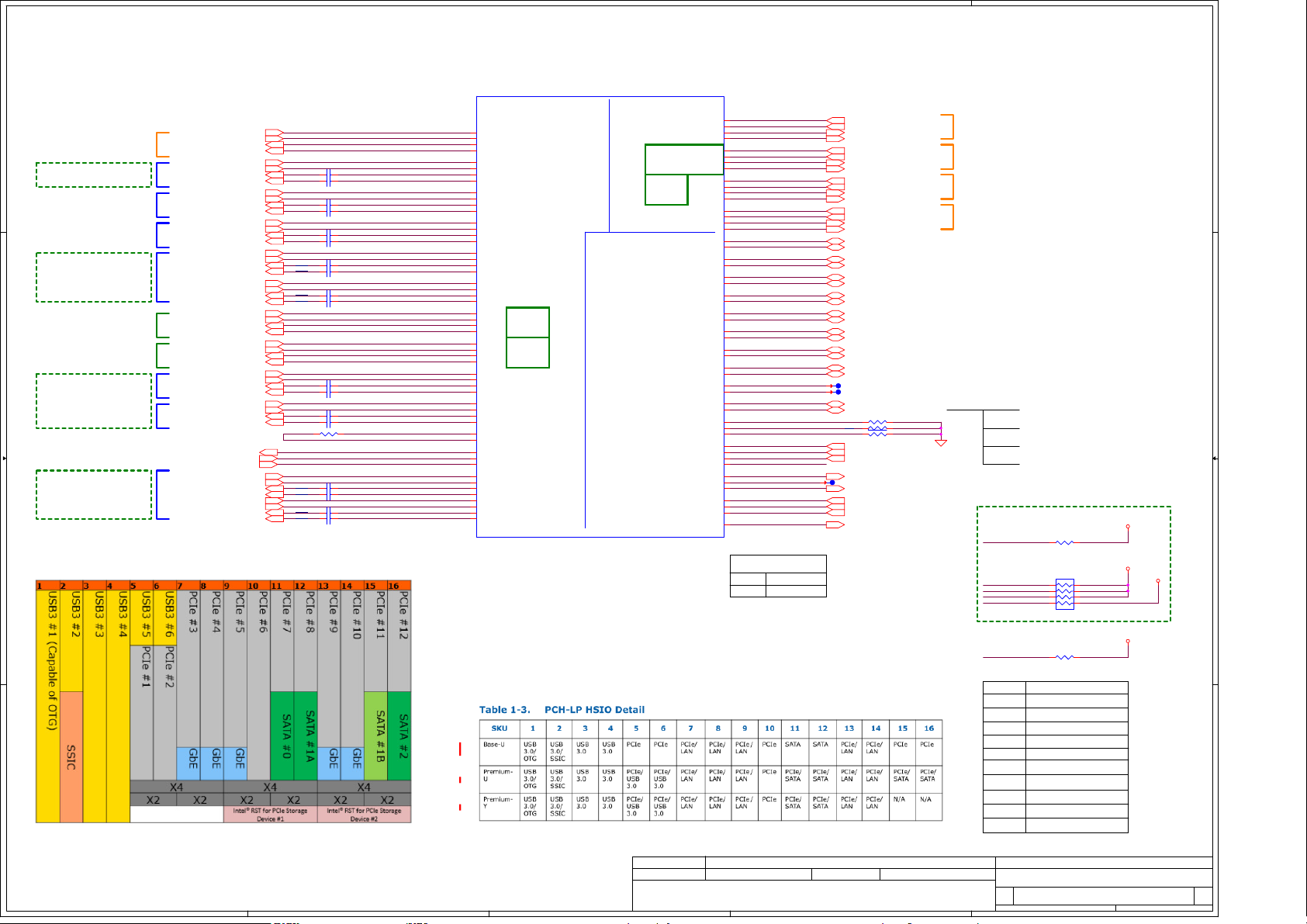

I/O mapping

Define.

USB3# 1

1

2

USB3# 2

USB3# 3

3

USB3# 4

4

USB3#5/P CIE#1

5

6

USB3#6/P CIE#2

PCIE#3/ Gbe

7

PCIE#4/ Gbe

8

PCIE#5/ Gbe

9

PCIE# 6

10

PCIE#7/S ATA#0

11

PCIE#8/S ATA#1

12

PCIE#9/ Gbe

13

PCIE#10/ Gbe

14

PCIE#11/ SATA#1

15

PCIE#12/ SATA#2

16

USB 2.0

LIN

USB3_Re ar

1

USB3_Doc king

2

USB3_Rig ht-1

USB3_Rig ht-2

3

USB3_Rig ht-3

4

USB3_Le ft

5

FPR

6

CAM

7

BT

8

X

9

USB 2.0 HUB

10

LIN-2

USB3#1_R ear

USB3#2_D ocking

USB3#2_R ight-1

USB3#3_R ight-2

USB3#4_R ight-3

USB3#5_L eft

PCIE2_PCMCIA Bridge

PCIE#3_ GBE

PCIE#4_W LAN

PCIE#5_ L0

PCIE#5_ L1

SATA#0_ HDD

SATA#1_ ODD

PCIE#5_Card Reader

PCIE#6_Express Card

PCIE#11 _L1

PCIE#11_ L0/SATA #2

USB 2.0 HUB (LNV)

1

(LNV)

2

(NEC)

3

4

(LNV)

(LNV)

EC SM Bus1 address

(LNV)

(NEC)

(NEC)

M.2

2

280 SSD

Optane /

242 SSD

2

Device

Smart Battery 0001 011X b

Charger 0001 011X b

EC SM Bus2 address

Device

Thermal Sensor Fintek F75303M

Thermal Sensor ON-semi ADM1032

CPU Intel KBL-U

APS Kionix KX023-1025

APS ST LIS3DHTR

(LNV)

Address

Address

1001_101xb

0100_110xb

0011_110xb

0011_100xb

PCH SM Bus address

Device

DDR DIMM1

LIN

WWAN

(LNV)

Express Card

(LNV)

Smart Card

(LNV)

X

Security Classification Compal Secret Data

Security Classification Compal Secret Data

Security Classification Compal Secret Data

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRI ETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRI ETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRI ETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET I NFORMATION. THIS SHEET MAY NOT BE TRANSFERE D FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET I NFORMATION. THIS SHEET MAY NOT BE TRANSFERE D FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET I NFORMATION. THIS SHEET MAY NOT BE TRANSFERE D FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPALELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPALELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPALELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAYBE USED BY OR DISCLOSED T O ANYT HIRD PARTY WITHOUT PRIO R WRITTEN CONSENT O F COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED T O ANYT HIRD PARTY WITHOUT PRIO R WRITTEN CONSENT O F COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSED T O ANYT HIRD PARTY WITHOUT PRIO R WRITTEN CONSENT O F COMPAL ELECTRONICS, INC.

4

DDR DIMM2

Synaptics Inter Touch Click Pad

PCH SM Link0 address

Device

LAN Intel WGI219

Deciphered Date

Deciphered Date

2016/03/21 2017/03/01

2016/03/21 2017/03/01

2016/03/21 2017/03/01

Deciphered Date

Address

1001 000Xb

TBD TBD

Address

HEX

16H

12H

HEX

9AH

4CH

3Ch/3Dh

30h/31h

HEX

A0H/A1H

A3H/A4H1001 001Xb

HEX

C8H

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes_List

Notes_List

Notes_List

Size

Size

Size

Document N umber Rev

Document N umber Rev

Document N umber Rev

Custom

Custom

Custom

LA-C422P

LA-C422P

LA-C422P

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

4 58Tuesday, November 15, 2016

4 58Tuesday, November 15, 2016

4 58Tuesday, November 15, 2016

1.0

1.0

1.0

5

4

3

2

1

+3VS

Function Board

D D

C C

RP1

DDIP1_CTRL_CLK

1 8

DDIP1_CTRL_DATA

2 7

DDIP2_CTRLCLK

3 6

DDIP2_CTRLDATA

4 5

2.2K_0804_8P4R_5%

DDPB_CTRLDATA: Port B Detected

DDPC_CTRLDATA:

1: Port B or C is detected

0: Port B or C is not detected

Port have internal PD

COMPENSATION PU FOR eDP

+1.0VS_VCCIO

R3

CAD note:

Trace width=20 mils,Spacing=25 mil,Max length=100mils

+1.0V_VCCST

1 2

R6 1K_0402_5%

R9 100K_0402_5%

R12

1 2

100K_0402_5%

Port C Detected

EDP_COMP

24.9_0402_1%

H_THERMTRIP#

DDIP1_mDP_HDMI_HPD

12

DDIP2_HPD

12

MUX

DDC for HDMI

H_PROCHOT#[45]

DDIP1_CTRL_CLK[42]

DDIP1_CTRL_DATA[42]

DDIP2_CTRLCLK[20]

DDIP2_CTRLDATA[20]

+1.0VS_VCCSTG

12

R4

1K_0402_5%

CPU_DP1_N0[42]

CPU_DP1_P0[42]

CPU_DP1_N1[42]

CPU_DP1_P1[42]

CPU_DP1_N2[42]

CPU_DP1_P2[42]

CPU_DP1_N3[42]

CPU_DP1_P3[42]

DDIP2_0N[20]

DDIP2_0P[20]

DDIP2_1N[20]

DDIP2_1P[20]

DDIP2_2N[20]

DDIP2_2P[20]

DDIP2_3N[20]

DDIP2_3P[20]

ODD_DA#_R[10,37]

T9 TP@

H_PECI[45]

12

R5 499_0402_1%

T10 TP@

T21 TP@

T29 TP@

T13 TP@

12

R7 49.9_0402_1%

12

R8 49.9_0402_1%

12

R10 49.9_0402_1%

12

R11 49.9_0402_1%

DDIP2_0N

DDIP2_0P

DDIP2_1N

DDIP2_1P

DDIP2_2N

DDIP2_2P

DDIP2_3N

DDIP2_3P

DDIP1_CTRL_CLK

DDIP1_CTRL_DATA

DDIP2_CTRLCLK

DDIP2_CTRLDATA

ODD_DA#_R

EDP_COMP

H_PECI

H_PROCHOT#_R

H_THERMTRIP#

SOC_OCC#

XDP_BPM#0

XDP_BPM#1

SOC_GPIOE3

CPU_POPIRCOMP

PCH_OPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

U1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

K

BL-U_BGA1356

U1D

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

KBL-U_BGA1356

DDI

DISPLAY SIDEBANDS

CPU MISC

1 OF 20

4 OF 20

EDP

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

JTAGX

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

SOC_GPIOE9

L6

EC_SCI#

N9

EDP_HPD

L10

R12

EDP_BKCTL

R11

U13

XDP_TCK0

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

PCH_TRST#

JTAGX

1 2

R2 0_0402_5%@

EDP_TXN0 [19]

EDP_TXP0 [19]

EDP_TXN1 [19]

EDP_TXP1 [19]

EDP_AUXN [19]

T5TP@

T8TP@

EDP_AUXP [19]

DDI1_AUXN [42]

DDI1_AUXP [42]

DDIP2_AUXN [20]

DDIP2_AUXP [20]

DDIP1_mDP_HDMI_HPD [42]

DDIP2_HPD [20]

EC_SCI# [10,45]

EDP_HPD [19]

ENBKL [45]

INVPWM [19]

PCH_ENVDD [19]

<eDP> 2 Lane for FHD LCD

mDP or HDMI

MUX

XDP CONN

APS CONN

B B

PM_SLP_S3#[9,25,45,46]

PM_SLP_S5#[9,45]

PM_SLP_S4#[9,12,45,46,52]

PM_SLP_A#[9,28,45,54]

SOC_RTCRST#[9]

PBTN_OUT#[9,45]

SYS_RESET#[9]

PM_SLP_S0#[9]

A A

+3V_PRIM+3VALW

JAPS1

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

GND

20

GND

ACES_50506-01841-P01

ME@

+1.0V_VCCST

+1.0V_XDP

+1.0VS_VCCSTG

JTAGX

PCH_TCK

PCH_TMS

PCH_TDI

PCH_TRST#

PCH_TDO

@

1 2

XDP@

RPC1

1 8

2 7

3 6

4 5

0_0804_8P4R_5%

XDP@

RPC2

1 8

2 7

3 6

4 5

0_0804_8P4R_5%

XDP@

RP9

1 8

2 7

3 6

4 5

51_0804_8P4R_5%

XDP@

RP13

1 8

2 7

3 6

4 5

51_0804_8P4R_5%

R191K_0402_5%

XDP_ITP_PMODE

XDP_TCK0

XDP_TCK1

XDP_TMS

XDP_TDI

XDP_TRST#

XDP_TDO

PCH_TDI

PCH_TMS

PCH_TDO

XDP_TCK0

XDP_TRST#

PCH_TCK

+1.0V_XDP+1.0V_PRIM

1 2

R14 0_0603_5%@

XDP_TCK0

XDP_TCK1

XDP_TMS

XDP_TDI

XDP_TRST#

XDP_TDO

SYS_RESET#

XDP_ITP_PMODE[16]

EC_RSMRST#[9,45]

CFG3[16]

XDP_PRDY#[11]

XDP_PREQ#[11]

XDP_ITP_PMODE

EC_RSMRST#

CFG3

XDP_PRDY#

XDP_PREQ#

@

1

0.1U_0201_10V6K

C258

2

JXDP1

28

GND

27

GND

26

26

25

25

24

24

23

23

22

22

21

21

20

20

19

19

18

18

17

17

16

16

15

15

14

14

13

13

12

12

11

11

10

10

9

9

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

ACES_51522-02601-001

ME@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2016/03/21 2017/03/01

2016/03/21 2017/03/01

2016/03/21 2017/03/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

KBL ULT(1/12) DDI,MSIC,XDP

KBL ULT(1/12) DDI,MSIC,XDP

KBL ULT(1/12) DDI,MSIC,XDP

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

C

C

C

LA-C422P

LA-C422P

LA-C422P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

5 58Tuesday, November 15, 2016

5 58Tuesday, November 15, 2016

5 58Tuesday, November 15, 2016

1.0

1.0

1.0

5

4

3

2

1

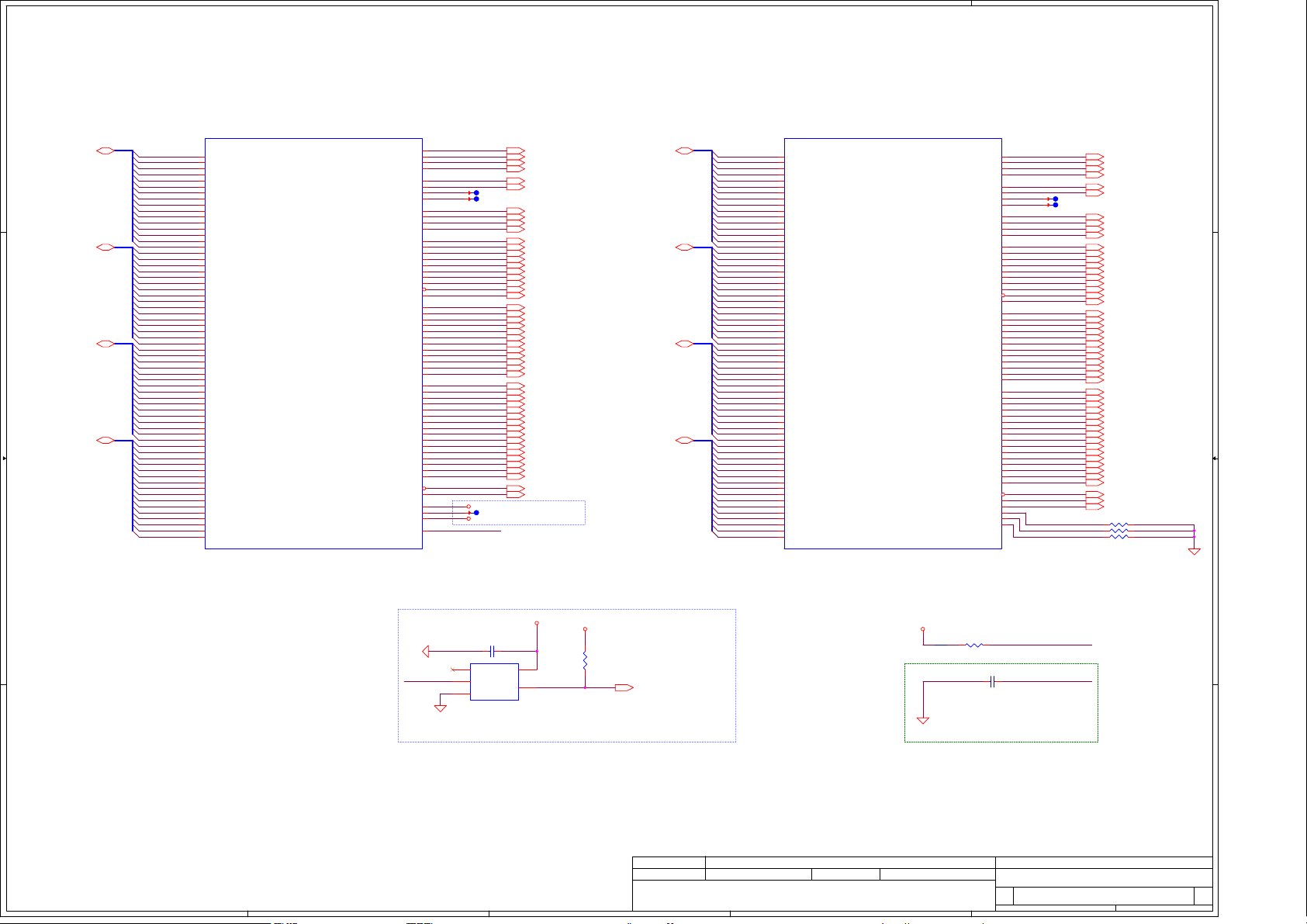

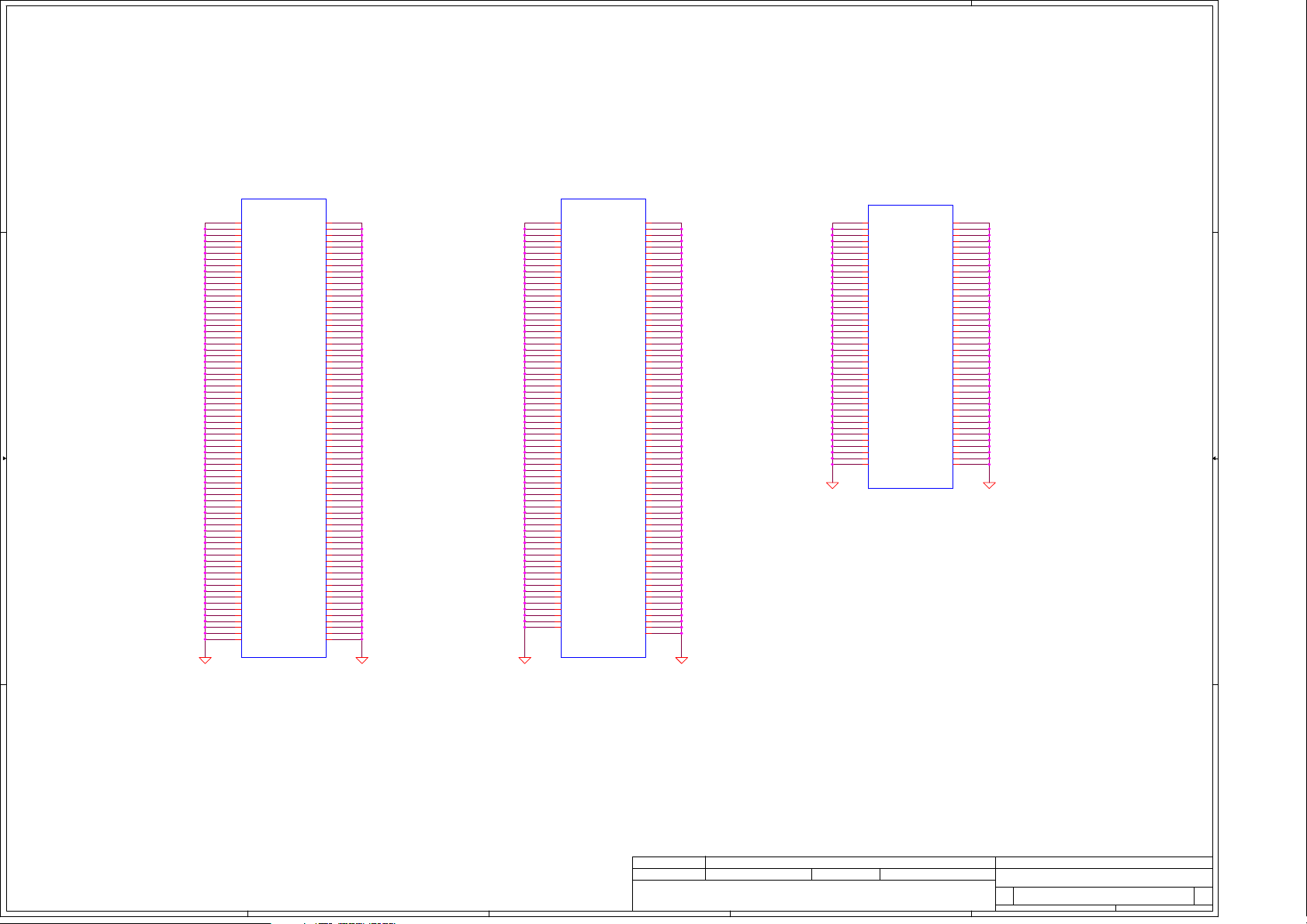

Interleaved

LIN-2

Memory

D D

DDR_A_D[0..15][17]

DDR_A_D[16..31][17]

C C

B B

DDR_A_D[32..47][17]

DDR_A_D[48..63][17]

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

U1B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

K

BL-U_BGA1356

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR_VREF_CA

DDR CH - A

2 OF 20

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_ALERT#

DDR0_PAR

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_MA5

DDR_A_MA9

DDR_A_MA6

DDR_A_MA8

DDR_A_MA7

DDR_A_BG0

DDR_A_MA12

DDR_A_MA11

DDR_A_ACT#

DDR_A_BG1

DDR_A_MA13

DDR_A_MA15

DDR_A_MA14

DDR_A_MA16

DDR_A_BA0

DDR_A_MA2

DDR_A_BA1

DDR_A_MA10

DDR_A_MA1

DDR_A_MA0

DDR_A_MA3

DDR_A_MA4

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

DDR_A_ALERT#

DDR_A_PARITY

DDR_PG_CTRL

T14TP@

T15TP@

+0.6V_VREFCA

T233TP@

+0.6V_B_VREFDQ

DDR_A_CLK#0 [17]

DDR_A_CLK0 [17]

DDR_A_CLK#1 [17]

DDR_A_CLK1 [17]

DDR_A_CKE0 [17]

DDR_A_CKE1 [17]

DDR_A_CS#0 [17]

DDR_A_CS#1 [17]

DDR_A_ODT0 [17]

DDR_A_ODT1 [17]

DDR_A_MA5 [17]

DDR_A_MA9 [17]

DDR_A_MA6 [17]

DDR_A_MA8 [17]

DDR_A_MA7 [17]

DDR_A_BG0 [17]

DDR_A_MA12 [17]

DDR_A_MA11 [17]

DDR_A_ACT# [ 17]

DDR_A_BG1 [17]

DDR_A_MA13 [17]

DDR_A_MA15 [17]

DDR_A_MA14 [17]

DDR_A_MA16 [17]

DDR_A_BA0 [17]

DDR_A_MA2 [17]

DDR_A_BA1 [17]

DDR_A_MA10 [17]

DDR_A_MA1 [17]

DDR_A_MA0 [17]

DDR_A_MA3 [17]

DDR_A_MA4 [17]

DDR_A_DQS#0 [17]

DDR_A_DQS0 [17]

DDR_A_DQS#1 [17]

DDR_A_DQS1 [17]

DDR_A_DQS#2 [17]

DDR_A_DQS2 [17]

DDR_A_DQS#3 [17]

DDR_A_DQS3 [17]

DDR_A_DQS#4 [17]

DDR_A_DQS4 [17]

DDR_A_DQS#5 [17]

DDR_A_DQS5 [17]

DDR_A_DQS#6 [17]

DDR_A_DQS6 [17]

DDR_A_DQS#7 [17]

DDR_A_DQS7 [17]

DDR_A_ALERT# [17]

DDR_A_PARITY [17] DDR_B_ALERT# [18]

DDR_B_D[0..15][18]

DDR_B_D[16..31][18]

DDR_B_D[32..47][18]

DDR_B_D[48..63][18]

Trace width/Spacing >= 20mils

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

U1C

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

K

BL-U_BGA1356

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

3 OF 20

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

DDR_B_CLK#0

DDR_B_CLK#1

DDR_B_CLK0

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_MA5

DDR_B_MA9

DDR_B_MA6

DDR_B_MA8

DDR_B_MA7

DDR_B_BG0

DDR_B_MA12

DDR_B_MA11

DDR_B_ACT#

DDR_B_BG1

DDR_B_MA13

DDR_B_MA15

DDR_B_MA14

DDR_B_MA16

DDR_B_BA0

DDR_B_MA2

DDR_B_BA1

DDR_B_MA10

DDR_B_MA1

DDR_B_MA0

DDR_B_MA3

DDR_B_MA4

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_DQS#5

DDR_B_DQS5

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_DQS#7

DDR_B_DQS7

DDR_B_ALERT#

DDR_B_PARITY

DDR_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR_B_CLK#0 [18]

DDR_B_CLK#1 [18]

DDR_B_CLK0 [18]

DDR_B_CLK1 [18]

DDR_B_CKE0 [18]

DDR_B_CKE1 [18]

T16TP@

T17TP@

DDR_B_CS#0 [18]

DDR_B_CS#1 [18]

DDR_B_ODT0 [18]

DDR_B_ODT1 [18]

DDR_B_MA5 [18]

DDR_B_MA9 [18]

DDR_B_MA6 [18]

DDR_B_MA8 [18]

DDR_B_MA7 [18]

DDR_B_BG0 [ 18]

DDR_B_MA12 [18]

DDR_B_MA11 [18]

DDR_B_ACT# [18]

DDR_B_BG1 [ 18]

DDR_B_MA13 [18]

DDR_B_MA15 [18]

DDR_B_MA14 [18]

DDR_B_MA16 [18]

DDR_B_BA0 [18]

DDR_B_MA2 [18]

DDR_B_BA1 [18]

DDR_B_MA10 [18]

DDR_B_MA1 [18]

DDR_B_MA0 [18]

DDR_B_MA3 [18]

DDR_B_MA4 [18]

DDR_B_DQS#0 [18]

DDR_B_DQS0 [18]

DDR_B_DQS#1 [18]

DDR_B_DQS1 [18]

DDR_B_DQS#2 [18]

DDR_B_DQS2 [18]

DDR_B_DQS#3 [18]

DDR_B_DQS3 [18]

DDR_B_DQS#4 [18]

DDR_B_DQS4 [18]

DDR_B_DQS#5 [18]

DDR_B_DQS5 [18]

DDR_B_DQS#6 [18]

DDR_B_DQS6 [18]

DDR_B_DQS#7 [18]

DDR_B_DQS7 [18]

DDR_B_PARITY [18]

DDR_DRAMRST# [17,18]

1 2

RC1 121_0402_1%

1 2

RC2 80.6_0402_1%

1 2

RC3 100_0402_1%

+1.2V_VDDQ

0.1U_0201_10V6K

DDR_PG_CTRL

Buffer with Open Drain Output

For VTT power control

A A

5

4

2

3

74AUP1G07GW_TSSOP5

12

NC1VCC

A

GND

CC1

UC1

5

4

Y

+5VALW

1 2

R92

10K_0402_5%

DDR_VTT_PG_CTRL [ 52]

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2016/03/21 2017/03/01

2016/03/21 2017/03/01

2016/03/21 2017/03/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

+1.2V_VDDQ

R163 470_0402_5%

100P_0402_50V8J

1 2

ESD@

DDR_DRAMRST#

DDR_DRAMRST#

12

C3

ESD request

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

KBL ULT(2/12) DDR4

KBL ULT(2/12) DDR4

KBL ULT(2/12) DDR4

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

C

C

C

LA-C422P

LA-C422P

LA-C422P

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

1.0

1.0

6 58Tuesday, November 15, 2016

6 58Tuesday, November 15, 2016

1

6 58Tuesday, November 15, 2016

1.0

5

U1E

AV2

AW3

AV3

AW2

AU4

AU3

AU2

AU1

M2

M3

J4

V1

V2

M1

G3

G2

G1

AW13

AY11

22P_0402_50V8J

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

BL-U_BGA1356

K

C5

@EMI@

33_0804_8P4R_5%

33_0804_8P4R_5% @

68P_0402_50V8J

RP3

18

27

36

45

RP4

18

27

36

45

C6

@EMI@

SOC_SPI_HOLD#_R0

SOC_SPI_WP#_R0

SOC_SPI_MISO_R0

SOC_SPI_MOSI_R0

SOC_SPI_HOLD#_R1

SOC_SPI_WP#_R1

SOC_SPI_MISO_R1

SOC_SPI_MOSI_R1

SERIRQ[26,37,45]

SOC_SPI_CLK

SOC_SPI_CLK

SOC_SPI_SO

SOC_SPI_SI

SOC_SPI_WP#

SOC_SPI_HOLD#

SOC_SPI_CS#0

SOC_SPI_CS#1

SOC_SPI_CS#2

TCH_SPI_CLK

CL_CK

CL_DAT

CL_RST#

SERIRQ

1 2

R42 33_0402_5%

1 2

R44 33_0402_5%@

1 2

R45 33_0402_5%@EMI@

SOC_SPI_HOLD#

SOC_SPI_WP#

SOC_SPI_SO

SOC_SPI_SI

SOC_SPI_CLK[41]

SOC_SPI_SO[41]

D D

C C

SOC_SPI_SI[41]

SOC_SPI_CS#2[ 41]

T20 TP@

CL_CLK[28]

CL_DAT[28]

CL_RST#[28]

KB_RST#[45]

SPI Signals

SOC side

B B

4

SMBUS, SMLINK

LPC

GPP_A14/SUS_STAT#/ESPI_RESET#

5 OF 20

SOC_SPI_CLK_R0

SOC_SPI_CLK_R1

1

1

C7

68P_0402_50V8J

@EMI@

2

2

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

EMIEMI

SOC_SMBCLK

R7

SOC_SMBDATA

R8

SOC_SMBALERT#

R10

SOC_SML0CLK

R9

SOC_SML0DATA

W2

SOC_SML0ALERT#

W1

SOC_SML1CLK

W3

SOC_SML1DATA

V3

SOC_SML1ALERT#

AM7

LPC_AD0

AY13

LPC_AD1

BA13

LPC_AD2

BB13

LPC_AD3

AY12

LPC_FRAME#

BA12

SUS_STAT#

BA11

CLKOUT_LPC0

AW9

CLKOUT_LPC1

AY9

AW11

CLKRUN#

SOC_SPI_CS#0

SOC_SPI_WP#_R0

SOC_SPI_CS#1

SOC_SPI_MISO_R1

SOC_SPI_WP#_R1

R37 22_0402_1%

R38 22_0402_1%

R590 0_0402_5%@

3

SOC_SML0CLK [23]

SOC_SML0DATA [23]

SOC_SML0ALERT# [10]

1 2

1 2

NEC@

1 2

12

R400_0402_5% @

SPI ROM ( 16MByte )

U2

1

/CS

2

DO(IO1)

3

/WP(IO2)

GND4DI(IO0)

W25Q128FVSIQ_SO8

/HOLD(IO3)

VCC

CLK

SPI ROM (Reserve)

U3

@

1

/CS

2

DO/IO1

3

/WP/IO2

4

GND

W25Q32FVSSIQ_SO8

VCC

/HOLD/IO3

CLK

DI/IO0

U3

@

SMB

(DDR, CP)

SML0

(GBE)

SML1

(EC, Thermal Sensor, APS)

LPC_AD0 [ 37,45]

LPC_AD1 [ 37,45]

LPC_AD2 [ 37,45]

LPC_AD3 [ 37,45]

LPC_FRAME# [37,45]

SUS_STAT# [37]

CLK_LPC_EC [ 45]

PCMCIA_CLK_24 [26]

LPCCLK_DEBUG_24M [37]

PCMCIA_CLKRUN# [26]

CLKRUN# [37]

8

SOC_SPI_HOLD#_R0SOC_SPI_MISO_R0

7

SOC_SPI_CLK_R0

6

SOC_SPI_MOSI_R0

5

C8

68P_0402_50V8J

@EMI@

EMI

8

SOC_SPI_HOLD#_R1

7

SOC_SPI_CLK_R1

6

SOC_SPI_MOSI_R1

5

2

SOC_SPI_SO

SOC_SPI_SI

SOC_SPI_WP#

SOC_SPI_HOLD#

SOC_SPI_CS#0

SOC_SPI_HOLD#

1 2

R346 1K_0402_1%@

1 2

R345 1K_0402_1%@

1 2

R31 1K_0402_1%@

1 2

R32 1K_0402_1%@

1 2

R33 1K_0402_1%@

1 2

R34 1K_0402_1%@

1

+3V_SPI

From WW36 MOW for SKL-U ES sample

+3VALW

RP2

SOC_SML1CLK

SOC_SML1DATA

SOC_SMBCLK

SOC_SMBDATA

LPC Bus

SOC_SMBALERT#

SMBALERT# / GPP_C2

TLS CONFIDENTIALITY

H

ENABLE

DISABLE

L

+3V_SPI

1

C4

0.1U_0201_10V6K

2

1

2

+3V_SPI

1

C9

@

0.1U_0201_10V6K

2

The R87 need s tuf f If use PCHHOT# fr o m WW52 MO W

SOC_SML1ALERT#

SERIRQ

CLKRUN#

SOC_SML0CLK

SOC_SML0DATA

@

1 8

2 7

3 6

4 5

1K_0804_8P4R_5%

1 2

R46 1K_0402_5%M3@

1 2

R87 150K_0402_1%@

+3VS_PGPPA

1 2

R41 10K_0402_5%

1 2

R348 8.2K_0402_5%

1 2

R334 499_0402_1%

1 2

R331 499_0402_1%

+3VALW

+3VALW

VCC3GBE

SPI ROM ( 8MByte )

ROM side

SPI ROM

1st

2nd

Vendor

Winbond

W25Q64FVSSIQ_SO8

16MB

SA00005VV10

8MB

SA000039A30

4MB

SA00003K820

PCH_SMB_DATA

PCH_SMB_CLK

R210 2.2K_0402_5%

R211 2.2K_0402_5%

+3VS

12

12

SOC_SMB (+3VALW) EC_SMB (+3VS)

+3VS

RF request

PCH_SMB_CLK

A A

5

EC_SMB_CK2

CLKOUT_LPC0

C10 22P_0402_50V8J

@RF@

C11 22P_0402_50V8J

@RF@

1 2

C556 33P_0402_50V8J

RF@

4

SOC_SMBDATA

NX7002BKS 2N SOT363-6

SOC_SMBCLK

2

@

Q9A

16

NX7002BKS 2N SOT363-6

Q9B

PCH_SMB (+3VS)

DIMM1/DIMM2/Clic kPad

SOC_SMBDATA PCH_SMB_DATA

SOC_SMBCLK PCH_SMB_CLK

PCH_SMB_DATA

5

PCH_SMB_CLK

43

@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

1 2

@

R47 0_0402_5%

1 2

@

R49 0_0402_5%

PCH_SMB_DATA [17,18,40]

PCH_SMB_CLK [ 17,18,40] EC_SMB_DA2 [37,40,45]

Compal Secret Data

Compal Secret Data

2016/03/21 2017/03/01

2016/03/21 2017/03/01

2016/03/21 2017/03/01

Compal Secret Data

SOC_SML1 (+3VALW)

Deciphered Date

Deciphered Date

Deciphered Date

2

SOC_SML1CLK

SOC_SML1DATA

+3VS

NX7002BKS 2N SOT363-6

Q10A

EC, Thermal Sensor, APS

SOC_SML1CLK EC_SMB_CK2

SOC_SML1DATA EC_SMB_DA2

2

16

@

5

43

NX7002BKS 2N SOT363-6

@

Q10B

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

KBL ULT(3/12) SPI,ESPI,SMB

KBL ULT(3/12) SPI,ESPI,SMB

KBL ULT(3/12) SPI,ESPI,SMB

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

C

C

C

LA-C422P

LA-C422P

LA-C422P

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

R48 0_0402_5%

R50 0_0402_5%

EC_SMB_CK2

EC_SMB_DA2

1 2

1 2

@

@

EC_SMB_CK2 [37,40,45]

1

1.0

1.0

7 58Tuesday, November 15, 2016

7 58Tuesday, November 15, 2016

7 58Tuesday, November 15, 2016

1.0

5

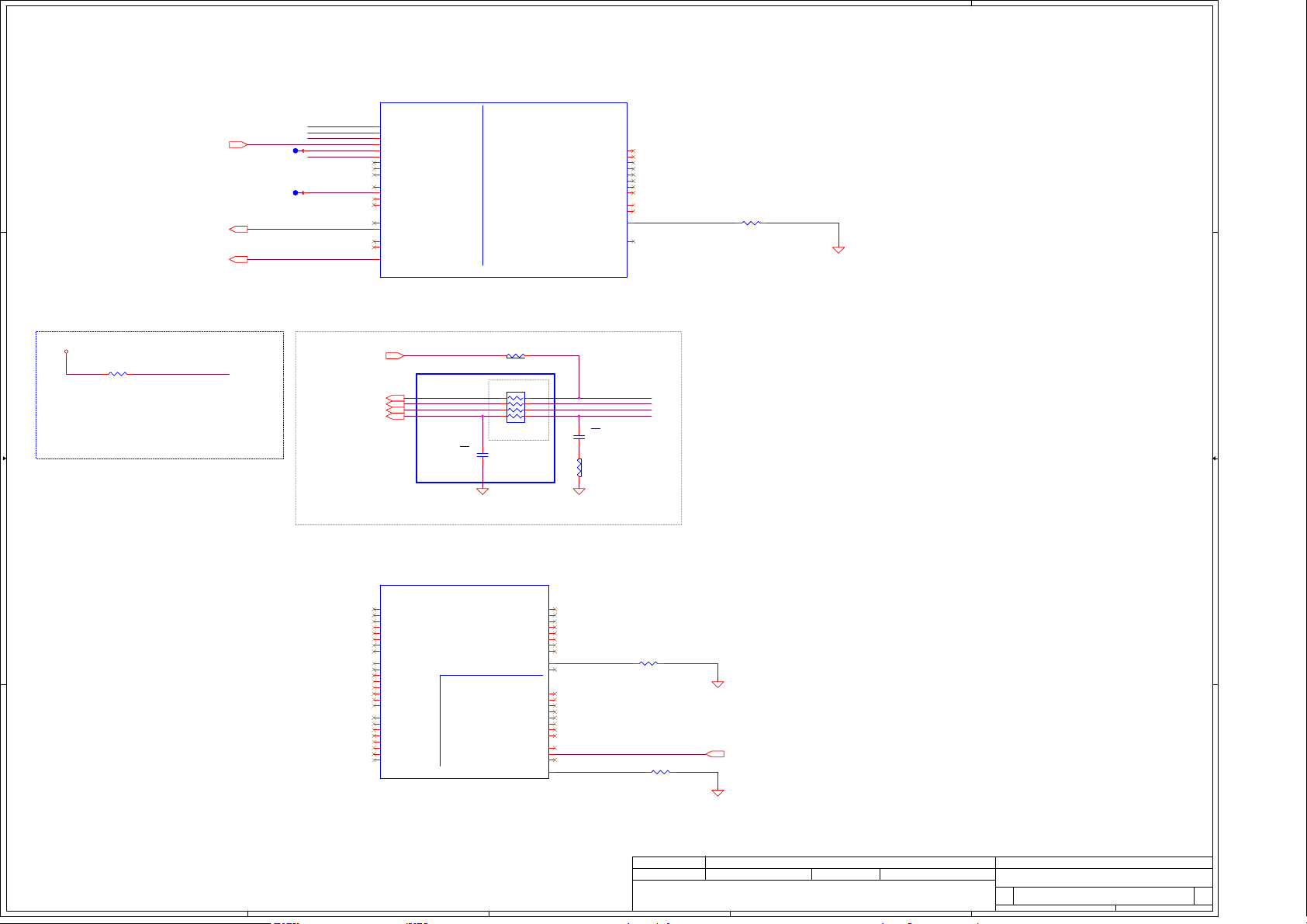

D D

HDA_SDIN0[38]

SC_OFF#[36]

SPKR[10,38]

T28 TP@

T38 TP@

HDA_SYNC

HDA_BIT_CLK

HDA_SDOUT

HDA_SDIN0

HDA_RST#

SOC_GPIOF0

SC_OFF#

4

BA22

HDA_SYNC/I2S0_SFRM

AY22

HDA_BLK/I2S0_SCLK

BB22

HDA_SDO/I2S0_TXD

BA21

HDA_SDI0/I2S0_RXD

AY21

HDA_SDI1/I2S1_RXD

AW22

HDA_RST#/I2S1_SCLK

J5

GPP_D23/I2S_MCLK

AY20

I2S1_SFRM

AW20

I2S1_TXD

AK7

GPP_F1/I2S2_SFRM

AK6

GPP_F0/I2S2_SCLK

AK9

GPP_F2/I2S2_TXD

AK10

GPP_F3/I2S2_RXD

H5

GPP_D19/DMIC_CLK0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17/DMIC_CLK1

C8

GPP_D18/DMIC_DATA1

AW5

GPP_B14/SPKR

K

BL-U_BGA1356

3

U1G

AUDIO

7 OF 20

SDIO/SDXC

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_A16/SD_1P8_SEL

SD_RCOMP

GPP_F23

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

SDIO_RCOMP

12

R52 200_0402_1%

2

1

C C

B B

A A

+3VALW

1 2

@

R54 1K_0402_5%

HDA_SDOU T

ME debug mode,this signal has a weak internal PD

Low = Disabled (Default)

*

High = Enabled [Flash Descriptor Security Overide]

HDA_SDOUT

HDA for AUDIO

ME_FLASH[45]

HDA_SDOUT_AUDIO[38]

HDA_SYNC_AUDIO[38]

HDA_RST_AUDIO#[38]

HDA_BITCLK_AUDIO[38]

A36

B36

C38

D38

C36

D36

A38

B38

C31

D31

C33

D33

A31

B31

A33

B33

A29

B29

C28

D28

A27

B27

C27

D27

KBL-U_BGA1356

U1I

CSI-2

CSI2_DN0

CSI2_DP0

CSI2_DN1

CSI2_DP1

CSI2_DN2

CSI2_DP2

CSI2_DN3

CSI2_DP3

CSI2_DN4

CSI2_DP4

CSI2_DN5

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

CSI2_DN9

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

Closed to CPU

33P_0402_50V8J

C12

RF@

9 OF 20

1 2

R53 0_0402_5%@

RP5

1 8

2 7

3 6

4 5

33_8P4R_5%

EMI@

1

2

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

EMI

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

HDA_SDOUT

HDA_SYNC

HDA_RST#

HDA_BIT_CLK

C13

1

33P_0402_50V8J

RF@

2

12

R55

0_0402_5%

@

CSI2_COMP

R58 100_0402_1%

TAMPER_SW_DTCT#

EMMC_RCOMP

12

12

R67 200_0402_1%

TAMPER_SW_DTCT# [9]

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2016/03/21 2017/03/01

2016/03/21 2017/03/01

2016/03/21 2017/03/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

KBL ULT(4/12) HDA,EMMC,SDIO

KBL ULT(4/12) HDA,EMMC,SDIO

KBL ULT(4/12) HDA,EMMC,SDIO

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

C

C

C

LA-C422P

LA-C422P

LA-C422P

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

1

8 58Tuesday, November 15, 2016

8 58Tuesday, November 15, 2016

8 58Tuesday, November 15, 2016

1.0

1.0

1.0

5

+3VL_RTC

1 2

R69 20K_0402_5%

1 2

D D

C14 1U_0402_6.3V6K

1 2

CLRP1 SHORT PADS

SOC_SRTCRST#

CLR ME

GLAN

1 2

R71 20K_0402_5%

1 2

C15 1U_0402_6.3V6K

1 2

CLRP2 SHORT PADS

1 2

R72 1M_0402_5%

SOC_RTCRST#

CLR CMOS

SM_INTRUDER#

WLAN

Card Reader

M.2_Optane

+3VS

RP6

10K_0804_8P4R_5%

Premium@

1 2

R77 10K_0402_5%

1 2

C C

+3VALW_DSW

B B

+3V_PRIM

+3VALW_DSW

R78 10K_0402_5%

+3VALW_DSW+3V_PRIM

RP7

10K_0804_8P4R_5%

CXDP1 SHORT PADS

1 2

@

R81 1K_0402_5%

R82 100K_0402_5%

1 2

R83 8.2K_0402_5%

1 2

R85 1K_0402_5%

1 2

@

R86 10K_0402_5%

1 2

@

R88 10K_0402_5%

1 2

@

R90 100K_0402_5%

12

From EC(open-drain)

A A

VCCST_PG_EC[45,46]

CLKREQ_WLAN#

18

CLKREQ_LAN#

27

CLKREQ_CR#

36

CLKREQ_PCI#

45

CLKREQ_2242#

CLKREQ_SATAex#

PCH_PWROK

18

LAN_WAKE#

27

EC_RSMRST#

36

SYS_RESET#

45

SYS_RESET#

SUSCLK

PCH_DPWROK

12

PM_BATLOW#

PCIE_WAKE#

AC_PRESENT_R

SOC_VRALERT#

PBTN_OUT#_R

+1.0V_VCCST

12

R96 60.4_0402_1%

LIN-2

R95

1K_0402_5%

1 2

PCMCIA / Express Card

SATA-EX

LIN-2

ESD request

100P_0402_50V8J

100P_0402_50V8J

100P_0402_50V8J

100P_0402_50V8J

T84 TP@

EC_VCCST_PG

CLKREQ_SATAex#[32]

ESD@

ESD@

ESD@

ESD@

R84 10K_0402_5%@

SUSPWRDNACK[45]

4

CLK_PCIE_LAN#[23]

CLK_PCIE_LAN[23]

CLKREQ_LAN#[23]

CLK_PCIE_WLAN#[28]

CLK_PCIE_WLAN[28]

CLKREQ_WLAN#[28]

CLK_PCIE_CR#[24]

CLK_PCIE_CR[24]

CLKREQ_CR#[24]

CLK_PCIE_2242#[29]

CLK_PCIE_2242[29]

CLKREQ_2242#[29]

CLK_PCIE_PCI#[26]

CLK_PCIE_PCI[ 26]

CLKREQ_PCI#[25,26]

CLK_PCIE_SATAex#[32]

CLK_PCIE_SATAex[32]

12

C20

12

C22

12

C23

12

C24

SYS_RESET#[5]

SYS_PWROK[45]

PCH_PWROK[45]

PCIE_WAKE#[25,28]

LAN_WAKE#[23]

LANPHYPC[23]

+1.0V_VCCST

C341

RF@

68P_0402_50V8J

SOC_PLTRST#

H_CPUPWRGD_R

SYS_PWROK

PCH_PWROK

12

T114 TP@

1

2

CLK_PCIE_LAN#

CLK_PCIE_LAN

CLKREQ_LAN#

CLK_PCIE_WLAN#

CLK_PCIE_WLAN

CLKREQ_WLAN#

CLK_PCIE_CR#

CLK_PCIE_CR

CLKREQ_CR#

CLK_PCIE_2242#

CLK_PCIE_2242

CLKREQ_2242#

CLK_PCIE_PCI#

CLK_PCIE_PCI

CLKREQ_PCI#

CLK_PCIE_SATAex#

CLK_PCIE_SATAex

CLKREQ_SATAex#

SOC_PLTRST#

SYS_RESET#

EC_RSMRST#

H_CPUPWRGD_R

EC_VCCST_PG

SYS_PWROK

PCH_PWROK

PCH_DPWROK

SUSPWRDNACK

SUSACK#

PCIE_WAKE#

LAN_WAKE#

LANPHYPC

TAMPER_SW_DTCT#[8]

U1J

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

K

BL-U_BGA1356

PCH PLTRST Buf f er

SOC_PLTRST#

TC7SH08FU_SSOP 5P

U1K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

K

BL-U_BGA1356

TAMPER_SW_DTCT#

AC_PRESENT[45]

PBTN_OUT#[5,45]

EC_RSMRST#[5,45]

3

CLOCK SIGNALS

10 OF 20

R79 0_0402_5%@

+3VALW

1

IN1

2

IN2

SYSTEM POWER MANAGEMENT

1 2

R89 0_0402_5%@

1 2

R91 0_0402_5%@

1 2

R94 0_0402_5%@

1 2

5

U5

P

O

G

3

11 OF 20

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

XCLK_BIASREF

C21

1 2

0.1U_0201_10V6K

4

GPP_B11/EXT_PWR_GATE#

SW1

1

2

SPVR310100_4P

Lenovo@

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

RTCX1

RTCX2

SRTCRST#

RTCRST#

12

R80

100K_0402_5%

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

GPP_B2/VRALERT#

3

4

AC_PRESENT_R

PBTN_OUT#_R

PCH_DPWROK

2

CLK_CPU_ITP#

F43

CLK_CPU_ITP

E43

BA17

SUSCLK

SOC_XTAL24_IN

E37

SOC_XTAL24_OUT

E35

XCLK_BIASREF

E42

SOC_RTCX1 SOC_RTCX1

AM18

SOC_RTCX2

AM20

SOC_SRTCRST#

AN18

AM16

PLT_RST#

PLT_RST# [23,24,25,26,28,29,32,37,41,45]

PM_SLP_S0#

AT11

PM_SLP_S3#

AP15

PM_SLP_S4#

BA16

PM_SLP_S5#

AY16

SLP_SUS#

AN15

SLP_LAN#

AW15

SLP_WLAN#

BB17

PM_SLP_A#

AN16

PBTN_OUT#_R

BA15

AC_PRESENT_R

AY15

PM_BATLOW#

AU13

AU11

SM_INTRUDER#

AP16

EXT_PWR_GATE#

AM10

SOC_VRALERT#

AM11

T85TP@

T86TP@

SUSCLK [28,29]

1 2

R605 33_0402_5%

1 2

R73 33_0402_5%

1 2

R74 2.7K_0402_1%

1 2

R75 0_0402_5%@

SOC_RTCRST# [ 5]

PM_SLP_S0# [5]

PM_SLP_S3# [5,25, 45,46]

PM_SLP_S4# [5,12, 45,46,52]

PM_SLP_S5# [5,45]

SLP_SUS# [13,53]

SLP_LAN# [12]

SLP_WLAN# [28]

PM_SLP_A# [5,28,45,54]

EXT_PWR_GATE# [13]

1 2

R62 0_0402_5%@

1000P_0402_50V7K

0_0402_5%

C119

@

SOC_XTAL24_IN_R

SOC_XTAL24_OUT_R

+1.0V_CLK5_F24NS

SOC_RTCX2_R

R595

@

1 2

2

1

D27

RB751V40_SOD-323

Lenovo@

1 2

SOC_RTCX2_RSOC_RTCRST#

5.6P_0402_50V8D

C16

C18

1

1 2

R70 1M_0402_5%

Y1

24MHZ_12PF_7V24000020

3

3

GND

4

22P_0402_50V8J

1 2

R76 10M_0402_5%

32.768KHZ_9PF_9H03280012

1

2

1

1

GND

2

Y2

12

C19

5.6P_0402_50V8D

SM_INTRUDER_D# [50]

1

C17

2

6.8P_0402_50V8C

1

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION.THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPE TENT DIVISION OF R&D

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUTPRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2016/03/21 2017/03/01

2016/03/21 2017/03/01

2016/03/21 2017/03/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

KBL ULT(5/12) CLK,GPIO

KBL ULT(5/12) CLK,GPIO

KBL ULT(5/12) CLK,GPIO

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

C

C

C

LA-C422P

LA-C422P

LA-C422P

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

1

9 58Tuesday, November 15, 2016

9 58Tuesday, November 15, 2016

9 58Tuesday, November 15, 2016

1.0

1.0

1.0

5

4

3

2

1

U1F

GSPI0_CS#

D D

HDD_I FDe t#

SEL

(PCIE)

L

H (SATA)

HDD_I/F (reserve)

PTN33 55(re serv e)

C C

WWAN_PWROFF#[29]

3G_OFF#[29]

HDD_IFDet_SOC#[32]

BT_ON[28]

EXTPWRG[47]

PWRON_DOCK#[47]

I2C_1_SDA[21]

I2C_1_SCL[21]

WWAN_RST#[29]

WWAN_CFG0[29]

WWAN_CFG1[29]

GSPI0_CLK

GSPI0_MISO

GSPI0_MOSI

WWAN_PWROFF#

3G_OFF#

DDI1_Config

GSPI1_MOSI

HDD_IFDet_SOC#

SOC_SPI_IRQ#

BT_ON

EXTPWRG

PWRON_DOCK#

I2C_0_SDA

I2C_0_SCL

I2C_1_SDA

I2C_1_SCL

WWAN_RST#

WWAN_CFG0

WWAN_CFG1

AH10

AH11

AH12

AF11

AF12

AN8

AP7

AP8

AR7

AM5

AN7

AP5

AN5

AB1

AB2

W4

AB3

AD1

AD2

AD3

AD4

U7

U6

U8

U9

AH9

LPSS ISH

GPP_B15/GSPI0_CS#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_C8/UART0_RXD

GPP_C9/UART0_TXD

GPP_C10/UART0_RTS#

GPP_C11/UART0_CTS#

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_F4/I2C2_SDA

GPP_F5/I2C2_SCL

GPP_F6/I2C3_SDA

GPP_F7/I2C3_SCL

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

BL-U_BGA1356

K

6 OF 20

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL