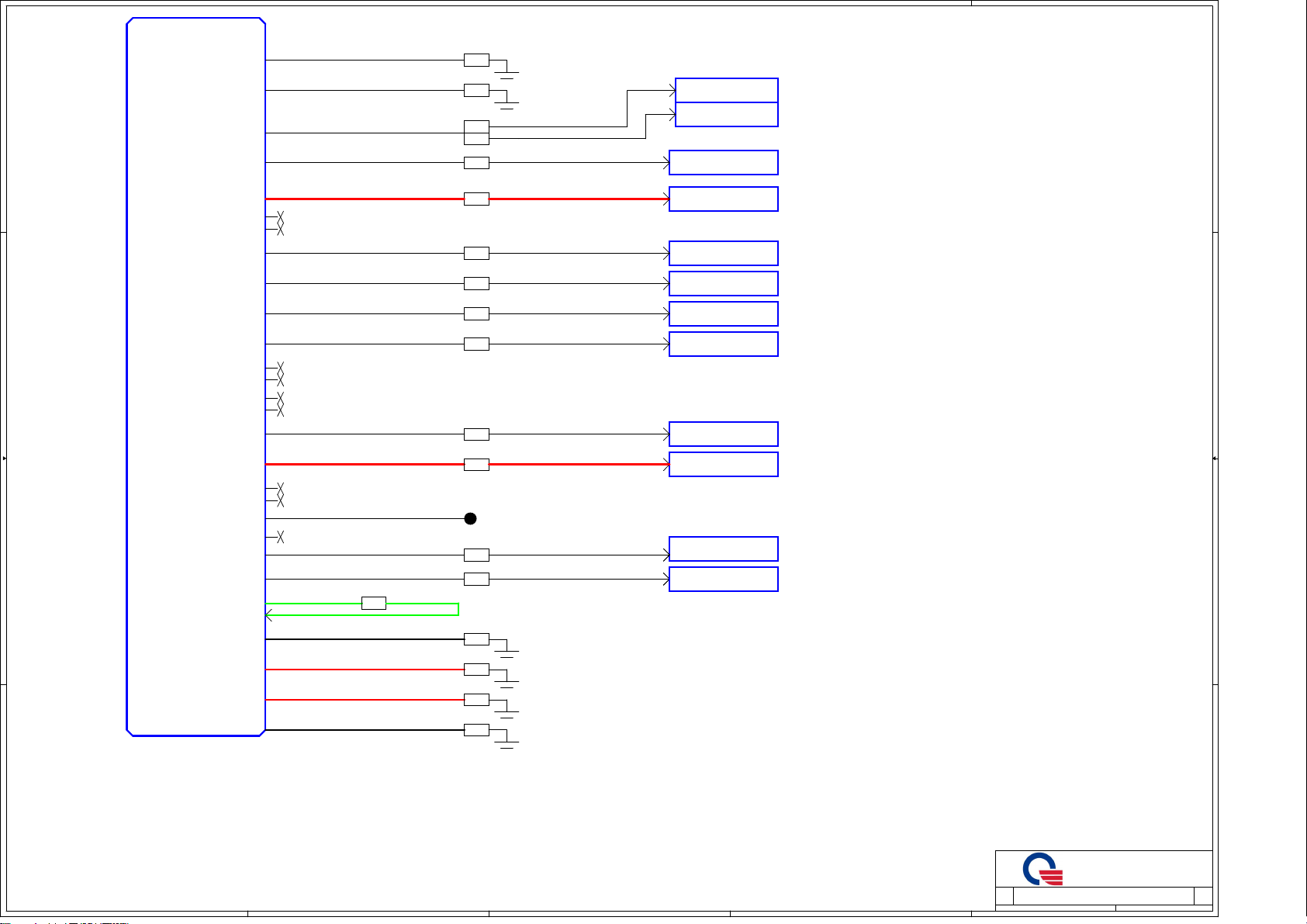

Lenovo C440 Schematic

5

4

3

2

1

SIT Change List

SIT-0427-01 15 change Q39 PIN Connect,Unmount R125 change Q39 PIN Connect for SA TA Led always light issue ,Un mount R125

SIT-0420-01 37 change JP8 PIN define

SIT-0504-01 33 change Q40 PIN Connect change Q40 PIN Connect for Wl an Led always light issue

SIT-0505-01 34/35 Mount R47/Unmou nt R341 for flash scree n issue in disc rete board

SIT-0510-01 36 ADD Q42/Mount R192 ,DEL R719

SIT-0511-01 30 add D21/D22 ADD D21/D22 FOR Current leakag e

SIT-0511-01 33 add R724/R725/R 726/Q45;Del C27 3/R361 Meet HDMI SPEC

D D

SIT-0511-01 33 add R727 /Reser ve Q44/Q43/R652 Meet VOL Comman d:reserve wlan wake up functio n

SIT-0511-01 7 un mount C4 H_PWRGD Rise ti me over SPEC

SIT-0512-01 del sense PR111/PR112/PR 133/PR156/PR170 /PR171/PR198/PR 222/PR241/PR181

SIT-0512-01 ADD C273/C711/D 25/D27/D28/C709 , Reserve D24/D 26 For ESD

16/12/15/21/20

Change USB30_SM I#_PCH from PCH GPIO24 to GPIO 1316SIT-0510-01

DEL F2/F3/C262/ C250/Q6/Q8/R365 /R364/R354/R353SIT-0512-01 33

PC82 Change to CC73301MZ00; Re serve PC254SIT-0512-01

42

Q30 change to D TC144U SIT-0516-01 36

SIT-0516-01 34 D18 Connect to EC_PWRGD

SIT-0516-01 29 Un-stuff AR76,A R77,AR78,AR79

SIT-0516-01 29 AC47/AC52 Chang e to 100uF DIP cap

SIT-0516-01 37/16 Add RN5/RN6/R35 3/R354

SIT-0516-01 ADD AR8029 vendor suggest

SIT-0516-01 29 DEL AR70/AR75

SIT-0516-01 29 AC48/AC50 Chang e to 0

SIT-0516-01 29 del AR71/AR72/A R73/AR74/AR76/A R77/AR78/AR79 vendor suggest

SIT-0516-01 29 DEL AR64/AR65 vendor suggest

SIT-0517-01 ADD D29 for ESD36

SIT-0517-01 DEL R653/R654/R 656/Q32 Cancel USB OC D etect function

SIT-0518-01 PR44 Unmount,Mo unt PR48,reserv e PR170/PQ45 for ACPI SMDDR_ VTERM fail

C C

SIT-0518-01 Reserve C250/C2 62/FB6 for USB3.0 Devi ce lost issue,c hange to 1.05V_ S336

SIT-0519-01 U31 power PIN3 /7/8 Change to USB30_+3.3VAUX For Vendor sugg est36

SIT-0611-01

SIT-0611-01

SIT-0611-01

SIT-0611-01

SIT-0611-01

SIT-0611-01

SIT-0611-01

SIT-0611-01 Power concern

B B

AC43/AC44 Chang e to 0/0603SIT-0516-01 29 vendor suggest

36

38/42

ADD PQ46/PR181/ PR171/PQ76/PR25 1SIT-0518-01 41 For 1.05V_S3 Di scharge

ADD PR133/PC255 /PC253/PC260/PR 131/PR132/PC259 /PC257/PC258/PU 15,reserve PC25 6SIT-0518-01 41 ADD 1.05V_S3 Po wer for USB3.0 Device lost iss ue

Reserve PR284/ PQ77SIT-0518-01

ADD C712/D30/D3 2SIT-0519-01 20 For ESD

Stuff L1/L2/L11

Stuff L5/AC39/A C40/AC41/AC42

Stuff C113

Stuff C91/C284/ C237/C206

Stuff R399/R400 /R401/R402

Stuff R83/R109 Change to 22

Reserve R206/R2 12

PR35 Change to 24.9K Power concern40

PL10/PL13 Chang e to CV-2275MZ0 0 Power concern

39

PC143 Change to 680p

40

Stuf C574/C581

33

39 PR227 Change to 150k/PR232 Cha nge to 180k Power concernSIT-0611-01

PR137 Change to 3.57k Power concern44

U10/U26 Change to BC101504Z00

Reseve PC60

40

stuf C573/C563/ PC153/PC95/PC9

schematic Match BOM

meet new type F AN

Support PCIE W ake up function

GPIO 24 no USB3 0_SMI#_PCH Func tion

Cancel PCH Dete ct USB OC PIN/F USE ADD Back IO BOARD

C-Stage power s ense DEL

Power concern

for current lea kage issue unde r S4/S5

vendor suggest

vendor suggest

for LPC OVER/Un der SHOOT

vendor suggest

vendor suggest

12V_HDD Disch arge38

STP_PCI_N Reser ve PU/PD resist ance for VERB T able control(TV /PC mode)SIT-0518-01 16 reserve R361

For EMI

Power concern

For Wlan 1.5V P ower

For ESD36

After SIT Change List

30SIT-0603-01 add F11/F12/F13 (DK300WFU0 00) For safty

Remove PQ64/PQ6 5SIT-0603-01 41 Power concern

SIT-0607-01 NO Stuff R198 for leakage cur rent

SIT-0613-01 D24/D26 Reserve14/12

SIT-0613-01 JP61 footprint change to sata- ld1107f-s33t5-7 p-r follow SMT Requ irement30

SIT-0613-01 PR284 footprint from RC1206 to RC2512 Power concern38

A A

SIT-0704-01 33 Mount Q43/R652 Support Wlan wa ke up function

41SIT-0607-01 Power concernPQ37/PQ38 Chang e to BAM4926000 0

23

5

For system hang up issueSIT-0611-01 14 Del C709

4

3

2

1

5

4

3

2

1

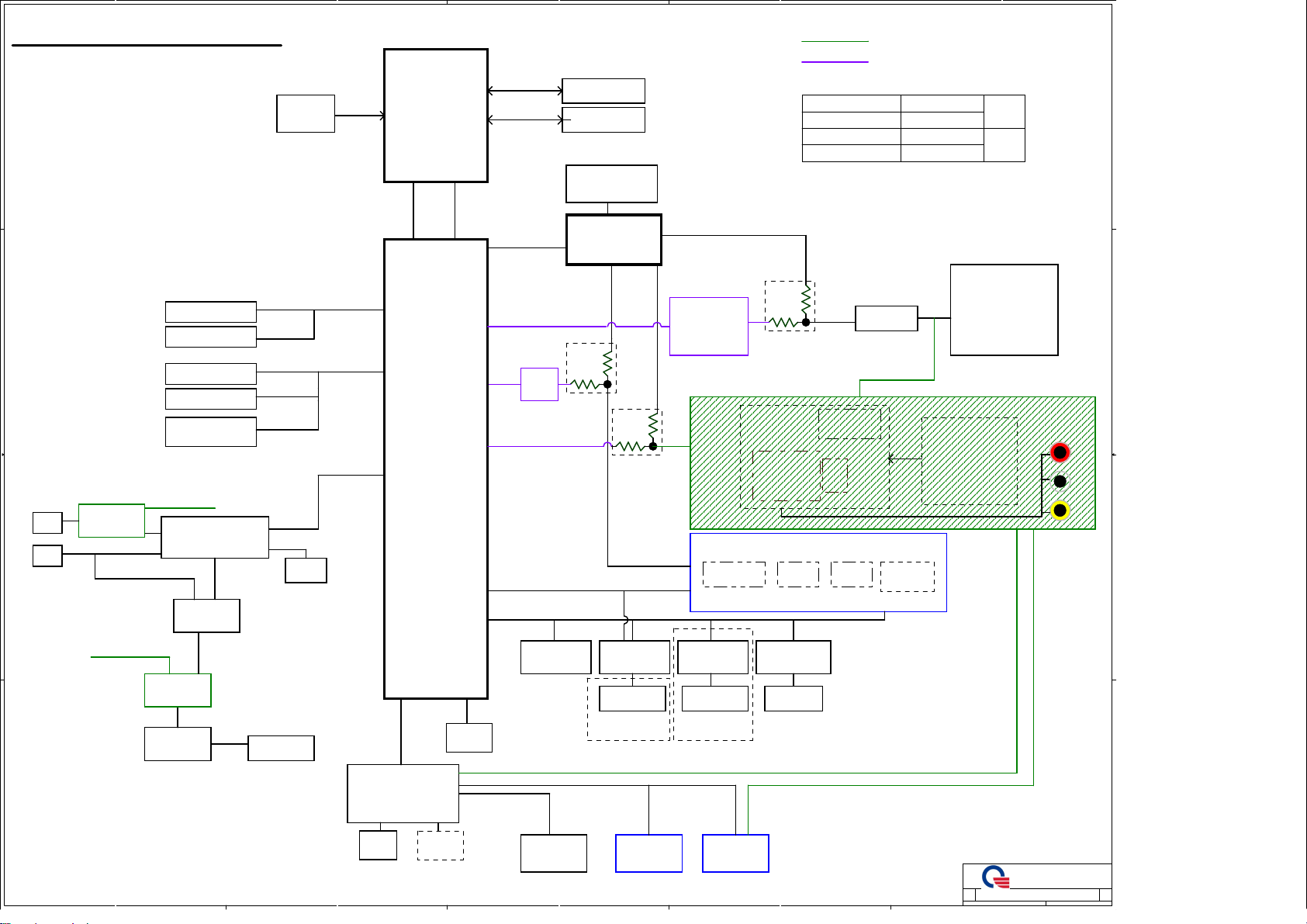

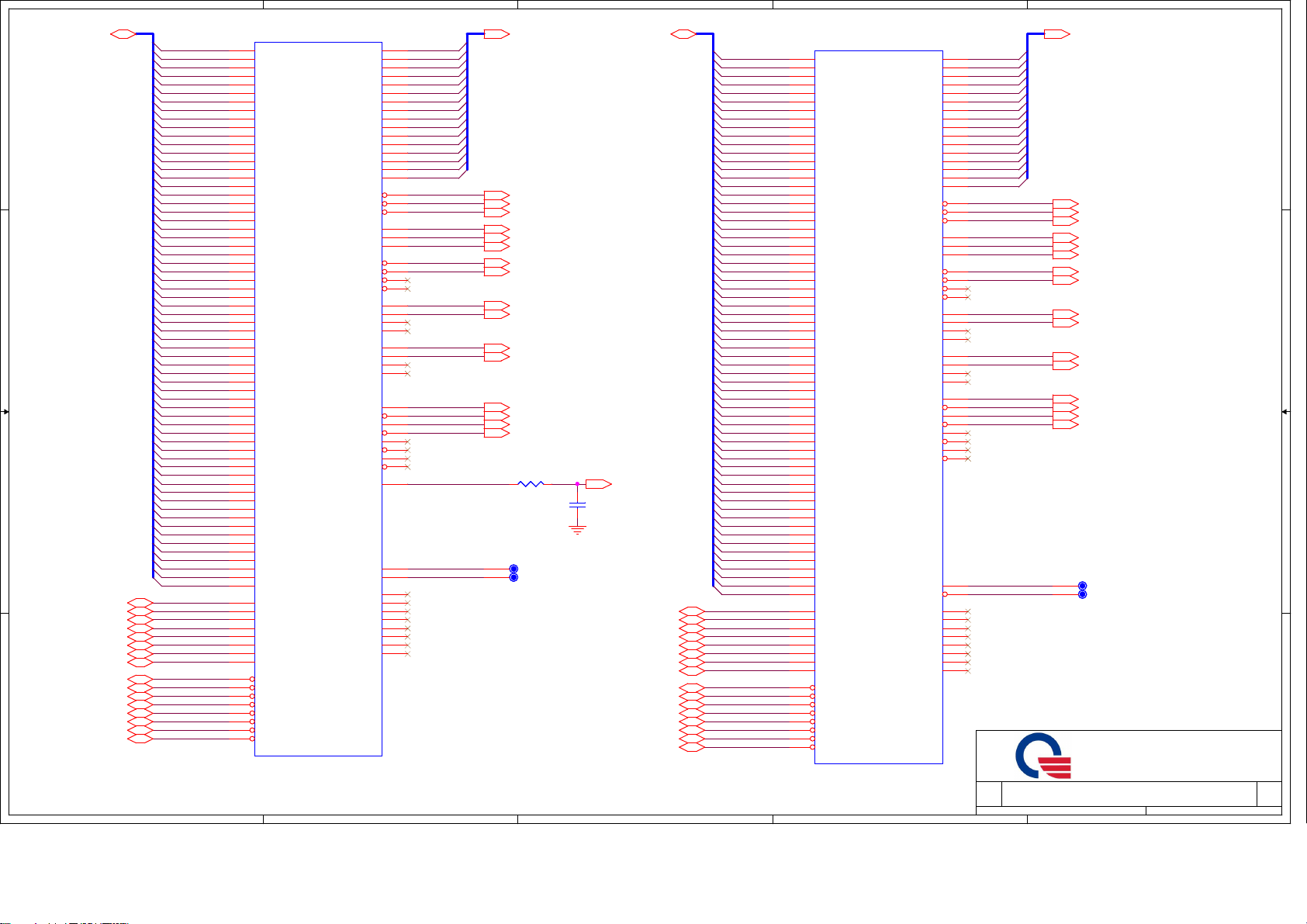

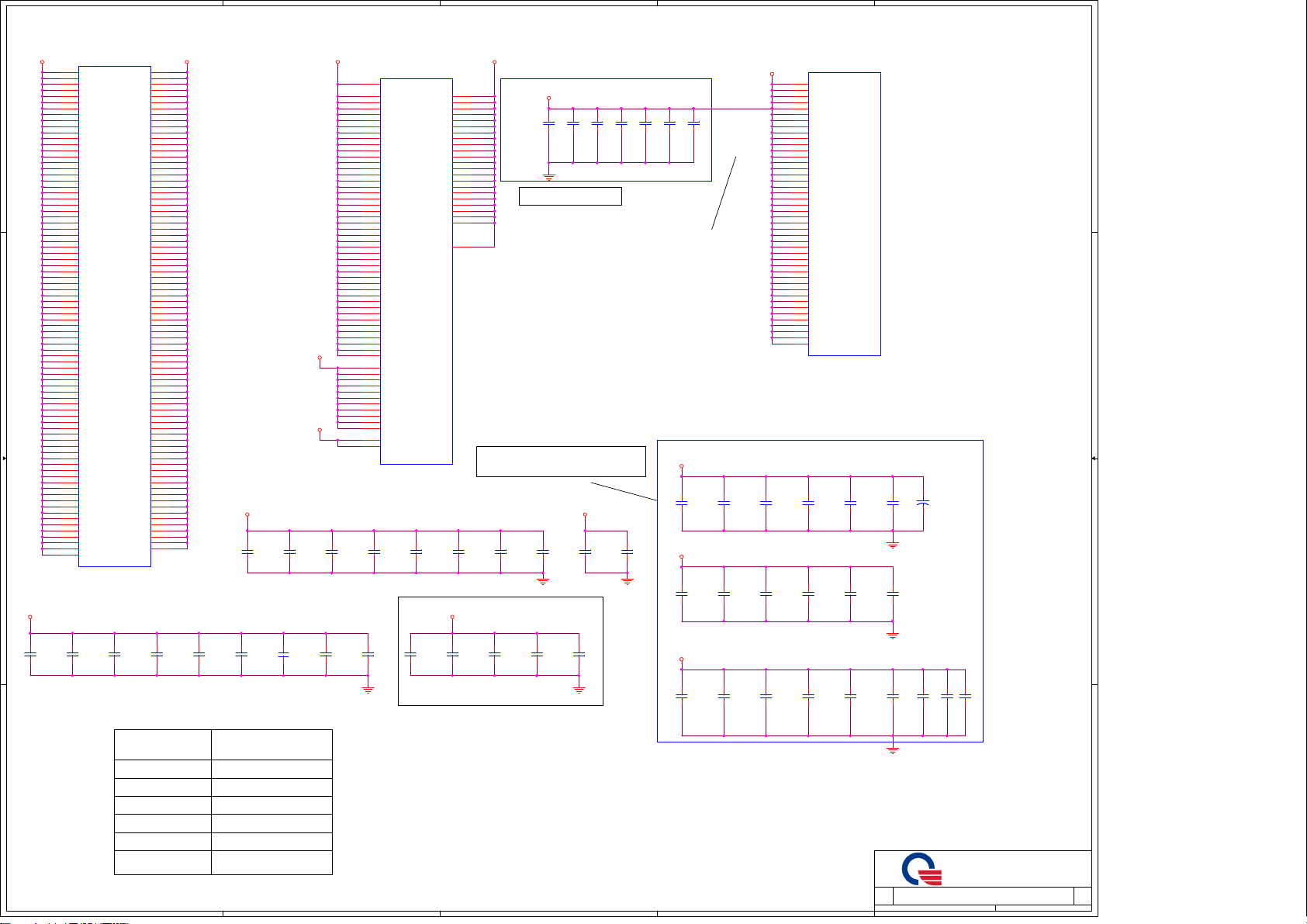

QUA Block Diagram

w/ HWTV

w/ UMA

SANDY BRIDGE

D D

CPU VCore

PG33

PROCESSOR

64-bit/32nm

LGA1155

Channel A

800/1066/1333MHz

Channel B

800/1066/1333MHz

Max to 8GB

DDR3 S0-DIMM

Socket 1

DDR3 SO-DIMM

Socket 2

PG11

PG11

65W

PG[5..10]

DMI Gen2 x4

FDI x4

PEG X16

VRAM DDR3

512MB (64M*16b*4)

GPU

Caspian M2

<Sean0327> Modify

LVDS

BOM

Control/Value

DIS w/

TV

UMA w/ TV

DIS w/o

TV

UMA w/o TV

DIS_TV@_

UMA_TV@_

DIS@_

UMA@_

TV@_

PC@_

<20W

HDMI

RGB

SATA HDD(DT)

C C

SATA ODD

Multi TOUCH

CAREMA

Side USB * 1

PG29

PG29

PG27

PG27

PG25

SATA 0

SATA 1

USBP9

USBP8

USBP4/5

SATA I/II

USB I/F

SATA * 4

USB *10

Cougar Point

(6.1W)

FCBGA

eDP

HDMI

RGB

Level

shifter

UMA/DIS

Option

UMA/DIS

Option

eDP to LVDS

Converter

RTD2136S

HW TV

PCH

HD AUDIO

HWTV(HP

HP

out

MIC

IN

B B

Audio Switch

TS5A23157

Support

S5_Speaker

AMP)

AUDIO CODEC

ALC-272

PG22

PC BEEP

PG24

Audio Switch

TS5A23157

(H61)

PCIE * 6

USBP0/1/2/3

PCIE I/F

HDMI

IO

USB Port*4 HDMI

USB

PG24

Scalar Board

RTD2673S

UMA/DIS

Option

LVDS

LVDS CONN

DDR

DC IN

LVDS CONN

GB LAN

RTL8111E

20" 16:9 Panel

1600*900 Pixel

TV Tuner Board

HWTV(Audio Out)

Mini PCIE

WLAN

PG26

CIR

Option

PG18

PG[12..20]

SPI FLASH

ROM

PG18

FAN CTRL

CPU X 1

Audio Switch

TS5A23157

FLASH

ROM

LPC

EC/KBC

ITE8519

LQFP128

PG18

Amplifier

ALC107

A A

5

R/L Header

3Wx2 Speaker

4

PG28

PG26

3

Mini PCIE

TV

PG28

B-CAS

Option

for Japan TV Model)

LED/PWR HotKey

LED BOARD

USB3.0

VL801

USB3.0 CNN

Option

Switch Button

CARD READER

RTS5209

3IN1 Card

CONN

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

QUA

PROJECT :

QUA

PROJECT :

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Block Diagram

Block Diagram

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

QUA

1 48Monday, July 04, 20 11

1 48Monday, July 04, 20 11

1 48Monday, July 04, 20 11

1A

1A

1A

5

4

3

2

1

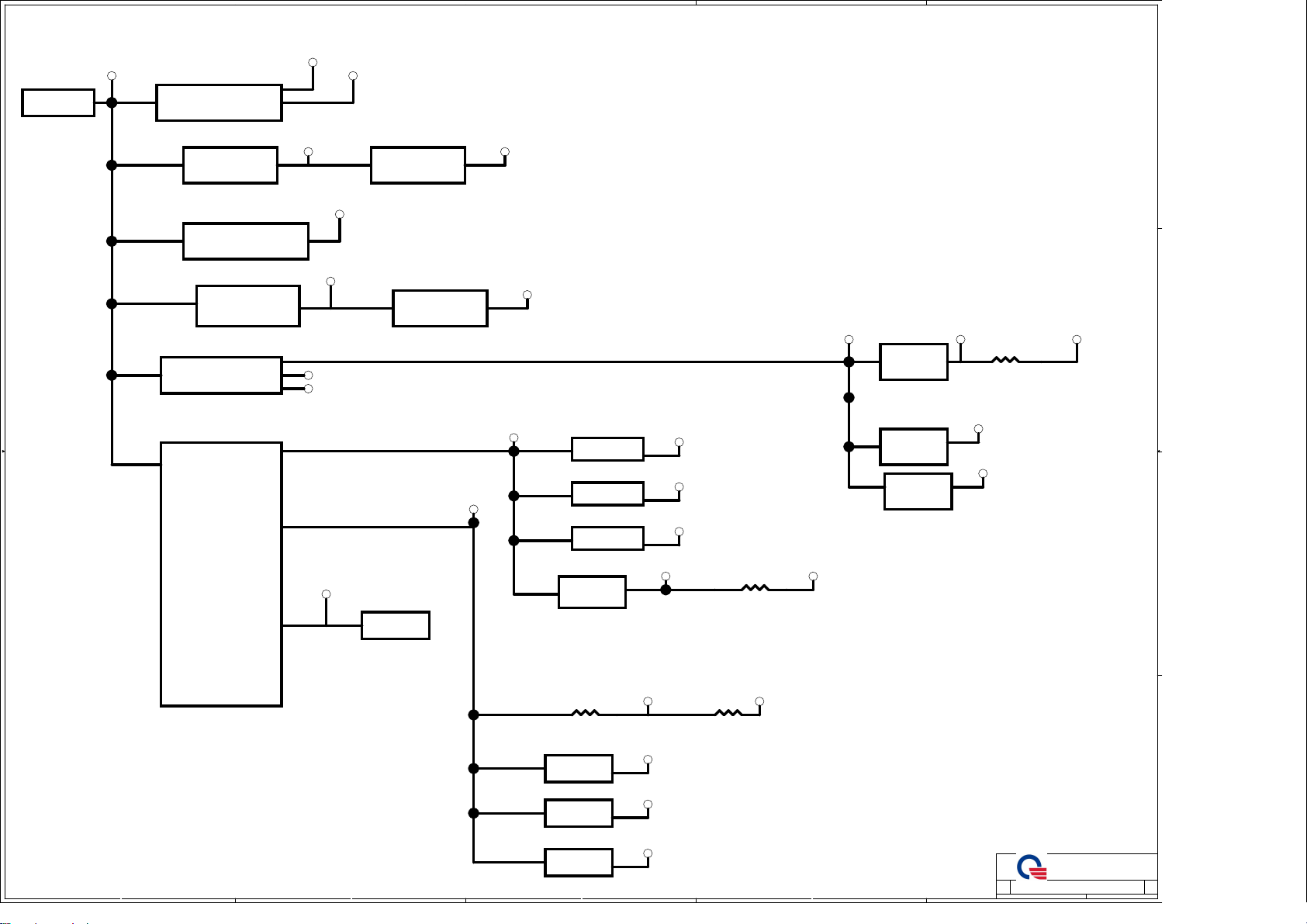

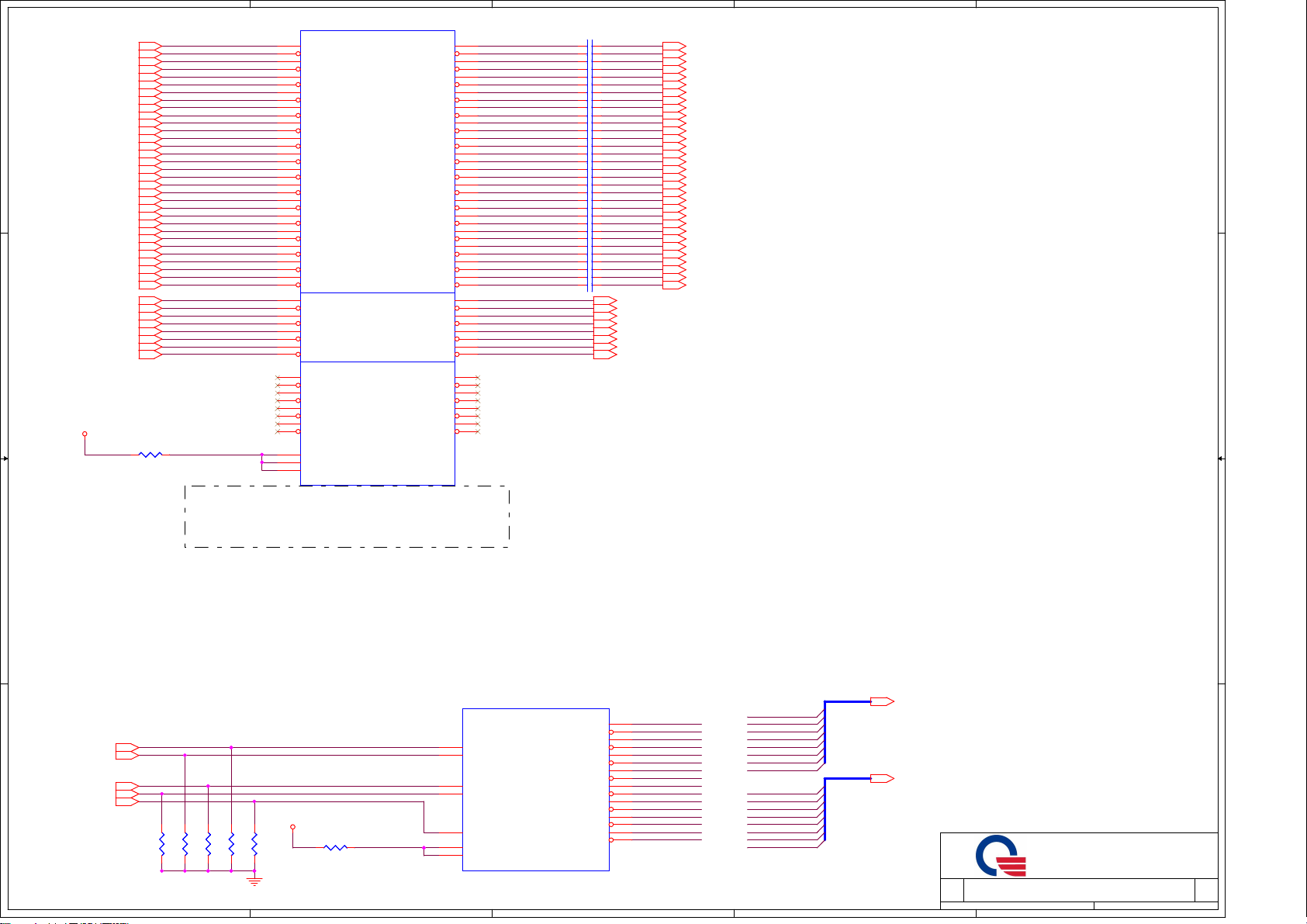

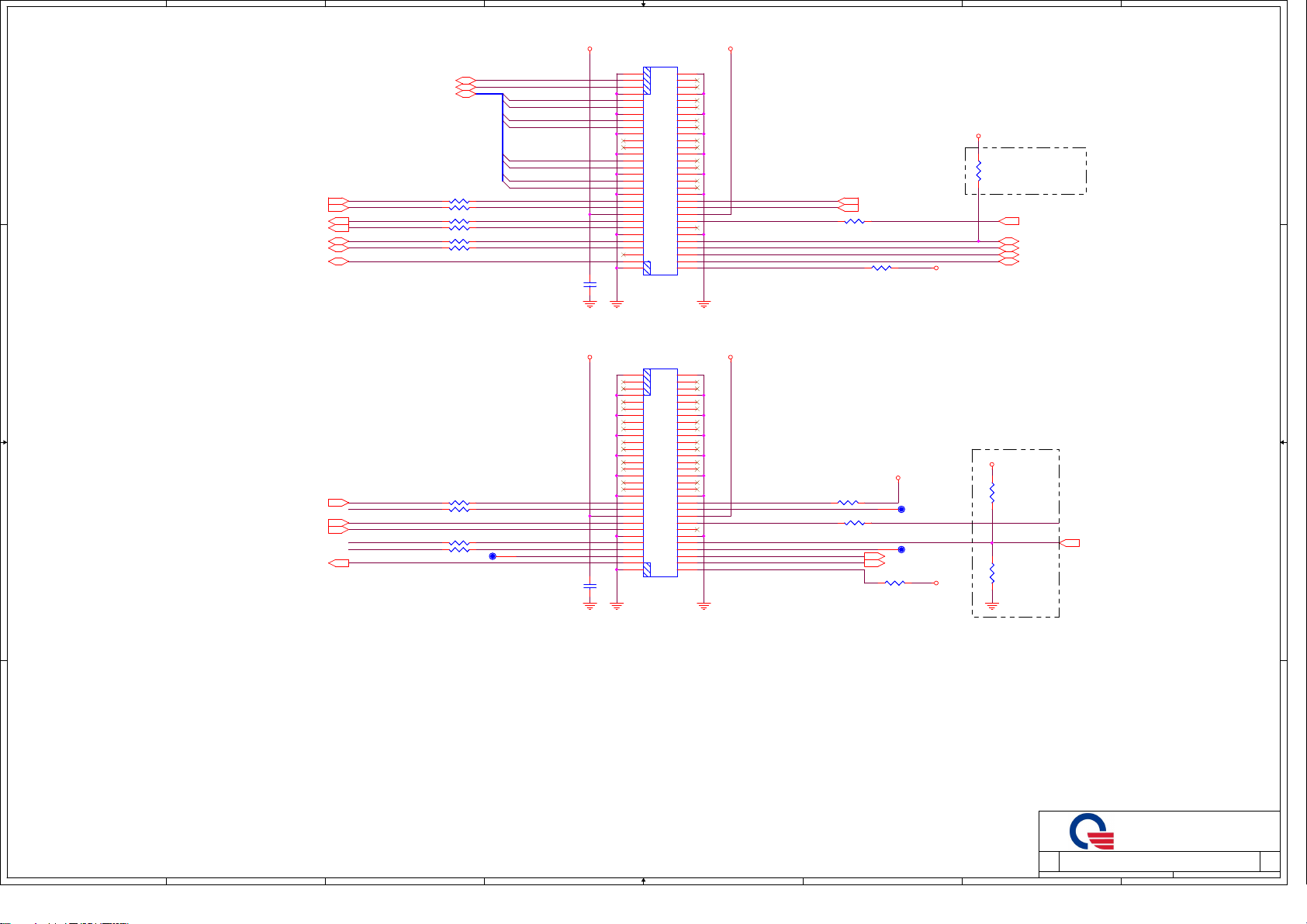

CPU_CORE

VIN

Adaptor

D D

DC-DC CPU_CORE

NCP6131 3+1phases

65A

CPU_AXG

35A

1.05V_VCCIO 0.925V_VCCSA

DC-DC VCCIO

RT8240B

17.4A

LDO VCCSA

LM358A

8.8A

VGA_CORE

11A

DC-DC VGA_CORE

ISL62881HRTZ-T

12V_HDD

0.78A

8V_CORE

DC-DC VCC12

NCP1587

C C

DC-DC DDR 1.5V

RT8207A

B B

DC-DC 3V / 5V

RT8223

VREF_DDR

SMDDR_VTERM

VREG3

APL1117UC

5V_AUX

3V_AUX

8.7A

SI4128

1.5V

1.5V_VGA

1A

4A

1.5V_S3

14A

1.05V

8A

SI4128

SI4128

3V_S5

0.1A

3V_S3

LDO VCC1.05

LM358A

LDO 1.05V

APL5920

8.3A

1V_VGA

1A

3.3V

1.8V

2A

4A

1.8V_VGA

0.5A

SI4129

LDO 1.8V

LM358A

EC

5V_AMP

3.2A

5V_TV

2A

5V_S5

SI4128

A A

SI4128

0.001A

5V_S3

3.6A

5V

SI4128

5

4

3

3.4A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Power Map

Power Map

Power Map

1

QUA

QUA

QUA

2 48Monday, July 04, 2 011

2 48Monday, July 04, 2 011

2 48Monday, July 04, 2 011

1A

1A

1A

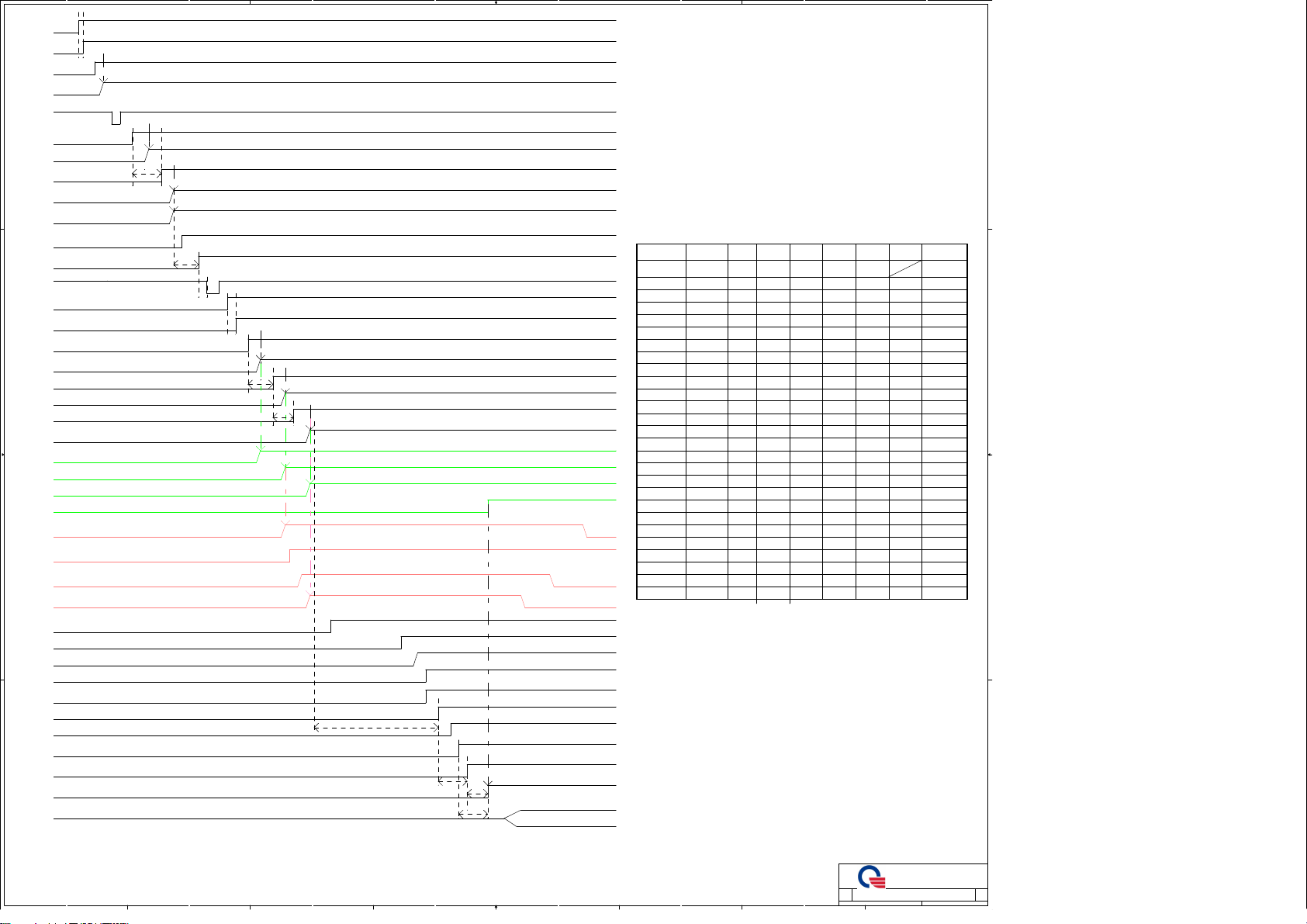

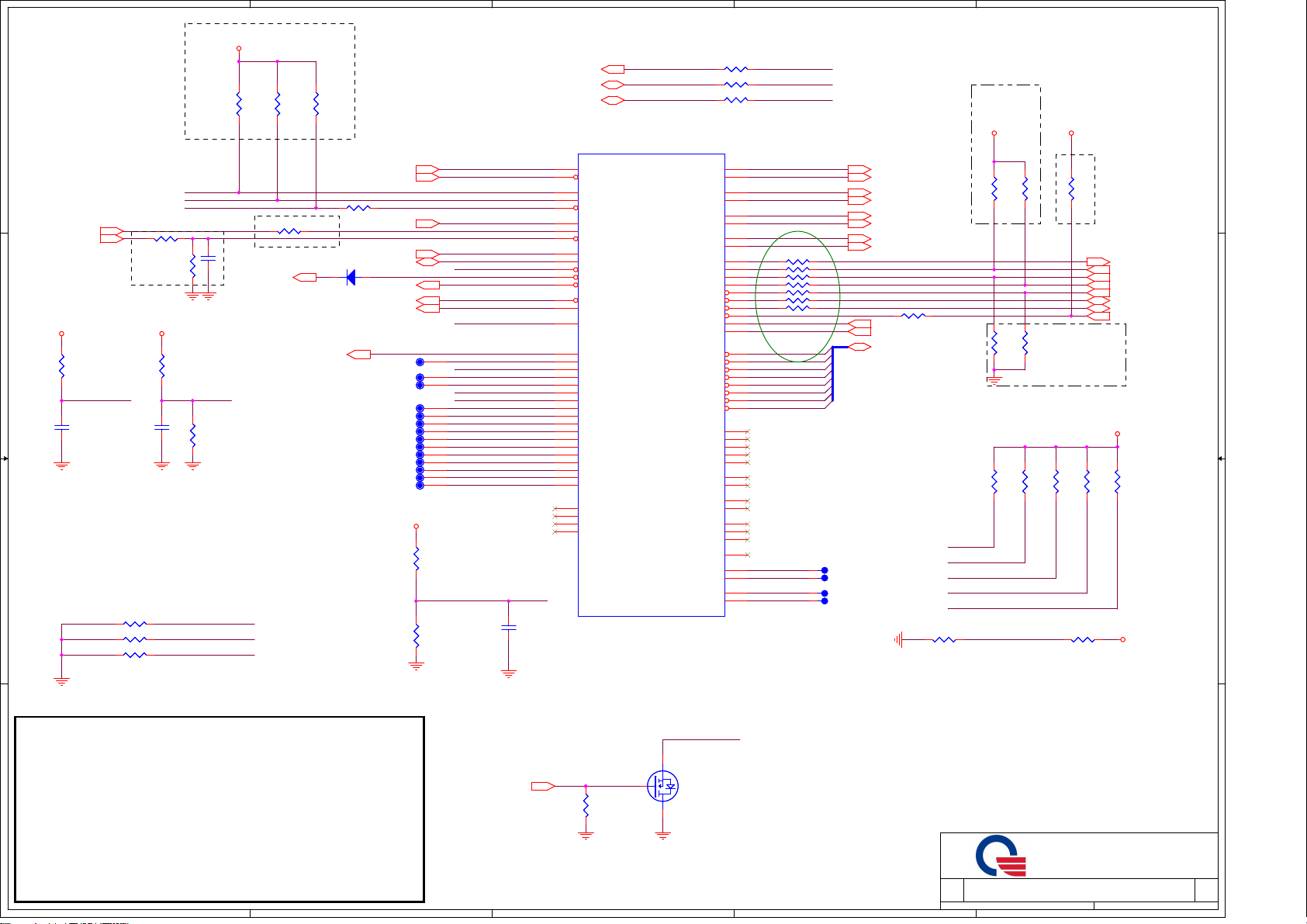

8

Battery

VCC_RTC

>9ms

RTCRST

Battery

VINAdapter

VREG3

DC/DC

D D

C C

B B

A A

FP_PWRBTN#PowerKey /SENSE_MIC_IN#/HWTV_PWR_ON#

EC

3V5V_ON

3V_AUX/5V_AUX/5V_AMP/5V_TV

DC/DC

EC

AVDD_ON/S5ON

AVDD

DC/DC

DC/DC

3V_S5/5V_S5

TV

HWTV_PWRGD

EC

RSMRST#

EC

EC_PWRBTN_OUT#

SLP_S4#

PCH

SLP_S3#

PCH

EC

S3_ON

5V_S3/3V_S3/1.5V_S3

DC/DC

S0_ON1

EC

12V_HDD/8V_CORE/5V/3.3V

DC/DC

S0_ON2

EC

DC/DC

1.8V/1.5V/1.05V_VCCIO/1.05V/1V_VGA/0.925V_VCCSA/SMDDR_VTERM

USB3

USB30_+3.3VAUX

USB3

USB30_3.3V

USB3

USB30_1VE/USB30_1VL

PLTRST_PCIE_N_USB

USB3

3V_VGA

GPU

EC

VGA_ON

VGA_CORE

DC/DC

1.8V_VGA/1.5V_VGA

DC/DC

HWPG

DC/DC

EC

VRON(/DRON)

CPU_CORE/CPU_AXG

DC/DC

IMVP_PWRGD

DC/DC

EC

EC_PWROK

PCH_SYSPWROK/PCH_PWRGD

Logic

PWRGD_DRAM

PCH

H_PWRGD

PCH

SUS_STAT#

PCH

PLTRST#

PCH

DMI

PCH

10ms

TV MODE

PC MODE

>15ms

7

6

5

4

3

2

1

3

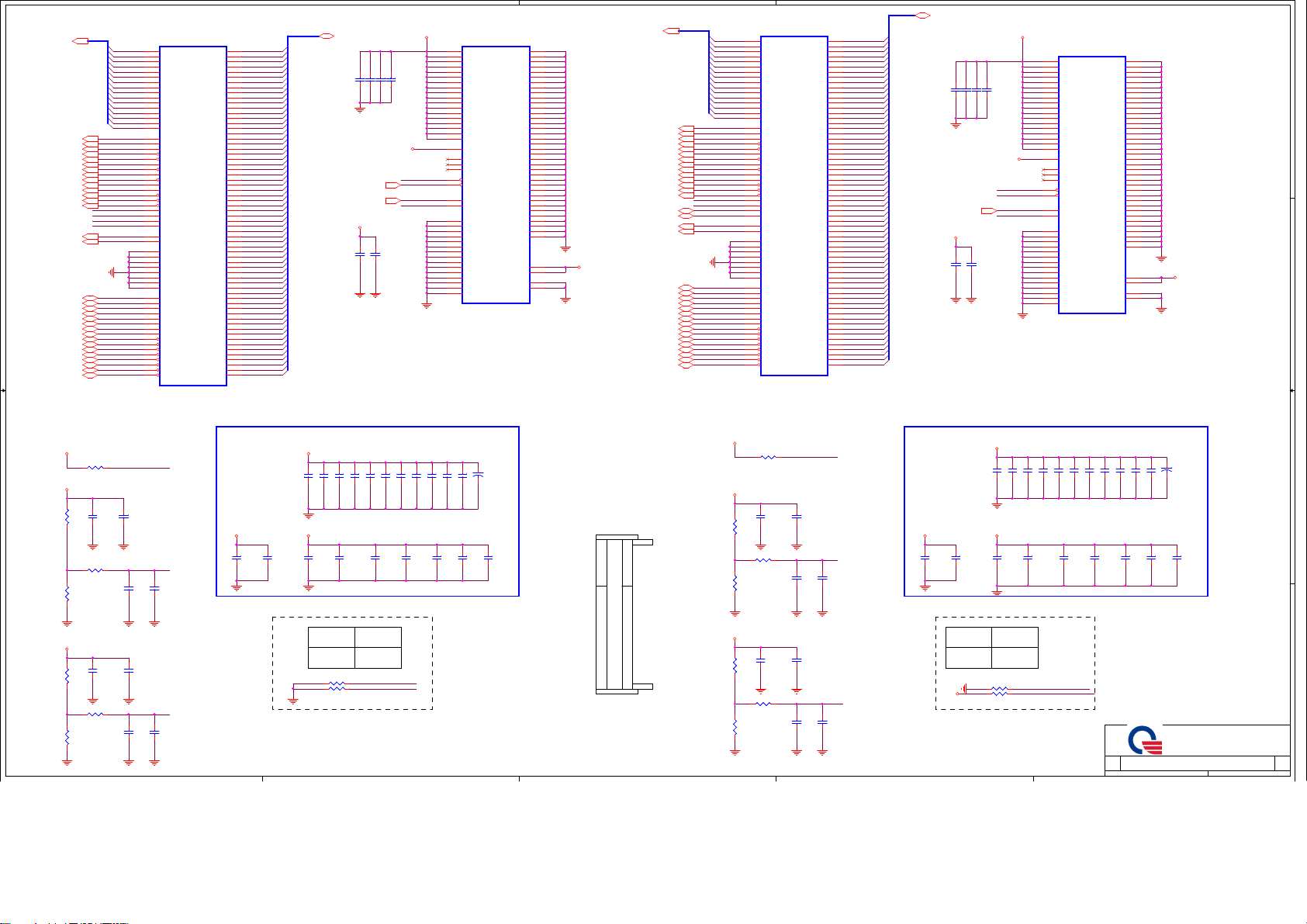

QUA Power sequence

Voltage Rails

TV mode

ON

ON

ON

ON

ON

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

Ctl Signal

Battery IN

Adaptor IN

VIN

3V5V_ON

3V5V_ON

5V_AUX

5V_AMP

S5_ON

S5_ON

S3_ON

S3_ON

S0_ON1

S0_ON1

S0_ON1

S0_ON2

S0_ON2

S0_ON2

S0_ON2

S0_ON2

S0_ON2

12V_HDD

VGA_ON

1.8V

1.5V

VR_PVCCUSA_SEL

VR_ON

VR_ON

=20ms

>30us

Ramp <20ms

20ms

<10ms

20ms

5-20ms

>99ms

>10ms

=10ms

>1ms

50-450ms

>210us

>30us

Power S0

VCCRTC

VIN

VREG3 3.3V

5V_AUX

5V_AMP

5V_TV

5V_S5

3V_S5

5V_S3

3V_S3 3.3V

12V_HDD 12V

5V

3.3V

1.8V

1.5V

1.05V

1.05V_VCCIO

SMDDR_VTERM

1V_VGA

8V_CORE

VGA_CORE

1.8V_VGA

1.5V_VGA

0.95V_VCCSA

CPU_CORE

CPU_AXG by SVID

3.3V

19V

5V

3.3V3V_AUX

5V

5V

5V

3.3V

5V

5V

3.3V

1.8V

1.5V

1.05V

1.05V

0.75V

1V

8V

0.8V- 1.15V

1.8V

1.5V

0.95V

by SVID

S4

S3Voltage

ON

ON

ON ON

ON

ON ON

ON

ON

ONON

ON ON OFF OFF

ONONON

ON

ONONON

ON

ON OFF OFF OFF

ON

ON

OFF

ON

OFF

ON

OFF

OFF

ON

ON

OFF OFF OFF OFF

ON

OFF

ON

OFF

ON

OFF

ON

OFF

ON

OFF OFF

ON OFF

ONONOFF

OFF

OFFON OFFOFFOFF

ONONOFF

OFF

S5

G3

ON

ON ON

ON ON OFF

ON OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF OFF OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFFOFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFFOFF OFF

OFF

OFF

OFF OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF OFF

OFF

OFF

OFF

OFF

OFF

OFF

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

QUA

PROJECT :

QUA

PROJECT :

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Power Sequence

Power Sequence

Power Sequence

Date: Sheet of

Date: Sheet of

8

7

6

5

4

3

Date: Sheet of

2

QUA

1A

1A

1A

3 48Monday, July 04, 20 11

3 48Monday, July 04, 20 11

3 48Monday, July 04, 20 11

1

5

4

3

2

1

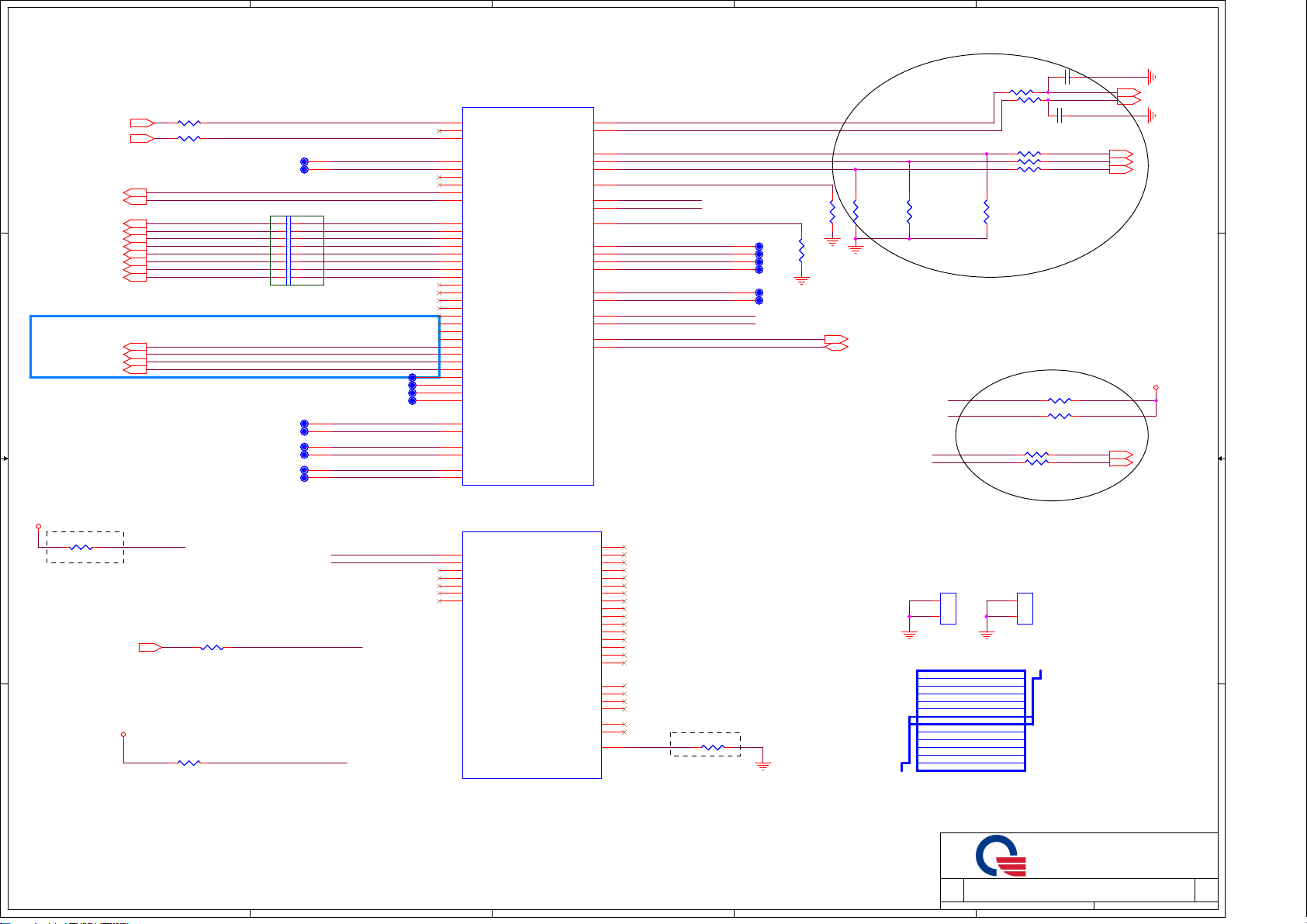

Intel PCH (H61)

CLKIN_GND0_N

CLKIN_GND0_P

CLKIN_GND1_N

CLKIN_GND1_P

D D

C C

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

CLKOUT_PCIE7_N

CLKOUT_PCIE7_P

CLKOUT_DMI_N

CLKOUT_DMI_P

CLKOUT_DP_N

CLKOUT_DP_P

CLKOUT_PCIE0_N

CLKOUT_PCIE0_P

CLKOUT_PCIE1_N

CLKOUT_PCIE1_P

CLKOUT_PCIE2_N

CLKOUT_PCIE2_P

CLKOUT_PCIE3_N

CLKOUT_PCIE3_P

CLKOUT_PCIE4_N

CLKOUT_PCIE4_P

CLKOUT_PCIE5_N

CLKOUT_PCIE5_P

CLKOUT_PCIE6_N

CLKOUT_PCIE6_P

CLKOUT_PEG_A_N

CLKOUT_PEG_A_P

CLKOUT_PEG_B_N

CLKOUT_PEG_B_P

CLKOUT_PCI0

CLKOUT_PCI1

CLKOUT_PCI2

B B

CLKOUT_PCI3

CLKOUT_PCI4

PCICLK_IN

CLKIN_DOT_96N

CLKIN_DOT_96P

CLKIN_SATA_N

CLKIN_SATA_P

CLKIN_DMI_N

CLKIN_DMI_P

REFCLK14MIN

CK_CSI_PCH_IN_DP/DN

PCHCLK_P/N

CLK_100M_PCH_CPUXDP_DP/DN_R

Rs

Rs

CLK_100M_CPU_ITP_DP/DN

R0

CLK_100M_XDP_HEADER_DP/DN

R0

R0

CLK_100M_PCH_CPU_RP/N CLK_100M_CPU/#

CLK_PCIE_TV_RP/RN CLK_PCIE_TV_P/N

CLK_PCIE_LAN_RP/RN CLK_PCIE_LAN_P/N

CLK_PCIE_CR_RP/RN

CLK_PCIE_USB3_RP/RN

PCH_XDP_100M_RP/RN PCH_XDP_100M/#

CLK_PCIE_VGA_RP/RN CLK_PCIE_VGA_P/N

TP__CLK_33M

PCICLK_DB_R

PCLK_EC_R

CLK_33M_PCH_R

CLK_33M_PCH

Rs

R0

R0

R0

CLK_PCIE_CR_P/N

R0

CLK_PCIE_USB3_P/N

R0

R0

R0

Test Pad

PCICLK_DB

Rs

PCLK_EC

Rs

Rs

Rs

Rs

Rs

Co-Layout

RSVD1

CPU

RSVD2

Pin40

XDP1

Pin42

(CN33)

WLAN Mini Card

CPU BCLK

PCIE MINI CARD

(TV TUNER)

PCIE MINI CARD

(Daughter B/D)

CARD READER

(RTS5209)

USB3.0

(VL800)

XDP2

(CN34)

GPU

(Caspian M2)

PCIE MINI CARD

(PORT80)

EC(ITE8519E)

BTM: Buffer Through Mode

Need CK505 to provide 4 clock to PCH

FCIM: Full Clock Intergration Mode

Remove CK505

Note: Red Color is Gen2 spec.

Note: R0 is 0 ohm optional resister

Note: Rs is series resister

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

CLK Map

CLK Map

CLK Map

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

QUA

QUA

QUA

4 48Monday, July 04, 2011

4 48Monday, July 04, 2011

1

4 48Monday, July 04, 2011

1A

1A

1A

5

4

3

2

1

M_A_DQ[63:0][11]

D D

C C

B B

M_A_DQS0[11]

M_A_DQS1[11]

M_A_DQS2[11]

M_A_DQS3[11]

M_A_DQS4[11]

M_A_DQS5[11]

M_A_DQS6[11]

M_A_DQS7[11]

M_A_DQS#0[11]

M_A_DQS#1[11]

M_A_DQS#2[11]

M_A_DQS#3[11]

A A

M_A_DQS#4[11]

M_A_DQS#5[11]

M_A_DQS#6[11]

M_A_DQS#7[11]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

5

AJ3

AJ4

AL3

AL4

AJ2

AJ1

AL2

AL1

AN1

AN4

AR3

AR4

AN2

AN3

AR2

AR1

AV2

AW3

AV5

AW5

AU2

AU3

AU5

AY5

AY7

AU7

AV9

AU9

AV7

AW7

AW9

AY9

AU35

AW37

AU39

AU36

AW35

AY36

AU38

AU37

AR40

AR37

AN38

AN37

AR39

AR38

AN39

AN40

AL40

AL37

AJ38

AJ37

AL39

AL38

AJ39

AJ40

AG40

AG37

AE38

AE37

AG39

AG38

AE39

AE40

AK3

AP3

AW4

AV8

AV37

AP38

AK38

AF38

AK2

AP2

AV4

AW8

AV36

AP39

AK39

AF39

XU1A

XU1A

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS_N_0

SA_DQS_N_1

SA_DQS_N_2

SA_DQS_N_3

SA_DQS_N_4

SA_DQS_N_5

SA_DQS_N_6

SA_DQS_N_7

LGA1155

LGA1155

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_WE_N

SA_CAS_N

SA_RAS_N

SA_BS0

SA_BS1

SA_BS2

SA_CS_N0

SA_CS_N1

SA_CS_N2

SA_CS_N3

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_ODT0

SA_ODT1

SA_ODT2

SA_ODT3

SA_CK0

SA_CK_N0

SA_CK1

SA_CK_N1

SA_CK2

SA_CK_N2

SA_CK3

SA_CK_N3

SM_DRAMRST_N

SA_DQS_8

SA_DQS_N_8

SA_ECC_CB0

SA_ECC_CB1

SA_ECC_CB2

SA_ECC_CB3

SA_ECC_CB4

SA_ECC_CB5

SA_ECC_CB6

SA_ECC_CB7

DDR_0

DDR_0

M_A_A0

AV27

M_A_A1

AY24

M_A_A2

AW24

M_A_A3

AW23

M_A_A4

AV23

M_A_A5

AT24

M_A_A6

AT23

M_A_A7

AU22

M_A_A8

AV22

M_A_A9

AT22

M_A_A10

AV28

M_A_A11

AU21

M_A_A12

AT21

M_A_A13

AW32

M_A_A14

AU20

M_A_A15

AT20

M_A_WE#

AW29

M_A_CAS#

AV30

M_A_RAS#

AU28

M_BA_A0

AY29

M_BA_A1

AW28

M_BA_A2

AV20

M_CS#_A0

AU29

M_CS#_A1

AV32

AW30

AU33

M_CKE_A0

AV19

M_CKE_A1

AT19

AU18

AV18

M_ODT_A0

AV31

M_ODT_A1

AU32

AU30

AW33

M_CLK_DDR_A0

AY25

M_CLK_DDR#_A0

AW25

M_CLK_DDR_A1

AU24

M_CLK_DDR#_A1

AU25

AW27

AY27

AV26

AW26

DDR3_DRAMRST_N_R

AW18

AV13

AV12

AU12

AU14

AW13

AY13

AU13

AU11

AY12

AW12

4

M_A_DQS8

M_A_DQS#8

M_A_A[15:0] [11] M_B_DQ[63:0][11]

M_A_WE# [11]

M_A_CAS# [11]

M_A_RAS# [11]

M_BA_A0 [11]

M_BA_A1 [11]

M_BA_A2 [11]

M_CS#_A0 [11]

M_CS#_A1 [11]

M_CKE_A0 [11]

M_CKE_A1 [11]

M_ODT_A0 [11]

M_ODT_A1 [11]

M_CLK_DDR_A0 [11]

M_CLK_DDR#_A0 [11]

M_CLK_DDR_A1 [11]

M_CLK_DDR#_A1 [11]

R46 0R_4R46 0R_4

TP5TP5

1

TP6TP6

1

C41

C41

*1u/6.3V_4

*1u/6.3V_4

DDR3_DRAMRST# [11]

M_B_DQS0[11]

M_B_DQS1[11]

M_B_DQS2[11]

M_B_DQS3[11]

M_B_DQS4[11]

M_B_DQS5[11]

M_B_DQS6[11]

M_B_DQS7[11]

M_B_DQS#0[11]

M_B_DQS#1[11]

M_B_DQS#2[11]

M_B_DQS#3[11]

M_B_DQS#4[11]

M_B_DQS#5[11]

M_B_DQS#6[11]

M_B_DQS#7[11]

3

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

AG7

AG8

AJ9

AJ8

AG5

AG6

AJ6

AJ7

AL7

AM7

AM10

AL10

AL6

AM6

AL9

AM9

AP7

AR7

AP10

AR10

AP6

AR6

AP9

AR9

AM12

AM13

AR13

AP13

AL12

AL13

AR12

AP12

AR28

AR29

AL28

AL29

AP28

AP29

AM28

AM29

AP32

AP31

AP35

AP34

AR32

AR31

AR35

AR34

AM32

AM31

AL35

AL32

AM34

AL31

AM35

AL34

AH35

AH34

AE34

AE35

AJ35

AJ34

AF33

AF35

AH7

AM8

AR8

AN13

AN29

AP33

AL33

AG35

AH6

AL8

AP8

AN12

AN28

AR33

AM33

AG34

XU1B

XU1B

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS_N_0

SB_DQS_N_1

SB_DQS_N_2

SB_DQS_N_3

SB_DQS_N_4

SB_DQS_N_5

SB_DQS_N_6

SB_DQS_N_7

LGA1155

LGA1155

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SA_CK[2]

AS_CK[1]

AS_ODT[2]

SB_BS0

SB_BS1

SB_BS2

SB_CS_N0

SB_CS_N1

SB_CS_N2

SB_CS_N3

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_ODT0

SB_ODT1

SB_ODT2

SB_ODT3

SB_CK0

SB_CK_N0

SB_CK1

SB_CK_N1

SB_CK2

SB_CK_N2

SB_CK3

SB_CK_N3

SB_DQS_8

SB_DQS_N_8

SB_ECC_CB0

SB_ECC_CB1

SB_ECC_CB2

SB_ECC_CB3

SB_ECC_CB4

SB_ECC_CB5

SB_ECC_CB6

SB_ECC_CB7

DDR_1

DDR_1

2

M_B_A[15:0] [11]

M_B_A0

AK24

M_B_A1

AM20

M_B_A2

AM19

M_B_A3

AK18

M_B_A4

AP19

M_B_A5

AP18

M_B_A6

AM18

M_B_A7

AL18

M_B_A8

AN18

M_B_A9

AY17

M_B_A10

AN23

M_B_A11

AU17

M_B_A12

AT18

M_B_A13

AR26

M_B_A14

AY16

M_B_A15

AV16

M_B_WE#

AR25

M_B_CAS#

AK25

M_B_RAS#

AP24

M_BA_B0

AP23

M_BA_B1

AM24

M_BA_B2

AW17

M_CS#_B0

AN25

M_CS#_B1

AN26

AL25

AT26

M_CKE_B0

AU16

M_CKE_B1

AY15

AW15

AV15

M_ODT_B0

AL26

M_ODT_B1

AP26

AM26

AK26

M_CLK_DDR_B0

AL21

M_CLK_DDR#_B0

AL22

M_CLK_DDR_B1

AL20

M_CLK_DDR#_B1

AK20

AL23

AM22

AP21

AN21

M_B_DQS8

AN16

M_B_DQS#8

AN15

AL16

AM16

AP16

AR16

AL15

AM15

AR15

AP15

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SOCKET H2 DDR3

SOCKET H2 DDR3

SOCKET H2 DDR3

Date: Sheet of

Date: Sheet of

Date: Sheet of

M_B_WE# [11]

M_B_CAS# [11]

M_B_RAS# [11]

M_BA_B0 [11]

M_BA_B1 [11]

M_BA_B2 [11]

M_CS#_B0 [11]

M_CS#_B1 [11]

M_CKE_B0 [11]

M_CKE_B1 [11]

M_ODT_B0 [11]

M_ODT_B1 [11]

M_CLK_DDR_B0 [11]

M_CLK_DDR#_B0 [11]

M_CLK_DDR_B1 [11]

M_CLK_DDR#_B1 [11]

TP54TP54

1

TP55TP55

1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

QUA

QUA

QUA

5 48Monday, July 04, 2011

5 48Monday, July 04, 2011

5 48Monday, July 04, 2011

1

1A

1A

1A

5

XU1C

AA4

AA5

B11

B12

D12

D11

C10

E10

C9

E9

B8

B7

C6

C5

A5

A6

E2

E1

F4

F3

G2

G1

H3

H4

J1

J2

K3

K4

L1

L2

M3

M4

N1

N2

W5

W4

V3

V4

Y3

Y4

P3

P4

R2

R1

T4

T3

U2

U1

B5

C4

B4

XU1C

PEG_RX_0

PEG_RX_N0

PEG_RX_1

PEG_RX_N1

PEG_RX_2

PEG_RX_N2

PEG_RX_3

PEG_RX_N3

PEG_RX_4

PEG_RX_N4

PEG_RX_5

PEG_RX_N5

PEG_RX_6

PEG_RX_N6

PEG_RX_7

PEG_RX_N7

PEG_RX_8

PEG_RX_N8

PEG_RX_9

PEG_RX_N9

PEG_RX_10

PEG_RX_N10

PEG_RX_11

PEG_RX_N11

PEG_RX_12

PEG_RX_N12

PEG_RX_13

PEG_RX_N13

PEG_RX_14

PEG_RX_N14

PEG_RX_15

PEG_RX_N15

DMI_RX_0

DMI_RX_N0

DMI_RX_1

DMI_RX_N1

DMI_RX_2

DMI_RX_N2

DMI_RX_3

DMI_RX_N3

PE_RX_0

PE_RX_N0

PE_RX_1

PE_RX_N1

PE_RX_2

PE_RX_N2

PE_RX_3

PE_RX_N3

PEG_ICOMPO

PEG_RCOMPO

PEG_COMPI

LGA1155

LGA1155

PEG_RX15[22]

PEG_RX#15[22]

PEG_RX14[22]

PEG_RX#14[22]

PEG_RX13[22]

PEG_RX#13[22]

PEG_RX12[22]

PEG_RX#12[22]

PEG_RX11[22]

DMI_PCH_CPU_RXP0[14]

DMI_PCH_CPU_RXN0[14]

DMI_PCH_CPU_RXP1[14]

DMI_PCH_CPU_RXN1[14]

DMI_PCH_CPU_RXP2[14]

DMI_PCH_CPU_RXN2[14]

DMI_PCH_CPU_RXP3[14]

DMI_PCH_CPU_RXN3[14]

1.05V_VCCIO

PEG_RX#11[22]

PEG_RX10[22]

PEG_RX#10[22]

PEG_RX9[22]

PEG_RX#9[22]

PEG_RX8[22]

PEG_RX#8[22]

PEG_RX7[22]

PEG_RX#7[22]

PEG_RX6[22]

PEG_RX#6[22]

PEG_RX5[22]

PEG_RX#5[22]

PEG_RX4[22]

PEG_RX#4[22]

PEG_RX3[22]

PEG_RX#3[22]

PEG_RX2[22]

PEG_RX#2[22]

PEG_RX1[22]

PEG_RX#1[22]

PEG_RX#0[22]

R45 24.9R/F_4R45 24.9R/F_4

D D

C C

FDI DISABLE GUIDELINES (FROM PDG)

FDI SIGNAL RECOMMENDATION

FDI_TX[7:0] FLOAT

FDI_TX_N[7:0] FLOAT

FDI_FSYNC 1K RESISTOR TO VCC_FDI OR VSS

FDI_LSYNC 1K RESISTOR TO VCC_FDI OR VSS

B B

FDI_INT 1K RESISTOR TO VCC_FDI OR VSS

PEG_RX15

PEG_RX#15

PEG_RX14

PEG_RX#14

PEG_RX13

PEG_RX#13

PEG_RX12

PEG_RX#12

PEG_RX11

PEG_RX#11

PEG_RX10

PEG_RX#10

PEG_RX9

PEG_RX#9

PEG_RX8

PEG_RX#8

PEG_RX7

PEG_RX#7

PEG_RX6

PEG_RX#6

PEG_RX5

PEG_RX#5

PEG_RX4

PEG_RX#4

PEG_RX3

PEG_RX#3

PEG_RX2

PEG_RX#2

PEG_RX1

PEG_RX#1

PEG_RX0

PEG_RX#0

DMI_PCH_CPU_RXP0

DMI_PCH_CPU_RXN0

DMI_PCH_CPU_RXP1

DMI_PCH_CPU_RXN1

DMI_PCH_CPU_RXP2

DMI_PCH_CPU_RXN2

DMI_PCH_CPU_RXP3

DMI_PCH_CPU_RXN3

GRCOMP

CAD NOTE:

PIN B5 ROUTING TO RESISTOR NEED TO BE 5 MILS

PIN C4 AND B4 ROUTING TO RESISTOR NEED TO BE 4 MILS

THERE ARE SPACING RULES ALSO - CHECK RULES DOCUMENT

4

PEGDMIGEN

PEGDMIGEN

PEG_TX_0

PEG_TX_N0

PEG_TX_1

PEG_TX_N1

PEG_TX_2

PEG_TX_N2

PEG_TX_3

PEG_TX_N3

PEG_TX_4

PEG_TX_N4

PEG_TX_5

PEG_TX_N5

PEG_TX_6

PEG_TX_N6

PEG_TX_7

PEG_TX_N7

PEG_TX_8

PEG_TX_N8

PEG_TX_9

PEG_TX_N9

PEG_TX_10

PEG_TX_N10

PEG_TX_11

PEG_TX_N11

PEG_TX_12

PEG_TX_N12

PEG_TX_13

PEG_TX_N13

PEG_TX_14

PEG_TX_N14

PEG_TX_15

PEG_TX_N15

DMI_TX_0

DMI_TX_N0

DMI_TX_1

DMI_TX_N1

DMI_TX_2

DMI_TX_N2

DMI_TX_3

DMI_TX_N3

PE_TX_0

PE_TX_N0

PE_TX_1

PE_TX_N1

PE_TX_2

PE_TX_N2

PE_TX_3

PE_TX_N3

C13

C14

E14

E13

G14

G13

F12

F11

J14

J13

D8

D7

D3

C3

E6

E5

F8

F7

G10

G9

G5

G6

K7

K8

J5

J6

M8

M7

L6

L5

N5

N6

V7

V6

W7

W8

Y6

Y7

AA7

AA8

P8

P7

T7

T8

R6

R5

U5

U6

PEG_TXP15_C

PEG_TXN15_C

PEG_TXP14_C

PEG_TXN14_C

PEG_TXP13_C

PEG_TXN13_C

PEG_TXP12_C

PEG_TXN12_C

PEG_TXP11_C

PEG_TXN11_C

PEG_TXP10_C

PEG_TXN10_C

PEG_TXP9_C

PEG_TXN9_C

PEG_TXP8_C

PEG_TXN8_C

PEG_TXP7_C

PEG_TXN7_C

PEG_TXP6_C

PEG_TXN6_C

PEG_TXP5_C

PEG_TXN5_C

PEG_TXP4_C

PEG_TXN4_C

PEG_TXP3_C

PEG_TXN3_C

PEG_TXP2_C

PEG_TXN2_C

PEG_TXP1_C

PEG_TXN1_C

PEG_TXP0_C

PEG_TXN0_C

DMI_CPU_PCH_TXP0

DMI_CPU_PCH_TXN0

DMI_CPU_PCH_TXP1

DMI_CPU_PCH_TXN1

DMI_CPU_PCH_TXP2

DMI_CPU_PCH_TXN2

DMI_CPU_PCH_TXP3

DMI_CPU_PCH_TXN3

C105 DIS@0.22u/6.3V_4C105 DIS@0.22u/6.3V_4

C104 DIS@0.22u/6.3V_4C104 DIS@0.22u/6.3V_4

C107 DIS@0.22u/6.3V_4C107 DIS@0.22u/6.3V_4

C106 DIS@0.22u/6.3V_4C106 DIS@0.22u/6.3V_4

C76 DIS@0.22u/6.3V_4C76 DIS@0.22u/6.3V_4

C75 DIS@0.22u/6.3V_4C75 DIS@0.22u/6.3V_4

C93 DIS@0.22u/6.3V_4C93 DIS@0.22u/6.3V_4

C92 DIS@0.22u/6.3V_4C92 DIS@0.22u/6.3V_4

C78 DIS@0.22u/6.3V_4C78 DIS@0.22u/6.3V_4

C77 DIS@0.22u/6.3V_4C77 DIS@0.22u/6.3V_4

C95 DIS@0.22u/6.3V_4C95 DIS@0.22u/6.3V_4

C94 DIS@0.22u/6.3V_4C94 DIS@0.22u/6.3V_4

C80 DIS@0.22u/6.3V_4C80 DIS@0.22u/6.3V_4

C79 DIS@0.22u/6.3V_4C79 DIS@0.22u/6.3V_4

C97 DIS@0.22u/6.3V_4C97 DIS@0.22u/6.3V_4

C96 DIS@0.22u/6.3V_4C96 DIS@0.22u/6.3V_4

C82 DIS@0.22u/6.3V_4C82 DIS@0.22u/6.3V_4

C81 DIS@0.22u/6.3V_4C81 DIS@0.22u/6.3V_4

C99 DIS@0.22u/6.3V_4C99 DIS@0.22u/6.3V_4

C98 DIS@0.22u/6.3V_4C98 DIS@0.22u/6.3V_4

C84 DIS@0.22u/6.3V_4C84 DIS@0.22u/6.3V_4

C83 DIS@0.22u/6.3V_4C83 DIS@0.22u/6.3V_4

C101 DIS@0.22u/6.3V_4C101 DIS@0.22u/6.3V_4

C100 DIS@0.22u/6.3V_4C100 DIS@0.22u/6.3V_4

C86 DIS@0.22u/6.3V_4C86 DIS@0.22u/6.3V_4

C85 DIS@0.22u/6.3V_4C85 DIS@0.22u/6.3V_4

C74 DIS@0.22u/6.3V_4C74 DIS@0.22u/6.3V_4

C73 DIS@0.22u/6.3V_4C73 DIS@0.22u/6.3V_4

C103 DIS@0.22u/6.3V_4C103 DIS@0.22u/6.3V_4

C102 DIS@0.22u/6.3V_4C102 DIS@0.22u/6.3V_4

C88 DIS@0.22u/6.3V_4C88 DIS@0.22u/6.3V_4

C87 DIS@0.22u/6.3V_4C87 DIS@0.22u/6.3V_4

3

<SEAN0331> change

X5R

AC-CAP

DMI_CPU_PCH_TXP0 [14]

DMI_CPU_PCH_TXN0 [14]

DMI_CPU_PCH_TXP1 [14]

DMI_CPU_PCH_TXN1 [14]

DMI_CPU_PCH_TXP2 [14]

DMI_CPU_PCH_TXN2 [14]

DMI_CPU_PCH_TXP3 [14]

DMI_CPU_PCH_TXN3 [14]

PEG_TX15 [22]

PEG_TX#15 [22]

PEG_TX14 [22]

PEG_TX#14 [22]

PEG_TX13 [22]

PEG_TX#13 [22]

PEG_TX12 [22]

PEG_TX#12 [22]

PEG_TX11 [22]

PEG_TX#11 [22]

PEG_TX10 [22]

PEG_TX#10 [22]

PEG_TX9 [22]

PEG_TX#9 [22]

PEG_TX8 [22]

PEG_TX#8 [22]

PEG_TX7 [22]

PEG_TX#7 [22]

PEG_TX6 [22]

PEG_TX#6 [22]

PEG_TX5 [22]

PEG_TX#5 [22]

PEG_TX4 [22]

PEG_TX#4 [22]

PEG_TX3 [22]

PEG_TX#3 [22]

PEG_TX2 [22]

PEG_TX#2 [22]

PEG_TX1 [22]

PEG_TX#1 [22]

PEG_TX0 [22]PEG_RX0[22]

PEG_TX#0 [22]

2

1

XU1D

XU1D

AC8

FDI_TX_0

FDI_TX_1

FDI_TX_2

FDI_TX_3

FDI_TX_4

FDI_TX_5

FDI_TX_6

FDI_TX_7

3

AC7

AC2

AC3

AD2

AD1

AD4

AD3

AD7

AD6

AE7

AE8

AF3

AF2

AG2

AG1

FDI_FSYNC0[18]

FDI_LSYNC0[18]

FDI_FSYNC1[18]

A A

FDI_LSYNC1[18]

FDI_INT[18]

1.05V_VCCIO

R58

R56

R56

R54

R54

R55

R55

*1K/F_4

*1K/F_4

*1K/F_4

*1K/F_4

5

R58

R59

R59

*1K/F_4

*1K/F_4

*1K/F_4

*1K/F_4

*1K/F_4

*1K/F_4

R483

R483

24.9R/F_4

24.9R/F_4

SNB_IPL_RCOMP

4

AC5

AC4

AE5

AE4

AG3

AE2

AE1

FDI_FSYNC_0

FDI_LSYNC_0

FDI_FSYNC_1

FDI_LSYNC_1

FDI_INT

FDI_COMPIO

FDI_ICOMPO

LGA1155

LGA1155

FDI_TX_N0

FDI_TX_N1

FDI_TX_N2

FDI_TX_N3

FDI_TX_N4

FDI_TX_N5

FDI_TX_N6

FDI_TX_N7

FDI LINK

FDI LINK

FDI_TXP0

FDI_TXN0

FDI_TXP1

FDI_TXN1

FDI_TXP2

FDI_TXN2

FDI_TXP3

FDI_TXN3

FDI_TXP4

FDI_TXN4

FDI_TXP5

FDI_TXN5

FDI_TXP6

FDI_TXN6

FDI_TXP7

FDI_TXN7

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

2

FDI_TXN[7:0] [18]

FDI_TXP[7:0] [18]

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SOCKET H2 PEG/DMI

SOCKET H2 PEG/DMI

SOCKET H2 PEG/DMI

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

QUA

QUA

QUA

1

1A

1A

6 48Monday, July 04, 2011

6 48Monday, July 04, 2011

6 48Monday, July 04, 2011

1A

5

4

3

2

1

1.05V_VCCIO

CLK_100M_CPU[12]

CLK_100M_CPU#[12]

R10 44.2R/F_4R10 44.2R/F_4

H_PM_SYNC_0[15]

H_THERMTRIP_N[15]

FM_PROCSEL_DMI_TERM[13]

CAD NOTE:

PLACE NEAR CPU

H_PWRGD[10,16]

H_PECI[15,37]

H_SKTOCC_N[37]

TP35TP35

TP44TP44

TP18TP18

TP31TP31

TP20TP20

TP45TP45

TP26TP26

TP41TP41

TP28TP28

TP22TP22

TP38TP38

TP17TP17

TP25TP25

TP40TP40

1.5V_S3

CLK_100M_CPU

CLK_100M_CPU#

VIDALERT_N

H_PWRGD

PWRGD_DRAM_R

PLTRST_CPU_N_R

H_PM_SYNC_0

H_PECI

H_CATERR_N

H_PROCHOT_N

H_THERMTRIP_N

H_SKTOCC_N

FM_PROCSEL_DMI_TERM

SM_VREF

PD_TEST_CPU_0

PD_TEST_CPU_1 XDP_CPU_MBP_N1

1

PD_TEST_CPU_2

PD_TEST_CPU_3

1

PD_TEST_CPU_4

1

PD_TEST_CPU_5

PD_TEST_CPU_6

PD_TEST_CPU_7

1

PD_TEST_CPU_8

1

PD_TEST_CPU_9

1

PD_TEST_CPU_10

1

PD_TEST_CPU_11

1

PD_TEST_CPU_12

1

PD_TEST_CPU_13

1

PD_TEST_CPU_14

1

PD_TEST_CPU_15

1

PD_TEST_CPU_16

1

PD_TEST_CPU_17

1

R42

R42

100R/F_4

100R/F_4

R43

R43

100R/F_4

100R/F_4

R11

R11

R9

R9

110/F_4

110/F_4

*54.9R/F_4

*54.9R/F_4

D D

H_VIDSCK

H_VIDSOUT

CAD NOTE:

PLACE NEAR CPU

PWRGD_DRAM[16]

PLTRST_CPU_N[10,16]

CAD NOTE:

PLACE NEAR CPU

1.5V_S3 1.05V_VCCIO

C C

B B

R482

R482

*1K/F_4

*1K/F_4

PWRGD_DRAM H_PWRGD

C353

C353

1u/6.3V_4

1u/6.3V_4

R463 200R_4R463 200R_4

R17 1K/F_4R17 1K/F_4

R473 *1K/F_4R473 *1K/F_4

R18 *1K/F_4R18 *1K/F_4

H_VIDALERT_N

PWRGD_DRAM

R16

R16

100R/F_4

100R/F_4

R19

R19

*1K/F_4

*1K/F_4

C4

*1u/6.3V_4C4*1u/6.3V_4

C3

C3

*0.1U/16V_4

*0.1U/16V_4

R6

1K/F_4R61K/F_4

PD_TEST_CPU_2

PD_TEST_CPU_5

PD_TEST_CPU_6

R4

75R/F_4R475R/F_4

R481 120R/F_4R481 120R/F_4

VR_HOT#[40]

PD_TEST_CPU_0[10]

D1 1N4148WSD1 1N4148WS

CAD NOTE:

MINIMIZE STUB BETWEEN THESE AND RESISTORS AT SINAI PAGE

SM_VREF

C24

C24

0.1u/16V_4

0.1u/16V_4

H_VIDSCK_VR[40]

H_VIDSOUT_VR[40]

H_VIDALERT_N_VR[40]

XU1E

XU1E

W2

BCLK_0

W1

BCLK_N0

C37

VIDSCLK

B37

VIDSOUT

A37

VIDALERT_N

J40

UNCOREPWRGOOD

AJ19

SM_DRAMPWROK

F36

RESET_N

E38

PM_SYNC

J35

PECI

E37

CATERR_N

H34

PROCHOT_N

G35

THERMTRIP_N

AJ33

SKTOCC_N

K32

PROC_SEL

AJ22

SM_VREF

H36

CFG_0

J36

CFG_1

J37

CFG_2

K36

CFG_3

L36

CFG_4

N35

CFG_5

L37

CFG_6

M36

CFG_7

J38

CFG_8

L35

CFG_9

M38

CFG_10

N36

CFG_11

N38

CFG_12

N39

CFG_13

N37

CFG_14

N40

CFG_15

G37

CFG_16

G36

CFG_17

AT14

RSVD_16

AY3

RSVD_23

H7

RSVD_28

H8

RSVD_29

H_VIDSCK_VR H_VIDSCK

H_VIDSOUT_VR H_VIDSOUT

H_VIDALERT_N_VR

VCCAXG_SENSE

VSSAXG_SENSE

LGA1155

LGA1155

VCCSA_VID

VCCSA_SENSE

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSSIO_SENSE

TDO

TCK

TMS

TRST_N

PRDY_N

PREQ_N

DBR_N

RSVD_1

RSVD_2

BPM_N0

BPM_N1

BPM_N2

BPM_N3

BPM_N4

BPM_N5

BPM_N6

BPM_N7

RSVD_24

RSVD_30

RSVD_37

RSVD_36

RSVD_33

RSVD_40

RSVD_39

RSVD_18

RSVD_20

RSVD_38

RSVD_32

RSVD_34

RSVD_35

RSVD_50

RSVD_53

RSVD_51

RSVD_52

R2 0R_4R2 0R_4

R12 0R_4R12 0R_4

R3 0R_4R3 0R_4

P34

T2

A36

B36

AB4

AB3

L32

M32

L39

L40

TDI

M40

L38

J39

K38

K40

E39

C40

D40

H40

H38

G38

G40

G39

F38

E40

F40

B39

J33

L34

L33

K34

N33

M34

AV1

AW2

L9

J9

K9

L31

J31

K31

AD34

AD35

XDP_CPU_DBRESET_N

CLK_100M_CPU_ITP_DP

CLK_100M_CPU_ITP_DN

XDP_CPU_MBP_N0

XDP_CPU_MBP_N2

XDP_CPU_MBP_N3

XDP_CPU_MBP_N4

XDP_CPU_MBP_N5

XDP_CPU_MBP_N6

XDP_CPU_MBP_N7

Z1218

Z1219

Z1220

Z1221

H_VIDALERT_N

VR_PVCCUSA_SEL

VCCSA_SENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE+

VTT_SENSE-

VCCAXG_SENSE

VSSAXG_SENSE

R52 0R_4R52 0R_4

R259 0R_4R259 0R_4

R460 0R_4R460 0R_4

R705 0R_4R705 0R_4

R721 0R_4R721 0R_4

R722 0R_4R722 0R_4

R723 0R_4R723 0R_4

TP49TP49

TP50TP50

TP43TP43

TP36TP36

ET-0329-09

VR_PVCCUSA_SEL [43]

VCCSA_SENSE [43]

VCC_SENSE [40]

VSS_SENSE [40]

VTT_SENSE+ [43]

VTT_SENSE- [43]

VCCAXG_SENSE [40]

VSSAXG_SENSE [40]

XDP_CPU_TDO

XDP_CPU_TDI

XDP_CPU_TCLK0

XDP_CPU_TMS

XDP_CPU_TRST_N

XDP_CPU_PRDY_N

XDP_CPU_PREQ_N

R13 0R_4R13 0R_4

CLK_100M_CPU_ITP_DP [12]

CLK_100M_CPU_ITP_DN [12]

XDP_CPU_MBP_N[0:7] [10]

H_PWRGD

H_PECI

H_THERMTRIP_N

H_PROCHOT_N

H_CATERR_N

R422 *10K/F_4R422 *10K/F_4

CAD NOTE: PLACE

NEXT TO CPU

R8

R21

R21

51R/F_4R851R/F_4

51R/F_4

51R/F_4

R20

R20

R22

R22

51R/F_4

51R/F_4

R471

R471

R7

*1K/F_4

*1K/F_4

*51R/F_4R7*51R/F_4

H_SKTOCC_N

3V_S51.05V_VCCIO

R5

*220R_4R5*220R_4

51R/F_4

51R/F_4

CAD NOTE: PLACE

NEXT TO CPU

R14

R14

R474

R474

51R/F_4

51R/F_4

*51R/F_4

*51R/F_4

R23 10K/F_4R23 10K/F_4

XDP_CPU_TDO [10]

XDP_CPU_TDI [10]

XDP_CPU_TCLK0 [10]

XDP_CPU_TMS [10]

XDP_CPU_TRST_N [10]

XDP_CPU_PRDY_N [10]

XDP_CPU_PREQ_N [10]

FP_RST_PCH_N [16]

1.05V_VCCIO

R15

R15

*1K/F_4

*1K/F_4

3.3V

The CFG signals have a default value of '1' if not erminated on

the board

CFG[1:0]

CFG[2]

CFG[3]

CFG[4]

A A

CFG[5:6]

CFG[17:7]

RVSD/TP

0

RVSD/TP

RVSD/TP

11

RVSD/TP

Reserved

configuration lane

PCI Express* Static x16 Lane

Numbering Reversal.

1 = Normal operation 0 = Lane

PCI Express* Static x4 Lane

numbers reversed

Numbering Reversal.

Reserved

configuration lane

PCI Express Bifurcation

00 = 1 x8, 2 x4 PCI Express

01 = reserved

10 = 2 x8 PCI Express

11 = 1 x16 PCI Express

Reserved

configuration lane

5

H_THERMTRIP_N

1

Q1

R44

R44

*DIS@10K/F_4

*DIS@10K/F_4

3

2

GFX_CTF[23]

1 2

4

3

Q1

*DIS@2N7002

*DIS@2N7002

2

CPU

Internal

BPM[7:0] Pull Up VCCIO 65-165

PU/PD

PRDY# Pull Up VCCIO 65-165

PREQ# Pull Up VCCIO 65-165

TCK Pull Down VSS 5-15 k

TDI Pull Up VCCIO 5-15 k

TMS Pull Up VCCIO 5-15 k

TRST# Pull Up VCCIO 5-15 k

VCCSA_VID Pull Up VCCIO 5-15

k

CFG[17:0] Pull Up VCCIO 5-15 k

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SOCKET H2 CLK/CTRL/MISC/DE

SOCKET H2 CLK/CTRL/MISC/DE

SOCKET H2 CLK/CTRL/MISC/DE

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

QUA

QUA

QUA

7 48Monday, July 04, 2011

7 48Monday, July 04, 2011

7 48Monday, July 04, 2011

1

1A

1A

1A

5

2011C: 65W TDP desktop

and server/workstation SKUs

XU1F

XU1F

A12

VCC_1

A13

VCC_2

A14

VCC_3

A15

VCC_4

A16

VCC_5

A18

VCC_6

A24

VCC_7

A25

VCC_8

D D

C C

B B

1.05V_VCCIO

A27

VCC_9

A28

VCC_10

B15

VCC_11

B16

VCC_12

B18

VCC_13

B24

VCC_14

B25

VCC_15

B27

VCC_16

B28

VCC_17

B30

VCC_18

B31

VCC_19

B33

VCC_20

B34

VCC_21

C15

VCC_22

C16

VCC_23

C18

VCC_24

C19

VCC_25

C21

VCC_26

C22

VCC_27

C24

VCC_28

C25

VCC_29

C27

VCC_30

C28

VCC_31

C30

VCC_32

C31

VCC_33

C33

VCC_34

C34

VCC_35

C36

VCC_36

D13

VCC_37

D14

VCC_38

D15

VCC_39

D16

VCC_40

D18

VCC_41

D19

VCC_42

D21

VCC_43

D22

VCC_44

D24

VCC_45

D25

VCC_46

D27

VCC_47

D28

VCC_48

D30

VCC_49

D31

VCC_50

D33

VCC_51

D34

VCC_52

D35

VCC_53

D36

VCC_54

E15

VCC_55

E16

VCC_56

E18

VCC_57

E19

VCC_58

E21

VCC_59

E22

VCC_60

E24

VCC_61

E25

VCC_62

E27

VCC_63

E28

VCC_64

E30

VCC_65

E31

VCC_66

E33

VCC_67

E34

VCC_68

E35

VCC_69

F15

VCC_70

F16

VCC_71

F18

VCC_72

F19

VCC_73

F21

VCC_74

F22

VCC_75

F24

VCC_76

F25

VCC_77

F27

VCC_78

F28

VCC_79

F30

VCC_80

F31

VCC_81

LGA1155

LGA1155

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

VCC_124

VCC_125

VCC_126

VCC_127

VCC_128

VCC_129

VCC_130

VCC_131

VCC_132

VCC_133

VCC_134

VCC_135

VCC_136

VCC_137

VCC_138

VCC_139

VCC_140

VCC_141

VCC_142

VCC_143

VCC_144

VCC_145

VCC_146

VCC_147

VCC_148

VCC_149

VCC_150

VCC_151

VCC_152

VCC_153

VCC_154

VCC_155

VCC_156

VCC_157

VCC_158

VCC_159

VCC_160

VCC_161

F32

F33

F34

G15

G16

G18

G19

G21

G22

G24

G25

G27

G28

G30

G31

G32

G33

H13

H14

H15

H16

H18

H19

H21

H22

H24

H25

H27

H28

H30

H31

H32

J12

J15

J16

J18

J19

J21

J22

J24

J25

J27

J28

J30

K15

K16

K18

K19

K21

K22

K24

K25

K27

K28

K30

L13

L14

L15

L16

L18

L19

L21

L22

L24

L25

L27

L28

L30

M14

M15

M16

M18

M19

M21

M22

M24

M25

M27

M28

M30

VCC:75A max

VCCIO:8.5A max

VCCSA:8.8A max

VCCPLL:1.5A max

0.925V_VCCSA 1.8V

C34

C34

10u/10V_8

10u/10V_8

0.925V_VCCSA

C25

C25

10u/10V_8

10u/10V_8

1.05V_VCCIO

1.8V

4

1.5V_S3CPU_CORE CPU_CORE

XU1H

XU1H

M13

VCCIO_34

A11

VCCIO_1

A7

VCCIO_2

AA3

VCCIO_3

AB8

VCCIO_4

AF8

VCCIO_5

AG33

VCCIO_6

AJ16

VCCIO_7

AJ17

VCCIO_8

AJ26

VCCIO_9

AJ28

VCCIO_10

AJ32

VCCIO_11

AK15

VCCIO_12

AK17

VCCIO_13

AK19

VCCIO_14

AK21

VCCIO_15

AK23

VCCIO_16

AK27

VCCIO_17

AK29

VCCIO_18

AK30

VCCIO_19

B9

VCCIO_20

D10

VCCIO_21

D6

VCCIO_22

E3

VCCIO_23

E4

VCCIO_24

G3

VCCIO_25

G4

VCCIO_26

J3

VCCIO_27

J4

VCCIO_28

J7

VCCIO_29

J8

VCCIO_30

L3

VCCIO_31

L4

VCCIO_32

L7

VCCIO_33

N3

VCCIO_35

N4

VCCIO_36

N7

VCCIO_37

R3

VCCIO_38

R4

VCCIO_39

R7

VCCIO_40

U3

VCCIO_41

U4

VCCIO_42

U7

VCCIO_43

V8

VCCIO_44

W3

VCCIO_45

H10

VCCSA_1

H11

VCCSA_2

H12

VCCSA_3

J10

VCCSA_4

K10

VCCSA_5

K11

VCCSA_6

L11

VCCSA_7

L12

VCCSA_8

M10

VCCSA_9

M11

VCCSA_10

M12

VCCSA_11

AK11

VCCPLL_1

AK12

VCCPLL_2

LGA1155

LGA1155

C367

C367

C373

C373

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

VDDQ_1

VDDQ_2

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

VDDQ_3

POWER

POWER

C381

C381

10u/10V_8

10u/10V_8

1.05V_VCCIO

AJ13

AJ14

AJ23

AJ24

AR20

AR21

AR22

AR23

AR24

AU19

AU23

AU27

AU31

AV21

AV24

AV25

AV29

AV33

AW31

AY23

AY26

AY28

AJ20

VDDQ:4.75A max

change to 22u from 10u,add C690/C691/692,add 330uF

03/24 Jerry

C20

C20

C38

C38

10u/10V_8

10u/10V_8

CAD note: Place on back side

3

BOM note:

EV@Cavity need

to stuff 0ohm RES

CPU_AXG

C331

C331

C332

C332

UMA@22u/6.3V_8

UMA@22u/6.3V_8

UMA@22u/6.3V_8

UMA@22u/6.3V_8

change to 22u from 10u

03/24 Jerry

C16

C16

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

CAVITY

C333

UMA@22u/6.3V_8

UMA@22u/6.3V_8

UMA@22u/6.3V_8C8UMA@22u/6.3V_8

UMA@22u/6.3V_8

UMA@22u/6.3V_8

UMA@22u/6.3V_8C9UMA@22u/6.3V_8

<Sean0327> add

UMA@

UMA@22u/6.3V_8

UMA@22u/6.3V_8

C10

C10

C9

C8

C11

C11

C333

PLACE BACKSIDE OF MCP CAVITY

VCCAXG:35A max

CPU_CORE

C31

C31

C349

C349

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

C377

C377

C383

C383

10u/10V_8

10u/10V_8

CPU_CORE

10u/10V_8

10u/10V_8

C27

C27

C345

C345

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

2

CPU_AXG

C29

C29

22u/6.3V_8

22u/6.3V_8

C19

C19

22u/6.3V_8

22u/6.3V_8

AB33

AB34

AB35

AB36

AB37

AB38

AB39

AB40

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

W33

W34

W35

W36

W37

W38

T33

T34

T35

T36

T37

T38

T39

T40

U33

U34

U35

U36

U37

U38

U39

U40

Y33

Y34

Y35

Y36

Y37

Y38

XU1G

XU1G

VCCAXG_1

VCCAXG_2

VCCAXG_3

VCCAXG_4

VCCAXG_5

VCCAXG_6

VCCAXG_7

VCCAXG_8

VCCAXG_9

VCCAXG_10

VCCAXG_11

VCCAXG_12

VCCAXG_13

VCCAXG_14

VCCAXG_15

VCCAXG_16

VCCAXG_17

VCCAXG_18

VCCAXG_19

VCCAXG_20

VCCAXG_21

VCCAXG_22

VCCAXG_23

VCCAXG_24

VCCAXG_25

VCCAXG_26

VCCAXG_27

VCCAXG_28

VCCAXG_29

VCCAXG_30

VCCAXG_31

VCCAXG_32

VCCAXG_33

VCCAXG_34

VCCAXG_35

VCCAXG_36

VCCAXG_37

VCCAXG_38

VCCAXG_39

VCCAXG_40

VCCAXG_41

VCCAXG_42

VCCAXG_43

VCCAXG_44

LGA1155

LGA1155

C32

C32

22u/6.3V_8

22u/6.3V_8

C335

C335

22u/6.3V_8

22u/6.3V_8

1

C361

C361

C340

C340

22u/6.3V_8

22u/6.3V_8

C26

C26

22u/6.3V_8

22u/6.3V_8

+

+

22u/6.3V_8

22u/6.3V_8

C707

C707

330uF/SP-cap

330uF/SP-cap

C17

C17

22u/6.3V_8

22u/6.3V_8

C336

C334

C334

C33

C33

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

C336

C362

C362

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

C28

C28

C40

C12

C12

10u/10V_8

10u/10V_8

C40

10u/10V_8

10u/10V_8

10u/6.3V_6

10u/6.3V_6

C369

C369

C35

C35

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

C36

C36

C39

C39

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

C15

C15

C342

C18

C18

10u/10V_8

10u/10V_8

C342

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

CPU_CORE

C23

C23

22u/6.3V_8

22u/6.3V_8

C690

C360

C360

C14

C30

C30

22u/6.3V_8

22u/6.3V_8

C14

C355

C355

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

C690

C354

C354

22u/6.3V_8

22u/6.3V_8

C692

C692

C691

C691

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

22u/6.3V_8

DESIGN NOTE:

NET PROCESSOR

CPU_CORE

CPU_AXG

A A

1.05V_VCCIO

0.925V_VCCSA

1.5V_S3

1.8V

5

SVID

SVID

1.05V

0.925V

1.5V

1.8V

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SOCKET H2 VCCP

SOCKET H2 VCCP

SOCKET H2 VCCP

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

PROJECT :

QUA

QUA

QUA

8 48Monday, July 04, 2011

8 48Monday, July 04, 2011

8 48Monday, July 04, 2011

1

1A

1A

1A

5

XU1I

XU1I

A17

VSS_1

A23

VSS_2

A26

VSS_3

A29

VSS_4

A35

VSS_5

AA33

VSS_6

D D

C C

B B

A A

AA34

VSS_7

AA35

VSS_8

AA36

VSS_9

AA37

VSS_10

AA38

VSS_11

AA6

VSS_12

AB5

VSS_13

AC1

VSS_14

AC6

VSS_15

AD33

VSS_16

AD36

VSS_17

AD38

VSS_18

AD39

VSS_19

AD40

VSS_20

AD5

VSS_21

AD8

VSS_22

AE3

VSS_23

AE33

VSS_24

AE36

VSS_25

AF1

VSS_26

AF34

VSS_27

AF36

VSS_28

AF37

VSS_29

AF40

VSS_30

AF5

VSS_31

AF6

VSS_32

AF7

VSS_33

AG36

VSS_34

AH2

VSS_35

AH3

VSS_36

AH33

VSS_37

AH36

VSS_38

AH37

VSS_39

AH38

VSS_40

AH39

VSS_41

AH40

VSS_42

AH5

VSS_43

AH8

VSS_44

AJ12

VSS_45

AJ15

VSS_46

AJ18

VSS_47

AJ21

VSS_48

AJ25

VSS_49

AJ27

VSS_50

AJ36

VSS_51

AJ5

VSS_52

AK1

VSS_53

AK10

VSS_54

AK13

VSS_55

AK14

VSS_56

AK16

VSS_57

AK22

VSS_58

AK28

VSS_59

AK31

VSS_60

AK32

VSS_61

AK33

VSS_62

AK34

VSS_63

AK35

VSS_64

AK36

VSS_65

AK37

VSS_66

AK4

VSS_67

AK40

VSS_68

AK5

VSS_69

AK6

VSS_70

AK7

VSS_71

AK8

VSS_72

AK9

VSS_73

AL11

VSS_74

AL14

VSS_75

AL17

VSS_76

AL19

VSS_77

AL24

VSS_78

AL27

VSS_79

AL30

VSS_80

AL36

VSS_81

AL5

VSS_82

AM1

VSS_83

AM11

VSS_84

AM14

VSS_85

AM17

VSS_86

AM2

VSS_87

AM21

VSS_88

AM23

VSS_89

AM25

VSS_90

VSS_NCTF_1A4VSS_NCTF_2

LGA1155

LGA1155

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

AM27

AM3

AM30

AM36

AM37

AM38

AM39

AM4

AM40

AM5

AN10

AN11

AN14

AN17

AN19

AN22

AN24

AN27

AN30

AN31

AN32

AN33

AN34

AN35

AN36

AN5

AN6

AN7

AN8

AN9

AP1

AP11

AP14

AP17

AP22

AP25

AP27

AP30

AP36

AP37

AP4

AP40

AP5

AR11

AR14

AR17

AR18

AR19

AR27

AR30

AR36

AR5

AT1

AT10

AT12

AT13

AT15

AT16

AT17

AT2

AT25

AT27

AT28

AT29

AT3

AT30

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AT39

AT4

AT40

AT5

AT6

AT7

AT8

AT9

AU1

AU15

AU26

AU34

AU4

AU6

AU8

AV10

AV39

AV11

AV14

AV17

AV3

AV35

AV38

AV6

AW10

AW11

AW14

AW16

AW36

AW6

AY11

AY14

AY18

AY35

AY4

AY6

AY8

B10

B13

B14

B17

B23

B26

B29

B32

B35

B38

C11

C12

C17

C20

C23

C26

C29

C32

C35

D17

D20

D23

D26

D29

D32

D37

D39

E11

E12

E17

E20

E23

E26

E29

E32

E36

F10

F13

F14

F17

F20

F23

F26

F29

F35

F37

F39

G11

G12

G17

G20

G23

G26

G29

G34

AY37

B6

C7

C8

D2

D4

D5

D9

E7

E8

F1

F2

F5

F6

F9

G7

LGA1155

LGA1155

XU1J

XU1J

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_NCTF_3

4

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357

VSS_358

VSS_359

VSS_360

VSS_NCTF_4

G8

H1

H17

H2

H20

H23

H26

H29

H33

H35

H37

H39

H5

H6

H9

J11

J17

J20

J23

J26

J29

J32

K1

K12

K13

K14

K17

K2

K20

K23

K26

K29

K33

K35

K37

K39

K5

K6

L10

L17

L20

L23

L26

L29

L8

M1

M17

M2

M20

M23

M26

M29

M33

M35

M37

M39

M5

M6

M9

N8

P1

P2

P36

P38

P40

P5

P6

R33

R35

R37

R39

R8

T1

T5

T6

U8

V1

V2

V33

V34

V35

V36

V37

V38

V39

V40

V5

W6

Y5

Y8

B3

3

2

DE NOTE:

DQ VREF OPTION 1 - VOLTAGE DIVIDER GENERATED -- Page 8

DQ VREF OPTION 2 - PROGRAMMABLE DAC GENERATED -- Removed

DQ VREF OPTION 3 - CPU GENERATED -- This Page

TO MAINTAIN CONSISTENCY

AH4 FOR CHANNEL A DDR_VREF, AH1 FOR CHANNEL B

XU1K

TP58TP58

TP32TP32

TP60TP60

TP51TP51

TP48TP48

TP47TP47

TP4TP4

TP3TP3

VTT_SEL[43]

TP39TP39

TP29TP29

TP19TP19

TP46TP46

TP33TP33

TP27TP27

TP15TP15

TP30TP30

TP1TP1

TP2TP2

TP62TP62

TP63TP63

DE NOTE:

STUFF ALL FOUR EMPTY RESISTOR,AND THE UPSTREAM ONE TO USE CPU VREF DQ B TO DRIVE VREF CA A AND B

NEED TO UNSTUFF THE APPROPRIATE RESISTORS ON PAGE 16 AND 17

STUFF THE LOWER THREE EMPTY RESISTOR TO USE DIG. POT. VREF DQ B TO DRIVE VREF CA A AND B

NEED TO UNSTUFF THE APPROPRIATE RESISTORS ON PAGE 16 AND 17

Z1502

1

Z1503

1

Z1504

1

Z1505

1

Z1506

1

Z1507

1

Z1508

1

VTT_SEL

Z1509

1

Z1510

1

Z1511

1

Z1512

1

Z1513

1

Z1514

1

Z1515

1

Z1516

1

Z1517

1

Z1518

1

Z1519

1

Z1520

1

U35

U35

Z1501

1

AB7

AD37

AG4

AJ29

AJ30

AJ31

AV34

AW34

P33

P35

P37

P39

R34

R36

R38

R40

A38

AU40

AW38

C2

D1

CPU BKT/31BOM

CPU BKT/31BOM

XU1K

RSVD_4

RSVD_5

RSVD_8

RSVD_10

RSVD_11

RSVD_12

RSVD_19

RSVD_21

RSVD_42

RSVD_43

RSVD_44

RSVD_45

RSVD_46

RSVD_47

RSVD_48

RSVD_49

NCTF_1

NCTF_2

NCTF_3

NCTF_4

NCTF_5

LGA1155

LGA1155

SPARES

SPARES

FC_AH1

FC_AH4

RSVD_15

RSVD_14

RSVD_13

RSVD_17

RSVD_22

RSVD_7

RSVD_3

RSVD_6

RSVD_9

RSVD_27

RSVD_26

RSVD_25

RSVD_31

RSVD_41

DIMM_VREFB

AH1

DIMM_VREFA

AH4

Z1521

AT11

AP20

AN20

AU10

AY10

Z1522

Z1523

Z1524

Z1525

1

TP7TP7

1

TP52TP52

1

TP53TP53

1

TP8TP8

1

TP9TP9

CAD NOTE: PLACE NEAR CPU PINS

Z1526

AF4

Z1527

AB6

Z1528

AE6

Z1529

AJ11

Z1530

D38

Z1531

C39

Z1532

C38

Z1533

J34

PD_CPU_RSVD_4_N34

N34

U36

U36

CPU Frame Cover/31BOM

CPU Frame Cover/31BOM

1

TP61TP61

1

TP59TP59

1

TP57TP57

1

TP56TP56

1

TP37TP37

1

TP16TP16

1

TP24TP24

1

TP42TP42

C54

C54

0.1u/25V_4

0.1u/25V_4

R472

R472

24.9R/F_4

24.9R/F_4

C53

C53

0.1u/25V_4

0.1u/25V_4

R53 *0R_4R53 *0R_4

R57 *0R_4R57 *0R_4

1

VREF_DQ_DDRB [11]

VREF_DQ_DDRA [11]

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SOCKET H2 GND

SOCKET H2 GND

SOCKET H2 GND

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

QUA

QUA

QUA

1A

1A

9 48Monday, July 04, 2011

9 48Monday, July 04, 2011

9 48Monday, July 04, 2011

1

1A

1

A A

2

H_PWRGD[7,16]

EC_PWRBTN_OUT#[16,37]

PD_TEST_CPU_0[7]

PCH_SYSPWROK[16]

SMB_DAT_DEVICE[11,16,31,35]

SMB_CLK_DEVICE[11,16,31,35]

XDP_CPU_TCLK0[7]

SMB_DAT_DEVICE

SMB_CLK_DEVICE

XDP_CPU_PREQ_N[7]

XDP_CPU_PRDY_N[7]

XDP_CPU_MBP_N[0:7][7]

H_PWRGD

PD_TEST_CPU_0

XDP_CPU_TCLK0

3

R24 *1K/F_4R24 *1K/F_4

R25 *0R_4R25 *0R_4

R464 *1K/F_4R464 *1K/F_4

R26 *0R_4R26 *0R_4

R27 *0R_4R27 *0R_4

R28 *0R_4R28 *0R_4

XDP_CPU_PREQ_N

XDP_CPU_PRDY_N

XDP_CPU_MBP_N0

XDP_CPU_MBP_N1

XDP_CPU_MBP_N2

XDP_CPU_MBP_N3

XDP_CPU_MBP_N4

XDP_CPU_MBP_N5

XDP_CPU_MBP_N6

XDP_CPU_MBP_N7

XDP_PWRGD

XDP_BP_PWRGD_RST_N

XDP_CPU_EAR_R

XDP_SYS_PWROK_R_N

XDP_CPU_SMBDAT

XDP_CPU_SMBCLK

4

CN2

CN2

1

1

2

3

3

4

5

5

6

7

7

8

9

9

10

11

11

12

13

13

14

15

15

16

17

17

18

19

19

20

21

21

22

23

23

24

25

25

26

27

27

28

29

29

30

31

31

32

33

33

34

35

35

36

37

37

38

39

39

40

41

41

42

43

43

44

45

45

46

47

47

48

49

49

50

51

51

52

53

53

54

55

55

56

57

57

58

59

59

C308

C308

*CN XDP SMD 60P(P0.5,H3.25)

*CN XDP SMD 60P(P0.5,H3.25)

*1u/6.3V_4

*1u/6.3V_4

60

5

1.05V_VCCIO1.05V_VCCIO

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

CLK_100M_XDP_HEADER_DP

CLK_100M_XDP_HEADER_DN

XDP_CPU_RST_N PLTRST_CPU_N

XDP_CPU_TRST_N

XDP_CPU_TDI

XDP_CPU_TMS

PU_XDP_CPU_PRESENT_N

R462 *1K/F_4R462 *1K/F_4

6

CLK_100M_XDP_HEADER_DP [12]

CLK_100M_XDP_HEADER_DN [12]

XDP_CPU_TDO

R1 *1K/F_4R1 *1K/F_4

3V_S5

1.05V_VCCIO

R461

R461

51R/F_4

51R/F_4

7

NOTE: PLACE

NEXT TO XDP

PLTRST_CPU_N [7,16]

XDP_CPU_TDO [7]

XDP_CPU_TRST_N [7]

XDP_CPU_TDI [7]

XDP_CPU_TMS [7]

8

B B

C C

D D

<Sean0327> add *

PCH_PWRGD[15,16]

PCH_XDP_100M[12]

PCH_XDP_100M#[12]

XDP_PCH_TCK0[16]

EC_PWRBTN_OUT#

PCH_XDP_100M

PCH_XDP_100M#

SMB_DAT_DEVICE

SMB_CLK_DEVICE

XDP_PCH_TCK0

R41 *1K/F_4R41 *1K/F_4

R39 *0R_4R39 *0R_4

R37 *0R_4R37 *0R_4

R34 *0R_4R34 *0R_4

TP21TP21

PCH_PWRGD_XDP

XDP_PCH_HK1

XDP_PCH_SMBDAT

XDP_PCH_SMBCLK

TP_XDP_PCH_TCK1

1

3V_S5 3V_S5

CN4

CN4

1

1

3

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

21

21

23

23

25

25

27

27

29

29

31

31

33

33

35

35

37

37

39

39

41

41

43

43

45

45

47

47

49

49

51

51

53

53

55

55

57

57

59

C6

*1u/6.3V_4C6*1u/6.3V_4

59

*CN XDP SMD 60P(P0.5,H3.25)

*CN XDP SMD 60P(P0.5,H3.25)

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

32

32

34

34

36